JP2006139295A - Liquid crystal display - Google Patents

Liquid crystal display Download PDFInfo

- Publication number

- JP2006139295A JP2006139295A JP2005358174A JP2005358174A JP2006139295A JP 2006139295 A JP2006139295 A JP 2006139295A JP 2005358174 A JP2005358174 A JP 2005358174A JP 2005358174 A JP2005358174 A JP 2005358174A JP 2006139295 A JP2006139295 A JP 2006139295A

- Authority

- JP

- Japan

- Prior art keywords

- liquid crystal

- substrate

- pixel

- display device

- crystal display

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Liquid Crystal (AREA)

- Liquid Crystal Display Device Control (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

Abstract

Description

本発明は新規な構成を持つ液晶表示装置に関する。 The present invention relates to a liquid crystal display device having a novel configuration.

従来の液晶表示装置は、ツイステッドネマチック(TN)表示モードに代表されるように、基板面に対してほぼ垂直な電界を印加する表示モードを採用している。しかし、TN表示モードでは、視野角特性が不十分であるという問題がある。一方、インプレーン・スイッチング(In−PlaneSwitching:IPS)表示モードが、特公昭63−21907号、USP4345249号、WO91/10936号、特開平6−160878号等の公報により提案されている。 Conventional liquid crystal display devices employ a display mode in which an electric field substantially perpendicular to the substrate surface is applied, as represented by a twisted nematic (TN) display mode. However, the TN display mode has a problem that viewing angle characteristics are insufficient. On the other hand, in-plane switching (IPS) display modes have been proposed in Japanese Patent Publication Nos. 63-21907, USP 4345249, WO 91/10936, and Japanese Patent Laid-Open No. 6-160878.

このIPS表示モードでは、液晶駆動用の電極が液晶を挟持する一対の基板のうち一方の基板上に形成され、液晶には基板面に対して平行な成分を持つ電界が印加される。このIPS表示モードでは、TN表示モードに比較して広い視野角が得られる。しかしながら、IPS表示モードにおいても色調が視角に応じて変化するという問題を持っている。この問題を解決するマルチドメインIPS表示モードが特開平9−258269等の公報により提案されている。このマルチドメインIPS表示モードによる液晶表示装置を図2、図3、および図4を用いて説明する。 In this IPS display mode, the liquid crystal driving electrode is formed on one of the pair of substrates sandwiching the liquid crystal, and an electric field having a component parallel to the substrate surface is applied to the liquid crystal. In this IPS display mode, a wider viewing angle can be obtained than in the TN display mode. However, even in the IPS display mode, there is a problem that the color tone changes according to the viewing angle. A multi-domain IPS display mode that solves this problem has been proposed in Japanese Patent Laid-Open No. 9-258269. A liquid crystal display device according to the multi-domain IPS display mode will be described with reference to FIGS. 2, 3, and 4. FIG.

図2はマルチドメインIPS表示モードによる液晶表示装置の構成を示す図である。画素電極35に信号電位を供給する信号ドライバ51と、画素を選択する電位を供給する走査ドライバ52と、共通電極36に電位を供給する共通電極ドライバ54と、信号ドライバ51および走査ドライバ52および共通電極ドライバ54とを制御する表示制御装置53とを有している。

FIG. 2 is a diagram illustrating a configuration of a liquid crystal display device in a multi-domain IPS display mode. A

基板1には、走査ドライバ52に接続された複数の走査線32と、信号ドライバ51に接続され、かつ走査線32と交差した信号線31と、走査線32と信号線31との交点付近に対応して配置され、走査線32と信号線31と電気的に接続された第1TFT33と、第1TFT33に電気的に接続され、信号線31に対応した画素電極35と、画素電極35に対応した共通電極36と、共通電極36と共通電極ドライバ54とに電気的に接続された共通電極接続部36’が備えられている。信号線31と走査線32とに囲まれた領域に対応して画素11が形成され、複数の画素11によって表示部22が形成されている。

In the

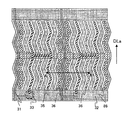

図3はマルチドメインIPS表示モードによる液晶表示装置の画素近傍の回路配置パタン構成を示す図である。走査線32と信号線31とは互いに交差し、走査線32と信号線31とに囲まれた領域に対応して画素11が形成されている。第1TFT33は走査線32と信号線31との交点付近に対応して配置され、走査線32と信号線31と画素電極35とに電気的に接続されている。共通電極36は画素電極35に対応して配置され、共通電極36と画素電極35とで基板面に対して平行な成分を持つ電界を発生する。画素電極35と共通電極36と信号線31は一つの画素内で1回以上折れ曲がり、マルチドメインを形成している。電界印加時の液晶の回転方向を隣合うドメイン同士で反対方向とし、視野角を広げるためである。

FIG. 3 is a diagram showing a circuit arrangement pattern configuration in the vicinity of a pixel of the liquid crystal display device in the multi-domain IPS display mode. The

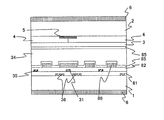

図4は、図3のA−A’断面の断面図である。材質が透明ガラスの基板1と、基板1に対向配置され、材質が透明ガラスの基板2と、基板1と基板2とで狭持された液晶層34とを有する。基板1は、共通電極36と、第1絶縁膜81を介し共通電極36よりも上層に配置された信号線31と、共通電極36に対応し、基板1面に対して平行な成分を持つ電界を発生する画素電極35と、画素電極35上に備えられた保護膜82と、保護膜82上に備えられた配向膜85と、基板1の液晶に面しない側の面上に備えられ、液晶の配向状態に応じて光学特性を変える手段である偏光板6とを有する。基板2は、不要な間隙部からの光を遮光する遮光膜5と、遮光膜5上に備えられ、R、G、Bに対応した色を表現するカラーフィルタ4と、カラーフィルタ4上に備えられ、凹凸を平坦化する平坦化膜3と、平坦化膜上3に備えられた配向膜85と、基板2の液晶に面しない側の面上に備えられた偏光板6とを有する。

FIG. 4 is a cross-sectional view taken along the line A-A ′ of FIG. 3. A

配向膜85には液晶を配向させるためのラビング処理が施されている。ラビング方向は信号線の延伸方向DLaに平行である。屈曲した画素電極の一辺とラビング方向とのなす角は15度であり、IPS表示モードに対応している。偏光板6の透過軸は、それぞれの偏光板が配置されている基板上の配向膜のラビング方向に対して平行あるいは垂直に向けられており、基板1の偏光板と基板2の偏光板はクロスニコルに配置され、ノーマリーブラックモードに対応している。画像表示は、基板1面と平行な成分を持つ電界を共通電極36と画素電極35とによって液晶34に印加し、液晶34を基板1とほぼ平行な面内で回転させることによって行う。

The

近年、液晶表示装置への期待はPC(Personal Computer)モニターのみに向けたものではなく、動画に対応した液晶テレビへと拡大している。液晶テレビとしては、複数人で鑑賞できるように視野角の広いIPS表示モードが適していると考えられる。このIPS表示モードによる液晶表示装置において、より美しく動画を表示するためには、液晶の応答時間の短縮が望まれる。また、IPS表示モードでは、駆動電圧によって色調が変化するという問題もあり、これを解決することが望まれる。さらに、近年、液晶表示装置において、動画像の輪郭が不鮮明になるといった問題が指摘されている。 In recent years, expectations for liquid crystal display devices are not limited to PC (Personal Computer) monitors, but are expanding to liquid crystal televisions that support moving images. As a liquid crystal television, an IPS display mode with a wide viewing angle is suitable for viewing by a plurality of people. In the liquid crystal display device using the IPS display mode, in order to display a moving image more beautifully, it is desired to shorten the response time of the liquid crystal. In the IPS display mode, there is a problem that the color tone changes depending on the drive voltage, and it is desired to solve this problem. Further, in recent years, a problem has been pointed out that the outline of a moving image becomes unclear in a liquid crystal display device.

よって、本発明の第1の目的は、新規な画素構造により液晶の応答時間の短縮を図ることにある。また、本発明の第2の目的は、駆動電圧に伴う色調変化の生じない液晶表示装置を提供することにある。さらに、本発明の第3の目的は、動画像の輪郭が鮮明な液晶表示装置を提供することにある。 Therefore, the first object of the present invention is to shorten the response time of the liquid crystal by a novel pixel structure. A second object of the present invention is to provide a liquid crystal display device that does not cause a change in color tone due to a drive voltage. Furthermore, a third object of the present invention is to provide a liquid crystal display device in which the outline of a moving image is clear.

請求項1記載の発明は、光源、及び第1基板と、前記第1基板に対向配置された第2基板と、前記第1基板と前記第2基板とで狭持された液晶層と、前記第1基板上に配置された複数の走査線と、前記第1基板上に前記走査線と交差して配置された信号線と、前記走査線と前記信号線とに囲まれた領域に対応して構成される画素と、前記第1基板上に配置され、前記信号線に対応した画素電極と、前記第1基板上または前記第2基板上に配置され、前記画素電極に対応した共通電極と、前記走査線と前記信号線との交点に対応して配置され、前記信号線と前記走査線と前記画素電極とに電気的に接続された第1アクティブ素子と、前記第1基板上に配置された絶縁膜とを有し、1画像を表示する1周期期間中に、前記走査線に順次パルス電圧を印加して、前記画素電極の全てに画像を表示するための電位を印加し、保持させた後、一定期間を置いて光源が点灯される液晶表示装置において、前記1周期期間中の最後にパルス電圧が印加される走査線に対応する画素の液晶の前記パルス電圧が印加される直前の状態が、その状態から各階調への応答時間の最大値が前記一定期間よりも短い状態であるようにする状態調整手段を設けたことを特徴とする。

The invention according to

光源が点灯される前の一定期間内に、全ての画素電極に画像を表示するための電位が正しく印加されるので、動画像の輪郭が鮮明になる。請求項2記載の発明は、請求項1に記載の液晶表示装置において、前記状態調整手段が、前記走査線に順次前記パルス電圧を印加する前に、前記画素電極の全てに同一の電圧を印加する手段であることを特徴とする。予め画素電極の全てに同一の電圧を印加することにより、各画素電極周辺の液晶を各階調への応答時間の最大値が前記一定期間よりも短い状態になるような状態にしておく。例えば、一定期間が5msであればその状態は0に近い階調であれば良く、一定期間が6msであれば、その状態は階調0〜63であれば良い。

Since a potential for displaying an image is correctly applied to all the pixel electrodes within a certain period before the light source is turned on, the outline of the moving image becomes clear. According to a second aspect of the present invention, in the liquid crystal display device according to the first aspect, the state adjusting unit applies the same voltage to all of the pixel electrodes before sequentially applying the pulse voltage to the scanning lines. It is a means to do. By applying the same voltage to all of the pixel electrodes in advance, the liquid crystal around each pixel electrode is brought into a state where the maximum response time to each gradation is shorter than the predetermined period. For example, if the fixed period is 5 ms, the state may be a gradation close to 0, and if the fixed period is 6 ms, the state may be the

請求項3記載の発明は、請求項1又は2に記載の液晶表示装置において、前記状態調整手段が、前記走査線に順次前記パルス電圧を印加する前に、前記画素電極の電位と前記共通電極の電位とを等しくする手段を有することを特徴とする。一定期間が5msであれば、共通電極の電位を0に近い階調に対応する電位に、一定期間が6msであれば、共通電極の電位を階調0〜63に対応する電位にして印加すれば良い。

According to a third aspect of the present invention, in the liquid crystal display device according to the first or second aspect, before the state adjusting unit sequentially applies the pulse voltage to the scanning lines, the potential of the pixel electrode and the common electrode It is characterized by having a means for equalizing the potential of If the fixed period is 5 ms, the potential of the common electrode is applied to a potential corresponding to a gradation close to 0, and if the fixed period is 6 ms, the potential of the common electrode is applied to a potential corresponding to

請求項4記載の発明は、液晶表示装置の駆動方法であって、光源、及び第1基板と、前記第1基板に対向配置された第2基板と、前記第1基板と前記第2基板とで狭持された液晶層と、前記第1基板上に配置された複数の走査線と、前記第1基板上に前記走査線と交差して配置された信号線と、前記走査線と前記信号線とに囲まれた領域に対応して構成される画素と、前記第1基板上に配置され、前記信号線に対応した画素電極と、前記第1基板上または前記第2基板上に配置され、前記画素電極に対応した共通電極と、前記走査線と前記信号線との交点に対応して配置され、前記信号線と前記走査線と前記画素電極とに電気的に接続された第1アクティブ素子と、前記第1基板上に配置された絶縁膜とを有し、1画像を表示する1周期期間中に、前記走査線に順次パルス電圧を印加して、前記画素電極の全てに画像を表示するための電位を印加し、保持させた後、一定期間を置いて光源が点灯される液晶表示装置の駆動方法において、前記1周期期間中の最後にパルス電圧が印加される走査線に対応する画素の液晶の状態を、その状態から各階調への応答時間の最大値が前記一定期間よりも短い状態であるように状態調整をした後に、前記走査線に順次パルス電圧を印加することを特徴とする。請求項1記載の液晶表示装置に対応する駆動方法である。

According to a fourth aspect of the present invention, there is provided a method for driving a liquid crystal display device, comprising: a light source; a first substrate; a second substrate disposed opposite to the first substrate; the first substrate; the second substrate; A plurality of scanning lines disposed on the first substrate, a signal line disposed across the scanning line on the first substrate, the scanning line and the signal A pixel configured corresponding to a region surrounded by a line, a pixel electrode disposed on the first substrate and corresponding to the signal line, and disposed on the first substrate or the second substrate. A first active electrode disposed corresponding to the intersection of the scanning line and the signal line, and electrically connected to the signal line, the scanning line, and the pixel electrode. 1 period period which has an element and the insulating film arrange | positioned on the said 1st board | substrate, and displays 1 image In addition, a pulse voltage is sequentially applied to the scanning lines to apply and hold a potential for displaying an image on all of the pixel electrodes, and then a light source is turned on after a certain period of time. In the driving method, the liquid crystal state of the pixel corresponding to the scanning line to which the pulse voltage is applied at the end of the one cycle period is set, and the maximum response time from each state to each gradation is shorter than the predetermined period. After the state adjustment is performed, a pulse voltage is sequentially applied to the scanning lines. A driving method corresponding to the liquid crystal display device according to

請求項5記載の発明は、請求項4に記載の液晶表示装置の駆動方法において、前記状態調整を、前記走査線に順次前記パルス電圧を印加する前に、前記画素電極の全てに同一の電圧を印加して行うことを特徴とする。請求項2記載の液晶表示装置に対応する駆動方法である。

According to a fifth aspect of the present invention, in the driving method of the liquid crystal display device according to the fourth aspect, the state adjustment is performed by applying the same voltage to all the pixel electrodes before sequentially applying the pulse voltage to the scanning lines. It is characterized by being applied. A driving method corresponding to the liquid crystal display device according to

請求項6記載の発明は、請求項4又は5に記載の液晶表示装置の駆動方法において、前記状態調整を、前記走査線に順次前記パルス電圧を印加する前に、前記画素電極の電位と前記共通電極の電位とを等しくすることにより行うことを特徴とする。請求項3記載の液晶表示装置に対応する駆動方法である。なお、従来の液晶表示装置には段差があったとしても、電極やコンタクトホールや遮光膜等を形成する際の段差が残っているだけで、本願明細書で説明するように、液晶の応答時間を短縮するために意図的に形成されたことはなかった。

According to a sixth aspect of the present invention, in the method for driving a liquid crystal display device according to the fourth or fifth aspect, the state adjustment is performed by applying the potential of the pixel electrode and the potential before sequentially applying the pulse voltage to the scanning lines. This is performed by making the potential of the common electrode equal. A driving method corresponding to the liquid crystal display device according to

本発明によれば、電界を印加したとき液晶層の厚い領域部分からスイッチングが始まるため、ゼロ階調から中間調までの液晶の応答時間を短縮できるとともに、駆動電圧の変化に伴う色調の変化を抑制することができる。また、動画像の輪郭を鮮明に表示できる。 According to the present invention, when the electric field is applied, switching starts from a thick region of the liquid crystal layer, so that the response time of the liquid crystal from the zero gradation to the halftone can be shortened, and the change in the color tone accompanying the change in the driving voltage can be reduced. Can be suppressed. In addition, the outline of the moving image can be clearly displayed.

従来のIPS表示モードを用いた液晶表示装置では、図4に示すように、液晶層34の厚みはほぼ一定である。この液晶層を図6(a)に示すように、厚みを変化させると、液晶の応答時間を短縮できることを見出した。ここで、図6(a)では、図4に比較して、保護膜82上に第2絶縁膜86を選択的に配置し、凹凸を設けたことのみが異なる。このことによる高速化の原理を次に記述する。IPS表示モードにおける液晶配向変化のしきい値電圧(Vth)は、一般に次式〔1〕で表される。

In the liquid crystal display device using the conventional IPS display mode, the thickness of the

Vth=(π・L/d)・〔K2/(ε0・|Δε|)〕1/2 〔1〕

〔但し、L:電極間ギャップ、d:液晶層の厚み、K2:液晶のツイストの弾性定数、ε0:真空誘電率、Δε:液晶の誘電率異方性〕

V th = (π · L / d) · [K 2 / (ε 0 · | Δε |)] 1/2 [1]

[Where, L: gap between electrodes, d: thickness of liquid crystal layer, K 2 : elastic constant of twist of liquid crystal, ε 0 : vacuum dielectric constant, Δε: dielectric constant anisotropy of liquid crystal]

すなわち、液晶層の厚みdが厚い方がしきい値電圧Vthが低くなる。これは、次のように解釈できる。IPS表示モードでは、電界を印加することによる電界エネルギーと、捩れた液晶が初期配向状態に戻ろうとする弾性エネルギーとのバランスによってスイッチングが行われる。液晶層の厚みdが厚くなると、液晶の回転を固定している配向膜同士の距離が離れるため、弾性エネルギーが低下する。その結果、より少ない電界エネルギーで液晶の捩れを誘起することができ、しきい値電圧Vthが低下する。 That is, the threshold voltage Vth decreases as the thickness d of the liquid crystal layer increases. This can be interpreted as follows. In the IPS display mode, switching is performed by a balance between electric field energy generated by applying an electric field and elastic energy at which the twisted liquid crystal tries to return to the initial alignment state. When the thickness d of the liquid crystal layer is increased, the distance between the alignment films that fix the rotation of the liquid crystal is increased, so that the elastic energy is reduced. As a result, the twist of the liquid crystal can be induced with less electric field energy, and the threshold voltage Vth is lowered.

したがって、液晶層の厚みに変動がある場合には次のようにスイッチングが起こる。液晶層が厚い凹部では弾性エネルギーが低く、液晶層が薄い凸部では弾性エネルギー高い。そのため、図6(b)は液晶を透過する光の透過率の時間的変化をに示すが、電界が印加されると、液晶層の厚い凹部からスイッチングが始まり、その後から液晶層の薄い凸部でスイッチングが行われる。また、低い電圧のときは、液晶層の厚い凹部付近のみでスイッチングが行われる。 Therefore, when the thickness of the liquid crystal layer varies, switching occurs as follows. The elastic energy is low in the concave portion where the liquid crystal layer is thick, and the elastic energy is high in the convex portion where the liquid crystal layer is thin. Therefore, FIG. 6B shows a temporal change in the transmittance of light transmitted through the liquid crystal. When an electric field is applied, switching starts from a thick concave portion of the liquid crystal layer, and thereafter, a thin convex portion of the liquid crystal layer. Switching takes place at. When the voltage is low, switching is performed only near the thick concave portion of the liquid crystal layer.

以上のようにして、黒階調から中間調へのスイッチングでは、液晶層の厚い凹部付近の高速なスイッチングが支配的となるため、液晶の応答時間が短縮される。図7は、凹凸形成による液晶の応答時間の短縮の様相を示す図である。横軸はスイッチング後の階調であり、縦軸が応答時間である。ここで、スイッチング前の階調はゼロである。図7が示すように、凹凸がない従来の液晶表示装置では、ゼロ階調から中間調へのスイッチングが遅い。一方、凹凸を設けた液晶表示装置では、ゼロ階調から中間調へのスイッチングが高速化されている。さらに、本発明により、駆動電圧の増減に伴う色調変化を抑制することができる。それは、次に記述する原理による。IPS表示モードにおける透過率(T)は、一般に次式〔2〕で表される。 As described above, in the switching from the black gradation to the halftone, the high-speed switching near the thick concave portion of the liquid crystal layer becomes dominant, so that the response time of the liquid crystal is shortened. FIG. 7 is a diagram showing an aspect of shortening the response time of the liquid crystal by forming the unevenness. The horizontal axis is the gradation after switching, and the vertical axis is the response time. Here, the gradation before switching is zero. As shown in FIG. 7, in the conventional liquid crystal display device having no unevenness, switching from zero gradation to halftone is slow. On the other hand, in the liquid crystal display device provided with unevenness, switching from zero gradation to halftone is accelerated. Furthermore, according to the present invention, it is possible to suppress a change in color tone that accompanies an increase or decrease in drive voltage. It is based on the principle described below. The transmittance (T) in the IPS display mode is generally expressed by the following equation [2].

T=T0・sin2(2χ)・sin2(π・d・Δneff/λ) 〔2〕

〔但し、T0:補正係数、χ:液晶の実効的な光軸と入射光の偏光方向とのなす角、Δneff:液晶の実効的な屈折率異方性、λ:入射光の波長〕。

T = T 0 · sin 2 (2χ) · sin 2 (π · d · Δneff / λ) [2]

[Where T 0 is a correction coefficient, χ is an angle between the effective optical axis of the liquid crystal and the polarization direction of the incident light, Δn eff is an effective refractive index anisotropy of the liquid crystal, and λ is the wavelength of the incident light).

したがって、液晶の実効的な配向方向と入射光の偏光方向とのなす角χがπ/4ラジアン(45度)のとき、実効的なリターデーションdeff・Δneffの2倍の波長λの光が最大の透過率を示す。つまり、実効的なリターデーションdeff・Δneffが変化すると、透過率が最大となる波長が変化するため、色調が変化する。 Therefore, when the angle χ between the effective alignment direction of the liquid crystal and the polarization direction of the incident light is π / 4 radians (45 degrees), the light having the wavelength λ that is twice the effective retardation diff · Δneff is maximum. The transmittance is shown. That is, when the effective retardation deff · Δneff changes, the wavelength at which the transmittance is maximized changes, so the color tone changes.

ここで本発明によれば、電界が印加されたとき、液晶層が厚み(deff)が厚い領域、すなわち、実効的なリターデーションdeff・Δneffが大きい領域からスイッチングが始まる。すなわち、駆動電圧が低いときでもすでに、deff・Δneffが大きくなり、透過率が最大となる波長が長く、黄色が強調される。そのため、図2ないし図4に示した液晶層に厚みの変化のない従来の液晶表示装置における、駆動電圧の増大に伴って色調が青色から黄色へと変化するという問題を補正することができる。 Here, according to the present invention, when an electric field is applied, switching starts from a region where the liquid crystal layer is thick (def), that is, a region where the effective retardation diff · Δneff is large. That is, even when the driving voltage is low, diff · Δneff is already large, the wavelength at which the transmittance is maximum is long, and yellow is emphasized. Therefore, it is possible to correct the problem that the color tone changes from blue to yellow as the drive voltage increases in the conventional liquid crystal display device in which the thickness of the liquid crystal layer shown in FIGS.

本発明は、部分的に弾性エネルギーの低い領域があると、その領域からスイッチングが始まるという原理に基づいている。そのため、本発明を適用するためには、光の透過領域で液晶層の厚みの変動があれば良く、凹凸の形状は一切限定されない。凹凸は尖っていてもよいし、丸まっていてもよい。また、凹部と凸部の面積比も限定されない。ただし、凹凸の形状や凹部と凸部の面積比が変更されると、高速化の効果の大きさや高速化される階調、および駆動電圧の増減に伴う色調変化を抑制する効果の大きさが変化する。ただし、効果を大にするには、液晶層の厚みがある程度以上であることが好適である。次に、本発明の実施形態を図面に基づき、より具体的に説明する。 The present invention is based on the principle that when there is a region having a low elastic energy partially, switching starts from that region. Therefore, in order to apply the present invention, it is sufficient that the thickness of the liquid crystal layer varies in the light transmission region, and the shape of the unevenness is not limited at all. The unevenness may be pointed or rounded. Moreover, the area ratio of a recessed part and a convex part is not limited. However, if the shape of the unevenness or the area ratio between the concave and convex portions is changed, the magnitude of the effect of speeding up, the gradation to be speeded up, and the magnitude of the effect of suppressing the color tone change accompanying the increase or decrease in drive voltage Change. However, in order to increase the effect, it is preferable that the thickness of the liquid crystal layer is not less than a certain level. Next, embodiments of the present invention will be described more specifically based on the drawings.

〔実施形態1〕

本発明の実施形態1の構成を図1、図2および図5を用いて説明する。本実施形態1の液晶表示装置は、図2に示すように、画素電極35に信号電位を供給する信号ドライバ51と、画素を選択する電位を供給する走査ドライバ52と、共通電極36に電位を供給する共通電極ドライバ54と、信号ドライバ51および走査ドライバ52および共通電極ドライバ54とを制御する表示制御装置53とを有している。

The configuration of the first embodiment of the present invention will be described with reference to FIG. 1, FIG. 2, and FIG. As shown in FIG. 2, the liquid crystal display device according to the first embodiment has a

基板1には、走査ドライバ52に接続された複数の走査線32と、信号ドライバ51に接続され、かつ走査線32と交差した信号線31と、走査線32と信号線31との交点付近に対応して配置され、走査線32と信号線31と電気的に接続された第1TFT33と、第1TFT33に電気的に接続され、信号線31に対応した画素電極35と、画素電極35に対応した共通電極36と、共通電極36と共通電極ドライバ54とに電気的に接続された共通電極接続部36’が備えられている。信号線31と走査線32とに囲まれた1つの領域に対応して1つの画素11が形成され、複数の画素11によって表示部22が形成されている。

In the

図1は実施形態1の画素近傍の回路配置パタン構成を示す図である。走査線32と信号線31とは互いに交差し、走査線32と信号線31とに囲まれた領域に対応して画素11が形成されている。第1TFT33は走査線32と信号線31との交点付近に対応して配置され、走査線32と信号線31と画素電極35とに電気的に接続されている。共通電極36は画素電極35に対応して配置され、共通電極36と画素電極35とで基板面に対して平行な成分を持つ電界を発生する。画素電極35と共通電極36と信号線31は一つの画素内で1回以上折れ曲がり、マルチドメインを形成している。第2絶縁膜86は、画素電極35と共通電極36の間の光の透過領域に配置され、液晶層34の厚みを変動させている。

FIG. 1 is a diagram illustrating a circuit arrangement pattern configuration in the vicinity of a pixel according to the first embodiment. The scanning lines 32 and the

図5は、図1のA−A’断面の断面図である。材質が透明ガラスの基板1と、基板1に対向配置され、材質が透明ガラスの基板2と、基板1と基板2とで狭持された液晶層34とを有する。基板1は、共通電極36と、走査線32(図5に示されない)と、第1絶縁膜81を介し共通電極36よりも上層に配置された信号線31と、共通電極36に対応し、基板1面に対して平行な成分を持つ電界を発生する画素電極35と、画素電極35上に備えられた保護膜82と、保護膜上82に備えられ、液晶層34の厚みを変動させる凹凸を形成している第2絶縁膜86と、第2絶縁膜86上に備えられた配向膜85と、基板1の液晶に面しない側の面上に備えられ、液晶の配向状態に応じて光学特性を変える手段である偏光板6とを有する。

FIG. 5 is a cross-sectional view taken along the line A-A ′ of FIG. 1. A

共通電極36、画素電極35、信号線31は膜厚が0.2μm程度の導電体であり、CrMoやAlやITO(IndiumTin Oxide)などを用いることができる。第1絶縁膜81、保護膜82は膜厚がそれぞれ0.3μm、0.8μm程度の絶縁体であり、窒化珪素などを用いることができる。第2絶縁膜86は膜厚が1μm程度の絶縁体であり、凹凸による段差をつけるために形成されたものである。無機物質も有機物質も用いることができる。なお、本発明が上記の膜厚や材質に限定されるものではないことは、いうまでもない。

The

基板2は、不要な間隙部からの光を遮光する遮光膜5と、遮光膜5上に備えられ、R、G、Bに対応した色を表現するカラーフィルタ4と、カラーフィルタ4上に備えられ、凹凸を平坦化する平坦化膜3と、平坦化膜上3に備えられた配向膜85と、基板2の液晶に面しない側の面上に備えられた偏光板6とを有する。配向膜85には液晶を配向させるためのラビング処理が施されている。ラビング方向は信号線の延伸方向DLaに平行である。屈曲した画素電極の一辺とラビング方向とのなす角は15度であり、IPS表示モードに対応している。

The

偏光板6の透過軸は、それぞれの偏光板6が配置されている基板上の配向膜85のラビング方向に対して平行あるいは垂直に向けられており、基板1の偏光板と基板2の偏光板はクロスニコルに配置され、ノーマリーブラックモードに対応している。なお、本発明が上記のラビング角度に限定されるものではないこと、また、ノーマリーホワイトモードにも適用できることは、いうまでもない。

The transmission axes of the

基板1と基板2との間にはビーズが分散され、液晶層34の厚みを確保している。ビーズは凸部にも存在するため、凸部上のビーズによって液晶層の厚みが決定される。そのため、各画素の液晶層の厚みの平均値をパネル全体に渡って均一にするためには、凸部の面積が広い方が望ましい。そのため、信号線31上や走査線32上のように、画素内の表示領域外にも、凹凸を形成するための第2絶縁膜86が配置されている。なお、第2絶縁膜の代わりに柱状スペーサーが適用できることはいうまでもない。

Beads are dispersed between the

ビーズの直径は3μm程度、したがって液晶層34の厚みは4μm程度、液晶層34の屈折率異方性は0.1程度であり、この組み合わせによってレターデーションが調整される。なお、本発明が上記のレターデーションに限定されるものではないことは、いうまでもない。バックライト(図示せず)に対する制約はなく直下型方式の物もサイドライト方式の物も使用することができる。駆動はアクティブマトリクス駆動によって行われる。

The diameter of the beads is about 3 μm, the thickness of the

本発明によれば、液晶層の厚みが変動しているため、液晶層が厚い凹部では弾性エネルギーが低く、画素電極35と共通電極36との間に電界が印加されたときに、凹部の領域からスイッチングが始まる。そのため、ゼロ階調から中間調へのスイッチングを高速化することができ、動画表示品質の優れた液晶表示装置を提供することができる。なお、凹凸の形成に第2絶縁膜86を用いず、保護膜82で凹凸を形成しても本発明が適用できることはいうまでもない。さらに、第2絶縁膜86の有無によって凹凸を形成するのではなく、凹凸のある第2絶縁膜を表示部22全面に形成することによって、液晶層34の厚みを光の透過領域で変動させた場合にも本発明が適用できることはいうまでもない。

According to the present invention, since the thickness of the liquid crystal layer varies, the elastic energy is low in the concave portion where the liquid crystal layer is thick, and when the electric field is applied between the

〔比較例1〕

本発明の比較例1は、実施形態1に比較して、第2絶縁膜86が形成されず、液晶層34の厚みが光の透過領域でほぼ一定であることのみが異なる。図3は比較例1の画素近傍の回路配置パタン構成を示す図である。実施形態1と異なり第2絶縁膜が形成されていない。図4は、図3のA−A’断面の断面図である。実施形態1と異なり第2絶縁膜がなく、液晶層の厚みがほぼ一定である。そのため、ゼロ階調から中間調への液晶の応答時間が、実施形態1に比較して遅い。

[Comparative Example 1]

The first comparative example of the present invention differs from the first embodiment only in that the second insulating

〔実施形態2〕

実施形態2は、実施形態1に比較して、第2絶縁膜86の形状が異なるだけである。よって、これについて図8および図9を用いて説明する。図8は実施形態2の画素近傍の回路配置パタン構成を示す図である。実施形態1と異なり、第2絶縁膜の形状と配置とがランダムに形成されている。

[Embodiment 2]

The second embodiment is different from the first embodiment only in the shape of the second insulating

図9は、図8のA−A’断面の断面図である。実施形態1と異なり第2絶縁膜の形状と配置と凹凸の高さがランダムに形成されている。ただし、一つの画素内の凹部と凸部の面積比や、凹凸の高さの平均値は、各画素間で一致していることが望ましい。不一致である場合には、各画素毎に高速化の効果の大きさが変化することになり、輝度ムラ等の不具合を生じる原因となる。

FIG. 9 is a cross-sectional view taken along the line A-A ′ of FIG. 8. Unlike

本発明によれば、実施形態1と同様に、液晶層の厚みが変動しているため、液晶層が厚い凹部では弾性エネルギーが低く、画素電極35と共通電極36との間に電界が印加されたときに、凹部の領域からスイッチングが始まる。そのため、ゼロ階調から中間調へのスイッチングを高速化することができ、動画表示品質の優れた液晶表示装置を提供することができる。

According to the present invention, since the thickness of the liquid crystal layer varies as in the first embodiment, the elastic energy is low in the concave portion where the liquid crystal layer is thick, and an electric field is applied between the

〔実施形態3〕

実施形態3は、実施形態1に比較して、第2絶縁膜の形状と配置が異なる。これについて図10および図11を用いて説明する。図10は実施形態3の画素近傍の回路配置パタン構成を示す図である。また、図11は、図10のA−A’断面の断面図である。

[Embodiment 3]

本実施形態は実施形態1と異なり、第2絶縁膜86によって形成される凹凸に伴う段差が、画素電極35と共通電極36との間に一つだけある。また、画素電極35が凸部に重畳して配置され、共通電極36は凹部に重畳している。これにより、凹凸のパタン幅が実施形態1に比較して大きくなり、第2絶縁膜86の加工が容易になる。

This embodiment is different from the first embodiment in that there is only one step between the

〔実施形態4〕

実施形態4は、実施形態3に比較して、電極と第2絶縁膜の配置が異なる。これについて図12および図13を用いて説明する。図12は実施形態4の画素近傍の回路配置パタン構成を示す図である。また、図13は、図12のA−A’断面の断面図である。

[Embodiment 4]

The fourth embodiment differs from the third embodiment in the arrangement of the electrode and the second insulating film. This will be described with reference to FIGS. FIG. 12 is a diagram illustrating a circuit arrangement pattern configuration in the vicinity of a pixel according to the fourth embodiment. FIG. 13 is a cross-sectional view taken along the line AA ′ of FIG.

実施形態4は実施形態3と異なり、画素電極35及び信号線31が第2絶縁膜86より上層に配置されている。なお、共通電極36は走査線32(図13に示されない)と共に基板1上に配置されている。ここで、実施形態3では、図11から分かるように、画素電極35と共通電極36との間に発生する電界の電気力線21のうち、液晶層を通る電気力線21の大部分は第2絶縁膜86も通る。換言すれば、液晶層34は第2絶縁膜86を介して電界が印加される。一方、実施形態4では、図13から分かるように、画素電極35が第2絶縁膜86より上層に配置されているため、第2絶縁膜86を介することなく液晶層34に電界が印加される。そのため、実施形態4では実施形態3より駆動電圧を低下させることができる。

In the fourth embodiment, unlike the third embodiment, the

なお、保護膜82が形成されていない場合、保護膜82と第2絶縁膜86が一括加工されている場合、保護膜82と第2絶縁膜86が同一材料で一体化されている場合においても、液晶層34の厚みを変動させることができるため、本発明が適用できることはいうまでもない。

Even when the

〔実施形態5〕

実施形態5は、実施形態4に比較して、第2絶縁膜の配置が異なる。これについて図14、図15および図16を用いて説明する。図14は実施形態5の基板1上の画素近傍の回路配置パタン構成を示す図である。また、図15は実施形態5の基板2上の画素近傍の回路配置パタン構成を示す図である。図16は、図14のA−A’断面の断面図である。

[Embodiment 5]

The fifth embodiment is different from the fourth embodiment in the arrangement of the second insulating film. This will be described with reference to FIGS. 14, 15, and 16. FIG. FIG. 14 is a diagram illustrating a circuit arrangement pattern configuration in the vicinity of a pixel on the

基板1は、共通電極36と、走査線32(図16に示されない)と、第1絶縁膜81を介し共通電極36よりも上層に配置された信号線31と、画素電極35を備え、基板1面に対して平行な成分を持つ電界を発生する画素電極35と、画素電極35上に備えられた保護膜82と、保護膜82上に備えられた配向膜85と、基板1の液晶に面しない側の面上に備えられ、液晶の配向状態に応じて光学特性を変える手段である偏光板6とを有する。

The

基板2は、不要な間隙部からの光を遮光する遮光膜5と、遮光膜5上に備えられ、R、G、Bに対応した色を表現するカラーフィルタ4と、カラーフィルタ4上に備えられ、凹凸を平坦化する平坦化膜3と、平坦化膜上3に備えられ、液晶層34の厚みを変動させる凹凸を形成している第2絶縁膜86と、第2絶縁膜86上に備えられた配向膜85と、基板2の液晶に面しない側の面上に備えられた偏光板6とを有する。

The

実施形態5は実施形態4と異なり、液晶層の厚みを変動させる凹凸を形成する第2絶縁膜86が基板2上に配置されている。そのため、画素電極35や共通電極36や信号線31や走査線32等の配線あるいは電極と第2絶縁膜86とが離れているため、第2絶縁膜86の膜厚が変動する場合にも、画素電極35と共通電極36との間などの浮遊容量が変動することなく、表示ムラ等を誘発しにくくなる。

In the fifth embodiment, unlike the fourth embodiment, a second insulating

〔実施形態6〕

実施形態6は、実施形態5に比較して、第2絶縁膜の配置と形状が異なる。これについて図14、図17、図18および図19を用いて説明する。実施形態6の基板1上の画素近傍の回路配置パタン構成を示す図は図14と同様である。また、図17は実施形態6の基板2上の画素近傍の回路配置パタン構成を示す図である。図18は、図17のA−A’断面の断面図である。図19は、図14及び図17のB−B’断面の断面図である。

[Embodiment 6]

The sixth embodiment differs from the fifth embodiment in the arrangement and shape of the second insulating film. This will be described with reference to FIGS. 14, 17, 18 and 19. FIG. A diagram showing a circuit arrangement pattern configuration in the vicinity of a pixel on the

実施形態6では、第2絶縁膜86によって形成される凹凸の延伸方向DLbが、画素電極の延伸方向DLcからずれており、ほぼ垂直に交わっている。そのため、基板1と基板2との間に合わせずれが生じた場合にも、遮光膜5に対する第2絶縁膜86の位地関係は画素毎に変化せず、画素電極35と共通電極36との間の領域一つ一つで、凹部と凸部の面積比が変動せず、液晶の応答時間の短縮の効果が変動しない。

In

〔実施形態7〕

実施形態7は、実施形態6に比較して、第2絶縁膜の配置と形状が異なる。これについて図14、図20および図21を用いて説明する。実施形態7の基板1上の画素近傍の回路配置パタン構成は図14と同様である。また、図20は実施形態7の基板2上の画素近傍の回路配置パタン構成を示す図である。図21は、図20のA−A’断面の断面図である。実施形態7では、第2絶縁膜86によって形成される凹凸に伴う段差の延伸方向DLdが、液晶の初期配向方向DLeと一致している。そのため、配向膜85にラビング処理を施すときに、光の透過領域において凹凸に伴う段差を乗り越えることがなく、均一にラビング処理を施すができ、配向不良等を誘発しにくい。

[Embodiment 7]

The seventh embodiment is different from the sixth embodiment in the arrangement and shape of the second insulating film. This will be described with reference to FIGS. 14, 20 and 21. FIG. The circuit arrangement pattern configuration in the vicinity of the pixel on the

〔実施形態8〕

実施形態8は、実施形態7に比較して、第2絶縁膜の配置と形状が異なる。これについて図22および図23を用いて説明する。図22は実施形態8の基板1上の画素近傍の回路配置パタン構成を示す図である。また、図23は図22のA−A’断面の断面図である基板1は、共通電極36と、走査線32(図23に示されない)と、共通電極36上に配置された第1絶縁膜81と、第1絶縁膜81上に配置された保護膜82と、保護膜上82に配置され、液晶層34の厚みを変動させる凹凸を形成している第2絶縁膜86と、第2絶縁膜86上に配置された信号線31と、第2絶縁膜86より上層に配置され、共通電極36に対応して基板1面に対して平行な成分を持つ電界を発生する画素電極35と、画素電極35上に配置された配向膜85と、基板1の液晶に面しない側の面上に備えられ、液晶の配向状態に応じて光学特性を変える手段である偏光板6とを有する。なお、共通電極36は走査線32と共に基板1上に配置されている。

[Embodiment 8]

The eighth embodiment differs from the seventh embodiment in the arrangement and shape of the second insulating film. This will be described with reference to FIGS. 22 and 23. FIG. FIG. 22 is a diagram illustrating a circuit arrangement pattern configuration in the vicinity of a pixel on the

基板2は、不要な間隙部からの光を遮光する遮光膜5と、遮光膜5上に備えられ、R、G、Bに対応した色を表現するカラーフィルタ4と、カラーフィルタ4上に備えられ、凹凸を平坦化する平坦化膜3と、平坦化膜上3に備えられた配向膜85と、基板2の液晶に面しない側の面上に備えられた偏光板6とを有する。実施形態8は実施形態7と異なり、液晶層の厚みを変動させる凹凸を形成する第2絶縁膜86が基板1上に配置されている。そのため、基板1と基板2との間に合わせずれが生じた場合にも、第2絶縁膜86は影響を受けないため、全画素にわたって液晶の応答時間の短縮の効果が変動しない。

The

また、実施形態8は実施形態4と異なり、第2絶縁膜86によって形成される凹凸に伴う段差の延伸方向DLdが、液晶の初期配向方向DLeと一致している。そのため、配向膜85にラビング処理を施すときに、光の透過領域において凹凸に伴う段差を乗り越えることがなく、均一にラビング処理を施すができ、配向不良等を誘発することがない。

Further, unlike the fourth embodiment, the eighth embodiment differs from the fourth embodiment in that the step extending direction DLd due to the unevenness formed by the second insulating

〔実施形態9〕

実施形態9は、実施形態8に比較して、第2絶縁膜86と画素電極35と共通電極36の配置と形状が異なるだけである。よって、これについて図24を用いて説明する。図24は実施形態9の基板1上の画素近傍の回路配置パタン構成を示す図である。実施形態9は、実施形態8と異なり、画素電極35および共通電極36が屈曲していない。そのため、ラビング方向は信号線31の延伸方向に対して15度傾いている。ただし、画素電極35の一辺とラビング方向とのなす角が15度であることは、実施形態8と同じである。

[Embodiment 9]

The ninth embodiment is different from the eighth embodiment only in the arrangement and shape of the second insulating

第2絶縁膜86によって形成される凹凸に伴う段差の延伸方向は信号線31の延伸方向に対して15度傾いている。ただし、第2絶縁膜86によって形成される凹凸に伴う段差の延伸方向DLdが、液晶の初期配向方向DLeと一致していることは、実施形態8と同じである。そのため、実施形態8と同様に、実施形態9では、配向膜85にラビング処理を施すときに、光の透過領域において凹凸に伴う段差を乗り越えることがなく、均一にラビング処理を施すができ、配向不良等を誘発することがない。

The extending direction of the step due to the unevenness formed by the second insulating

〔実施形態10〕

実施形態10は、実施形態8に比較して、第2絶縁膜の配置と形状が異なる。これについて図25および図26を用いて説明する。図25は実施形態10の基板1上の画素近傍の回路配置パタン構成を示す図である。また、図26は図25のA−A’断面の断面図である実施形態10は、実施形態8と異なり、画素電極35および共通電極36が第2絶縁膜86による凹凸に伴う段差を乗り越えていない。例えば、実施形態8の図22R>2に示す部分Cでは、画素電極35が第2絶縁膜86の端を乗り越えている。一方、実施形態10の図25に示す部分Cでは、画素電極35は第2絶縁膜86を乗り越えてはいない。すなわち、図22ではA−A’断面に平行な断面をとった場合に、画素電極35が第2絶縁膜86上(段差の上部)にある個所と保護膜82上(段差の下部)にある個所が存在するのに対し、図25では、第2絶縁膜86は画素電極35を避けて配置されており、A−A’断面に平行などの断面をとっても、画素電極35が保護膜82上(段差の下部)にある。そのため、実施形態10では、第2絶縁膜86による凹凸に伴う段差によって画素電極35が切れるということなどの不良が生じない。

[Embodiment 10]

The tenth embodiment differs from the eighth embodiment in the arrangement and shape of the second insulating film. This will be described with reference to FIGS. 25 and 26. FIG. FIG. 25 is a diagram illustrating a circuit arrangement pattern configuration in the vicinity of a pixel on the

〔実施形態11〕

実施形態11は、実施形態10に比較して、第2絶縁膜の配置と形状が異なる。これについて図27および図28を用いて説明する。図27は実施形態11の基板1上の画素近傍の回路配置パタン構成を示す図である。また、図28は図27のA−A’断面の断面図である実施形態11は、実施形態10と異なり、第2絶縁膜86による凹凸に伴う段差が、画素電極35および共通電極36と重畳している。例えば、実施形態10の図25に示す部分Cでは、第2絶縁膜86による凹凸に伴う段差が画素電極35に重畳していない。一方、実施形態11の図27に示す部分Cでは、第2絶縁膜86による凹凸に伴う段差が画素電極35に重畳している。そのため、実施形態11では、第2絶縁膜86による凹凸に伴う段差部分でラビング処理が不十分となり、配向不良が生じた場合でも、画素電極35および共通電極36が不透明な導電体であれば、その不良は画素電極35および共通電極36によって隠されるため、表示には影響しない。

[Embodiment 11]

The eleventh embodiment differs from the tenth embodiment in the arrangement and shape of the second insulating film. This will be described with reference to FIGS. 27 and 28. FIG. FIG. 27 is a diagram illustrating a circuit arrangement pattern configuration in the vicinity of a pixel on the

また、実施形態11は、実施形態10と同様に、第2絶縁膜86による凹凸に伴う段差が、画素電極35および共通電極36と重畳しているものの、乗り越えてはいない。すなわち、図27では、第2絶縁膜86はおおよそ画素電極35を避けて配置されているが、画素電極35は端部で第2絶縁膜86上に乗り上げている。このため、A−A’断面に平行などの断面をとっても、画素電極35はおおよそ保護膜82上(段差の下部)にあり、端部のみ第2絶縁膜86上(段差の上部)にある。そのため、実施形態10と同様に、第2絶縁膜86による凹凸に伴う段差によって画素電極35が切れるということなどの不良が生じない。

In the eleventh embodiment, as in the tenth embodiment, the level difference caused by the unevenness due to the second insulating

〔実施形態12〕

実施形態12は、実施形態9に比較して、第2絶縁膜の配置と形状が異なる。これについて図29を用いて説明する。図29は実施形態12の基板1上の画素近傍の回路配置パタン構成を示す図である。実施形態12は、実施形態9と異なり、画素電極35および共通電極36が第2絶縁膜86による凹凸に伴う段差を乗り越えていない。例えば、実施形態9の図24に示す部分Cでは、画素電極35が第2絶縁膜86の端を乗り越えている。一方、実施形態12の図29に示す部分Cでは、画素電極35は第2絶縁膜86に一部重畳しているものの乗り越えてはいない。すなわち、図29では、第2絶縁膜86はおおよそ画素電極35を避けて配置されているが、画素電極35は端部で第2絶縁膜86上に乗り上げている。このため、横軸に平行などの断面をとっても、画素電極35はおおよそ保護膜82上(段差の下部)にあり、端部のみ第2絶縁膜86上(段差の上部)にある。

[Embodiment 12]

The twelfth embodiment is different from the ninth embodiment in the arrangement and shape of the second insulating film. This will be described with reference to FIG. FIG. 29 is a diagram illustrating a circuit arrangement pattern configuration in the vicinity of a pixel on the

そのため、実施形態12では、実施形態10と同様に、第2絶縁膜86による凹凸に伴う段差によって画素電極35が切れるということなどの不良が生じない。さらに、第2絶縁膜86による凹凸に伴う段差が、画素電極35および共通電極36と重畳している。そのため、実施形態12では、第2絶縁膜86による凹凸に伴う段差部分でラビング処理が不十分となり、配向不良が生じた場合でも、画素電極35および共通電極36が不透明な導電体であれば、その不良は画素電極35および共通電極36によって隠されるため、表示には影響しない。

Therefore, in the twelfth embodiment, as in the tenth embodiment, there is no defect such as the

〔実施形態13〕

実施形態13は、実施形態11に比較して、第2絶縁膜の配置と形状が異なる。これについて図30および図31を用いて説明する。図30は実施形態13の画素近傍の回路配置パタン構成を示す図である。また、図31は、図30のA−A’断面の断面図である。

[Embodiment 13]

The thirteenth embodiment differs from the eleventh embodiment in the arrangement and shape of the second insulating film. This will be described with reference to FIGS. 30 and 31. FIG. FIG. 30 is a diagram illustrating a circuit arrangement pattern configuration in the vicinity of a pixel according to the thirteenth embodiment. FIG. 31 is a cross-sectional view taken along the line AA ′ of FIG.

実施形態13は実施形態11と異なり、第2絶縁膜86によって形成される凹凸に伴う段差が、画素電極35と共通電極36との間に一つだけある。また、画素電極35が凸部に重畳して配置され、共通電極は凹部に重畳している。これにより、凹凸のパタン幅が実施形態11に比較して大きくなり、第2絶縁膜86の加工が容易になる。

The thirteenth embodiment differs from the eleventh embodiment in that there is only one step between the

なお、画素電極35が第2絶縁膜86より上層に配置されているため、第2絶縁膜86を介することなく液晶層34に電界を印加することができ、駆動電圧の上昇を抑制している。さらに、第2絶縁膜86によって形成される凹凸に伴う段差の延伸方向DLdが、液晶の初期配向方向DLeと一致しているため、配向膜85にラビング処理を施すときに、光の透過領域において凹凸に伴う段差を乗り越えることがなく、均一にラビング処理を施すができ、配向不良等を誘発しにくい。

Since the

さらに、光の透過領域において、画素電極35および共通電極36が第2絶縁膜86による凹凸に伴う段差を乗り越えていないため、段差によって画素電極35が切れるということなどの不良が生じない。すなわち、図30では画素電極35及び信号線31は全て第2絶縁膜86上に形成されており、段差にかかることはない。

Further, in the light transmission region, the

〔実施形態14〕

実施形態14は、実施形態13に比較して、信号線31と画素電極35と共通電極36と第2絶縁膜86の形状と配置が異なる。これについて図32および図33を用いて説明する。図32は実施形態14の画素近傍の回路配置パタン構成を示す図である。走査線32と信号線31とは互いに交差し、走査線32と信号線31とに囲まれた領域に対応して画素が形成されている。第1TFT33は走査線32と信号線31との交点付近に対応して配置され、走査線32と信号線31と画素電極35とに電気的に接続されている。共通電極36は画素電極35に対応して配置され、共通電極36と画素電極35とで基板面に対して平行な成分を持つ電界を発生する。画素電極35と共通電極36と信号線31は一つの画素内で1回以上折れ曲がり、マルチドメインを形成している。第2絶縁膜86は、画素電極と共通電極の間の光の透過領域に配置され、液晶層34の厚みを変動させている。信号線31と共通電極36とは第2絶縁膜86を介して重畳している。

[Embodiment 14]

The fourteenth embodiment is different from the thirteenth embodiment in the shape and arrangement of the

図33は、図32のA−A’断面の断面図である。材質が透明ガラスの基板1と、基板1に対向配置され、材質が透明ガラスの基板2と、基板1と基板2とで狭持された液晶層34とを有する。基板1は、第1絶縁膜81と、第1絶縁膜81上に配置された信号線31および画素電極35と、信号線31および画素電極35上に配置された保護膜82と、保護膜82上に配置された第2絶縁膜86と、第2絶縁膜86を介して信号線31に重畳して配置された共通電極36と、液晶34との界面に配置された配向膜85と、基板1の液晶に面しない側の面上に備えられ、液晶の配向状態に応じて光学特性を変える手段である偏光板6とを有する。なお、共通電極36は走査線32(図33に示されない)と共に第1絶縁膜81上に配置される。

33 is a cross-sectional view taken along the line A-A ′ of FIG. 32. A

共通電極36、画素電極35、信号線31は膜厚が0.2μm程度の導電体であり、CrMoやAlやITO(IndiumTin Oxide)などを用いることができる。第1絶縁膜81、保護膜82は膜厚がそれぞれ0.3μm、0.8μm程度の絶縁体であり、窒化珪素などを用いることができる。第2絶縁膜86は膜厚が1μm程度の絶縁体であり、無機物質も有機物質も用いることができる。なお、本発明が上記の膜厚に限定されるものではないことは、いうまでもない。基板2は、不要な間隙部からの光を遮光する遮光膜5と、遮光膜5上に備えられ、R、G、Bに対応した色を表現するカラーフィルタ4と、カラーフィルタ4上に備えられ、凹凸を平坦化する平坦化膜3と、平坦化膜上3に備えられた配向膜85と、基板2の液晶に面しない側の面上に備えられた偏光板6とを有する。

The

配向膜85には液晶を配向させるためのラビング処理が施されている。ラビング方向は信号線の延伸方向に平行である。屈曲した画素電極の一辺とラビング方向とのなす角は15度であり、IPS表示モードに対応している。偏光板6の透過軸は、それぞれの偏光板が配置されている基板上の配向膜のラビング方向に対して平行あるいは垂直に向けられており、基板1の偏光板と基板2の偏光板はクロスニコルに配置され、ノーマリーブラックモードに対応している。なお、本発明が上記のラビング角度に限定されるものではないこと、また、ノーマリーホワイトモードにも適用できることは、いうまでもない。

The

基板1と基板2との間にはビーズが分散され、液晶層の厚みを確保している。ビーズは凸部にも存在するため、凸部上のビーズによって液晶層の厚みが決定される。そのため、各画素の液晶層の厚みの平均値をパネル全体に渡って均一にするためには、凸部の面積が広い方が望ましい。そのため、信号線31上や走査線32上の画素内の表示領域外にも、凹凸を形成するための第2絶縁膜86が配置されている。なお、本発明に柱状スペーサーが適用できることはいうまでもない。

Beads are dispersed between the

ビーズの直径は3μm程度、液晶層の屈折率異方性は0.1程度であり、この組み合わせによってレターデーションが調整される。なお、本発明が上記のレターデーションに限定されるものではないことは、いうまでもない。バックライト(図示せず)に対する制約はなく直下型方式の物もサイドライト方式の物も使用することができる。駆動はアクティブマトリクス駆動によって行われる。 The diameter of the beads is about 3 μm, the refractive index anisotropy of the liquid crystal layer is about 0.1, and the retardation is adjusted by this combination. Needless to say, the present invention is not limited to the above-mentioned retardation. There is no restriction on the backlight (not shown), and either a direct type or a side light type can be used. Driving is performed by active matrix driving.

実施形態14によれば、液晶層の厚みが変動しているため、液晶層が厚い凹部では弾性エネルギーが低く、画素電極35と共通電極36との間に電界が印加されたときに、凹部の領域からスイッチングが始まる。そのため、ゼロ階調から中間調へのスイッチングを高速化することができ、動画表示品質の優れた液晶表示装置を提供することができる。

According to the fourteenth embodiment, since the thickness of the liquid crystal layer varies, the elastic energy is low in the concave portion where the liquid crystal layer is thick, and when the electric field is applied between the

また、電界が印加されたとき、液晶層が厚み(deff)が厚い領域、すなわち、実効的なリターデーションdeff・Δneffが大きい領域からスイッチングが始まるため、駆動電圧が低いときでもすでに透過率が最大となる波長が長く、黄色が強調される。これにより、液晶層の厚みの変化のない従来の液晶表示装置における、駆動電圧の増大に伴って色調が青色から黄色へと変化するという問題を補正することができる。 Further, when an electric field is applied, switching starts from a region where the liquid crystal layer has a large thickness (defeff), that is, a region where the effective retardation deff · Δneff is large, so that the transmittance is already maximum even when the driving voltage is low. The wavelength becomes long and yellow is emphasized. This can correct the problem that the color tone changes from blue to yellow as the drive voltage increases in a conventional liquid crystal display device in which the thickness of the liquid crystal layer does not change.

実施形態14は実施形態13と異なり、信号線31と共通電極36とは第2絶縁膜86を介して重畳しており、実施形態13では信号線31の両側に配置された二つの共通電極36が一つにまとめられている。そのため、フォトレジスト工程のマスクを増やすことなく、開口率が向上される。

In the fourteenth embodiment, unlike the thirteenth embodiment, the

また、実施形態14は実施形態13と異なり、信号線31と共通電極36とは第2絶縁膜86を介して重畳しているため、光の透過領域における凹部と凸部の面積比が同じ場合で比較して、実施形態14は実施形態13に比較して信号線31に重畳している第2絶縁膜の面積を広く取ることができる。これにより、液晶層34の厚みは凸部上のビーズによって決定されるため、実施形態14は実施形態13に比較して各画素の液晶層34の厚みの平均値をパネル全体に渡って均一にすることが容易になる。

In the fourteenth embodiment, unlike the thirteenth embodiment, the

さらには、実施形態11と異なり、第2絶縁膜86によって形成される凹凸に伴う段差が、画素電極35と共通電極36との間に一つだけある。また、画素電極35が凹部に重畳して配置され、共通電極36は凸部に重畳している。これにより、凹凸の形状が実施形態11に比較して大きくなり、第2絶縁膜86の加工が容易になる。なお、凸部に重畳している共通電極36が第2絶縁膜86より上層に配置されているため、第2絶縁膜86を介することなく液晶層34に電界を印加することができ、駆動電圧の上昇を抑制している。

Furthermore, unlike

さらに、第2絶縁膜86によって形成される凹凸に伴う段差の延伸方向DLdが、液晶の初期配向方向DLeと一致しているため、配向膜85にラビング処理を施すときに、光の透過領域において凹凸に伴う段差を乗り越えることがなく、均一にラビング処理を施すができ、配向不良等を誘発しにくい。さらに、光の透過領域において、画素電極35および共通電極36が第2絶縁膜86による凹凸に伴う段差を乗り越えていないため、段差によって画素電極35が切れるということなどの不良が生じない。

Furthermore, since the extending direction DLd of the level difference caused by the unevenness formed by the second insulating

〔実施形態15〕

実施形態15は、実施形態14に比較して、第2絶縁膜86の形状と配置が異なる。これについて図34および図35を用いて説明する。図34は実施形態15の画素近傍の回路配置パタン構成を示す図である。また、図35は、図34のA−A’断面の断面図である。

[Embodiment 15]

The fifteenth embodiment differs from the fourteenth embodiment in the shape and arrangement of the second insulating

実施形態15は実施形態14と異なり、第2絶縁膜86が信号線31と共通電極36とに重畳している部分で、共通電極36より小さい幅で、選択的に形成されている。そのため、図35に示すように、共通電極36が第2絶縁膜86を覆うように形成されている。これにより、電気力線21が示すような、信号線31と画素電極35との間に発生する表示に不要なノイズ電界のうち、第2絶縁膜86と液晶層34の凹部とを通るノイズ電界を遮断することができ、表示品質を向上させることができる。

In the fifteenth embodiment, unlike the fourteenth embodiment, the second insulating

〔実施形態16〕

実施形態16は、実施形態14に比較して、共通電極36の形状と配置が異なる。これについて図36および図37を用いて説明する。図36は実施形態16の画素近傍の回路配置パタン構成を示す図である。また、図37は、図36のA−A’断面の断面図である。

[Embodiment 16]

In the sixteenth embodiment, the shape and arrangement of the

実施形態16は実施形態14と異なり、信号線31と第2絶縁膜86とが重畳している部分で、第2絶縁膜86の上に共通電極36と配向膜85とが配置されている。すなわち、実施形態14の図33では信号線31の全面(ただし、図36のA−A’断面において全面という意味である)に共通電極36が重畳しているが、実施形態16の図37では信号線31の一部分に共通電極36が重畳している。そのため、この重畳している面積を変化させることによって、信号線31と共通電極36との間に発生する容量を変化させることができる。ここで、信号線31を通る映像信号の遅延を引き起こすため、この容量を調整することは重要である。

In the sixteenth embodiment, unlike the fourteenth embodiment, the

つまり、実施形態14では、第2絶縁膜86の厚みを変化させることで容量を変化させることができたが、実施形態16では、第2絶縁膜86の厚みだけではなく、信号線31と共通電極36とが重畳している面積を変化させることでも容量を変化させることができる。したがって、第2絶縁膜86の厚みに関する自由度が広がり、液晶層34の厚みの凹凸による高速化の効果が最適化されるように第2絶縁膜の厚みを決定することができる。換言すれば、実施形態16は液晶層34の厚みの変動の最適化と、信号線31と共通電極36との間の容量の最適化を、独立してそれぞれ行うことができる。

In other words, in the fourteenth embodiment, the capacitance can be changed by changing the thickness of the second insulating

〔実施形態17〕

実施形態17は、実施形態14に比較して、保護膜82の形状が異なるだけである。これについて図32および図38を用いて説明する。図32は実施形態17の画素近傍の回路配置パタン構成を示す図である。また、図38は、図32のA−A’断面の断面図である。

[Embodiment 17]

The seventeenth embodiment is different from the fourteenth embodiment only in the shape of the

実施形態17は実施形態14と異なり、凹凸を形成する第2絶縁膜86とは異なって、かつ凹凸を有する絶縁膜である保護膜82が基板1上に配置され、凹凸を形成する第2絶縁膜86と保護膜82の凹部とが重畳している。すなわち、図38に示すように、実施形態17は保護膜82が凹凸を有し、保護膜82の凹部に絶縁膜86が配置されているため、実施形態14に比較して液晶層の厚みの変動が小さくなっている。

The seventeenth embodiment is different from the fourteenth embodiment in that a

すなわち、実施形態17では、液晶層34の厚みの変動を第2絶縁膜86と保護膜82の両方で変化させることができる。そのため、信号線31と共通電極36との間の容量は第2絶縁膜の厚みで変化させることができ、液晶層34の厚みの変動は第2絶縁膜86の厚みと保護膜82の凹凸の大きさとの組み合わせで変化させることができる。

That is, in the seventeenth embodiment, the variation in the thickness of the

換言すれば、実施形態17は液晶層34の厚みの変動の最適化と、信号線31と共通電極36との間の容量の最適化を、独立してそれぞれ行うことができる。なお、最初から保護膜82の断面形状を本実施形態での第2絶縁膜86と保護膜82を合わせた断面形状になるように形成しても、同様の効果を得られる。

In other words, the seventeenth embodiment can independently optimize the variation in the thickness of the

〔実施形態18〕

実施形態18は、実施形態1に比較して、駆動方法が異なるだけである。これについて図39を用いて説明する。図39は実施形態18の各配線および電極の電位の時間変化と液晶に印加される電圧の時間変化の例である。

[Embodiment 18]

The eighteenth embodiment is different from the first embodiment only in the driving method. This will be described with reference to FIG. FIG. 39 is an example of the time change of the potential of each wiring and electrode and the time change of the voltage applied to the liquid crystal in the eighteenth embodiment.

実施形態18では、1周期期間110中に2回の選択パルスが走査線に供給される。初めの選択パルス101によって、画素電極には共通電極と同じ電位が供給され、液晶への印加電圧はゼロになり、ノーマリーブラック表示モードの本液晶表示装置は黒階調を表示する。同じ周期期間110中の、次の選択パルス102によって、画像を表示するための電位が前記画素電極に供給され、本液晶表示装置は黒階調から画像を表示する階調へと変化する。このように、実施形態18は、1画像を表示する1周期期間中に、画素電極の電位と共通電極の電位とを等しくする手段を有する駆動方法を用いている。

In the eighteenth embodiment, two selection pulses are supplied to the scanning line during one cycle period 110. By the first selection pulse 101, the same potential as that of the common electrode is supplied to the pixel electrode, the voltage applied to the liquid crystal becomes zero, and the present liquid crystal display device in the normally black display mode displays a black gradation. In the same period 110, the

そのため、各画素の輝度が画像を表示する階調へと変化するときは、必ず、黒階調から画像を表示する階調へと変化する。実施形態18は黒階調から中間調への応答時間を短縮できる構成であるため、上記の駆動方法と回路構成を組み合わせることによって、高速化された黒階調から中間調へのスイッチングを多用することになり、動画像の表示品質が向上する。 Therefore, whenever the luminance of each pixel changes to a gradation for displaying an image, it always changes from a black gradation to a gradation for displaying an image. In the eighteenth embodiment, since the response time from the black gradation to the halftone can be shortened, the switching from the black gradation to the halftone that has been speeded up is frequently used by combining the above driving method and the circuit configuration. As a result, the display quality of the moving image is improved.

なお、実施形態18は実施形態1におけるアクティブマトリクス駆動を上記の駆動方法に入れ換えたものである。そのため、アクティブマトリクス駆動を用いている実施形態2ないし実施形態17においても、アクティブマトリクス駆動を上記の駆動方法で置き換えることによって、実施形態18と同様の効果が得られることは、いうまでもない。

In the eighteenth embodiment, the active matrix driving in the first embodiment is replaced with the above driving method. Therefore, in

〔実施形態19〕

実施形態19は、実施形態18に比較して、駆動方法が異なるだけである。これについて図40および図41を用いて説明する。なお、バックライト光源を用いてもよい。

図40は実施形態19による液晶表示装置の構成を示す図である。実施形態19の液晶表示装置は、画素電極35に信号電位を供給する信号ドライバ51と、画素を選択する電位を供給する走査ドライバ52と、共通電極36に電位を供給する共通電極ドライバ54と、信号ドライバ51および走査ドライバ52および共通電極ドライバ54とを制御する表示制御装置53とを有している。

[Embodiment 19]

The nineteenth embodiment is different from the eighteenth embodiment only in the driving method. This will be described with reference to FIGS. 40 and 41. FIG. A backlight light source may be used.

FIG. 40 is a diagram showing the configuration of the liquid crystal display device according to the nineteenth embodiment. The liquid crystal display device according to the nineteenth embodiment includes a

基板1には、走査ドライバ52に接続された複数の走査線32と、信号ドライバ51に接続され、かつ走査線32と交差した信号線31と、走査線32と信号線31との交点付近に対応して配置され、走査線32と信号線31と電気的に接続された第1TFT33と、第1TFT33に電気的に接続され、信号線31に対応した画素電極35と、画素電極35に対応した共通電極36と、第1TFTが接続されている走査線32と異なる走査線と画素電極35と共通電極36とに電気的に接続された第2TFT33’と、共通電極36と共通電極ドライバ54とに電気的に接続された共通電極配線36”が備えられている。

In the

図41は実施形態19の各配線および電極の電位の時間変化と液晶に印加される電圧の時間変化の例である。実施形態19の駆動は、図41に示すように、共通電極配線36”を介して共通電極36に負の選択パルスが103供給されると、図40の第2TFT33’が接続されている走査線32が選択された場合と等価になることから、第2TFT33’がオンになり、画素電極35の電位と共通電極36の電位とが等しくなり、ノーマリーブラック表示モードの本液晶表示装置は黒階調を表示する。この場合、走査線32は1番目からm番目へと順次選択されていくので、共通電極配線36”駆動時に選択中の走査線に接続された第2TFT33’のみがオンになり、画素電極35の電位と共通電極36の電位とが等しくなる。続いて、同じ周期期間110中の、選択パルス102によって、画像を表示するための電位が前記画素電極に供給され、本液晶表示装置は黒階調から画像を表示する階調へと変化する。この場合、次の走査線32が選択されているので、共通電極と同じ電位になった当該画素電極35に接続された第1TFT33のみがオンになり、画像を表示するための電位が当該画素電極に供給される。このようにして、走査線が1番目からm番目へと順次選択されるにつれて、走査線に接続された画素電極も順次選択されていき、一旦、共通電極の電位と等しくなった後に画像を表示するための電位が供給されていくこととなる。

FIG. 41 shows an example of the time change of the potential of each wiring and electrode and the time change of the voltage applied to the liquid crystal in the nineteenth embodiment. In the driving of the nineteenth embodiment, as shown in FIG. 41, when 103 negative selection pulses are supplied to the

このように、実施形態19は、1画像を表示する1周期期間中に、画素電極の電位と共通電極の電位とを等しくする手段を有する駆動方法を用いている。そのため、各画素の輝度が画像を表示する階調へと変化するときは、必ず、黒階調から画像を表示する階調へと変化する。実施形態19は黒階調から中間調への応答時間を短縮できる構成であるため、上記の駆動方法と回路構成を組み合わせることによって、高速化された黒階調から中間調へのスイッチングを多用することになり、動画像の表示品質が向上する。 As described above, the nineteenth embodiment uses a driving method having means for equalizing the potential of the pixel electrode and the potential of the common electrode during one period of displaying one image. Therefore, whenever the luminance of each pixel changes to a gradation for displaying an image, it always changes from a black gradation to a gradation for displaying an image. Since the nineteenth embodiment has a configuration capable of shortening the response time from the black gradation to the halftone, the switching from the black gradation to the halftone, which is accelerated, is frequently used by combining the driving method and the circuit configuration. As a result, the display quality of the moving image is improved.

また、実施形態19は実施形態18と異なり、画素電極の電位と共通電極の電位とを等しくする手段が信号線31に対して独立であるため、画像を表示するための電位の供給と、画素電極の電位と共通電極の電位とを等しくすることとを、異なる画素で同時刻に行うことができ、黒階調を表示する時間と画像を表示する時間との割合を任意に変更することができる。

In addition, the nineteenth embodiment is different from the eighteenth embodiment in that the means for equalizing the potential of the pixel electrode and the common electrode is independent of the

なお、実施形態19は実施形態1におけるアクティブマトリクス駆動を上記の駆動方法に入れ換えたものである。そのため、アクティブマトリクス駆動を用いている実施形態2ないし実施形態17においても、アクティブマトリクス駆動を上記の駆動方法で置き換えることによって、実施形態19と同様の効果が得られることは、いうまでもない。

In the nineteenth embodiment, the active matrix driving in the first embodiment is replaced with the above driving method. Therefore, in

〔実施形態20〕

実施形態20は実施形態1と異なり、ラビング処理の代わりに、液晶層と接する部分に光反応性の材料層を配置し、光配向を適用したことのみが異なる。すなわち、配向膜85として光配向に適した材料を使用し、ほぼ直線に偏光した光を照射して液晶層34の初期配向方向を決定した。そのため、凹凸に伴う段差部において配向不良等を誘発しにくくなる。光反応性の材料としてはポリビニルシンナメート等を使用できる。なお、実施形態20は実施形態1における配向処理を変更しただけである。そのため、実施形態2ないし実施形態19においても、配向処理に光配向を適用すれば、実施形態20と同様の効果が得られることは、いうまでもない。

[Embodiment 20]

The

〔比較例2〕

本発明の比較例2は、実施形態1から20に比較して、駆動方法が異なるだけである。よって、これについて図42を用いて説明する。図42は比較例2の各配線および電極の電位の時間変化と画素の輝度の時間変化の例である。

[Comparative Example 2]

Comparative Example 2 of the present invention differs from

比較例2では、すべての走査線に選択パルスが順次供給されて、すべての画素電極に表示するための電位が信号線から画素電極に印加され、保持された後、バックライトが点灯して表示が行なわれる。従来のバックライトが点灯され続けられた状態で、画素電極に電位を印加する表示方式では、動画像の輪郭が不鮮明になるといった問題があったが、この比較例2の駆動方式を用いて、間欠的に表示を行うことによって、この輪郭の不鮮明を防ぐことが可能ではある。しかしながら、画面全体で均一な表示を実現するためには、画素電極に電圧を印加した後、液晶が完全に応答してからバックライトを点灯させる必要があるため,点灯時間が短くなり、明るい表示が得られないといった問題がある。 In Comparative Example 2, the selection pulse is sequentially supplied to all the scanning lines, and the potential for displaying on all the pixel electrodes is applied from the signal line to the pixel electrodes and held, and then the backlight is turned on for display. Is done. In the conventional display method in which the potential is applied to the pixel electrode while the backlight is kept on, there is a problem that the outline of the moving image becomes unclear, but using the drive method of this comparative example 2, By performing intermittent display, it is possible to prevent blurring of the outline. However, in order to realize a uniform display on the entire screen, it is necessary to turn on the backlight after the liquid crystal has completely responded after applying a voltage to the pixel electrode. There is a problem that cannot be obtained.

図42に示す例では、1〜m番目の走査線にVG(1)〜VG(m)の電圧波形(選択パルス)を順次印加して、それぞれ表示に対応した信号電圧VDを画素電極に順次書き込んでいく。最後の走査線(m番目)に対応した画素電極に電圧が書き込まれたあと、一定期間(この場合5ms)をおいてバックライトを点灯させる。この時間を1フレームと称する。この場合、16.6msである。図42において、画素の輝度B(1)〜B(m)は特定の信号線に対応した、1〜m番目の走査線に接続された画素の輝度を示している。バックライトが点灯している期間は斜線で示した。この例の場合、(1)(2)番目のフレームでは表示は変化していない。(3)番目のフレームで画像Aから画像Bに表示が変化した後、(4)(5)のフレームでは再び表示は変化していない。 In the example shown in FIG. 42, voltage waveforms (selection pulses) VG (1) to VG (m) are sequentially applied to the 1st to mth scanning lines, and the signal voltage VD corresponding to each display is sequentially applied to the pixel electrodes. Write. After the voltage is written to the pixel electrode corresponding to the last scanning line (m-th), the backlight is turned on after a certain period (5 ms in this case). This time is called one frame. In this case, 16.6 ms. In FIG. 42, the luminances B (1) to B (m) of the pixels indicate the luminances of the pixels connected to the 1-mth scanning lines corresponding to the specific signal lines. The period during which the backlight is on is indicated by hatching. In this example, the display has not changed in the (1) and (2) th frames. (3) After the display changes from the image A to the image B in the third frame, the display does not change again in the frames (4) and (5).

(2)番目のフレームから(3)番目のフレームにおいて、1番目及び2番目の走査線に対応する画素の表示は最高階調レベル(255レベル)から中間階調レベルに変化している。これらの画素の輝度B(1)及びB(2)は、電圧が書き込まれてから、バックライトが点灯するまでの間に十分な時間があるので、所望の(画像Bを表示するための)中間階調調レベルに達してからバックライトが点灯している。一方、m番目の走査線に対応する画素の表示は最高階調レベル(255階調レベル)から最低階調レベル(0階調レベル)に変化している。一番最後のm番めの走査線に対応する画素では、画素電極に電圧が印加されてから、バックライトが点灯するまでの期間が5msと短いため、B(m)のように、輝度が0階調レベルに達する前にバックライトが点灯してしまう。このように、動画の輪郭の不鮮明さを防ぐための本比較例2の駆動方法の場合においても、1番目に近い最初の方の走査線に対応した画素では効果があるが、m番目に近い最後の方の走査線に対応した画素では効果が得られない。 From the (2) th frame to the (3) th frame, the display of the pixels corresponding to the first and second scanning lines is changed from the highest gradation level (255 level) to the intermediate gradation level. The luminance B (1) and B (2) of these pixels has a desired time (for displaying the image B) since there is sufficient time from when the voltage is written to when the backlight is turned on. The backlight is turned on after reaching the halftone level. On the other hand, the display of the pixel corresponding to the mth scanning line is changed from the highest gradation level (255 gradation level) to the lowest gradation level (0 gradation level). In the pixel corresponding to the last m-th scanning line, since the period from when the voltage is applied to the pixel electrode until the backlight is turned on is as short as 5 ms, the luminance is as in B (m). The backlight is turned on before reaching the 0 gradation level. As described above, even in the case of the driving method according to the second comparative example for preventing blurring of the outline of the moving image, the pixel corresponding to the first scanning line that is closest to the first is effective, but is close to the mth. No effect can be obtained with the pixel corresponding to the last scanning line.

図43は、本比較例で用いた液晶表示素子の輝度の応答特性を示す図である。256階調の場合で、0階調レベルから各階調レベルへの応答時間と、255階調レベルから各階調レベルへの応答時間と、中間階調レベルから各階調レベルへの応答時間を示した。最終到達階調レベルを横軸、応答時間を縦軸にとり、始点での階調レベルをパラメータとして示す。応答時間の定義を図44に示す。縦軸は輝度を階調レベルで表したもの、横軸は時間である。最高階調レベル(この場合は255階調レベル)と最低階調レベル(0階調レベル)との輝度差を100%として、輝度が最終到達階調レベルに対して±5%に達するまでの時間を応答時間と定義する。図43(a)は低い階調レベル(63階調レベル)から高い階調レベル(191階調レベル)への応答の場合である(立ち上がり)。最終到達階調レベルである191階調レベルの−5%、すなわち178.25階調レベルに達するまでの時間が応答時間である。図43(b)は高い階調レベル(191階調レベル)から低い階調レベル(0階調レベル)への応答の場合である(立ち下がり)。最終到達階調レベルである0階調レベルの+5%、すなわち12.75階調レベルに達するまでの時間が応答時間である。 FIG. 43 is a diagram showing the luminance response characteristics of the liquid crystal display element used in this comparative example. In the case of 256 gradations, the response time from the 0 gradation level to each gradation level, the response time from the 255 gradation level to each gradation level, and the response time from the intermediate gradation level to each gradation level are shown. . The final reached gradation level is taken on the horizontal axis, the response time is taken on the vertical axis, and the gradation level at the start point is shown as a parameter. The definition of the response time is shown in FIG. The vertical axis represents luminance in terms of gradation level, and the horizontal axis represents time. The luminance difference between the highest gradation level (255 gradation level in this case) and the lowest gradation level (0 gradation level) is assumed to be 100% until the luminance reaches ± 5% with respect to the final gradation level. Time is defined as response time. FIG. 43A shows a case of a response from a low gradation level (63 gradation levels) to a high gradation level (191 gradation levels) (rise). The response time is −5% of the 191 gradation level which is the final arrival gradation level, that is, the time until the gradation reaches the 178.25 gradation level. FIG. 43B shows a response from the high gradation level (191 gradation level) to the low gradation level (0 gradation level) (falling). The response time is the time required to reach + 5% of the 0th gradation level, which is the final reached gradation level, that is, the 12.75th gradation level.

本発明では、0階調レベルから各階調レベルへの応答が5ms以下と改善されているが、255階調レベルからの応答特性は、基本的に緩和過程によるものであり改善はされておらず、図43に示すように遅い応答となっている。特に、255階調レベルから0階調レベルへの応答は遅く、バックライトが点灯するまでの期間を長くしないと、輝度が0階調レベルに達する前にバックライトが点灯してしまうという問題の原因となっている。 In the present invention, the response from the 0 gradation level to each gradation level is improved to 5 ms or less, but the response characteristic from the 255 gradation level is basically due to the relaxation process and is not improved. As shown in FIG. 43, the response is slow. In particular, the response from the 255 gradation level to the 0 gradation level is slow, and unless the period until the backlight is turned on is lengthened, the backlight is turned on before the luminance reaches the 0 gradation level. It is the cause.

〔実施形態21〕

実施形態21は比較例2の問題を解決する駆動方法である。実施形態1から20に比較して、駆動方法が異なるだけである。図45は本実施形態の各配線および電極の電位の時間変化と画素の透過率の時間変化の例である。

[Embodiment 21]

The twenty-first embodiment is a driving method that solves the problem of the second comparative example. Compared with

比較例2と異なるのは、順次走査を行う前に、すべての走査線に選択パルスを与えて、すべての画素に0階調レベルに対応する電圧を印加している点である。図45では黒く塗りつぶしたパルスで示してある。以後このパルスをアシストパルスと称する。 The difference from Comparative Example 2 is that a selection pulse is applied to all scanning lines and a voltage corresponding to the 0 gradation level is applied to all pixels before sequential scanning. In FIG. 45, the pulses are blacked out. Hereinafter, this pulse is referred to as an assist pulse.

B(1)〜B(m)、VG(1)〜VG(m)、VDは、それぞれ図42の場合と同様に画素の輝度、走査線の印加電圧波形(選択パルス)、信号電圧線の印加電圧波形を示している。また、図42の場合と同様、(1)(2)番目のフレームでは表示は変化していない。(3)番目のフレームで画像Aから画像Bに表示が変化した後、(4)(5)のフレームでは再び表示は変化していない。 B (1) to B (m), VG (1) to VG (m), and VD are the pixel brightness, scanning line applied voltage waveform (selection pulse), and signal voltage line as in FIG. The applied voltage waveform is shown. As in the case of FIG. 42, the display is not changed in the (1) and (2) th frames. (3) After the display changes from the image A to the image B in the third frame, the display does not change again in the frames (4) and (5).

(1)番目のフレームについて説明する。1番目の走査線に対応した画素の輝度B(1)は、アシストパルスによって、階調レベル0の輝度に向かって応答しかけるが、続けてすぐに選択パルスが印加されて、所定の(画像Aを表示するための)電圧が画素電極に印加されるため、すぐにもとの輝度に戻る。2番目の走査線に対応した画素の輝度B(2)も同様である。最後の走査線に対応した画素の輝度B(m)は、アシストパルスが印加された後、選択パルスが印加されるまでに十分な時間があるため、その輝度は0階調レベルに達する。その後、選択パルスの印加によって輝度は所定の(画像Aを表示するための)輝度に向かって応答する。この時、図4242に示すように0階調レベルから各階調レベルへの応答は最大でも5msと高速であるため、バックライトが点灯するまでの期間(5ms)中に所定の(画像Aを表示するための)輝度に達することができる。以上のようにして、すべての画素が応答し終わってからバックライトが点灯するので、(1)番目のフレームにおいて均一な表示が可能である。(2)番目のフレームに関しても同様である。

The (1) th frame will be described. The brightness B (1) of the pixel corresponding to the first scanning line responds toward the brightness of

(3)番目のフレームでは、表示が変化している。比較例2の場合と同様に、(2)番目のフレームから(3)番目のフレームにおいて、1番目及び2番目の走査線に対応する画素の表示は最高階調レベル(255階調レベル)から中間階調レベルに変化している。これらの画素の輝度B(1)及びB(2)は、電圧が書き込まれてから、バックライトが点灯するまでの間に十分な時間があるので、所望の(画像Bを表示するための)中間階調レベルに達してからバックライトが点灯している。一方、m番目の走査線に対応する画素の表示は最高階調レベル(255階調レベル)から最低階調レベル(0階調レベル)に変化している。アシストパルスが印加されてから、選択パルスが印加されるまでの期間は、(1)番目及び(2)番目のフレームと同様で、画素の輝度B(m)は、アシストパルスが印加された後、選択パルスが印加されるまでに十分な時間があるため、その輝度は0階調レベルに達する。その後、選択パルスによって、所定の表示(画像Bを表示するための)である0階調レベルに対応した電圧が画素電極に印加されるが、その輝度B(m)はすでに0階調レベルに達している。したがって、バックライトが点灯する際にはすべての画素が所定の(画像Bを表示するための)輝度に達しており、所定の表示が可能である。 (3) In the second frame, the display changes. As in the case of Comparative Example 2, in the (2) th frame to the (3) th frame, the display of the pixels corresponding to the first and second scanning lines starts from the highest gray level (255 gray level). It has changed to an intermediate gradation level. The luminance B (1) and B (2) of these pixels has a desired time (for displaying the image B) since there is sufficient time from when the voltage is written to when the backlight is turned on. The backlight is turned on after reaching the halftone level. On the other hand, the display of the pixel corresponding to the mth scanning line is changed from the highest gradation level (255 gradation level) to the lowest gradation level (0 gradation level). The period from when the assist pulse is applied to when the selection pulse is applied is the same as that of the (1) th and (2) th frames, and the luminance B (m) of the pixel is after the assist pulse is applied. Since there is a sufficient time until the selection pulse is applied, the luminance reaches the 0 gradation level. Thereafter, a voltage corresponding to the 0 gradation level which is a predetermined display (for displaying the image B) is applied to the pixel electrode by the selection pulse, but the luminance B (m) is already at the 0 gradation level. Has reached. Therefore, when the backlight is lit, all the pixels reach a predetermined luminance (for displaying the image B), and a predetermined display is possible.

以上のように、実施形態20を用いれば、選択パルスから点灯までの期間の短い、m番目に近い最後の方の走査線に対応した画素では、その応答がかならず0階調レベルからの速い応答となるため、比較例2のように、最後の方の走査線に対応した画素の表示が不良となることは無く、良好な表示が可能である。以上のように、選択パルスを順次印加して、すべての画素電極に所定の電圧を書き込んだあとに、バックライトを点灯させることによって、動画を鮮明に表示する駆動方法において、選択パルスを順次印加する前に、すべての画素に0階調レベルに対応した電圧を印加することにより、良好な動画表示を実現することが可能である。 As described above, according to the twentieth embodiment, the response corresponding to the last scanning line closest to the m-th, which has a short period from the selection pulse to lighting, is always a fast response from the 0 gradation level. Therefore, unlike the comparative example 2, the display of the pixel corresponding to the last scanning line does not become defective, and a good display is possible. As described above, after applying a selection pulse in sequence and writing a predetermined voltage to all the pixel electrodes, the selection pulse is applied sequentially in the driving method in which the backlight is turned on to display a moving image clearly. Before the image is displayed, a satisfactory moving image display can be realized by applying a voltage corresponding to the 0 gradation level to all the pixels.

尚、本実施形態ではアシストパルスによって0階調レベルに対応した電圧をすべての画素電極に印加し、保持したが、液晶表示方式によっては必ずしも0階調レベルに対応した電圧を印加する必要はない。図46R>6はTN液晶の応答特性を示す図であるが、この場合にはその階調からの各階調レベルへの応答時間の最大値が最も小さい63階調レベルに対応した電圧を印加するべきである。以上のように、液晶素子の特性に応じて、その状態からの各階調レベルへの応答時間の最大値がもっとも小さくなる状態になるような電圧をアシストパルスの期間に画素に印加するべきである。 In this embodiment, the voltage corresponding to the 0 gradation level is applied to and held by all the pixel electrodes by the assist pulse. However, depending on the liquid crystal display method, it is not always necessary to apply the voltage corresponding to the 0 gradation level. . FIG. 46R> 6 shows the response characteristics of the TN liquid crystal. In this case, a voltage corresponding to the 63 gradation level with the smallest maximum response time from the gradation to each gradation level is applied. Should. As described above, in accordance with the characteristics of the liquid crystal element, a voltage that minimizes the maximum response time from each state to each gradation level should be applied to the pixel during the assist pulse period. .

また、IPS表示モードにおいても、アシストパルスによって必ずしも0階調レベルに対応した電圧をすべての画素電極に印加する必要はない。走査線に順次パルス電圧を印加する前に、予め画素電極の全てに同一の電圧を印加することにより、各画素電極周辺の液晶を各階調への応答時間の最大値が前記一定期間よりも短い状態になるような状態にしておけば良い。例えば、一定期間が5msであればその状態は0に近い階調であれば良く、一定期間が6msであれば、その状態は階調0〜63であれば良い。

In the IPS display mode, it is not always necessary to apply a voltage corresponding to the 0 gradation level to all the pixel electrodes by the assist pulse. By applying the same voltage to all of the pixel electrodes in advance before sequentially applying the pulse voltage to the scanning lines, the maximum response time for each gradation of the liquid crystal around each pixel electrode is shorter than the predetermined period. It should be in a state that will be in a state. For example, if the fixed period is 5 ms, the state may be a gradation close to 0, and if the fixed period is 6 ms, the state may be the

また、このようなアシストパルスは、一定の階調に統一するのであれば、前記画素電極の全てに同一の電圧を印加すれば良い。また、画素電極の電位と前記共通電極の電位とを等しくすることにより同一の電圧を印加しても良い。このようなアシストパルスの印加は、図2のような回路構成を用いて、初めの選択パルスの代わりにアシストパルスを用いて、画素電極に共通電極と同じ電位を供給し、次の選択パルスによって、画像を表示するための電位を前記画素電極に供給することにより実現しても良く、図40のような回路構成を用いて、共通電極配線36”を介して共通電極36に印加する選択パルスの代わりにアシストパルスを用いて、画素電極に共通電極と同じ電位を供給し、続いて、同じ周期期間中の、選択パルス102によって、画像を表示するための電位を画素電極に供給することにより実現しても良い。それ以外にも、図2のような回路構成を用いて、信号線電位を0階調レベルにして全ての走査線を一括選択することによりアシストパルスを印加する等、走査線に順次選択パルスを印加する前に、予め画素電極の全てにアシストパルスを用いて所定の(0階調の付近にする)電位を供給できる回路構成であれば良い。

Further, if such assist pulses are unified to a certain gradation, the same voltage may be applied to all the pixel electrodes. Further, the same voltage may be applied by making the potential of the pixel electrode equal to the potential of the common electrode. Such an assist pulse is applied by using the circuit configuration as shown in FIG. 2 to supply the same potential as the common electrode to the pixel electrode by using the assist pulse instead of the first selection pulse, and by the next selection pulse. This may be realized by supplying a potential for displaying an image to the pixel electrode, and a selection pulse applied to the

1,2…基板、3…平坦化膜、4…カラーフィルタ、5…ブラックマトリクス、6…偏光板、11…画素、21…電気力線、22…表示部、31…信号線、32…走査線、33…第1TFT、33’…第2TFT、34…液晶、35…画素電極、36…共通電極、36’…共通電極接続部、36”…共通電極配線、81…絶縁膜、82…保護膜、85…配向膜、86…第2絶縁膜、101,102,103…選択パルス、110…1周期期間

DESCRIPTION OF

Claims (6)

前記第1基板上に配置された複数の走査線と、前記第1基板上に前記走査線と交差して配置された信号線と、前記走査線と前記信号線とに囲まれた領域に対応して構成される画素と、前記第1基板上に配置され、前記信号線に対応した画素電極と、前記第1基板上または前記第2基板上に配置され、前記画素電極に対応した共通電極と、前記走査線と前記信号線との交点に対応して配置され、前記信号線と前記走査線と前記画素電極とに電気的に接続された第1アクティブ素子と、前記第1基板上に配置された絶縁膜とを有し、

1画像を表示する1周期期間中に、前記走査線に順次パルス電圧を印加して、前記画素電極の全てに画像を表示するための電位を印加し、保持させた後、一定期間を置いて光源が点灯される液晶表示装置において、

前記1周期期間中の最後にパルス電圧が印加される走査線に対応する画素の液晶の前記パルス電圧が印加される直前の状態が、その状態から各階調への応答時間の最大値が前記一定期間よりも短い状態であるようにする状態調整手段を設けたことを特徴とする液晶表示装置。 A light source, a first substrate, a second substrate disposed opposite to the first substrate, a liquid crystal layer sandwiched between the first substrate and the second substrate,

Corresponding to a plurality of scanning lines arranged on the first substrate, a signal line arranged intersecting the scanning line on the first substrate, and a region surrounded by the scanning lines and the signal lines And a pixel electrode disposed on the first substrate and corresponding to the signal line, and a common electrode disposed on the first substrate or the second substrate and corresponding to the pixel electrode A first active element disposed corresponding to an intersection of the scanning line and the signal line and electrically connected to the signal line, the scanning line, and the pixel electrode; and on the first substrate. And having an insulating film disposed,

During one cycle period for displaying one image, a pulse voltage is sequentially applied to the scanning lines, a potential for displaying an image is applied to all of the pixel electrodes, and held for a certain period. In the liquid crystal display device in which the light source is turned on,

The state immediately before the pulse voltage is applied to the liquid crystal of the pixel corresponding to the scanning line to which the pulse voltage is applied last in the one cycle period is the maximum value of the response time from that state to each gradation is the constant. A liquid crystal display device, characterized in that a state adjusting means is provided to make the state shorter than the period.

前記状態調整手段が、前記走査線に順次前記パルス電圧を印加する前に、前記画素電極の全てに同一の電圧を印加する手段であることを特徴とする液晶表示装置。 The liquid crystal display device according to claim 1.

The liquid crystal display device, wherein the state adjusting means is means for applying the same voltage to all of the pixel electrodes before sequentially applying the pulse voltage to the scanning lines.

前記状態調整手段が、前記走査線に順次前記パルス電圧を印加する前に、前記画素電極の電位と前記共通電極の電位とを等しくする手段を有することを特徴とする液晶表示装置。 The liquid crystal display device according to claim 1 or 2,

The liquid crystal display device, wherein the state adjusting means includes means for equalizing the potential of the pixel electrode and the potential of the common electrode before sequentially applying the pulse voltage to the scanning lines.

前記第1基板上に配置された複数の走査線と、前記第1基板上に前記走査線と交差して配置された信号線と、前記走査線と前記信号線とに囲まれた領域に対応して構成される画素と、前記第1基板上に配置され、前記信号線に対応した画素電極と、前記第1基板上または前記第2基板上に配置され、前記画素電極に対応した共通電極と、前記走査線と前記信号線との交点に対応して配置され、前記信号線と前記走査線と前記画素電極とに電気的に接続された第1アクティブ素子と、前記第1基板上に配置された絶縁膜とを有し、

1画像を表示する1周期期間中に、前記走査線に順次パルス電圧を印加して、前記画素電極の全てに画像を表示するための電位を印加し、保持させた後、一定期間を置いて光源が点灯される液晶表示装置の駆動方法において、

前記1周期期間中の最後にパルス電圧が印加される走査線に対応する画素の液晶の状態を、その状態から各階調への応答時間の最大値が前記一定期間よりも短い状態であるように状態調整をした後に、前記走査線に順次パルス電圧を印加することを特徴とする液晶表示装置の駆動方法。 A light source, a first substrate, a second substrate disposed opposite to the first substrate, a liquid crystal layer sandwiched between the first substrate and the second substrate,

Corresponding to a plurality of scanning lines arranged on the first substrate, a signal line arranged intersecting the scanning line on the first substrate, and a region surrounded by the scanning lines and the signal lines And a pixel electrode disposed on the first substrate and corresponding to the signal line, and a common electrode disposed on the first substrate or the second substrate and corresponding to the pixel electrode A first active element disposed corresponding to an intersection of the scanning line and the signal line and electrically connected to the signal line, the scanning line, and the pixel electrode; and on the first substrate. And having an insulating film disposed,

During one cycle period for displaying one image, a pulse voltage is sequentially applied to the scanning lines, a potential for displaying an image is applied to all of the pixel electrodes, and held for a certain period. In a driving method of a liquid crystal display device in which a light source is turned on,

The liquid crystal state of the pixel corresponding to the scanning line to which the pulse voltage is applied last in the one cycle period is set so that the maximum response time from that state to each gradation is shorter than the predetermined period. A method for driving a liquid crystal display device, comprising: sequentially applying a pulse voltage to the scanning lines after adjusting the state.

前記状態調整を、前記走査線に順次前記パルス電圧を印加する前に、前記画素電極の全てに同一の電圧を印加して行うことを特徴とする液晶表示装置の駆動方法。 The method for driving a liquid crystal display device according to claim 4,

The method of driving a liquid crystal display device, wherein the state adjustment is performed by applying the same voltage to all of the pixel electrodes before sequentially applying the pulse voltage to the scanning lines.

前記状態調整を、前記走査線に順次前記パルス電圧を印加する前に、前記画素電極の電位と前記共通電極の電位とを等しくすることにより行うことを特徴とする液晶表示装置の駆動方法。 In the driving method of the liquid crystal display device according to claim 4 or 5,

The method for driving a liquid crystal display device, wherein the state adjustment is performed by equalizing a potential of the pixel electrode and a potential of the common electrode before sequentially applying the pulse voltage to the scanning lines.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005358174A JP2006139295A (en) | 2005-12-12 | 2005-12-12 | Liquid crystal display |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005358174A JP2006139295A (en) | 2005-12-12 | 2005-12-12 | Liquid crystal display |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001261744A Division JP3847590B2 (en) | 2001-08-30 | 2001-08-30 | Liquid crystal display |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2006139295A true JP2006139295A (en) | 2006-06-01 |

Family

ID=36620112

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005358174A Pending JP2006139295A (en) | 2005-12-12 | 2005-12-12 | Liquid crystal display |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2006139295A (en) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7821606B2 (en) | 2006-11-22 | 2010-10-26 | Toshiba Matsushita Display Technology Co., Ltd. | LCD device having common and pixel electrodes on first substrate and shield electrode, resin color filter layer with resin overcoat layer on second substrate |

| US8054427B2 (en) | 2007-10-05 | 2011-11-08 | Toshiba Matsushita Display Technology Co., Ltd. | Liquid crystal display device |

| US8064022B2 (en) | 2009-01-16 | 2011-11-22 | Toshiba Matsushita Display Technology Co., Ltd. | Liquid crystal display device and method of manufacturing the same |

| US8542327B2 (en) | 2007-10-16 | 2013-09-24 | Japan Display Central Inc. | Liquid crystal display device |

-

2005

- 2005-12-12 JP JP2005358174A patent/JP2006139295A/en active Pending

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7821606B2 (en) | 2006-11-22 | 2010-10-26 | Toshiba Matsushita Display Technology Co., Ltd. | LCD device having common and pixel electrodes on first substrate and shield electrode, resin color filter layer with resin overcoat layer on second substrate |

| US8054427B2 (en) | 2007-10-05 | 2011-11-08 | Toshiba Matsushita Display Technology Co., Ltd. | Liquid crystal display device |

| US8542327B2 (en) | 2007-10-16 | 2013-09-24 | Japan Display Central Inc. | Liquid crystal display device |

| US8064022B2 (en) | 2009-01-16 | 2011-11-22 | Toshiba Matsushita Display Technology Co., Ltd. | Liquid crystal display device and method of manufacturing the same |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3847590B2 (en) | Liquid crystal display | |

| US8319926B2 (en) | Liquid crystal display device | |

| KR100842503B1 (en) | Liquid crystal display panel, liquid crystal display device and liquid crystal television | |

| JP4051001B2 (en) | Liquid crystal display | |

| JP4667587B2 (en) | Liquid crystal display device | |

| US8355104B2 (en) | Liquid crystal display device | |

| US7800570B2 (en) | LCD device capable of controlling a viewing angle and method for driving the same | |

| JP2007240752A (en) | Semitransmissive liquid crystal display device | |

| JP2005234527A (en) | Method for aligning polarizer and rubbing axes in fringe field switching liquid crystal display | |

| KR101147090B1 (en) | Liquid Crystal Display Device | |

| US20130069855A1 (en) | Liquid crystal display device | |

| JP4095872B2 (en) | Liquid crystal display | |

| WO2012093621A1 (en) | Liquid-crystal display device | |

| JP2006139295A (en) | Liquid crystal display | |

| US20090096946A1 (en) | Liquid crystal display device | |

| JP4566579B2 (en) | Driving method of liquid crystal display device | |

| JP4676261B2 (en) | LIQUID CRYSTAL DISPLAY DEVICE INCLUDING COUNTER ELECTRODE HAVING HOLE AND ITS MANUFACTURING METHOD | |

| KR100680510B1 (en) | Liquid Crystal Display device | |

| JPH0980383A (en) | Liquid crystal display device | |

| KR101108387B1 (en) | Twisted nematic mode liquid crystal display device and method for manufacturing lcd | |

| JP2006153904A (en) | Liquid crystal display device | |

| JP2008058689A (en) | Liquid crystal device, and electronic apparatus | |

| JPH07318944A (en) | Liquid crystal display element and liquid crystal display device using this element | |

| KR20040006662A (en) | Liquid crystal display device | |

| JP2003149623A (en) | Liquid crystal display device and method for driving the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060801 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20061128 |