JP2006040535A - Semiconductor memory device and dynamic type semiconductor memory device - Google Patents

Semiconductor memory device and dynamic type semiconductor memory device Download PDFInfo

- Publication number

- JP2006040535A JP2006040535A JP2005299072A JP2005299072A JP2006040535A JP 2006040535 A JP2006040535 A JP 2006040535A JP 2005299072 A JP2005299072 A JP 2005299072A JP 2005299072 A JP2005299072 A JP 2005299072A JP 2006040535 A JP2006040535 A JP 2006040535A

- Authority

- JP

- Japan

- Prior art keywords

- signal

- memory

- circuit

- level

- refresh

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Dram (AREA)

Abstract

Description

この発明は半導体記憶装置に関し、特に、ダイナミック型メモリセルの記憶データを保持するためのデータ保持モードにおける消費電流を低減するための構成に関する。 The present invention relates to a semiconductor memory device, and more particularly to a configuration for reducing current consumption in a data holding mode for holding data stored in a dynamic memory cell.

ダイナミック型半導体記憶装置(以下、DRAMと称す)においては、1ビットのメモリセルが1つのMOSトランジスタ(絶縁ゲート型電界効果トランジスタ)と1つのキャパシタとで構成される。1ビットのメモリセルの占有面積が小さくかつビット単価が複数のトランジスタ素子を1ビットのメモリセルに必要とするスタティック・ランダム・アクセス・メモリ(SRAM)よりも安いため、大記憶容量の記憶装置としてDRAMは広く用いられている。 In a dynamic semiconductor memory device (hereinafter referred to as DRAM), a 1-bit memory cell is composed of one MOS transistor (insulated gate field effect transistor) and one capacitor. As a memory device with a large storage capacity, the occupied area of a 1-bit memory cell is small and the unit price per bit is lower than that of a static random access memory (SRAM) that requires a plurality of transistor elements in a 1-bit memory cell. DRAM is widely used.

このDRAMは、キャパシタに情報を電荷の形態で格納しており、リーク電流によりその蓄積電荷量が低減して記憶データが破壊されるのを防止するために、定期的にメモリセルの記憶データを読出して再書込するリフレッシュ動作を行う必要がある。 In this DRAM, information is stored in a capacitor in the form of electric charge, and in order to prevent the stored data from being destroyed due to a reduction in the amount of stored charge due to a leakage current, the stored data in the memory cell is periodically stored. It is necessary to perform a refresh operation for reading and rewriting.

近年、ラップトップ型コンピュータなどの携帯端末等の主記憶装置としてDRAMは広く用いられている。携帯端末などの情報機器は、電池を動作電源として利用しており、この電池の寿命をできるだけ長くするためには携帯端末の消費電流をできるだけ小さくすることが必要とされる。携帯端末において情報処理が行われていない場合においても、DRAMの記憶データを定期的にリフレッシュする必要がある。このように、DRAMに対してデータの入出力を行わず内部でメモリセルの記憶データのリフレッシュのみを行う動作モードは、「データ保持モード」と呼ばれている。 In recent years, DRAMs have been widely used as main storage devices for portable terminals such as laptop computers. An information device such as a portable terminal uses a battery as an operating power source, and it is necessary to make the current consumption of the portable terminal as small as possible in order to make the battery life as long as possible. Even when information processing is not performed in the portable terminal, it is necessary to periodically refresh the data stored in the DRAM. As described above, an operation mode in which only data stored in the memory cell is refreshed without inputting / outputting data to / from the DRAM is called a “data holding mode”.

このようなデータ保持モードにおいては、たとえばDRAMの電源電圧を低下させたり、またリフレッシュ間隔を長くすることにより、消費電流を小さくすることが図られている。 In such a data holding mode, for example, the power consumption is reduced by decreasing the power supply voltage of the DRAM or by extending the refresh interval.

しかしながら、この電池駆動型機器において電池の寿命をより長くするために、DRAMにおいて、データ保持モード時に消費されるデータ保持電流(リフレッシュ動作時の電流およびスタンドバイ時の電流)をより低減することが要求されている。また、通常動作モード時においても安定に動作電源電圧を供給することが要求される。 However, in order to extend the life of the battery in this battery-driven device, it is possible to further reduce the data retention current (current during the refresh operation and current during standby) consumed in the data retention mode in the DRAM. It is requested. Further, it is required to stably supply the operation power supply voltage even in the normal operation mode.

それゆえ、この発明の目的は、通常動作モード時に安定に動作電源電圧を供給しかつデータ保持モード時における消費電流がより低減された半導体記憶装置およびダイナミック型半導体記憶装置を提供することである。 SUMMARY OF THE INVENTION Therefore, an object of the present invention is to provide a semiconductor memory device and a dynamic semiconductor memory device that can stably supply an operating power supply voltage in a normal operation mode and can further reduce current consumption in a data holding mode.

この発明の第1の観点に係る半導体記憶装置は、メモリセルが行列状に配列された構成を有するメモリセルアレイをそれぞれが含む複数のメモリマットを備える半導体記憶装置であって、半導体記憶装置の外部からデータアクセスが行われ、第1の動作電流が流れる第1の動作モードと、半導体記憶装置の外部からデータアクセスが行われず、メモリセルの記憶データがリフレッシュされ、第1の動作電流よりも少ない第2の動作電流が流れる第2の動作モードとを有し、さらに、各メモリマットにそれぞれ設けられ、半導体記憶装置の外部から与えられる電源電位を降下させた内部電源電位を対応のメモリマットに与える内部降圧手段を備える。この内部降圧手段は、メモリマットを指定するメモリマット指定信号により活性化され、第1の動作モード時に比べ、第2の動作モードにおいて半導体記憶装置の外部の電源から対応のメモリマットへ流れる電流量を小さくして電流を供給する。 A semiconductor memory device according to a first aspect of the present invention is a semiconductor memory device including a plurality of memory mats each including a memory cell array having a configuration in which memory cells are arranged in a matrix, and is external to the semiconductor memory device. Data access is performed from the first operation mode in which the first operation current flows, and data access is not performed from the outside of the semiconductor memory device, the stored data in the memory cell is refreshed, and is less than the first operation current. A second operation mode in which a second operation current flows, and is provided in each memory mat, and an internal power supply potential applied from the outside of the semiconductor memory device is reduced to a corresponding memory mat. Provide internal pressure drop means. This internal voltage step-down means is activated by a memory mat designation signal for designating a memory mat, and compared with the first operation mode, the amount of current flowing from the power supply external to the semiconductor memory device to the corresponding memory mat in the second operation mode Reduce the current to supply current.

この発明の第2の観点に係るダイナミック型半導体記憶装置は、メモリセルが行列状に配列された構成を有するメモリセルアレイをそれぞれが含む複数のメモリマットを備える。このダイナミック型半導体記憶装置は、半導体記憶装置の外部からデータアクセスが行われ、第1の動作電流が流れる通常動作モードと、半導体記憶装置の外部からデータアクセスが行われず、メモリセルの記憶データがリフレッシュされ、第1の動作電流よりも少ない第2の動作電流が流れるデータ保持モードとを有する。 A dynamic semiconductor memory device according to a second aspect of the present invention includes a plurality of memory mats each including a memory cell array having a configuration in which memory cells are arranged in a matrix. In this dynamic semiconductor memory device, data is accessed from outside the semiconductor memory device, the normal operation mode in which the first operating current flows, and data access from outside the semiconductor memory device is not performed. A data holding mode in which the second operating current is refreshed and a second operating current smaller than the first operating current flows.

この発明の第2の観点に係るダイナミック型半導体記憶装置は、さらに各メモリマットにそれぞれ設けられ、半導体記憶装置の外部から与えられる電源電位を降下させた内部電源電位を対応のメモリマットに与える内部降圧手段を備える。この内部降圧手段は、メモリマットを指定するメモリマット指定信号により活性化され、通常動作モード時に比べ、データ保持モードにおいて半導体記憶装置の外部の電源から対応のメモリマットへ流れる電流量を小さくして電流を供給する。 The dynamic semiconductor memory device according to the second aspect of the present invention is further provided in each memory mat, and an internal power supply potential obtained by lowering the power supply potential applied from the outside of the semiconductor memory device is supplied to the corresponding memory mat. Step-down means is provided. This internal voltage step-down means is activated by a memory mat designation signal for designating a memory mat, and reduces the amount of current flowing from the power supply external to the semiconductor memory device to the corresponding memory mat in the data holding mode as compared with the normal operation mode. Supply current.

各メモリマットに対応して内部降圧回路を設け、それぞれ対応のメモリマットに内部電源電圧を供給することにより、各メモリマットに対して安定に電源電圧を供給することができる。 By providing an internal step-down circuit corresponding to each memory mat and supplying the internal power supply voltage to the corresponding memory mat, the power supply voltage can be stably supplied to each memory mat.

[実施の形態1]

図1は、この発明の実施の形態1に従うDRAMの選択メモリセルの配置を示す図である。図1(A)は、通常動作モード時の選択メモリセルの配置を示し、図1(B)は、データ保持モードにおけるリフレッシュ動作時における選択メモリセル(リフレッシュメモリセル)の配置を示す。

[Embodiment 1]

FIG. 1 shows an arrangement of selected memory cells in a DRAM according to the first embodiment of the present invention. FIG. 1A shows the arrangement of selected memory cells in the normal operation mode, and FIG. 1B shows the arrangement of selected memory cells (refresh memory cells) in the refresh operation in the data holding mode.

図1(A)において、半導体記憶装置1は、4つのメモリマットMM♯0〜MM♯3を含む。ここで、以下の説明において「メモリマット」は、メモリセルが行列状に配置されたメモリアレイと、このメモリセルを選択状態へ駆動するための周辺回路との両者を含む用語として用いる。メモリマットMM♯0〜MM♯3の各々は、複数のサブアレイ(以下の説明においては、8個のサブアレイMB♯0〜MB♯7を例示的に示す)を有する。

1A,

選択メモリセルに対しデータの入力または出力を行うデータアクセスが行われる通常動作モード時においては、メモリマットMM♯0〜MM♯3各々において、1つのサブアレイ(図1(A)においてMB♯0)が選択状態とされる。この選択状態とされたサブアレイMB♯0においてメモリセルが選択される。この図1(A)に示すように、選択状態へ駆動されるサブアレイをメモリマットMM♯0〜MM♯3それぞれに分散させることにより、メモリマットMM♯0〜MM♯3各々において、センスアンプ動作時(選択メモリセルデータの検知および増幅)におけるピーク電流を低減することができ、応じて電源線のノイズが低減される。これにより、高速動作時においても、電源ノイズの影響に対するマージンを考慮する必要がなく高速動作を行うことができる。

In the normal operation mode in which data access for inputting or outputting data to / from the selected memory cell is performed, each memory

図1(B)に示すように、データ保持モード動作時においてメモリセルの記憶データのリフレッシュが行われる場合、4つのメモリマットMM♯0〜MM♯3のうち、1つのメモリマット(メモリマットMM♯0を例示的に示す)が選択状態とされる。この選択状態とされたメモリマットMM♯0において、複数のサブアレイ(図1(B)において、MB♯0,MB♯2、MB♯4およびMB♯6)が選択状態へ駆動され、選択状態とされたサブアレイMB♯0,MB♯2,MB♯4およびMB♯6においてメモリセルの記憶データのリフレッシュが行われる。リフレッシュ動作が行われるサブアレイを1つのメモリマットに集中させることにより、リフレッシュ動作時において、サブアレイを活性化するためのローカル活性化信号を1つのメモリマットに対してのみ活性状態とすることができる。したがって、メモリマットそれぞれにおいて設けられた制御回路においてローカル活性化信号を活性状態へ駆動する必要がなく、消費電流を大幅に低減することができる。

As shown in FIG. 1B, when data stored in the memory cell is refreshed during the data holding mode operation, one memory mat (memory mat MM) among the four memory

図2は、この発明の実施の形態1に従う半導体記憶装置(DRAM1)のデータ保持モード動作時におけるリフレッシュ動作に関連する部分の構成を概略的に示すブロック図である。図2において、メモリマットMM♯0〜MM♯3の各々は、行列状に配列される複数のメモリセルを有するメモリアレイMA♯0〜MA♯3と、活性化時、対応のメモリアレイMA♯0〜MA♯3において、リフレッシュされるメモリセルの行を選択状態へ駆動するロウデコーダRD0〜RD3を含む。

FIG. 2 is a block diagram schematically showing a configuration of a portion related to the refresh operation during the data holding mode operation of the semiconductor memory device (DRAM 1) according to the first embodiment of the present invention. In FIG. 2, each of memory mats MM # 0-

DRAM1は、さらに、入力端子2aを介して外部から与えられるロウアドレスストローブ信号/RASと入力端子2bを介して外部から与えられるコラムアドレスストローブ信号/CASとに応答して、データ保持モードが指定されたか否かを検出するデータ保持モード検出回路4と、このリフレッシュ検出回路4からのデータ保持モード検出信号REFに応答して、リフレッシュに必要とされる各種制御を行うリフレッシュ制御回路6と、リフレッシュ制御回路6からのデータ保持モード検出に応答して活性化されて、所定の間隔でリフレッシュ要求信号φrefを出力するタイマ8と、リフレッシュ制御回路6からの制御信号に応答して活性化され、リフレッシュされるべきメモリセルを指定するリフレッシュアドレスを生成するリフレッシュカウンタ10を含む。このリフレッシュカウンタ10は、リフレッシュされるべきメモリマットおよびサブアレイを指定するリフレッシュアレイ指定アドレスRAAならびにサブアレイおよびそこにおけるリフレッシュされるべきメモリセルの行を指定するリフレッシュ行アドレスRRAを出力する。

DRAM1は、さらに、リフレッシュ制御回路6からの制御信号に応答して、リフレッシュカウンタ10からのリフレッシュ行アドレスRRAおよび入力端子2cを介して外部から与えられるアドレス信号の一方を選択的に通過させるマルチプレクサ14と、リフレッシュ制御回路6からの制御信号(リフレッシュ動作活性化信号)に応答して活性化され、マルチプレクサ14から与えられる内部ロウアドレス信号をバッファ処理して内部ロウアドレス信号を生成するロウアドレスバッファ16と、リフレッシュ制御回路6からの制御信号に応答して活性化され、リフレッシュカウンタ10からのアレイ指定アドレスRAAをデコードし、メモリマットMM♯0〜MM♯3のうちの1つのメモリマットを選択状態とする信号を出力するアレイ制御回路12を含む。

Further, in response to a control signal from the

マルチプレクサ14はデータ保持モード指定時、リフレッシュ制御回路6の制御の下に、リフレッシュカウンタ10から与えられるリフレッシュアドレスRRAを選択してロウアドレスバッファ16へ与える。ロウアドレスバッファ16は、その内部構成は後に詳細に説明するが、データ保持モード検出時、複数のサブアレイを同時に選択状態とするように、サブアレイ指定アドレスを縮退状態とする。ここで、「縮退する」は、相補アドレス信号がともに選択状態とされる状態を示す。

When the data holding mode is designated, the

アレイ制御回路12は、リフレッシュ制御回路6の制御の下に、データ保持モード指定時、リフレッシュカウンタ10からのアレイアドレスRAAをデコードして、1つのメモリマットのみを選択状態とする。このアレイ制御回路12は、データ保持モードの非検出時、すなわち通常動作モード時においては、すべてのメモリマットMM♯0〜MM♯3を選択状態とする。次に各部の構成および動作について説明する。

Under the control of the

図3は図2に示すリフレッシュ検出回路4およびリフレッシュ制御回路6の動作を示す波形図である。図3において、リフレッシュ検出回路4は、ロウアドレスストローブ信号/RASの立下がりよりも先にコラムアドレスストローブ信号/CASがLレベルとされると、データ保持モードが指定されたと判定して、データ保持モード検出信号REFを活性状態のHレベルとする。リフレッシュ制御回路6は、このリフレッシュ検出回路4からのデータ保持モード検出信号REFに応答してタイマ8を起動する。タイマ8は、このリフレッシュ制御回路6からの起動信号に応答して、所定期間tuが経過すると、リフレッシュ要求信号φrefを出力する。

FIG. 3 is a waveform diagram showing operations of the

リフレッシュ制御回路6は、このタイマ8からのリフレッシュ要求信号φrefに応答して、リフレッシュ動作活性化信号ZRASをLレベルの活性状態とする。このリフレッシュ動作活性化信号ZRASは、通常動作時において外部から与えられるロウアドレスストローブ信号/RASの活性化に応答して発生される内部ロウアドレスストローブ信号/RASと同じ機能を備える。異なっているのは、このリフレッシュ動作活性化信号ZRASがLレベルの活性状態とされる期間は、予め定められている点である。このリフレッシュ動作活性化信号ZRASの活性化に応答して、リフレッシュアドレスに従ってメモリセルのデータのリフレッシュ動作が実行される。リフレッシュ制御回路6は、リフレッシュ検出回路4からのデータ保持モード検出信号REFの活性化時(ロウアドレスストローブ信号/RASがLレベルの間)、タイマ8を作動状態とする。

In response to refresh request signal φref from

タイマ8は、このリフレッシュ制御回路6からの活性化信号に応答して、所定期間Trごとにリフレッシュ要求信号φrefをHレベルの活性状態とする。このリフレッシュ要求信号φrefに従って、リフレッシュ動作活性化信号ZRASが所定期間活性状態のLレベルとされ、リフレッシュ動作が実行される。このリフレッシュ動作完了時ごとにリフレッシュカウンタ10のカウント値が変更され、次のリフレッシュされるメモリセル行の位置が指定される。

In response to the activation signal from the

リフレッシュ検出回路4の構成は、通常のいわゆる「CBR検出器」の構成と同じ構成を備える。

The configuration of the

図4は、図2に示すメモリマットのアドレス信号の割当を例示的に示す図である。図4においては、1つのメモリアレイMAのサブアレイの構成を示す。メモリアレイMAは、8つのサブアレイMB♯0〜MB♯7を含む。内部ロウアドレス信号ビットRAaおよび/RAaにより、サブアレイMB♯0〜MB♯3とサブアレイMB♯4〜MB♯7のうちの一方の4つのサブアレイのグループが指定される。内部ロウアドレス信号ビットRAaがHレベルのときには、サブアレイMB♯0〜MB♯3が指定され、ロウアドレス信号ビット/RAaがHレベルとされたときにはサブアレイMB♯4〜MB♯7が指定される。ここで、ビットRAaおよび/RAaは、互いに相補な論理を有する。

FIG. 4 is a diagram exemplarily showing allocation of address signals of the memory mat shown in FIG. FIG. 4 shows a configuration of a subarray of one memory array MA. Memory array MA includes eight subarrays MB # 0-

ロウアドレス信号ビットRAbおよび/RAbが、4つのサブアレイのうちの2つのサブアレイを選択するために用いられる。ロウアドレス信号ビットRAbがHレベルのときにはサブアレイMB♯0およびMB♯1またはサブアレイMB♯4およびMB♯5が指定され、ロウアドレス信号ビット/RAbがHレベルのときには、サブアレイMB♯2およびMB♯3またはサブアレイMB♯6およびMB♯7が指定される。8個のサブアレイMB♯0〜MB♯7のうち偶数番号のサブアレイが、ロウアドレス信号ビットRAcにより指定され、奇数番号のサブアレイは、ロウアドレス信号ビット/RAcにより指定される。サブアレイMB♯0〜MB♯7の各々は、自身に割当てられた3ビットのロウアドレス信号ビットがすべてHレベルのとき選択状態とされる。

Row address signal bits RAb and / RAb are used to select two of the four subarrays. When row address signal bit RAb is at H level,

図5は、図2に示すリフレッシュカウンタ、マルチプレクサおよびロウアドレスバッファの構成を概略的に示すである。図5においては、リフレッシュアドレスと外部から与えられるアドレスを切換えるためのマルチプレクサは、図面を簡略化するために示していない。単に、リフレッシュ動作時にリフレッシュカウンタ10からロウアドレスバッファ16およびアレイ制御回路12へ与えられるアドレス信号および生成されるロウアドレス信号ビットを示す。

FIG. 5 schematically shows configurations of the refresh counter, the multiplexer, and the row address buffer shown in FIG. In FIG. 5, a multiplexer for switching between a refresh address and an externally applied address is not shown in order to simplify the drawing. It simply shows an address signal supplied from the

図5において、リフレッシュカウンタ10は、リフレッシュされるメモリセルおよび行ブロックを指定するアドレス信号ビットRRAc〜RRAeを生成するリフレッシュセルカウンタ10aと、このリフレッシュセルカウンタ10aから出力されるアドレス信号ビットRRAcの立下がりをカウントするアレイカウンタ10bを含む。このリフレッシュセルカウンタ10aは、アドレス信号ビットRRAcを最上位ビットとし、アドレス信号ビットRRAeを最下位ビットとして出力する。このアドレス信号ビットRRAc〜RRAeにより、メモリマットM♯0〜M♯3それぞれにおいてリフレッシュされるべきメモリセルが指定される。

In FIG. 5, a

アレイカウンタ10bは、このロウアドレス信号ビットRRAcが立下がると、その出力されるアドレス信号ビットRAA0〜RAA1が示すカウント値を1増分(または減分)する。すなわち、アドレス信号ビットRRAcがHレベルからLレベルへ立下がると、1つのメモリマットにおいて、すべてのメモリセルがリフレッシュされたことを示す。 When the row address signal bit RRAc falls, the array counter 10b increments (or decrements) the count value indicated by the output address signal bits RAA0 to RAA1. That is, when address signal bit RRAc falls from the H level to the L level, it indicates that all the memory cells are refreshed in one memory mat.

ロウアドレスバッファ16は、このリフレッシュセルカウンタ10aから与えられたアドレス信号ビットRRAc〜RRAeをバッファ処理し、相補アドレス信号ビットRAa,/RAa〜RAe、/RAeを生成する。このロウアドレスバッファ16は、データ保持モード時においてはメモリマットM♯0〜M♯3それぞれにおいてサブアレイのグループを指定するアドレス信号ビットRAa,/RAa,RAbおよび/RAbを縮退状態とする。したがって、メモリマットM♯0〜M♯3それぞれにおいては、アドレス信号ビットRAc,/RAcに従って奇数番号のサブアレイまたは偶数番号のサブアレイが選択状態とされる。

アレイ制御回路12は、データ保持モード指示信号REFの活性化時に、このアレイカウンタ10bから出力されるアドレス信号ビットRAA0およびRAA1をデコードし、メモリマットM♯0〜M♯3をそれぞれ指定するマット指定信号MS0〜MS3の1つを選択状態とする。デコーダ12aは、データ保持モード指定信号REFの非活性化時には、このマット指定信号MS0〜MS3をすべて選択状態とする。これにより、データ保持モードにおいて、リフレッシュが行われる場合には、1つのメモリマットにおいて複数のサブアレイ(奇数番号のサブアレイまたは偶数番号のサブアレイ)がリフレッシュされ、通常動作モード時においてすべてのメモリマットにおいて所定数(1つ)のサブアレイが選択状態とされてデータのアクセスが行われる。

図6は、図5に示すロウアドレスバッファ16の、サブアレイグループを指定するためのアドレス信号ビットRAa,RAbおよび/RAa,/RAbを生成する部分の構成を示す図である。アドレス信号ビットRAa,/RAbおよびRAb,/RAbは、同じ構成のバッファ回路から出力されるため、図6においては、1つのバッファ回路部分のみを示す。

FIG. 6 is a diagram showing a configuration of a portion of

図6において、ロウアドレスバッファ16は、通常動作時にマルチプレクサを介して外部から与えられるアドレス信号ビットAa(Ab)を受けて反転するインバータ16aと、このアドレス信号ビットAaおよびインバータ16aの出力信号を受けてデータ保持モード時に縮退状態とするビット変更回路16bと、ビット変更回路16bの出力信号とアドレスバッファ活性化信号RADEを受けるNAND回路16cと、ビット変更回路16eの出力信号とアドレスバッファ活性化信号RADEを受けるNAND回路16dと、NAND回路16cの出力信号を受けるインバータ16eと、NAND回路16eの出力信号を受けるインバータ16fを含む。インバータ16eから内部ロウアドレス信号ビットRAa(RAb)が出力され、インバータ16fから内部ロウアドレス信号ビット/RAa(/RAb)が出力される。

In FIG. 6, a

ビット変更回路16bは、アドレス信号ビットAaとデータ保持モード指定信号REFを受けるOR回路16baと、インバータ16aの出力信号とデータ保持モード指定信号REFを受けるOR回路16bbとを含む。RO回路16baの出力信号がNAND回路16cの一方入力へ与えられ、OR回路16bbの出力信号がNAND回路16dの一方入力に与えられる。

Bit change circuit 16b includes an OR circuit 16ba receiving address signal bit Aa and data holding mode designating signal REF, and an OR circuit 16bb receiving an output signal of inverter 16a and data holding mode designating signal REF. The output signal of RO circuit 16ba is applied to one input of NAND circuit 16c, and the output signal of OR circuit 16bb is applied to one input of

通常動作モード時においては、データ保持モード指定信号REFはLレベルであり、OR回路16baおよび16bbは、バッファ回路として動作する。したがってビット変更回路16bからは、アドレス信号ビットAaから互いに相補なアドレス信号ビットAa(Ab)および/Aa(/Ab)が出力される。アドレスバッファ活性化信号RADEは、図7に示すように、リフレッシュ動作活性化時には、このリフレッシュ動作活性化信号ZRASの活性化に応答して、活性状態のHレベルとされる。このバッファ活性化信号RADEの活性化に応答して、NAND回路16cおよび16dがそれぞれインバータとして動作し、このビット変更回路16bから与えられた信号に従って内部ロウアドレス信号ビットRAa(RAb)および/RAa(/RAb)が生成される。したがって、データ保持モード時においては、ロウアドレス信号ビットRAa,/RAa、RAbおよび/RAbはすべてHレベルとされる。したがって、図4に示すように、メモリマットMAにおいて、サブアレイMB♯0〜MB♯7のうち、偶数番号のサブアレイまたは偶数番号のサブアレイが、内部ロウアドレス信号ビットRAc/RAcに従って選択状態とされる。

In the normal operation mode, data retention mode designating signal REF is at L level, and OR circuits 16ba and 16bb operate as buffer circuits. Therefore, the bit change circuit 16b outputs address signal bits Aa (Ab) and / Aa (/ Ab) which are complementary to each other from the address signal bit Aa. As shown in FIG. 7, address buffer activation signal RADE is set to an active H level in response to activation of refresh operation activation signal ZRAS when the refresh operation is activated. In response to activation of buffer activating signal RADE,

ロウアドレスバッファ16の下位のアドレス信号ビットRAc〜RAeに対する部分は、この図6に示すビット変更回路16bが削除された構成を備える。

The lower address signal bits RAc to RAe of the

なお、このリフレッシュ動作活性化信号ZRASは、リフレッシュ動作モード時において所定の時間幅を有して生成される。通常動作モード時においては、外部から与えられるロウアドレスストローブ信号/RASに応答して活性状態とされ、その活性期間は、外部ロウアドレスストローブ信号/RASにより決定される。 The refresh operation activation signal ZRAS is generated with a predetermined time width in the refresh operation mode. In the normal operation mode, the active state is activated in response to a row address strobe signal / RAS applied from the outside, and the active period is determined by external row address strobe signal / RAS.

なお、図6に示すロウアドレスバッファ16の構成において、データ保持モード動作時においては、マルチプレクサから与えられるアドレス信号ビットAa(Ab)の論理レベルはHレベルおよびLレベルいずれであってもよい。したがって、マルチプレクサは、データ保持モード動作時においては、アドレス信号ビットAaおよびAbに対する部分においては、出力ハイインピーダンス状態とされる構成が利用されればよいか、または特に設けられなくてもよい。

In the configuration of

図8は、図5に示すデコーダ12aの概略構成を示す図である。図8においては、メモリマットM♯0を選択状態とするデコーダ回路の部分が示される。デコーダ12aは、アレイカウンタ(図5参照)10bから出力されるアレイアドレス信号ビット/RAA0および/RAA1を受けるNAND回路12aaと、NAND回路12aaの出力信号とデータ保持モード指定信号REFを受けるNAND回路12abを含む。NAND回路12abから、メモリマットM♯0を指定するマット指定信号MS0が出力される。通常動作モード時においては、データ保持モード指定信号REFは、Lレベルであり、NAND回路12abから出力されるマット指定信号MS0はHレベルとされる。他のメモリマットを指定する回路部分においても同様の構成が設けられているため、したがってメモリマットM♯0〜M♯3がすべて通常動作モード時においては選択状態とされる。

FIG. 8 is a diagram showing a schematic configuration of the decoder 12a shown in FIG. FIG. 8 shows a portion of the decoder circuit that selects memory

データ保持モード動作時においては、データ保持モード指定信号REFが、活性状態のHレベルとされ、NAND回路12abがインバータとして作用する。NAND回路12aaは、アレイカウンタ10bの出力するビット/RAA0および/RAA1がともにHレベルのときにLレベルの信号を出力する。メモリマットM♯1〜M♯3それぞれにおいては、アレイカウンタの出力ビットRAA0,/RAA0,RAA1,/RAA1の所定の組合せの信号が与えられる。したがって、データ保持モード動作時においては、メモリマットM♯0〜M♯3を指定するメモリマット指定信号MS0〜MS3のうちの1つのメモリマット指定信号のみが選択状態とされる。これにより、1つのメモリマットに対してのみデータ保持動作すなわちリフレッシュ動作を行うことができる。

In the data holding mode operation, data holding mode designating signal REF is set to an active H level, and NAND circuit 12ab functions as an inverter. NAND circuit 12aa outputs a signal at L level when both bits / RAA0 and / RAA1 output from array counter 10b are at H level. In each of memory mats M # 1-

図9は、図2に示すロウデコーダRD0〜RD3の構成を概略的に示す図である。図9においては、メモリマットM♯i(i=0〜3)における一本のワード線WLに対するデコード回路の構成が概略的に示される。ロウデコーダRDiは、メモリマット指定信号MSiと、所定の組合せの内部ロウアドレス信号ビットRAc〜RAeを受けるNAND回路13aと、このNAND回路13aの出力信号に従ってワード線WLを選択状態(通常内部高電圧Vppレベル)へ駆動するワード線ドライブ回路13bを含む。 FIG. 9 schematically shows a configuration of row decoders RD0-RD3 shown in FIG. FIG. 9 schematically shows a configuration of a decoding circuit for one word line WL in memory mat M # i (i = 0 to 3). The row decoder RDi receives a memory mat designation signal MSi and a predetermined combination of internal row address signal bits RAc to RAe, and selects a word line WL according to an output signal of the NAND circuit 13a (normal internal high voltage The word line drive circuit 13b is driven to the (Vpp level).

NAND回路13aは、与えられた信号がすべてHレベルのときに選択状態を示すLレベルの信号を出力する。通常動作モード時においては、メモリマット指定信号MSiは、Hレベルである。一方、データ保持モード動作時においては、メモリマット指定信号MS0〜MS3のうち1つのメモリマット指定信号のみがHレベルの選択状態とされる。したがって、選択されたメモリマットにおいてのみロウデコーダがデコード動作を行うため、1つのメモリマットに対してのみリフレッシュ動作が行われる。 NAND circuit 13a outputs an L level signal indicating a selected state when all applied signals are at an H level. In the normal operation mode, memory mat designation signal MSi is at the H level. On the other hand, in the data holding mode operation, only one memory mat designation signal among memory mat designation signals MS0 to MS3 is set to the H level selected state. Therefore, since the row decoder performs the decoding operation only on the selected memory mat, the refresh operation is performed only on one memory mat.

なお、この図9に示す構成において、NAND回路13aは、機能的にロウデコーダの構成を示している。サブアレイを指定するアドレス信号ビットRAcがいわゆるブロックデコーダへ与えられ、各サブアレイにおいて、このブロックデコーダ(サブアレイを選択状態へ駆動するためのデコーダ)の出力信号に従ってサブアレイ対応に設けられたロウデコード回路が活性状態とされる構成が用いられてもよい。また、言うまでもなく、いわゆるプリデコーダの構成が用いられてもよい。 In the configuration shown in FIG. 9, the NAND circuit 13a functionally shows the configuration of a row decoder. Address signal bit RAc designating a subarray is applied to a so-called block decoder, and in each subarray, a row decode circuit provided corresponding to the subarray is activated according to an output signal of this block decoder (decoder for driving the subarray to a selected state). A configuration in a state may be used. Needless to say, a so-called predecoder configuration may be used.

[変更例]

図10は、この発明の実施の形態1に従うDRAMの変更例の構成を示す図である。図10(A)において、4つのメモリマットMM♯0〜MM♯3およびサブアレイMB♯0〜MB♯7に対するアドレス信号の配置が示される。この図10(A)に示す配置において、通常動作モード時においては、メモリマットMM♯0〜MM♯3は、コラムアドレス信号ビットCAa,/CAa,CAbおよび/CAbが割り当てられる。通常動作モード時においては、これらのコラムアドレス信号ビットCAa,/CAa,CAbおよび/CAbは縮退状態とされており、すべて選択状態とされる。メモリマットMM♯0〜MM♯3それぞれにおいて、サブアレイMB♯0〜MB♯7を選択するロウアドレス信号ビットRAa,/RAa,RAbおよび/RAbの割当は先の実施の形態(図4参照)と同じである。

[Example of change]

FIG. 10 shows a structure of a modification of the DRAM according to the first embodiment of the present invention. FIG. 10A shows the arrangement of address signals for four memory mats MM # 0-

データ保持モード時においては、1つのメモリマットを指定し、この選択状態とされるメモリマットにおいて複数のサブアレイが選択状態とされる。そこで、通常動作モード時において縮退状態とされるコラムアドレス信号ビットCAaおよびCAbと通常動作モード時において非縮退状態とされるロウアドレス信号ビットRAaおよびRAbを、データ保持モード時においては交換する。 In the data holding mode, one memory mat is designated, and a plurality of subarrays are selected in this selected memory mat. In view of this, column address signal bits CAa and CAb which are in a degenerated state in the normal operation mode and row address signal bits RAa and RAb in a non-degenerated state in the normal operation mode are exchanged in the data holding mode.

すなわち、図10(B)に示すように、データ保持モード時においては、コラムアドレス信号ビットCAaおよびCAbがロウアドレス信号ビットRAaおよびRAbにそれぞれ変換され、ロウアドレス信号ビットRAaおよびRAbがコラムアドレス信号ビットCAaおよびCAbに変換される。DRAMにおいて、縮退状態とされるコラムアドレス信号ビットCAaおよびCAbは、内部で(メモリセル選択動作時)選択状態とされる。したがって、コラムアドレス信号ビットをロウアドレス信号ビットとして用いても、内部動作においては、リフレッシュ動作活性化信号ZRASに従ってメモリセル選択動作が行われる。したがって、図10(A)において括弧で示すように、データ保持モード動作時においてはサブアレイMB♯0〜MB♯3のグループとサブアレイMB♯4〜MB♯7のグループのうちの一方のグループがコラムアドレス信号ビットCAa,/CAaにより選択され、各グループにおいて2つのサブアレイがコラムアドレス信号ビットCAb,/CAbにより選択される。コラムアドレス信号ビットCAa,/CAa,CAb,/CAbは、縮退状態とされているため、これらはすべて選択状態にある。したがって、データ保持モード時においては奇数番号のサブアレイまたは偶数番号のサブアレイがロウアドレス信号ビットRAc,/RAc(図4参照)に従って選択される。

That is, as shown in FIG. 10B, in the data holding mode, column address signal bits CAa and CAb are converted into row address signal bits RAa and RAb, respectively, and row address signal bits RAa and RAb are converted into column address signals. Converted to bits CAa and CAb. In DRAM, column address signal bits CAa and CAb which are in a degenerated state are internally selected (at the time of memory cell selection operation). Therefore, even if the column address signal bit is used as the row address signal bit, in the internal operation, the memory cell selection operation is performed according to the refresh operation activation signal ZRAS. Therefore, as shown in parentheses in FIG. 10A, in the data holding mode operation, one of the group of subarrays MB # 0-

また、データ保持モード動作時においては、ロウアドレス信号ビットRAa,/RAa,RAbおよび/RAbによりメモリマットが指定される。このロウアドレス信号ビットは、非縮退状態であるため、4つのメモリマットMM♯0〜MM♯3のうち1つのメモリマットが選択状態とされる。

In the data holding mode operation, the memory mat is designated by row address signal bits RAa, / RAa, RAb and / RAb. Since this row address signal bit is in a non-degenerate state, one of the four memory

図11は、図10に示すアドレス変換を行う部分の構成を概略的に示す図である。図11においても、外部からのアドレス信号と内部で発生されるリフレッシュアドレスとを切換えるためのマルチプレクサは図面を簡略化するために示していない。図11において、アドレス変換部は、データ保持モード時、リフレッシュカウンタ10から与えられるリフレッシュアドレスRRAa,RRAb,RRAc〜RRAeを受けて内部ロウアドレス信号ビットを生成するロウアドレスバッファ16と、このロウアドレスバッファ16からのロウアドレス信号ビットRAa,/RAa,RAb,/RAbと図示しないコラムアドレスバッファから与えられる縮退状態とされたコラムアドレス信号ビットCAa′,CAb′とを受け、データ保持モード指示信号REFの活性化時コラムアドレス信号ビットCAa′,CAb′とロウアドレスバッファ16からのロウアドレス信号ビットとを交換するスクランブラ19を含む。ロウアドレスバッファ16は、内部ロウアドレス信号ビットRAc,/RAc〜RAe,/RAeを生成して各メモリマットに設けられたロウデコーダへ与える。スクランブラ19は、データ保持モード指示信号REFの活性化時、コラムアドレス信号ビットCAa′,CAb′を内部ロウアドレス信号ビットRAa,RAbとして出力し、かつロウアドレスバッファ16からのロウアドレス信号ビットをコラムアドレス信号ビットCAa,CAbとして出力する。データ保持モード指示信号REFの非活性化時、スクランブラ19は、ビット交換を行わず、与えられたアドレス信号ビットを出力する。

FIG. 11 is a diagram schematically showing a configuration of a portion that performs address conversion shown in FIG. Also in FIG. 11, a multiplexer for switching between an external address signal and an internally generated refresh address is not shown in order to simplify the drawing. In FIG. 11, in the data holding mode, the address conversion unit receives a refresh address RRAa, RRAb, RRAc to RRAe supplied from the

この図11に示す構成の場合、リフレッシュカウンタ10において、その最小カウント値から最大カウント値までカウント値が変化すると、すべてのメモリマットにおいてすべてのメモリセルが一度リフレッシュされたことを示す。したがって、単にスクランブラ19において常時縮退状態とされるコラムアドレス信号ビットCAa′およびCAb′とロウアドレスバッファ16から出力されるロウアドレス信号ビットRAa′およびRAb′をスクランブルするだけであり、簡易な回路構成で容易にデータ保持モードのときに1つのメモリマットにおいて複数のサブアレイを選択状態とすることができる。

In the configuration shown in FIG. 11, when the count value changes from the minimum count value to the maximum count value in the

図12は、図11に示すスクランブラの1ビットのアドレス信号に対する部分を示す図である。この図12に示す構成が必要とされるビットの数だけ設けられる。図12において、スクランブラ19は、データ保持モード指示信号REFの活性化時導通し、コラムアドレス信号ビットCAa′を内部コラムアドレス信号ビットCAaとして出力する双方向トランスミッションゲートXF1と、データ保持モード指示信号REFの活性化時導通し、コラムアドレス信号ビットCAa′をロウアドレス信号ビットRAaとして出力する双方向トランスミッションゲートXF2と、データ保持モード指示信号REFの活性化時導通し、ロウアドレス信号ビットRAa′を内部コラムアドレス信号ビットCAaとして出力する双方向トランスミッションゲートXF3と、データ保持モード指示信号REFの非活性化時に導通し、ロウアドレス信号ビットRAa′を内部ロウアドレス信号ビットRAaとして出力する双方向トランスミッションゲートXF4を含む。この双方向トランスミッションゲートXF1〜XF4の各々は、CMOSトランジスタで構成され、このCMOSトランジスタの導通を制御するために、データ保持モード指示信号REFを反転するインバータIVが設けられる。このデータ保持モード指示信号REFおよびインバータIVの出力する反転データ保持モード指示信号によりこれらのトランスミッションゲートXF1〜XF4の導通/非導通が実現される。

FIG. 12 is a diagram showing a portion of the scrambler shown in FIG. 11 for a 1-bit address signal. The number of bits required for the configuration shown in FIG. 12 is provided. In FIG. 12,

この図12に示す構成においては、トランスミッションゲートXF1〜XF4により、コラムアドレス信号ビットCAa′およびロウアドレス信号ビットRAa′の伝搬経路が切換えられているだけである。通常動作モード時においては、アドレス信号ビットCAa′およびRAa′は、それぞれ内部アドレス信号ビットCAaおよびRAaとして出力され、データ保持モード動作時においては、アドレス信号ビットCAa′およびRAa′は、それぞれアドレス信号ビットRAaおよびCAaとして出力される。コラムアドレス信号ビットCAa′は縮退状態であり、常時選択状態にある。したがって単にこの伝搬経路を切換えるだけで、容易にデータ保持モード時において縮退状態とされるアドレス信号ビットを得ることができる。 In the configuration shown in FIG. 12, the transmission paths of column address signal bit CAa 'and row address signal bit RAa' are only switched by transmission gates XF1-XF4. In the normal operation mode, address signal bits CAa 'and RAa' are output as internal address signal bits CAa and RAa, respectively, and in the data holding mode operation, address signal bits CAa 'and RAa' are respectively address signals. Output as bits RAa and CAa. Column address signal bit CAa 'is in a degenerated state and is always in a selected state. Therefore, it is possible to easily obtain an address signal bit that is in a degenerated state in the data holding mode simply by switching the propagation path.

なお、図12に示す構成において、アドレス信号ビットCAaおよびRAaが伝達される部分は示していない。内部コラムアドレス信号ビットCAaは、メモリマットを選択状態とするためのマットデコーダ部分へ与えられ、内部ロウアドレス信号ビットRAaは、メモリマットそれぞれに対するロウデコーダ(RD0〜RD3)へ与えられる。 In the configuration shown in FIG. 12, the portion to which address signal bits CAa and RAa are transmitted is not shown. Internal column address signal bit CAa is applied to a mat decoder portion for selecting a memory mat, and internal row address signal bit RAa is applied to a row decoder (RD0 to RD3) for each memory mat.

なお、このスクランブラ19を用いる構成の場合、DRAMの構成に応じて、縮退されるアドレス信号ビットの数が異なる場合(たとえば×8ビット構成の場合3ビットのアドレスが縮退される)、通常動作モード時において縮退状態とされるアドレス信号ビットをデータ保持モード時において縮退状態とすべきアドレス信号ビットと交換するように構成すれば、常にデータ保持モード時において1つのメモリマットを選択状態としてリフレッシュ動作を行うことができる。

In the configuration using this

上述のように、データ保持モード時において、メモリマットおよびサブアレイを指定する信号を選択的に縮退状態とすることにより、データ保持モード時において、1つのメモリマットにおいて所定数のサブアレイで構成されるグループのみに対しリフレッシュ動作を行うことができる。他のメモリマットにおいては、周辺回路は動作していない。したがって、他の周辺回路を駆動するための回路および他の周辺回路の動作が停止されるため、消費電流が低減される。 As described above, by selectively degenerating signals specifying the memory mat and the sub-array in the data holding mode, a group composed of a predetermined number of sub-arrays in one memory mat in the data holding mode. Only the refresh operation can be performed. In other memory mats, peripheral circuits are not operating. Therefore, a circuit for driving other peripheral circuits and the operation of the other peripheral circuits are stopped, so that current consumption is reduced.

図13(A)は、センスアンプ駆動部の構成を概略的に示す図である。図13(A)においては、1つのサブアレイの1対のビット線に対して設けられたセンスアンプを代表的に示す。このセンスアンプは、メモリセルの各列に対応して配置され、活性化時、対応のメモリセル列(ビット線対)に読出されたメモリセルのデータの検知および増幅を行う。 FIG. 13A schematically shows a configuration of a sense amplifier driving unit. FIG. 13A representatively shows sense amplifiers provided for a pair of bit lines in one subarray. The sense amplifier is arranged corresponding to each column of memory cells, and when activated, senses and amplifies data of the memory cell read to the corresponding memory cell column (bit line pair).

図13(A)において、1対のビット線BL,/BLに対し、センスアンプ20が設けられる。ビット線対BLおよび/BLには、1列のメモリセルが接続される。図13(A)においては、ワード線WLとビット線BLとの交差部に対応して設けられるメモリセルMCを代表的に示す。また、ワード線WLには、1行のメモリセルが接続される。

In FIG. 13A, a

センス駆動部は、リフレッシュ動作活性化信号ZRASと行ブロック指定アドレス信号ビットRAa,RAbおよびRAcに従って所定のタイミングでセンスアンプ活性化信号SOPおよびSONを活性状態とするセンス活性化回路24と、センス活性化回路24からのセンスアンプ活性化信号SOPに応答して導通して、センスアンプ駆動信号SAPを接地電位Vssレベルの活性状態とするnチャネルMOSトランジスタで構成される活性化トランジスタ27aと、センス活性化回路24からのセンスアンプ活性化信号SONに応答して導通し、電源電位Vintレベルの活性状態へセンス駆動信号SANを駆動するpチャネルMOSトランジスタで構成されるセンス活性化トランジスタ28aと、センスアンプ駆動信号SAPに応答して導通し、センスアンプ20の一方ノードへ電源電位Vintを伝達するpチャネルMOSトランジスタで構成されるセンスアンプ駆動トランジスタ22aと、センスアンプ駆動信号SANに応答して導通し、センスアンプ20の他方ノードへ接地電位Vssを伝達するnチャネルMOSトランジスタで構成されるセンス駆動トランジスタ22bを含む。

The sense driver includes a

センスアンプ20は、通常の交差結合されたpチャネルMOSトランジスタおよび交差結合されたnチャネルMOSトランジスタを含む。このpチャネルMOSトランジスタ部分へ、センスアンプ駆動トランジスタ22aを介して電源電位Vintが伝達され、nチャネルMOSトランジスタ部分へ、センスアンプ駆動トランジスタ22bを介して接地電位Vssが伝達される。

センス駆動部は、さらに、センス活性化回路24からのセンスアンプ活性化信号SOPと反転データ保持モード指定信号/REFを受けるAND回路26aと、AND回路26aの出力信号に応答して導通し、センスアンプ駆動信号SAPを接地電位Vssレベルへ駆動するnチャネルMOSトランジスタで構成される補助駆動トランジスタ27bと、センスアンプ活性化信号SONとデータ保持モード指定信号REFを受けるOR回路26bと、OR回路26bの出力信号に応答して選択的に導通して、センスアンプ駆動信号SANを電源電位Vintレベルへ駆動するpチャネルMOSトランジスタで構成される補助駆動トランジスタ28bを含む。

The sense driver further conducts in response to an AND circuit 26a receiving the sense amplifier activation signal SOP and the inverted data holding mode designating signal / REF from the

トランジスタ27aの電流駆動力は、トランジスタ27bの電流駆動力よりも好ましくは、小さくされる。また、駆動トランジスタ28bの電流駆動力は、補助駆動トランジスタ28bのそれよりも好ましくは小さくされる。次に、この図13(A)に示すセンスアンプ駆動部の動作をその動作波形図である図13(B)を参照して説明する。

The current driving capability of the transistor 27a is preferably smaller than the current driving capability of the transistor 27b. The current driving capability of the driving

データ保持モードにおいては、データ保持モード指定信号REFはHレベルであり、また反転データ保持モード指定信号/REFがLレベルである。この状態においては、AND回路26aの出力信号がLレベルに固定され、また、OR回路26bの出力信号はHレベルに固定され、したがって、補助駆動トランジスタ27bおよび28bは、ともに、非道通状態に保持される。

In the data holding mode, data holding mode designating signal REF is at the H level, and inverted data holding mode designating signal / REF is at the L level. In this state, the output signal of AND circuit 26a is fixed at the L level, and the output signal of OR circuit 26b is fixed at the H level, so that

スタンバイ状態時(リフレッシュ動作活性化信号ZRSのHレベルおよび通常動作時における内部RAS信号の非活性状態)においては、センス活性化回路24からのセンスアンプ活性化信号SOPおよびSONは、それぞれLレベルおよびHレベルである。したがって、センス駆動トランジスタ27aおよび28aは非道通状態になる。

In the standby state (the H level of refresh operation activation signal ZRS and the inactive state of internal RAS signal during normal operation), sense amplifier activation signals SOP and SON from

リフレッシュ動作時においては、まず、リフレッシュ動作活性化信号ZRASがLレベルとされる。サブアレイ指定信号ビットRAa,RAbおよびRAcがすべて選択状態とされると、センス活性化回路24が、所定のタイミングでセンスアンプ活性化信号SONをLレベルへ駆動し、またセンスアンプ活性化信号SOPをHレベルへ駆動する。これにより、駆動トランジスタ27aおよび28aは、それぞれ導通状態とされ、センスアンプ駆動信号SANおよびSAPが活性状態のHレベルおよびLレベルとされる。このセンス駆動トランジスタ27aおよび28aは、比較的その電流駆動力は小さくされており、図13(B)に破線で示すように、センスアンプ駆動信号SANおよびSAPは比較的緩やかに電位が変化する。このセンスアンプ活性化信号SANおよびSAPに応答して、センスアンプ活性化トランジスタ22aおよび22bが導通し、センスアンプ20へ、それぞれ電源電位Vintおよび接地電位Vssが伝達されてセンスアンプ20が活性化され、ビット線BLおよび/BL上に現れたメモリセルデータの検知および増幅を行う。センスアンプ駆動信号SAPおよびSANの電位変化が緩やかであるため、このセンスアンプ活性化トランジスタ22aおよび22bのコンダクタンスの変化は比較的緩やかであり、応じてセンスアンプ20の動作速度も遅くされる(センスアンプ20は、その活性化トランジスタ22aおよび22bを介してビット線BLおよび/BLの充放電を行うため)。

In the refresh operation, first, the refresh operation activation signal ZRAS is set to L level. When subarray designating signal bits RAa, RAb and RAc are all selected,

したがって、図13(B)において、破線の波形で示すように、ビット線BLおよび/BLの電位は、緩やかに変化する。 Accordingly, in FIG. 13B, the potentials of the bit lines BL and / BL change gently as indicated by the broken line waveform.

このビット線BLおよび/BLの充放電を緩やかに行うことにより、センスアンプ20の動作時における充放電電流のピーク電流を低減することができ、電源線のノイズ(電源電位Vintの低下および接地電位Vssの上昇)は防止され、1つのメモリマットにおいて複数のサブアレイにおいてセンス動作が行われる場合においても、安定にセンス動作を行うことができる。このリフレッシュ動作時においては、高速動作性は何ら要求されないため(データの外部入出力は行われないため)、何ら問題は生じない。

By gently charging / discharging the bit lines BL and / BL, the peak current of the charge / discharge current during the operation of the

通常動作モード時においてはデータ保持モード指定信号REFはLレベルであり、AND回路26aおよびOR回路26bは、それぞれバッファ回路として動作する。したがって、この通常動作モード時においては、リフレッシュ動作活性化信号ZRASに対応する内部RAS信号(外部から与えられるロウアドレスストローブ信号/RASに追随する)の活性化に応答して、アドレス信号ビットRAa,RAbおよびRAcにより選択状態とされたセンス活性化回路24が活性状態とされて、センスアンプ活性化信号SOPおよびSONをそれぞれ所定のタイミングでHレベルおよびLレベルの活性状態とする。

In the normal operation mode, data holding mode designating signal REF is at L level, and AND circuit 26a and OR circuit 26b each operate as a buffer circuit. Therefore, in this normal operation mode, in response to activation of an internal RAS signal (following row address strobe signal / RAS applied from the outside) corresponding to refresh operation activation signal ZRAS, address signal bits RAa,

このセンスアンプ活性化信号SOPおよびSONの活性化に応答して、駆動トランジスタ27aおよび27bならびに駆動トランジスタ28aおよび28bが導通し、高速でセンスアンプ駆動信号SAPおよびSANを活性状態のLレベルおよびHレベルとする。これにより、センスアンプ活性化トランジスタ22aおよび22bが高速で導通し、センスアンプ20が、このセンスアンプ活性化トランジスタ22aおよび22bを介してビット線BLおよび/BLを充放電する。これにより、図13(B)において実線で示すように、ビット線BL,/BLの電位が高速で変化する。

In response to activation of sense amplifier activation signals SOP and SON, drive transistors 27a and 27b and drive

なお、図13(A)に示す構成においては、センス活性化回路24aは、リフレッシュ動作活性化信号ZRASおよびサブアレイ指定アドレス信号ビットRAa,RAbおよびRAcを受けてセンスアンプ活性化信号SOPおよびSONを活性状態へ駆動している。センス活性化回路24の構成は、任意であり、このセンス活性化回路24がサブアレイそれぞれに対応して設けられてもよく、リフレッシュ動作活性化信号ZRASに応答してセンスアンプ活性化信号が各メモリマットのセンス活性化回路へ伝達され、サブアレイ対応のセンス活性化回路がサブアレイ指定信号に従って対応のセンスアンプ活性化信号を活性状態とする構成が用いられてもよい。

In the configuration shown in FIG. 13A, sense activation circuit 24a activates sense amplifier activation signals SOP and SON in response to refresh operation activation signal ZRAS and subarray designation address signal bits RAa, RAb and RAc. Driving to the state. The configuration of

なお、図13(B)においては、ビット線BL上にHレベルのデータが読出された場合のビット線BLおよび/BLの電位変化が示されるが、Lレベルのメモリセルデータが読出された場合においても同様の効果が得られる。センスアンプ24は、ビット線BLおよび/BLの高電位のビット線の電位を電源電位Vintレベルへ駆動し、低電位のビット線の電位を接地電位Vssレベルへ駆動する。

In FIG. 13B, the potential change of bit lines BL and / BL when H level data is read on bit line BL is shown, but when L level memory cell data is read. The same effect can be obtained in.

図14は、データ保持モード時と通常動作モード時における内部RAS信号を切換える部分の構成を示す図である。リフレッシュ制御回路6は、リフレッシュ要求信号(タイマから与えられる)φrefに応答して、所定の時間幅を有するリフレッシュ動作活性化信号ZRASを発生するZRAS発生回路6aを含む。通常動作モード時においては、RASバッファ30が、外部から与えられるロウアドレスストローブ信号ext./RASをバッファ処理して、内部ロウアドレスストローブ信号/RASを生成する。この通常動作モード時とリフレッシュ動作モード時における駆動信号の経路を切換えるために、RASバッファ30から与えられる内部ロウアドレスストローブ信号とデータ保持モード指定信号REFを受けるORゲート32と、ZRAS発生回路6aから与えられるリフレッシュ動作活性化信号ZRASとOR回路32の出力信号を受けるAND回路34とが設けられる。このAND回路34から、DRAM内部に設けられたRAS系回路(信号RASに従って駆動される回路であり、ロウデコーダ、ロウアドレスバッファ、およびセンスアンプ駆動回路の部分を含む)へ与えられる内部RAS信号φRASZが生成される。

FIG. 14 is a diagram showing a configuration of a portion for switching the internal RAS signal in the data holding mode and the normal operation mode.

データ保持モード動作時においては、データ保持モード指定信号REFがHレベルであり、OR回路32の出力信号はHレベルに固定される。この状態においては、RASバッファ30の出力する内部ロウアドレスストローブ信号/RASの状態が無視される。AND回路34が、したがって、ZRAS発生回路6aから与えられるリフレッシュ動作活性化信号ZRASに従って内部RAS信号φRASZをLレベルの活性状態とする。

During the data holding mode operation, data holding mode designating signal REF is at H level, and the output signal of

通常動作モード時においては、リフレッシュ制御回路6に含まれるZRAS発生回路6aからのリフレッシュ動作活性化信号ZRASはHレベルに固定される。また、データ保持モード指定信号REFは、Lレベルに固定される。したがって、OR回路32およびAND回路34がそれぞれバッファとして動作し、RASバッファ30から与えられる内部ロウアドレスストローブ信号/RASに従って、内部RAS信号φRASZが出力される。これにより、通常動作モード時およびリフレッシュ動作モード時いずれにおいても、この内部RAS信号φRASZに従って、DRAMの内部回路が動作する。

In the normal operation mode, refresh operation activation signal ZRAS from ZRAS generation circuit 6a included in

以上のように、この発明の実施の形態1に従えば、通常動作モード時とデータ保持モード動作時において、選択状態とされるメモリマットの数を変更可能としているため、このデータ保持モード動作時において、必要に応じて動作状態とされるメモリマットの数を調整して、消費電流を低減することができる。また、データ保持モード動作時において、1つのメモリマットにおいてのみ複数のサブアレイを選択状態としてリフレッシュ動作を行うことにより、1つのメモリマットに対してのみ活性化信号を伝達するだけでよく、他のメモリマットにおいては、すべて活性化信号が非選択状態に維持されるため、これらの他のメモリマットの周辺回路における消費電流が低減され、応じてデータ保持モード時における消費電流が低減される。 As described above, according to the first embodiment of the present invention, the number of memory mats to be selected can be changed in the normal operation mode and the data holding mode operation. In this case, current consumption can be reduced by adjusting the number of memory mats to be operated as necessary. Further, during the data holding mode operation, it is only necessary to transmit an activation signal to only one memory mat by performing a refresh operation with a plurality of sub-arrays selected in only one memory mat. Since all activation signals are maintained in the non-selected state in the mats, the current consumption in the peripheral circuits of these other memory mats is reduced, and accordingly the current consumption in the data holding mode is reduced.

また、リフレッシュ動作モードにおいて、センス動作を緩やかに行うことにより、このピーク電流を低減することができ、これにより1つのメモリマットの複数のサブアレイにおいて同時にリフレッシュ動作を正確に行うことができる。 Further, in the refresh operation mode, the peak current can be reduced by performing the sensing operation gently, and thereby the refresh operation can be accurately performed simultaneously in a plurality of subarrays of one memory mat.

[実施の形態2]

図15は、この発明の実施の形態2に従うDRAMのアレイの配置を概略的に示す図である。図15(A)においては、通常動作モード時における選択メモリサブアレイの配置を示し、図15(B)に、データ保持モード動作時において、リフレッシュのために選択状態とされるサブアレイの配置を示す。図15(A)および(B)に示すように、DRAM1は、4つのメモリマットMM♯0〜MM♯3を含む。メモリマットMM♯0〜MM♯3それぞれに対応して、内部降圧回路VDC0〜VDC3が設けられる。この内部降圧回路VDC0〜VDC3のそれぞれの内部構成は、後に説明するが、外部から与えられる電源電位を変換して、内部電源電位を生成して、対応のメモリマットMM♯0〜MM♯3へ供給する。メモリマットMM♯0〜MM♯3の各々は、対応の内部降圧回路VDC0〜VDC3から電源電位を供給されて動作する。このメモリマットは、周辺回路としてのロウデコーダおよびコラムデコーダ、センスアンプ活性化回路などを含み、またメモリアレイ内に対しては、センスアンプを活性化するための電源電位Vint(図13(A)参照))などが供給される。

[Embodiment 2]

FIG. 15 schematically shows an arrangement of an array of DRAMs according to the second embodiment of the present invention. FIG. 15A shows the arrangement of the selected memory sub-array in the normal operation mode, and FIG. 15B shows the arrangement of the sub-array selected for refresh in the data holding mode operation. As shown in FIGS. 15A and 15B,

図15(A)に示すように、通常動作モード時においては、メモリマットMM♯0〜MM♯3それぞれにおいて1つのサブアレイ(サブアレイMB♯0を例示的に示す)が選択状態とされて、選択されたサブアレイMB♯0内の選択されたメモリセルに対するアクセスが行われる。メモリマットMM♯0〜MM♯3それぞれに対応して内部降圧回路を配置し、内部降圧回路VDC0〜VDC3それぞれが、対応のメモリマットMM♯0〜MM♯3へのみ電源電位を供給する構成とすることにより、電源ノイズを低減することができる。

As shown in FIG. 15A, in the normal operation mode, one sub-array (

すなわち、1つの内部降圧回路を用いてメモリマットMM♯0〜MM♯3全てへ電源電位を供給した場合、以下のような問題が生じる。すべてのメモリマットMM♯0〜MM♯3に共通に設けられた内部降圧回路を用いてメモリマットMM♯0〜MM♯3へ内部電源電位Vintを供給した場合、メモリマットMM♯0〜MM♯3の動作時に、すべてのメモリマットMM♯0〜MM♯3の消費電流が共通の内部降圧回路を介して供給されることになり、この内部電源電位の低下ならびにこれを補償するために供給される大きな電流による内部電源電位の上昇およびリンギングが生じ、内部電源電位が不安定となる。一方、メモリマットMM♯0〜MM♯3それぞれに対し、内部降圧回路VDC0〜VDC3を配置することにより、内部降圧回路VDC0〜VDC3それぞれは、対応のメモリマットMM♯0〜MM♯3へ内部電源電位Vintを供給することが要求されるだけである。したがって、内部降圧回路VDC0〜VDC3が補償すべき消費電流は、1つのメモリマットの消費電流だけであり、応じて消費電流が分散されるため、メモリマットMM♯0〜MM♯3動作時における電源ノイズを低減することができ、応じて内部電源電位が少し低下した場合においても、安定に内部電源電位を供給することができるためメモリマットMM♯0〜MM♯3はそれぞれ、大きな動作マージン(内部電源電位に対する)を持って安定に動作することができる。

That is, when the power supply potential is supplied to all the memory

この実施の形態2においては、さらに、データ保持モード動作時においてリフレッシュする場合に、実施の形態1に従って1つのメモリマット(図15(B)においては、メモリマットMM♯0を例示的に示す)においてのみリフレッシュ動作が実行される。非選択状態のメモリマット(MM♯1〜MM♯3)に対して設けられた内部降圧回路(VDC0〜VDC3)は、内部電源電圧Vintの供給を停止する。これにより、非選択状態のメモリマットに対する消費電流がなくなるため、データ保持モード動作時における消費電流は大幅に低減される。この選択状態とされたメモリマット(MM♯0)においては、センスアンプなどの周辺回路の動作を緩やかとすることによりピーク電流を低減することができ、1つの内部降圧回路(VDC0)を用いて複数のサブアレイに対し安定に内部電源電位を供給することができる(電流消費が小さいため、その電源電位の低下速度は遅く、1つの内部降圧回路により、十分に消費電流を補償することができるため)。

In the second embodiment, one memory mat (memory

図16(A)は内部降圧回路の構成の一例を示す図である。図16(A)において、内部降圧回路VDCは、基準電位Vrefと内部電源電位Vintとを比較する比較器40と、メモリマット指定信号MSiに応答して比較器40を選択的に活性状態とするための活性化トランジスタ42と、比較器40の出力信号に応答して外部電源電位供給ノードVextから電流を内部電源線41上に供給するpチャネルMOSトランジスタで構成されるドライブトランジスタ44を含む。このトランジスタ42は、メモリマット指定信号MSiの活性状態のとき導通し、比較器40の電流経路を形成する。メモリマット指定信号MSiの非活性化時には、活性化トランジスタ42が非導通状態とされ、比較器40を非活性状態とする。このトランジスタ42は、したがって、比較器40の電流源トランジスタとして作用する。

FIG. 16A shows an example of the structure of the internal voltage down converter. 16A, internal voltage down converter VDC selectively activates

比較器40は、動作時、基準電位Vrefが内部電源電位Vintよりも高い場合には、Lレベルの信号を出力し、ドライブトランジスタ44のコンタクタンスを大きくする。これにより、ドライブトランジスタ44が外部電源電位供給ノードVextから内部電源線41上へ電流を供給し、内部電源電位Vintの電位を上昇させる。一方、内部電源電位Vintが基準電位Vrefよりも高い場合には、比較器40は、Hレベルの信号を出力して、このドライブトランジスタ44をオフ状態とする。これにより、ドライブトランジスタ44を介しての電流の供給が停止される。したがって、この内部電源電位Vintは、基準電位Vrefの電位レベルに保持される。

During operation, the

図16(B)に示すように、この内部降圧回路VDCは、1つのメモリマットに対してのみ外部電源電位Vintを供給する。したがってこの消費電流iは比較的小さく、対応のメモリマットが選択状態にされ、動作する場合においても、そのピーク電流は小さく、内部電源電位Vintの低下も小さく、内部電源電位Vintは所定の電位レベルVrefに保持される。 As shown in FIG. 16B, this internal voltage down converter VDC supplies external power supply potential Vint to only one memory mat. Therefore, current consumption i is relatively small, and even when the corresponding memory mat is selected and operated, the peak current is small, the decrease in internal power supply potential Vint is small, and internal power supply potential Vint is at a predetermined potential level. Held at Vref.

データ保持モード動作時においては、通常動作モード時よりも、多くのサブアレイが駆動される。しかしながら、このサブアレイを駆動する回路の動作速度は遅いため、その消費電流iの変化速度は小さく、ピーク電流は通常動作モード時のそれと同じ程度とされる。それにより、データ保持モードにおいて数多くのサブアレイが1つのメモリマットにおいて同時に駆動されても、内部電源電位Vintは所定電位レベルに保持される。 In the data holding mode operation, more subarrays are driven than in the normal operation mode. However, since the operation speed of the circuit for driving the subarray is low, the change speed of the consumption current i is small, and the peak current is the same as that in the normal operation mode. Thus, even when a large number of subarrays are driven simultaneously in one memory mat in the data holding mode, internal power supply potential Vint is held at a predetermined potential level.

データ保持モード動作時においては、選択メモリマットに対してのみこのメモリマット指定信号MSiがHレベルとされる。したがって、非選択メモリマットに対しては、比較器40が、非活性状態とされてその出力信号はHレベルとされ、ドライブトランジスタ44はオフ状態を維持する。非選択メモリマットはスタンバイ状態を維持するため、その消費電流はリーク電流だけであり、たとえ対応の内部降圧回路から電流が供給されない場合においても、内部電源電位はほぼ一定の電位レベルを保持することができる。

In the data holding mode operation, this memory mat designation signal MSi is set to the H level only for the selected memory mat. Therefore, for the non-selected memory mat,

図17は、選択メモリマットにおける回路動作を遅くするための構成を示す図である。図17において、1つのメモリマットMM♯の周辺回路(ロウデコーダ、コラムデコーダ、センスアンプ活性回路等)と内部電源線41との間に、電流源として機能するpチャネルMOSトランジスタ46aと、データ保持モード時に、データ保持モード指定信号REFに応答して非導通状態とされるpチャネルMOSトランジスタ46bとが設けられる。pチャネルMOSトランジスタ46aは、そのゲートが接地電位Vssを受け、常時導通状態を維持し、電流源として機能する。

FIG. 17 is a diagram showing a configuration for slowing down the circuit operation in the selected memory mat. In FIG. 17, a p-channel MOS transistor 46a functioning as a current source is provided between a peripheral circuit (row decoder, column decoder, sense amplifier activation circuit, etc.) of one memory mat MM # and an internal

通常動作モード時においては、MOSトランジスタ46aおよび46bは、ともに導通状態にあり、周辺回路48は、内部電源線41上の電源電位Vintを受ける。周辺回路48の動作時においては、MOSトランジスタ46aおよび46bを介して大きな電流駆動力を持って電流が供給され、周辺回路48は、高速で安定に動作する。

In the normal operation mode,

データ保持モード動作時においては、データ保持モード指定信号REFがHレベルであり、MOSトランジスタ46bが非導通状態とされる。したがって、データ保持モード時においては、周辺回路48は、電流源として機能するMOSトランジスタ46aを介してのみ内部電源線41から電流を供給される。したがって、この周辺回路48の電流駆動力は、MOSトランジスタ46aにより決定され、通常動作時よりもその電流駆動力は小さくされ、周辺回路48の動作速度が遅くされる。これにより、データ保持モード時におけるピーク電流を抑制することができる。

In the data holding mode operation, data holding mode designating signal REF is at H level, and

なお、図17に示す構成において、データ保持モード指定信号REFに変えて、データ保持モード指定信号REFとメモリマット指定信号MSiの論理積信号REF・MSiが用いられてもよい。非選択メモリマットにおいては、データ保持モード時においては、MOSトランジスタ46bが導通状態とされるが、対応の内部降圧回路が非活性状態であり、また、対応のメモリマットも非選択状態であり電流は消費されないため、特に問題はない。

In the configuration shown in FIG. 17, instead of the data holding mode designation signal REF, a logical product signal REF · MSi of the data holding mode designation signal REF and the memory mat designation signal MSi may be used. In the non-selected memory mat,

また、回路動作を遅くする構成は、図13(A)のセンス動作を遅くする構成が用いられてもよい。 Further, as the configuration for delaying the circuit operation, the configuration for delaying the sensing operation in FIG. 13A may be used.

以上のように、この発明の実施の形態2に従えば、複数のメモリマットそれぞれに対応して設けられた内部降圧回路を、データ保持モード時においては、選択メモリマットに対する内部降圧回路のみを活性状態とするように構成したため、データ保持モード時における消費電流を大幅に低減することができる。また、このときデータ保持モード時において回路動作を遅くすることにより、ピーク電流を低減することができ、選択メモリマットにおける選択サブアレイの数が増加しても、ピーク電流を増加させることなく、安定にリフレッシュ動作を行うことができる。 As described above, according to the second embodiment of the present invention, the internal voltage down converter provided corresponding to each of the plurality of memory mats is activated only in the data holding mode. Since it is configured to be in the state, current consumption in the data holding mode can be greatly reduced. At this time, the peak current can be reduced by delaying the circuit operation in the data holding mode, and even if the number of selected sub-arrays in the selected memory mat is increased, the peak current can be stably increased. A refresh operation can be performed.

[実施の形態3]

DRAMにおいては、セルフリフレッシュモードを含むデータ保持モードに加えて、さまざまな動作モードが設けられている。たとえば、DRAMのテストモードを設定する場合には、WCBRタイミングが用いられ、テストモードのリセットにはCBRタイミングが用いられる。WCBRタイミングは、外部ロウアドレスストローブ信号ext./RASの立下がり前に、外部ライトイネーブル信号ext./WEおよび外部コラムアドレスストローブ信号ext./CASをLレベルに立下げる。CBRタイミングにおいては、外部ロウアドレスストローブ信号ext./RASの立下がり前に、外部コラムアドレスストローブ信号ext./CASをLレベルに立下げる。そのとき、外部ライトイネーブル信号ext./WEは、通常、Hレベルとされる。各動作モードを設定する部分の構成を図18に示す。

[Embodiment 3]

In the DRAM, various operation modes are provided in addition to the data holding mode including the self-refresh mode. For example, when setting the test mode of the DRAM, the WCBR timing is used, and the CBR timing is used for resetting the test mode. The WCBR timing is determined by the external row address strobe signal ext. / RAS before the fall of the external write enable signal ext. / WE and external column address strobe signal ext. / CAS falls to L level. At the CBR timing, the external row address strobe signal ext. / RAS falls before external column address strobe signal ext. / CAS falls to L level. At that time, the external write enable signal ext. / WE is normally set to the H level. FIG. 18 shows a configuration of a part for setting each operation mode.

図18においては、テストモードセット回路54およびテストモードリセット回路52が一例として示される。テストモードセット回路54は、WCBRタイミングを検出するWCBR検出器54aを含み、テストモードリセット回路52は、CBRタイミングを検出するCBR検出器52を含む。テストモードリセット時においては、CBR検出信号CBRが出力されてテストモードがリセットされ、WCBR検出器54aからは、WCBR検出信号WCBRが出力されてテストモードが設定される。データ保持モード指定時においては、このCBR検出信号CBRが所定時間以上活性状態とされるとDRAMはセルフリフレッシュモードに入る。このCBR検出信号は、したがって、データ保持モード検出信号REFと等価である。

In FIG. 18, a test mode set

これらのテストモードセット回路54およびテストモードリセット回路52へ、入力バッファ50a,50bおよび50cを介して外部ロウアドレスストローブ信号ext./RAS、外部コラムアドレスストローブ信号ext./CASおよび外部ライトイネーブル信号ext./WEが与えられる。

External row address strobe signal ext. Is supplied to test mode set

DRAMにおいては、その内部構成要素はCMOSトランジスタであり、CMOSレベルの信号が伝播される。 In the DRAM, the internal component is a CMOS transistor, and a CMOS level signal is propagated.

一方、DRAMの外部装置においては、その入出力信号は、たとえばTTLレベル(またはLV(低電圧)TTLレベル)の場合がある。外部装置が、たとえばバイポーラトランジスタなどで構成されている場合、その出力信号レベルは、高速動作性を保証するために小さくされ、TTLまたはLVTTLなどの信号が用いられる。TTLレベルにおいては、ハイレベルの信号電圧Vihが、2.0Vであり、Lレベル信号電圧Vinは、0.8Vである。入力初段に設けられる外部装置とのインタフェースとなるバッファをCMOS構成とした場合、TTL(またはLVTTL)レベルの信号が与えられた場合、貫通電流が流れる場合が生じる。データ保持モードにおいてこの貫通電流を低下させるための構成について以下に説明する。 On the other hand, in an external device of a DRAM, the input / output signal may be at a TTL level (or LV (low voltage) TTL level), for example. When the external device is composed of, for example, a bipolar transistor, its output signal level is reduced to ensure high-speed operation, and a signal such as TTL or LVTTL is used. At the TTL level, the high level signal voltage Vih is 2.0V, and the L level signal voltage Vin is 0.8V. When a buffer serving as an interface with an external device provided at the first input stage has a CMOS configuration, a through current may flow when a TTL (or LVTTL) level signal is applied. A configuration for reducing the through current in the data holding mode will be described below.

図19(A)は、この発明の実施の形態3に従う入力バッファ回路の構成を示し、図19(B)は、その等価論理ゲートを示す図である。図19(A)において、入力バッファ50は、電源ノードVccと内部出力ノードNbとの間に接続され、かつそのゲートが入力ノードNaに接続されるpチャネルMOSトランジスタQaと、内部出力ノードNbと内部ノードNcとの間に接続され、そのゲートがパワーカット指示信号PCを受けるように接続されるpチャネルMOSトランジスタQbと、内部ノードNcと接地ノードVssとの間に接続され、かつそのゲートが入力ノードNaに接続されるnチャネルMOSトランジスタQcと、内部ノードNcと接地ノードVssとの間に接続され、かつそのゲートがパワーカット指定信号PCを受けるように接続されるnチャネルMOSトランジスタQdを含む。

FIG. 19A shows a configuration of an input buffer circuit according to the third embodiment of the present invention, and FIG. 19B shows an equivalent logic gate thereof. In FIG. 19A,

電源ノードVccへ与えられる電源電位Vcc(ノードとその上の電位を同じ符号で示す)は、3.0Vであり、入力ノードNaへ与えられる入力信号INのHレベルは、TTLレベルの2.0Vである。パワーカット指示信号PCは、データ保持モード動作時において、Hレベルの活性状態とされ、MOSトランジスタQbを非導通状態、MOSトランジスタQdを導通状態として、ノードNcを接地電位レベルに固定する。MOSトランジスタQbが、データ保持モード動作時非導通状態とされるため、電源ノードVccから接地ノードVssへの電流が流れる経路は遮断される。したがって、入力信号INが、TTLレベルの2.0Vであっても、この入力バッファ50においては、貫通電流は生じず、データ保持モード時における消費電流が低減される。

A power supply potential Vcc applied to power supply node Vcc (a node and a potential thereon are indicated by the same sign) is 3.0 V, and an H level of input signal IN applied to input node Na is 2.0 V which is a TTL level. It is. Power cut instruction signal PC is activated at the H level in the data holding mode operation, MOS transistor Qb is turned off, MOS transistor Qd is turned on, and node Nc is fixed at the ground potential level. Since MOS transistor Qb is rendered non-conductive at the time of data holding mode operation, a path through which a current flows from power supply node Vcc to ground node Vss is cut off. Therefore, even if the input signal IN is at the TTL level of 2.0 V, no through current is generated in the

図19(B)は、この入力バッファ回路50の等価な論理ゲートを示し、入力信号INとパワーカット指示信号PCを受ける2入力NOR回路として表わされる。パワーカット指示信号PCがHレベルのときには、その内部出力信号Iintは、Lレベルに固定される。入力信号INのレベルは、Hレベルとされる場合もあり、またLレベルとされる場合もある。したがって、このノードNbの電位は実際には、パワーカット指示信号PCの活性化時における入力信号INの電位レベルにより決定される。ここでは、図19(B)においては、パワーカット指定信号PCの活性化時(Hレベルのとき)においては、内部入力信号Iintの電位レベルが固定されることを示すために、2入力NOR回路が示されるが、ノードNcから内部信号Iintが出力されてもよい。

FIG. 19B shows an equivalent logic gate of the

パワーカットモード指示信号PCがLレベルのとき、通常動作モード時であり、MOSトランジスタQbが導通状態とされ、MOSトランジスタQdが非導通状態とされる。この状態においては、入力信号INの電位レベルに従って、MOSトランジスタQcが、導通状態または非導通状態とされる。この状態においては、MOSトランジスタQbが導通しているため、MOSトランジスタQaおよびQcを介して電源ノードVccから接地ノードVssへ電流が流れる経路が形成されるためにこの入力信号INに応じた(反転された)内部入力信号Iint(CMOSレベル)を生成することができる。 When power cut mode instruction signal PC is at the L level, it is in the normal operation mode, MOS transistor Qb is turned on, and MOS transistor Qd is turned off. In this state, MOS transistor Qc is turned on or off according to the potential level of input signal IN. In this state, since MOS transistor Qb is conductive, a path is formed through which current flows from power supply node Vcc to ground node Vss via MOS transistors Qa and Qc. The internal input signal Iint (CMOS level) can be generated.

ここで、MOSトランジスタQdが設けられているのは、パワーカット指示信号PCの活性化時内部ノードNcがフローティング状態とされ、ノイズの影響により、MOSトランジスタQbおよびQcが導通状態とされて、貫通電流が流れる経路が形成されるのを防止するためである。内部出力ノードNbは、MOSトランジスタQaにより充電され、その電位レベルは固定される。 Here, MOS transistor Qd is provided because internal node Nc is brought into a floating state when power cut instruction signal PC is activated, and MOS transistors Qb and Qc are rendered conductive by the influence of noise, thereby penetrating. This is to prevent the formation of a path through which current flows. Internal output node Nb is charged by MOS transistor Qa, and its potential level is fixed.

図20(A)は、パワーカット指示信号PCを発生する部分の構成を概略的に示す図である。図20(A)において、パワーカット指示信号発生部は、バッファ回路55を介して与えられる外部ロウアドレスストローブ信号ext./RASおよび外部コラムアドレスストローブ信号ext./CASを受けて、データ保持モードが指定されたか否かを識別するリフレッシュ検出回路4と、このリフレッシュ検出回路4からのデータ保持モード指定信号REFと、リフレッシュタイマ18から与えられるリフレッシュ要求信号φrefを受けるインバータ57と、データ保持モード指定信号REFおよびインバータ57の出力信号を受けるAND回路59を含む。AND回路59からパワーカット指示信号PCが発生されてバッファ回路55へ与えられる。このバッファ回路55は、先の図18に示すバッファ50aおび50bを含む。このリフレッシュ検出器4は、バッファ回路55から与えられるロウアドレスストローブ信号/RASおよびコラムアドレスストローブ信号/CASがCBRタイミングを満足しているか否かを検出するCBR検出器4aを含む。このCBR検出器4aからデータ保持モード指定信号REFが出力される。CBR検出器4aは、また外部ライトイネーブル信号ext./WEをバッファ回路55を介して受けるように構成されてもよい。次にこの図20に示すパワーカット指示信号発生部の動作をその動作波形図である図20(B)を参照して説明する。

FIG. 20A schematically shows a configuration of a portion that generates power cut instruction signal PC. 20A, the power cut instruction signal generator generates an external row address strobe signal ext. / RAS and external column address strobe signal ext. In response to / CAS, a

バッファ回路55を介して与えられるロウアドレスストローブ信号/RASおよびコラムアドレスストローブ信号/CASがCBRタイミングを満足すると、CBR検出器4aから出力されるデータ保持モード指定信号RRFがHレベルの活性状態とされる。リフレッシュタイマ18が、リフレッシュ制御回路(図2参照)の制御の下に駆動され、所定時間が経過すると一定の時間間隔でリフレッシュ要求信号φrefを出力する。このリフレッシュ要求信号φrefは、Hレベルのときに活性状態とされる。したがって、データ保持モード期間の間、このリフレッシュ要求信号φrefがLレベルのとき、パワーカット指示信号PCがHレベルとされる。このパワーカット指定信号PCがHレベルの期間、図19(A)に示すように、入力バッファにおいて、電流経路が遮断される。リフレッシュ要求信号φrefがHレベルの活性状態とされると、インバータ57の出力信号がLレベルとされ、パワーカット指定信号PCが、応じてLレベルとされる。この期間の間、バッファ回路55において電源ノードVccから接地ノードVssの間に電流が流れる経路が形成され、入力バッファ(バッファ回路55)が動作状態とされ、外部から与えられる制御信号(/RASおよび/CAS)を取込むことができる。

When row address strobe signal / RAS and column address strobe signal / CAS applied through buffer circuit 55 satisfy the CBR timing, data holding mode designating signal RRF output from CBR detector 4a is activated to an H level. The The

データ保持モードのリセット時においては、外部ロウアドレスストローブ信号ext.RASがHレベルとされる。この外部ロウアドレスストローブ信号ext./RASがHレベルとされても、パワーカット指定信号PCがHレベルであれば、バッファ回路55は非動作状態であり、このバッファ回路55の出力信号の電位レベルは変化しない。ある時間が経過して、外部ロウアドレスストローブ信号ext./RASおよびコラムアドレスストローブ信号ext./CASがともにHレベルとされる状態において、リフレッシュ要求信号φrefが活性状態とされると、パワーカット指定信号PCがLレベルとされ、このHレベルの信号ext./RASおよびext./CASがバッファ回路55を介してリフレッシュ制御検出回路4へ与えられ、データ保持モード指定信号REFがHレベルの信号/RASによりLレベルとされる。そのデータ保持モード指定信号REFのLレベルへの立下がりに応答して、パワーカット指示信号PCがLレベルとされ、バッファ回路55(入力バッファ50a〜50c)が常時作動状態とされる。

At the time of resetting the data holding mode, the external row address strobe signal ext. RAS is set to H level. The external row address strobe signal ext. Even if / RAS is at the H level, if the power cut designation signal PC is at the H level, the buffer circuit 55 is in an inoperative state, and the potential level of the output signal of the buffer circuit 55 does not change. After a certain period of time, external row address strobe signal ext. / RAS and column address strobe signal ext. In a state where both / CAS are at the H level, when the refresh request signal φref is activated, the power cut designating signal PC is set at the L level, and the signal ext. / RAS and ext. / CAS is applied to the refresh

したがって、この図20(A)に示す構成においては、データ保持モードリセット時において、外部から与えられる制御信号ext./RASおよびext./CASを1リフレッシュサイクル期間(1φref期間)Hレベルに保持することにより、データ保持モードが解除される。データ保持モード解除時において、リフレッシュ要求信号φrefがHレベルの活性状態とされ、内部でリフレッシュ動作が行われる。したがって、このリフレッシュデータ保持モード解除後1リフレッシュ期間(リフレッシュ動作が実際に行われる期間)の間、外部からのこのDRAMへのアクセスを禁止することが必要とされる。 Therefore, in the configuration shown in FIG. 20A, when data holding mode is reset, control signal ext. / RAS and ext. By holding / CAS at the H level for one refresh cycle period (1φref period), the data holding mode is released. When the data holding mode is released, the refresh request signal φref is activated to an H level, and a refresh operation is performed internally. Therefore, it is necessary to prohibit external access to the DRAM for one refresh period (period in which the refresh operation is actually performed) after the refresh data holding mode is released.

[変更例]

図21(A)は、この発明の実施の形態3の変更例の構成を示す図である。図21(A)においては、リフレッシュ要求信号φrefを受けるインバータ57とパワーカット指示信号PCを出力するAND回路59との間に、分周器58が設けられる。他の構成は、図20(A)に示す構成と同じであり、対応する部分には同一の参照番号を付す。この図21(A)に示す構成の場合、図21(B)に示す動作波形図において明らかに見られるように、パワーカット指示信号PCは、リフレッシュ要求信号φrefを所定の分周比で分周した周期でLレベルとされる。ここで、図21(B)においては、分周比1/2の場合が一例として示される。したがって、データ保持モードリセット時においては、外部からの制御信号ext./RASおよびext./CASをHレベルに保持する期間は、この分周されたリフレッシュ要求信号の周期の期間で済み、次のアクセスを速いタイミングで行うことができる。この分周器58の分周比は、パワーカット指示信号PCをHレベルおよびLレベルへ駆動するために必要とされる充放電電流およびバッファ回路55における貫通電流の大きさを考慮して、適当な値に設定される。これにより、低消費電流でかつデータ保持モードリセット時において次のアクセスを速いタイミングで行うことが可能となる。

[Example of change]

FIG. 21A shows a configuration of a modification of the third embodiment of the present invention. In FIG. 21A, a

以上のように、この発明の実施の形態3に従えば、入力バッファの貫通電流が流れる経路を、データ保持モード時に遮断するように構成したため、データ保持モード動作時における消費電流を低減することができる。 As described above, according to the third embodiment of the present invention, since the path through which the through current of the input buffer flows is configured to be cut off during the data holding mode, current consumption during the data holding mode operation can be reduced. it can.

また、リフレッシュ要求信号の活性化時に、入力バッファ回路を動作状態とすることにより、確実にデータ保持モードをリセット状態とすることができる。このリフレッシュ要求信号を分周して得られる信号により、入力バッファ回路の貫通電流経路を選択的に導通状態とすることにより、データ保持モードリセット時における外部の制御信号の状態を所定状態(Hレベルの非活性状態)に保持する期間が短くされ、応じて次のアクセス開始タイミングを速くすることができる。 Further, when the refresh request signal is activated, the data holding mode can be surely set to the reset state by setting the input buffer circuit to the operating state. The signal obtained by dividing the refresh request signal is used to selectively turn on the through-current path of the input buffer circuit, so that the state of the external control signal when the data holding mode is reset is set to a predetermined state (H level). (Inactive state) is shortened, and the next access start timing can be accelerated accordingly.

[実施の形態4]

図22は、この発明の実施の形態4に従うDRAMの要部の構成を示す図である。図22に示す構成においては、リフレッシュ動作時において内部ロウアドレス信号RA,/RAを発生する部分の構成が示される。

[Embodiment 4]

FIG. 22 shows a structure of a main portion of the DRAM according to the fourth embodiment of the present invention. In the configuration shown in FIG. 22, the configuration of the portion generating internal row address signals RA, / RA during the refresh operation is shown.

図19においては、リフレッシュ検出回路4からのデータ保持モード検出信号REFの活性化時、ロウアドレスバッファ16をスタティックに動作させるためのバッファ制御回路62が設けられる。

In FIG. 19, a

リフレッシュモード検出回路4は、外部ロウアドレスストローブ信号ext./RASの立下がりに応答して、外部コラムアドレスストローブ信号ext./CASをラッチするラッチ回路4aaと、このラッチ回路4aaの出力信号(ラッチ信号)のHレベルのときにセットされ、データ保持モード指定信号REFをHレベルの活性状態とするセット/リセットフリップフロップ4abを含む。このセット/リセットフリップフロップ4abは、外部ロウアドレスストローブ信号ext./RASの立上がりに応答してリセットされる。

Refresh

ラッチ回路4aaは、外部ロウアドレスストローブ信号ext./RASのがHレベルのとき導通状態とされて外部コラムアドレスストローブ信号ext./CASを通過させるnチャネルMOSトランジスタにより構成されるトランスファーゲート4caと、トランスファーゲート4caから伝達された信号を反転するインバータ4cbと、インバータ4cbの出力信号を反転してインバータ4cbの入力部へ伝達するインバータ4ccと、外部ロウアドレスストローブ信号ext./RASがLレベルのときに導通し、インバータ4cbの出力信号をセット/リセットフリップフロップ4abのセット入力Sへ与えるpチャネルMOSトランジスタで構成されるトランスファーゲート4cbを含む。ここで、実施の形態3の入力バッファが設けられていてもよい。

Latch circuit 4aa receives external row address strobe signal ext. / RAS is rendered conductive when H level, external column address strobe signal ext. Transfer gate 4ca formed of an n-channel MOS transistor that passes / CAS, inverter 4cb that inverts the signal transmitted from transfer gate 4ca, and the output signal of inverter 4cb is inverted and transmitted to the input of inverter 4cb Inverter 4cc and external row address strobe signal ext. It includes a transfer gate 4cb formed of a p-channel MOS transistor which conducts when / RAS is at L level and supplies the output signal of inverter 4cb to set input S of set / reset flip-flop 4ab. Here, the input buffer of

リフレッシュ制御回路6は、このリフレッシュモード検出回路4から与えられるデータ保持モード検出信号REFに応答してタイマ18を起動し、タイマ18から与えられるリフレッシュ要求信号φrefに応答してリフレッシュ動作活性化信号ZRASを活性状態としてRAS系駆動回路60へ与える。このリフレッシュ制御回路6は、またリフレッシュ動作完了時、このリフレッシュ動作活性化信号ZRASの立上がり(非活性化)に応答して、リフレッシュカウンタ10のカウント値を1増分(減分)する。

RAS系駆動回路60は、リフレッシュ動作活性化信号ZRASの活性化に応答して、ロウアドレスバッファにおけるラッチタイミングおよびその出力許可タイミングを与えるラッチ指示信号RALおよびバッファ活性化信号RADEを出力する。このRAS系駆動回路60は、またRAS系回路(信号RASに応答して動作する)に対する制御信号をも発生する。図22においては、センスアンプを活性化するためのセンスアンプ活性化信号φSAを代表的に示す。ビット線をイコライズするためのビット線イコライズ信号もこのRAS系駆動回路60は発生する。

In response to the activation of the refresh operation activation signal ZRAS, the

制御回路62は、データ保持モード指示信号REFとラッチ指示信号RALを受けるOR回路62aと、データ保持モード指示信号REFとバッファ活性化信号RADEを受けるOR回路62bを含む。OR回路62aは、データ保持モード指示信号REFとラッチ指示信号RALの一方がHレベルのときにHレベルの出力信号を生成する。OR回路62bは、データ保持モード指示信号REFおよびバッファ活性化信号RADEの一方がHレベルのときにHレベルの信号を出力する。

ロウアドレスバッファ16は、内部ロウアドレス信号ビットそれぞれに対応して設けられるロウアドレスバッファ回路を含む。図22においては、1ビットの内部ロウアドレス信号RAおよび/RAを発生するバッファ回路16aを代表的に示す。ロウアドレスバッファ回路16aは、OR回路62aの出力信号がHレベルのときに導通し、マルチプレクサ14から与えられる信号を通過させるnチャネルMOSトランジスタで構成されるトランスファーゲート16aaと、トランスファゲート16aaから与えられる信号を反転するインバータ16abと、インバータ16abの出力信号を反転してインバータ16abの入力部へ伝達するインバータ16acと、インバータ16abの出力信号を反転するインバータ16abと、インバータ16abの出力信号とOR回路62bの出力信号とを受けるNAND回路16aeと、NAND回路16aeの出力信号を反転して内部ロウアドレス信号ビット/RAを出力するインバータ16afと、インバータ16adの出力信号とOR回路62bの出力信号とを受けるNAND回路16agと、NAND回路16agの出力信号を反転して内部ロウアドレス信号ビットRAを生成するインバータ16ahを含む。

マルチプレクサ14は、リフレッシュ制御回路6から与えられる制御信号の制御の下に、リフレッシュカウンタ10から与えられるリフレッシュアドレスおよび外部から与えられるアドレス信号Aの一方を選択的に通過させる。次に、この図22に示すアドレス系回路の動作について、その動作波形図である図23を参照して説明する。

The

図23(A)は、図22に示すRAS系駆動回路60の動作を示す信号波形図である。RAS系駆動回路60は、リフレッシュ動作活性化信号ZRASが非活性状態のHレベルのときには、ラッチ指示信号RALをHレベルに保持し、またバッファ活性化信号RADEをLレベルに保持する。データ保持モード指示信号REFがLレベルの通常動作モード時の場合には、この状態においては、OR回路62aの出力信号がHレベルであり、OR回路62bの出力信号はLレベルである。ロウアドレスバッファ回路16aにおいては、したがってトランスファーゲート16aaがOR回路62aからのHレベルの信号に応答して導通状態とされ、マルチプレクサ14から与えられる信号を通過させる。一方、OR回路62bの出力信号は、Lレベルであり、NAND回路16aeおよび16adの出力信号はHレベルであり、ロウアドレス信号ビット/RAおよびRAはともにLレベルとされる。

FIG. 23A is a signal waveform diagram representing an operation of

リフレッシュ動作活性化信号ZRASがLレベルの活性状態とされると、ラッチ指示信号RALがLレベルとされ、また次いでバッファ活性化信号RADEがHレベルとされる。これにより、トランスファゲート16aaが非導通状態とされて、ラッチ状態にこのロウアドレスバッファ回路16aが入り、アドレスバッファ活性化信号RADEの立上がりに応答してNAND回路16aeおよび16adがインバータとして動作し、そのインバータ16abおよび16acで構成されるラッチ回路によりラッチされたアドレス信号ビットに対応する内部ロウアドレス信号ビット/RAおよびRAが生成される。 When refresh operation activation signal ZRAS is activated to an L level, latch instruction signal RAL is set to an L level, and then buffer activation signal RADE is set to an H level. As a result, transfer gate 16aa is rendered non-conductive, row address buffer circuit 16a enters the latch state, and NAND circuits 16ae and 16ad operate as inverters in response to the rise of address buffer activation signal RADE. Internal row address signal bits / RA and RA corresponding to the address signal bits latched by the latch circuit formed of inverters 16ab and 16ac are generated.

したがって、通常動作モード時においては、このリフレッシュ動作活性化信号ZRASに対応する内部RAS信号φRASZに従ってロウアドレスバッファ回路16aが、与えられるアドレス信号ビットをラッチして、内部ロウアドレス信号ビットを生成する。このロウアドレスバッファ回路16aは、リフレッシュ動作活性化信号ZRAS(内部RAS信号φRASZ)の非活性化に応答してリセット状態とされる。すなわち、信号RALがHレベルとされ 信号RADEがLレベルとされ、内部ロウアドレス信号ビットRAおよび/RAはともにLレベルとされる。 Therefore, in the normal operation mode, row address buffer circuit 16a latches an applied address signal bit in accordance with internal RAS signal φRASZ corresponding to refresh operation activation signal ZRAS to generate an internal row address signal bit. Row address buffer circuit 16a is reset in response to inactivation of refresh operation activation signal ZRAS (internal RAS signal φRASZ). That is, signal RAL is set to H level, signal RADE is set to L level, and internal row address signal bits RA and / RA are both set to L level.

データ保持モード動作時においては、データ保持モード指示信号REFがHレベルである。この状態においては、OR回路62aおよび62bの出力信号は常時Hレベルに保持される。したがって、ロウアドレスバッファ回路16aにおいては、トランスファーゲート16aaが導通状態を保持し、またNAND回路16aeおよび16adがインバータとして動作する。すなわち、このロウアドレスバッファ回路16aがスタティックに動作し、マルチプレクサ14から与えられる信号ビットに従って変化する信号ビットRAおよび/RAを生成する。

During the data holding mode operation, data holding mode instruction signal REF is at the H level. In this state, the output signals of OR circuits 62a and 62b are always held at the H level. Therefore, in row address buffer circuit 16a, transfer gate 16aa maintains a conductive state, and NAND circuits 16ae and 16ad operate as inverters. That is, row address buffer circuit 16a operates statically and generates signal bits RA and / RA that change according to the signal bits applied from

すなわち、図23(B)に示すように、外部ロウアドレスストローブ信号ext./RASおよび外部コラムアドレスストローブ信号ext./CASがCBRタイミングで与えられ、リフレッシュ検出回路4からのデータ保持モード指示信号REFがHレベルとされると、ロウアドレスバッファ16がスタティック動作を開始する。リフレッシュ制御回路6が、タイマ18からこのデータ保持モード指定信号REFが活性状態とされてから時間t経過後に与えられるリフレッシュ要求信号φrefに応答してリフレッシュ動作活性化信号ZRASを活性化すると、リフレッシュカウンタ10が活性化され、そのカウント値がマルチプレクサ14を介してロウアドレスバッファ16へ与えられ、応じて内部ロウアドレス信号ビットRAおよび/RAの状態が変化する。リフレッシュ動作が完了し、リフレッシュ動作活性化信号ZRASが非活性状態とされると、この非活性化に応答してリフレッシュカウンタ10のカウント値が更新される。これのカウント値の更新に従って、スタティック動作を行うロウアドレスバッファ回路16から出力されるロウアドレス信号ビットRAおよび/RAの状態が変化する。以降、このデータ保持モード動作期間の間、ロウアドレスバッファ16がスタティック動作を行い、リフレッシュ動作活性化信号ZRASの非活性化に応答してリフレッシュカウンタ10のカウント値が更新される毎に内部ロウアドレス信号ビットRAおよび/RAの状態が変化する。

That is, as shown in FIG. 23B, the external row address strobe signal ext. / RAS and external column address strobe signal ext. When / CAS is applied at the CBR timing and the data holding mode instruction signal REF from the

データ保持モード動作が完了すると、データ保持モード指定信号REFがLレベルの非活性状態とされ、ロウアドレスバッファ16がリセットされ、内部ロウアドレス信号ビットRAおよび/RAはLレベルに保持される。

When the data holding mode operation is completed, data holding mode designating signal REF is rendered inactive at L level,

上述のように、データ保持モード動作時において、ロウアドレスバッファ16をスタティックに動作させることにより、内部ロウアドレス信号ビットのうち、変化するロウアドレス信号ビットを出力するロウアドレスバッファ回路のみが充放電動作を行う。変化しないロウアドレス信号ビットに対するロウアドレスバッファ回路は充放電動作を行わないため、データ保持モード動作時における消費電流を低減することができる。このとき、選択メモリアレイ(サブアレイ)のセット/リセット(アクティブ状態/プリチャージ状態)は、RAS系駆動回路60の制御の下にリフレッシュ動作活性化信号ZRASに応答して行われている。

As described above, when the

図24は、データ保持モード時におけるリフレッシュ動作シーケンスを示す図である。リフレッシュ動作シーケンスにおいては、図24(a)に示すバーストリフレッシュモードと、図24(b)に示す分散リフレッシュモードとがある。バーストリフレッシュモードにおいては、図24(a)に示すように、連続して所定回数リフレッシュ動作が行われる。この所定回数のリフレッシュが完了すると、比較的長いポーズ時間Tpの間、DRAMはスタンバイ状態(プリチャージ状態)に維持される。このポーズ時間Tpが完了すると、再び所定回数のリフレッシュ動作が行われる。このバーストリフレッシュモードにおいては、先の図22において示したように、ロウアドレスバッファをスタティックに動作させ、変化するアドレス信号ビットの信号線のみを充放電させることにより、リフレッシュ動作時における動作電流が低減される。 FIG. 24 is a diagram showing a refresh operation sequence in the data holding mode. In the refresh operation sequence, there are a burst refresh mode shown in FIG. 24A and a distributed refresh mode shown in FIG. In the burst refresh mode, the refresh operation is continuously performed a predetermined number of times as shown in FIG. When the predetermined number of refreshes are completed, the DRAM is maintained in a standby state (precharge state) for a relatively long pause time Tp. When this pause time Tp is completed, a predetermined number of refresh operations are performed again. In this burst refresh mode, as shown in FIG. 22, the row address buffer is operated statically, and only the signal line of the changing address signal bit is charged / discharged, thereby reducing the operating current during the refresh operation. Is done.

また、図24(b)に示す分散リフレッシュモードにおいては、リフレッシュ動作は、所定のリフレッシュ期間Trefごとに行われる。したがってこの分散リフレッシュの構成と比べて、図21(a)に示すバーストリフレッシュモードの場合、ポーズ時間Tpをリフレッシュ間隔Trefよりも長く取ることができる(連続して複数行にわたるメモリセルデータがリフレッシュされるため)。結果として、実効的にDRAMがスタンバイ(プリチャージ状態)に維持される時間が長くなり、消費電流を低減することができる。本実施の形態4においては、このバーストリフレッシュモードを先の図22に示すロウアドレスバッファの構成と組合せて用いてサブアレイまたはメモリブロック単位でリフレッシュ動作を実行する。 In the distributed refresh mode shown in FIG. 24B, the refresh operation is performed every predetermined refresh period Tref. Therefore, compared to this distributed refresh configuration, in the burst refresh mode shown in FIG. 21A, the pause time Tp can be longer than the refresh interval Tref (memory cell data over a plurality of rows is refreshed continuously). For). As a result, the time during which the DRAM is effectively maintained in the standby (precharged state) becomes longer, and the current consumption can be reduced. In the fourth embodiment, this burst refresh mode is used in combination with the configuration of the row address buffer shown in FIG. 22 to perform a refresh operation in units of subarrays or memory blocks.

図25は、この発明の実施の形態4におけるDRAMのメモリブロック部の構成を概略的に示す図である。図25においては、2つのメモリブロックMBLおよびMBRを示す。このメモリブロックMBLおよびMBRの間に、メモリセルデータの検知および増幅を行うセンスアンプSAを含むセンスアンプ帯SABが配置される。このメモリブロックMBLおよびMBRによりセンスアンプ帯SABのセンスアンプSAを共有する構成は「シェアードセンスアンプ配置」と呼ばれる。「シェアードセンスアンプ配置」は、またセンスアンプがメモリブロックの両側に各列に交互に配置される「交互配置型シェアードセンスアンプ配置」の構成であってもよいが、この図25においては、説明を簡略化するために「シェアードセンスアンプ配置」の構成を示す。また、メモリブロックMBLおよびMBRは、それぞれ先の実施の形態1および2で示したサブアレイMB♯j(j=0〜7)であってもよく、またこのメモリブロックMBLおよびMBRが1つのサブアレイを構成してもよい。 FIG. 25 schematically shows a structure of a memory block portion of the DRAM according to the fourth embodiment of the present invention. In FIG. 25, two memory blocks MBL and MBR are shown. A sense amplifier band SAB including a sense amplifier SA for detecting and amplifying memory cell data is arranged between memory blocks MBL and MBR. A configuration in which the sense amplifier SA of the sense amplifier band SAB is shared by the memory blocks MBL and MBR is referred to as “shared sense amplifier arrangement”. The “shared sense amplifier arrangement” may be a configuration of an “alternate arrangement type shared sense amplifier arrangement” in which the sense amplifiers are alternately arranged in each column on both sides of the memory block. In order to simplify the above, a configuration of “shared sense amplifier arrangement” is shown. Memory blocks MBL and MBR may be subarrays MB # j (j = 0 to 7) shown in the first and second embodiments, respectively, and each of memory blocks MBL and MBR includes one subarray. It may be configured.

メモリブロックMBLが、一例として、128本のワード線WL0〜WL127を含み、メモリブロックMBRも、128本のワード線WL128〜WL225を含む。メモリブロックMBLに対しては、XデコーダRDLが設けられ、メモリブロックMBRに対しては、XデコーダRDRが配置される。 As an example, the memory block MBL includes 128 word lines WL0 to WL127, and the memory block MBR also includes 128 word lines WL128 to WL225. An X decoder RDL is provided for the memory block MBL, and an X decoder RDR is provided for the memory block MBR.

メモリブロックMBLおよびMBRそれぞれにおいてメモリセルの各列に対応してビット線対が配置される。図25においては、メモリブロックMBLにおいては、1つのビット線対BLL,/BLLを示し、メモリブロックMBRにおいては1つのビット線対BLRおよび/BLRを代表的に示す。 In each of memory blocks MBL and MBR, a bit line pair is arranged corresponding to each column of memory cells. In FIG. 25, memory block MBL shows one bit line pair BLL, / BLL, and memory block MBR representatively shows one bit line pair BLR and / BLR.

センスアンプ帯SABは、このメモリブロックMBLおよびMBRの対応の列のビット線対BLL,/BLLおよびBLR,/BLRに対応して配置されるセンスアンプSAを含む。このセンスアンプSAは、ビット線分離制御信号BLILに応答して選択的に導通状態とされるビット線分離ゲートIGLを介してビット線BLL,/BLLに接続され、かつ分離制御信号BLIRに応答して選択的に導通状態とされるビット線分離ゲートIGRを介してビット線BLR,/BLRに接続される。このビット線分離制御信号BLILおよびBLIRは、メモリブロック指定信号BSに応答する分離制御回路ICLから出力される。この分離制御回路ICLは、メモリブロックMBLがブロック指定信号BSにより指定されたときには、分離制御信号BLILをHレベルに保持し、分離制御信号BLIRをLレベルに保持する。 Sense amplifier band SAB includes sense amplifiers SA arranged corresponding to bit line pairs BLL, / BLL and BLR, / BLR in corresponding columns of memory blocks MBL and MBR. Sense amplifier SA is connected to bit lines BLL and / BLL via bit line isolation gate IGL which is selectively turned on in response to bit line isolation control signal BLIL, and in response to isolation control signal BLIR. Are connected to the bit lines BLR and / BLR via the bit line isolation gate IGR which is selectively turned on. Bit line isolation control signals BLIL and BLIR are output from isolation control circuit ICL responding to memory block designating signal BS. The separation control circuit ICL holds the separation control signal BLIL at the H level and the separation control signal BLIR at the L level when the memory block MBL is designated by the block designation signal BS.

センスアンプSAの動作時においては、ビット線対BLL,/BLLのみがセンスアンプSAに接続されるため、センスアンプSAが駆動する負荷が軽減され、高速でセンス動作を行うことができる。また、センスアンプSAのセンスノード(センスアンプとビット線対との接続ノード)の負荷容量(寄生容量)が小さくなるため、メモリセルMCからの読出電圧(ビット線に伝達されたメモリセルの記憶データにより生じるビット線の電位変化量)を大きくすることができ、安定にセンス動作を行うことができる。メモリブロック指定信号BSが、これらのメモリブロックMBLおよびMBR以外のメモリブロックを指定するときには、このビット線分離制御信号BLILおよびBLIRがともにHレベルとされて、センスアンプSAは分離制御ゲートIGLおよびIGRを介してビット線対BL,/BLLおよびBLR,/BLRに接続される。この状態においては、メモリブロックMBLおよびMBRはスタンバイ状態(プリチャージ状態)を維持する。 During the operation of the sense amplifier SA, only the bit line pair BLL, / BLL is connected to the sense amplifier SA, so that the load driven by the sense amplifier SA is reduced and the sense operation can be performed at high speed. Further, since the load capacitance (parasitic capacitance) of the sense node of sense amplifier SA (connection node between the sense amplifier and the bit line pair) is reduced, the read voltage from memory cell MC (memory cell memory transmitted to the bit line is stored). The amount of change in the potential of the bit line caused by the data can be increased, and the sensing operation can be performed stably. When memory block designating signal BS designates a memory block other than these memory blocks MBL and MBR, both bit line isolation control signals BLIL and BLIR are set to H level, and sense amplifier SA has isolation control gates IGL and IGR. To the bit line pairs BL, / BLL and BLR, / BLR. In this state, memory blocks MBL and MBR maintain a standby state (precharge state).

図26(A)は、ビット線分離制御信号BLILおよびBLIRを発生する部分の構成を示す図である。図26(A)において、リフレッシュ制御回路6は、リフレッシュ検出回路から与えられるデータ保持モード検出信号REFに応答して作動状態とされるリフレッシュ制御部70と、リフレッシュ制御部70からの起動信号に応答して所定期間をカウントするタイマ18aと、リフレッシュ制御部70の制御の下に起動され、ポーズ時間をカウントし、ポーズ時間経過ごとにリフレッシュ要求信号φPAを出力するポーズタイマ72と、リフレッシュ制御部70から出力されるリフレッシュ動作活性化信号ZRASをカウントするカウンタ74を含む。

FIG. 26A shows a structure of a portion for generating bit line isolation control signals BLIL and BLIR. In FIG. 26A, the

カウンタ74は、このメモリブロックMBLおよびMBRそれぞれに含まれるワード線の数(128)をカウントし、カウント動作完了後カウントアップ信号φCNTをたとえばLレベルの非活性状態とする。タイマ18aは、リフレッシュ制御部70の制御の下に、データ保持モード検出信号REFが活性状態とされてから所定期間経過後セルフリフレッシュ動作に入ることを示す信号を出力する。リフレッシュ制御部70は、このタイマ18aからのセルフリフレッシュモード指定信号に応答して連続してカウンタ74からのカウント信号φCNTがHレベルの間リフレッシュ動作活性化信号ZRASを繰返し活性化する。

リフレッシュ制御部70からのリフレッシュ動作活性化信号ZRASは、ブロックアドレス信号ビットRABa〜RABbをデコードするブロックデコーダ76へ与えられる。このブロックデコーダ76へ与えられるアドレス信号ビットの数は、メモリマットに含まれるメモリブロックの数により決定される。ブロックデコーダ76は、このリフレッシュ制御部70からのリフレッシュ動作活性化信号ZRASの活性化時に活性化されてデコード動作を行い、ブロック指定信号BSを出力する。

Refresh operation activation signal ZRAS from

分離制御回路ICLは、カウンタ74からのカウント制御信号φCNTおよびブロック指定信号BSおよびリフレッシュ動作活性化信号ZRASを受けて、ビット線分離信号BLILおよびBLIRを出力する。分離制御回路ICLは、カウンタ74からのカウント制御信号φCNTがHレベルの活性状態の間、すなわちバーストリフレッシュが行われる期間、分離制御信号BLILおよびBLIRの状態を保持する。次に、この図26(A)の示す回路の動作をその動作を波形図である図26(B)を参照して説明する。

Isolation control circuit ICL receives count control signal φCNT from

データ保持モード指定信号REFがHレベルの活性状態とされると、リフレッシュ制御部70は、タイマ18aを起動する。タイマ18aからタイムアップ信号が与えられると、リフレッシュ制御部70は、カウンタ74を活性状態として、その出力信号φCNTをHレベルの活性状態とする。これと並行して、リフレッシュ動作活性化信号ZRASを活性状態とする。図26(B)においては、リフレッシュ動作活性化信号ZRASの反転信号RASを示す。ブロックデコーダ76は、このリフレッシュ動作活性化信号ZRASの活性化に応答して、ロウアドレスバッファから与えられるブロックアドレス信号ビットRABa〜RABbをデコードし、選択されたメモリブロックに対するブロック選択信号BSをデコードし、選択されたメモリブロックに対するブロック選択信号BSを活性状態とする。

When the data holding mode designating signal REF is activated to the H level, the

分離制御回路ICLは、ブロックデコーダ76から与えられるブロック選択信号(BS0)に従って、ビット線分離制御信号BLILおよびBLIRの一方をHレベルとし、他方をLレベルとする。

Isolation control circuit ICL sets one of bit line isolation control signals BLIL and BLIR to H level and the other to L level in accordance with a block selection signal (BS0) provided from

今、メモリブロックMBLが最初に指定されたと仮定する。この状態においては、分離制御回路ICLは、ビット線分離信号BLILをHレベルに維持し、ビット線分離制御信号BLIRをLレベルに固定する。カウンタ74からのカウント信号φCNTがHレベルの間、分離制御回路ICLは、内部でリフレッシュ動作活性化信号ZRASを常時活性状態とみなす。したがって、リフレッシュ制御部70からのリフレッシュ動作活性化信号ZRASが繰返し活性状態と非活性状態を繰返しても、そのカウンタ74からのカウント制御信号φCNTがHレベルの間、分離制御信号BLILはHレベルを維持し、分離制御信号BLIRはLレベルを維持する。これにより、分離制御回路ICLにおける分離制御信号BLILおよびBLIRの充放電電流を低減し、データ保持モードにおける消費電流を低減する。

Now, assume that the memory block MBL is designated first. In this state, isolation control circuit ICL maintains bit line isolation signal BLIL at H level and fixes bit line isolation control signal BLIR at L level. While the count signal φCNT from the

リフレッシュ制御部70が128回リフレッシュ動作活性化信号ZRASを発生すると、カウンタ74は、そのカウント制御信号φCNTをLレベルにリセットする。このカウンタ74からのカウント制御信号φCNTのリセットに応答して、分離制御回路ICLは、その分離制御信号BLIRをHレベルに復帰させる。このときまた、リフレッシュ制御部70は、カウンタ74からのカウント制御信号φCNTの立下がりに応答してポーズタイマ72を起動する。ポーズタイマ72は、予め定められたポーズ時間を計測し、このポーズ時間が経過すると、再びリフレッシュ要求信号φPAを出力する。このリフレッシュ要求信号φPAに応答してリフレッシュ制御部70は、再びカウンタ74を駆動状態とし、カウント制御信号φCNTをHレベルとし、またリフレッシュ動作活性化信号ZRASを128回連続的に出力する。この状態においては、ブロックデコー76からのブロック選択信号BSが、メモリブロックMBRを指定する。したがって、分離制御回路ICLは、分離制御信号BLILをLレベルに立下げ、分離制御信号BLIRをHレベルに固定する。

When

メモリブロックMBRの128本のワード線が順次選択状態とされて、メモリブロックMBRのメモリセルの記憶データのリフレッシュが実行される。リフレッシュ動作活性化信号ZRASが128回発生されると、カウンタ74からのカウント制御信号φCNTがLレベルとされ、分離制御回路ICLは、リセット状態とされ、分離制御信号BILおよびBIRをともにHレベルとする。リフレッシュ制御部70は、このカウンタ74からのカウント制御信号φCNTの立下がりに応答して、再びポーズタイマ72を起動する。この間、ブロックデコーダ76は、リフレッシュ動作活性化信号ZRASが非活性状態にあり、この出力するブロック選択信号BSの状態を維持する。これは、ブロックデコーダ76へ与えられるクロック指定アドレス信号ビットRABaおよびRABbがスタティックに動作するロウアドレスバッファから与えられるためである。しかしながら、このブロックデコーダ76は、図26(B)において破線で示すように、バーストリフレッシュ動作完了後のポーズ期間においては、リセット状態とされる構成が用いられてもよい。

The 128 word lines in the memory block MBR are sequentially selected, and the stored data in the memory cells in the memory block MBR is refreshed. When refresh operation activation signal ZRAS is generated 128 times, count control signal φCNT from

ポーズタイマ72から、再びリフレッシュ要求信号φPAが与えられると、リフレッシュ制御部70は、再びカウンタ70を起動し、リフレッシュ動作活性化信号ZRASを繰り返し活性化状態とする。ブロックデコーダ76は、再びアドレス信号ビットをデコードして、メモリブロック指定信号BSを出力する。この状態において、メモリブロックMBLおよびMBRと異なるメモリブロックが指定される。したがって、分離制御回路ICLは、分離制御信号BILおよびBIRをともにHレベルに保持する。

When refresh request signal φPA is applied again from

上述の動作により、バーストリフレッシュをメモリブロック単位で実行することにより、センスアンプとメモリブロックとを接続するための分離制御信号の充放電は、このバーストリフレッシュ動作期間中行われないため、データ保持モード時における消費電流を低減することができる。 By performing burst refresh for each memory block by the above-described operation, the charge / discharge of the separation control signal for connecting the sense amplifier and the memory block is not performed during this burst refresh operation period. The current consumption in can be reduced.

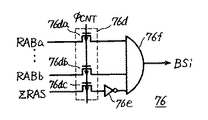

図27は、図26(A)に示すブロックデコーダ76の構成の一例を示す図である。図27においては、1つのブロック選択信号BSiを発生する部分の構成を示す。図27において、ブロックデコーダ76は、リフレッシュ動作活性化信号ZRSを受けるインバータ76aと、インバータ76aの出力信号とデータ保持モード指定信号REFを受けるOR回路76bと、OR回路76bの出力信号とブロック指定アドレス信号ビットRABa〜RABbを受けるAND回路76cを含む。AND回路76cからメモリブロック指定信号BSiが出力される。