CN113917747B - 显示面板及显示装置 - Google Patents

显示面板及显示装置 Download PDFInfo

- Publication number

- CN113917747B CN113917747B CN202111164181.8A CN202111164181A CN113917747B CN 113917747 B CN113917747 B CN 113917747B CN 202111164181 A CN202111164181 A CN 202111164181A CN 113917747 B CN113917747 B CN 113917747B

- Authority

- CN

- China

- Prior art keywords

- conductive

- pad

- display panel

- pins

- substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000000758 substrate Substances 0.000 claims abstract description 146

- 239000012790 adhesive layer Substances 0.000 claims abstract description 71

- 239000010410 layer Substances 0.000 claims description 162

- 229910052751 metal Inorganic materials 0.000 description 86

- 239000002184 metal Substances 0.000 description 86

- 239000010408 film Substances 0.000 description 32

- 239000004065 semiconductor Substances 0.000 description 16

- 239000011229 interlayer Substances 0.000 description 13

- 238000002161 passivation Methods 0.000 description 9

- 239000000203 mixture Substances 0.000 description 7

- 239000000853 adhesive Substances 0.000 description 6

- 230000001070 adhesive effect Effects 0.000 description 6

- 238000010586 diagram Methods 0.000 description 6

- 239000000463 material Substances 0.000 description 5

- 229910052581 Si3N4 Inorganic materials 0.000 description 4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 239000003292 glue Substances 0.000 description 4

- 239000004973 liquid crystal related substance Substances 0.000 description 4

- 230000000149 penetrating effect Effects 0.000 description 4

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 4

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 3

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 3

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 3

- 229910052782 aluminium Inorganic materials 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 230000009286 beneficial effect Effects 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 239000010949 copper Substances 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 229910052750 molybdenum Inorganic materials 0.000 description 3

- 239000011733 molybdenum Substances 0.000 description 3

- 239000002245 particle Substances 0.000 description 3

- 229910052709 silver Inorganic materials 0.000 description 3

- 239000004332 silver Substances 0.000 description 3

- 229910052719 titanium Inorganic materials 0.000 description 3

- 239000010936 titanium Substances 0.000 description 3

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 2

- 239000004642 Polyimide Substances 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229920000058 polyacrylate Polymers 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/131—Interconnections, e.g. wiring lines or terminals

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

- G02F1/13452—Conductors connecting driver circuitry and terminals of panels

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

- G02F1/13458—Terminal pads

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/02—Bonding areas ; Manufacturing methods related thereto

- H01L24/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L24/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/02—Bonding areas ; Manufacturing methods related thereto

- H01L24/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L24/06—Structure, shape, material or disposition of the bonding areas prior to the connecting process of a plurality of bonding areas

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L24/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L24/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L24/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L24/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/90—Assemblies of multiple devices comprising at least one organic light-emitting element

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/05001—Internal layers

- H01L2224/0502—Disposition

- H01L2224/05022—Disposition the internal layer being at least partially embedded in the surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/05001—Internal layers

- H01L2224/05073—Single internal layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/05001—Internal layers

- H01L2224/05099—Material

- H01L2224/051—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05117—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 400°C and less than 950°C

- H01L2224/05124—Aluminium [Al] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/05001—Internal layers

- H01L2224/05099—Material

- H01L2224/051—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/05139—Silver [Ag] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/05001—Internal layers

- H01L2224/05099—Material

- H01L2224/051—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/05147—Copper [Cu] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/05001—Internal layers

- H01L2224/05099—Material

- H01L2224/051—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05163—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than 1550°C

- H01L2224/05166—Titanium [Ti] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/05001—Internal layers

- H01L2224/05099—Material

- H01L2224/051—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05163—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than 1550°C

- H01L2224/0518—Molybdenum [Mo] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0556—Disposition

- H01L2224/05562—On the entire exposed surface of the internal layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0556—Disposition

- H01L2224/05571—Disposition the external layer being disposed in a recess of the surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05573—Single external layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05599—Material

- H01L2224/05686—Material with a principal constituent of the material being a non metallic, non metalloid inorganic material

- H01L2224/05688—Glasses, e.g. amorphous oxides, nitrides or fluorides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/06—Structure, shape, material or disposition of the bonding areas prior to the connecting process of a plurality of bonding areas

- H01L2224/061—Disposition

- H01L2224/0612—Layout

- H01L2224/0615—Mirror array, i.e. array having only a reflection symmetry, i.e. bilateral symmetry

- H01L2224/06152—Mirror array, i.e. array having only a reflection symmetry, i.e. bilateral symmetry being non uniform, i.e. having a non uniform pitch across the array

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/2901—Shape

- H01L2224/29016—Shape in side view

- H01L2224/29017—Shape in side view being non uniform along the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/2902—Disposition

- H01L2224/29026—Disposition relative to the bonding area, e.g. bond pad, of the semiconductor or solid-state body

- H01L2224/29028—Disposition relative to the bonding area, e.g. bond pad, of the semiconductor or solid-state body the layer connector being disposed on at least two separate bonding areas, e.g. bond pads

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32135—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/32145—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/053—Oxides composed of metals from groups of the periodic table

- H01L2924/0549—Oxides composed of metals from groups of the periodic table being a combination of two or more materials provided in the groups H01L2924/0531 - H01L2924/0546

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

- H01L2924/141—Analog devices

- H01L2924/1426—Driver

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Mathematical Physics (AREA)

- General Physics & Mathematics (AREA)

- Optics & Photonics (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Liquid Crystal (AREA)

Abstract

本申请提供一种显示面板及显示装置,显示面板具有显示区和焊盘区,焊盘区位于显示区的一侧,显示面板包括:基板,具有承载面;第一导电垫,设置于基板的承载面上,且位于焊盘区;第二导电垫,设置于基板的承载面上,且位于焊盘区;驱动芯片,绑定于焊盘区,驱动芯片包括第一引脚和第二引脚,第一引脚与第一导电垫对应设置,第二引脚与第二导电垫对应设置,第一导电胶层,填充于第一导电垫与第一引脚之间,且电性连接第一导电垫与第一引脚,以及第二导电胶层,填充于第二导电垫与第二引脚之间,且电性连接第二导电垫与第二引脚;其中,第一导电胶层靠近第一引脚的表面至基板的距离与第二导电胶层靠近第二引脚的表面至基板的距离不同。

Description

技术领域

本申请涉及显示技术领域,尤其涉及一种显示面板及显示装置。

背景技术

如图1所示,其为传统显示面板的平面示意图,显示面板100具有显示区100a,显示面板100包括驱动芯片200,驱动芯片200绑定于显示面板100的显示区100a的一侧,驱动芯片200包括输入引脚201、输出引脚202以及冗余引脚203,输入引脚201和输出引脚202起到传输信号的作用,冗余引脚203不具有输入或输出功能,冗余引脚203只用于支撑驱动芯片200的平衡,冗余引脚203并排设置于驱动芯片200靠近显示区100a的局部区域,输入引脚201和输出引脚202并排设置于冗余引脚203远离显示区100a的一侧,且输入引脚201位于输出引脚202的相对两侧,图1所示驱动芯片200会导致部分远离冗余引脚203的输入引脚201翘起而无法绑定于显示面板100上,进而导致显示面板性能降低,甚至不能正常工作。

因此,有必要提出一种技术方案以解决部分远离冗余引脚的输入引脚翘起而无法绑定于显示面板上导致显示面板不能正常工作的问题。

发明内容

本申请的目的在于提供一种显示面板,以解决驱动芯片绑定于阵列基板上时由于部分引脚翘起而无法绑定于显示面板上的问题。

为实现上述目的,技术方案如下:

一种显示面板,所述显示面板具有显示区和焊盘区,所述焊盘区位于所述显示区的一侧,所述显示面板包括:

基板,具有承载面;

第一导电垫,设置于所述基板的所述承载面上,且位于所述焊盘区;

第二导电垫,设置于所述基板的所述承载面上,且位于所述焊盘区;

驱动芯片,绑定于所述焊盘区,所述驱动芯片包括:

第一引脚,与所述第一导电垫对应设置;以及

第二引脚,与所述第二导电垫对应设置;

第一导电胶层,填充于所述第一导电垫与所述第一引脚之间,且电性连接所述第一导电垫与所述第一引脚;以及

第二导电胶层,填充于所述第二导电垫与所述第二引脚之间,且电性连接所述第二导电垫与所述第二引脚;

其中,所述第一导电胶层靠近所述第一引脚的表面至所述基板的距离与所述第二导电胶层靠近所述第二引脚的表面至所述基板的距离不同。

本申请还提供一种显示装置,所述显示装置包括上述显示面板。

有益效果:本申请提供一种显示面板及显示装置,通过电性连接第一导电垫和第一引脚的第一导电胶层靠近第一引脚的表面至基板的距离与电性连接第二导电垫和第二引脚的第二导电胶层靠近第二引脚的表面至基板的距离不同,以补偿绑定驱动芯片时驱动芯片上引脚部分翘曲导致的高度差异,保证驱动芯片能良好地绑定于显示面板上。

附图说明

图1为传统显示面板的平面示意图;

图2为本申请第一实施例显示面板的示意图;

图3为沿图2所示显示面板A-A切线的第一种截面示意图;

图4为图2中驱动芯片绑定于图3中第一导电垫和第二导电垫的截面示意图;

图5为驱动芯片、柔性印刷电路板绑定于阵列基板上的平面示意图;

图6为沿图2所示显示面板A-A切线的第二种截面示意图;

图7为沿图2所示显示面板A-A切线的第三种截面示意图;

图8为沿图2所示显示面板A-A切线的第四种截面示意图;

图9为沿图2所示显示面板A-A切线的第五种截面示意图;

图10为沿图2所示显示面板A-A切线的第六种截面示意图;

图11为本申请第二实施例显示面板的示意图;

图12为沿图11所示显示面板的B-B切线的截面示意图;

图13为本申请第三实施例显示面板的示意图;

图14为沿图13所示显示面板的C-C切线的截面示意图;

图15为本申请第四实施例显示面板的示意图;

图16为本申请第五实施例显示面板的示意图;

图17为本申请第六实施例显示面板的局部截面示意图。

附图标记:

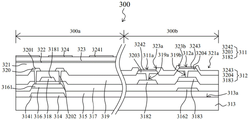

300显示面板;300a显示区;300b焊盘区;300b2空白区域;31阵列基板;311第一导电垫;311a第一结合面;312第二导电垫;312a第二结合面;313基板;313a承载面;314遮光层;3141遮光图案;3142遮光构件;3143第一遮光构件;3144第二遮光构件;315缓冲层;316半导体层;3161有源图案;3162半导体构件;317栅极绝缘层;318第一金属层;3181栅极;3182第一金属构件;3183第二金属构件;3184第五金属构件;3185第六金属构件;3186第九金属构件;319层间绝缘层;319a第三过孔;319b第四过孔;320第二金属层;3201源极;3202漏极;3203第三金属构件;3204第四金属构件;3205第七金属构件;3206第八金属构件;3207第十金属构件;321平坦化层;321a第一开口;322第一透明导电层;323钝化层;323a第二开口;323b第三开口;324第二透明导电层;3241像素电极;3242第一透明导电构件;3243第二透明导电构件;3244第三透明导电构件;3245第四透明导电构件;3246第五透明导电构件;325导电构件;326第三导电垫;326a第三结合面;327冗余导电垫;327a冗余结合面;328第四导电垫;328a第四结合面;329第五导电垫;329a第五结合面;33驱动芯片;330基体;331第一引脚;332第二引脚;333第三引脚;334冗余引脚;335第四引脚;336第五引脚;330a第一边缘;330b第二边缘;34柔性印刷电路板;341主体部;342第一绑定部;343第二绑定部;401第一导电胶层;401a第一表面;402第二导电胶层;402a第二表面;40a导电粒子。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

针对背景技术的问题,发明人发现驱动芯片上的部分引脚翘起的主要原因在于,驱动芯片上的引脚分布不均,导致驱动芯片绑定于显示面板上时,驱动芯片上的多个引脚受的支撑力分布不均,支撑力分布不均导致驱动芯片上的部分引脚出现翘起而无法绑定于显示面板的焊盘上,有鉴于此,本申请通过电性连接第一导电垫和第一引脚的第一导电胶层靠近第一引脚的表面至基板的距离与电性连接第二导电垫和第二引脚的第二导电胶层靠近第二引脚的表面至基板的距离不同,使得驱动芯片上翘起的引脚与导电的第一导电胶层和导电的第二导电胶层中至基板的距离较大的一者结合,保证驱动芯片上翘起的引脚能正常地绑定于显示面板。其中,第一导电垫与第二导电垫均设置于基板的承载面上,且两者均位于焊盘区。

请参阅图2-图5,图2为本申请第一实施例显示面板的示意图,图3为沿图2所示显示面板A-A切线的第一种截面示意图,图4为图2中驱动芯片绑定于图3中第一导电垫和第二导电垫的截面示意图,图5为驱动芯片、柔性印刷电路板绑定于阵列基板上的平面示意图。显示面板300可以为液晶显示面板,显示面板300也可以为有机发光二极管显示面板。具体地,显示面板300为边缘场开关(FringeField Switching,FFS)液晶显示面板。可以理解的是,显示面板300也可以为平面转换(In-Plane Switching,IPS)液晶显示面板或者垂直配向(Vertical Alignment)液晶显示面板。显示面板300具有显示区300a和焊盘区300b,焊盘区300b设置于显示区300a的一侧。显示面板300包括阵列基板31、驱动芯片33以及柔性印刷电路板34,驱动芯片33和柔性印刷电路板34均绑定于阵列基板31的焊盘区300b。

在本实施例中,显示面板300对应显示区300a的部分用于显示。在显示区300a,阵列基板31包括多个阵列排布的薄膜晶体管、像素电极、公共电极、扫描线以及数据线。

在本实施例中,焊盘区300b设置有多个导电垫,驱动芯片33绑定于焊盘区300b的多个导电垫上,即显示面板300的驱动芯片33绑定于玻璃上(Chip OnGlass,COG)。部分导电垫用于输入电信号且传输至驱动芯片33,以为驱动芯片33工作提供工作信号;部分导电垫用于输出电信号至显示面板300的显示区300a,以为显示面板300提供显示信号。多个导电垫包括多个第一导电垫311和多个第二导电垫312,多个第一导电垫311沿第一方向呈直线并排设置,多个第二导电垫312沿第一方向呈直线并排设置,第二导电垫312位于第一导电垫311远离显示区300a的一侧,多个第二导电垫312与多个第一导电垫311在第二方向上错位设置,以使得与第二导电垫312连接的布线可以从相邻两个第一导电垫311之间的区域之间延伸出。其中,第二方向为显示区300a指向焊盘区300b的方向,第一方向与第二方向垂直。

在本实施例中,驱动芯片33包括基体330、多个第一引脚331以及多个第二引脚332,驱动芯片33具有第一边缘330a和第二边缘330b,第一边缘330a与第二边缘330b相对,驱动芯片33绑定于阵列基板31上时,第一边缘330a靠近显示区300a且第二边缘330b远离显示区300a,多个第一引脚331以及多个第二引脚332均设置于基体330上且靠近第二边缘330b设置,即第一引脚331至第一边缘330a的距离大于第一引脚331至第二边缘330b的距离,且第二引脚332至第一边缘330a的距离大于第二引脚332至第二边缘330b的距离,多个第一引脚331位于多个第二引脚332远离第二边缘330b的一侧,即第二引脚332位于第一引脚331远离显示区100a的一侧,第一引脚331与第二引脚332在第二方向上错位设置。第一引脚331的厚度等于第二引脚332的厚度。

在本实施例中,阵列基板31包括依次堆叠的基板313、遮光层314、缓冲层315、半导体层316、栅极绝缘层317、第一金属层318、层间绝缘层319、第二金属层320、平坦化层321、第一透明导电层322、钝化层323以及第二透明导电层324。

在本实施例中,基板313为玻璃基板,基板313具有承载面313a,承载面313a为平坦的水平表面。

在本实施例中,遮光层314包括遮光图案3141和遮光构件3142,遮光图案3141设置于基板313的承载面313a上且位于显示区300a,遮光图案3141起到遮光的作用,遮光构件3142设置于基板313上且位于焊盘区300b,遮光构件3142对应第二导电垫312设置。遮光层314为金属层。遮光层314的厚度为450埃-550埃。遮光层314的制备材料选自钼、铝、钛、铜以及银中的至少一种。

在本实施例中,缓冲层315覆盖遮光层314以及基板313,缓冲层315位于显示区300a和焊盘区300b。缓冲层315的厚度为2500埃-3500埃。缓冲层315包括氮化硅层和氧化硅层,氮化硅层靠近基板313设置,氧化硅层远离基板313设置。

在本实施例中,半导体层316设置于缓冲层315上,半导体层316包括有源图案3161,有源图案3161位于显示区300a且对应遮光图案3141设置。半导体层316的制备材料选自非晶硅、多晶硅以及金属氧化物中的任意一种。半导体层316的厚度为400埃-500埃。

在本实施例中,栅极绝缘层317覆盖半导体层316和缓冲层315,栅极绝缘层317位于显示区300a和焊盘区300b。栅极绝缘层317的厚度为1000埃-1500埃。栅极绝缘层317的制备材料为氮化硅或者氧化硅。

在本实施例中,第一金属层318设置于栅极绝缘层317上。第一金属层318包括栅极3181、第一金属构件3182以及第二金属构件3183,栅极3181位于显示区300a且对应有源图案3161设置,第一金属构件3182和第二金属构件3183均位于焊盘区300b,第二金属构件3183位于第一金属构件3182远离显示区300a的一侧,第二金属构件3183位于遮光构件3142的正上方,栅极3181的厚度、第一金属构件3182的厚度以及第二金属构件3183的厚度均相同。第一金属层318的厚度为2500埃-3500埃。第一金属层318的制备材料选自钼、铝、钛、铜以及银中的至少一种。

在本实施例中,层间绝缘层319覆盖第一金属层318和栅极绝缘层317,层间绝缘层319位于显示区300a和焊盘区300b。层间绝缘层319的厚度为5500埃-6500埃。层间绝缘层319的制备材料选自氮化硅、氧化硅中的至少一种。

在本实施例中,第二金属层320设置于层间绝缘层319上。第二金属层320包括源极3201、漏极3202、第三金属构件3203以及第四金属构件3204,源极3201和漏极3202位于显示区300a且设置于栅极3181的相对两侧,源极3201通过贯穿层间绝缘层319和栅极绝缘层317的第一过孔与有源图案3161接触,漏极3202通过贯穿层间绝缘层319和栅极绝缘层317的第二过孔与有源图案3161接触,第三金属构件3203对应第一金属构件3182设置且通过贯穿层间绝缘层319的第三过孔319a与第一金属构件3182电性连接,第四金属构件3204对应第二金属构件3183设置且通过贯穿层间绝缘层319的第四过孔319b与第二金属构件3183电性连接,源极3201、漏极3202、第三金属构件3203以及第四金属构件3204的厚度均相同。第二金属层320的厚度为4000埃-6500埃。第二金属层320的制备材料选自钼、铝、钛、铜以及银中的至少一种。

在本实施例中,平坦化层321覆盖第二金属层320和层间绝缘层319,平坦化层321包括位于焊盘区300b的第一开口321a,第一开口321a使第三金属构件3203以及第四金属构件3204均暴露。平坦化层321的厚度为2.0微米-3.0微米。平坦化层321的制备材料为聚酰亚胺或者聚丙烯酸酯。

在本实施例中,第一透明导电层322设置于平坦化层321上且位于显示区300a,第一透明导电层322为公共电极层。第一透明导电层322的制备材料为氧化铟锡。第一透明导电层322的厚度为500埃-700埃。

在本实施例中,在显示区300a,钝化层323覆盖第一透明导电层322;在焊盘区300b,钝化层323覆盖平坦化层321、层间绝缘层319、第三金属构件3203以及第四金属构件3204,钝化层323对应第三金属构件3203设置有第二开口323a,钝化层323对应第四金属构件3204设置有第三开口323b。钝化层323的厚度为800埃-1200埃。钝化层323的制备材料为氮化硅或氧化硅中的任意一种。

在本实施例中,显示区300a的第二透明导电层324设置于钝化层323上,第二透明导电层324包括多个相互独立的像素电极3241、第一透明导电构件3242以及第二透明导电构件3243,第一透明导电构件3242的至少部分位于第二开口323a内且位于第三金属构件3203上,第二透明导电构件3243的至少部分位于第三开口323b内且位于第四金属构件3204上,像素电极3241、第一透明导电构件3242以及第二透明导电构件3243的厚度相同。第二透明导电层324的制备材料为氧化铟锡。第二透明导电层324的厚度为450埃-550埃。

在本实施例中,第一金属构件3182、第三金属构件3203以及第一透明导电构件3242组成第一导电垫311,第一导电垫311具有与驱动芯片33连接的第一结合面311a,第一结合面311a的至少部分与承载面313a平行。第二金属构件3183、第四金属构件3204以及第二透明导电构件3243组成第二导电垫312,第二导电垫312具有与驱动芯片33连接的第二结合面312a,第二结合面312a的至少部分与承载面313a平行。第一导电垫311的厚度等于第二导电垫312的厚度相同。由于第二导电垫312与基板313之间设置有遮光构件3142,使得第二导电垫312相对于第一导电垫311垫高,第一结合面311a与承载面313a平行的至少部分至基板313的距离小于第二结合面312a与承载面313a平行的至少部分至基板313的距离。如图3所示,第一结合面311a和第二结合面312a均与承载面313a平行且用于与驱动芯片33结合,可以理解的是,第一结合面311a和第二结合面312a也可以包括与承载面313a不平行的部分。

在本实施例中,如图4所示,显示面板还包括第一导电胶层401和第二导电胶层402,第一导电胶层401和第二导电胶层402均具有导电性,第一导电胶层401填充于第一导电垫311与第一引脚331之间且电性连接第一导电垫311与第一引脚331,第二导电胶层402填充于第二导电垫312与第二引脚332之间且电性连接第二导电垫312与第二引脚332,第一导电胶层401与第二导电胶层402之间通过各向异性导电胶连接且电性绝缘,第一导电胶层401的厚度与第二导电胶层402的厚度相同。其中,第一导电胶层401和第二导电胶层402的制备材料均为各向异性导电胶,第一导电胶层401和第二导电胶层402通过将各向异性导电胶层贴合至阵列基板上且使各向异性导电胶层受压后各向异性导电胶中的导电粒子40a受压相互接触导通而得到,即第一导电胶层401和第二导电胶层402是各向异性导电胶受压后具有导电性的胶层,且第一导电胶层401的厚度和第二导电胶层402的厚度为各向异性导电胶受压后具有导电性对应的厚度;第一导电胶层401与第二导电胶层402之间的各向异性导电胶中的导电粒子40a没有受力而分散设置导致没有形成导电通路,使得第一导电胶层401与第二导电胶层402之间电性绝缘。由于第一结合面311a至基板313的距离小于第二结合面312a至基板313的距离,第一导电胶层401的厚度与第二导电胶层402的厚度相同,第一导电胶层401靠近第一引脚331的第一表面401a至基板313的距离小于第二导电胶层402靠近第二引脚332的第二表面402a至基板313的距离。

需要说明的是,在其他实施例中,第一结合面311a至基板313的距离也可以等于第二结合面312a至基板313的距离,此时,第一导电胶层401的厚度小于第二导电胶层402的厚度;或者,第一导电胶层401的厚度小于第二导电胶层402的厚度,配合第一结合面311a至基板313的距离小于第二结合面312a至基板313的距离,以使得第一导电胶层401靠近第一引脚331的第一表面401a至基板313的距离小于第二导电胶层402靠近第二引脚332的第二表面402a至基板313的距离。

如图2及图4所示,由于焊盘区300b靠近显示区300a的空白区域300b2没有设置导电垫,多个第一引脚331与多个第一导电垫311一一对应设置且通过第一导电胶层401电性连接后,驱动芯片33靠近显示区300a的一端无支撑而向下倾斜,对应地,驱动芯片33的多个第二引脚332会翘起,多个翘起的第二引脚332与多个通过遮光构件3142垫高的第二导电垫312一一对应设置且通过第二导电胶层402电性连接。

在本实施例中,如图5所示,柔性印刷电路板34包括第一绑定部342、第二绑定部343以及主体部341,第一绑定部342与第二绑定部343均与主体部341连接,第一绑定部342和第二绑定部343均绑定于焊盘区300b且在垂直于显示区300a指向焊盘区300b的方向上位于驱动芯片33的相对两侧。柔性印刷电路板34的设计以及绑定方式使得显示面板300为窄边框的显示面板。

需要说明的是,阵列基板31还包括设置于焊盘区相对两侧的柔性印刷电路板绑定区(未示意出),阵列基板的柔性印刷电路板绑定区也设置有焊盘,柔性印刷电路板与柔性印刷电路板绑定区的焊盘之间电性连接,此处采用现有技术,不做详述。

本实施例显示面板在对应驱动芯片上翘起的第二引脚的第二导电垫的下方设置遮光构件,以垫高第二导电垫,垫高的第二导电垫与翘起的第二引脚之间能实现绑定且电性连接。

请参阅图6,其为沿图2所示显示面板A-A切线的第二种截面示意图。图6所示显示面板与图3所示显示面板基本相似,不同之处在于,半导体层316包括半导体构件3162,半导体构件3162位于焊盘区300b且对应第二导电垫312设置,遮光层314不包括设置于焊盘区300b的遮光构件。

相对于图3所示显示面板采用遮光层314中的遮光构件3142对第二导电垫312进行垫高,图6所示显示面板采用与有源图案3161同层设置的半导体构件3162对第二导电垫312进行垫高。

请参阅图7,其为沿图2所示显示面板A-A切线的第三种截面示意图。图7所示显示面板与图3所示显示面板基本相似,遮光层314包括遮光构件3142,遮光构件3142位于焊盘区300b且对应第二导电垫312设置的同时,半导体层316还包括半导体构件3162,半导体构件3162位于焊盘区300b且对应遮光构件3142设置。

相对于图3和图6所示显示面板中仅在第二导电垫312和基板313之间增设一个膜层,图7所示显示面板通过同时增设遮光构件3142和半导体构件3162,能将第二导电垫312垫得更高,更加有利于第二导电垫312与翘起得更高的第二引脚332之间进行绑定。

请参阅图8,其为沿图2所示显示面板A-A切线的第四种截面示意图。图8所示显示面板与图7所示显示面板基本相似,不同之处包括,在显示面板300的厚度方向上,第一导电垫311与基板313之间设置有第一膜层,第二导电垫312与基板313之间设置有第二膜层,第一膜层位于焊盘区300b且对应第一导电垫311设置,第二膜层位于焊盘区300b且对应第二导电垫312设置,第一膜层与第二膜层同层设置且第一膜层的厚度小于第二膜层的厚度。

具体地,遮光层314包括设置于焊盘区300b的第一遮光构件3143和设置于焊盘区300b的第二遮光构件3144,第一膜层为第一遮光构件3143,第二膜层为第二遮光构件3144,第一遮光构件3143对应第一导电垫311设置,第二遮光构件3144对应第二导电垫312设置,第一遮光构件3143的厚度小于第二遮光构件3144的厚度。可以理解的是,第一膜层也可以为第一导电垫与基板之间的其他膜层,第二膜层也可以为第二导电垫与基板之间的其他膜层,例如第一膜层和第二膜层均与有源图案同层。

在图3、图6、图7以及图8所示显示面板中,第一导电垫311与基板313之间的膜层数目小于第二导电垫312与基板313之间的膜层数目,以使得第一导电垫311的第一结合面311a与基板313的承载面313a平行的至少部分至基板313的距离小于第二导电垫312的第二结合面312a与基板313的承载面313a平行的至少部分至基板313的距离。在图8所示显示面板中,第一导电垫311与基板313之间的第一膜层的厚度小于第二导电垫312与基板313之间与第一膜层同层的第二膜层的厚度,以使得第一导电垫311的第一结合面311a与基板313的承载面313a平行的至少部分至基板313的距离小于第二导电垫312的第二结合面312a与基板313的承载面313a平行的至少部分至基板313的距离。可以理解的是,也可以通过在第二导电垫312与基板313之间增设显示区300a中不包括的其他一个或者多个膜层,该膜层包括但不限于金属层、绝缘层以及平坦化层,以对第二导电垫312进行垫高,垫高的第二导电垫312与翘起的第二引脚332之间实现绑定且电性连接。

请参阅图9,其为沿图2所示显示面板A-A切线的第五种截面示意图。图9所示显示面板与图3所示显示面板基板相似,不同之处在于,第一导电垫311的厚度小于第二导电垫312的厚度,且图9所示遮光层314不包括设置于焊盘区300b的遮光构件。

在本实施例中,第一导电垫311的膜层数目小于第二导电垫312的膜层数目。具体地,第一导电垫311由第一金属构件3182、第三金属构件3203以及第一透明导电构件3242组成,第二导电垫312由第二金属构件3183、第四金属构件3204、第二透明导电构件3243以及导电构件325组成,导电构件325设置于第二透明导电构件3243上,即增加第二导电垫312的膜层数目,以使第一导电垫311的膜层数目小于第二导电垫312的膜层数目。其中,导电构件325可以为透明导电层或者金属导电层。可以理解的是,也可以是第一导电垫311由第一金属构件3182以及第三金属构件3203组成,第二导电垫312由第二金属构件3183、第四金属构件3204以及第二透明导电构件3243组成,即减小第一导电垫311的膜层数目,以使第一导电垫311的膜层数目小于第二导电垫312的膜层数目。

图9所示显示面板通过在第二透明导电构件3243上增设导电构件325,以使得第二导电垫312与驱动芯片33结合的第二结合面312a更高,有利于第二导电垫312与驱动芯片33上翘起的第二引脚332之间绑定且电性连接。也可以通过减少第一导电垫311的膜层数目,以使得第二导电垫312与驱动芯片33结合的第二结合面312a结合。

请参阅图10,其为沿图2所示显示面板A-A切线的第六种截面示意图。图10所示显示面板与图3所示显示面板基本相似,不同之处在于,第一导电垫311包括第一导电膜,第二导电垫312包括第二导电膜,第二导电膜与第一导电膜同层设置,第一导电膜的厚度小于第二导电膜的厚度,且图10所示遮光层314不包括设置于焊盘区300b的遮光构件。

具体地,第一导电垫311由第一金属构件3182、第三金属构件3203以及第一透明导电构件3242组成,第二导电垫312由第二金属构件3183、第四金属构件3204以及第二透明导电构件3243组成,第一金属构件3182的厚度等于第二金属构件3183的厚度,第三金属构件3203的厚度小于第四金属构件3204的厚度,第一透明导电构件3242的厚度等于第二透明导电构件3243的厚度。可以理解的是,也可以第一金属构件3182的厚度小于第二金属构件3183的厚度,第三金属构件3203的厚度等于第四金属构件3204的厚度,第一透明导电构件3242的厚度等于第二透明导电构件3243的厚度。

图10所示显示面板通过使组成第一导电垫311的导电膜的厚度小于组成第二导电垫312的导电膜的厚度,以使得第二导电垫312的第二结合面312a至基板313的距离大于第一导电垫311的第一结合面311a至基板313的距离,有利于驱动芯片33上翘起的第二引脚332与第二导电垫312的第二结合面312a结合。

图9所示显示面板和图10所示显示面板通过调整第一导电垫311的膜层数目小于第二导电垫312的膜层数目,或者,调整第一导电垫311的导电膜层的厚度小于第二导电垫312的导电膜层的厚度,以使第一导电垫311的厚度小于第二导电垫312的厚度,进而使得第二导电垫312的第二结合面312a至基板的距离大于第一导电垫311的第一结合面311a至基板的距离,使得第二结合面312a与驱动芯片33上翘起的第二引脚332连接。

需要说明的是,图9所示第一导电垫311的膜层数目小于第二导电垫312的膜层数目,图10所示第一导电垫311的第一导电膜的厚度小于第二导电垫312的第二导电垫的厚度,图3、图6、图7中所示第一导电垫与基板之间的膜层数目小于第二导电垫与基板之间的膜层数目,以及图8所示第一导电垫311与基板313之间的第一膜层的厚度小于第二导电垫与基板之间与第一膜层同层的第二膜层的厚度可以相互组合,以使得第二导电垫312的第二结合面312a至基板的距离大于第一导电垫311的第一结合面311a的距离。

请参阅图11及图12,图11为本申请第二实施例显示面板的示意图,图12为沿图11所示显示面板的B-B切线的截面示意图。图11所示显示面板与图3所示显示面板基本相似,阵列基板31包括设置于基板313的承载面313a上的第一导电垫311、第二导电垫312、第三导电垫326以及冗余导电垫327,第一导电垫311、第二导电垫312、第三导电垫326以及冗余导电垫327均设置于焊盘区300b,第一导电垫311、第二导电垫312、第三导电垫326均会传输电信号,冗余导电垫327不会传输信号。多个冗余导电垫327沿第一方向呈直线形并排设置,多个第一导电垫311沿第一方向呈直线形并排设置,且多个冗余导电垫327位于第一导电垫311靠近显示区300a的一侧,多个第二导电垫312以及多个第三导电垫326设置于多个第一导电垫311远离显示区300a的一侧,多个第二导电垫312以及多个第三导电垫326沿第一方向呈直线形并排设置,且多个第二导电垫312在第一方向上对称地设置于多个第三导电垫326的相对两侧,一部分第一导电垫311与多个第二导电垫312在第二方向(显示区300a指向焊盘区300b的方向)上相邻设置且第一导电垫311与多个第二导电垫312在第二方向上错位设置,另一部分第一导电垫311与多个第三导电垫326与在第二方向上也相邻且错位设置,在第一方向上多个第二导电垫312位于多个冗余导电垫327的相对两侧,且部分第一导电垫311在第一方向上也位于多个冗余导电垫327的相对两侧。其中,第一导电垫311与上述图3中的第一导电垫相同,第二导电垫312与上述图3中的第二导电垫相同。第三导电垫326由第五金属构件3184、第七金属构件3205以及第三透明导电构件3244组成。冗余导电垫327由第六金属构件3185、第八金属构件3206以及第四透明导电构件3245组成。第一导电垫311具有第一结合面311a,第二导电垫312具有第二结合面312a,第三导电垫326具有第三结合面326a,第三结合面326a与承载面平行,第三结合面326a上设置有导电胶层,冗余导电垫327具有冗余结合面327a,冗余结合面327a与承载面313a平行,第一结合面311a与承载面313a平行的至少部分至基板313的距离小于第二结合面312a与承载面313a平行的至少部分至基板313的距离,第三结合面326a与承载面313a平行的至少部分至基板313的距离小于第二结合面312a与承载面313a平行的至少部分至基板313的距离,第三结合面326a与承载面313a平行的至少部分至基板313的距离等于第一结合面311a与承载面313a平行的至少部分至基板313的距离,冗余结合面327a与承载面313a平行的至少部分至基板313的距离等于第一结合面311a与承载面313a平行的至少部分至基板313的距离。

在本实施例中,驱动芯片33包括第一引脚331、第二引脚332、第三引脚333以及冗余引脚334。驱动芯片33具有第一边缘330a和第二边缘330b,第一边缘330a与第二边缘330b相对,驱动芯片33绑定于显示面板300上时,第一边缘330a靠近显示区300a,第二边缘330b远离显示区300a。冗余引脚334靠近第一边缘330a呈直线形并排设置使得多个冗余引脚334靠近显示区300a设置,冗余引脚334不会接入电信号。第一引脚331靠近第二边缘330b呈直线形并排设置,多个第二引脚332与多个第三引脚333位于多个第一引脚331远离显示区300a的一侧,多个第二引脚332在第一方向上设置于多个第三引脚333的相对两侧,部分第一引脚331在第二方向上与第二引脚332相邻错开设置且该部分第一引脚331在第一方向上位于多个冗余引脚334的相对两侧,另一部分第一引脚331在第二方向上与多个第三引脚333相邻错开设置,且多个第二引脚332在第一方向上对称地位于多个冗余引脚334的相对两侧,第一引脚331的厚度、第二引脚332的厚度、第三引脚333的厚度以及冗余引脚334的厚度均相等。

驱动芯片33绑定于显示面板300上时,多个冗余引脚334与多个冗余导电垫327一对一设置且连接,多个第一引脚331与多个第一导电垫311一对一设置且电性连接,多个第三引脚333与多个第三导电垫326一对一设置且第三结合面326a与第三引脚333之间填充有导电胶层,由于多个冗余导电垫327的相对两侧的布线区域300b1设置有多个布线,导致布线区域300b1没有设置冗余导电垫327,驱动芯片33在布线区域300b1无支撑而下倾,对应地,驱动芯片33的多个第二引脚332翘起,多个翘起的第二引脚332与垫高的第二导电垫312的第二结合面312a通过填充于两者之间的第二导电胶层402结合且第二引脚332与第二导电垫312电性连接,进而使得多个第二引脚332能绑定于阵列基板上且第二引脚332与对应的第二导电垫312电性连接。

在本实施例中,由于多个第二引脚332在第一方向上位于多个冗余电垫327的相对两侧而受到冗余电垫327的支撑力不同,多个第二引脚332翘起的程度也不同,第二引脚332距离冗余导电垫327越远则获得的支撑力越小,第二引脚332翘起越高,多个第二导电垫312的第二结合面312a与承载面313a平行的至少部分至基板313的距离从靠近第三导电垫326至远离第三导电垫326而递增,以适应驱动芯片33绑定于阵列基板上时,翘起的第二引脚332至基板313的距离从靠近第三导电垫326至远离第三导电垫326递增。

需要说明的是,第一导电垫311的第一结合面311a与承载面平行的至少部分至基板的距离小于第二导电垫312的第二结合面312a与承载面平行的至少部分至基板的距离可以通过前述方法实现,此处不做详述。

请参阅图13及图14,图13为本申请第三实施例显示面板的示意图,图14为沿图13所示显示面板的C-C切线的截面示意图。图13所示显示面板与图12所示显示面板基本相似,不同之处包括,阵列基板31还包括至少两排第四导电垫328和至少一排第五导电垫329,至少两排第四导电垫328位于至少一排第五导电垫329远离显示区300a的一侧,至少两排第四导电垫328和至少一排第五导电垫329沿第二方向设置且在第二方向上位于冗余导电垫327远离显示区300a的一侧,至少两排第四导电垫328在第一方向上位于第二导电垫312的相对两侧,故至少两排第四导电垫328在第一方向上也位于冗余导电垫327的相对两侧,至少一排第五导电垫329在第一方向上位于第一导电垫311的相对两侧,故至少一排第五导电垫329在第一方向上也位于冗余导电垫327的相对两侧,每个第四导电垫328具有第四结合面328a,第四结合面328a与承载面313a平行,每个第五导电垫329具有第五结合面329a,第五结合面329a与承载面313a平行;驱动芯片33还包括至少两排第四引脚335以及至少一排第五引脚336,至少两排第四引脚335位于至少一排第五引脚336远离显示区的一侧,至少两排第四引脚335与至少一排第五引脚336沿第二方向设置且在第二方向上位于冗余引脚334远离显示区300a的一侧,至少两排第四引脚335与至少两排第四导电垫328一一对应设置且电性连接,至少一排第五引脚336与至少一排第五导电垫329一一对应设置且电性连接,第四结合面328a与第四引脚335相对且两者之间填充有导电胶层,第五结合面329a与第五引脚336相对且两者之间填充有导电胶层,第五导电垫329的第五结合面329a与承载面313a平行的至少部分至基板313的距离小于靠近第五导电垫329的第四导电垫328的第四结合面328a与承载面313a平行的至少部分至基板313的距离,第五导电垫329的第五结合面329a与承载面313a平行的至少部分至基板313的距离等于第一导电垫311的第一结合面311a与承载面平行的至少部分至基板的距离,至少两排第四导电垫328的第四结合面328a与承载面313a平行的至少部分至基板313的距离从靠近显示区300a至远离显示区300a递增,以适应与第四导电垫328对应的第四引脚335从靠近显示区300a至远离显示区300a的翘起程度递增。

具体地,每个第四导电垫328由第九金属构件3186、第十金属构件3207以及第五透明导电构件3246组成,多个第四导电垫328的第九金属构件3186的厚度相同,多个第四导电垫328的第五透明导电构件3246的厚度相同,至少两排第四导电垫328的第十金属构件3207的厚度从靠近显示区300a至远离显示区300a递增,进而使得至少两排第四导电垫328的第四结合面328a与承载面313a平行的至少部分至基板313的距离在第二方向上从靠近显示区300a至远离显示区300a递增。

需要说明的是,在第二方向上,多个冗余导电垫的相对两侧为未设置冗余导电垫的空白区域,驱动芯片33绑定阵列基板上时,驱动芯片33在空白区域处无支撑而下倾,导致距离显示区300a越远的第四引脚335翘起越高,对应地,需要与第四引脚335对应的第四导电垫328的第四结合面328a越高。在第一方向上,由于多个第四导电垫328在第一方向上位于多个冗余导电垫327的相对两侧,多个第四导电垫328距离冗余导电垫327越远,则第四导电垫328得到冗余导电垫327支撑越小,则驱动芯片上的第四引脚335翘起得越高,在第一方向上,至少两排第四导电垫328的第四结合面328a与承载面313a平行的至少部分至基板313的距离从靠近第二导电垫312至远离第二导电垫312而递增,与第二导电垫312相邻的第四导电垫328的第四结合面328a与承载面313a平行的至少部分至基板313的距离大于与第四导电垫328相邻的第二导电垫312的第二结合面312a与承载面313a平行的至少部分至基板313的距离。

请参阅图15,其为本申请第四实施例显示面板的示意图。图15所示显示面板与图2所示显示面板基本相似,显示面板300包括多个第一导电垫311、多个第二导电垫312以及多个第三导电垫326,多个第三导电垫326呈两排设置,两排第一导电垫311在第一方向上分别倾斜地设置于两排第三导电垫326的相对两侧,且两排第二导电垫312在第一方向上倾斜地分别设置于两排第三导电垫326的相对两侧,两排第二导电垫312在第二方向上分别位于两排第一导电垫311远离显示区300a的一侧,一排第一导电垫311与一排第二导电垫312相邻且平行设置,一排第一导电垫311所在直线与一排第三导电垫326所在直线之间的夹角大于0且小于90度;驱动芯片33包括与第一导电垫311一一对应的第一引脚331、与第二导电垫312一一对应的第二引脚332以及与第三导电垫326一一对应的第三引脚333,多个第三引脚333在第二方向上呈两排设置于驱动芯片33的中间位置,且多个第一引脚331分为两排分别倾斜地设置于两排第三引脚333的相对两侧,多个第二引脚332分为两排分别倾斜地设置于两排第三引脚333的相对两侧,两排第一引脚331和两排第二引脚332靠近驱动芯片33的第二边缘330b设置。图15所示第一导电垫311的组成和第二导电垫312的组成分别与图2所示第一导电垫311的组成和第二导电垫312的组成相同,此处不做详述,图15所示第三导电垫326的组成与图15所示第一导电垫311的组成相同。

具体地,由于驱动芯片33绑定于显示面板300上时,驱动芯片33靠近显示区300a的一端无支撑,驱动芯片33的多个第一引脚331绑定于第一导电垫311上且第三引脚333绑定于第三导电垫326上时,驱动芯片33靠近显示区300a的一端下倾,且驱动芯片33的多个第二引脚332会翘起,第一导电垫311的第一结合面311a与承载面313a平行的至少部分至基板313的距离小于第二导电垫312的第二结合面312a与承载面313a平行的至少部分至基板313的距离,以使得驱动芯片33上翘起的第二引脚332与对应垫高的第二导电垫312的第二结合面312a结合。

请参阅图16,其为本申请第五实施例显示面板的示意图。图16所示显示面板与图15所示显示面板基本相似,不同之处在于,阵列基板31还包括多个冗余导电垫327,冗余导电垫327在第二方向上设置于第一导电垫311靠近显示区300a的一侧,至少两排第一导电垫311在第一方向上分别位于多个冗余导电垫327和两排第三导电垫326的相对两侧,至少两排第二导电垫312在第一方向上位于多个冗余导电垫327和两排第三导电垫326的相对两侧,至少两排第二导电垫312位于至少两排第一导电垫311远离显示区300a的一侧,至少两排第二导电垫312与至少两排第一导电垫311均倾斜设置且相互平行;驱动芯片33还包括多个冗余引脚334,冗余引脚334设置于第三引脚333靠近第一边缘330a的位置,至少两排第一引脚331在第一方向上位于多个冗余引脚334和两排第三引脚333的相对两侧,至少两排第二引脚332在第一方向上位于多个冗余引脚334和两排第三引脚333的相对两侧,至少两排第二引脚332位于至少两排第一引脚331远离显示区的一侧,至少两排第二引脚332与至少两排第二引脚332均倾斜设置且相互平行。

驱动芯片33绑定于阵列基板31上时,第三导电垫326与第三引脚通过导电胶层电性连接,第一导电垫311与第一引脚331之间通过第一导电胶层一对一电性连接,第二导电垫312与第二引脚332之间通过第二导电胶层一对一电性连接,冗余导电垫327与冗余引脚334一对一设置且连接,至少两排第二导电垫312中的第二导电垫312的第二结合面312a与承载面平行的至少部分至基板313的距离从靠近显示区300a至远离显示区300a递增,以适应驱动芯片33绑定于阵列基板上时第二引脚332从靠近显示区300a至远离显示区300a的翘起程度增加的情况。

请参阅图17,其为本申请第六实施例显示面板的局部截面示意图。图17所示显示面板与图4所示显示面板基本相似,不同之处在于,第一导电垫311与第二导电垫312的组成相同且两者的厚度相同,第一引脚331的厚度小于第二引脚332的厚度,以使得翘起的第二引脚332能与第二导电垫312之间实现电性连接,保证驱动芯片33绑定于阵列基板31上。

本实施例通过使第一引脚的厚度与第二引脚的厚度不同,以使补偿第一引脚和第二引脚中翘起的一者与基板之间距离,保证第一引脚和第二引脚中翘起的一者能绑定于阵列基板上且与对应的导电垫电性连接。

需要说明的是,本实施例控制驱动芯片上的引脚的厚度差异化与图3-图16控制阵列基板上导电垫的结合面的高度差异化可以结合使用,以保证驱动芯片上翘起的引脚均能与阵列基板上对应的导电垫电性连接。

本申请还提供一种显示装置,显示装置包括上述任意一种显示面板和背光模组,显示面板位于背光模组的出光侧。

以上实施例的说明只是用于帮助理解本申请的技术方案及其核心思想;本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本申请各实施例的技术方案的范围。

Claims (20)

1.一种显示面板,其特征在于,所述显示面板具有显示区和焊盘区,所述焊盘区位于所述显示区的一侧,所述显示面板包括:

基板,具有承载面;

第一导电垫,设置于所述基板的所述承载面上,且位于所述焊盘区;

第二导电垫,设置于所述基板的所述承载面上,且位于所述焊盘区,所述第二导电垫位于所述第一导电垫远离所述显示区的一侧;

驱动芯片,绑定于所述焊盘区,所述驱动芯片包括:

第一引脚,与所述第一导电垫对应设置;以及

第二引脚,与所述第二导电垫对应设置,所述第二引脚位于所述第一引脚远离所述显示区的一侧;

第一导电胶层,填充于所述第一导电垫与所述第一引脚之间,且电性连接所述第一导电垫与所述第一引脚;以及

第二导电胶层,填充于所述第二导电垫与所述第二引脚之间,且电性连接所述第二导电垫与所述第二引脚;

其中,所述第一导电胶层靠近所述第一引脚的表面至所述基板的距离与所述第二导电胶层靠近所述第二引脚的表面至所述基板的距离不同;

其中,所述第一导电垫具有与所述承载面至少部分平行且与所述第一导电胶层接触的第一结合面,所述第二导电垫具有与所述承载面至少部分平行且与所述第二导电胶层接触的第二结合面,所述第一结合面与所述承载面平行的至少部分至所述基板的距离小于所述第二结合面与所述承载面平行的至少部分至所述基板的距离。

2.根据权利要求1所述的显示面板,其特征在于,所述第一导电垫用于传输电信号,所述第二导电垫用于输出电信号。

3.根据权利要求1所述的显示面板,其特征在于,所述驱动芯片靠近所述显示区的一端向靠近所述基板的方向倾斜,所述驱动芯片远离所述显示区的一端向远离所述基板的方向倾斜。

4.根据权利要求1所述的显示面板,其特征在于,所述第一导电垫的厚度小于所述第二导电垫的厚度。

5.根据权利要求4所述的显示面板,其特征在于,组成所述第一导电垫的膜层数目小于组成所述第二导电垫的膜层数目。

6.根据权利要求4所述的显示面板,其特征在于,所述第一导电垫包括第一导电膜,所述第二导电垫包括与所述第一导电膜同层设置的第二导电膜,所述第一导电膜的厚度小于所述第二导电膜的厚度。

7.根据权利要求1所述的显示面板,其特征在于,所述第一导电垫的厚度等于所述第二导电垫的厚度。

8.根据权利要求1、4或7所述的显示面板,其特征在于,在所述显示面板的厚度方向上,所述第一导电垫与所述基板之间的膜层数目小于所述第二导电垫与所述基板之间的膜层数目。

9.根据权利要求1、4或7所述的显示面板,其特征在于,在所述显示面板的厚度方向上,所述第一导电垫与所述基板之间设置有第一膜层,所述第二导电垫与所述基板之间设置有第二膜层,所述第一膜层位于焊盘区且对应所述第一导电垫设置,所述第二膜层位于焊盘区且对应所述第二导电垫设置,所述第一膜层与所述第二膜层同层设置且所述第一膜层的厚度小于所述第二膜层的厚度。

10.根据权利要求1所述的显示面板,其特征在于,所述显示面板包括多个所述第二导电垫,所述显示面板还包括:

多个冗余导电垫,设置于所述基板的所述承载面上,且位于所述焊盘区,多个所述冗余导电垫位于所述第一导电垫靠近所述显示区的一侧,且多个所述第二导电垫在垂直于所述显示区指向所述焊盘区的方向上位于多个所述冗余导电垫的相对两侧;

所述驱动芯片包括多个所述第二引脚,所述驱动芯片还包括:

多个冗余引脚,与多个所述冗余导电垫一一对应设置,位于所述第一引脚靠近所述显示区的一侧,且多个所述第二引脚在垂直于所述显示区指向所述焊盘区的方向上位于多个所述冗余引脚的相对两侧。

11.根据权利要求10所述的显示面板,其特征在于,所述第一引脚的厚度小于或等于所述第二引脚的厚度。

12.根据权利要求10所述的显示面板,其特征在于,所述第一导电垫为多个,所述显示面板还包括:

第三导电垫,设置于所述焊盘区,在所述显示区指向所述焊盘区的方向上位于多个所述第一导电垫远离所述显示区的一侧且与部分所述第一导电垫相邻且错开设置,且所述第三导电垫具有与所述承载面至少部分平行的第三结合面,多个所述第二导电垫在垂直于所述显示区指向所述焊盘区的方向上位于所述第三导电垫的相对两侧;

所述第一引脚为多个,所述驱动芯片还包括:

第三引脚,与所述第三导电垫一一对应设置且电性连接,在所述显示区指向所述焊盘区的方向上位于所述第一引脚远离所述显示区的一侧且与部分所述第一引脚相邻且错开设置,多个所述第二引脚在垂直于所述显示区指向所述焊盘区的方向上位于所述第三引脚的相对两侧;

其中,所述第三结合面与所述第三引脚之间填充有导电胶层,且所述第三结合面与所述承载面平行的至少部分至所述基板的距离小于所述第二结合面与所述承载面平行的至少部分至所述基板的距离。

13.根据权利要求12所述的显示面板,其特征在于,多个所述第二导电垫的所述第二结合面与所述承载面平行的至少部分至所述基板的距离沿从靠近所述第三导电垫至远离所述第三导电垫的方向而递增。

14.根据权利要求12所述的显示面板,其特征在于,所述第三结合面与所述承载面平行的至少部分至所述基板的距离等于所述第一结合面与所述承载面平行的至少部分至所述基板的距离。

15.根据权利要求1或10所述的显示面板,其特征在于,所述显示面板还包括:

至少两排设置于所述焊盘区的第四导电垫,至少两排第四导电垫位于所述第一导电垫远离所述显示区的一侧,至少两排第四导电垫在垂直于显示区指向焊盘区的方向上位于所述第二导电垫的相对两侧,每排所述第四导电垫包括至少两个并排设置的所述第四导电垫,至少两排所述第四导电垫沿所述显示区指向所述焊盘区的方向排布,每个所述第四导电垫具有第四结合面;

所述驱动芯片还包括:

至少两排第四引脚,与至少两排所述第四导电垫一一对应设置且电性连接,位于所述第一引脚远离所述显示区的一侧,且在垂直于显示区指向焊盘区的方向上位于所述第二引脚的相对两侧;

其中,所述第四结合面与所述第四引脚之间填充有导电胶层,至少两排所述第四导电垫的所述第四结合面与所述承载面平行的至少部分至所述基板的距离在所述显示区指向所述焊盘区的方向上从靠近显示区至远离所述显示区递增。

16.根据权利要求15所述的显示面板,其特征在于,在垂直于所述显示区指向所述焊盘区的方向上,至少两排所述第四导电垫的所述第四结合面与所述承载面平行的至少部分至所述基板的距离从靠近第二导电垫至远离所述第二导电垫递增。

17.根据权利要求1、3或4所述的显示面板,其特征在于,所述第二导电垫位于所述第一导电垫远离所述显示区的一侧,所述第一导电胶层与所述第二导电胶层连接且所述第一导电胶层与所述第二导电胶层之间电性绝缘,所述第一导电胶层的厚度小于所述第二导电胶层的厚度。

18.根据权利要求1所述的显示面板,其特征在于,所述显示面板还包括:

柔性印刷电路板,包括第一绑定部、第二绑定部以及主体部,所述第一绑定部与所述第二绑定部均与所述主体部连接,所述第一绑定部和所述第二绑定部均绑定于所述焊盘区且在垂直于所述显示区指向焊盘区的方向上位于所述驱动芯片的相对两侧。

19.根据权利要求1或18所述的显示面板,其特征在于,所述第一引脚和所述第二引脚均为多个,多个所述第一引脚和多个所述第二引脚设置在所述驱动芯片远离所述显示区的一侧,所述驱动芯片还包括设置在靠近所述显示区的多个冗余引脚,在所述显示区指向所述焊盘区的方向上多个所述第二引脚位于多个所述第一引脚远离多个所述冗余引脚的一侧且至少部分所述第一引脚与多个所述第二引脚相邻设置;

在垂直于所述显示区指向所述焊盘区的方向上,至少部分所述第一引脚分别位于多个所述冗余引脚的相对两侧,且多个所述第二引脚均分别位于多个所述冗余引脚的相对两侧。

20.一种显示装置,其特征在于,所述显示装置包括如权利要求1-19任一项所述的显示面板。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202111164181.8A CN113917747B (zh) | 2021-09-30 | 2021-09-30 | 显示面板及显示装置 |

| US17/613,509 US20240251610A1 (en) | 2021-09-30 | 2021-10-12 | Display panel and display device |

| PCT/CN2021/123357 WO2023050474A1 (zh) | 2021-09-30 | 2021-10-12 | 显示面板及显示装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202111164181.8A CN113917747B (zh) | 2021-09-30 | 2021-09-30 | 显示面板及显示装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN113917747A CN113917747A (zh) | 2022-01-11 |

| CN113917747B true CN113917747B (zh) | 2022-11-01 |

Family

ID=79237728

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN202111164181.8A Active CN113917747B (zh) | 2021-09-30 | 2021-09-30 | 显示面板及显示装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US20240251610A1 (zh) |

| CN (1) | CN113917747B (zh) |

| WO (1) | WO2023050474A1 (zh) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20230217591A1 (en) * | 2022-01-03 | 2023-07-06 | Mediatek Inc. | Board-level pad pattern for multi-row qfn packages |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009217116A (ja) * | 2008-03-12 | 2009-09-24 | Hitachi Displays Ltd | 液晶表示装置 |

| KR102535557B1 (ko) * | 2016-03-07 | 2023-05-24 | 삼성디스플레이 주식회사 | 표시 장치 및 전자 디바이스 |

| CN107422551A (zh) * | 2017-07-25 | 2017-12-01 | 武汉天马微电子有限公司 | 一种显示装置 |

| CN107329297A (zh) * | 2017-08-30 | 2017-11-07 | 上海中航光电子有限公司 | 显示面板的绑定结构和显示面板 |

| CN107749239B (zh) * | 2017-10-31 | 2020-08-25 | 武汉天马微电子有限公司 | 显示面板、显示装置及显示面板的制作方法 |

| JP2019095694A (ja) * | 2017-11-27 | 2019-06-20 | 株式会社ジャパンディスプレイ | 表示装置 |

| CN109036155A (zh) * | 2018-07-26 | 2018-12-18 | 武汉华星光电技术有限公司 | 显示面板及显示装置 |

| CN111681538A (zh) * | 2020-06-24 | 2020-09-18 | 武汉华星光电技术有限公司 | 显示面板及显示装置 |

| CN111665658B (zh) * | 2020-06-29 | 2022-08-30 | 厦门天马微电子有限公司 | 阵列基板、显示基板及显示装置 |

| CN111883039B (zh) * | 2020-07-31 | 2023-05-30 | 厦门天马微电子有限公司 | 一种驱动芯片及显示装置 |

| CN112037649A (zh) * | 2020-08-12 | 2020-12-04 | 上海中航光电子有限公司 | 显示面板和显示装置 |

| CN114035388B (zh) * | 2021-11-30 | 2022-07-08 | 绵阳惠科光电科技有限公司 | 阵列基板和显示装置 |

-

2021

- 2021-09-30 CN CN202111164181.8A patent/CN113917747B/zh active Active

- 2021-10-12 WO PCT/CN2021/123357 patent/WO2023050474A1/zh active Application Filing

- 2021-10-12 US US17/613,509 patent/US20240251610A1/en active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| CN113917747A (zh) | 2022-01-11 |

| WO2023050474A1 (zh) | 2023-04-06 |

| US20240251610A1 (en) | 2024-07-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102673523B1 (ko) | 전자 부품 및 이를 포함하는 전자 장치 | |

| CN110349979B (zh) | 柔性显示器 | |

| US9113545B2 (en) | Tape wiring substrate and chip-on-film package including the same | |

| KR102655727B1 (ko) | 표시 장치 및 표시 장치 제조 방법 | |

| JP6806431B2 (ja) | 表示装置 | |

| US7916262B2 (en) | Signal transmission assembly and display device applied with the same | |

| KR20160035696A (ko) | 곡면형 표시 장치 | |

| TWI671572B (zh) | 顯示面板及其製造方法 | |

| US20130335940A1 (en) | Electronic circuit substrate, display device, and wiring substrate | |

| CN113193017B (zh) | 显示面板和显示装置 | |

| US20200295113A1 (en) | Display device | |

| US20240312934A1 (en) | Display panel and display device | |

| CN113917747B (zh) | 显示面板及显示装置 | |

| CN108845465B (zh) | 显示面板扇出走线结构及其制作方法 | |

| CN113823183A (zh) | 显示面板及显示装置 | |

| US11790839B2 (en) | Electronic device | |

| CN102394231A (zh) | 一种用于液晶显示器的芯片接合结构 | |

| US20240096264A1 (en) | Splicing screen | |

| US20230317903A1 (en) | Display device, method of manufacturing the same, and tiled display device including the same | |

| KR101814598B1 (ko) | 디스플레이 패널 및 이를 포함하는 디스플레이 장치 | |

| TWI390691B (zh) | 銲墊、晶片-基板接合之封裝構造及液晶顯示面板 | |

| WO2023141863A1 (zh) | 显示基板及显示面板 | |

| KR20240099670A (ko) | 칩 온 필름 패키지 및 이를 포함하는 디스플레이 장치 | |

| CN117855220A (zh) | 显示装置 | |

| CN115206993A (zh) | 一种显示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant |