CN112397621A - Epitaxial wafer of ultraviolet light-emitting diode and preparation method thereof - Google Patents

Epitaxial wafer of ultraviolet light-emitting diode and preparation method thereof Download PDFInfo

- Publication number

- CN112397621A CN112397621A CN202011189257.8A CN202011189257A CN112397621A CN 112397621 A CN112397621 A CN 112397621A CN 202011189257 A CN202011189257 A CN 202011189257A CN 112397621 A CN112397621 A CN 112397621A

- Authority

- CN

- China

- Prior art keywords

- layer

- epitaxial

- substrate

- type

- epitaxial wafer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 238000002360 preparation method Methods 0.000 title claims abstract description 8

- 229910002704 AlGaN Inorganic materials 0.000 claims abstract description 79

- 239000000758 substrate Substances 0.000 claims abstract description 39

- 230000008021 deposition Effects 0.000 claims abstract description 32

- 230000004888 barrier function Effects 0.000 claims abstract description 13

- 238000000151 deposition Methods 0.000 claims description 48

- 230000000903 blocking effect Effects 0.000 claims description 28

- 238000005530 etching Methods 0.000 claims description 21

- 239000002019 doping agent Substances 0.000 claims description 13

- 238000000034 method Methods 0.000 claims description 11

- 239000011777 magnesium Substances 0.000 description 11

- 238000010586 diagram Methods 0.000 description 8

- 238000000137 annealing Methods 0.000 description 5

- 239000013078 crystal Substances 0.000 description 5

- 230000005540 biological transmission Effects 0.000 description 4

- 238000004519 manufacturing process Methods 0.000 description 4

- 229920002120 photoresistant polymer Polymers 0.000 description 4

- 239000002131 composite material Substances 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- 238000000605 extraction Methods 0.000 description 3

- 238000004020 luminiscence type Methods 0.000 description 3

- 230000006798 recombination Effects 0.000 description 3

- 238000005215 recombination Methods 0.000 description 3

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 2

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 2

- 238000011049 filling Methods 0.000 description 2

- 238000009616 inductively coupled plasma Methods 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 238000005240 physical vapour deposition Methods 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 238000002310 reflectometry Methods 0.000 description 2

- 229910052594 sapphire Inorganic materials 0.000 description 2

- 239000010980 sapphire Substances 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- 239000000243 solution Substances 0.000 description 2

- RGGPNXQUMRMPRA-UHFFFAOYSA-N triethylgallium Chemical compound CC[Ga](CC)CC RGGPNXQUMRMPRA-UHFFFAOYSA-N 0.000 description 2

- JLTRXTDYQLMHGR-UHFFFAOYSA-N trimethylaluminium Chemical compound C[Al](C)C JLTRXTDYQLMHGR-UHFFFAOYSA-N 0.000 description 2

- XCZXGTMEAKBVPV-UHFFFAOYSA-N trimethylgallium Chemical compound C[Ga](C)C XCZXGTMEAKBVPV-UHFFFAOYSA-N 0.000 description 2

- 238000009966 trimming Methods 0.000 description 2

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 230000009286 beneficial effect Effects 0.000 description 1

- 239000012159 carrier gas Substances 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 239000013256 coordination polymer Substances 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 238000011065 in-situ storage Methods 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 229910052749 magnesium Inorganic materials 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/10—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a light reflecting structure, e.g. semiconductor Bragg reflector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/005—Processes

- H01L33/0062—Processes for devices with an active region comprising only III-V compounds

- H01L33/0066—Processes for devices with an active region comprising only III-V compounds with a substrate not being a III-V compound

- H01L33/007—Processes for devices with an active region comprising only III-V compounds with a substrate not being a III-V compound comprising nitride compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/20—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a particular shape, e.g. curved or truncated substrate

- H01L33/22—Roughened surfaces, e.g. at the interface between epitaxial layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/44—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the coatings, e.g. passivation layer or anti-reflective coating

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Led Devices (AREA)

Abstract

The disclosure provides an epitaxial wafer of an ultraviolet light-emitting diode and a preparation method thereof, belonging to the field of light-emitting diodes. The epitaxial wafer includes: the epitaxial layer comprises a buffer layer, an undoped AlGaN layer, an N-type AlGaN layer, a multi-quantum well layer, an electron barrier layer and a P-type AlGaN layer which are sequentially stacked on the substrate, the epitaxial layer further comprises a reflecting layer positioned between the electron barrier layer and the P-type AlGaN layer, the reflecting layer is composed of a plurality of staggered lugs, the protruding direction of the lugs is the same as the deposition direction of the epitaxial layer, and the area of the cross section of the lugs is gradually reduced along the deposition direction of the epitaxial layer. The light emitting efficiency can be greatly improved.

Description

Technical Field

The disclosure relates to the field of light emitting diodes, and in particular relates to an epitaxial wafer of an ultraviolet light emitting diode and a preparation method thereof.

Background

In recent years, many researchers have developed AlGaN-based high-brightness ultraviolet light emitting diodes. The basic structure of an epitaxial wafer of an AlGaN-based ultraviolet light emitting diode is generally a substrate, and a buffer layer, an n-type doping layer, a multiple quantum well layer, an electron blocking layer, and a p-type layer deposited on the substrate.

When light reaches the surface critical from the active region (multiple quantum well layer), the light is absorbed from the side or by the substrate due to the total reflection, so that the light-emitting efficiency is low, and the external quantum efficiency is influenced. Therefore, how to improve the light emitting efficiency of the ultraviolet light emitting diode becomes a hot spot of industrial research. The related technology provides an epitaxial wafer of an ultraviolet light emitting diode for improving the light emitting efficiency, wherein an Al film is mainly arranged between a substrate and a buffer layer, and the Al film has high reflectivity of nearly 90% in the whole ultraviolet band, so that the ultraviolet light generated by a multi-quantum well layer can be reflected to the part of the substrate.

In implementing the present disclosure, the inventors found that the related art has at least the following problems: firstly, the Al film only reflects the ultraviolet light emitted to the substrate, but cannot reflect the ultraviolet light emitted to the side surface; and secondly, the reflected ultraviolet light needs to pass through the whole epitaxial layer and exit towards the light-emitting surface, so that most of the reflected ultraviolet light is absorbed by the whole epitaxial layer again, and the reflectivity is reduced.

Disclosure of Invention

The embodiment of the disclosure provides an epitaxial wafer of an ultraviolet light emitting diode and a preparation method thereof, which can greatly improve the light extraction efficiency. The technical scheme is as follows:

in one aspect, an epitaxial wafer of an ultraviolet light emitting diode is provided, the epitaxial wafer comprising: a substrate and an epitaxial layer deposited on the substrate, the epitaxial layer including a buffer layer, an undoped AlGaN layer, an N-type AlGaN layer, a multi-quantum well layer, an electron blocking layer, and a P-type AlGaN layer sequentially stacked on the substrate,

the epitaxial layer further comprises a reflecting layer located between the electronic barrier layer and the P-type AlGaN layer, the reflecting layer is composed of a plurality of staggered lugs, the protruding direction of the lugs is the same as the deposition direction of the epitaxial layer, and the area of the cross section of each lug is gradually reduced along the deposition direction of the epitaxial layer.

Optionally, the bump is a cone.

Optionally, the reflective layer is an undoped GaN layer or an undoped AlGaN layer.

Optionally, the reflective layer is a P-type doped GaN layer.

Optionally, the P-type dopant of the reflective layer is Mg with a doping concentration of 1017cm-3-1018cm-3。

Optionally, the reflective layer has a thickness of 50nm to 100 nm.

In another aspect, a method for preparing an epitaxial wafer of an ultraviolet light emitting diode is provided, the method comprising:

providing a substrate;

depositing an epitaxial layer on the substrate, wherein the epitaxial layer comprises a buffer layer, an undoped AlGaN layer, an N-type AlGaN layer, a multi-quantum well layer and an electron barrier layer which are sequentially stacked on the substrate;

depositing a reflective layer on the electron blocking layer;

etching the reflecting layer, wherein the etched reflecting layer consists of a plurality of staggered lugs, the protruding direction of the lugs is the same as the deposition direction of the epitaxial layer, and the area of the cross section of the lugs is gradually reduced along the deposition direction of the epitaxial layer;

and depositing a P-type AlGaN layer on the etched reflecting layer.

Optionally, the reflective layer is a P-type doped GaN layer,

the depositing a reflective layer on the electron blocking layer includes:

and growing a P-type doped GaN layer on the electron blocking layer by taking 950-1050 ℃ as a growth temperature and 100-600 Torr as a growth pressure.

Optionally, the P-type dopant of the reflective layer is Mg with a doping concentration of 1017cm-3-1018cm-3。

Optionally, the etching the reflective layer includes:

growing a patterned mask on the reflecting layer, wherein the patterned mask is used for indicating the positions of the bumps;

etching the part, which is not covered by the graphical mask, on the reflecting layer;

and removing the patterned mask.

The technical scheme provided by the embodiment of the disclosure has the following beneficial effects:

the reflecting layer is arranged between the electron blocking layer and the P-type AlGaN layer in the epitaxial wafer of the ultraviolet light-emitting diode and consists of a plurality of bumps which are arranged in a staggered mode, the protruding direction of each bump is the same as the deposition direction of the epitaxial layer, and the area of the cross section of each bump is gradually reduced along the deposition direction of the epitaxial layer, so that each bump is provided with a side face which is inclined relative to the deposition direction; therefore, the reflecting layer with the bumps can increase the escape probability of light and improve the light-emitting efficiency.

Drawings

In order to more clearly illustrate the technical solutions in the embodiments of the present disclosure, the drawings needed to be used in the description of the embodiments are briefly introduced below, and it is obvious that the drawings in the following description are only some embodiments of the present disclosure, and it is obvious for those skilled in the art to obtain other drawings based on the drawings without creative efforts.

Fig. 1 is a schematic structural diagram of an epitaxial wafer of an ultraviolet light emitting diode provided in an embodiment of the present disclosure;

fig. 2 is a schematic diagram of a light transmission route of an ultraviolet light emitting diode provided by an embodiment of the present disclosure when no reflective layer is disposed;

fig. 3 is a schematic diagram of a light transmission route of the ultraviolet light emitting diode provided by the embodiment of the disclosure after a reflective layer is disposed;

fig. 4 is a schematic diagram of threading dislocation of an ultraviolet light emitting diode provided by an embodiment of the present disclosure after a reflective layer is disposed;

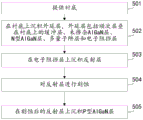

fig. 5 is a flowchart of a method for manufacturing an epitaxial wafer of an ultraviolet light emitting diode according to an embodiment of the present disclosure;

fig. 6 is a flowchart of a method for manufacturing an epitaxial wafer of an ultraviolet light emitting diode according to an embodiment of the present disclosure.

Detailed Description

To make the objects, technical solutions and advantages of the present disclosure more apparent, embodiments of the present disclosure will be described in detail with reference to the accompanying drawings.

Fig. 1 is a schematic structural diagram of an epitaxial wafer of an ultraviolet light emitting diode provided by an embodiment of the present disclosure, and referring to fig. 1, the epitaxial wafer includes: the epitaxial layer comprises a substrate 1 and an epitaxial layer deposited on the substrate 1, wherein the epitaxial layer comprises a buffer layer 2, an undoped AlGaN layer 3, an N-type AlGaN layer 4, a multi-quantum well layer 5, an electron barrier layer 6 and a P-type AlGaN layer 8 which are sequentially laminated on the substrate.

The epitaxial layer further comprises a reflecting layer 7 positioned between the electron blocking layer 6 and the P-type AlGaN layer 8, the reflecting layer 7 is composed of a plurality of staggered bumps 71, the protruding direction of the bumps 71 is the same as the deposition direction of the epitaxial layer, and the area of the cross section of each bump 71 is gradually reduced along the deposition direction of the epitaxial layer.

Referring to fig. 1, the direction of deposition of the epitaxial layer is shown by the arrows. When the protruding direction of the bump 71 is the same as the deposition direction of the epitaxial layer and the area of the cross section of the bump 71 is gradually reduced in the deposition direction of the epitaxial layer, the bump 71 has a side surface inclined with respect to the deposition direction.

In the embodiment of the disclosure, a reflecting layer located between an electron blocking layer and a P-type AlGaN layer is arranged in an epitaxial wafer of an ultraviolet light emitting diode, the reflecting layer is composed of a plurality of bumps which are arranged in a staggered manner, the protruding direction of the bumps is the same as the deposition direction of the epitaxial layer, and the area of the cross section of the bumps is gradually reduced along the deposition direction of the epitaxial layer, so that the bumps have side surfaces which are inclined relative to the deposition direction, when electrons and holes are subjected to composite luminescence in a quantum well, and upward-emitted light reaches the surface of the epitaxial layer critically, the light may be reflected or totally reflected due to the larger refractive index difference between the epitaxial layer and air, and the reflected light is reflected upward again by the inclined side surfaces of the bumps when reaching the reflecting layer with the bumps, and the light reflected upward again is also partially reflected out of the epitaxial layer, and partially; therefore, the reflecting layer with the bumps can increase the escape probability of light and improve the light-emitting efficiency.

Meanwhile, the substrate and the epitaxial layer generate threading dislocation due to lattice mismatch, the threading dislocation grows along with the growth of the epitaxial layer, the surface of a bump in the reflecting layer is usually formed by etching and is rough, and partial threading dislocation can be annihilated on the inclined side face, so that the threading dislocation continuously growing longitudinally is reduced, the diffusion of current is facilitated, and the forward working voltage is reduced.

Fig. 2 is a schematic diagram of a light transmission route when the ultraviolet light emitting diode provided by the embodiment of the present disclosure is not provided with a reflective layer, and fig. 3 is a schematic diagram of a light transmission route after the ultraviolet light emitting diode provided by the embodiment of the present disclosure is provided with a reflective layer.

Referring to fig. 2, when electrons and holes emit light in a quantum well recombination manner, and light emitted upward reaches the surface critical (the P-type AlGaN layer 8 side) of the epitaxial layer, due to a large refractive index difference between the epitaxial layer and air, the light may be reflected or totally reflected, a part of the reflected light may be emitted from the side surface of the epitaxial layer, the reflected light may reach the bottom (the substrate 1 side) and then be reflected upward again, a part of the light reflected upward may be emitted out of the epitaxial layer, and a part of the light may be reflected back again, and this is repeated, and finally, the light which cannot be reflected out may be absorbed by the material and converted into heat, which affects the light extraction efficiency.

Referring to fig. 3, when the electrons and the holes emit light in a quantum well recombination manner, when the light emitted upward reaches the surface of the epitaxial layer, the light may be reflected or totally reflected due to the large refractive index difference between the epitaxial layer and the air, the reflected light may reach the reflective layer 7 with the bump 71 and be reflected upward again by the inclined side surface of the bump 71, and the light reflected upward again is also partially reflected out of the epitaxial layer and partially reflected back again. Therefore, the reflective layer 7 having the bump 71 can increase the escape probability of light and improve the light extraction efficiency.

Fig. 4 is a schematic threading dislocation diagram of the ultraviolet light emitting diode provided by the embodiment of the disclosure after the reflective layer is disposed. The substrate 1 and the epitaxial layer generate threading dislocation due to lattice mismatch, and the threading dislocation is grown along with the growth of the epitaxial layer. When the reflective layer 7 is not provided, threading dislocations may penetrate through the entire epitaxial layer, and after the reflective layer 7 is provided, referring to fig. 4, since the reflective layer 7 is a structure of a bump 71, the surface is rough, and a part of the threading dislocations (shown by thick lines) may be annihilated on the inclined side surface, so that threading dislocations continuing to grow longitudinally are reduced.

The substrate 1 may be a sapphire substrate.

The epitaxial layer may be an AlGaN epitaxial layer.

The buffer layer 2 may be an AlN buffer layer for reducing lattice mismatch between the substrate 1 and the AlGaN epitaxial layer.

The undoped AlGaN layer 3 is not doped and is used for improving the crystal growth quality of the epitaxial bottom layer.

Optionally, the undoped AlGaN layer 3 includes a low temperature AlGaN layer and a high temperature AlGaN layer, which are sequentially stacked on the buffer layer 2, and both the low temperature AlGaN layer and the high temperature AlGaN layer are undoped. The low-temperature AlGaN layer is used as a three-dimensional growth layer, and the high-temperature AlGaN layer is used as a two-dimensional filling layer, so that the crystal growth quality of the epitaxial bottom layer is favorably improved.

The N-type AlGaN layer 4 serves to supply electrons.

The N-type dopant in the N-type AlGaN layer 4 may be Si and the doping concentration may be 1018cm-3-1020cm-3。

The multiple quantum well layer 5 serves as an electron-hole radiation recombination region.

The multiple quantum well layer 5 includes a plurality of quantum barrier layers and quantum well layers which are alternately grown. The quantum well layer may be a GaN layer, and the quantum barrier layer may be an AlxGa1-xN (0< x <0.3) layer.

The electron blocking layer 6 serves to block electrons from overflowing toward the P-type AlGaN layer 8.

The electron blocking layer 6 may be a layer of AlyGa1-yN (0.2< y < 0.5).

Alternatively, the electron blocking layer 6 may be a P-type electron blocking layer 6, the P-type dopant may be Mg, and the doping concentration may be 1016cm-3-1018cm-3. The P-type electron blocking layer 6 can further increase the hole concentration of the P-type semiconductor layer.

As the shape of the convex block 71 in the reflective layer 7, a tapered body and a semicircular shape are possible.

Illustratively, the bumps 71 are tapered. For example, the projections 71 may be pyramids and quadrangular pyramids. The bump 71 is usually fabricated by etching, so that the cone is easy to fabricate, and the processing efficiency of the bump 71 can be improved.

The material of the bump 71 in the reflective layer 7 may be GaN or AlGaN.

The reflective layer 7 may or may not be doped, and again for the purpose of providing holes, the doping concentration is not so high as to affect the crystal quality of the interposed layer and to provide some holes. Due to the difficulty in doping p-type AlGaN and the low carrier injection efficiency, the adoption of p-type GaN can help to improve the hole concentration.

Illustratively, the reflective layer 7 is an undoped GaN layer or an undoped AlGaN layer 3.

Illustratively, the reflective layer 7 is a P-type doped GaN layer.

Illustratively, the P-type dopant of the reflective layer 7 is Mg with a doping concentration of 1017cm-3-1018cm-3。

Illustratively, the thickness of the reflective layer 7 is 50nm to 100 nm.

The P-type AlGaN layer 8 is used to provide holes.

The P-type dopant in the P-type AlGaN layer 8 may be Mg with a doping concentration of 1017cm-3-1018cm-3。

Optionally, the epitaxial wafer may further include a P-type contact layer deposited on the P-type AlGaN layer 8. The P-type contact layer is used for contacting with a subsequent chip, and the contact resistance is reduced.

The P-type contact layer may be a P-type GaN layer, the P-type dopant may be Mg, and the doping concentration is 1019cm-3-1020cm-3。

Fig. 5 is a flowchart of a method for manufacturing an epitaxial wafer of an ultraviolet light emitting diode according to an embodiment of the present disclosure. Referring to fig. 5, the process flow of the preparation method comprises the following steps.

And 504, etching the reflecting layer, wherein the etched reflecting layer consists of a plurality of staggered lugs, the protruding direction of the lugs is the same as the deposition direction of the epitaxial layer, and the area of the cross section of the lugs is gradually reduced along the deposition direction of the epitaxial layer.

And 505, depositing a P-type AlGaN layer on the etched reflecting layer.

In the embodiment of the disclosure, a reflecting layer located between an electron blocking layer and a P-type AlGaN layer is arranged in an epitaxial wafer of an ultraviolet light emitting diode, the reflecting layer is composed of a plurality of bumps which are arranged in a staggered manner, the protruding direction of the bumps is the same as the deposition direction of the epitaxial layer, and the area of the cross section of the bumps is gradually reduced along the deposition direction of the epitaxial layer, so that the bumps have side surfaces which are inclined relative to the deposition direction, when electrons and holes are subjected to composite luminescence in a quantum well, and upward-emitted light reaches the surface of the epitaxial layer critically, the light may be reflected or totally reflected due to the larger refractive index difference between the epitaxial layer and air, and the reflected light is reflected upward again by the inclined side surfaces of the bumps when reaching the reflecting layer with the bumps, and the light reflected upward again is also partially reflected out of the epitaxial layer, and partially; therefore, the reflecting layer with the bumps can increase the escape probability of light and improve the light-emitting efficiency.

Meanwhile, the substrate and the epitaxial layer generate threading dislocation due to lattice mismatch, the threading dislocation grows along with the growth of the epitaxial layer, the surface of a bump in the reflecting layer is usually formed by etching and is rough, and partial threading dislocation can be annihilated on the inclined side face, so that the threading dislocation continuously growing longitudinally is reduced, the diffusion of current is facilitated, and the forward working voltage is reduced.

Fig. 6 is a flowchart of a method for manufacturing an epitaxial wafer of an ultraviolet light emitting diode according to an embodiment of the present disclosure. Referring to fig. 6, the process flow of the preparation method comprises the following steps.

The substrate may be sapphire (Al) with (0001) crystal orientation2O3) Is a substrate.

An AlN buffer layer was grown on the substrate using a PVD (Physical vapor Deposition) apparatus. The growth temperature is 400-. The thickness of the buffer layer is 15 to 40 nm.

Before growing the undoped AlGaN layer, the buffer layer (with the substrate) is subjected to in-situ annealing treatment in an MOCVD (Metal Organic Chemical Vapor Deposition) apparatus at a temperature of 1000 ℃ to 1200 ℃ under a pressure of 150Torr to 500Torr for a time of 5 minutes to 10 minutes.

After the annealing is finished, the temperature of the MOCVD equipment is adjusted to 1000-1200 ℃, an undoped AlGaN layer with the thickness of 0.1-3.0 microns is grown, and the growth pressure is 50-200 Torr.

Optionally, the undoped AlGaN layer includes a low temperature AlGaN layer and a high temperature AlGaN layer stacked on the buffer layer in sequence, and both the low temperature AlGaN layer and the high temperature AlGaN layer are undoped. The low-temperature AlGaN layer is used as a three-dimensional growth layer, and the high-temperature AlGaN layer is used as a two-dimensional filling layer, so that the crystal growth quality of the epitaxial bottom layer is favorably improved.

The growth temperature of the low-temperature AlGaN layer is 1000-1100 ℃, the thickness is 0.1-1.0 microns, and the growth pressure is 50-200 Torr.

The growth temperature of the high-temperature AlGaN layer is 1100-1200 ℃, the growth thickness is 1.0-3.0 microns, and the growth pressure is 50-200 Torr.

And step 604, depositing an N-type AlGaN layer on the undoped AlGaN layer.

After the growth of the undoped AlGaN layer is finished, a Si-doped N-type AlGaN layer grows, the thickness of the Si-doped N-type AlGaN layer is 1.0-4.0 microns, the growth temperature is 1000-1200 ℃, the pressure is 50Torr-200Torr, and the Si doping concentration is 1018cm-3-1020cm-3In the meantime.

And 605, depositing a multi-quantum well layer on the N-type AlGaN layer.

The multiple quantum well layer comprises a plurality of quantum barrier layers and quantum well layers which are alternately grown. The quantum well layer may be a GaN layer, and the quantum barrier layer may be an AlxGa1-xN (0< x <0.3) layer. For example, the MQW layer is composed of 4 to 12 periods of GaN and AlxGa1-xN (0< x < 0.3). The thickness of the quantum well layer is about 3nm, the growth temperature range is 850-950 ℃, and the pressure range is between 100Torr and 300 Torr; the thickness of the quantum barrier layer is between 8nm and 20nm, the growth temperature is between 900 ℃ and 1000 ℃, and the growth pressure is between 50Torr and 200 Torr.

And step 606, depositing an electron barrier layer on the multi-quantum well layer.

The electron blocking layer may be an AlyGa1-yN (0.2< y <0.5) layer. The growth temperature is between 900 ℃ and 1050 ℃, the growth pressure is between 50Torr and 200Torr, and the growth thickness is between 15nm and 60 nm.

The electron blocking layer may be a P-type electron blocking layer, the P-type dopant may be Mg, and the doping concentration may be 1016cm-3-1018cm-3. The P-type electron blocking layer can further increase the hole concentration of the P-type semiconductor layer.

The reflective layer is a P-type doped GaN layer, and step 607 includes:

growing a P-type doped GaN layer on the electron blocking layer by taking 950-1050 ℃ as a growth temperature and 100-600 Torr as a growth pressure.

Illustratively, the P-type dopant of the reflective layer is Mg with a doping concentration of 1017cm-3-1018cm-3。

The growth temperature of the P-type doped GaN layer is between 950 ℃ and 1050 ℃, the growth pressure is between 100Torr and 600Torr, and the growth thickness is between 50nm and 100 nm.

The etched reflecting layer consists of a plurality of staggered lugs, the protruding direction of the lugs is the same as the deposition direction of the epitaxial layer, and the area of the cross section of the lugs is gradually reduced along the deposition direction of the epitaxial layer.

Step 608 includes:

firstly, growing a patterned mask on the reflecting layer, wherein the patterned mask is used for indicating the positions of the bumps.

And coating a layer of photoresist on the reflecting layer, exposing and developing the photoresist, and forming a graphical mask on the photoresist, wherein the graphical mask is a plurality of bumps which are uniformly distributed.

And secondly, etching the part, which is not covered by the patterned mask, on the reflecting layer.

After the patterning by exposure and development, the epitaxial wafer is put into an ICP (Inductively Coupled Plasma) machine for etching, and the etching is divided into Main Etching (ME) and Over Etching (OE), wherein the ME is rough trimming and the OE is fine trimming.

The etch depth is less than the thickness of the reflective layer, which may damage the epitaxial other layer structures. The requirement on etching is high, the etching rate needs to be simulated firstly, and the etching depth is controlled by controlling the etching time.

And thirdly, removing the patterned mask.

And after the etching is finished, removing the photoresist to obtain the reflecting layer with a regular shape.

And 609, depositing a P-type AlGaN layer on the etched reflecting layer.

Growing a P-type doped AlGaN layer on the reflecting layer, wherein the thickness of the P-type doped AlGaN layer is between 100nm and 300nm, the growth temperature is between 850 ℃ and 1050 ℃, the growth pressure interval is between 50Torr and 200Torr, the Mg doping concentration is 1019cm-3-1020cm-3In the meantime.

Growing a P-type contact layer GaN on the P-type doped AlGaN layer, wherein the thickness is between 10nm and 300nm, the growth temperature range is 850-1050 ℃, and the growth pressure range is 100-600 Torr.

And after the epitaxial layer is grown, reducing the temperature of a reaction cavity of the MOCVD equipment, annealing in a nitrogen atmosphere, wherein the annealing temperature range is 650-850 ℃, annealing for 5-15 minutes, and finishing the epitaxial growth at room temperature.

In the embodiments of the present disclosure, the undoped AlGaN layer, the N-type AlGaN layer, the multiple quantum well layer, the electron blocking layer, the P-type AlGaN layer, and the P-type contact layer are all prepared by using an MOCVD apparatus. Wherein, high-purity H is adopted2(Hydrogen) or high purity N2(Nitrogen) or high purity H2And high purity N2The mixed gas of (2) is used as a carrier gas, high-purity NH3As the N source, trimethyl gallium (TMGa) and triethyl gallium (TEGa) as gallium sources, silane (SiH4) as an N-type dopant, trimethyl aluminum (TMAl) as an aluminum source, and magnesium dicylocene (CP)2Mg) as a P-type dopant.

In the embodiment of the disclosure, a reflecting layer located between an electron blocking layer and a P-type AlGaN layer is arranged in an epitaxial wafer of an ultraviolet light emitting diode, the reflecting layer is composed of a plurality of bumps which are arranged in a staggered manner, the protruding direction of the bumps is the same as the deposition direction of the epitaxial layer, and the area of the cross section of the bumps is gradually reduced along the deposition direction of the epitaxial layer, so that the bumps have side surfaces which are inclined relative to the deposition direction, when electrons and holes are subjected to composite luminescence in a quantum well, and upward-emitted light reaches the surface of the epitaxial layer critically, the light may be reflected or totally reflected due to the larger refractive index difference between the epitaxial layer and air, and the reflected light is reflected upward again by the inclined side surfaces of the bumps when reaching the reflecting layer with the bumps, and the light reflected upward again is also partially reflected out of the epitaxial layer, and partially; therefore, the reflecting layer with the bumps can increase the escape probability of light and improve the light-emitting efficiency.

Meanwhile, the substrate and the epitaxial layer generate threading dislocation due to lattice mismatch, the threading dislocation grows along with the growth of the epitaxial layer, the surface of a bump in the reflecting layer is usually formed by etching and is rough, and partial threading dislocation can be annihilated on the inclined side face, so that the threading dislocation continuously growing longitudinally is reduced, the diffusion of current is facilitated, and the forward working voltage is reduced.

The above description is intended to be exemplary only and not to limit the present disclosure, and any modification, equivalent replacement, or improvement made without departing from the spirit and scope of the present disclosure is to be considered as the same as the present disclosure.

Claims (10)

1. An epitaxial wafer of an ultraviolet light emitting diode, the epitaxial wafer comprising: a substrate and an epitaxial layer deposited on the substrate, the epitaxial layer including a buffer layer, an undoped AlGaN layer, an N-type AlGaN layer, a multi-quantum well layer, an electron blocking layer, and a P-type AlGaN layer sequentially stacked on the substrate,

the epitaxial layer further comprises a reflecting layer located between the electronic barrier layer and the P-type AlGaN layer, the reflecting layer is composed of a plurality of staggered lugs, the protruding direction of the lugs is the same as the deposition direction of the epitaxial layer, and the area of the cross section of each lug is gradually reduced along the deposition direction of the epitaxial layer.

2. The epitaxial wafer of claim 1, wherein the bumps are tapered.

3. The epitaxial wafer of claim 1, wherein the reflective layer is an undoped GaN layer or an undoped AlGaN layer.

4. The epitaxial wafer of claim 1, wherein the reflective layer is a P-type doped GaN layer.

5. The epitaxial wafer of claim 4, wherein the P-type dopant of the reflective layer is Mg at a doping concentration of 1017cm-3-1018cm-3。

6. The epitaxial wafer of claim 1, wherein the reflective layer has a thickness of 50nm to 100 nm.

7. A preparation method of an epitaxial wafer of an ultraviolet light-emitting diode is characterized by comprising the following steps:

providing a substrate;

depositing an epitaxial layer on the substrate, wherein the epitaxial layer comprises a buffer layer, an undoped AlGaN layer, an N-type AlGaN layer, a multi-quantum well layer and an electron barrier layer which are sequentially stacked on the substrate;

depositing a reflective layer on the electron blocking layer;

etching the reflecting layer, wherein the etched reflecting layer consists of a plurality of staggered lugs, the protruding direction of the lugs is the same as the deposition direction of the epitaxial layer, and the area of the cross section of the lugs is gradually reduced along the deposition direction of the epitaxial layer;

and depositing a P-type AlGaN layer on the etched reflecting layer.

8. The method according to claim 7, wherein the reflective layer is a P-type doped GaN layer,

the depositing a reflective layer on the electron blocking layer includes:

and growing a P-type doped GaN layer on the electron blocking layer by taking 950-1050 ℃ as a growth temperature and 100-600 Torr as a growth pressure.

9. The method according to claim 8, wherein the P-type dopant of the reflective layer is Mg at a doping concentration of 1017cm-3-1018cm-3。

10. The method according to claim 7, wherein the etching the reflective layer comprises:

growing a patterned mask on the reflective layer, wherein the patterned mask is used for indicating the positions of the bumps;

etching the part, which is not covered by the graphical mask, on the reflecting layer;

and removing the patterned mask.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202011189257.8A CN112397621B (en) | 2020-10-30 | 2020-10-30 | Epitaxial wafer of ultraviolet light-emitting diode and preparation method thereof |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202011189257.8A CN112397621B (en) | 2020-10-30 | 2020-10-30 | Epitaxial wafer of ultraviolet light-emitting diode and preparation method thereof |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN112397621A true CN112397621A (en) | 2021-02-23 |

| CN112397621B CN112397621B (en) | 2022-03-18 |

Family

ID=74597765

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN202011189257.8A Active CN112397621B (en) | 2020-10-30 | 2020-10-30 | Epitaxial wafer of ultraviolet light-emitting diode and preparation method thereof |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN112397621B (en) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN113257969A (en) * | 2021-05-10 | 2021-08-13 | 广东先导稀材股份有限公司 | Nonpolar AlGaN-based ultraviolet LED epitaxial wafer and preparation method thereof |

| CN114335270A (en) * | 2021-12-27 | 2022-04-12 | 江西兆驰半导体有限公司 | Light emitting diode epitaxial wafer, manufacturing method thereof and light emitting diode |

| CN116885069A (en) * | 2023-09-05 | 2023-10-13 | 至芯半导体(杭州)有限公司 | Light extraction layer, ultraviolet LED epitaxial structure, and preparation method and application thereof |

Citations (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20050236636A1 (en) * | 2004-04-23 | 2005-10-27 | Supernova Optoelectronics Corp. | GaN-based light-emitting diode structure |

| JP2007095744A (en) * | 2005-09-27 | 2007-04-12 | Matsushita Electric Works Ltd | Semiconductor light-emitting element and manufacturing method thereof, and luminaire using the same |

| US20070272930A1 (en) * | 2006-05-26 | 2007-11-29 | Huan-Che Tseng | Light-emitting diode package |

| US20090261318A1 (en) * | 2008-04-22 | 2009-10-22 | Cheong Hung Seob | Semiconductor light emitting device |

| CN101606248A (en) * | 2006-11-28 | 2009-12-16 | 旭晶光科技股份有限公司 | Pyramidal photonic crystal light emitting device |

| CN101689593A (en) * | 2007-05-21 | 2010-03-31 | Lg伊诺特有限公司 | Semiconductor light emitting device and method of manufacturing the same |

| CN101859855A (en) * | 2010-05-14 | 2010-10-13 | 厦门市三安光电科技有限公司 | Quaternary upright lighting diode with double roughened surfaces and preparation method thereof |

| CN102569588A (en) * | 2010-12-27 | 2012-07-11 | 同方光电科技有限公司 | Light-emitting diode capable of being increased in light extraction efficiency and manufacturing method thereof |

| CN102623598A (en) * | 2011-01-26 | 2012-08-01 | Lg伊诺特有限公司 | Light emitting device |

| CN103078023A (en) * | 2013-01-31 | 2013-05-01 | 武汉迪源光电科技有限公司 | Bireflection light emitting diode |

| CN105870275A (en) * | 2016-05-25 | 2016-08-17 | 天津三安光电有限公司 | LED (light emitting diode) and manufacturing method thereof |

| CN111066160A (en) * | 2017-09-06 | 2020-04-24 | 欧司朗Oled有限责任公司 | Method for producing an optoelectronic semiconductor chip and optoelectronic semiconductor chip |

| US10770622B2 (en) * | 2015-12-29 | 2020-09-08 | Lg Innotek Co., Ltd. | Light-emitting element and light-emitting element package comprising same |

| CN111739989A (en) * | 2020-07-24 | 2020-10-02 | 深圳市昂德环球科技有限公司 | AlGaN-based deep ultraviolet LED epitaxial wafer and preparation method thereof |

-

2020

- 2020-10-30 CN CN202011189257.8A patent/CN112397621B/en active Active

Patent Citations (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20050236636A1 (en) * | 2004-04-23 | 2005-10-27 | Supernova Optoelectronics Corp. | GaN-based light-emitting diode structure |

| JP2007095744A (en) * | 2005-09-27 | 2007-04-12 | Matsushita Electric Works Ltd | Semiconductor light-emitting element and manufacturing method thereof, and luminaire using the same |

| US20070272930A1 (en) * | 2006-05-26 | 2007-11-29 | Huan-Che Tseng | Light-emitting diode package |

| CN101606248A (en) * | 2006-11-28 | 2009-12-16 | 旭晶光科技股份有限公司 | Pyramidal photonic crystal light emitting device |

| CN101689593A (en) * | 2007-05-21 | 2010-03-31 | Lg伊诺特有限公司 | Semiconductor light emitting device and method of manufacturing the same |

| US20090261318A1 (en) * | 2008-04-22 | 2009-10-22 | Cheong Hung Seob | Semiconductor light emitting device |

| CN101859855A (en) * | 2010-05-14 | 2010-10-13 | 厦门市三安光电科技有限公司 | Quaternary upright lighting diode with double roughened surfaces and preparation method thereof |

| CN102569588A (en) * | 2010-12-27 | 2012-07-11 | 同方光电科技有限公司 | Light-emitting diode capable of being increased in light extraction efficiency and manufacturing method thereof |

| CN102623598A (en) * | 2011-01-26 | 2012-08-01 | Lg伊诺特有限公司 | Light emitting device |

| CN103078023A (en) * | 2013-01-31 | 2013-05-01 | 武汉迪源光电科技有限公司 | Bireflection light emitting diode |

| US10770622B2 (en) * | 2015-12-29 | 2020-09-08 | Lg Innotek Co., Ltd. | Light-emitting element and light-emitting element package comprising same |

| CN105870275A (en) * | 2016-05-25 | 2016-08-17 | 天津三安光电有限公司 | LED (light emitting diode) and manufacturing method thereof |

| CN111066160A (en) * | 2017-09-06 | 2020-04-24 | 欧司朗Oled有限责任公司 | Method for producing an optoelectronic semiconductor chip and optoelectronic semiconductor chip |

| CN111739989A (en) * | 2020-07-24 | 2020-10-02 | 深圳市昂德环球科技有限公司 | AlGaN-based deep ultraviolet LED epitaxial wafer and preparation method thereof |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN113257969A (en) * | 2021-05-10 | 2021-08-13 | 广东先导稀材股份有限公司 | Nonpolar AlGaN-based ultraviolet LED epitaxial wafer and preparation method thereof |

| CN114335270A (en) * | 2021-12-27 | 2022-04-12 | 江西兆驰半导体有限公司 | Light emitting diode epitaxial wafer, manufacturing method thereof and light emitting diode |

| CN116885069A (en) * | 2023-09-05 | 2023-10-13 | 至芯半导体(杭州)有限公司 | Light extraction layer, ultraviolet LED epitaxial structure, and preparation method and application thereof |

| CN116885069B (en) * | 2023-09-05 | 2023-12-19 | 至芯半导体(杭州)有限公司 | Light extraction layer, ultraviolet LED epitaxial structure, and preparation method and application thereof |

Also Published As

| Publication number | Publication date |

|---|---|

| CN112397621B (en) | 2022-03-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5103271A (en) | Semiconductor light emitting device and method of fabricating the same | |

| JP5420137B2 (en) | Group III light emitting device grown on textured substrate | |

| US6441403B1 (en) | Semiconductor device with roughened surface increasing external quantum efficiency | |

| CN112397621B (en) | Epitaxial wafer of ultraviolet light-emitting diode and preparation method thereof | |

| CN109524522B (en) | GaN-based light emitting diode epitaxial wafer and preparation method thereof | |

| CN109346576B (en) | Light emitting diode epitaxial wafer and preparation method thereof | |

| CN109360871B (en) | Patterned substrate, light-emitting diode epitaxial wafer and preparation method thereof | |

| CN112133797B (en) | Growth method of light emitting diode epitaxial wafer | |

| US20190157069A1 (en) | Semipolar amd nonpolar light-emitting devices | |

| CN109786530B (en) | GaN-based light emitting diode epitaxial wafer and preparation method thereof | |

| CN112885937B (en) | Preparation method of P electrode of light-emitting diode chip with vertical structure | |

| CN112687773B (en) | Epitaxial wafer of ultraviolet light-emitting diode and preparation method thereof | |

| CN109904066B (en) | Preparation method of GaN-based light-emitting diode epitaxial wafer | |

| CN112331749A (en) | Epitaxial wafer of ultraviolet light-emitting diode and preparation method thereof | |

| CN109671817B (en) | Light emitting diode epitaxial wafer and preparation method thereof | |

| KR20060075539A (en) | Semiconductor emitting device and manufacturing method for the same | |

| US7153713B2 (en) | Method for manufacturing high efficiency light-emitting diodes | |

| CN109802022B (en) | GaN-based light emitting diode epitaxial wafer and preparation method thereof | |

| CN116344698B (en) | Patterned substrate GaN-based LED epitaxial wafer and preparation method thereof | |

| JP2005085932A (en) | Light-emitting diode and its manufacturing method | |

| CN109786522B (en) | GaN-based light emitting diode epitaxial wafer and preparation method thereof | |

| CN109473521B (en) | Light emitting diode epitaxial wafer and preparation method thereof | |

| US5235194A (en) | Semiconductor light-emitting device with InGaAlP | |

| CN113013299B (en) | Light emitting diode epitaxial wafer and growth method thereof | |

| KR100990226B1 (en) | GaN-based Light Emitting Diode having omnidirectional reflector with 3-dimensional structure and method for fabricating the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant | ||

| CP03 | Change of name, title or address |

Address after: 215600 No.28 CHENFENG Road, Zhangjiagang Economic Development Zone, Suzhou City, Jiangsu Province Patentee after: BOE Huacan Optoelectronics (Suzhou) Co.,Ltd. Country or region after: China Address before: 215600 No.28 CHENFENG Road, Zhangjiagang Economic Development Zone, Suzhou City, Jiangsu Province Patentee before: HC SEMITEK (SUZHOU) Co.,Ltd. Country or region before: China |

|

| CP03 | Change of name, title or address |