CN110416297B - N-type fin field effect transistor and forming method thereof - Google Patents

N-type fin field effect transistor and forming method thereof Download PDFInfo

- Publication number

- CN110416297B CN110416297B CN201810389918.8A CN201810389918A CN110416297B CN 110416297 B CN110416297 B CN 110416297B CN 201810389918 A CN201810389918 A CN 201810389918A CN 110416297 B CN110416297 B CN 110416297B

- Authority

- CN

- China

- Prior art keywords

- fin

- layer

- stop layer

- etching

- contact

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000000034 method Methods 0.000 title claims abstract description 54

- 230000005669 field effect Effects 0.000 title claims abstract description 33

- 238000005530 etching Methods 0.000 claims abstract description 118

- 208000012868 Overgrowth Diseases 0.000 claims abstract description 7

- 239000010410 layer Substances 0.000 claims description 316

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 58

- 229910052710 silicon Inorganic materials 0.000 claims description 58

- 239000010703 silicon Substances 0.000 claims description 58

- 229910052698 phosphorus Inorganic materials 0.000 claims description 48

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical group [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 claims description 47

- 239000011574 phosphorus Substances 0.000 claims description 47

- 239000000463 material Substances 0.000 claims description 41

- 229910052751 metal Inorganic materials 0.000 claims description 29

- 239000002184 metal Substances 0.000 claims description 29

- 239000011229 interlayer Substances 0.000 claims description 21

- 239000004065 semiconductor Substances 0.000 claims description 13

- 238000001312 dry etching Methods 0.000 claims description 11

- 238000005229 chemical vapour deposition Methods 0.000 claims description 8

- 239000002210 silicon-based material Substances 0.000 claims description 8

- 150000001875 compounds Chemical class 0.000 claims description 7

- 239000013078 crystal Substances 0.000 claims description 6

- 239000000376 reactant Substances 0.000 claims description 3

- 238000001465 metallisation Methods 0.000 abstract description 9

- 239000000758 substrate Substances 0.000 description 41

- 238000002955 isolation Methods 0.000 description 22

- 239000007789 gas Substances 0.000 description 15

- 239000010408 film Substances 0.000 description 14

- 230000000694 effects Effects 0.000 description 12

- 230000000903 blocking effect Effects 0.000 description 8

- 239000003989 dielectric material Substances 0.000 description 7

- 229910052732 germanium Inorganic materials 0.000 description 7

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 7

- 238000002360 preparation method Methods 0.000 description 7

- 238000004519 manufacturing process Methods 0.000 description 6

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 5

- 238000000151 deposition Methods 0.000 description 5

- 238000010586 diagram Methods 0.000 description 5

- 229910052814 silicon oxide Inorganic materials 0.000 description 5

- 229910052581 Si3N4 Inorganic materials 0.000 description 4

- 230000004888 barrier function Effects 0.000 description 4

- 238000006243 chemical reaction Methods 0.000 description 4

- 238000000407 epitaxy Methods 0.000 description 4

- 238000011049 filling Methods 0.000 description 4

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 4

- 229920005591 polysilicon Polymers 0.000 description 4

- 239000012495 reaction gas Substances 0.000 description 4

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 4

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 3

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 3

- TVGGZXXPVMJCCL-UHFFFAOYSA-N [Si].[La] Chemical compound [Si].[La] TVGGZXXPVMJCCL-UHFFFAOYSA-N 0.000 description 3

- UGACIEPFGXRWCH-UHFFFAOYSA-N [Si].[Ti] Chemical compound [Si].[Ti] UGACIEPFGXRWCH-UHFFFAOYSA-N 0.000 description 3

- CSDREXVUYHZDNP-UHFFFAOYSA-N alumanylidynesilicon Chemical compound [Al].[Si] CSDREXVUYHZDNP-UHFFFAOYSA-N 0.000 description 3

- 230000009286 beneficial effect Effects 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 3

- 239000004020 conductor Substances 0.000 description 3

- 230000008021 deposition Effects 0.000 description 3

- 239000012212 insulator Substances 0.000 description 3

- 150000002500 ions Chemical class 0.000 description 3

- LGERWORIZMAZTA-UHFFFAOYSA-N silicon zinc Chemical compound [Si].[Zn] LGERWORIZMAZTA-UHFFFAOYSA-N 0.000 description 3

- 239000000243 solution Substances 0.000 description 3

- 239000000126 substance Substances 0.000 description 3

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- 239000010937 tungsten Substances 0.000 description 3

- 238000000137 annealing Methods 0.000 description 2

- 238000002513 implantation Methods 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- 238000006467 substitution reaction Methods 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 1

- JXBAVRIYDKLCOE-UHFFFAOYSA-N [C].[P] Chemical compound [C].[P] JXBAVRIYDKLCOE-UHFFFAOYSA-N 0.000 description 1

- ILCYGSITMBHYNK-UHFFFAOYSA-N [Si]=O.[Hf] Chemical compound [Si]=O.[Hf] ILCYGSITMBHYNK-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 229910000449 hafnium oxide Inorganic materials 0.000 description 1

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 1

- 239000007943 implant Substances 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- NFFIWVVINABMKP-UHFFFAOYSA-N methylidynetantalum Chemical compound [Ta]#C NFFIWVVINABMKP-UHFFFAOYSA-N 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 239000002070 nanowire Substances 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 238000001020 plasma etching Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 238000007517 polishing process Methods 0.000 description 1

- 230000035484 reaction time Effects 0.000 description 1

- 230000000717 retained effect Effects 0.000 description 1

- 229910003468 tantalcarbide Inorganic materials 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

- 229910001928 zirconium oxide Inorganic materials 0.000 description 1

- GFQYVLUOOAAOGM-UHFFFAOYSA-N zirconium(iv) silicate Chemical compound [Zr+4].[O-][Si]([O-])([O-])[O-] GFQYVLUOOAAOGM-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66787—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a gate at the side of the channel

- H01L29/66795—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a gate at the side of the channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/785—Field effect transistors with field effect produced by an insulated gate having a channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Abstract

The invention provides a method for forming an N-type fin field effect transistor with a plurality of fin parts, which comprises the following steps: forming an epitaxial layer on the fin portions, wherein the epitaxial layer has gaps between the fin portions adjacent to each other; and forming a fin contact etching stop layer on the epitaxial layer, wherein the fin contact etching stop layer can fill the gap. The forming method fills gaps among fin parts by continuing epitaxial overgrowth on the existing epitaxial layers, and connects the epitaxial layers which are originally separated from each other. In the subsequent contact etching step, the film layer at the gap is used as a fin part contact etching stop layer to prevent the gap from being etched through, thereby avoiding the generation of electric leakage points after metal deposition and improving the product yield.

Description

Technical Field

The present invention relates to the field of semiconductor manufacturing processes, and more particularly, to a method for manufacturing an N-type fin field effect transistor.

Background

In the existing Fin Field effect transistor (Fin Field-Effect Transistor, finFET) manufacturing process, phosphorus doped and germanium doped silicon epitaxial layers have been widely used to improve the carrier mobility of the transistor and the doping of the source and drain. The germanium doped silicon epitaxial layer is usually formed on the fin of the P-type FinFET to obtain a P-type source/drain electrode with high doping concentration; and a phosphorus doped silicon epitaxial layer with high doping concentration is arranged in a source-drain region on the N-type FinFET fin so as to improve the performance of the device.

In some FinFET devices, some single FinFET transistors (e.g., 4T-FinFET) have multiple fins that together serve as source and drain electrodes, so that the fins may be shorted to each other, eliminating the need for shorting concerns when growing germanium doped silicon epitaxial layers in the source and drain regions of P-FinFET, and combining them as much as possible to achieve a larger epitaxial volume. Since the larger the volume of the germanium doped silicon epitaxial layer, the higher the compressive stress created, an increase in the compressive stress of the P-type FinFET can generally be achieved by an increase in the volume of the epitaxial layer.

For an N-type FinFET, the situation is not the same. The smaller the volume of the phosphorus doped silicon epitaxial layer, the better the tensile stress effect can be obtained when the epitaxial layer is grown outside the source-drain region of the N-type FinFET, so that in the prior art, the phosphorus doped silicon epitaxial layer with small volume and separated fin parts is generally adopted.

Although such small volume, discontinuous phosphorus doped silicon epitaxial layers have no impact on device performance in subsequent processes such as epitaxy, sidewall processing, source drain implantation, metal gate growth, etc. However, in the process of forming the contact hole by contact etching, the gap of the non-combined phosphorus doped silicon epitaxial layer is etched through, after metal deposition, the bottom of the metal layer is connected with the non-phosphorus doped position at the bottom of the fin part, and the connection point becomes a leakage point in the integrated circuit system, so that the device performance and the product yield are damaged.

Disclosure of Invention

In view of the above problems in the prior art, that is, gaps among fin portions of an N-type FinFET transistor are easily etched in a contact etching process, a large number of leakage points are formed to ultimately affect device performance and yield.

The method for forming the N-type fin field effect transistor comprises the following steps:

forming an epitaxial layer on the fin portions, wherein the epitaxial layer has gaps between the fin portions adjacent to each other;

and forming a fin contact etching stop layer on the epitaxial layer, wherein the fin contact etching stop layer can fill the gap.

According to the forming method provided by the invention, the fin part contact etching stop layer is grown on the epitaxial layer, gaps among the fin parts are filled, and the epitaxial layers which are originally separated from each other are connected. In the subsequent contact etching step, the fin portion contact etching stop layer at the gap can prevent the fin portion gap from being etched through, so that the generation of electric leakage points after metal deposition is avoided, and the product yield is improved.

In the preferred technical solution of the present invention, in the step of forming the fin contact etch stop layer, the fin contact etch stop layer is obtained by continuing epitaxial overgrowth on a crystal plane of the epitaxial layer.

Further, in the preferred technical scheme of the invention, the fin contact etching stop layer is formed by adopting a chemical vapor deposition method.

Furthermore, in the preferred technical scheme of the invention, when the fin portion is formed by adopting a chemical vapor deposition method to contact the etching stop layer, the temperature of the cavity is 400-800 ℃.

Furthermore, in the preferred technical scheme of the invention, when the fin portion is formed by adopting a chemical vapor deposition method to contact the etching stop layer, the adopted reaction gas at least comprises SiH 4 、SiH 2 Cl 2 、PH3、H 2 、HCl。

In a preferred embodiment of the present invention, the epitaxial layer is a phosphorus doped silicon epitaxial layer. When the epitaxial layer is a phosphorus doped silicon epitaxial layer, the smaller the volume of the epitaxial layer is, the larger the tensile stress applied to the fin part is; therefore, technicians can adopt a small-volume discontinuous epitaxial layer to contact the etching stop layer in combination with a continuous fin part, and the generation of electric leakage points is avoided on the premise of ensuring the tensile stress effect.

Further, in a preferred embodiment of the present invention, the fin contact etch stop layer is made of undoped, phosphorus lightly doped or phosphorus doped silicon material or metal semiconductor compound. Preferably, the metal semiconductor compound is a titanium silicon compound, an aluminum silicon compound, a lanthanum silicon compound, a zinc silicon compound. The metal semiconductor compound has metal characteristics and lower resistance, and can inhibit the rise of contact resistance when the subsequent etching is incomplete.

When the fin portion contact etching stop layer is prepared by adopting the material which is the same as or similar to the epitaxial layer, the preparation process can be carried out in the same CVD chamber and is finished by adopting the same or basically the same reaction gas, no additional step is required, and the method is simple and convenient.

In a preferred aspect of the invention, the fin contact etch stop layer has a thickness of less than 200 angstroms. The thickness is the thickness of the etching stop layer contacted with the unetched fin part originally formed, and is the thickness of the film layer on the surface of the epitaxial layer above the fin part. The film layer should not be too thick to prevent the final retained thickness from being too great, resulting in an effect on contact resistance.

In a preferred technical scheme of the invention, after forming the fin portion contact etching stop layer, the method further comprises the following steps: the fin portion is etched back to contact the etching stop layer. After the continuous fin contact etch stop layer is formed, the stop layer covers the whole source drain region, and the stop layer plays a role in blocking metal from entering the gap, but parasitic resistance is formed between the epitaxial layer and the metal contact, so that the reduction of contact resistance of the source drain region is not facilitated. Therefore, in the preferred technical scheme, an additional step of etching back the fin contact etching stop layer is added, and because the fin contact etching stop layer can be combined at the position between adjacent fins in the growth process, the thickness of the combined area (namely the adjacent position of the fins) is larger than that of the direct growth area (namely the film layer at the position above the fins), in the subsequent etching back step, even if the stop layer above the fins is completely etched, the gap position between the fins still remains filled with the stop layer with a certain thickness due to the thickness difference, and the effect of blocking contact etching is achieved in the subsequent step. Therefore, by reasonably adjusting the parameters of the back etching step, the increase of the contact resistance can be restrained and the device performance can be improved while the film layer is ensured to resist the etching effect.

Further, in the preferred embodiment of the present invention, HCl reactant gas is used to etch back the fin contact etch stop layer in the epitaxial growth chamber. According to the technical scheme, the steps of epitaxial growth, overgrowth and back etching can be completed in the same chamber by technicians, and the production process flow is simplified.

Further, in the preferred technical solution of the present invention, dry etching is adopted for the etching back step of the fin portion contacting the etching stop layer. After the film layer grows by adopting an isotropic deposition step, the anisotropic dry etching is used for etching back the film layer, so that the connection effect of the residual film layer can be effectively ensured. In addition, the etching back step in the invention has lower requirement on the selection ratio, and in some embodiments, even the same or similar epitaxial layer and stop layer materials can be adopted, so that the etching back method is more suitable for adopting dry etching.

Furthermore, in the preferred technical scheme of the invention, the etching gas of the dry etching adopts HBr、Cl 2 、HCl、SO 2 、Ar、O 2 、CF 4 、CHF 3 、CH 2 F 2 、CH 3 F、He、H 2 、CH 4 One or a combination of several of them.

Further, in the preferred technical scheme of the invention, after back etching, the thickness of the fin contact etching stop layer on the fin portions is-100 angstroms, and the thickness of the fin contact etching stop layer between the fin portions is 0-200 angstroms. In the preferred technical scheme, the negative value in the thickness of the fin contact etching stop layer means that in the etching back step, the fin contact etching stop layer is completely etched, and the epitaxial layer with a certain thickness is etched. Etching the fin contact etching stop layer between the fin parts to 0-100 angstroms or exposing the epitaxial layer, thereby being beneficial to reducing the contact resistance between the metal and the epitaxial layer and improving the performance of the device; meanwhile, the fin parts with certain thickness are required to be reserved among the fin parts to contact with the etching stop layer, so that no gap is reserved among the fin parts, and metal deposition is prevented from entering.

In a preferred technical scheme of the present invention, the method for manufacturing the N-type fin field effect transistor further comprises the following steps: forming an interlayer dielectric layer on the fin portion contact etching stop layer; contact etching at least a part of the interlayer dielectric layer of the active region; when the interlayer dielectric layer of at least a part of the active region is etched in a contact mode, the selectivity of the interlayer dielectric layer to the fin contact etching stop layer is more than 5:1, preferably more than 10:1 or more than 20:1. In the preferred technical scheme, the material of the fin part contact etching stop layer, the equipment for contact etching and the parameter selection are limited according to the requirement of the selection ratio, so that the contact etching can be stopped at the stop layer in time, and the blocking effect is improved.

The invention also provides an N-type fin field effect transistor which comprises a plurality of fin parts and an epitaxial layer on the fin parts, wherein the epitaxial layer is provided with gaps at positions between the fin parts adjacent to each other, and a fin part contact etching stop layer is arranged on the epitaxial layer and covers the gaps between the fin parts adjacent to each other. The existing N-type fin field effect transistor adopts a phosphorus doped silicon epitaxial layer with a small volume, gaps exist between different fin parts, and the gaps can induce the generation of leakage points, so that the device performance is reduced. According to the invention, the fin part is arranged on the epitaxial layer to contact with the etching stop layer, so that the generation of a leakage point is eliminated, and the product performance and yield are improved.

In a preferred technical scheme of the invention, the epitaxial layer is a phosphorus doped silicon epitaxial layer, and the fin contact etching stop layer is an undoped silicon layer, a phosphorus lightly doped silicon layer or a phosphorus medium doped silicon layer or a metal semiconductor compound layer. The undoped, phosphorus lightly doped or phosphorus medium doped silicon layer can be well combined with the phosphorus doped silicon epitaxial layer, has higher selection ratio with the interlayer dielectric oxide in the subsequent contact etching step, and can improve the blocking effect and prevent the penetration. In addition, the epitaxial layer and the fin contact etching stop layer in the preferred technical scheme are made of the same or basically the same material, so that the epitaxial layer and the fin contact etching stop layer can be formed in the same cavity in the preparation process without adding extra steps, and the product preparation is greatly facilitated.

In the preferred technical scheme of the invention, the thickness of the fin contact etching stop layer at the gap position is 0-200 angstroms, and the thicknesses of the fin contact etching stop layers on the fin parts are 0-100 angstroms. The thickness of the fin part contact etching stop layer between the fin parts is limited to 0-100 angstroms or the epitaxial layer is directly exposed, so that the contact resistance between the metal and the epitaxial layer is reduced, and the device performance is improved; meanwhile, the positions among the fin parts keep certain thickness of the fin parts to contact with the etching stop layer, so that no gap is reserved among the fin parts, and metal deposition is prevented from entering.

Drawings

FIGS. 1-3 are schematic diagrams illustrating a process of forming a P-type FinFET in the prior art;

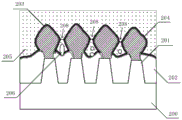

FIGS. 4-5 are schematic diagrams illustrating a process of forming an N-type FinFET in the prior art;

fig. 6-12 are schematic diagrams illustrating a process of forming an N-type finfet in an embodiment of the present invention.

Detailed Description

As known from the background art, the existing N-type fin field effect transistor is prepared by adopting a small-volume discontinuous phosphorus doped silicon epitaxial layer, and the gap is etched through during contact etching to become a leakage point, so that the device performance and the product yield are damaged.

In order to more clearly explain how the gap between the epitaxial layers induces the generation of the leakage point of the N-type fin field effect transistor in the prior art, the formation processes of the P-type and N-type fin field effect transistors in the prior art are respectively analyzed by combining the drawings, and the cause of the leakage point is analyzed by comparison.

For the P-type fin field effect transistor, the formation process is as shown in fig. 1-3.

As shown in fig. 1, the forming process of the P-type fin field effect transistor includes: first, a substrate 100 is provided, a plurality of discrete fins 101 are formed on the substrate 100 and isolation layers 102 are filled; after forming the gate structure (not shown), a first germanium-doped silicon epitaxial layer 103 needs to be grown on the fin 101. In order to apply a higher compressive stress to the fin 101, the first germanium-doped silicon epitaxial layers 103 that are separate from each other cannot meet the volume requirement, and therefore it is necessary to continue growing the second germanium-doped silicon epitaxial layer 104 so that the first germanium-doped silicon epitaxial layers 103 are connected to each other.

Next, as shown in fig. 2, a field contact etch stop layer 105 (Contact Etch Stop Layer, CESL) and a first interlayer dielectric layer 106 are formed in the subsequent process, and the deposited interlayer dielectric layer 106 fills the gaps 108 between adjacent positions of the fins 101, but the gaps 108 cannot be filled with interlayer dielectric due to the smaller gaps 108, and holes 107 are formed in the interlayer dielectric layer 106.

With continued reference to fig. 3, the M0 bit line contact 109 is etched and filled with M0 metal. During the etching of the M0 bit line contact 109, the second germanium-doped silicon epitaxial layer 104 and the field contact etch stop layer 105 may both act as a stop layer to protect the underlying structure from impact. Therefore, for the P-type finfet, even if the hole 107 is formed, the M0 metal does not make electrical contact with the fin 101, and thus, no leakage point is formed.

For an N-type fin field effect transistor, referring to fig. 4, the formation process includes: first, a substrate 200 is provided, a plurality of discrete fins 201 are formed on the substrate 200 and an isolation layer 202 is filled; after forming the gate structure (not shown), a phosphorus doped silicon epitaxial layer 203 is grown on the fin 201, and since the N-type fin field effect transistor applies a tensile stress to the fin 201 by using the phosphorus doped silicon epitaxial layer 203, the characteristics are that: the phosphorus doped silicon epitaxial layer 203 is typically less bulky and has a better effect on the tensile stress applied to the fin 201. Therefore, typically a small volume of phosphorus doped silicon epitaxial layers 203 are used, separated from each other, leaving gaps 208 between the phosphorus doped silicon epitaxial layers 203 on different fins 201. Since the pitch between fins 201 is very small, the size of the gap 208 between the phosphorus doped silicon epitaxial layers 203 grown thereon is also very small, and the very small size of the gap 208 makes it difficult for both the contact etch stop layer 204 and the interlayer dielectric layer 205 to enter from the position of the gap 208 during the deposition step, so that it is difficult for the contact etch stop layer 204 and the interlayer dielectric layer 205 in the gap 208 to completely fill and form the hole 206.

With continued reference to fig. 5, since the contact etch stop layer 204 between the fin portions 201 is less completely filled, and it is difficult to perform a normal blocking function, and the hole 206 existing in the interlayer dielectric layer 205 further worsens the situation, therefore, during the etching process of the M0 bit line contact window 207, the structure below the gap 208 of the fin portion 201 is easily etched through, so that when the contact metal is deposited, the contact metal enters from the gap 208, and directly contacts the fin portion 201 after being deposited, thereby forming a leakage point in the device, damaging the device performance and affecting the product yield.

Hereinafter, preferred embodiments of the present invention will be described generally with reference to the accompanying drawings. The embodiments of the present invention are not limited to the following embodiments, and various embodiments within the scope of the technical idea of the present invention can be employed.

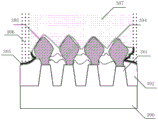

The schematic structural diagrams of the fin-type N-type field effect transistor forming process according to the embodiment of the present invention are shown in fig. 6 to 12.

Step S1: referring to fig. 6, 300 is a substrate, a plurality of separated fins 301 are formed on the surface of the substrate 300, and an isolation layer 302 is formed on the surface of the substrate 300, wherein the top of the isolation layer 302 is lower than the top of the fins 301 and covers part of the sidewall surface of the fins 301.

The substrate 300 may be silicon or silicon-on-insulator (SOI), and the substrate may also be germanium, silicon germanium, gallium arsenide, or germanium-on-insulator, and the material of the substrate 300 in this embodiment is silicon. The use of a silicon substrate as a substrate can reduce the cost of forming the fin field effect transistor and is compatible with existing planar transistor fabrication processes.

A P-well is formed within the substrate 300. The substrate 300 may also be subjected to a threshold adjustment implant to adjust the threshold voltage of a subsequently formed finfet. And annealing the substrate 300 to activate the dopant ions within the substrate 300.

The material of the fin 301 may be monocrystalline silicon or nanowire silicon. In this embodiment, the fin 301 is formed by etching an initial substrate by dry etching, and the raised fin 301 is formed on the surface of the substrate 300.

In other embodiments of the present invention, after forming the semiconductor epitaxial layer on the surface of the substrate, the fin 301 may be formed by etching the semiconductor epitaxial layer, where the semiconductor epitaxial layer may be a monocrystalline silicon layer.

As an embodiment, the forming steps of the fin 301 are as follows: providing an initial substrate; forming a patterned mask layer on the surface of the initial substrate, wherein the patterned mask layer defines the position for forming the fin portion 301 subsequently; the patterned mask layer is used as a mask, and a reactive ion etching process is used to etch a portion of the thickness of the initial substrate to form the substrate 300, and simultaneously, a plurality of discrete fins 301 are formed on the surface of the substrate 300.

In other embodiments, the fin 301 may also be formed by a dual pattern exposure method, and specifically, the process steps for forming the fin include: providing an initial substrate; forming a patterned sacrificial layer on the surface of the initial substrate; forming an initial side wall film covering the surface of the sacrificial layer and the surface of the initial substrate; etching the initial side wall film back to form an initial side wall layer on the side wall of the sacrificial layer; removing the sacrificial layer; and etching to remove part of the thickness of the initial substrate to form the substrate 300 by taking the initial side wall layer as a mask, and forming a plurality of discrete fin portions 301 on the surface of the substrate 300.

The material of the isolation layer 302 may be an insulating dielectric material such as silicon oxide, silicon nitride or silicon oxycarbide, and the isolation layer 302 serves as an isolation structure between adjacent fins 301 and an isolation structure between a subsequently formed gate structure and the substrate 300.

The method for forming the isolation layer 302 includes: depositing an isolation material on the substrate 300, the isolation material covering the fins 301 and filling up the grooves between adjacent fins 301; taking the top of the fin 301 as an polishing stop layer, and performing planarization treatment on the isolation material by adopting a chemical mechanical polishing process to form an isolation material layer flush with the top surface of the fin 301; and then, etching back the isolation material layer to reduce the surface height of the isolation material layer, so as to form an isolation layer 302 with the surface lower than the top surface of the fin 301.

Step S2: a gate structure is formed on the surface of the isolation layer 302 and spans at least one fin 301, where the gate structure covers a portion of the top surface and a portion of the sidewall surface of the fin 301, and the schematic diagram mainly shows the structure of the source-drain region in the embodiment of the present invention, so the gate structure is not shown in the figure.

In this embodiment, the gate structure is a dummy gate structure, and the dummy gate structure includes a gate dielectric layer and a dummy gate located on a surface of the gate dielectric layer, where materials of the gate dielectric layer and the dummy gate may be the same or different; the material of the gate dielectric layer is silicon oxide, and the material of the dummy gate is polysilicon. And a post gate process is adopted, and a metal gate structure is formed after the dummy gate structure is removed.

As an embodiment, the gate structure may further include a gate dielectric layer and a gate conductive layer located on a surface of the gate dielectric layer. A metal gate structure is exemplified. The gate dielectric layer is made of high-K dielectric materials such as hafnium oxide, zirconium oxide, aluminum oxide, hafnium silicon oxide or zirconium silicon oxide, the gate conductive layer is made of gate metal materials such as aluminum, tungsten, titanium oxide, tantalum or tantalum carbide, and the gate structure is used as a gate structure of the fin field effect transistor finally formed.

In other embodiments, the gate structure may be a polysilicon gate structure, where the material of the gate dielectric layer is silicon oxide, and the material of the gate conductive layer is polysilicon or doped polysilicon.

In this embodiment, the gate structure spans across the fins 301, so that the area of the channel region under the gate structure may be increased. In other embodiments, the gate structure may span one or more fins 301, depending on the actual process requirements.

As one embodiment, the forming of the gate structure includes: forming a gate dielectric material layer on the surface of the isolation layer 302, wherein the gate dielectric material layer covers the surface of the isolation layer 302, the top surface of the fin 301 and the surface of the side wall; forming a gate conductive material layer on the surface of the gate dielectric material layer; forming a patterned mask layer on the surface of the gate conductive material layer; patterning the gate conductive material layer and the gate dielectric material layer by using the patterned mask layer as a mask, so as to form a gate structure crossing the fin 301; and removing the patterned mask layer.

Step S3: offset side walls are formed on the side wall surfaces of the two sides of the gate structure, and lightly doped implantation is performed on the fin portions 301 on the two sides of the gate structure to form lightly doped regions.

As an embodiment, the forming step of the offset sidewall includes: depositing an offset side wall material layer; and etching the offset side wall material layer by adopting an anisotropic dry etching process, and forming offset side walls on the side wall surfaces of the two sides of the grid structure.

The material of the offset side wall is an insulating material such as silicon nitride, silicon oxide or silicon oxynitride, and in this embodiment, the material of the offset side wall is silicon nitride. The lightly doped region is used for reducing the transverse electric field intensity of the source drain region and reducing the hot carrier effect.

As an embodiment, the forming process of the lightly doped region includes: using the grid structure and the offset side wall as masks, implanting impurity ions into the semiconductor substrate at two sides of the grid structure to form lightly doped semiconductorAnd (5) a doped region. In this embodiment, the fin field effect transistor is of N type, the implanted ions used are As or P, the energy of the ion implantation is 1 keV-4 keV, and the dose is 2E14 atoms/cm 2 ~1E15atom/cm 2 The injection included angle is 0-20 degrees.

Step S4: referring to fig. 7, the growth time is adjusted and an epitaxial layer 303 is formed at the top of the fin 301.

In this embodiment, taking a phosphorus doped silicon material (SiP) as an example for the material of the epitaxial layer 303, the epitaxial layer 303 can generate a tensile stress on the fin 301 serving as a channel region below the gate structure, so as to improve the electron mobility in the channel region and improve the performance of the N-type fin field effect transistor.

And forming the epitaxial layer 303 on the top surface of the fin 301 by adopting a selective epitaxial process. The epitaxial reaction temperature is 400-800 ℃, and silicon source and phosphorus source gas are adopted to react to form SiP, wherein the silicon source gas is SiH 4 And SiH 2 Cl 2 The phosphorus source gas is PH 3 Also comprises H 2 And HCl, wherein the flows of the silicon source gas, the phosphorus source gas and the HCl are all 1 sccm-1000 sccm, H 2 The flow rate of (2) is 0.1slm to 50slm.

Epitaxial layers 303 are obtained by respectively epitaxially growing on different fin portions 301, and the epitaxial layers 303 on each fin portion 301 have a crystal structure, and the crystal structure finally formed has a diamond-like structure as shown in fig. 7 due to different growth rates of the crystal directions. The epitaxial layer 303 has gaps 308 between adjacent fins 301.

Although the epitaxial layer 303 is formed by phosphorus doped silicon epitaxy in the present embodiment, a skilled person may choose other types of epitaxial materials, such as carbon doped silicon epitaxy or carbon phosphorus doped silicon epitaxy, as long as it can apply a tensile stress with a suitable magnitude and direction to the channel in the fin 301.

Step S5: referring to fig. 8, the epitaxial overgrowth is continued on the crystal plane of the already formed epitaxial layer 303 to obtain a fin contact etch stop layer 304, and the fin contact etch stop layer 304 is capable of filling the gap 308 inside the epitaxial layer 303 in step S4, so that the epitaxial structure becomes a continuous thin film.

As an example, the epitaxial layer 303 and the fin contact etch stop layer 304 are made of the same or substantially the same material. As used herein, "substantially the same material" means that the material types are the same, but that the proportions of certain components or atomic composition are slightly different. For example, in this embodiment, the material of the epitaxial layer 303 is a phosphorus-doped silicon material, and the fin portion may be made of a silicon simple substance, a phosphorus-lightly doped silicon material, or a phosphorus-moderately doped silicon material by contacting the etching stop layer 304. Correspondingly, step S5 and step S4 may occur continuously in the same chemical vapor deposition chamber, i.e. the chemical vapor deposition process starts with epitaxially growing the epitaxial layer 303 until the overgrowth of the fin contact etch stop layer 304 is completed. If the fin portion contact etch stop layer 304 is made of a material with a different proportion from that of the epitaxial layer 303, such as a silicon simple substance or a silicon material doped with phosphorus with a different concentration, the growth of the fin portion contact etch stop layer 304 can be realized by adjusting the concentration proportion of the reaction gas in the reaction process.

In the embodiment, the undoped, phosphorus lightly doped or phosphorus medium doped silicon layer can be well combined with the phosphorus doped silicon epitaxial layer, and has a higher selection ratio with the interlayer dielectric oxide in the subsequent contact etching step, so that the blocking effect can be improved, and the etching through can be prevented. In addition, the epitaxial layer 303 and the fin contact etching stop layer 304 are made of the same or substantially the same material, and can be deposited and formed in the same chamber in the preparation process without adding extra steps, so that the product preparation process is greatly simplified.

Of course, in other preferred embodiments of the present invention, the skilled person may also use different materials to make the fin contact etch stop layer 304 according to the actual process requirements, for example, when the etching back thickness of the fin contact etch stop layer 304 is smaller in the subsequent step, in order to reduce the contact resistance, the fin contact etch stop layer 304 may use a metal semiconductor compound, such as a titanium silicon compound, an aluminum silicon compound, a lanthanum silicon compound, a zinc silicon compound, and the like. As long as the material of the fin contact etch stop layer 304 can have a higher selectivity (typically, the selectivity is set to be greater than 5:1, preferably 10:1 or 20:1) than the interlayer dielectric layer 306 in the subsequent contact etch step, and the effect of the tensile stress on the epitaxial layer 303 is less affected.

Similarly, the epitaxial reaction temperature is 400-800 ℃, and the silicon source and the phosphorus source gas are used for reaction to form SiP, wherein the silicon source gas is SiH 4 Or SiH 2 Cl 2 The phosphorus source gas is PH 3 Also comprises H 2 And HCl, wherein the flow rates of the silicon source gas, the phosphorus source gas and the HCl are all 1sccm to the extent

1000sccm,H 2 The flow rate of the fin portion is 0.1 slm-50 slm, and the thickness of the finally formed fin portion contact etching stop layer is smaller than 200 angstroms by adjusting the epitaxial growth reaction time. The thickness of the film may not be too thin to prevent the growth time from being too short to connect the epitaxial layers 303 on top of the different fins 301. At the same time, the film layer is not too thick to prevent the influence on the contact resistance caused by the excessive thickness finally remained.

Step S6: referring to fig. 9, the back-etched fin contacts the etch stop layer 304, after back-etching, the contact etch stop layer 304 on the top and upper sidewall surfaces of the epitaxial layer 303 is thinned, and the contact etch stop layer 304 at the lateral junction is able to maintain the connection between adjacent fins 301.

After the continuous fin contact etch stop layer is formed, the stop layer covers the whole source drain region, and the stop layer plays a role in blocking metal from entering the gap, but parasitic resistance is formed between the epitaxial layer and the metal contact, so that the reduction of contact resistance of the source drain region is not facilitated. Therefore, in this embodiment, an additional step of etching back the fin portion contact etching stop layer is added, so that on the premise of ensuring the barrier effect of the film layer, the rise of contact resistance is reduced, and the device performance is improved.

In this embodiment, the etching back step uses anisotropic dry etching. The etching gas used in the dry etching adopts HBr and Cl 2 、HCl、SO 2 、Ar、O 2 Fluorine-containing gases (e.g. CF 4 、CHF 3 、CH 2 F 2 、CH 3 F, etc.), he, H 2 、CH 4 Is a mixed gas of (a) and (b).

As an embodiment, the etching back step occurs in the epitaxial growth chamber, and HCl reaction gas is used to directly etch back the fin portion contact etching stop layer 304, and further, the forming steps of the epitaxial layer 303, the fin portion contact etching stop layer 304 and the etching back step all occur in the same chamber and continuously occur front and back.

In other preferred embodiments of the present invention, the etching back step may also be accomplished using a wet etch.

Referring to fig. 10, during deposition of the fin contact etch stop layer 304, when adjacent fin contact etch stop layers 304 are grown gradually to merge, the thickness T of the merge location (i.e., the adjacent location between fins 301) will be much greater than the thickness d or l of a single growth location (i.e., the location above the fins). Therefore, whether anisotropic dry etching or isotropic wet etching is adopted, the etching thickness is preferably controlled between d, l and T as long as the etching time and speed are reasonably controlled, and due to the thickness difference, the gap 308 between the fin portions is always filled with a stop layer with a certain thickness, so that the effect of blocking contact etching in the subsequent step is achieved. Therefore, by reasonably adjusting the parameters of the back etching step, the increase of the contact resistance can be restrained and the device performance can be improved while the film layer is ensured to resist the etching effect.

In this embodiment, after etching back, the thickness l of the fin contact etch stop layer 304 above the fins 301 is-100 angstroms, and the thickness T of the fin contact etch stop layer 304 between the fins 301 is 0-200 angstroms. Etching the fin contact etching stop layer 304 between the fin parts to 0-100 angstrom or exposing the epitaxial layer 303, thereby being beneficial to reducing the contact resistance between contact metal formed later and the epitaxial layer 303 and improving the performance of the device; meanwhile, the fin parts with certain thickness are reserved among the fin parts to contact the etching stop layer 304, so that no gap is reserved among the fin parts, and metal deposition is prevented from entering.

Step S7: referring to fig. 11, forming a side wall; completing source drain injection and annealing; removing the pseudo grid electrode to form a metal grid electrode; forming a field contact etch stop layer 305; filling an interlayer dielectric to form an interlayer dielectric layer 306; the final source and drain region cross-sectional structure is shown in fig. 11.

Step S8: referring to fig. 12, the M0 bit line is etched and M0 metal tungsten is deposited to form a contact metal layer 307.

In the M0 bit line etching step, since the fin portion contact etching barrier layer 304 covers the surface and the gap of the epitaxial layer 303 in this embodiment, the barrier layer has an etching selectivity ratio to the interlayer dielectric layer 306 of about 20:1 in the M0 bit line etching step. Thus, the contact etch step is often difficult to etch through the barrier layer. Thus, in the subsequent M0 metal deposition step, the tungsten metal is not contacted with the fin portion to form a leakage point.

In summary, the present embodiment provides a method for forming an N-type fin field effect transistor. The epitaxial layers that were originally discrete from each other are connected by continuing epitaxial overgrowth on the existing epitaxial layer, filling in the gaps between the plurality of fins. In the subsequent contact etching step, the film layer at the gap is used as a fin portion contact etching stop layer to prevent the fin portion gap from being etched through, so that the generation of electric leakage points after metal deposition is avoided, and the product yield is improved. In addition, the forming method in the embodiment also reduces the contact resistance of the source drain region and improves the device performance by etching back the fin portion contact etching stop layer.

With continued reference to fig. 12, the present embodiment also provides an N-type fin field effect transistor structure. The N-type fin field effect transistor comprises a substrate 300, a plurality of fins 301, isolation layers 302 between the fins 301, and an epitaxial layer 303 on the fins, wherein gaps 308 are formed between the fins adjacent to each other in the epitaxial layer 303, a fin contact etching stop layer 304 is arranged on the epitaxial layer 303, and the fin contact etching stop layer 304 covers the gaps 308 between the fins.

In this embodiment, the substrate 300 is a silicon substrate. In other embodiments, the substrate may also be a semiconductor substrate such as a germanium substrate, a silicon germanium substrate, or a silicon-on-insulator substrate.

In this embodiment, the fin 301 is made of silicon. In other embodiments, the fin 301 may also be made of germanium or silicon germanium.

In this embodiment, the material of the isolation layer 302 is silicon oxide. In other embodiments, the material of the isolation layer may also be a dielectric material such as silicon nitride, silicon oxycarbide, and the like.

In this embodiment, the material of the epitaxial layer 303 is SiP. In this embodiment, the epitaxial layer 303 is a phosphorus doped silicon epitaxial layer, and the fin contact etch stop layer 304 is a phosphorus lightly doped silicon layer. In other embodiments, the material of the epitaxial layer 303 may be SiCP or SiC, and the material of the fin contact etch stop layer 304 may be an undoped or phosphorus doped silicon layer, or a metal semiconductor compound such as a titanium silicon compound, an aluminum silicon compound, a lanthanum silicon compound, a zinc silicon compound, or the like.

The fin contact etch stop layer 304 between the plurality of fins 301 is 0-200 angstroms thick and the fin contact etch stop layer 304 above the plurality of fins 301 is 0-100 angstroms thick.

The existing N-type fin field effect transistor adopts a phosphorus doped silicon epitaxial layer with a small volume, gaps exist among different fin parts, and the gaps are filled with metal to form leakage points, so that the device performance is reduced. According to the invention, the fin part is arranged on the epitaxial layer to contact the etching stop layer 304, so that the generation of electric leakage points is eliminated, and the product performance and yield are improved. The epitaxial layer 303 and the fin contact etch stop layer 304 are made of the same or substantially the same material, so that they can be formed in the same chamber during the preparation process without adding additional steps, thereby greatly facilitating the preparation of the product. The thickness of the fin contact etching stop layer 304 between the fins 301 is limited to 0-100 angstrom or the epitaxial layer 303 is directly exposed, which is beneficial to reducing the contact resistance between the contact metal layer 307 and the epitaxial layer 303 and improving the device performance; meanwhile, the positions among the fin parts 301 keep a certain thickness of fin parts to contact the etching stop layer 304, so that gaps among the fin parts are not reserved, and metal deposition is prevented from entering.

Thus far, the technical solution of the present invention has been described in connection with the accompanying drawings, but it is easily understood by those skilled in the art that the scope of protection of the present invention is not limited to these specific embodiments. Equivalent modifications and substitutions for related technical features may be made by those skilled in the art without departing from the principles of the present invention, and such modifications and substitutions will fall within the scope of the present invention.

Claims (15)

1. A method of forming an N-type fin field effect transistor having a plurality of discrete fins, comprising the steps of:

forming an epitaxial layer on the fin parts, wherein gaps are formed between the fin parts adjacent to each other in the epitaxial layer;

forming a fin contact etching stop layer on the epitaxial layer, wherein the fin contact etching stop layer can fill the gap;

the epitaxial layer and the fin contact etching stop layer are made of the same or basically the same material, wherein the material of the epitaxial layer is phosphorus doped silicon material, and the material of the fin contact etching stop layer is undoped, phosphorus lightly doped or phosphorus doped silicon material.

2. The method of claim 1, wherein in the step of forming a fin contact etch stop layer, the fin contact etch stop layer is obtained by continuing epitaxial overgrowth on a crystal plane of the epitaxial layer.

3. The method of claim 2, wherein the fin contact etch stop layer is formed by chemical vapor deposition.

4. The method of claim 3, wherein a chamber temperature is 400-800 ℃ when the fin contacts the etch stop layer by chemical vapor deposition.

5. The method of claim 3, wherein the reactant gas comprises SiH at least when the fin contact etch stop layer is formed by chemical vapor deposition 4 、SiH 2 Cl 2 、PH 3 、H 2 、HCl。

6. The method of claim 1, wherein the fin contact etch stop layer is less than 200 angstroms thick.

7. The method of forming an N-type fin field effect transistor of claim 1, further comprising, after forming the fin contact etch stop layer, the steps of:

and etching back the fin part to contact with the etching stop layer.

8. The method of claim 7, wherein the fin contact etch stop layer is etched back using HCl reactant gas in an epitaxial growth chamber.

9. The method of claim 7, wherein the etching back the fin contact etch stop layer is performed by dry etching.

10. The method for forming the N-type fin field effect transistor according to claim 9, wherein the etching gas of the dry etching adopts HBr and Cl 2 、HCl、SO 2 、Ar、O 2 、CF 4 、CHF 3 、CH 2 F 2 、CH 3 F、He、H 2 、CH 4 One or more combinations thereof.

11. The method of claim 7, wherein after etching back, the fin contact etch stop layer on the plurality of fins has a thickness of-100 to 100 angstroms, and the fin contact etch stop layer at the gap position has a thickness greater than 0 and less than 200 angstroms.

12. The method of forming an N-type fin field effect transistor of claim 1, further comprising the steps of:

forming an interlayer dielectric layer on the fin portion contact etching stop layer;

contact etching the interlayer dielectric layer;

and when the interlayer dielectric layer is etched in a contact mode, the interlayer dielectric layer and the fin portion contact etching stop layer have a selection ratio of more than 5:1.

13. The N-type fin field effect transistor comprises a plurality of discrete fin parts and an epitaxial layer on the fin parts, wherein the epitaxial layer is provided with gaps between the fin parts adjacent to each other.

14. The N-type fin field effect transistor of claim 13, wherein the epitaxial layer is a phosphorus doped silicon epitaxial layer and the fin contact etch stop layer is an undoped, phosphorus lightly doped, phosphorus medium doped silicon layer or a metal semiconductor compound layer.

15. The N-type fin field effect transistor of claim 13, wherein a thickness of the fin contact etch stop layer at the gap location is greater than 0 and less than 200 angstroms, and a thickness of the fin contact etch stop layer on the plurality of fins is 0-100 angstroms.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201810389918.8A CN110416297B (en) | 2018-04-27 | 2018-04-27 | N-type fin field effect transistor and forming method thereof |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201810389918.8A CN110416297B (en) | 2018-04-27 | 2018-04-27 | N-type fin field effect transistor and forming method thereof |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN110416297A CN110416297A (en) | 2019-11-05 |

| CN110416297B true CN110416297B (en) | 2023-07-04 |

Family

ID=68345835

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201810389918.8A Active CN110416297B (en) | 2018-04-27 | 2018-04-27 | N-type fin field effect transistor and forming method thereof |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN110416297B (en) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN113658918B (en) * | 2021-08-17 | 2023-05-23 | 福建省晋华集成电路有限公司 | Method for manufacturing semiconductor device and semiconductor device |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103187304A (en) * | 2012-01-03 | 2013-07-03 | 台湾积体电路制造股份有限公司 | Methods of manufacturing semiconductor devices and transistors |

| CN103972236A (en) * | 2013-02-05 | 2014-08-06 | 格罗方德半导体公司 | Integrated circuits including finfet devices and methods for fabricating the same |

| CN105845725A (en) * | 2015-01-12 | 2016-08-10 | 中芯国际集成电路制造(上海)有限公司 | Semiconductor device, manufacturing method therefor, and electronic device |

-

2018

- 2018-04-27 CN CN201810389918.8A patent/CN110416297B/en active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103187304A (en) * | 2012-01-03 | 2013-07-03 | 台湾积体电路制造股份有限公司 | Methods of manufacturing semiconductor devices and transistors |

| CN103972236A (en) * | 2013-02-05 | 2014-08-06 | 格罗方德半导体公司 | Integrated circuits including finfet devices and methods for fabricating the same |

| CN105845725A (en) * | 2015-01-12 | 2016-08-10 | 中芯国际集成电路制造(上海)有限公司 | Semiconductor device, manufacturing method therefor, and electronic device |

Also Published As

| Publication number | Publication date |

|---|---|

| CN110416297A (en) | 2019-11-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US20230215935A1 (en) | Fets and methods of forming fets | |

| KR100487922B1 (en) | A transistor of a semiconductor device and a method for forming the same | |

| US20240021466A1 (en) | Finfet with source/drain regions comprising an insulator layer | |

| US11532750B2 (en) | Semiconductor device and method of manufacture | |

| US11935793B2 (en) | Dual dopant source/drain regions and methods of forming same | |

| US12009406B2 (en) | FinFET device and method | |

| TWI739147B (en) | Semiconductor device and method for forming the same | |

| US11854688B2 (en) | Semiconductor device and method | |

| US11996466B2 (en) | Semiconductor device and method of manufacture | |

| US20240363443A1 (en) | Source/Drain Structures and Method of Forming | |

| US11532628B2 (en) | Semiconductor device and method | |

| US12107149B2 (en) | Air spacer and method of forming same | |

| CN110416297B (en) | N-type fin field effect transistor and forming method thereof | |

| US20220384617A1 (en) | Semiconductor Device and Method | |

| US20220367717A1 (en) | Semiconductor Device and Method of Manufacture | |

| US20230163075A1 (en) | Semiconductor Device and Method | |

| US12087775B2 (en) | Gate structures in transistor devices and methods of forming same | |

| US11769821B2 (en) | Semiconductor device having a corner spacer | |

| US11302567B2 (en) | Shallow trench isolation forming method and structures resulting therefrom | |

| KR20210053227A (en) | Semiconductor device and method | |

| US11804487B2 (en) | Source/drain regions of semiconductor devices and methods of forming the same | |

| KR102454025B1 (en) | Gate electrode deposition and structure formed thereby | |

| US20240371875A1 (en) | Gate structures in transistor devices and methods of forming same | |

| US20230238271A1 (en) | Semiconductor Device and Method | |

| US20240332357A1 (en) | Transistor Contacts and Methods of Forming the Same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant |