차동 증폭기

Differential amplifier차동 증폭기는 두 입력 전압 사이의 차이를 증폭시키지만 [1]두 입력에 공통되는 전압을 억제하는 전자 증폭기의 한 유형입니다.입력 V + {\와 V (\의 2개의 입력 가 아날로그 회로입니다. 여기서 출력은 두 전압의 차이에 이상적입니다.

서앰프의 이득입니다.

단일 증폭기는 보통 적절한 피드백 저항을 표준 op-amp에 추가하거나 내부 피드백 저항을 포함하는 전용 집적회로를 통해 구현됩니다.또한 아날로그 신호를 처리하는 대규모 집적회로의 일반적인 서브 컴포넌트입니다.

이론.

이상적인 차동 증폭기의 출력은 다음과 같습니다.

서 -의 는 입력 전압이고, {\A_d}}}}는 차동 이득입니다.

그러나 실제로는 두 입력에 대해 이득이 상당히 동일하지 않다.예를 들어 의와-의 가 동일한 출력이 0이 되지 않습니다.따라서 차동 증폭기의 출력에 대한 보다 현실적인 표현에는 두 번째 항이 포함됩니다.

서 c{\를 앰프의 공통 모드 게인이라고 합니다.

차동 증폭기는 양쪽 입력에 나타나는 노이즈 또는 바이어스 전압을 제거하는 데 자주 사용되므로 일반적으로 낮은 공통 모드 게인이 바람직합니다.

보통 차분 모드 게인과 공통 모드 게인 간의 비율로 정의되는 공통 모드 제거 비율(CMR)은 두 입력에 공통되는 전압을 정확하게 취소할 수 있는 증폭기의 능력을 나타냅니다.공통 모드 제거 비율은 다음과 같이 정의됩니다.

완전 대칭 차동 증폭기에서 A c{\는 0이고 CMRR은 무한이다.차동 앰프는 단일 입력이 있는 앰프보다 더 일반적인 형태의 앰프입니다. 차동 앰프의 한 입력을 접지하면 싱글 엔드 앰프가 생성됩니다.

긴꼬리쌍둥이

이력

현대의 차동 증폭기는 일반적으로 "롱테일" 쌍 또는 차동 쌍이라고 불리는 기본 2 트랜지스터 회로와 함께 구현됩니다.이 회로는 원래 한 쌍의 진공 튜브를 사용하여 구현되었습니다.회로는 전류 게인이 있는 모든 3단자 디바이스에서 동일하게 동작합니다."롱테일" 저항 회로의 바이어스 포인트는 주로 옴의 법칙에 의해 결정되며, 액티브-컴포넌트 특성에 의해 결정됩니다.

긴 꼬리 쌍은 푸시풀 회로 기술과 측정 [2]브리지에 대한 이전의 지식에서 개발되었습니다.영국 신경학자 브라이언 매튜스가 1934년에 [3]긴 꼬리를 가진 한 쌍과 매우 흡사한 초기 회로를 발표했는데, 이것은 진짜 긴 꼬리를 가진 한 쌍이 되려고 의도된 것으로 보이지만 그림 오차가 있어 출판된 것으로 보인다.최초의 확실한 긴 꼬리 쌍 회로는 1936년 [4]앨런 블루믈린이 제출한 특허에 등장한다.1930년대 말까지 위상은 잘 확립되었고 프랭크 오프너(1937), 오토 슈미트(1937),[5][6] 얀 프리드리히 토니즈(1938)[7]를 포함한 다양한 저자들에 의해 설명되었고, 특히 생리적인 [8]충동을 감지하고 측정하는 데 사용되었다.

긴 꼬리를 가진 이 쌍은 초기 영국 컴퓨팅에서 매우 성공적으로 사용되었으며, 특히 파일럿 ACE 모델과 그 [nb 1]후속 모델인 Maurice Wilkes의 EDSAC, 그리고 Blumlein이나 그의 동료에 의해 설계된 다른 모델도 눈에 띄었습니다.긴꼬리 쌍은 스위치로 사용할 경우 튜브(트랜지스터)의 변화에 크게 영향을 받지 않으며(머신에 1,000개 이상의 튜브가 포함되어 있을 때 매우 중요), 높은 게인, 게인 안정성, 높은 입력 임피던스, 중간/낮은 출력 임피던스, 좋은 클리퍼(너무 길지 않은 테일 포함), 인버터(EDSAC)가 없습니다.출력 전압이 크게 변동합니다.한 가지 단점은 출력 전압 스윙(일반적으로 ±10–20V)이 높은 DC 전압(200V 정도)에 가해져 신호 커플링(일반적으로 일종의 광대역 DC 커플링)에 주의가 필요하다는 것입니다.이 시대의 많은 컴퓨터들은 AC 커플링 펄스 논리만을 사용하여 이 문제를 피하려고 했습니다.그 때문에, 컴퓨터는 매우 크고 복잡하거나(20자리 계산기의 경우 18,000 튜브) 신뢰할 수 없게 되었습니다.DC 결합 회로는 진공관 컴퓨터의 1세대 이후 표준이 되었습니다.

구성

차동(롱테일,[nb 2] 이미터 커플링) 쌍 증폭기는 공통(이미터, 소스 또는 캐소드) 변성이 있는 2단 증폭기로 구성됩니다.

차동 출력

2개의 입력과 2개의 출력으로 차동 증폭기를 형성합니다(그림 2).두 개의 베이스(또는 그리드 또는 게이트)는 트랜지스터 쌍에 의해 차동 증폭(감산 및 곱셈)되는 입력입니다. 차동(균형) 입력 신호를 공급하거나 한 개의 입력을 접지하여 위상 스플리터 회로를 형성할 수 있습니다.차동출력의 증폭기는 부동부하 또는 차동입력의 다른 단을 구동할 수 있다.

싱글 엔드 출력

차동출력이 바람직하지 않은 경우 1개의 출력만 사용할 수 있으며(또는 양극 또는 드레인) 다른 출력은 무시합니다.이 설정을 싱글 엔드 출력이라고 부릅니다.게인은 차동 출력을 사용하는 스테이지의 절반입니다.이득 손실을 방지하기 위해 차동-단일 엔드 컨버터를 사용할 수 있습니다.이는 종종 전류 미러로 구현됩니다(아래 그림 3).

싱글 엔드 입력

입력 중 하나가 접지되거나 기준 전압에 고정된 경우 차동 쌍을 싱글 엔드 입력 앰프로 사용할 수 있습니다(일반적으로 다른 수집기는 싱글 엔드 출력으로 사용됨).이 배치는 캐스케이드된 공통 수집기 및 공통 베이스 스테이지 또는 버퍼링된 공통 베이스 [nb 3]스테이지라고 생각할 수 있습니다.

이미터 커플링 앰프는 온도 드리프트에 대해 보정되고BE V가 취소되며 밀러 효과 및 트랜지스터 포화가 방지됩니다.따라서 이미터 커플링 앰프(밀러 효과 회피), 위상 스플리터 회로(역전압 2개 포함), ECL 게이트 및 스위치(트랜지스터 포화 회피) 등을 형성하는 데 사용됩니다.

작동

회로 작동을 설명하기 위해, 4개의 특정 모드를 아래에 격리합니다. 그러나 실제로는 이들 중 일부는 동시에 작동하며 그 효과는 중첩됩니다.

바이어싱

베이스측에서 바이어스된 고전적인 증폭단(따라서 매우 β의존적)과는 대조적으로 차동쌍은 총대기전류를 침하/주입함으로써 방사체측에서 직접 바이어스된다.직렬 음의 피드백(이미터 변성)은 트랜지스터를 전압 안정기로 작동시킵니다. 트랜지스터는 V 전압BE(기본 전류)을 조정하여 콜렉터-이미터 [nb 4]접합부를 통해 대기 전류를 통과시킵니다.따라서 음의 피드백으로 인해 대기 전류는 트랜지스터의 β에 약간만 의존합니다.

대기 콜렉터 전류를 발생시키는 데 필요한 바이어스 베이스 전류는 보통 지면에서 나와 입력 소스를 통과하여 베이스로 들어갑니다.따라서 바이어스 전류 경로를 보장하고 전압 강하를 크게 일으키지 않을 만큼 저저항을 보장하려면 소스가 갈바닉(DC)이어야 합니다.그렇지 않으면 베이스와 접지(또는 양극 전원장치) 사이에 추가 DC 요소를 연결해야 합니다.

공통 모드

공통 모드(두 입력 전압이 동일한 방향으로 변화)에서는 두 전압(이미터) 팔로어가 공통의 고저항 이미터 로드('롱 테일')에서 서로 협력합니다.이들 모두 공통의 이미터 포인트의 전압을 높이거나 낮춥니다(그림상으로는, 함께 「풀업」 또는 「풀다운」해 이동시킵니다).또한 동적 부하는 입력 전압과 동일한 방향으로 순간적인 오믹 저항을 변화시켜 두 공급 레일 사이의 총 저항을 일정하게 유지함으로써 "도움"을 줍니다.완전한 음의 피드백(100%)이 존재합니다.콜렉터 전류와 총 전류는 변경되지 않지만 2개의 입력 베이스 전압과 이미터 전압이 동시에 변경됩니다.그 결과 출력 수집기 전압도 변경되지 않습니다.

차동 모드

통상. 차동모드(두 입력전압이 반대방향으로 변화)에서는 2개의 전압(이미터) 팔로어가 서로 반대합니다.한쪽은 공통의 이미터 포인트의 전압을 올리려고 하고, 다른 한쪽은 공통의 포인트를 「풀다운」하고, 다른 한쪽은 공통의 포인트를 「풀다운」합니다.움직이지 않음)과 그 반대도 마찬가지입니다.따라서 공통점은 전압을 변경하지 않고 공통 모드 입력 전압에 따라 크기가 결정되는 가상 접지처럼 작동합니다.고저항 이미터 소자는 아무런 역할도 하지 않습니다.다른 저저항 이미터 팔로어에 의해 교체됩니다.입력 베이스 전압이 변경되어도 이미터 전압은 전혀 변하지 않기 때문에 음의 피드백은 없습니다.두 트랜지스터 사이의 공통 대기 전류와 출력 수집기 전압은 격렬하게 변화합니다.두 트랜지스터는 서로 이미터를 접지합니다.따라서 공통 수집기 단계이긴 하지만 실제로는 최대 게인을 가진 공통 이미터 단계로 작동합니다.상대적으로 저항이 작은 음극/이미터 저항을 통해 도입된 부귀환을 통해 장치 파라미터의 변화로부터 바이어스 안정성과 독립성을 개선할 수 있습니다.

과몰입.입력차전압이 크게 변화하면(약 100밀리볼트 이상), 낮은 입력전압에 의해 구동되는 트랜지스터가 꺼지고 콜렉터전압이 정공급레일에 도달한다.높은 오버드라이브에서는 베이스-이미터 접합부가 반전됩니다.다른 트랜지스터(높은 입력 전압에 의해 구동됨)는 모든 전류를 구동합니다.컬렉터의 저항이 비교적 크면 트랜지스터가 포화됩니다.비교적 작은 컬렉터 저항과 적당한 오버드라이브를 사용해도 이미터는 채도 없이 입력 신호를 따를 수 있습니다.이 모드는 차동 스위치 및 ECL 게이트에서 사용됩니다.

고장.입력전압이 계속 상승하여 베이스에미터 파괴전압을 넘으면 낮은 입력전압에 의해 구동되는 트랜지스터의 베이스에미터 접합이 파괴된다.입력 소스가 저저항일 경우 무제한 전류가 두 입력 소스 사이의 다이오드 브릿지를 직접 통과하여 손상시킵니다.

공통 모드에서는 이미터 전압이 입력 전압 변동을 따릅니다. 완전한 음의 피드백이 존재하며 이득은 최소입니다.차동 모드에서는 이미터 전압이 고정되며(순간 공통 입력 전압과 동일), 음의 피드백이 없으며 이득이 최대입니다.

차동 증폭기 개선

이미터 정전류원

공통 모드에서 수집기 전압을 일정하게 유지하려면 대기 전류가 일정해야 합니다.차동 출력의 경우 두 수집기 전압이 동시에 변화하지만 차이(출력 전압)는 변하지 않으므로 이 요건은 그다지 중요하지 않습니다.단, 싱글 엔드 출력의 경우 출력 수집기 전압이 변동하므로 전류를 일정하게 유지하는 것이 매우 중요합니다.따라서 전류 의 저항이 높을수록 (더 좋은) 공통 모드 가 됩니다.필요한 정전류는 공유 이미터 노드와 공급 레일(NPN의 경우 음수, PNP 트랜지스터의 경우 양수) 사이에 매우 높은 저항을 가진 소자(저항기)를 연결하여 생성할 수 있지만, 이를 위해서는 높은 공급 전압이 필요합니다.그렇기 때문에 보다 정교한 설계에서는 정전류원/싱크에 가까운 높은 차동(동적) 저항을 가진 소자가 "긴 꼬리"로 대체된다(그림 3).일반적으로 높은 준수 전압(출력 트랜지스터에서 전압 강하가 작음) 때문에 전류 미러에 의해 구현됩니다.

수집기 전류 미러

집전체 저항은 전류 미러로 대체할 수 있으며, 이 미러의 출력 부분이 활성 부하 역할을 합니다(그림 3).따라서 차동 수집기 전류 신호가 고유 50% 손실 없이 단일 엔드 전압 신호로 변환되어 이득이 크게 증가합니다.이는 입력 수집기 전류를 왼쪽에서 오른쪽으로 복사하여 두 입력 신호의 크기가 더해지는 방식으로 이루어집니다.이를 위해 전류 미러의 입력은 좌측 출력에 연결되고 전류 미러의 출력은 차동 증폭기의 우측 출력에 연결됩니다.

전류 미러는 좌측 컬렉터 전류를 복사하여 우측 트랜지스터를 통과시켜 우측 컬렉터 전류를 생성합니다.차동 증폭기의 이 오른쪽 출력에서는 두 신호 전류(양 및 음의 전류 변화)가 감산됩니다.이 경우(차동 입력 신호)는 동일하고 반대입니다.따라서 차이는 개별 신호 전류(δI - δI) = 2 δI)의 2배이며, 이득 손실 없이 싱글 엔드 변환이 완료됩니다.그림 4는 이 회로의 전송 특성을 나타낸다.

인터페이스 고려 사항

부동 입력 소스

2개의 베이스간에 플로팅 소스를 접속할 수 있지만, 바이어스 베이스 전류의 패스를 확보할 필요가 있습니다.갈바닉 소스의 경우 베이스 중 하나와 접지 사이에 하나의 저항만 연결하면 됩니다.바이어스 전류는 이 베이스에 직접 유입되고 다른 베이스에는 간접적으로(입력 소스를 통해) 유입됩니다.소스가 용량성일 경우 베이스 전류에 대한 다른 경로를 보장하기 위해 두 개의 저항을 두 개의 베이스와 접지 사이에 연결해야 합니다.

입출력 임피던스

차동 쌍의 입력 임피던스는 입력 모드에 따라 크게 달라집니다.커먼 모드에서는, 2개의 부품이, 높은 이미터 부하로 공통 수집기 스테이지로서 동작하기 때문에, 입력 임피던스가 매우 높아집니다.차동 모드에서는, 접지된 이미터와의 공통 이미터 스테이지로서 동작하기 때문에, 입력 임피던스는 낮아집니다.

차동 쌍의 출력 임피던스는 높습니다(특히 그림 3과 같이 전류 미러를 갖춘 개선된 차동 쌍의 경우).

입력/출력 범위

공통 모드 입력 전압은 두 공급 레일 간에 다를 수 있지만 일부 전압 강하(최소 1V)가 두 전류 미러의 출력 트랜지스터에 걸쳐 유지되어야 하므로 근접하게 도달할 수 없습니다.

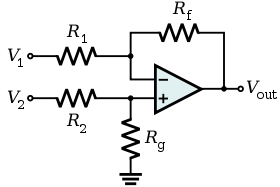

차동 증폭기로서의 연산 증폭기

연산 증폭기(op-amp)는 매우 높은 차동 모드 게인, 매우 높은 입력 임피던스 및 낮은 출력 임피던스를 가진 차동 증폭기입니다.op-amp 차동 증폭기는 음의 피드백을 적용하여 예측 가능하고 안정적인 게인으로 구축할 수 있습니다(그림 5).[nb 5]차동 증폭기의 일부 종류는 일반적으로 몇 가지 단순한 차동 증폭기를 포함합니다.예를 들어 전차동증폭기, 계장증폭기 또는 절연증폭기는 종종 여러 op-amp의 조합으로 구축된다.

적용들

차동 증폭기는 직렬 부귀환(op-amp follower, 비반전 증폭기 등)을 사용하는 많은 회로에서 발견됩니다. 여기서 한 입력은 입력 신호에 사용되고 다른 입력은 피드백 신호(일반적으로 작동 증폭기에 의해 구현됨)에 사용됩니다.비교를 위해 1940년대 초반의 구식 반전 싱글 엔드 op-amp는 추가적인 저항 네트워크를 연결함으로써 병렬 음성 피드백만 실현할 수 있었습니다(op-amp 반전 증폭기가 가장 일반적인 예입니다).일반적인 애플리케이션은 모터 또는 서보의 제어 및 신호 증폭 애플리케이션입니다.이산전자장치에서 차동증폭기를 구현하기 위한 공통배치는 롱테일쌍이며, 롱테일쌍은 보통 대부분의 op-amp 집적회로에서 차동소자로도 발견된다.긴꼬리쌍은 차동전압을 하나의 입력으로 하고 바이어스 전류를 다른 입력으로 하여 아날로그 곱셈기로 사용할 수 있다.

차동증폭기는 입력단 이미터 결합논리게이트 및 스위치로 사용된다.스위치로 사용할 경우 "왼쪽" 베이스/그리드가 신호 입력으로 사용되며 "오른쪽" 베이스/그리드가 접지됩니다. 출력은 오른쪽 콜렉터/플레이트에서 가져옵니다.입력이 0 또는 음의 경우 출력은 0에 가깝습니다(단, 포화 상태가 될 수 없습니다). 입력이 양수이면 출력이 가장 양의 동적 작동으로 위에서 설명한 앰프 사용과 동일합니다.

대칭 피드백 네트워크를 통해 공통 모드 이득 및 공통 모드 편향 제거

Op 앰프의 (이상적이지 않은) 입력 바이어스 전류 또는 차동 입력 임피던스가 중대한 영향을 미치는 경우 공통 모드 입력 신호 및 바이어스의 영향을 개선하는 피드백 네트워크를 선택할 수 있습니다.그림 6에서 전류 발생기는 각 단자의 입력 바이어스 전류를 모델링합니다+b. I와−b I는 각각 단자+ V와− V의 입력 바이어스 전류를 나타냅니다.

V 단자를 구동하는+ 네트워크에 대한 테베닌 등가물은 전압+ V'와 임피던스+ R'을 가집니다.

V 터미널을− 구동하는 네트워크의 경우:

op-amp의 출력은 개방 루프 게인ol A 곱하기 차동 입력 전류 i 곱하기 차동 입력 임피던스d 2R입니다.

여기서 R은 R과− R의 평균입니다+ .

이 방정식은 매우 단순화되어 있다.

결과적으로 관계가 생기다

즉, 차동 신호의 폐쇄 루프 게인은 V - V이지만+in−in 공통 모드 게인은 0임을 의미합니다.

또한 공통 모드 입력 바이어스 전류가 상쇄되어 입력 오프셋 전류Δb I = I+b - I만−b 남아 있고 계수가 R임을i 의미합니다.이는 입력 오프셋 전류가 입력 단자에 대한 피드백 네트워크의 소스 저항인 입력 저항i R에 걸쳐 작용하는 입력 오프셋 전압과 동일한 것과 같습니다.

마지막으로 개방 루프 전압 게인ol A가 단일성보다 훨씬 큰 한 폐쇄 루프 전압 게인은f R/R이며i, 이는 "가상 접지"[nb 6]로 알려진 썸 규칙 분석을 통해 얻을 수 있는 값입니다.

각주

- ^ 초기 컴퓨팅에 사용된 긴 꼬리 쌍의 회로에 대한 자세한 내용은 Alan Turing의 Automatic Computing Engine(Oxford University Press, 2005), ISBN0-19-856593-3)를 제4부 "ELECTRONICS"에 수록.

- ^ 롱테일은 커먼 모드에서 높은 이미터 저항을 나타내며, 비례적인 길이의 공통 롱테일(차동 모드에서는 이 꼬리가 0으로 짧아집니다)을 나타냅니다.(차동 모드에서 작은 음의 피드백을 도입하기 위해) 이미터와 공통 노드 사이에 저항이 작은 추가 이미터 저항이 포함되어 있는 경우, 짧은 꼬리로 비유적으로 나타낼 수 있습니다.

- ^ 보다 일반적으로 이 배열은 음의 피드백을 가진 두 개의 상호 작용 전압 팔로어로 간주할 수 있습니다. 차동 쌍의 출력 부분이 일정한 입력 전압을 생성하는 전압 팔로어(전압 안정기) 역할을 하며 입력 부분이 다양한 입력 전압을 변경하려고 시도하는 전압 팔로어 역할을 합니다.e 스태빌라이저의 안정적인 출력 전압.스태빌라이저는 회로 출력 역할을 하는 출력량(각각 전압)을 변경하여 이 개입에 반응합니다.

- ^ 흥미롭게도, 음의 피드백이 트랜지스터 동작을 역전시킨 것 같습니다. 즉, 수집기 전류가 입력량이 되는 반면 기본 전류는 출력량 역할을 합니다.

- ^ 이 배열에서는 고이득 차동 증폭기(op-amp)가 저이득 차동 증폭기(op-amp)의 성분으로 사용되는 것이 이상하다고 생각됩니다.음피드백 증폭기의 역설은 해롤드 블랙이 특허를 획득하는 것을 방해했다.

- ^ 폐쇄 루프 공통 모드 게인이 0이 되기 위해서는 저항 R/R의i 비율이f 반전 레그 및 비반전 레그에서 일치해야 합니다.입력 바이어스 전류를 취소하려면 여기에 제시된 보다 엄격한 관계를 얻어야 합니다.

참고 항목

레퍼런스

- ^ Laplante, Philip A. (2005). Comprehensive Dictionary of Electrical Engineering (2nd ed.). CRC Press. p. 190. ISBN 978-1420037807.

- ^ Eglin, J. M. (1 May 1929). "A Direct-Current Amplifier for Measuring Small Currents". Journal of the Optical Society of America. 18 (5): 393–402. doi:10.1364/JOSA.18.000393.

- ^ Matthews, Bryan H. C. (1 December 1934). "PROCEEDINGS OF THE PHYSIOLOGICAL SOCIETY". The Journal of Physiology. 81 (suppl): 28–29. doi:10.1113/jphysiol.1934.sp003151.

- ^ "US Patent 2185367" (PDF). Freepatensonline.com. Retrieved 15 February 2016.

- ^ Offner, Franklin (1937). "Push-Pull Resistance Coupled Amplifiers". Review of Scientific Instruments. 8 (1): 20–21. doi:10.1063/1.1752180.

- ^ Schmitt, Otto H. (1941). "Cathode Phase Inversion" (PDF). Review of Scientific Instruments. 12 (11): 548–551. doi:10.1063/1.1769796. Retrieved 15 February 2016.

- ^ "US Patent 2147940" (PDF). Google Inc. Retrieved 16 February 2016.

- ^ 게데스, L. A.차동 증폭기는 누가 발명했습니까?IEEE Engineering in Medicine and Biology, 1996년 5월/6월, 페이지 116–117.

외부 링크

- BJT 디퍼렌셜 앰프 – 회로 및 설명

- 차동 회로용 테스트 벤치

- 응용 프로그램 주의:아날로그 디바이스 – AN-0990 : 싱글 엔드 입력 애플리케이션에서의 차동 증폭기 종단

앰프의 공통 모드 게인이라고 합니다.

앰프의 공통 모드 게인이라고 합니다.

![{\displaystyle V_{\text{in}}^{+}-V_{\text{in}}^{-}-R_{\text{i}}I_{\text{b}}^{\Delta }=V_{\text{out}}\left[{\frac {R_{\text{i}}}{R_{\text{f}}}}+{\frac {1}{A_{\text{ol}}{\frac {R_{\text{i}}}{R_{\text{i}}\parallel R_{\text{f}}\parallel R_{\text{d}}}}}}\right],}](https://wikimedia.org/api/rest_v1/media/math/render/svg/898f4d56ac076d04fe6954494c03580f27d3bc2d)