PowerPC

PowerPC (Performance Optimization With Enhanced RISC - Performance Computing), prescurtat PPC, este o arhitectură pentru microprocesoare de tip RISC derivate din arhitectura procesorului IBM POWER. PowerPC a fost specificată prima dată în anul 1991 de către consorțiul AIM al firmelor Apple, IBM și Motorola. Procesoarele PowerPC urmau să fie proiectate și produse în comun de IBM și Motorola și utilizate pe computerele Apple și pe piața sistemelor înglobate. Din 2004, arhitectura a fost administrată de fundația Power.org, iar din anul 2007 descendenta din acest consorțiu este firma Freescale. Începând cu 2019, Power Foundation este administrat de Linux Foundation, ale cărui seturi de design și instrucțiuni sunt sub licență Open Source.

Arhitectura PowerPC este flexibilă pentru că oferă multe opțiuni preț/performanță funcție de aplicație și scalabilă cu avantajele unei tehnologii continue. Procesoarele PowerPC au fost proiectate pentru o scară largă de sisteme cum ar fi: calculatoare personale, controllere intregrate, stații de lucru, multiprocesare, procesoare pentru sisteme mainframe.

Istoric

[modificare | modificare sursă]Rădăcinile PowerPC provin de la IBM 801, unul dintre primele procesoare pe arhitectura RISC, proiect de cercetare condus de John Cocke la mijlocul anilor '70. Cipurile bazate pe IBM 801 au fost utilizate într-o serie de produse IBM, în cele din urmă încorporate în procesorul ROMP cu 16 registre utilizat în stația de lucru IBM RT. RT a avut însă performanțe dezamăgitoare și IBM a început în perioada 1982-1984 un proiect pentru a construi cel mai rapid microprocesor de pe piață. Această nouă arhitectură pe 64 biți a devenit cunoscută sub numele de „AMERICA architecture”. Rezultatul a fost arhitectura POWER (Performance Optimization With Enhanced RISC), introdusă cu sistemul RS/6000 în anul 1990. La început, s-a folosit arhitectura setului de instrucțiuni IBM POWER ISA, care a evoluat în PowerPC în generațiile ulterioare și apoi Power ISA, dezvoltată de OpenPOWER Foundation. Microprocesorul original POWER, una dintre primele implementări RISC superscalare, a fost de înaltă performanță, dezvoltând tehnologia multi-cip.

La începutul anului 1991, IBM în colaborare cu Apple dezvoltă cipul de microprocesor POWER1 RSC (RISC Single Chip), ce a condus la apariția unei familii de microprocesoare cu un singur cip bazat pe arhitectura POWER. La această colaborare s-a aliat și Motorola formând alianța AIM. După doi ani de dezvoltare, a rezultat PowerPC ISA urmată de versiunea modificată a arhitecturii RSC, PowerPC.

Pentru a dezvolta viitoarele microprocesoare PowerPC, AIM au pus în funcțiune în 1992 centrul de cercetare Somerset Design Center în Austin, Texas. Primul microprocesor PowerPC a fost PowerPC 601, din familia PowerPC 600 (G1), bazate pe procesorul IBM cu un singur cip. A fost proiectat ca procesor de tranziție de la arhitectura POWER la arhitectura PowerPC și implementează un superset de caracteristici atât POWER, cât și PowerPC. Procesorul PowerPC 601 a fost utilizat în computerele Apple Macintosh, IBM și sisteme înglobate.

A urmat curând a doua generație PowerPC G2 cu seria PowerPC 600: PowerPC 603, PowerPC 604 și PowerPC 620, primul procesor PowerPC pe 64 biți.

Concomitent cu dezvoltarea PowerPC, în 1994 a fost creată platforma PReP (PowerPC Reference Platform). Aceasta conține un set de specificații tehnice pentru a permite producătorilor de hardware conceperea de computere bazate pe procesoare PowerPC capabile să ruleze multiple sisteme de operare: Windows NT, OS/2, BeOS, Solaris, Taligent și IBM AIX. Sistemele PReP nu au fost niciodată populare, cu excepția câtorva unități RS/6000 bazate pe AIX.

PReP a fost ulterior înlocuit de CHRP (Common Hardware Reference Platform) în 1995. Spre deosebire de PReP, CHRP a încorporat elemente ale arhitecturii Power Macintosh și suport pentru sistemele de operare Clasic Mac OS și NetWare, în plus față de cele patru sisteme de operare care au fost portate de la PreP.

A treia generație de microprocesoare PowerPC G3 seria PowerPC 7xx pe 32 biți, a fost introdusă pe 10 noiembrie 1997. La fel ca procesoarele anterioare de a doua generație, au fost dezvoltate în comun de Apple, IBM și Motorola. Procesoarele PowerPC G3 au fost utilizate în computerele PowerBook G3, iMac, iBook și în mai multe desktopuri sub numele Power Macintosh G3. Consumul redus de energie și dimensiunile mai mici, au făcut ca procesoarele să fie ideale pentru utilizarea în sisteme înglobate, imprimante, routere, dispozitive de stocare, laptopuri, console de jocuri video, iar ultimii membri ai familiei au fost montați pe modelele iBook G3. Un model al acestui procesor, special adaptat condițiilor de vid spațial a fost folosit în sonda Mars Reconnaissance Orbiter.

PowerPC G4 este termenul folosit de Apple Computer pentru familia de microprocesoare PowerPC 74xx de 32 biți din a patra generație. Au debutat în august 1999 cu PowerPC 7400 pe computerele Macintosh precum PowerBook G4, iBook G4, Power Mac G4 și Power Mac G4 Cube. Au fost folosite și în eMac, prima generație Xserve, prima generație Mac mini și iMac G4. Procesorul PowerPC 7447 a funcționat și pe platformele Genesi PegasosPPC și Genesi EfikaPPC. [1]

Seria PowerPC G5 introdusă în 2002, a inclus procesoarele PowerPC 970, PowerPC 970FX și PowerPC 970MP pe 64 biți de la IBM. Acestea au fost utilizate în computerele Power Mac G5 și iMac G5.

În 2004, Motorola a întrerupt producția de microprocesoare, mutând dezvoltarea și producția la o companie separată numită Freescale Semiconductor. În aceeași perioadă, IBM a ieșit de pe piața procesoarelor pentru sisteme înglobate pe 32 biți prin vânzarea liniei sale de produse PowerPC către Applied Micro Circuits Corporation (AMCC) și concentrându-se asupra proiectelor de cipuri pe 64 biți.

La 6 iunie 2005, Apple a anunțat că renunță la arhitectura PowerPC și va produce în viitor sisteme PC cu procesoare Intel x86.

PowerPC e700 sau NG-64 (Next Generation 64-bit) au fost numele de cod ale primelor nuclee de procesor RISC încorporate pe 64 biți ale Freescale. În iunie 2010 Freescale a lansat un nucleu cu specificații similare numit PowerPC e5500.[2][3]

Caracteristici

[modificare | modificare sursă]Arhitectura generală PowerPC este o arhitectură superscalară, în care mai multe instrucțiuni diferite pot fi executate simultan de către unități independente. PowerPC este o arhitectură completă pe 64 de biți care are un subset de 32 de biți. Arhitectura permite atât versiunile pe 32, cât și pe 64 de biți ale procesoarelor PowerPC, dar toate procesoarele sunt necesare pentru a sprijini cel puțin programele pe 32 de biți. Arhitectura definește un comutator de mod pe 32/64 de biți controlabil din codul de supraveghere care permite implementarea procesorului pe 64 de biți să ruleze programe pe 32 de biți. Varianta pe 32 bit (PP32), este IBM "Subset". PowerPC acceptă o gamă variată de memorie: centrală, cache, ierarhizată etc. Prin construcție, realizează funcțiile unui sistem multiprocesor, ceea ce garantează eficiența lor. [4]Microprocesoarele de tip PowerPC pot opera cu numere cu virgulă mobilă în simplă sau dublă precizie. Modul lor de calcul privitor la ordinea de prelucrare a octetilor este în general Big-Endian, iar unele din ele pot fi comutate la modul Little-Endian. Aproape toate procesoarele mai noi conțin și posibilitatea de calcul vectorial AltiVec, proiectată și realizată de Motorola, sau cea numită VMX de la IBM.

Arhitectura PowerPC păstrează același model de programare de bază și atribuiri de instrucțiuni opcode ca și arhitectura POWER. Arhitectura PowerPC definește următoarele caracteristici:

- registre separate cu 32 intrări pentru instrucțiuni întregi și în VM; registrele cu scop general (GPR) grupează sursa pentru instrucțiuni aritmetice întregi, iar registrele în virgulă mobilă (FPR) țin sursa și destinația pentru instrucțiunile aritmetice în virgulă mobilă

- instrucțiuni load/store între memoria sistemului și FPR sau GPR

- format fix de instrucțiuni pe 32 biți ce permite simplificarea și procesarea paralelă a instrucțiunilor (“dispatch mechanism”)

- utilizarea nedistructivă a registrelor pentru instrucțiuni aritmetice în care al 2-lea, al 3-lea și uneori al 4-lea operand specifică de regulă registrele și sursa pentru calcule ale căror rezultate sunt memorate în registrul destinație specificat prin primul operand

- model de tratare execepții

- suport în VM care include și operații în VM conform IEEE-754

- arhitectură flexibilă care permite ca anumite caracteristici să fie executate în hardware sau software funcție de diferite opțiuni

- abilitatea de a executa operații VM în precizie simplă și dublă

- instrucțiuni de nivel utilizator pentru memorări, goliri (flushing) și invalidări de date în cache-urile on-chip; se definesc și instrucțiuni speciale (cache block touch instructions) pentru încărcări speculative de date înainte de a fi folosite, reducând “latența” (întârzierea) memoriei

- un model de memorie care permite accese slab ordonate, ceea de permite operațiilor pe registre să le reordoneze dinamic, cu creșterea performanțelor generale (overall) și reducerea latenței memoriei pentru ieșirea instrucțiunilor din execuție (throughput)

- arhitectură Harvard (cache separat de date și instrucțiuni) și cache-uri unificate

- suport pentru mod de adresare big-endian (Motorola) si little-endian (Intel)

- suport de adresare pentru 64 biți cu posibilitate de lucru și pe 32 biți.

Unele dintre modificările mai semnificative făcute în trecerea de la arhitecturile POWER la arhitecturile PowerPC includ următoarele:

- simplificarea arhitecturii pentru a fi mai adecvată pentru microprocesoarele cu un singur chip cu cost redus

- eliminarea instrucțiunilor care ar putea împiedica creșterea ratelor de ceas

- eliminarea barierelor impuse din punct de vedere arhitectural în calea expedierii suprascalare și a executării în afara comenzii

- încurajarea sistemelor simetrice multiprocesor prin adăugarea de caracteristici de suport multiprocesor

- adăugarea de instrucțiuni cu virgulă mobilă cu precizie simplă adăugate

- definirea clară a liniei dintre „arhitectură” și „implementare”

- extinderea la arhitectura pe 64 biți.

Aceste schimbări au dus la o nouă arhitectură, denumită oficial PowerPC Architecture, care va sta la baza produselor de generația următoare nu numai de la cele trei companii fondatoare, ci și de la un număr mare de alte companii.[5]

Procesoare PowerPC

[modificare | modificare sursă]Procesoare pentru uz general

[modificare | modificare sursă]PowerPC G1

- 601, 601v

- 602, în special pentru sistemele înglobate

PowerPC G2

- 603, 603e, 603ev: suprascalar, destinat calculatoarelor desktop și laptop

- 604, 604e, 604ev: procesor de înaltă performanță pentru desktop și stații de lucru uniprocesor sau multiprocesor

- 620: prima implementare pe 64 de biți, pentru stații de lucru, servere și sisteme multiprocesor

- Implementarea x704 în tehnologia BiCMOS proiectată de Exponential Technologies

PowerPC G3

- 740

- 745

- 750 (1997): 233 MHz și 266 MHz

- 755

- 750CX, 750CXe (2000): 366 MHz … 600 MHz

- 750FX (2002): 600 MHz … 900 MHz

- 750GX (2003): 733 MHz … 1,1 GHz

- 750CL (2006): 400 MHz … 1 GHz, versiunea low energy a 750GX, utilizat în Wii

PowerPC G4

- 7400/7410 (1999): 550 MHz, cip AltiVec, extensie SIMD a specificației PowerPC originale

- 7450: viteză de ceas de până la 1,5 GHz, 256 KiB Cache L2 și cip AltiVec îmbunătățit

- 7447/7457: viteză de ceas de până la 1,8 GHz și 512 KiB Cache L2

- 7448: tehnologie de 90nm cu 1 MiB Cache L2

- 8641S și 8641D: procesoare single-dual-core bazate pe nucleul e600

PowerPC G5

- 970 (2003): implementare pe 64 de biți se bazează pe un microprocesor IBM POWER4 extins cu o unitate VMX (compatibilă cu unitatea de execuție AltiVec tip SIMD), 512 KiB Cache L2, frecvențe de 1,4 GHz … 2,7 GHz realizate în tehnologie de 130 nm.

- 970FX (2001): 512 KiB Cache L2, produs în tehnologie de 90 nm.

- 970GX (2003): 1 MiB Cache L2, niciodată lansat.

- 970MP (2005): 1,6 GHz … 2,5 GHz cu 1 MiB Cache L2, primul procesor PowerPC dual-core de uz general

- Gekko 485 MHz (folosit în Nintendo GameCube )

- PA6T-1682M (PWRficient) unitate dual-core care funcționează la 2 GHz

Noua generație de procesoare PowerPC, cu numele planificat POWER6, este concepută pentru a funcționa cu ceasuri în gama de 4GHz … 5 GHz și va oferi funcționalitatea simultană MultiThreading.

Procesoare pentru sisteme înglobate

[modificare | modificare sursă]

AMCC

- 440SP: 533 … 667 MHz, 10/100/1G Ethernet, (2) 64 biți PCI-X, 32bit PCI-X, XOR engine, 32k L1 Cache

- 440SPe: 533 … 667 MHz, 10/100/1G Ethernet, (3) 64 biți PCI-Express, 64 biți PCI-X, XOR engine, 32k L1 Cache

- 440EPx: 333 … 667 MHz, (2) 10/100/1G Ethernet, Hardware Security, PCI, DDR2 SDRAM, FPU, USB 2.0, 32k L1 Cache

- 440GR: 333 … 667 MHz, (2) 10/100 Ethernet, (4) UART, (2) IIC, 53 GPIO, SPI, 32k L1 Cache

- 440GRx: 333 … 667 MHz, (2) 10/100/1G Ethernet, (4) UART, (2) IIC, 53 GPIO, SPI, DDR2 SDRAM, Hardware Security, 32 KiB L1 Cache.

- RAD750: versiune pentru misiuni militare și spațiale, bazată pe microprocesorul PowerPC 750 cu rezistență sporită la radiații electromagnetice.

Culturecom

- V-Dragon: bazat pe nucleul microprocesorului PowerPC 405.

IBM

- 401

- 403: cip MMU inclus în versiunea 403GCX

- 405: MMU, Ethernet, UART, PCI, SRAM, SDRAM; versiunea NPe405 a fost înbunătățită cu noi dispozitive de rețea

- 440xx: serie de microprocesoare bazate pe nucleul Book E

- 440EP: 333 … 667 MHz, (2) 10/100 Ethernet, PCI, DDR, FPU, USB 1.1 și 2.0, 32 KiB L1 Cache

- 440GP: 400 … 500 MHz, (2) 10/100 Ethernet, PCI-X, DDR, 32 KiB L1 Cache

- 440GX: 533 … 800 MHz, (2) 10/100 Ethernet, (2) 10/100/1G Ethernet cu descărcare TCP/IP, PCI-X, DDR, 32 KiB L1 Cache.

- MPC 860/8xx (PowerQUICC): controlere de rețea și telecomunicații

- MPC 550/5xx (nucleu 8xx): controlere industriale

- MPC 5200/5200B (nucleu 603e): controlere industriale

- MPC 8260/82xx (PowerQUICC II): controlere de rețea și telecomunicații cu magistrală de date înglobată comutată de înaltă performanță

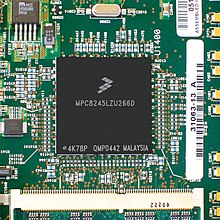

- MPC 8560/85xx (PowerQUICC III): nucleu PowerPC Book E, controlere de rețea și telecomunicații cu magistrală de date comutată de înaltă performanță înglobată.

PA Semi

- PA6T-1682M (PWRficient): unitate dual-core cu frecvența de 2 GHz (niciodată introdus pe piață).

Xilinx

- Virtex-II Pro și Virtex-4: circuite FPGA cu până la patru nuclee PowerPC 405

- Virtex-5: circuite FPGA cu două sau mai multe nuclee PowerPC 440.

Sisteme de operare

[modificare | modificare sursă]- Apple Mac OS 7.1.2 la Mac OS X 10.5.

- GNU+Linux

- Crux PPC

- Debian, până la versiunea 9 (Stretch)

- Fedora

- Gentoo Linux

- OpenSUSE

- Red Hat Enterprise Linux

- Slackintosh

- Ubuntu

- Yellow Dog Linux [6]

- AmigaOS 4.x

- FreeBSD

- IBM AIX

- MorphOS

- NetBSD

- OpenBSD

- OpenSolaris

- ReactOS

- Windows NT 3.51 și 4.0

- Solaris 2.5.1 PowerPC edition

- T2 SDE

- Vine Linux

Sisteme înglobate

- BlueCat LynuxWorks

- eCos

- ENEA OSE

- Integrity

- LynxOS

- Mobilinux

- Microware OS-9

- PikeOS

- QNX

- VxWorks

- LiveDevices RTA-OSEK

- FreeRTOS

- Juniper Networks Junos OS router and switch OS

- RTEMS

- Wind River Systems Linux

Domenii de aplicație

[modificare | modificare sursă]Arhitectura PowerPC este utilizată în prezent ca bază pentru o mare varietate de microprocesoare compatibile cu instrucțiuni. Unul dintre procesoarele de tip PowerPC încă folosit este IBM PPC970FX, cu care sunt echipate calculatoarele Apple Macintosh G5, care ajung până la frecvența tactului de 2,7 GHz. Cel mai nou procesor din familia PowerPC este procesorul cu miez dublu (engleză: dual core) IBM PPC970MP; el se folosește actualmente la computerele de tip Apple PowerMac G5, și anume începând de la 2,0 și 2,3 GHz, și până la 2,5 GHz în cel mai rapid model PowerMac G5 Quad 2,5.

Pe lângă Apple Macintosh procesoarele de tip PowerPC mai sunt utilizate și pentru calculatoarele de tip IBM pSeries (RS/6000) și IBM Blade JS20, apoi în calculatoarele Motorola PowerStack, la sistemele de jocuri Nintendo GameCube și Wii, apoi drept Cell în Playstation 3 a firmei Sony, precum și la Xbox 360 al lui Microsoft și în multe alte sisteme înglobate.

De asemenea ele mai fac parte constituentă din următoarele calculatoare și aparate: Amiga, Genesi Pegasos, Eyetech AmigaOne, receiverele digitale d-box 2 (PPC823), Dreambox (PPC405) și multe alte receivere. Până și cel mai modern avion de luptă american de tip Lockheed Martin F-22 conține sisteme cu procesoare cu arhitectura PowerPC.

În domeniul militar, avionul de luptă american de tip Lockheed Martin F-22 conține sisteme cu procesoare cu arhitectura PowerPC, iar avionul multirol francez Dassault Rafale, are centrala de integrare si fuziune de date (MDPU - Modular Data Processing Unit), construită de Thales, compusă de 18 LRU (Line Replaceable Unit) bazate pe microprocesorul PowerPC.

Vezi și

[modificare | modificare sursă]Referințe și note

[modificare | modificare sursă]- ^ PegasosPPC Platform genesi.company

- ^ Introduction To PowerPC Processor piembsystech.com

- ^ PowerPC on Apple: An Architectural History, Part I arstechnica.com, Jon Stokes, aug 4, 2004

- ^ 16 Conceptele CISC și RISC Arhivat în , la Wayback Machine. tet.pub.ro

- ^ History of the PowerPC architecture thefreelibrary.com

- ^ PowerPC linux.fandom.com

Legături externe

[modificare | modificare sursă]- IBM:PowerPC® Microprocessor Family: The Programming Environments Manual for 32 and 64-bit Microprocessors. Version 2.3

- IBM RT page

- The IBM RT PC ROMP processor and memory management unit architecture

- The OpenPOWER Foundation

Bibliografie

[modificare | modificare sursă]- May, Cathy : The PowerPC Architecture: A Specification for A New Family of RISC Processors, Morgan Kaufmann Publishers, 1994, ISBN 1-55860-316-6 (2nd ed.).

- Jeff Duntemann and Ron Pronk: Inside the PowerPC Revolution, Coriolis Group Books, 1994, ISBN 1-883577-04-7

| ||||||||