WO2015146430A1 - 暗号処理装置、および暗号処理方法、並びにプログラム - Google Patents

暗号処理装置、および暗号処理方法、並びにプログラム Download PDFInfo

- Publication number

- WO2015146430A1 WO2015146430A1 PCT/JP2015/055280 JP2015055280W WO2015146430A1 WO 2015146430 A1 WO2015146430 A1 WO 2015146430A1 JP 2015055280 W JP2015055280 W JP 2015055280W WO 2015146430 A1 WO2015146430 A1 WO 2015146430A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- key

- conversion

- round

- function

- cryptographic processing

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09C—CIPHERING OR DECIPHERING APPARATUS FOR CRYPTOGRAPHIC OR OTHER PURPOSES INVOLVING THE NEED FOR SECRECY

- G09C1/00—Apparatus or methods whereby a given sequence of signs, e.g. an intelligible text, is transformed into an unintelligible sequence of signs by transposing the signs or groups of signs or by replacing them by others according to a predetermined system

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L9/00—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols

- H04L9/06—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols the encryption apparatus using shift registers or memories for block-wise or stream coding, e.g. DES systems or RC4; Hash functions; Pseudorandom sequence generators

- H04L9/0618—Block ciphers, i.e. encrypting groups of characters of a plain text message using fixed encryption transformation

- H04L9/0625—Block ciphers, i.e. encrypting groups of characters of a plain text message using fixed encryption transformation with splitting of the data block into left and right halves, e.g. Feistel based algorithms, DES, FEAL, IDEA or KASUMI

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L9/00—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols

- H04L9/06—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols the encryption apparatus using shift registers or memories for block-wise or stream coding, e.g. DES systems or RC4; Hash functions; Pseudorandom sequence generators

- H04L9/0618—Block ciphers, i.e. encrypting groups of characters of a plain text message using fixed encryption transformation

- H04L9/0631—Substitution permutation network [SPN], i.e. cipher composed of a number of stages or rounds each involving linear and nonlinear transformations, e.g. AES algorithms

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L2209/00—Additional information or applications relating to cryptographic mechanisms or cryptographic arrangements for secret or secure communication H04L9/00

- H04L2209/12—Details relating to cryptographic hardware or logic circuitry

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L2209/00—Additional information or applications relating to cryptographic mechanisms or cryptographic arrangements for secret or secure communication H04L9/00

- H04L2209/24—Key scheduling, i.e. generating round keys or sub-keys for block encryption

Definitions

- the present disclosure relates to a cryptographic processing device, a cryptographic processing method, and a program. More specifically, the present invention relates to a cryptographic processing apparatus, a cryptographic processing method, and a program that execute common key encryption.

- common key block cipher There are various cryptographic processing algorithms, but one of the basic techniques is called common key block cipher.

- the encryption key and the decryption key are common.

- a plurality of keys are generated from the common key, and the data conversion process is repeatedly executed in a certain block unit, for example, a block data unit such as 64 bits, 128 bits, 256 bits.

- DES Data Encryption Standard

- AES Advanced Encryption Standard

- CLEFIA proposed by Sony Corporation in 2007 is one of the common key block ciphers.

- Patent Document 1 Japanese Patent Laid-Open No. 2012-215813.

- Such a common key block cipher algorithm mainly includes an encryption processing unit having a round function execution unit that repeatedly executes conversion of input data, and a key schedule unit that generates a round key to be applied in each round of the round function unit. It is comprised by.

- the key schedule unit first generates an extended key with an increased number of bits based on a master key (primary key) that is a secret key, and applies it to each round function unit of the cryptographic processing unit based on the generated extended key. Generate a round key (subkey).

- a structure for repeatedly executing a round function having a linear conversion unit and a non-linear conversion unit is known.

- typical structures include an SPN (Substitution-Permutation Network) structure, a Feistel structure, and an extended Feistel structure.

- Cryptographic processing devices are required to have resistance to these various attacks, high-speed processing, or downsizing.

- the present disclosure has been made in view of, for example, the above-described situation, and an encryption processing device that realizes improvements in various elements required for an encryption processing device, such as safety, high speed, and downsizing, and encryption processing It is an object to provide a method and a program.

- the first aspect of the present disclosure is: An encryption processing unit that performs round operation on input data to generate output data; A key schedule unit that outputs a round key applied in a round operation in the cryptographic processing unit to the cryptographic processing unit;

- the key schedule part A key register storing a secret key K;

- a key conversion unit that generates a conversion key Kd by a conversion process in which a conversion function G is applied to the secret key K;

- the secret key K and the conversion key Kd are configured to be a round key that is output to the encryption processing unit, or round key generation data.

- the conversion function G is in a cryptographic processing device which is an involution function in which the inverse function G ⁇ 1 is the same function as the function G.

- the second aspect of the present disclosure is: An encryption processing unit that performs round operation on input data to generate output data; A key schedule unit that outputs a round key applied in a round operation in the cryptographic processing unit to the cryptographic processing unit;

- the key schedule part A key register storing a secret key K;

- a key conversion unit that generates a conversion key Kd by a conversion process in which a conversion function G is applied to the secret key K;

- the secret key K and the conversion key Kd are configured to be a round key that is output to the encryption processing unit, or round key generation data.

- Each of the secret key K and the conversion key Kd is a state composed of m ⁇ n elements each having 1 bit or more

- the conversion function G is in the cryptographic processing apparatus in which all the state elements of the secret key K are functions having full diffusion that affects all the state elements of the conversion key Kd.

- the third aspect of the present disclosure is: A cryptographic processing method executed in the cryptographic processing device,

- the cryptographic processing device includes: An encryption processing unit that performs round operation on input data to generate output data;

- a key schedule unit that outputs a round key applied in a round operation in the cryptographic processing unit to the cryptographic processing unit;

- the key schedule part A conversion key Kd is generated by a conversion process in which a conversion function G is applied to the secret key K stored in the key register, A process of setting the secret key K and the conversion key Kd as a round key to be output to the cryptographic processing unit or data for generating a round key;

- the conversion function G is in a cryptographic processing method that is an involution function in which the inverse function G ⁇ 1 is the same function as the function G.

- the fourth aspect of the present disclosure is: A cryptographic processing method executed in the cryptographic processing device,

- the cryptographic processing device includes: An encryption processing unit that performs round operation on input data to generate output data;

- a key schedule unit that outputs a round key applied in a round operation in the cryptographic processing unit to the cryptographic processing unit;

- the key schedule part A conversion key Kd is generated by a conversion process in which a conversion function G is applied to the secret key K stored in the key register, A process of setting the secret key K and the conversion key Kd as a round key to be output to the cryptographic processing unit or data for generating a round key;

- Each of the secret key K and the conversion key Kd is a state composed of m ⁇ n elements each having 1 bit or more,

- the conversion function G is in a cryptographic processing method in which all the state elements of the secret key K are functions having full diffusion properties that affect all the state elements of the conversion key Kd.

- the fifth aspect of the present disclosure is: A program for executing cryptographic processing in the cryptographic processing device,

- the cryptographic processing device includes: An encryption processing unit that performs round operation on input data to generate output data; A key schedule unit that outputs a round key applied in a round operation in the cryptographic processing unit to the cryptographic processing unit;

- the program is stored in the key schedule unit.

- the conversion function G is in a program having an involution property in which the inverse function G ⁇ 1 is the same function as the function G.

- the sixth aspect of the present disclosure is: A program for executing cryptographic processing in the cryptographic processing device,

- the cryptographic processing device includes: An encryption processing unit that performs round operation on input data to generate output data; A key schedule unit that outputs a round key applied in a round operation in the cryptographic processing unit to the cryptographic processing unit;

- the program is stored in the key schedule unit.

- Each of the secret key K and the conversion key Kd is a state composed of m ⁇ n elements each having 1 bit or more,

- the conversion function G is in a program in which all the state elements of the secret key K are functions having full diffusion that affects all the state elements of the conversion key Kd.

- the program of the present disclosure is a program provided by, for example, a storage medium to an information processing apparatus or a computer system that can execute various program codes. By executing such a program by the program execution unit on the information processing apparatus or the computer system, processing according to the program is realized.

- system is a logical set configuration of a plurality of devices, and is not limited to one in which the devices of each configuration are in the same casing.

- a highly secure cryptographic processing configuration with improved resistance to various attacks has a cryptographic processing unit that repeats a round operation on input data to generate output data, and a key schedule unit that outputs a round key applied in the round operation in the cryptographic processing unit to the cryptographic processing unit.

- the unit includes a key register that stores the secret key K, and a key conversion unit that generates a conversion key Kd by a conversion process in which the conversion function G is applied to the secret key K.

- the secret key K and the conversion key Kd are The round key to be output to the encryption processing unit or round key generation data.

- the conversion function G As the conversion function G, an involution property in which the inverse function G ⁇ 1 is the same function as the function G and a function having a full diffusion property are applied. With this configuration, diffusion characteristics are improved, and a highly secure cryptographic processing configuration with improved resistance to various attacks is realized. Note that the effects described in the present specification are merely examples and are not limited, and may have additional effects.

- n bit common key block encryption algorithm corresponding to the key length of k bits. It is a figure explaining the decoding algorithm corresponding to the n bit common key block cipher algorithm corresponding to the key length of k bit shown in FIG. It is a figure explaining the relationship between a key schedule part and an encryption process part. It is a figure explaining the structural example of an encryption processing part. It is a figure explaining the example of the round function of a SPN structure. It is a figure explaining an example of the round function of a Feistel structure. It is a figure explaining an example of an extended Feistel structure. It is a figure explaining an example of an extended Feistel structure. It is a figure explaining the structural example of a nonlinear transformation part.

- S box (S-box) of the nonlinear transformation part of an encryption processing part It is a figure explaining the structural example of S box (S-box) of the nonlinear transformation part of an encryption processing part. It is a figure explaining the structural example of S box (S-box) of the nonlinear transformation part of an encryption processing part. It is a figure explaining the structural example of S box (S-box) of the nonlinear transformation part of an encryption processing part. It is a figure explaining one structural example of a cryptographic processing apparatus. It is a figure which shows the structural example of IC module 700 as a cryptographic processing apparatus. It is a figure which shows the structural example of the smart phone which has an encryption process execution function.

- the common key block cipher (hereinafter sometimes referred to as block cipher) refers to the one defined below.

- the block cipher takes as input plaintext P and key K and outputs ciphertext C.

- n can take an arbitrary integer value, it is usually a predetermined value for each block cipher algorithm.

- a block cipher with a block length of n is sometimes called an n-bit block cipher.

- the bit length of the key is represented by k.

- the key can take any integer value.

- Plaintext P n bits

- Ciphertext C n bits

- K k bits

- FIG. 1 shows a diagram of an n-bit common key block cipher algorithm E corresponding to a key length of k bits.

- the decryption algorithm D corresponding to the encryption algorithm E can be defined as the inverse function E ⁇ 1 of the encryption algorithm E, receives the ciphertext C and the key K as input, and outputs the plaintext P.

- FIG. 2 shows a diagram of a decryption algorithm D corresponding to the encryption algorithm E shown in FIG.

- Block ciphers can be considered in two parts.

- One is the secret key K, and the “key schedule part” that outputs the round key to be applied in each round of the cryptographic processing part in a certain step.

- the other is the round key from the plaintext P and the key schedule part.

- it is a “cryptographic processing unit” that performs data conversion and outputs ciphertext C.

- the relationship between the two parts is shown in FIG.

- the encryption processing unit is configured to be able to execute decryption processing in which the ciphertext C is input and the plaintext P is output. Also in this case, the decryption process using the round key supplied from the key schedule unit is executed. The relationship between the two parts is shown in FIG.

- the cryptographic processing unit used in the following embodiments can be divided into processing units called round functions.

- the round function performs predetermined data conversion on input data and outputs converted data.

- the input data for the round function is, for example, n-bit data being encrypted.

- the output of the round function in one round is supplied as the input of the next round.

- one configuration of the round function includes a calculation configuration with a round key generated based on the key output from the key schedule unit. Specifically, an exclusive OR operation is performed on the n-bit data being encrypted and the round key.

- the total number of round functions is called the total number of rounds, and is a value determined in advance for each cryptographic algorithm.

- Round function Depending on the block cipher algorithm, the round function can take various forms. Round functions can be classified according to the structure adopted by the cryptographic algorithm. As typical structures, an SPN (Substitution-Permutation Network) structure, a Feistel structure, and an extended Feistel structure are exemplified here.

- SPN substitution-Permutation Network

- Feistel structure Feistel structure

- extended Feistel structure extended Feistel structure

- a SPN (Substitution-Permutation Network) structure round function A configuration in which exclusive OR operation with a round key, nonlinear transformation, linear transformation processing, etc. are applied to all n-bit input data. The order of each operation is not particularly determined.

- FIG. 5 shows an example of a round function having an SPN structure.

- the linear conversion unit may be referred to as a P layer (Permutation-layer).

- (A) Feistel structure The n-bit input data is divided into two n / 2-bit data.

- a function (F function) having one of the data and the round key as inputs is applied, and the output is exclusively ORed with the other data. After that, the left and right data are exchanged as output data.

- F function function having one of the data and the round key as inputs

- the output is exclusively ORed with the other data.

- the left and right data are exchanged as output data.

- There are various types of internal structure of the F function but basically, it is realized by a combination of exclusive OR operation, non-linear operation, and linear transformation with round key data as in the SPN structure.

- FIG. 6 shows an example of the round function of the Feistel structure.

- the extended Feistel structure is an extended Feistel structure in which the number of data divisions is 2 and is divided into 3 or more. If the number of divisions is d, various extended Feistel structures can be defined by d. Since the input / output size of the F function is relatively small, it is said that it is suitable for small packaging.

- Nonlinear conversion unit tends to increase the cost in mounting as the size of input data increases. In order to avoid this, it is often the case that the target data is divided into a plurality of units and nonlinear transformation is performed on each of the units. For example, the input size is set to ms bits, and these are divided into m pieces of data of s bits, and nonlinear conversion having s bits input / output is performed on each of them.

- These non-linear conversion execution units in s bit units are called S-boxes. An example of the S box (S-box) is shown in FIG.

- the input data consisting of ms bits is divided into m s-bit data, and each divided data is input to m S-boxes that execute s-bit nonlinear conversion processing,

- the output of each S box is concatenated to obtain an ms-bit nonlinear conversion result.

- the linear conversion unit can be defined as a matrix due to its nature.

- the matrix elements can be expressed in various ways, such as a body element of the extension field GF (2 8 ) or an element of GF (2).

- FIG. 10 shows an example of a linear conversion unit having an ms-bit input / output and defined by an m ⁇ m matrix defined on GF (2 s ).

- FIG. 11 shows an example in which input data is represented as A, output data after data conversion for input data A is represented as B, and input data A and output data B are represented as states each having an m ⁇ n array.

- the input data A is an element of the extension field GF (2 s ) mn

- Input data A (a 0 a 1 a 2 ... A mn ⁇ 2 a mn ⁇ 1 ).

- a 0 MSB

- a mn-1 is the bit data of the LSB side.

- the output data B is an element of the extension field GF (2 s ) mn

- Output data B (b 0 b 1 b 2 ... B mn ⁇ 2 b mn ⁇ 1 ).

- B 0 is MSB and b mn ⁇ 1 is bit data on the LSB side.

- an m ⁇ n array state includes m ⁇ n elements.

- state A shown in FIG. 11 includes mn elements a 0 to a nm ⁇ 1 .

- the elements of state B are mn elements from b 0 to b nm ⁇ 1 .

- each element is bit data such as 4-bit data and 8-bit (1 byte) data, for example.

- bit data such as 4-bit data and 8-bit (1 byte) data

- FIG. 12 shows an example of the 4 ⁇ 4 state when each of the 16 elements included in the 4 ⁇ 4 state is 4-bit data.

- the input data is A

- the output data after some data conversion is B

- the input data A is an element of the extension field GF (2 4 ) 4 ⁇ 4

- Input data A (a 0 a 1 a 2 ... A 14 a 15 ).

- a 0 is MSB

- a 15 is the bit data of the LSB side.

- the output data B is an element of the expansion field GF (2 4 ) 4 ⁇ 4

- Output data B (b 0 b 1 b 2 ... B 14 b 15 ).

- B 0 is MSB and b 15 is bit data on the LSB side.

- the example shown in FIG. 12 is an example in which input data A and output data B are expressed as a state having a 4 ⁇ 4 arrangement in which each element is composed of 4-bit data.

- state A shown in FIG. 12 includes 16 elements a 0 to a 15 , each of which is 4-bit data. That is, when the 64-bit input data A is shown as a state, each element shown in FIG. 12 can be expressed as a state A having a 4 ⁇ 4 arrangement of 4-bit data.

- state B shown in FIG. 12 includes 16 elements b 0 to b 15 , each of which is 4-bit data. That is, when the 64-bit output data B is shown as a state, each element shown in FIG. 12 can be expressed as a state B having a 4 ⁇ 4 array of 4-bit data.

- the output data B is calculated by an exclusive OR operation between the round key K output from the key schedule unit and the input data A. All of the input data A, the round key K, and the output data B are 64-bit data expressed in a state composed of 16 4-bit elements.

- (XOR) indicates an exclusive OR operation.

- One round operation is set by a combination of operations that sequentially execute the above operations (1) to (3) in a predetermined sequence.

- a round operation is repeatedly executed on the input data to generate and output output data, for example, encrypted data.

- the basic round operation is set such that exclusive OR operation with a round key, linear conversion processing, and nonlinear conversion processing are executed once each.

- an irregular round operation configuration can be set in the round operation executed in the cryptographic processing sequence.

- many configurations are used in which only the operation with the round key is executed at the beginning or end of the cryptographic processing sequence. This process is called a key whitening process and is not generally counted as the number of rounds.

- Each of X 0 , X 1 ,..., X n ⁇ 1 is an m ⁇ m matrix in which each element is composed of elements on GF (2 s ).

- FIG. MC [X 0 , X 1 ,..., X n ⁇ 1 ]

- the elements of the state columns (0 to n ⁇ 1) and the matrix X 0 , X 1, ..., X n ⁇ 1 corresponding to each column are applied to the elements of the state expression data.

- Matrix operations are defined as column diffusion operations. Note that MC means diffusion (Mix) in units of columns (Column), that is, (MixColumn).

- a matrix operation in which one matrix X k is applied to an element of one column of the state is performed.

- the matrix X k applied to each of a plurality of columns constituting the state can be set to be the same matrix or set to be different.

- an arithmetic expression for calculating the state B, which is output data, by executing a column diffusion operation on the state A, which is input data can be expressed as follows.

- B MC [X 0 , X 1 ,..., X n ⁇ 1 ] (A)

- t (b 1 b 2 ... B k ) represents a transposed matrix of (b 1 b 2 ... B k ).

- FIG. Input data A is 64-bit data and state A is state A consisting of 16 4-bit data elements.

- the output data B is also 64-bit data, and the state B is a state B composed of 16 4-bit data elements.

- the elements of state B calculated by the above arithmetic expression are as follows.

- t (b 0 b 1 b 2 b 3 ) X 0 ⁇ t (a 0 a 1 a 2 a 3 ),

- t (b 4 b 5 b 6 b 7) X 1 ⁇ t (a 4 a 5 a 6 a 7),

- t (b 8 b 9 b 10 b 11) X 2 ⁇ t (a 8 a 9 a 10 a 11),

- t (b 12 b 13 b 14 b 15 ) X 3 ⁇ t (a 12 a 13 a 14 a 15 )

- the above arithmetic expressions are shown in accordance with the actual element arrays of states A and B, the following arithmetic expressions are obtained as shown in the lower part of FIG.

- MC [X] when performing a matrix operation applying the same matrix X to each column element of the state, MC [X] Sometimes expressed. That is, MC [X] and MC [X, X,.

- Each of X 0 , X 1 ,..., X m ⁇ 1 is an n ⁇ n matrix in which each element is composed of elements on GF (2 s ).

- MR [X 0 , X 1 ,..., X m ⁇ 1 ]

- a matrix operation in which the above operation is applied to the elements of the state expression data by applying the elements of each row (0 to n ⁇ 1) of the state and the matrix X 0 , X 1, ..., X m ⁇ 1 corresponding to each row. Is defined as a row diffusion operation.

- MR means diffusion (Mix) in units of rows, that is, (MixRow).

- a matrix operation in which one matrix X k is applied to elements in one row of the state is performed.

- the matrix X k applied to each of a plurality of rows constituting the state can be set to be the same matrix or different matrix settings.

- an arithmetic expression for calculating the state B that is the output data by performing the row diffusion operation on the state A that is the input data can be expressed as follows.

- B MR [X 0 , X 1 ,..., X m ⁇ 1 ] (A)

- This row diffusion calculation process is the process shown in the lower part of FIG.

- FIG. Input data A is 64-bit data and state A is state A consisting of 16 4-bit data elements.

- the output data B is also 64-bit data, and the state B is a state B composed of 16 4-bit data elements, Row diffusion operation: MR [X 0 , X 1 , X 2 , X 3 ] It is the figure which showed the example of application processing.

- the elements of state B calculated by the above arithmetic expression are as follows.

- t (b 0 b 4 b 8 b 12) X 0 ⁇ t (a 0 a 4 a 8 a 12),

- t (b 1 b 5 b 9 b 13 ) X 1 ⁇ t (a 1 a 5 a 9 a 13 ),

- t (b 2 b 6 b 10 b 14 ) X 2 ⁇ t (a 2 a 6 a 10 a 14 ),

- t (b 3 b 7 b 11 b 15 ) X 3 ⁇ t (a 3 a 7 a 11 a 15 )

- the above arithmetic expression is shown according to the actual element arrangement of states A and B, the following arithmetic expression is obtained as shown in the lower part of FIG.

- MR [X] when performing a matrix operation applying the same matrix X to each row element of the state, MR [X] Sometimes expressed. That is, MR [X] and MR [X, X,..., X] are the same calculation.

- D (C, k1, k2,..., Kr) E (C, KR,..., K2, K1) That is, when the decryption function D is configured to use the same function only by reversing the order of application of the round keys in the encryption function E, This common key block cipher is said to have involution.

- the common key block cipher that can form the decryption function D only by changing the input order of the round keys using the encryption function E has involution.

- the Feistel type common key block cipher usually has an involution property because it is known that the encryption function and the decryption function can be performed by the same circuit only by reversing the use order of the round keys to be used.

- An involution common key block cipher basically implements an encryption function and implements an encryption function and a decryption function only by implementing an encryption function, so it requires fewer circuits and can be reduced in weight (miniaturized). Yes, mounting efficiency is high.

- the differential attack is an attack in which data having a specific difference is input to the cryptographic apparatus, data that reflects the input difference is detected from the output, and a key is estimated. Note that the propagation probability of the difference value is called the difference probability.

- a linear attack is an attack that attempts to estimate a key by observing the correlation between the exclusive OR of specific bits at the input and the exclusive OR of specific bits at the output, and finding a strong correlation. is there. Note that the correlation coefficient of specific bits of input and output is called linear probability.

- Highly secure ciphers are ciphers that are highly resistant to various attacks as described above, that is, ciphers that are difficult to decipher secret information applied to cryptographic processing, such as keys.

- ciphers that are difficult to decipher secret information applied to cryptographic processing, such as keys.

- cryptographic processing such as keys.

- a plurality of data serving as the security index of the encryption algorithm will be described.

- Branch n ( ⁇ ) min ⁇ ⁇ 0 ⁇ hw n ( ⁇ ) + hw n ( ⁇ ( ⁇ )) ⁇

- min ⁇ ⁇ 0 ⁇ X ⁇ represents the minimum value of all X ⁇ satisfying ⁇ ⁇

- hw n (Y) is a function that returns the number of elements in which all n-bit data is not 0 (non-zero) when the bit string Y is divided into n bits.

- a mapping ⁇ such that the branch number Branch n ( ⁇ ) is b + 1 is called an optimal diffusion mapping (Optical Diffusion Mappings).

- the MDS matrix is a matrix in which an arbitrary small matrix constituting the matrix is a regular matrix.

- a regular matrix is a matrix having an inverse matrix, where the matrix is A and the inverse matrix is A ⁇ 1 .

- an S box (S-box) that performs nonlinear transformation in units of s bits is used for the nonlinear transformation unit set in the common key block cipher.

- S-box an S box that performs nonlinear transformation in units of s bits

- a minimum number of differential active S-boxes included in a differential path expressing a differential connection relationship that is, a minimum differential active S-box number.

- the difference path is a specific difference value specified for all data parts except key data in the encryption function.

- the difference value is not freely determined, and the difference values before and after the conversion process are related to each other.

- the relationship between the input difference and the output difference is determined one-to-one.

- the relationship between the input difference and the output difference is not one-to-one, but the concept of probability is introduced.

- the probability for a certain input difference and output difference can be calculated in advance. The sum of the probabilities for all outputs is 1.

- the difference path having a probability other than 0 is a set of difference data starting from the difference value for the plaintext (input) and reaching the difference value for the ciphertext (output), and for all S-boxes.

- Difference values given before and after have a probability other than zero.

- a difference value input to an S-box of a certain differential path having a probability other than 0 is not 0, and is called a differential active S-box.

- the smallest number among the differential active S-box numbers of all differential paths having a probability other than 0 is called the minimum differential active S-box number, and this value is well known as a safety index against differential attacks.

- the linear path is often called a linear approximation, but the term “path” is used here in order to correspond to the difference.

- the linear path is a path in which a specific linear mask value is designated for all data portions except key data in the encryption function.

- the linear mask value is not freely determined, and the linear mask values before and after the conversion process are related to each other. Before and after the linear conversion process, the relationship between the input linear mask value and the output linear mask value is determined one-to-one.

- the relationship between the input linear mask value and the output linear mask value is not determined one-to-one, but the concept of probability is introduced.

- For an input linear mask value there is a set of one or more linear mask values that can be output, and the probability that each will be output can be calculated in advance. The sum of the probabilities for all outputs is 1.

- a linear path having a probability other than 0 is a set of linear mask value data starting from a linear mask value for plaintext (input) to a linear mask value for ciphertext (output).

- the linear mask values given before and after the box (S-box) have a probability other than zero.

- a non-zero linear mask value input to an S box (S-box) of a certain linear path having a probability other than 0 is referred to as a linear active S box (S-box).

- the smallest number of active S-boxes (S-boxes) of all linear paths with non-zero probabilities is called the minimum linear active S-box (S-box) number, and this number is a safety measure against linear attacks.

- S-box The minimum linear active S-box

- the cryptographic processing device of the present disclosure described below is a device that executes a common key block cipher (block cipher), and is a device that has a Substitution-Permutation Network (SPN) structure round function.

- block cipher common key block cipher

- SPN Substitution-Permutation Network

- the cryptographic processing apparatus 100 includes a key schedule unit 110 and a cryptographic processing unit 120.

- the key schedule unit 110 receives the secret key K and outputs a round key to be applied in each round of the encryption processing unit 120 according to a predetermined key generation algorithm.

- the cryptographic processing unit 120 receives the round key from the key scheduling unit 110, converts the plaintext P data, and outputs the ciphertext C.

- the encryption processing unit 120 can also execute a decryption process in which the ciphertext C is input and the plaintext P is output. When executing the decryption process, a process in which the round keys supplied from the key schedule unit 110 are applied in the reverse order of the encryption process is executed.

- the encryption processing unit 120 An exclusive OR unit 121 that performs an exclusive OR operation between the input data and the round key, A non-linear transformation unit 122 that performs non-linear transformation processing on input data; A linear transformation unit 123 that performs linear transformation processing on input data; Have

- the cryptographic processing unit 120 of the cryptographic processing device 100 of the present disclosure has a configuration in which an exclusive OR unit 121, a nonlinear conversion unit 122, a linear conversion unit 123, and these three different data conversion processes are repeatedly executed. Have.

- the plaintext P as input data and the ciphertext C as output data are the state expression data described above, and each element is composed of 4 bits and 16 elements of 4 ⁇ 4. This is 64-bit data. Note that the round key input from the key schedule unit 110 is also 64-bit data expressed in a state consisting of 16 4-bit data elements.

- the non-linear conversion process executed in the non-linear conversion unit of the cryptographic processing unit 120 is executed using a plurality of S boxes (S-boxes) as shown in FIG. 22 (1), for example.

- the linear transformation process performed in the linear transformation part of the encryption processing part 120 is performed as a matrix calculation process as shown, for example in FIG. 22 (2).

- the cryptographic processing unit 120 of the cryptographic processing device 100 has a configuration in which an exclusive OR operation, a non-linear conversion, and a linear conversion process with a round key are repeatedly executed for a plurality of rounds. .

- One of the features of the cryptographic processing apparatus according to the present disclosure is that the linear conversion process executed in each round is executed as a different process for each round.

- details of the linear conversion processing executed by the cryptographic processing device according to the present disclosure will be described.

- FIG. 23 is a diagram illustrating a configuration example of a different linear conversion unit included in the cryptographic processing unit of the cryptographic processing device according to the present disclosure.

- the configuration diagram of FIG. 23 is a configuration diagram in which the exclusive OR unit is omitted.

- Linear converters P1, 201, Linear converters P2, 202, Linear converters P3, 203 These three different linear conversion units are configured to execute any one of these three different linear conversion processes in each round, and different linear conversion processes are performed without continuing the same linear change process in successive rounds. It is in setting.

- the above four different matrices M 0 to M 3 are used in combination.

- the above four matrices are non-MDS matrices that are not the above-described MDS (Maximum Distance Separable) matrix.

- MDS Maximum Distance Separable

- FIG. 24 (2) is a diagram illustrating a specific matrix calculation mode of the linear conversion processes P1 to P3.

- a 4 ⁇ 4 rectangle shown in FIG. 24 (2) indicates a state composed of 16 elements each having 4 bits for a linear conversion process. That is, it is a 64-bit 4 ⁇ 4 state.

- a matrix operation using a combination of the matrices M 0 to M 3 is executed on the 4 ⁇ 4 state input data.

- the linear transformation process P1 is For each column element of 4 ⁇ 4 state input data, a matrix operation is performed by applying one matrix M 0 for each column. This is the column diffusion operation (MixColumn) described above with reference to FIGS.

- the linear transformation process P1 is MC [M 0 ] It is a column diffusion calculation (MC) shown by the above formula.

- MC [M 0 ] is an expression indicating a matrix operation in which the same matrix M 0 is applied to each column of the state, and an expression individually indicating a matrix to be applied to each column of the state, MC [M 0 , M 0 , M 0 , M 0 ] It has the same meaning as the above formula.

- the linear transformation process P2 is MR [M 0 , M 1 , M 2 , M 3 ]

- This is a row diffusion operation (MixRow) represented by the above equation.

- the linear conversion process P3 will be described. Similarly to the linear conversion process P2, the linear conversion process P3 performs a matrix operation in which a different matrix is applied to each row element of 4 ⁇ 4 state input data as shown in FIG. 24 (2). . Unlike the linear transformation process P2, the linear transformation process P3 executes a matrix operation that applies the following matrix to the first to fourth rows. 1st row: application matrix M 2 , Second row: application matrix M 0 , 3rd row: application matrix M 1 , 4th row: application matrix M 3 , This is the row diffusion operation (MixRow) described above with reference to FIGS.

- the linear transformation process P2 is performed as row diffusion calculation type 1 (MixRow1)

- the linear transformation process P3 is performed by row diffusion calculation type 2 (MixRow2), Call it.

- the linear transformation process P1 is a column diffusion calculation (MixColumn).

- FIG. 25 is a diagram for explaining a specific calculation process example of the linear conversion process P1, that is, the column diffusion calculation (MixColumn).

- Input A is a state composed of 16 elements a 0 to a 15 of n-bit data.

- the output B is also a state composed of 16 elements b 0 to b 15 of n-bit data.

- n 4

- each element has 4-bit data

- both input A and output B are 64 bits.

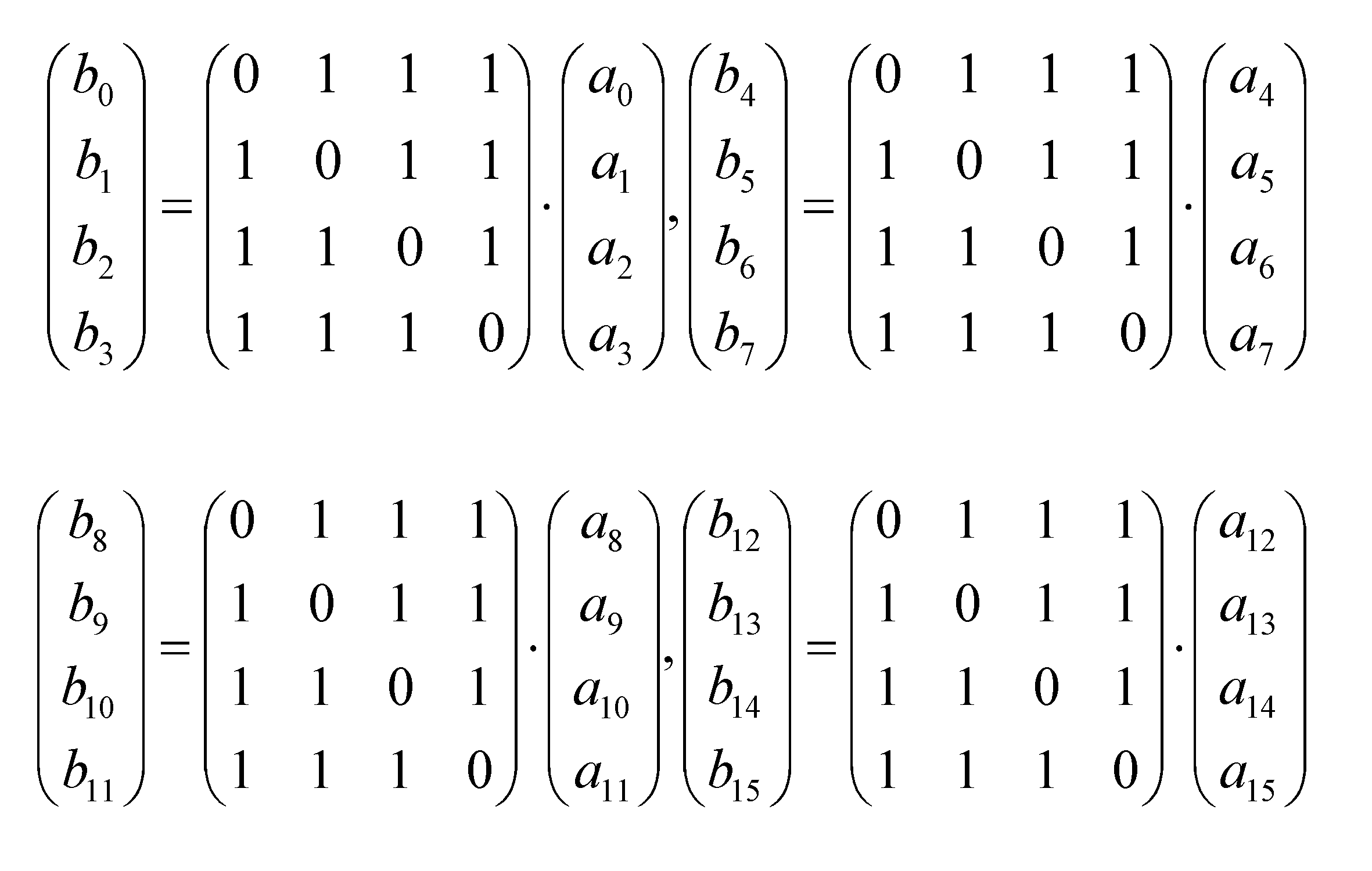

- FIG. 25 (2) shows a specific calculation process example of the linear conversion process P1, that is, the column diffusion calculation (MixColumn).

- the column diffusion operation (MixColumn) performed as the linear transformation process P1 is a matrix operation according to the following equation.

- the 16 elements b 0 to b 15 of the output B are calculated by the following calculation based on the matrix M 0 and the 16 elements a 0 to a 15 of the input A.

- b 0 a 1 (+) a 2 (+) a 3

- b 1 a 0 (+) a 2 (+) a 3

- b 2 a 0 (+) a 1 (+) a 3

- b 3 a 0 (+) a 1 (+) a 2

- b 4 a 5 (+) a 6 (+) a 7

- b 5 a 4 (+) a 6 (+) a 7

- b 6 a 4 (+) a 5 (+) a 7

- b 7 a 4 (+) a 5 (+) a 6

- b 8 a 9 (+) a 10 (+) a 11

- b 9 a 8 (+) a 10 (+) a 11

- b 10 a 8 (+) a 9 (+) a 9 (+) a 10 (+

- the column diffusion calculation (MixColumn) performed as the linear conversion process P1 is performed according to the calculation process described above, based on the matrix M 0 and the 16 elements a 0 to a 15 of the input A to the 16 elements b 0 to b of the output B. to calculate the b 15.

- FIG. 26 is a diagram for explaining a specific calculation process example of the linear conversion process P2, that is, the row diffusion calculation type 1 (MixRow1).

- Input A is a state composed of 16 elements a 0 to a 15 of n-bit data.

- the output B is also a state composed of 16 elements b 0 to b 15 of n-bit data.

- n 4

- each element has 4-bit data

- both input A and output B are 64 bits.

- FIG. 26 (2) shows a specific calculation process example of the linear conversion process P2, that is, the row diffusion calculation type 1 (MixRow1).

- the row diffusion calculation type 1 (MixRow1) performed as the linear transformation process P2 is a matrix calculation according to the following equation.

- the 16 elements b 0 to b 15 of the output B are calculated by the following calculation based on the matrices M 0 , M 1 , M 2 , and M 3 and the 16 elements a 0 to a 15 of the input A. .

- b 0 a 4 (+) a 8 (+) a 12

- b 1 a 1 (+) a 5 (+) a 13

- b 2 a 2 (+) a 6 (+) a 10

- b 3 a 3 (+) a 11 (+) a 15

- b 4 a 0 (+) a 8 (+) a 12

- b 5 a 1 (+) a 5 (+) a 9

- b 6 a 2 (+) a 6 (+) a 14

- b 7 a 7 (+) a 11 (+) a 15

- b 8 a 0 (+) a 4 (+) a 12

- b 9 a 5 (+) a 9 (+) a 13

- b 10 a 2 (+) a 10 (+) a 14

- b 11 a 3 (+) a 7 (+) a 11

- b 12 a 0 (+) a 4 (+) a 12

- b 9 a 5 (+) a 9 (+) a 13

- the row diffusion calculation type 1 (MixRow1) performed as the linear conversion process P2 is based on the matrix M 0 , M 1 , M 2 , M 3 and the 16 elements a 0 to a 15 of the input A according to the above calculation process.

- 16 elements b 0 to b 15 of the output B are calculated.

- FIG. 27 is a diagram for explaining a specific calculation example of the linear conversion process P3, that is, the row diffusion calculation type 2 (MixRow2).

- Input A is a state composed of 16 elements a 0 to a 15 of n-bit data.

- the output B is also a state composed of 16 elements b 0 to b 15 of n-bit data.

- n 4

- each element has 4-bit data

- both input A and output B are 64 bits.

- FIG. 27 (2) shows a specific calculation process example of the linear conversion process P2, that is, the row diffusion calculation type 2 (MixRow2).

- the row diffusion calculation type 2 (MixRow2) performed as the linear conversion process P3 is a matrix calculation according to the following equation.

- the 16 elements b 0 to b 15 of the output B are calculated by the following calculation based on the matrices M 0 , M 1 , M 2 , and M 3 and the 16 elements a 0 to a 15 of the input A. .

- b 0 a 0 (+) a 4 (+) a 8

- b 1 a 5 (+) a 9 (+) a 13

- b 2 a 2 (+) a 6 (+) a 14

- b 3 a 3 (+) a 11 (+) a 15

- b 4 a 0 (+) a 4 (+) a 12

- b 5 a 1 (+) a 9 (+) a 13

- b 6 a 2 (+) a 6 (+) a 10

- b 7 a 7 (+) a 11 (+) a 15

- b 8 a 0 (+) a 8 (+) a 12

- b 9 a 1 (+) a 5 (+) a 13

- b 10 a 6 (+) a 10 (+) a 14

- b 11 a 3 (+) a 7 (+) a 11

- the row diffusion calculation type 2 (MixRow2) performed as the linear conversion process P3 is based on the matrix M 0 , M 1 , M 2 , M 3 and the 16 elements a 0 to a 15 of the input A according to the calculation process.

- 16 elements b 0 to b 15 of the output B are calculated.

- the number of active S boxes in the cryptographic processing device of the present disclosure that is, the cryptographic processing device that executes three different types of linear transformation processing P1 to P3 and the cryptographic processing device that repeatedly executes a single type of linear transformation processing of the conventional type Verified.

- the cryptographic processing device of the present disclosure has a configuration in which three types of linear conversion processing are used in the cryptographic processing sequence, and these are switched and executed for each round.

- the exclusive OR operation unit with the round key is omitted.

- the number of non-linear conversion units is the number of rounds.

- seven round keys of the round keys RK 1 to RK 7 are applied. However, since there are six layers of non-linear conversion units, it is assumed that the encryption processing apparatus is six rounds.

- Linear transformation processing P1 is a sequence spreading operation of applying the matrix M 0 (MixColumn).

- the linear transformation process P2 is a row diffusion calculation type 1 (MixRow1) to which the matrices M 0 , M 1 , M 2 , and M 3 are applied.

- the linear transformation process P3 is a row diffusion calculation type 2 (MixRow2) to which the matrices M 0 , M 1 , M 2 , and M 3 are applied.

- FIG. 29 shows an example of a cryptographic processing apparatus that executes a conventional single linear conversion process for the cryptographic processing apparatus shown in FIG.

- the cryptographic processing apparatus shown in FIG. 29 also has a 6-round configuration, but the linear conversion processing in each round is configured to perform the same linear conversion processing.

- Both the configurations of FIG. 28 and FIG. 29 are settings for executing the encryption process on the 64-bit input plaintext P and outputting the 64-bit ciphertext C.

- the S box is set in each nonlinear conversion unit, and each S box is configured to execute a 4-bit input / output nonlinear conversion as described above with reference to FIG.

- FIG. 30 shows the result of counting the number of minimum differential / linear differential active S boxes by configuring cryptographic processing apparatuses having different round numbers of 4 to 24 rounds.

- the number of active S-boxes is 4 and the same value in both the conventional configuration in which the same linear conversion unit is repeatedly executed and the configuration in which the different linear conversion processing of the present disclosure is executed. In all cases (except 8), the number of active S boxes is larger in the configuration in which the different linear transformation processing of the present disclosure is performed in any case. This result is shown as a graph in FIG.

- the input data is a state composed of 4 ⁇ 4 elements each having 4 bits

- the linear conversion unit uses four types of matrices M 0 , M 1 , M 2 , and M 3 .

- the configuration for executing the linear transformation process by the matrix operation has been described. However, when the above process is generalized, the following setting is made.

- the linear conversion unit applies a column spreading operation for performing a linear conversion by applying a matrix for each column element of the state, and a state

- the matrix operation is performed in a round operation in one of row diffusion operations in which a matrix is applied in units of each row element to perform linear transformation.

- the linear conversion unit is configured to execute linear conversion processing by matrix operation using a plurality of types of matrices M0 to Mk (k is an integer of 1 or more), and the matrix M0 to Mk for each column element of the state.

- a column diffusion operation that performs linear transformation by applying a selection matrix selected from the above to each column in a specific order, and a selection matrix selected from the matrices M0 to Mk for each row element of the state is applied to each row in a specific order

- the row diffusion operation for performing linear transformation is switched and executed according to the round transition.

- An example of a specific linear transformation processing configuration is, for example, the following configuration.

- A a column diffusion operation that performs linear transformation by applying a selection matrix selected from the matrices M0 to Mk to each column in a specific order for each column element of the state;

- B a row diffusion operation type 1 that performs linear transformation by applying a selection matrix selected from the matrices M0 to Mk to each row in a specific order A for each row element of the state;

- C A row diffusion operation type 2 for performing linear transformation by applying a selection matrix selected from the matrices M0 to Mk in each row element unit of the state to each row in a different order B from a specific order A.

- a cryptographic processing apparatus that executes by switching according to round transition.

- a column diffusion operation for performing linear transformation by applying a selection matrix selected from the matrices M0 to Mk to each row in a specific order for each row element of the state

- B a row diffusion operation type 1 that performs linear transformation by applying a selection matrix selected from the matrices M0 to Mk to each column in a specific order A for each column element of the state

- C A row diffusion operation type 2 for performing linear transformation by applying a selection matrix selected from the matrices M0 to Mk to each column in a sequence B different from the specific sequence A in units of column elements of the state,

- a cryptographic processing apparatus that executes by switching according to round transition.

- the linear conversion unit is configured to execute linear conversion processing by matrix calculation using four types of matrices M0, M1, M2, and M3.

- A a column diffusion operation for performing linear transformation by applying the matrix M0 in units of column elements of the state

- B Row diffusion operation type 1 that performs linear transformation by applying each matrix in the order of the matrices M0, M1, M2, and M3 in units of each row element of the state

- C a row diffusion operation type 2 that performs linear transformation by applying each matrix in a different order from the type 1 for each row element of the state

- a cryptographic processing apparatus that switches and executes the three types of matrix operations in accordance with a round transition.

- the combination of the matrix applied in units of each row element of the state in the row diffusion calculation type 1 and the matrix applied in units of each row element of the state in the row diffusion calculation type 2 is combined in any two rows of the state.

- a total of four matrices that is, two matrices applied in type 1 and two matrices applied in type 2 are assumed to be combinations composed of at least three types of matrices.

- a matrix to be applied to each row of 4 ⁇ 4 states first to fourth rows, M1, M3, M0, M2

- each row of 4 ⁇ 4 states the matrix applied to the first to fourth rows, M0, M2, M3, M1

- a total of four matrices including two matrices applied in type 1 and two matrices applied in type 2 for any two rows of 4 ⁇ 4 states are composed of at least three types of matrices. It becomes a combination.

- the above setting is a combination of at least three types of matrixes including a total of four matrices including two matrices applied in type 1 and two matrices applied in type 2 in any other combination of two rows. .

- the linear conversion unit is configured to execute linear conversion processing by matrix calculation using four types of matrices M0, M1, M2, and M3.

- A a row diffusion operation for performing linear transformation by applying the matrix M0 for each row element of the state;

- B Column diffusion operation type 1 that performs linear transformation by applying each matrix in the order of matrices M0, M1, M2, and M3 in units of column elements of the state;

- C Column diffusion operation type 2 for performing linear transformation by applying each matrix in the order different from type 1 for each column element of the state;

- a cryptographic processing apparatus that switches and executes the three types of matrix operations in accordance with a round transition.

- the combination of the matrix applied in units of each column element of the state in the row diffusion calculation type 1 and the matrix applied in units of each column element of the state in the row diffusion calculation type 2 is an arbitrary state. Assume that a total of four matrices including two matrices applied in type 1 and two matrices applied in type 2 for two columns are composed of at least three types of matrices.

- the cryptographic processing apparatus 100 includes the key schedule unit 110 and the cryptographic processing unit 120.

- the key schedule unit 110 generates a round key to be applied in each round of the cryptographic processing unit 120 according to a predetermined key generation algorithm based on the secret key K, for example, and outputs the round key to the cryptographic processing unit 120.

- the cryptographic processing unit 120 receives the round key from the key scheduling unit 110, converts the plaintext P data, and outputs the ciphertext C. Note that the same processing is performed in the decoding processing.

- the configuration and processing of the key schedule unit 110 that executes the round key generation and supply processing will be described.

- FIG. 32 is a diagram illustrating a configuration example of a key schedule unit in the cryptographic processing device according to the present disclosure.

- the key scheduling part 300 includes a key supply unit (key register) 301 as a storage unit for storing a secret key K 1.

- the key schedule unit 300 outputs the key K 1 to the exclusive OR unit (round key calculation unit) 321 of the first round of the cryptographic processing unit 320. That key K 1 is used as a round key for the first round.

- the key scheduling part 300 inputs the key K 1 in the key conversion unit 302a.

- the key conversion unit 302a generates a conversion key Kd 1 executes a predetermined operation on the key K 1. Further, the conversion key Kd 1 generated by the key conversion unit 302 a is output to the exclusive OR unit (round key calculation unit) 322 of the second round of the encryption processing unit 320. That is, the conversion key Kd 1 is used as a round key for the second round.

- the key scheduling part 300 inputs the conversion key Kd 1 in the key conversion unit 302b.

- the key conversion unit 302b generates the key K 1 by performing a predetermined operation on the conversion key Kd 1.

- This key K 1 is the same key as the key K 1 that is the generation source of the conversion key Kd 1 .

- the key schedule unit 300 outputs the key K 1 generated by the key conversion unit 302 b to the third round exclusive OR unit (round key calculation unit) 323 of the encryption processing unit 320. That key K 1 is used as a round key for the third round.

- the key conversion unit 302c ⁇ f, the key K 1 and the key K 1d are alternately generated, and outputs the generated key to the exclusive OR unit 324 to 327 of the encryption processing unit.

- All of the key conversion units 302a to 302f execute the same calculation. That is, by the same arithmetic processing, A conversion key Kd 1 is generated from the key K 1 , A key K 1 is generated from the conversion key Kd 1 .

- FIG. 33 shows the key K 1 described in FIG. 32 as the base key K and the conversion key Kd 1 as the conversion key Kd.

- Each key shown in FIG. 33 is expressed as 4 ⁇ 4 states of 16 4-bit elements. That is, both are 64-bit key data.

- FIG. 34 is a diagram for explaining processing for generating the conversion key Kd from the base key K.

- the process of generating the conversion key Kd from the base key K is configured by the following two steps.

- S1 An intermediate key S is generated by executing an operation to which the intermediate key generation sequence spreading operation (MixColumn_KSF ()) is applied to the base key K.

- S2 The conversion key Kd is generated by executing an operation to which the conversion key generation sequence spreading operation (MixRow_KSF ()) is applied to the intermediate key S.

- the column diffusion operation (MixColumn) executed in step S1 and the row diffusion operation (MixRow) executed in step S2 are matrix application operations similar to those described above with reference to FIGS. However, the matrix M D to be applied in this key conversion processing is a matrix shown below.

- Matrix M D shown above is a matrix called Hadamard (Hadamard) MDS matrix.

- the MDS matrix is a matrix in which an arbitrary small matrix constituting the matrix is a regular matrix.

- a regular matrix is a matrix having an inverse matrix, where the matrix is A and the inverse matrix is A ⁇ 1 .

- a matrix A having an inverse matrix A ⁇ 1 in which the above equation holds is a regular matrix.

- the mapping ⁇ in which the branch number Branch ( ⁇ ) is b + 1 is called an optimal diffusion transformation

- the MDS matrix is a matrix that performs the optimum diffusion transformation.

- the Hadamard (Hadamard) MDS matrix M D is applied, to perform a column spreading operation in step S1 shown in FIG. 34, the row spreading operation in step S2.

- the column diffusion calculation in step S1 is represented by the following calculation expression.

- MC [M D ] MC [M D , M D , M D , M D ]

- the row diffusion calculation in step S2 is expressed by the following calculation expression.

- MR [M D ] MR [M D , M D , M D , M D ]

- the column spreading operation in step S1 is run against all four columns of the state representation data of 4 ⁇ 4 consisting of 4-bit elements, the applied matrix operation the same Hadamard (Hadamard) MDS matrix M D .

- the row spreading operation in Step S2 is for all four rows of four states represent data ⁇ 4 consisting of 4-bit elements to perform the applied matrix operation the same Hadamard (Hadamard) MDS matrix M D .

- the column diffusion operation MC [M D ] in step S1 shown in FIG. 34 is a matrix operation according to the following equation.

- the row diffusion operation MR [M D ] in step S2 shown in FIG. 34 is a matrix operation according to the following equation.

- the key conversion unit 302 of the key scheduling part 300 shown in FIG. 32 in step S1 shown in FIG. 34, and executes the sequence spreading operation MC of applying the matrix M D [M D], the matrix M in step S2 A row diffusion operation MR [M D ] to which D is applied is executed.

- the conversion key Kd is generated from the base key K by continuously executing these two matrix operations.

- the function G composed of continuous processing of the column diffusion operation MC [M D ] and the row diffusion operation MR [M D ] has involution properties and is in the forward direction. Since the function G and the backward function G ⁇ 1 are the same, the original value is calculated by repeating twice.

- the key conversion unit 302 constitutes a column spreading operation MC of applying the matrix M D [M D], by executing the matrix M D applied row diffusion operation MR [M D], the input data 4

- All of the x4 state components i.e. all 16 components, can affect all 16 components of the output data. That is, data diffusion is performed between all elements in the input / output state.

- Such a data conversion mode is defined as “full diffusion conversion” or diffusion having full diffusion properties.

- the input and output are states each consisting of 16 n-bit elements, and a conversion function f to be applied to the input is assumed.

- B f (A)

- the output state B is set to be calculated according to the above formula.

- Input state A (a 0 , a 1 , a 2 ,... A 15 )

- Output state B (b 0 , b 1 , b 2 ,... B 15 ) It is.

- a i and b i are elements of states A and B.

- the execution function G of the key conversion unit 302 is a function having the following two properties. (1) Full diffusion property that realizes full diffusion conversion, (2) Involution property in which the forward function G and the backward function G ⁇ 1 are the same, It has these two properties.

- the base key K is input to the exclusive OR unit 331 of the encryption processing unit, and an exclusive OR operation with the input state A is performed. Thereafter, the nonlinear / linear conversion unit (S & P) 332 performs nonlinear conversion processing and linear conversion processing. Further, an exclusive OR operation with the conversion key Kd is executed in the exclusive OR operation unit 333 for the output. The output of the exclusive OR operation unit 333 is set to state B.

- This property can be said to be a property that contributes to the safety and implementation performance of the cryptographic processing device. Specifically, improvement of data diffusibility by a key is realized, and high diffusion performance can be exhibited even if the number of rounds is reduced. As a result, it is possible to increase resistance to various attacks. For example, it is possible to further improve resistance to key analysis processing based on an intermediate value matching attack using key dependency.

- the diffusion performance of the data to be converted in the encryption processing unit is improved, and the resistance to various attacks such as encryption processing that is safe with a smaller number of rounds, such as key analysis, is high.

- Cryptographic processing is realized.

- FIG. (1) Cryptographic processing configuration in which the same round key is applied without performing key conversion in each round

- 2 3 shows an example of one encryption processing configuration.

- the box G shown in FIG. 36 (2) corresponds to the key conversion unit 302 shown in FIG.

- the number of rounds necessary for spreading the configuration information (bit string) of the applied key to all the bits of the input plaintext P that is the conversion target data is (Full diffusion).

- R the round function

- the configuration information (bit string) of the applied key is diffused (Full diffusion) to all the bits of the input plaintext P that is the conversion target data.

- the number of rounds required for the number of rounds is the number of rounds in which two base keys K 1 and two conversion keys Kd 1 are used. In the example shown in the figure, there are one round.

- the processing of the present disclosure is applied, the diffusion of the configuration information of the key data with respect to the conversion target data is realized in one round, and a larger diffusion performance is guaranteed without depending on the processing of the round function (R). That is, secure cryptographic processing with high resistance to attacks is realized with a small number of rounds. As a result, high-speed processing and weight reduction are realized.

- the key conversion unit 302 of the key schedule unit 300 of the present disclosure realizes the forward function G and the backward function G- 1 with the same function. Has involution properties. Hereinafter, the effect based on this involution property will be described.

- the cryptographic processing unit includes a number of round function execution units corresponding to the specified number of rounds as hardware.

- the effect of the involution property of the key conversion unit of the present disclosure when the cryptographic processing unit is unrolled-mounted will be described.

- FIG. 37 and FIG. 38 show implementation examples of the following cryptographic processing apparatuses.

- FIG. 37 (1) Hardware implementation example when the key conversion unit (F) does not have the involution property

- FIGS. 38 (2a) and (2b) The key conversion unit (G) has the involution property.

- FIGS. 38 (2a) and (2b) are hardware implementation examples when the key conversion unit (G) has the involution property.

- the example shown in FIG. 38 (2a) is for generating an input key (round key) for the exclusive OR part (round key operation part) of the encryption processing part, similarly to the hardware configuration shown in FIG. 37 (1).

- the key conversion unit G is set in association with each round.

- FIG. 38 (2b) as set a key transformation unit G of only one, the base key K 1 held in advance, exclusive of the cryptographic processing unit to convert the key Kd 1 generated by the key conversion unit G

- This is a configuration in which input is alternately performed with respect to the sum part (round key calculation part).

- keys generated by repetition of conversion processing by the key conversion unit are repetitions of K 1 , Kd 1 , K 1 , Kd 1 , K 1 .

- a base key K 1 the conversion key Kd 1 produced by a single key conversion process performed by the key conversion unit G encryption It becomes possible to alternately input to the exclusive OR part (round key operation part) of the processing part.

- the number of key conversion units G can be reduced to one, and the weight reduction (miniaturization) of hardware mounting is realized.

- FIG. 39 shows a configuration example of a cryptographic processing apparatus corresponding to the configuration shown in FIG. 38 (2b).

- the key conversion unit (G) 302 of the key schedule unit 300 has only one base key held in advance for each exclusive OR unit (round key operation unit) of the encryption processing unit 320. and K 1, it is possible to enter the conversion key Kd 1 generated by the key conversion unit G alternately.

- FIG. 40 shows (a1) cryptographic processing configuration and (a2) round implementation example when the key conversion unit does not have involution property.

- FIG. 41 shows (b1) encryption processing configuration and (b2) round implementation example when the key conversion unit has involution property.

- the encryption processing configuration shown in FIG. 40 (a1) is the same as the configuration described above with reference to FIG. That is, since the key conversion unit F does not have the involution property, the keys obtained as conversion results by the key conversion unit F are sequentially different keys. As shown in FIG. 40 (a1), Kd1, Kd2, Kd3, Kd4, Kd5, and Kd6 are sequentially generated based on the key K1 by the conversion process of the key conversion unit F, and each of these keys is used as a round key. It becomes a structure which inputs sequentially to the exclusive OR part (round key calculating part) of a cryptographic processing part.

- the cryptographic processing unit 350 can be configured with one exclusive OR unit (round key calculation unit) 351 and one nonlinear / linear conversion unit 352.

- the key schedule unit 360 includes a key register 361 for storing and supplying the base key K 1 , a key register 362 for storing and supplying the conversion keys Kd 1 to Kd 6 , a key conversion unit (F) 363, a key

- the switch 364 executes the output switching of the registers 361 and 362.

- the cryptographic processing configuration shown in FIG. 41 (b1) is similar to the configuration described above with reference to FIG. 38 (2b), and the cryptographic processing configuration in which the key conversion unit G has the involution property. It is. That is, since the key conversion unit G has involution properties, the keys generated by repeating the conversion process by the key conversion unit are K 1 , Kd 1 , K 1 , Kd 1 , K 1 . Repeat. Based on this property, as one key conversion unit G as shown in FIG. 41 (b1), a base key K 1, the conversion key Kd 1 produced by a single key conversion process performed by the key conversion unit G encryption It becomes possible to alternately input to the exclusive OR part (round key operation part) of the processing part.

- the cryptographic processing unit 350 can be configured with one exclusive OR unit (round key calculation unit) 351 and one nonlinear / linear conversion unit 352.

- the key schedule unit 370 includes a key register 371 that stores and supplies the base key K 1 and the conversion key Kd 1 and a key conversion unit (G) 372.

- the key schedule unit 360 requires two key registers, one key conversion unit, and one switch. It becomes.

- the key schedule unit 370 having a round implementation configuration when the key conversion unit (G) illustrated in FIG. 41 (b2) has the involution property is configured by one key register and one key conversion unit. It is proved that the weight reduction (miniaturization) of the hardware configuration is realized.

- a key register for sequentially generating, storing, and supplying a plurality of different conversion keys And a new hardware circuit corresponding to the number of gates for the key register is required.

- the key conversion unit of the key schedule unit configured in the cryptographic processing device of the present disclosure has the following two characteristics. (1) Full diffusion property that realizes full diffusion conversion, (2) Involution property in which the forward function G and the backward function G ⁇ 1 are the same, It has these two characteristics.

- FIG. 42 is a diagram illustrating a configuration example of an encryption processing apparatus including a key schedule unit 380 having a key conversion unit having the above-described two characteristics.

- the cryptographic processing apparatus shown in FIG. 42 includes a key schedule unit 380 and a cryptographic processing unit 385.

- the key register 381 of the key schedule unit 380 stores a secret key K generated in advance.

- the secret key K is a consolidated data of the key K 1 and the key K 2.

- the keys K 1 and K 2 are 64-bit keys, and the concatenated data, the secret key K, is 128-bit data.

- G shown in the figure is a key conversion unit, and a function G having these two characteristics, full diffusion property and involution property, is applied, similar to the key conversion unit 302 described above with reference to FIG. A key conversion unit that performs key conversion processing.

- the key schedule unit 380 shown in FIG. 42 includes keys K 1 and K 2 that are divided data of the secret key K stored in the key register 381, and a conversion key Kd obtained by converting these keys in the key conversion unit (G). 1 and Kd 2 are sequentially output to the exclusive OR unit (round key operation unit) of the encryption processing unit 385.

- the keys K 1 and K 2 are 64-bit keys

- the plaintext P to be converted by the encryption processing unit 385 is also 64-bit data.

- the output order of the keys is as follows. Key K 1 , Key K 2 , Conversion key Kd 1 , Conversion key Kd 2 , Key K 1 , Key K 2 , Conversion key Kd 1 , In this order, four types of keys are input to the encryption processing unit 385. Various settings can be made for the key input order.

- FIG. 42 shows a plurality of key conversion units (G).

- this key conversion unit (G) has only one configuration. Is possible.

- FIG. 43 shows the following figures.

- A Configuration of key schedule unit

- b Key output configuration by key schedule unit

- a secret key K generated in advance is stored in the key register 391 of the key schedule unit.

- the secret key K is a consolidated data of the key K 1 and the key K 2.

- the keys K 1 and K 2 are 64-bit keys, and the concatenated data, the secret key K, is 128-bit data.

- the key schedule unit shown in FIG. 43A includes a key conversion unit G393 and exclusive OR units 392 and 394. Similar to the key conversion unit 302 described above with reference to FIG. 32 and subsequent drawings, the key conversion unit G393 performs key conversion processing using a function G having the two characteristics of full diffusion and involution. It is a conversion unit.

- the key schedule unit shown in FIG. 43 (a) generates the following six types of keys based on these components. Key K 1 , Key K 2 , Conversion key Kd 1 , Conversion key Kd 2 , Exclusive OR key K 1 (+) K 2 , Exclusive OR operation conversion key Kd 1 (+) Kd 2 , The key schedule unit shown in FIG. 43A generates these six types of keys and sequentially outputs them to the encryption processing unit.

- the plaintext P to be converted by the encryption processing unit is also 64-bit data.

- the key output order is as follows. Key K 1 , Key K 2 , Conversion key Kd 1 , Conversion key Kd 2 , Exclusive OR key K 1 (+) K 2 , Exclusive OR operation conversion key Kd 1 (+) Kd 2 , Exclusive OR key K 1 (+) K 2 , Exclusive OR operation conversion key Kd 1 (+) Kd 2 , Exclusive OR key K 1 (+) K 2 , Conversion key Kd 2 , Conversion key Kd 1 , Key K 2 , Key K 1 , In this order, six types of keys are input to the encryption processing unit.

- the key input sequence is the same sequence in the reverse order. This means that the key input order in the encryption process for generating the ciphertext C from the plaintext P and the key input order in the decryption process for generating the plaintext P from the ciphertext C can be set to the same setting. This means that hardware and programs applied to encryption processing and decryption processing can be shared, and is a setting that contributes to weight reduction (downsizing) of the apparatus.

- the specific configuration of the cryptographic processing apparatus having the key schedule unit shown in FIG. 43 will be further described later.

- FIG. 44 is a diagram showing that the full diffusion property of the internal state S of the input data (P) is guaranteed when the key conversion function G has full diffusion property.

- the base key K 1 is input to the exclusive OR of the encryption processing unit, is XORed with the input state is made. Thereafter, the round calculation unit R 1 further performs non-linear conversion processing and linear conversion processing. Further, an exclusive OR operation with the conversion key Kd 1 is performed on the output in the exclusive OR operation unit.

- the output (S) of the exclusive OR operation unit Consider the output (S) of the exclusive OR operation unit.

- Full diffusion property is guaranteed between the base key K 1 and the conversion key Kd 1.

- This property can be said to be a property that contributes to the safety and implementation performance of the cryptographic processing device. Specifically, improvement of data diffusibility by a key is realized, and high diffusion performance can be exhibited even if the number of rounds is reduced. As a result, it is possible to increase resistance to various attacks. For example, it is possible to further improve resistance to key analysis processing based on an intermediate value matching attack using key dependency.

- the round necessary for spreading the configuration information (bit string) of the applied key to all the bits of the input plaintext P that is the conversion target data (Full diffusion).

- the number will depend on the round function (R) processing.

- the number of rounds required for spreading the configuration information (bit string) of the applied key to all the bits of the input plaintext P that is the conversion target data is (Full diffusion).

- the diffusion of the configuration information of the key data with respect to the conversion target data is realized in one round, and a larger diffusion performance is guaranteed without depending on the processing of the round function (R). That is, secure cryptographic processing with high resistance to attacks is realized with a small number of rounds. As a result, high-speed processing and weight reduction are realized.

- G function having the full diffusion property

- the G function described below is configured by a combination of the following two functions.

- Df 4 Full diffusion 4-bit function

- B 16-bit replacement function