US20090203172A1 - Enhanced Die-Up Ball Grid Array and Method for Making the Same - Google Patents

Enhanced Die-Up Ball Grid Array and Method for Making the Same Download PDFInfo

- Publication number

- US20090203172A1 US20090203172A1 US12/424,270 US42427009A US2009203172A1 US 20090203172 A1 US20090203172 A1 US 20090203172A1 US 42427009 A US42427009 A US 42427009A US 2009203172 A1 US2009203172 A1 US 2009203172A1

- Authority

- US

- United States

- Prior art keywords

- stiffener

- die

- substrate

- package

- solder balls

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Abandoned

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

- H01L23/36—Selection of materials, or shaping, to facilitate cooling or heating, e.g. heatsinks

- H01L23/367—Cooling facilitated by shape of device

- H01L23/3677—Wire-like or pin-like cooling fins or heat sinks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

- H01L23/36—Selection of materials, or shaping, to facilitate cooling or heating, e.g. heatsinks

- H01L23/373—Cooling facilitated by selection of materials for the device or materials for thermal expansion adaptation, e.g. carbon

- H01L23/3735—Laminates or multilayers, e.g. direct bond copper ceramic substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

- H01L23/42—Fillings or auxiliary members in containers or encapsulations selected or arranged to facilitate heating or cooling

- H01L23/433—Auxiliary members in containers characterised by their shape, e.g. pistons

- H01L23/4334—Auxiliary members in encapsulations

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49811—Additional leads joined to the metallisation on the insulating substrate, e.g. pins, bumps, wires, flat leads

- H01L23/49816—Spherical bumps on the substrate for external connection, e.g. ball grid arrays [BGA]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49838—Geometry or layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/50—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor for integrated circuit devices, e.g. power bus, number of leads

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5384—Conductive vias through the substrate with or without pins, e.g. buried coaxial conductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/562—Protection against mechanical damage

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L24/14—Structure, shape, material or disposition of the bump connectors prior to the connecting process of a plurality of bump connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05599—Material

- H01L2224/056—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05617—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 400°C and less than 950°C

- H01L2224/05624—Aluminium [Al] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/29099—Material

- H01L2224/29198—Material with a principal constituent of the material being a combination of two or more materials in the form of a matrix with a filler, i.e. being a hybrid material, e.g. segmented structures, foams

- H01L2224/29199—Material of the matrix

- H01L2224/2929—Material of the matrix with a principal constituent of the material being a polymer, e.g. polyester, phenolic based polymer, epoxy

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/29099—Material

- H01L2224/29198—Material with a principal constituent of the material being a combination of two or more materials in the form of a matrix with a filler, i.e. being a hybrid material, e.g. segmented structures, foams

- H01L2224/29298—Fillers

- H01L2224/29299—Base material

- H01L2224/293—Base material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/29338—Base material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/29339—Silver [Ag] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32245—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/33—Structure, shape, material or disposition of the layer connectors after the connecting process of a plurality of layer connectors

- H01L2224/331—Disposition

- H01L2224/3318—Disposition being disposed on at least two different sides of the body, e.g. dual array

- H01L2224/33181—On opposite sides of the body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/45144—Gold (Au) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

- H01L2224/48228—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item the bond pad being disposed in a recess of the surface of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48237—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a die pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/48463—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond

- H01L2224/48465—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond the other connecting portion not on the bonding area being a wedge bond, i.e. ball-to-wedge, regular stitch

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/49105—Connecting at different heights

- H01L2224/49109—Connecting at different heights outside the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49171—Fan-out arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73215—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/838—Bonding techniques

- H01L2224/8385—Bonding techniques using a polymer adhesive, e.g. an adhesive based on silicone, epoxy, polyimide, polyester

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L24/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01013—Aluminum [Al]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01039—Yttrium [Y]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01046—Palladium [Pd]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01078—Platinum [Pt]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

- H01L2924/143—Digital devices

- H01L2924/1433—Application-specific integrated circuit [ASIC]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1515—Shape

- H01L2924/15153—Shape the die mounting substrate comprising a recess for hosting the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/15165—Monolayer substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/156—Material

- H01L2924/15786—Material with a principal constituent of the material being a non metallic, non metalloid inorganic material

- H01L2924/15787—Ceramics, e.g. crystalline carbides, nitrides or oxides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/1901—Structure

- H01L2924/1904—Component type

- H01L2924/19041—Component type being a capacitor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/30107—Inductance

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/35—Mechanical effects

- H01L2924/351—Thermal stress

Definitions

- the invention relates generally to the field of integrated circuit (IC) device packaging technology, and more particularly to substrate stiffening and heat spreading techniques in ball grid array (BGA) packages.

- IC integrated circuit

- BGA ball grid array

- Integrated circuit (IC) dies are typically mounted in or on a package that is attached to a printed circuit board (PCB).

- PCB printed circuit board

- One such type of IC die package is a ball grid array (BGA) package.

- BGA packages provide for smaller footprints than many other package solutions available today.

- a BGA package has an array of solder balls located on a bottom external surface of a package substrate. The solder balls are reflowed to attach the package to the PCB.

- the IC die is mounted to a top surface of the package substrate. Wire bonds typically couple signals in the IC die to the substrate.

- the substrate has internal routing which electrically couples the IC die signals to the solder balls on the bottom substrate surface.

- BGA package substrate types including ceramic, plastic, and tape (also known as “flex”).

- a stiffener may be attached to the substrate to supply planarity and rigidity to the package.

- the IC die may be mounted to the stiffener instead of the substrate. Openings in the stiffener may be used to allow the IC die to be wire-bonded to the substrate.

- die-up and die-down BGA package configurations exist.

- the IC die is mounted on a top surface of the substrate or stiffener, opposite of the side to which the solder balls are attached.

- die-down BGA packages the IC die is mounted on a bottom surface of the substrate or stiffener, on the same side as which the solder balls are attached.

- the tape substrate used in flex BGA packages is typically polyimide, which has very low values of thermal conductivity. Consequently, the IC die is separated from the PCB internally by the tape substrate thermal barrier. The lack of direct thermal connection from IC die to PCB leads to relatively high resistance to heat transfer from IC die-to-board (theta-jb).

- a stiffener attached to a substrate enhances heat spreading.

- the openings on the stiffener for wire bond connections tend to reduce the thermal connections between the IC die and the edges of the stiffener.

- heat spreading is limited largely to the region of the IC die attach pad, while areas at the stiffener peripheral do not contribute effectively to heat spreading.

- Ball grid array packages that use plastic substrates (for example, BT or FR4 plastic) are commonly known as plastic BGAs, or PBGAs. See, e.g., Lau, J. H., Ball Grid Array Technology , McGraw-Hill, New York, (1995).

- a PBGA package may add solder balls to the bottom substrate surface under the IC die to aid in conducting heat to the PCB. Solder balls such as these are referred to as thermal balls.

- the cost of the PBGA package will increase with the number of thermal balls. Furthermore, a large array of thermal balls may be necessary for heat dissipation into the PCB for high levels of IC device power.

- a method of assembling a ball grid array (BGA) package includes providing a tape substrate that has a first surface and a second surface, attaching a first surface of a stiffener to the first substrate surface, mounting an IC die to the second stiffener surface, mounting a heat spreader to the IC die, and attaching a plurality of solder balls to the second substrate surface.

- BGA ball grid array

- Another method of assembling a ball grid array (BGA) package includes providing a substrate that has a first surface and a second surface, providing at least one opening in a stiffener from a first surface of the stiffener to the second surface of the stiffener, attaching the first stiffener surface to the first substrate surface, mounting an integrated circuit (IC) die to the second stiffener surface, coupling a contact pad to the second stiffener surface, attaching a plurality of solder balls to the second substrate surface, inside an outer dimensional profile of the IC die, and coupling the plurality of solder balls through corresponding vias in the substrate to the first stiffener surface.

- a first surface of the IC die includes the contact pad.

- Another method of assembling a ball grid array (BGA) package includes the steps of providing a substrate that has a first surface and a second surface, attaching a first surface of a stiffener to the first substrate surface, mounting an IC die to the first stiffener surface, attaching a plurality of solder balls to the second substrate surface, and attaching a metal ring to the first stiffener surface.

- BGA ball grid array

- Another method of assembling a ball grid array (BGA) package includes the steps of providing a substrate that has a first surface and a second surface, mounting an IC die to the first substrate surface, attaching a plurality of solder balls to the second substrate surface, coupling a first surface of a heat spreader to the second substrate surface, and configuring a second surface of the heat spreader to be coupled to a printed circuit board (PCB).

- PCB printed circuit board

- FIGS. 1A and 1B illustrate conventional flex BGA packages.

- FIG. 2A shows a top view of a stiffener.

- FIG. 2B shows a temperature distribution for a stiffener during operation of an IC device in a flex BGA package.

- FIG. 2C shows an top view of an alternative stiffener configuration.

- FIG. 3 shows a cross-sectional view of a conventional die-up plastic BGA package.

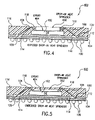

- FIG. 4 illustrates a cross-sectional view of a die-up flex BGA package with heat spreader, according to an embodiment of the present invention.

- FIG. 5 show a cross-sectional view of an alternative BGA package, according to embodiments of the present invention, where the heat spreader is internal to the BGA package.

- FIG. 6 illustrates a cross-sectional view of a die-up flex BGA package with stiffener ground plane, according to an embodiment of the present invention.

- FIG. 7 illustrates a cross-sectional view of a die-up flex BGA package with patterned stiffener, according to an embodiment of the present invention.

- FIG. 8 illustrates a cross-sectional view of a die-up flex BGA package with ground/thermal connector, according to an embodiment of the present invention.

- FIG. 9A illustrates a cross-sectional view of a die-up tape BGA package with metal ring, according to an embodiment of the present invention.

- FIG. 9B illustrates a top view of the die-up tape BGA package with metal ring of FIG. 9A , according to an embodiment of the present invention.

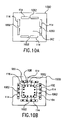

- FIG. 10A illustrates a stiffener that includes one or more thermal studs, according to an embodiment of the present invention.

- FIG. 10B illustrates an IC die that is wire bound to a substrate through openings in the stiffener of FIG. 10A , according to an embodiment of the present invention.

- FIG. 11 illustrates a cross-sectional view of a die-up PBGA package with ground/thermal connector, according to an embodiment of the present invention.

- FIG. 12A illustrates a cross-sectional view of a die-up BGA package.

- FIGS. 12B and 12C illustrate exemplary solder ball arrangements for the die-up BGA package of FIG. 12A .

- FIG. 13 shows exemplary routing in a substrate layer.

- FIG. 14 shows a flowchart related to FIGS. 4 and 5 , that provides operational steps of exemplary embodiments of the present invention.

- FIG. 15 shows a flowchart related to FIG. 6 that provides operational steps of exemplary embodiments of the present invention.

- FIGS. 16A-D show flowcharts related to FIGS. 7 and 8 that provide operational steps of exemplary embodiments of the present invention.

- FIG. 17 shows a flowchart related to FIGS. 9A and 9B that provides operational steps of exemplary embodiments of the present invention.

- FIG. 18 shows a flowchart related to FIGS. 10A and 10B that provides operational steps of exemplary embodiments of the present invention.

- FIGS. 19A-C show flowcharts related to FIG. 11 that provide operational steps of exemplary embodiments of the present invention.

- FIG. 20 illustrates a substrate that has a central window opening, according to an embodiment of the present invention.

- FIG. 21 illustrates a side view of a stiffener that has a downward protruding portion, according to an embodiment of the present invention.

- the present invention is directed to a method and system for improving the mechanical, thermal, and electrical performance of BGA packages.

- the present invention is applicable to all types of BGA substrates, including ceramic, plastic, and tape (flex) BGA packages. Furthermore the present invention is applicable to die-up (cavity-up) and die-down (cavity-down) orientations.

- BGA package thermal stress at the IC die/stiffener interface is released or altered with the introduction of a heat spreader on the top surface of the IC die, enabling large size dies with high input and output (I/O) counts to be packaged using BGA technology.

- BGA package thermal resistance and the length of the current return path are reduced by introducing thermal/ground balls underneath or within close proximity of the IC die.

- the package thermal resistance and ground inductance are reduced by removing center solder balls, and enabling the attachment of a die pad to the PCB.

- the die pad is attached to the PCB with novel patternings of the metal stiffener, or by positioning a thermal/ground connector in between the IC die pad and the PCB.

- the package thermal resistance is reduced by attaching a metal ring to the top surface of a stiffener.

- the package thermal resistance is reduced by bridging the die pad to the outer regions of the stiffener with metal studs.

- the electrical performance of the BGA package is improved.

- electrical performance is improved by connecting ground bonds from the IC die to the stiffener.

- the stiffener operates as a package ground plane.

- the package ground plane may be connected to PCB ground through either thermal/ground balls or thermal/ground connectors mentioned in embodiments above, and further described herein.

- package power distribution is enhanced by using a layer in a tape substrate as a power or ground plane.

- plastic ball grid array (PBGA) package thermal and electrical performances are improved.

- PBGA plastic ball grid array

- Ball grid array package types are described below. Further detail on the above described embodiments, and additional embodiments according to the present invention, are presented below. The embodiments described herein may be combined in any applicable manner, as required by a particular application.

- a ball grid array (BGA) package is used to package and interface an IC die with a printed circuit board (PCB).

- BGA packages may be used with any type of IC die, and are particularly useful for high speed ICs.

- solder pads do not just surround the package periphery, as in chip carrier type packages, but cover the entire bottom package surface in an array configuration.

- BGA packages are also referred to as pad array carrier (PAC), pad array, land grid array, and pad-grid array packages.

- PAC pad array carrier

- BGA packages types are further described in the following paragraphs. For additional description on BGA packages, refer to Lau, J. H., Ball Grid Array Technology, McGraw-Hill, New York, (1995), which is herein incorporated by reference in its entirety.

- die-up and die-down BGA package configurations exist.

- the IC die is mounted on a top surface of the substrate or stiffener, in a direction away from the PCB.

- die-down BGA packages the IC die is mounted on a bottom surface of the substrate or stiffener, in a direction towards the PCB.

- FIG. 1A illustrates a conventional flex BGA package 100 .

- Flex BGA package 100 includes an IC die 102 , a tape substrate 104 , a plurality of solder balls 106 , and one or more wire bonds 108 .

- Tape or flex BGA packages are particularly appropriate for large IC dies with large numbers of input and outputs, such as application specific integrated circuits (ASIC) and microprocessors.

- ASIC application specific integrated circuits

- Tape substrate 104 is generally made from one or more conductive layers bonded with a dielectric material.

- the dielectric material may be made from various substances, such as polyimide tape.

- the conductive layers are typically made from a metal, or combination of metals, such as copper and aluminum. Trace or routing patterns are made in the conductive layer material.

- Substrate 104 may be a single-layer tape, a two-layer tape, or additional layer tape substrate type. In a two-layer tape, the metal layers sandwich the dielectric layer, such as in a copper-Upilex-copper arrangement.

- IC die 102 is attached directly to substrate 104 , for example, by an epoxy.

- IC die 102 is any type of semiconductor integrated circuit, separated from a semiconductor wafer.

- One or more wire bonds 108 connect corresponding bond pads 118 on IC die 102 to contact points 120 on substrate 104 .

- An encapsulate, mold compound, or epoxy 116 covers IC die 102 and wire bonds 108 for mechanical and environmental protection.

- flex BGA package 100 does not include a stiffener.

- a stiffener can be attached to the substrate to add planarity and rigidity to the package.

- FIG. 1B illustrates a flex BGA package 110 , similar to flex BGA package 100 , that incorporates a stiffener 112 .

- Stiffener 112 may be laminated to substrate 104 .

- Stiffener 112 is typically made from a metal, or combination of metals, such as copper, tin, and aluminum, or may be made from a polymer, for example.

- Stiffener 112 also may act as a heat sink, and allow for greater heat spreading in BGA package 110 .

- One or more openings 114 in stiffener 112 may be used to allow for wire bonds 108 to connect IC die 102 to substrate 104 .

- Stiffener 112 may be configured in other ways, and have different opening arrangements than shown in FIG. 1B .

- FIG. 2A shows a top view of a stiffener 112 .

- Stiffener 112 includes an opening 114 adjacent to all four sides of an IC die mounting position 202 in the center of stiffener 112 .

- FIG. 2B shows a temperature distribution 204 of a stiffener, such as stiffener 112 , during operation of an IC die in a flex BGA package. Temperature distribution 204 shows that heat transfer from IC die mounting position 202 to the edges of stiffener 112 is substantially limited by openings 114 . Openings 114 act as thermal barriers to heat spreading in stiffener 112 .

- FIG. 2C shows a top view of an alternative configuration for stiffener 112 , according to an embodiment of the present invention.

- Stiffener 112 includes an opening 206 adjacent to all four sides of an IC die mounting position 202 in the center of stiffener 112 . Openings 206 are similar to openings 114 of FIG. 2A , but of different shape. Further alternatively shaped openings in stiffener 112 are applicable to the present invention.

- FIG. 3 shows a cross-sectional view of a conventional die-up PBGA package 300 .

- PBGA package 300 includes a plastic substrate 302 , an IC die 304 , a plurality of solder balls 306 , a plurality of wire bonds 308 , a die pad 310 , one or more vias 314 , and one or more thermal/ground vias 316 .

- Plastic substrate 302 includes one or more metal layers formed on an organic substrate (for example, BT resin or FR4 epoxy/glass).

- IC die 304 is mounted to die pad 310 .

- IC die 304 may be attached to die pad 310 with an epoxy, such as a silver-filled epoxy.

- Wire bonds 308 connect signals of IC die 304 to substrate 302 .

- gold bonding wire is bonded from aluminum bond pads on IC die 304 to gold-plated contact pads on substrate 302 .

- the contact pads on substrate 302 connect to solder balls 306 attached to the bottom surface of substrate 302 , through vias 314 and routing within substrate 302 using copper conductors 312 .

- Thermal/ground vias 316 connect die pad 310 to one or more thermal/ground balls 322 on the center bottom surface of substrate 302 .

- An encapsulate, mold compound, or epoxy 320 covers IC die 304 and wire bonds 308 for mechanical and environmental protection.

- FIG. 12A illustrates a cross-sectional view of a die-up BGA package 1200 .

- FIGS. 12B and 12C illustrate exemplary solder ball arrangements for die-up BGA package 1200 .

- BGA package 1200 includes an IC die 1208 mounted on a substrate 1212 .

- IC die 1208 is electrically connected to substrate 1212 by one or more wire bonds 1210 .

- Wire bonds 1210 are electrically connected to solder balls 1206 underneath substrate 1212 through corresponding vias and routing in substrate 1212 .

- the vias in substrate 1212 can be filled with a conductive material, such as solder, to allow for these connections.

- Solder balls 1206 are attached to substrate 1212 , and are used to attach the BGA package to a PCB.

- wire bonds such as wire bonds 1210

- IC dies may be mounted and coupled to a substrate with solder balls located on the bottom surface of the IC die, by a process commonly referred to as “C4” or “flip chip” packaging.

- solder balls 1206 may be arranged in an array.

- FIG. 12B shows a 14 by 14 array of solder balls on the bottom surface of BGA package 1200 .

- Solder balls 1206 are reflowed to attach BGA package 1200 to a PCB.

- the PCB may include contact pads to which solder balls 1206 are bonded.

- PCB contact pads are generally made from a metal or combination of metals, such as copper, nickel, tin, and gold.

- FIG. 12C shows a bottom view of BGA package 1200 , with an alternative solder ball array arrangement.

- BGA package 1200 attaches an array of solder balls 1206 on a bottom surface of substrate 1212 .

- solder balls 1206 are located in a peripheral area of the bottom surface of substrate 1212 , away from a substrate center 1224 .

- solder balls 1206 on the bottom surface of substrate 1212 may be located outside an outer profile area of an IC die mounted on the opposite surface of substrate 1212 .

- the solder ball array may be organized in any number of ways, according to the requirements of the particular BGA package application.

- the solder ball arrangement shown in FIG. 12C is particularly applicable to embodiments of the present invention described below, such as for attaching a heat spreader or ground/thermal connector to a bottom surface of a BGA package.

- the heat spreader or ground/thermal connector may be connected in substrate center 1224 .

- the BGA package substrate provides vias and routing on one or more layers to connect contact pads for wire bonds on its upper surface to solder balls attached to the bottom substrate surface.

- FIG. 13 shows an example routing 1304 in a substrate layer 1302 for accomplishing this.

- the present invention is applicable to improving thermal and electrical performance in the BGA package types described herein, and further BGA package types.

- a heat spreader may be used in a BGA package to provide for thermal stress relief and heat dissipation.

- a drop-in heat spreader is attached to the top surface of an IC die in a flex BGA package to provide for thermal stress relief and heat dissipation.

- FIG. 4 illustrates a cross-sectional view of a die-up flex BGA package 400 , according to an embodiment of the present invention.

- BGA package 400 includes IC die 102 , substrate 104 , plurality of solder balls 106 , one or more wire bonds 108 , stiffener 112 , epoxy 116 , a drop-in heat spreader 402 , and an epoxy 404 . Refer to the discussion above related to FIGS. 1A-1B for additional detail on the structure and operation of some of these elements.

- Substrate 104 has a top surface to which a bottom surface of stiffener 112 is mounted. A bottom surface of substrate 104 attaches the plurality of solder balls 106 . The plurality of solder balls 106 connect to vias and/or points on the bottom surface of substrate 104 to which signals internal to substrate 104 are routed and exposed.

- Stiffener 112 has a top surface to which IC die 102 is mounted.

- BGA package 400 does not require a stiffener, and does not include a stiffener 112 .

- IC die 102 is mounted to substrate 104 .

- wire bonds 108 connect corresponding bond pads 118 on IC die 102 to contact points 120 on substrate 104 .

- wire bonds 108 extend through one or more openings 114 in stiffener 112 to form connections with substrate 104 .

- Heat spreader 402 is attached to the top surface (active surface) of IC die 102 using epoxy 404 .

- the epoxy 404 may be the same substance as epoxy 116 , or may be a different substance.

- Silver filled epoxies may be used for epoxy 404 to enhance heat extraction from IC die 102 .

- heat spreader 402 is smaller in area than the upper surface of IC die 102 .

- Alternative sizes for heat spreader 402 are also applicable to the present invention, including sizes equal to the area of IC die 102 , or larger areas.

- Heat spreader 402 is shaped and configured to spread heat from IC die 102 , as is required by the application.

- FIG. 4 the top surface of heat spreader 402 forms a portion of a top surface of BGA package 400 .

- Heat dissipation to the environment can be improved by exposing the top surface of heat spreader 402 .

- additional heat sinks may be attached to heat spreader 402 .

- FIG. 5 show a cross-sectional view of an alternative BGA package 500 , according to embodiments of the present invention, where a heat spreader 502 is internal to BGA package 500 . Heat spreader 502 is completely encapsulated by epoxy 116 .

- the mechanical structure of BGA package 400 becomes more symmetrical in its center region, particularly when ground/thermal solder balls do not exist on the bottom surface of substrate 104 underneath the outer profile of IC die 102 .

- Thermal stress at the interface of IC die 102 and stiffener 112 is substantially released or altered by heat spreader 402 .

- Deformation caused by thermal stress in stiffener 112 and substrate 104 is substantially reduced through the use of heat spreader 402 .

- Drop-in heat spreader 402 allows for even larger sizes for IC die 102 and greater I/O counts by providing for greater heat spreading capacity in BGA package 400 .

- FIG. 14 shows a flowchart 1400 providing operational steps for assembling one or more embodiments of the present invention.

- the steps of FIG. 14 do not necessarily have to occur in the order shown, as will be apparent to persons skilled in the relevant art(s) based on the teachings herein.

- Other structural embodiments will be apparent to persons skilled in the relevant art(s) based on the following discussion. These steps are described in detail below.

- Flowchart 1400 begins with step 1402 .

- a substrate that has a first surface and a second surface is provided.

- the substrate is flex substrate 104 , or another substrate type suitable for a BGA package.

- an IC die mounting position and/or contact points are provided on a first, upper surface, and solder ball pads are provided on a second, bottom surface.

- a first surface of a stiffener is attached to the first substrate surface.

- the stiffener is stiffener 112 , which is attached to substrate 104 .

- a stiffener is not required.

- an IC die is mounted to the second stiffener surface.

- the IC die is IC die 102 , which is mounted to stiffener 112 .

- IC die 102 is mounted directly to the substrate.

- a heat spreader is mounted to the IC die, wherein the heat spreader dissipates heat from the IC die.

- the heat spreader is heat spreader 402 or 502 , which is mounted with epoxy 404 or other attachment means to the upper surface of IC die 102 .

- Heat spreader 402 or 502 typically is mounted to the center of the upper surface of IC die 102 , and covers less than the entire upper surface of IC die 102 .

- the smaller area of heat spreader 402 or 502 allows for bond pads 118 to be exposed on the upper surface of IC die 102 for wire bond connections.

- heat spreader 402 or 502 is of the same size, or comprises a larger area than the upper surface of IC die 102 .

- a plurality of solder balls are attached to the second substrate surface.

- the plurality of solder balls are plurality of solder balls 106 , which connect to vias and/or solder ball pads on the bottom surface of substrate 104 .

- the solder balls may be arranged on the bottom surface of substrate 104 as shown in FIGS. 12B and 12C , or in alternative arrangements.

- the solder balls are used to attach a BGA package to a PCB.

- a benefit of performing the steps of flowchart 1400 is that the heat spreader relieves thermal stress at an interface of the IC die and the first stiffener surface.

- Flowchart 1400 may include the additional step where the second stiffener surface is encapsulated.

- the second stiffener surface may be encapsulated by a resin or molding compound, that also encapsulates the IC die, heat spreader, and wire bonding.

- electrical performance of an IC die, and thermal performance of a corresponding BGA package may be improved by allowing a stiffener to act as a ground plane.

- a stiffener in a die-up tape BGA (Flex BGA) package is coupled to PCB ground through one or more vias to ground solder balls.

- Ground contact pads of the IC die are connected to the stiffener by ground wire bonds.

- one or more metal layers of a flex tape substrate may be coupled to a ground or power potential, to operate as a ground or power plane.

- FIG. 6 illustrates a cross-sectional view of a die-up flex BGA package 600 , according to an embodiment of the present invention.

- BGA package 600 includes IC die 102 , substrate 104 , plurality of solder balls 106 , one or more wire bonds 108 , stiffener 112 , epoxy 116 , one or more ground bonds to stiffener 602 , one or more ground/thermal vias 604 , one or more ground/thermal balls 606 , one or more ground contact pads 608 , one or more power contact pads 610 , and one or more power vias 612 .

- Substrate 104 has a top surface to which a bottom surface of stiffener 112 is mounted. A bottom surface of substrate 104 attaches the plurality of solder balls 106 . The plurality of solder balls 106 connect to vias and/or points on the bottom surface of substrate 104 to which signals internal to substrate 104 are routed and exposed.

- Stiffener 112 has a top surface to which IC die 102 is mounted.

- Wire bonds 108 connect corresponding bond pads 118 on IC die 102 to contact points 120 on substrate 104 .

- Wire bonds 108 extend through one or more openings 114 in stiffener 112 to form connections with substrate 104 .

- IC die 102 has a top surface that includes at least one ground pad 608 .

- Ground pad 608 is coupled to a ground potential signal in IC die 102 .

- a ground wire bond 602 connects ground pad 608 to stiffener 112 .

- the bottom surface of stiffener 112 is coupled to a ground potential signal in the PCB to which BGA package 600 is attached, to cause stiffener 112 to operate as a ground plane.

- Stiffener 112 is coupled to PCB ground through one or more of ground/thermal via 604 that extend through substrate 104 .

- the one or more of ground/thermal vias 604 are located in substrate 104 , underneath IC die 102 , and can be filled with a conductive material, such as solder.

- a ground/thermal solder ball 606 is attached to each ground/thermal via 604 on the bottom surface of substrate 104 .

- Ground/thermal solder ball 606 forms the connection to PCB ground, when reflowed to attach to the PCB.

- Each ground/thermal via 604 connects the respective ground/thermal solder ball 606 to stiffener 112 both electrically and thermally.

- a tape substrate is configured such that a metal layer is used as a package power or ground plane.

- a metal layer is used as a package power or ground plane.

- the bottom metal layer may be used as a power or ground plane.

- PCB package 600 includes a bottom metal layer 614 of a two-layer tape substrate 104 that is coupled to a potential to operate as a power plane, according to an embodiment of the present invention.

- One or more power contact pads 610 on IC die 102 are coupled to a power potential signal in IC die 102 .

- Power contact pad 610 on IC die 102 is connected to a corresponding power via 612 by a power wire bond 616 .

- power wire bond 616 extends through opening 114 .

- Power via 612 extends through substrate 104 .

- Power via 612 can be filled with a conductive material, such as solder.

- Each power via 612 is coupled to the bottom metal layer 614 of substrate 104 .

- one or more power vias 612 may be connected to corresponding solder balls on the bottom of substrate 104 , to connect bottom metal layer 614 to PCB power pads when the solder balls are reflowed.

- a stiffener ground plane, and/or a power/ground plane using a metal layer of a tape substrate allows for very short power and ground connections.

- Current return path lengths are shortened, voltage drop across planes is reduced, and power/ground inductance is reduced.

- the shorter power and ground paths are also significant in reducing a power/ground path resistance, which advantageously reduces required IC device power levels.

- thermal vias in a flex tape substrate and of the use of a thermal ball coupled to a heat spreader in a die-down TBGA package, refer to U.S. Pat. No. 6,020,637, which is incorporated by reference in its entirety herein.

- thermal via and a thermal ball in a plastic substrate BGA package refer to U.S. Pat. No. 5,894,410, which is incorporated by reference in its entirety.

- FIG. 15 shows a flowchart 1500 providing operational steps for assembling one or more embodiments of the present invention.

- the steps of FIG. 15 do not necessarily have to occur in the order shown, as will be apparent to persons skilled in the relevant art(s) based on the teachings herein.

- Other structural embodiments will be apparent to persons skilled in the relevant art(s) based on the following discussion. These steps are described in detail below.

- Flowchart 1500 begins with step 1502 .

- a substrate that has a first surface and a second surface is provided.

- the substrate is flex substrate 104 , or another substrate type suitable for a BGA package.

- an IC die mounting position and/or contact points are provided on a first, upper surface, and solder ball pads are provided on a second, bottom surface.

- step 1504 at least one opening in a stiffener from a first surface of the stiffener to a second surface of the stiffener is provided.

- the at least one opening includes openings 114 in stiffener 112 .

- an opening 114 is located on each of the four edges of IC die 102 .

- the first stiffener surface is attached to the first substrate surface.

- the stiffener is stiffener 112 , which is attached to substrate 104 .

- a stiffener is not required, and is not attached to the substrate.

- an integrated circuit (IC) die is mounted to the second stiffener surface, wherein a first surface of the IC die includes a contact pad.

- the IC die is IC die 102 , which is mounted to stiffener 112 .

- IC die 102 is mounted directly to the substrate.

- the contact pad is ground contact pad 608 .

- the contact pad is coupled to the second stiffener surface.

- contact pad is ground contact pad 608 , which is connected to stiffener 112 by ground wire bond 602 .

- Ground wire bond 602 may be soldered, or otherwise attached to stiffener 112 .

- a plurality of solder balls is attached to the second substrate surface, inside an outer dimensional profile of the IC die.

- the plurality of solder balls include one or more ground/thermal balls 606 , which are arranged on the bottom surface of substrate 104 in the region of substrate center 1224 , shown in FIG. 12C .

- the outer dimensional profile of the IC die is the area bounded by the edges of IC die 102 .

- the plurality of solder balls are coupled through corresponding vias in the substrate to the first stiffener surface.

- the vias include ground/thermal via 604 .

- the vias can be filled with a conductive material, such as solder, to allow the electrical connection of the solder balls to stiffener 112 .

- the substrate includes a metal layer, wherein the metal layer is coupled to a second potential.

- the stiffener has at least one opening extending from the first stiffener surface to the second stiffener surface.

- the second IC die surface includes a second contact pad.

- the second contact pad is coupled to the metal layer through one of the openings in the stiffener and through a corresponding via that extends through the substrate.

- the second contact pad may be coupled to a power or ground potential in the IC die.

- the second contact pad is power contact pad 610

- the metal layer is metal layer 614

- the corresponding via is power via 612 .

- flowchart 1500 may include an additional step, where the contact pad is coupled to a ground potential in the IC die.

- the contact pad may be connected to a ground plane or ground signal in IC die that is routed to the contact pad.

- Flowchart 1500 may include the additional step where the second stiffener surface is encapsulated.

- the second stiffener surface may be encapsulated by a resin or molding compound, that also encapsulates the IC die and wire bonding.

- Flowchart 1500 may include the additional step where a second plurality of solder balls is attached to the second substrate surface, outside an outer dimensional profile of the IC die.

- the second plurality of solder balls are plurality of solder balls 106 , which connect to vias and/or solder ball pads on the bottom surface of substrate 104 .

- the solder balls are arranged on the bottom surface of substrate 104 as shown in FIG. 12B , outside of substrate center 1224 .

- the solder balls are used to attach a BGA package to a PCB.

- electrical performance of the IC device, and thermal performance of a BGA package is improved by enabling an IC die pad to attach to a PCB.

- the IC die pad is attached to the PCB by a novel patterning of the metal stiffener in a die-up tape BGA package.

- the IC die pad is attached to the PCB by placing a thermal/ground connector between the IC die pad and PCB in a die-up tape BGA package.

- a BGA package junction-to-board thermal resistance can be substantially reduced by the attachment of a metal die-attach pad directly to a PCB.

- Metal die-attach pads are coupled to a PCB for package junction-to-board thermal resistance minimization in an exposed pad quad flat pack (QFP), a QFP with exposed heat sink at bottom, and a leadless plastic chip carrier (i.e. LPCC, QFN, SON, QLP) package, for instance.

- QFP exposed pad quad flat pack

- QFP QFP with exposed heat sink at bottom

- a leadless plastic chip carrier i.e. LPCC, QFN, SON, QLP

- All existing such designs that involve an exposed die pad or an exposed heat sink at package bottom are “lead frame” packages.

- the present invention provides for an exposed die-attach pad or heat sink at the bottom of flex BGA packages.

- FIG. 7 illustrates a cross-sectional view of a die-up flex BGA package 700 , according to an embodiment of the present invention.

- BGA package 700 includes IC die 102 , substrate 104 , plurality of solder balls 106 , one or more wire bonds 108 , stiffener 112 , epoxy 116 , ground wire bond to stiffener 602 , ground contact pad 608 , and a stiffener cavity 702 .

- Substrate 104 has a top surface to which a bottom surface of stiffener 112 is mounted. A bottom surface of substrate 104 attaches the plurality of solder balls 106 . The plurality of solder balls 106 connect to vias and/or points on the bottom surface of substrate 104 to which signals internal to substrate 104 are routed and exposed. Substrate 104 in FIG. 7 has a central window-shaped opening 704 , under which solder balls are preferably not connected.

- FIG. 20 illustrates a bottom view of a substrate 104 that has a central window opening 704 , according to an embodiment of the present invention.

- Stiffener 112 has a top surface to which IC die 102 is mounted. Stiffener 112 in FIG. 7 is patterned with a cavity 702 , which protrudes downward for attachment of IC die 102 . As described above, a central window-shaped opening 704 exists in substrate 104 . This opening 704 exists to allow stiffener 112 to protrude through, and make contact with soldering pads on a PCB to which BGA package 700 is to be mounted. The bottom exposed surface of cavity 702 can be plated with solder to facilitate surface mount to solder plated metal pads on a PCB to which BGA package 700 is mounted. Hence, stiffener 112 may act as a conduit for heat to be transferred from IC die 102 to the PCB.

- Stiffener 112 may optionally be configured to operate as a ground plane.

- One or more ground pads 608 may be coupled to a ground potential signal in IC die 102 .

- a ground wire bond 602 connects each ground pad 608 to stiffener 112 .

- the bottom exposed surface of cavity 702 may function both as an exposed ground pad of BGA package 700 , and as an exposed heat spreader.

- the bottom exposed surface of cavity 702 may be plated with solder to allows stiffener 112 to be surface mounted to one or more soldering pads on the PCB.

- the pads on the PCB can be connected to a PCB ground plane to shorten the length of electrical current return paths, as well as to form a conductive heat dissipation path from BGA package 700 to the PCB.

- FIG. 8 illustrates a cross-sectional view of a die-up flex BGA package 700 , according to an embodiment of the present invention.

- Substrate 104 in FIG. 8 has a central window-shaped opening, under which no solder balls are connected.

- a portion of the bottom surface of stiffener 112 is exposed through the central window-shaped opening 704 of substrate 104 .

- a heat spreader (for example, manufactured from copper or aluminum), shown as ground/thermal connector 802 , is coupled to the exposed portion of stiffener 112 .

- Ground/thermal connector 802 can be made from the same material as stiffener 112 .

- Ground/thermal connector 802 may be laminated to the exposed portion of stiffener 112 using conductive epoxy.

- the bottom surface of ground/thermal connector 802 may be plated with solder to facilitate its surface mount to soldering pads on the PCB.

- Metal pads on the PCB may be connected to a PCB ground plane to shorten the length of electrical current return paths, as well as enhance the conductive heat dissipation path from IC die 102 to the PCB.

- stiffener 112 and ground/thermal connector 802 may be manufactured from a single piece of metal, and hence consist of a single metal piece.

- FIG. 21 illustrates a side view of stiffener 112 that has a downward protruding portion 2102 , according to an embodiment of the present invention.

- portion 2102 extends partially or entirely through window-shaped opening 704 .