US20060244014A1 - Nonvolatile memory device and method of forming same - Google Patents

Nonvolatile memory device and method of forming same Download PDFInfo

- Publication number

- US20060244014A1 US20060244014A1 US11/476,006 US47600606A US2006244014A1 US 20060244014 A1 US20060244014 A1 US 20060244014A1 US 47600606 A US47600606 A US 47600606A US 2006244014 A1 US2006244014 A1 US 2006244014A1

- Authority

- US

- United States

- Prior art keywords

- gates

- gate

- charge storage

- disposed

- given

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Abandoned

Links

- 238000000034 method Methods 0.000 title abstract description 41

- 238000003860 storage Methods 0.000 claims abstract description 60

- 125000006850 spacer group Chemical group 0.000 claims abstract description 51

- 239000000758 substrate Substances 0.000 claims abstract description 24

- 239000004065 semiconductor Substances 0.000 claims abstract description 23

- 229910052710 silicon Inorganic materials 0.000 claims abstract description 10

- 239000010703 silicon Substances 0.000 claims abstract description 10

- 239000012535 impurity Substances 0.000 claims description 38

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 8

- 239000000463 material Substances 0.000 claims description 8

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 8

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 7

- 229920005591 polysilicon Polymers 0.000 claims description 7

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 6

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 4

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 4

- 239000002184 metal Substances 0.000 claims 1

- 229910052751 metal Inorganic materials 0.000 claims 1

- 229910021332 silicide Inorganic materials 0.000 claims 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 claims 1

- 239000010410 layer Substances 0.000 description 109

- 239000011229 interlayer Substances 0.000 description 13

- 238000005468 ion implantation Methods 0.000 description 10

- 238000005530 etching Methods 0.000 description 9

- 238000005229 chemical vapour deposition Methods 0.000 description 5

- 230000006870 function Effects 0.000 description 4

- 150000004767 nitrides Chemical class 0.000 description 3

- 238000001039 wet etching Methods 0.000 description 3

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- 238000000231 atomic layer deposition Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 238000007667 floating Methods 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000001590 oxidative effect Effects 0.000 description 2

- 238000005240 physical vapour deposition Methods 0.000 description 2

- 238000005086 pumping Methods 0.000 description 2

- 230000005689 Fowler Nordheim tunneling Effects 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- PZPGRFITIJYNEJ-UHFFFAOYSA-N disilane Chemical compound [SiH3][SiH3] PZPGRFITIJYNEJ-UHFFFAOYSA-N 0.000 description 1

- 238000011065 in-situ storage Methods 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B99/00—Subject matter not provided for in other groups of this subclass

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/30—EEPROM devices comprising charge-trapping gate insulators characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B69/00—Erasable-and-programmable ROM [EPROM] devices not provided for in groups H10B41/00 - H10B63/00, e.g. ultraviolet erasable-and-programmable ROM [UVEPROM] devices

Definitions

- the present invention relates to a nonvolatile memory device and a method of forming a nonvolatile memory device.

- nonvolatile memory devices store information without having to supply electrical power.

- a nonvolatile memory device such as a flash memory employs a floating gate to store information.

- the flash memory changes information stored in a cell transistor, for example, by performing program and erase operations.

- the program and erase operations generally require large voltage differences (greater than about 10 volts).

- the flash memory includes a plurality of pumping circuits to establish the necessary large voltage difference.

- the flash memory has a technical disadvantage, in that the transistor employing the flash memory (and interconnections thereto) should be designed so as to avoid breakdown due to the large voltage difference.

- the SONOS type nonvolatile memory device includes sequentially stacked layers, e.g., an oxide layer, a nitride layer, another oxide layer and a polysilicon layer that are sequentially stacked.

- the nitride layer is sandwiched between the oxide layers and used as an electric charge trapping medium.

- Information is stored in the charge trapping medium of the SONOS type nonvolatile memory device.

- the nitride layer performs a function similar to the function of a floating gate in the flash memory device.

- a SONOS type nonvolatile memory may be included in a structure where two adjoining cells, such as memory transistor cells, share a common source line.

- the two cells may have different channel lengths.

- Asymmetrical channel lengths may occur in what is referred to as a ‘split-gate’ type FLASH memory, for example.

- FIGS. 9 and 10 are perspective views illustrating a prior art method for fabricating a SONOS type nonvolatile memory device.

- a lower oxide layer 20 is formed on the semiconductor substrate 10

- a charge storage pattern 30 is formed on the lower oxide layer 20 .

- the charge storage pattern 30 is formed of an insulating layer (such as a silicon nitride layer, for example) having a sufficient number of charge trap sites.

- an upper oxide layer 40 is formed on the charge storage pattern 30 so as to conform to the charge storage pattern 30 .

- a gate conductive layer is formed over an entire surface of the semiconductor substrate 10 and the upper oxide layer 40 .

- the gate conductive layer is then patterned to form gate patterns 50 crossing over the charge storage pattern 30 .

- An ion implantation process is performed using the gate patterns 50 as a mask to form an impurity region 60 in the semiconductor substrate 10 .

- the impurity regions 60 are used as a source and/or a drain of a memory cell transistor.

- the gate patterns 50 are typically formed by a conventional photolithographic process so as to be misaligned to the charge storage pattern 30 . As shown in FIG. 10 , channel lengths I 1 and I 2 of the adjoining two cell transistors may be changed by the misalignment between the gate pattern 50 and the charge storage pattern 30 (i.e., I 1 ⁇ I 2 ).

- the asymmetry due to the misalignment may cause what is known as ‘periodical irregularities’ to appear at interconnections between one or more cell transistors and the one source line. These periodical irregularities are commonly known as ‘even-odd failures’ and may adversely affect cell transistor performance.

- An exemplary embodiments of the present invention is directed to a method of forming a silicon-oxide-nitride-oxide-silicon (SONOS) type nonvolatile memory device and a SONOS type memory device.

- a plurality of first gates may be formed on a semiconductor substrate.

- a plurality of charge storage spacers may be formed on the plurality of first gates so that a given charge storage spacer may be disposed on a sidewall of a given first gate.

- a plurality of second gates may be disposed on the plurality of first gates so that a given second gate is on a sidewall of a given first gate and covers a given charge storage spacer.

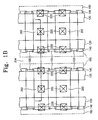

- FIGS. 1A to 1 H are top plan views illustrating a SONOS type nonvolatile memory device in accordance with the exemplary embodiments of the present invention.

- FIGS. 2A to 2 E are perspective views illustrating a SONOS type non-volatile memory device in accordance with the exemplary embodiments of the present invention.

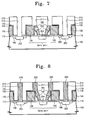

- FIGS. 3 to 8 are perspective views illustrating a method for forming a SONOS type non-volatile memory in accordance with the exemplary embodiments of the present invention.

- FIGS. 9 and 10 are perspective views illustrating a prior art method for fabricating a SONOS type nonvolatile memory device.

- FIGS. 1A to 1 H are top plan views illustrating a SONOS type nonvolatile memory device

- FIGS. 2A to 2 E are perspective views illustrating a SONOS type non-volatile memory device in accordance with the exemplary embodiments of the present invention.

- FIGS. 2A to 2 E correspond to FIGS. 1A, 1C , 1 D, 1 E and 1 F, respectively.

- the SONOS type nonvolatile memory device may include a plurality of device isolating layers 105 disposed so as to define active regions in a given region or area of a substrate 100 .

- the device isolating layers 105 may be disposed along columns (i.e., x-axis) and rows (i.e., y-axis), i.e., in 2-dimensions.

- each device isolating layer 105 may be island-shaped so as to have a different length and width.

- the device isolating layers 105 may be rectangular-shaped or elliptical-shaped active regions.

- the SONOS type nonvolatile memory device may include a plurality of first gates 120 provided on the substrate.

- the first gates 120 may be arranged in parallel along columns or rows, for example.

- several first gates 120 may be arranged so as to cross over device isolating layers 105 . That is, a plurality of device isolating layers 105 are disposed in parallel along one direction, and a plurality of first gates 120 are arranged so as to cross over these device isolating layers 105 , perpendicular to the device isolating layers 105 .

- two different first gates 120 may be arranged at sides (i.e., one first gate on either side) of an arbitrary first gate 120 .

- the arbitrary first gate may be referred to as a ‘reference gate’.

- FIG. 1A For example, where a first gate 120 labeled “Ref” at an upper portion of FIG. 1A may represent the reference gate, a first gate 120 is labeled “L” to the left of the first gate labeled Ref, and a first gate 120 is labeled “R” to the right of the first gate labeled Ref.

- the reference gate (Ref) and left gate (L) cross over the same device isolating layer 105 .

- the reference gate (Ref) and right gate (R) cross over different device isolating layers 105 , as shown in FIG. 1A , for example.

- the reference gate (Ref) and right gate (R) may be hereinafter referred to as a ‘gate pair’.

- the gate pair represents adjoining first gates 120 that cross over different device isolating layers 105 .

- the active region between an adjoining gates of a gate pair may be referred to as a first impurity region 202 .

- the first impurity regions 202 may be used as a drain of the cell transistors.

- the first impurity regions 202 are divided by the device isolating layers 105 .

- Bit line contact plugs 220 may be disposed on each of the first impurity regions 202 .

- the bit line contact plugs 220 may be connected by a bit line (not shown).

- the bit line contact plugs 220 may be arranged along a direction that is perpendicular to the first gates 120 , for example.

- the active regions between the gate pair may be referred to as second impurity regions 204 .

- the second impurity regions 204 may be used as a source region of cell transistors, for example.

- the first gates 120 of the gate pair cross over different device isolating layers 105 without being divided by the device isolating layers 105 . Therefore, the second impurity region 204 may be used as a common source line connecting the source regions of a plurality of transistors.

- the SONOS type nonvolatile memory device may include charge storage spacers 140 .

- the charge storage spacers 140 may be provided on one sidewall of the first gate 120 , so as to be disposed between two first gates 120 constituting the gate pair (i.e., adjacent to the second impurity region 204 ).

- the charge storage spacers 140 may be disposed on another sidewall of the first gate 120 (i.e., adjacent to the first impurity region 202 ).

- the charge storage spacers do not perform an information-storing function of a memory, but employed as a mask in an ion implantation process, for example.

- the charge storage spacers 140 may be cut over the device isolating layer 105 to form a rectangular-shaped island, as illustrated in FIGS. 1B, 1D , 1 H and 2 C. Alternatively, instead of being cut over the device isolating layer 105 , the charge storage spacers 140 may be arranged so as to extend in a continuous fashion along a sidewall of the first gate 120 .

- the SONOS type nonvolatile memory device may include second gates 185 .

- Two second gates 185 on a top surface and sidewalls of the charge storage spacers 140 may be disposed between the gate pair.

- the second gates 185 may be formed at, or in the vicinity of, a region where the charge storage spacers 140 are arranged, such that a second gate 185 covers one charge storage spacer 140 .

- a second gate 185 may be disposed at both sidewalls of a first gate 120 , as illustrated in FIGS. 1E, 1G , 1 H and 2 D, for example.

- An interlayer insulating layer may cover the semiconductor substrate, first gates 120 and second gates 185 .

- a connector 225 may be disposed in the interlayer insulating layer to connect the second gates 185 and first gates 120 .

- the connector 225 may have a rod-shaped form, similar to the bit line contact plug 220 .

- the connecter 225 may be continuously disposed along the first gate 120 without being cut.

- the non-cut connector 225 of FIGS. 1F and 2E may be employed in any of the other exemplary embodiments.

- the SONOS type nonvolatile memory device may include a gate insulating layer 110 that is disposed on the semiconductor substrate 100 .

- the first gate 120 , second gate 185 and charge storage spacer 140 may be disposed on the gate insulating layer 110 .

- a first insulating layer 130 such as a silicon oxide layer, for example, may be disposed between the first gate 120 and a second insulating layer 170 .

- the second insulating layer 170 may be disposed between the charge storage spacer 140 and second gate 185 . Additionally, the second insulating layer 170 may be arranged so as to be between the first gate 120 and the second gate 185 , as well as between the second gate 185 and the gate insulating layer 110 .

- a non-volatile memory may operate (e.g., to perform operations or functions such as programming, erasing, reading, etc.), in accordance with conventional operation mechanisms such as hot carrier injection, Fowler-Nordheim tunneling, etc.

- Exemplary operating conditions in accordance with the exemplary embodiments of the present invention may be shown in Table 1, it being understood that the nonvolatile memory in accordance with the exemplary embodiments of the present invention may be operated under operating conditions that are different from, or a modification of, the operating conditions shown in Table 1.

- Table 1 OPERATING CONDITIONS OF CELL TRANSISTOR gate source drain substrate programming Vcc H/V GND GND erasing H/V 0 0 0 reading Vcc 0 Vcc/2 GND

- a voltage Vcc may be applied to a gate electrode of the nonvolatile memory in accordance with the exemplary embodiments of the present invention. Therefore, even when a high voltage H/V is applied to the gate electrode, dissipation current may be prevented from overflowing.

- FIGS. 3 to 8 are cross-sectional views illustrating a method for forming a SONOS type nonvolatile memory device in accordance with the exemplary embodiments of the present invention.

- FIG. 3-8 illustrate sequential steps of a fabricating process for forming a SONOS type memory device.

- FIGS. 3-8 illustrate a cross-section as taken along a dotted line I-I′ of FIG. 1A .

- a plurality of device isolating layers 105 may be formed so as to define active regions in a given region or area of semiconductor substrate 100 .

- a gate insulating layer 110 may then be formed on the active region, and a first gate conductive layer formed on an entire surface of the semiconductor substrate 100 , including the gate insulating layer 110 .

- the device isolating layers 105 may be disposed along columns in two-dimensions (i.e., x-axis direction and y-axis direction).

- each device isolating layer 105 may be island-shaped (rectangular-shaped or elliptical-shaped active regions, for example) so as to have a different length and width.

- the device isolating layer 105 may be formed using a conventional Local Oxidation of Silicon (LOCOS) technology, for example.

- LOCOS Local Oxidation of Silicon

- trench technology may be used for forming the device isolating layer 105 .

- the gate insulating layer 110 may be formed of silicon oxide by thermally oxidizing the active region on semiconductor substrate 100 .

- the first gate conductive layer may be formed of polysilicon, or polysilicon and silicon layers that are sequentially stacked, for example.

- An insulating layer used as an anti-reflecting layer or a hard mask layer (“mask”) may be further disposed on the first gate conductive layer.

- the first gate conductive layer is patterned to form a plurality of first gates 120 crossing over the active region and device isolating layer 105 .

- the first gates 120 may be disposed in parallel along columns or rows.

- a plurality of device isolating layers 105 may be disposed in parallel along one direction, and two of the first gates 120 may be formed to cross over these parallel device isolating layers 105 .

- two of the first gates 120 may be embodied as the aforementioned gate pair illustrated in FIG. 1A .

- the gate pair may represent the adjoining two first gates 120 (Ref and R) crossing over the different or separate device isolating layers 105 of FIG. 1A .

- a first insulating layer 130 may be formed on an entire surface of a portion of the semiconductor substrate 100 that includes the first gates 120 .

- the first insulating layer 130 may be formed of silicon oxide by thermally oxidizing surfaces of the first gates 120 , or may be formed by a chemical vapor deposition (CVD) process, for example.

- CVD chemical vapor deposition

- a charge storage layer (not shown for reasons of clarity) may be formed so as to conform to the surface of the semiconductor substrate 100 and first insulating layer 130 .

- the charge storage layer is employed for storing information in a SONOS type nonvolatile memory device, for example.

- the charge storage layer may be formed of a material that has sufficient trap sites for storing information, such as silicon nitride or silicon oxynitride, for example, or another material that has sufficient trap sites for storing information.

- the charge storage layer may be anisotropically etched to form charge storage spacers 140 .

- the charge storage spacers 140 may be disposed on sidewalls of the first gates 120 .

- the charge storage spacers 140 may be formed so that top surfaces of the charge storage spacers 140 are lower than the first gates 120 , as shown in FIG. 3 .

- the anisotropic etching process is performed to expose the first insulating layer 130 on the first gate 120 , and to expose the gate insulating layer 110 on the active region between the first gates 120 .

- the etching process may employ an etch recipe having etch selectivity with respect to the silicon oxide layer, or with respect to a silicon layer.

- a mask pattern 150 is formed on a given region of the semiconductor substrate 100 that includes the charge storage spacers 140 .

- the mask pattern 150 may be a photoresist formed by a conventional photolithographic process, for example.

- the mask pattern 150 is formed to cover the charge storage spacers 140 between the gate pair and the active regions between the charge storage spacers 140 .

- both sidewalls of the mask pattern 150 are formed in the middle of a top surface of each first gate 120 , as shown in FIG. 4 .

- any charge storage spacers 140 on the external sidewalls of the gate pair are exposed.

- the exposed charge storage spacers 140 may be removed via a suitable etching process;

- FIG. 4 illustrates a state of the fabrication process in which the charge storage spacers 140 on the external sidewalls of the pair of first gates 120 have already been removed.

- the internal charge storage spacers 140 covered with the mask pattern 150 are not etched, as shown in FIG. 4 .

- the etching process may be performed using an etch recipe having etch selectivity with respect to the gate insulating layer 110 , the first insulating layer 130 and the mask pattern 150 .

- the etching process may be an isotropic etching or wet etching process for example, e.g., a wet etching process using an etchant with phosphoric acid, for example.

- a first ion implantation process 155 may be performed to form a first impurity region 160 .

- the first impurity region 160 may be used as a drain of a cell transistor, and is formed in the active region between the gate pair. As illustrated in FIGS. 1A to 1 H, the first impurity region 160 is divided by the device isolating layers 105 .

- the charge storage spacers 140 covered with the mask pattern 150 between the pair of gates are thus not removed (See FIGS. 1C, 1D , 1 G and 1 H).

- the first impurity region 160 is spaced apart from the charge storage spacers 140 by first gates 120 .

- the first impurity region 160 may be expanded during subsequent processes so as to extend under the charge storage spacers 140 . This may be accomplished using thermal diffusion, for example.

- the mask pattern 150 may be removed to expose the charge storage spacers 140 .

- a second insulating layer 170 and a second gate conductive layer 180 may then be sequentially formed on the entire surface of the semiconductor substrate 100 , once the mask pattern 150 has been removed.

- the second insulating layer 170 may be formed of silicon oxide by a CVD process, for example, so as to have good step coverage. Operation of the nonvolatile memory could be substantially affected by the thickness of the second insulating layer 170 .

- the second insulating layer 170 may be formed by an atomic layer deposition (ALD) process to more precisely control deposition thickness.

- ALD atomic layer deposition

- the second gate conductive layer 180 may be formed of polysilicon so as to have good step coverage.

- the second gate conductive layer 180 may be formed by a CVD process that includes a step of thermally dissolving the polysilicon with silane gas (SiH 4 ) or disilane gas (Si 2 H 6 ).

- the step of forming the second gate conductive layer 180 may further include performing an impurity doping step, either by ion-implantation or in-situ, in order to ensure that the second gate conductive layer 180 has good conductivity characteristics. Referring now to FIG. 6 , and with reference to FIG.

- the second gate conductive layer 180 may be anisotropically etched until the second insulating layer 170 is exposed to thereby form the second gates 185 .

- the second gates 185 may be disposed on both sidewalls of the first gates 120 , as shown in FIG. 6 for example.

- the second gates 185 disposed in facing relation on internal sidewalls of the gate pair may serve as another gate electrode of the SONOS type nonvolatile memory. As shown in FIG. 8 , the second gate 185 may be connected to the adjoining first gates 120 . Meanwhile, and as shown in FIG. 6 , the portions of the second gates 185 that are disposed on external sidewalls of the gate pair do not serve as a gate electrode, but may be used as an ion implantation mask in a subsequent process, for example.

- a second ion implantation process 190 may be performed using the second gates 185 and first gates 120 as a mask.

- the second impurity region 204 may be formed in the active region between the first gates 120 composing the gate pair.

- the second impurity region 204 may be used as a source of a cell transistor.

- a high-concentration drain region 202 which may be used as a drain of the cell transistor, may also be formed by the second ion implantation process 190 in the first impurity region 160 , i.e., the active region between the gate pair.

- the impurity concentration in the second impurity region 204 should be higher than the impurity concentration in the high-concentration drain region 202 . Therefore, after forming another mask pattern to screen the first impurity region 160 , an additional ion implantation process may be performed to inject impurities into the second impurity region 204 .

- concentrations of the first ion implantation process 155 and second ion implantation process 190 may be different. Accordingly, the concentrations of the high-concentration drain region 202 and the second impurity region 204 may have different concentrations.

- an interlayer insulating layer 210 may be formed on an entire surface of the semiconductor substrate 100 , including the second impurity region 204 .

- the interlayer insulating layer 210 may be patterned to form a contact hole 215 exposing the high-concentration drain region 202 .

- a contact hole 215 may also be formed to expose the second impurity region 204 at a given region or area (not shown).

- the interlayer insulating layer 210 may be composed of silicon oxide, silicon nitride or silicon oxynitride, for example.

- the interlayer insulating layer 210 may be formed by a CVD process, by a spin coating process, or by a physical vapor deposition (PVD) process, for example.

- selected second gates 185 may be selectively removed.

- An etch mask exposes those second gates 185 disposed on first impurity region 160 for the selective removal of certain second gates 185 .

- the mask pattern 150 used for forming the first impurity region 160 may be re-formed and used as an etching mask for the selective removal of certain second gates 185 .

- the selective removal may be performed using an etch recipe having an etch selectivity with respect to the interlayer insulating layer 200 such as a silicon oxide layer.

- the selective removal may be performed by an isotropic etching process such as wet etching, for example.

- a resultant structure, where the second gates 185 have been selectively removed, has a plan structure as illustrated in FIGS. 1A, 1B , 1 C, 1 D and 1 F.

- an interlayer insulating layer 210 may be formed without removing the second gates 185 .

- connection opening 217 may be formed to expose the first gate 120 and second gate 185 adjacent to the first gate 120 , as shown in FIG. 7 , for example.

- the connection opening 217 may be a hole type opening (such as the contact hole 215 ) or a groove type opening that is not cut in the middle, as illustrated in FIG. 1F , for example.

- a plug conductive layer may be formed on an entire surface of the semiconductor substrate 100 to fill the contact hole 215 and connection opening 217 .

- the plug conductive layer may be etched to expose a top surface of the interlayer insulating layer 210 , thereby forming a contact plug 220 that fills contact holes 215 , and a connector 225 that fills the connection openings 217 , respectively.

- the plug conductive layer may be composed of a material selected from a group consisting of polysilicon, aluminum, tungsten, titanium, titanium nitride, tantalum and tantalum nitride, for example.

- the connector 225 electrically connects the first gate 120 and the adjoining second gate 185 .

- the etching of the plug conductive layer may be performed using a chemical mechanical polishing (CMP) process.

- CMP chemical mechanical polishing

- the plug conductive layer may be over etched so as to be lower than a top surface of the interlayer insulating layer 210 .

- the top of the contact plug 220 and the top of the connector 225 may be lower than a top surface of the interlayer insulating layer 210 .

- another interlayer insulating layer may be formed on an entire surface of the resultant structures to form a bit line to connect the contact plugs 220 .

- a gate electrode of a nonvolatile memory device of a cell transistor may be formed by a process used for forming charge storage spacers that store information in the nonvolatile memory device.

- the gate electrode may configured so as to be self-aligned to the charge storage spacers, potentially preventing even-odd failure.

- a photolithographic process is not required in order to form the second gate electrode, so that production costs can be reduced.

- a stable SONOS type nonvolatile memory device may be fabricated at low cost.

- a voltage Vcc may be applied to a gate electrode during programming in an effort to prevent current from overflowing.

- a SONOS type nonvolatile memory device may be fabricated so as to have low or substantially low power consumption.

Landscapes

- Non-Volatile Memory (AREA)

- Semiconductor Memories (AREA)

Abstract

In a method of forming a silicon-oxide-nitride-oxide-silicon (SONOS) type nonvolatile memory device, a plurality of first gates may be formed on a semiconductor substrate. A plurality of charge storage spacers may be formed on the plurality of first gates so that a given charge storage spacer may be disposed on a sidewall of a given first gate. A plurality of second gates may be disposed on the plurality of first gates so that a given second gate is on a sidewall of a given first gate and covers a given charge storage spacer.

Description

- This application claims the priority of U.S. patent application Ser. No. 10/761,250 (parent application), filed on Jan. 22, 2004, the disclosure of which is incorporated herein in its entirety by reference.

- 1. Field of the Invention

- The present invention relates to a nonvolatile memory device and a method of forming a nonvolatile memory device.

- 2. Description of Related Art

- As electrical devices become miniaturized and portable, the need for nonvolatile memory devices becomes even greater. In general, nonvolatile memory devices store information without having to supply electrical power. For example, a nonvolatile memory device such as a flash memory employs a floating gate to store information. The flash memory changes information stored in a cell transistor, for example, by performing program and erase operations. The program and erase operations generally require large voltage differences (greater than about 10 volts). Accordingly, the flash memory includes a plurality of pumping circuits to establish the necessary large voltage difference. As the number of pumping circuits needed on the nonvolatile memory device rise, the integrity of a semiconductor device product containing the nonvolatile memory device is reduced, and cost of the product increases. In addition, the flash memory has a technical disadvantage, in that the transistor employing the flash memory (and interconnections thereto) should be designed so as to avoid breakdown due to the large voltage difference.

- As an alternative to flash memory devices, a silicon-oxide-nitride-oxide-silicon (SONOS) type nonvolatile memory device has recently been studied and proposed. Generally, the SONOS type nonvolatile memory device includes sequentially stacked layers, e.g., an oxide layer, a nitride layer, another oxide layer and a polysilicon layer that are sequentially stacked. The nitride layer is sandwiched between the oxide layers and used as an electric charge trapping medium. Information is stored in the charge trapping medium of the SONOS type nonvolatile memory device. In other words, the nitride layer performs a function similar to the function of a floating gate in the flash memory device.

- In order to provide a highly integrated semiconductor device, a SONOS type nonvolatile memory may be included in a structure where two adjoining cells, such as memory transistor cells, share a common source line. In this case, the two cells may have different channel lengths. Asymmetrical channel lengths may occur in what is referred to as a ‘split-gate’ type FLASH memory, for example.

-

FIGS. 9 and 10 are perspective views illustrating a prior art method for fabricating a SONOS type nonvolatile memory device. Referring toFIGS. 9 and 10 , alower oxide layer 20 is formed on thesemiconductor substrate 10, and acharge storage pattern 30 is formed on thelower oxide layer 20. Thecharge storage pattern 30 is formed of an insulating layer (such as a silicon nitride layer, for example) having a sufficient number of charge trap sites. Then, anupper oxide layer 40 is formed on thecharge storage pattern 30 so as to conform to thecharge storage pattern 30. - A gate conductive layer is formed over an entire surface of the

semiconductor substrate 10 and theupper oxide layer 40. The gate conductive layer is then patterned to formgate patterns 50 crossing over thecharge storage pattern 30. An ion implantation process is performed using thegate patterns 50 as a mask to form animpurity region 60 in thesemiconductor substrate 10. Theimpurity regions 60 are used as a source and/or a drain of a memory cell transistor. - The

gate patterns 50 are typically formed by a conventional photolithographic process so as to be misaligned to thecharge storage pattern 30. As shown inFIG. 10 , channel lengths I1 and I2 of the adjoining two cell transistors may be changed by the misalignment between thegate pattern 50 and the charge storage pattern 30 (i.e., I1≠I2). - The asymmetry due to the misalignment may cause what is known as ‘periodical irregularities’ to appear at interconnections between one or more cell transistors and the one source line. These periodical irregularities are commonly known as ‘even-odd failures’ and may adversely affect cell transistor performance.

- An exemplary embodiments of the present invention is directed to a method of forming a silicon-oxide-nitride-oxide-silicon (SONOS) type nonvolatile memory device and a SONOS type memory device. In the method, a plurality of first gates may be formed on a semiconductor substrate. A plurality of charge storage spacers may be formed on the plurality of first gates so that a given charge storage spacer may be disposed on a sidewall of a given first gate. A plurality of second gates may be disposed on the plurality of first gates so that a given second gate is on a sidewall of a given first gate and covers a given charge storage spacer.

- Exemplary embodiments of the present invention will become more fully understood from the detailed description herein below and the accompanying drawings, wherein like elements are represented by like reference numerals, which are by way of illustration only and thus do not limit the exemplary embodiments of the present invention and wherein:

-

FIGS. 1A to 1H are top plan views illustrating a SONOS type nonvolatile memory device in accordance with the exemplary embodiments of the present invention. -

FIGS. 2A to 2E are perspective views illustrating a SONOS type non-volatile memory device in accordance with the exemplary embodiments of the present invention. - FIGS. 3 to 8 are perspective views illustrating a method for forming a SONOS type non-volatile memory in accordance with the exemplary embodiments of the present invention.

-

FIGS. 9 and 10 are perspective views illustrating a prior art method for fabricating a SONOS type nonvolatile memory device. - The present invention will be described more fully hereinafter with reference to the accompanying drawings, in which exemplary embodiments of the invention are shown. The present invention is not limited to the exemplary embodiments set forth herein, which are provided so that the disclosure will be thorough and complete, and will fully convey the scope of the invention to those skilled in the art. In the drawings, the thickness of layers and regions are exaggerated for clarity. It will also be understood that when a layer is referred to as being “on” another layer or semiconductor substrate, it can be directly on the other layer or semiconductor substrate, or intervening layers may also be present. Like numbers refer to like elements throughout.

-

FIGS. 1A to 1H are top plan views illustrating a SONOS type nonvolatile memory device, andFIGS. 2A to 2E are perspective views illustrating a SONOS type non-volatile memory device in accordance with the exemplary embodiments of the present invention.FIGS. 2A to 2E correspond toFIGS. 1A, 1C , 1D, 1E and 1F, respectively. - Referring to

FIGS. 1A to 1H and 2A to 2E, the SONOS type nonvolatile memory device may include a plurality ofdevice isolating layers 105 disposed so as to define active regions in a given region or area of asubstrate 100. Thedevice isolating layers 105 may be disposed along columns (i.e., x-axis) and rows (i.e., y-axis), i.e., in 2-dimensions. In this case, eachdevice isolating layer 105 may be island-shaped so as to have a different length and width. For example, thedevice isolating layers 105 may be rectangular-shaped or elliptical-shaped active regions. - The SONOS type nonvolatile memory device may include a plurality of

first gates 120 provided on the substrate. Thefirst gates 120 may be arranged in parallel along columns or rows, for example. In an exemplary embodiment, severalfirst gates 120 may be arranged so as to cross over device isolating layers 105. That is, a plurality ofdevice isolating layers 105 are disposed in parallel along one direction, and a plurality offirst gates 120 are arranged so as to cross over thesedevice isolating layers 105, perpendicular to the device isolating layers 105. - Based on the above configuration, two different

first gates 120 may be arranged at sides (i.e., one first gate on either side) of an arbitraryfirst gate 120. The arbitrary first gate may be referred to as a ‘reference gate’. Thus may be illustrated inFIG. 1A , for example, where afirst gate 120 labeled “Ref” at an upper portion ofFIG. 1A may represent the reference gate, afirst gate 120 is labeled “L” to the left of the first gate labeled Ref, and afirst gate 120 is labeled “R” to the right of the first gate labeled Ref. The reference gate (Ref) and left gate (L) cross over the samedevice isolating layer 105. The reference gate (Ref) and right gate (R) cross over differentdevice isolating layers 105, as shown inFIG. 1A , for example. The reference gate (Ref) and right gate (R) may be hereinafter referred to as a ‘gate pair’. In other words, the gate pair represents adjoiningfirst gates 120 that cross over different device isolating layers 105. - The active region between an adjoining gates of a gate pair (i.e., L and Ref being adjoining gates of one pair; Ref and R being adjoining gates of another gate pair in

FIG. 1A ) may be referred to as afirst impurity region 202. Thefirst impurity regions 202 may be used as a drain of the cell transistors. Thefirst impurity regions 202 are divided by the device isolating layers 105. Bit line contact plugs 220 may be disposed on each of thefirst impurity regions 202. The bit line contact plugs 220 may be connected by a bit line (not shown). The bit line contact plugs 220 may be arranged along a direction that is perpendicular to thefirst gates 120, for example. - The active regions between the gate pair may be referred to as

second impurity regions 204. Thesecond impurity regions 204 may be used as a source region of cell transistors, for example. Thefirst gates 120 of the gate pair cross over differentdevice isolating layers 105 without being divided by the device isolating layers 105. Therefore, thesecond impurity region 204 may be used as a common source line connecting the source regions of a plurality of transistors. - The SONOS type nonvolatile memory device may include

charge storage spacers 140. Thecharge storage spacers 140 may be provided on one sidewall of thefirst gate 120, so as to be disposed between twofirst gates 120 constituting the gate pair (i.e., adjacent to the second impurity region 204). Alternatively, as illustrated inFIGS. 1C, 1D , 1G, 1H, 2B and 2C, thecharge storage spacers 140 may be disposed on another sidewall of the first gate 120 (i.e., adjacent to the first impurity region 202). However, in this configuration adjacentfirst impurity region 202, the charge storage spacers do not perform an information-storing function of a memory, but employed as a mask in an ion implantation process, for example. - The

charge storage spacers 140 may be cut over thedevice isolating layer 105 to form a rectangular-shaped island, as illustrated inFIGS. 1B, 1D , 1H and 2C. Alternatively, instead of being cut over thedevice isolating layer 105, thecharge storage spacers 140 may be arranged so as to extend in a continuous fashion along a sidewall of thefirst gate 120. - The SONOS type nonvolatile memory device may include

second gates 185. Twosecond gates 185 on a top surface and sidewalls of thecharge storage spacers 140 may be disposed between the gate pair. Thesecond gates 185 may be formed at, or in the vicinity of, a region where thecharge storage spacers 140 are arranged, such that asecond gate 185 covers onecharge storage spacer 140. Alternatively, asecond gate 185 may be disposed at both sidewalls of afirst gate 120, as illustrated inFIGS. 1E, 1G , 1H and 2D, for example. - An interlayer insulating layer (not shown) may cover the semiconductor substrate,

first gates 120 andsecond gates 185. Aconnector 225 may be disposed in the interlayer insulating layer to connect thesecond gates 185 andfirst gates 120. As illustrated inFIGS. 1A-1E , 1G, 1H, and 2A-2D, for example, theconnector 225 may have a rod-shaped form, similar to the bitline contact plug 220. Alternately, as illustrated inFIGS. 1F and 2E , theconnecter 225 may be continuously disposed along thefirst gate 120 without being cut. Thenon-cut connector 225 ofFIGS. 1F and 2E may be employed in any of the other exemplary embodiments. - The SONOS type nonvolatile memory device may include a

gate insulating layer 110 that is disposed on thesemiconductor substrate 100. Thefirst gate 120,second gate 185 andcharge storage spacer 140 may be disposed on thegate insulating layer 110. A first insulatinglayer 130, such as a silicon oxide layer, for example, may be disposed between thefirst gate 120 and a second insulatinglayer 170. - The second

insulating layer 170 may be disposed between thecharge storage spacer 140 andsecond gate 185. Additionally, the second insulatinglayer 170 may be arranged so as to be between thefirst gate 120 and thesecond gate 185, as well as between thesecond gate 185 and thegate insulating layer 110. In accordance with the exemplary embodiments of the present invention, a non-volatile memory may operate (e.g., to perform operations or functions such as programming, erasing, reading, etc.), in accordance with conventional operation mechanisms such as hot carrier injection, Fowler-Nordheim tunneling, etc. Exemplary operating conditions in accordance with the exemplary embodiments of the present invention may be shown in Table 1, it being understood that the nonvolatile memory in accordance with the exemplary embodiments of the present invention may be operated under operating conditions that are different from, or a modification of, the operating conditions shown in Table 1.TABLE 1 OPERATING CONDITIONS OF CELL TRANSISTOR gate source drain substrate programming Vcc H/V GND GND erasing H/V 0 0 0 reading Vcc 0 Vcc/2 GND - Referring to Table 1, during a programming operation, a voltage Vcc may be applied to a gate electrode of the nonvolatile memory in accordance with the exemplary embodiments of the present invention. Therefore, even when a high voltage H/V is applied to the gate electrode, dissipation current may be prevented from overflowing.

- FIGS. 3 to 8 are cross-sectional views illustrating a method for forming a SONOS type nonvolatile memory device in accordance with the exemplary embodiments of the present invention.

FIG. 3-8 illustrate sequential steps of a fabricating process for forming a SONOS type memory device. Each ofFIGS. 3-8 illustrate a cross-section as taken along a dotted line I-I′ ofFIG. 1A . - Referring to

FIG. 3 , and with reference toFIG. 1A , a plurality ofdevice isolating layers 105 may be formed so as to define active regions in a given region or area ofsemiconductor substrate 100. Agate insulating layer 110 may then be formed on the active region, and a first gate conductive layer formed on an entire surface of thesemiconductor substrate 100, including thegate insulating layer 110. - As discussed above, the

device isolating layers 105 may be disposed along columns in two-dimensions (i.e., x-axis direction and y-axis direction). Thus, eachdevice isolating layer 105 may be island-shaped (rectangular-shaped or elliptical-shaped active regions, for example) so as to have a different length and width. Thedevice isolating layer 105 may be formed using a conventional Local Oxidation of Silicon (LOCOS) technology, for example. Alternatively, trench technology may be used for forming thedevice isolating layer 105. In addition, thegate insulating layer 110 may be formed of silicon oxide by thermally oxidizing the active region onsemiconductor substrate 100. The first gate conductive layer may be formed of polysilicon, or polysilicon and silicon layers that are sequentially stacked, for example. An insulating layer used as an anti-reflecting layer or a hard mask layer (“mask”) may be further disposed on the first gate conductive layer. - Then, the first gate conductive layer is patterned to form a plurality of

first gates 120 crossing over the active region anddevice isolating layer 105. Thefirst gates 120 may be disposed in parallel along columns or rows. In an exemplary embodiment, a plurality ofdevice isolating layers 105 may be disposed in parallel along one direction, and two of thefirst gates 120 may be formed to cross over these parallel device isolating layers 105. In this case, two of thefirst gates 120 may be embodied as the aforementioned gate pair illustrated inFIG. 1A . In other words, the gate pair may represent the adjoining two first gates 120 (Ref and R) crossing over the different or separatedevice isolating layers 105 ofFIG. 1A . - A first insulating

layer 130 may be formed on an entire surface of a portion of thesemiconductor substrate 100 that includes thefirst gates 120. For example, the first insulatinglayer 130 may be formed of silicon oxide by thermally oxidizing surfaces of thefirst gates 120, or may be formed by a chemical vapor deposition (CVD) process, for example. - Continuously, a charge storage layer (not shown for reasons of clarity) may be formed so as to conform to the surface of the

semiconductor substrate 100 and first insulatinglayer 130. The charge storage layer is employed for storing information in a SONOS type nonvolatile memory device, for example. The charge storage layer may be formed of a material that has sufficient trap sites for storing information, such as silicon nitride or silicon oxynitride, for example, or another material that has sufficient trap sites for storing information. The charge storage layer may be anisotropically etched to formcharge storage spacers 140. Thecharge storage spacers 140 may be disposed on sidewalls of thefirst gates 120. Thecharge storage spacers 140 may be formed so that top surfaces of thecharge storage spacers 140 are lower than thefirst gates 120, as shown inFIG. 3 . In order to accomplish this, the anisotropic etching process is performed to expose the first insulatinglayer 130 on thefirst gate 120, and to expose thegate insulating layer 110 on the active region between thefirst gates 120. The etching process may employ an etch recipe having etch selectivity with respect to the silicon oxide layer, or with respect to a silicon layer. - Referring now to

FIG. 4 , with reference toFIG. 1A , amask pattern 150 is formed on a given region of thesemiconductor substrate 100 that includes thecharge storage spacers 140. Themask pattern 150 may be a photoresist formed by a conventional photolithographic process, for example. Themask pattern 150 is formed to cover thecharge storage spacers 140 between the gate pair and the active regions between thecharge storage spacers 140. In this case, both sidewalls of themask pattern 150 are formed in the middle of a top surface of eachfirst gate 120, as shown inFIG. 4 . Thus, anycharge storage spacers 140 on the external sidewalls of the gate pair (seeFIG. 3 , for example) are exposed. - Using the

mask pattern 150 as an etch mask, the exposedcharge storage spacers 140 may be removed via a suitable etching process;FIG. 4 illustrates a state of the fabrication process in which thecharge storage spacers 140 on the external sidewalls of the pair offirst gates 120 have already been removed. In this case, the internalcharge storage spacers 140 covered with themask pattern 150 are not etched, as shown inFIG. 4 . The etching process may be performed using an etch recipe having etch selectivity with respect to thegate insulating layer 110, the first insulatinglayer 130 and themask pattern 150. The etching process may be an isotropic etching or wet etching process for example, e.g., a wet etching process using an etchant with phosphoric acid, for example. - Using the

mask pattern 150 and thefirst gates 120 as an etch mask, a firstion implantation process 155 may be performed to form afirst impurity region 160. Thefirst impurity region 160 may be used as a drain of a cell transistor, and is formed in the active region between the gate pair. As illustrated inFIGS. 1A to 1H, thefirst impurity region 160 is divided by the device isolating layers 105. - The

charge storage spacers 140 covered with themask pattern 150 between the pair of gates are thus not removed (SeeFIGS. 1C, 1D , 1G and 1H). In this case, thefirst impurity region 160 is spaced apart from thecharge storage spacers 140 byfirst gates 120. However, thefirst impurity region 160 may be expanded during subsequent processes so as to extend under thecharge storage spacers 140. This may be accomplished using thermal diffusion, for example. - Referring now to

FIG. 5 , and with reference toFIG. 1A , themask pattern 150 may be removed to expose thecharge storage spacers 140. A second insulatinglayer 170 and a second gateconductive layer 180 may then be sequentially formed on the entire surface of thesemiconductor substrate 100, once themask pattern 150 has been removed. - The second

insulating layer 170 may be formed of silicon oxide by a CVD process, for example, so as to have good step coverage. Operation of the nonvolatile memory could be substantially affected by the thickness of the second insulatinglayer 170. Thus, the second insulatinglayer 170 may be formed by an atomic layer deposition (ALD) process to more precisely control deposition thickness. - The second gate

conductive layer 180 may be formed of polysilicon so as to have good step coverage. For example, the second gateconductive layer 180 may be formed by a CVD process that includes a step of thermally dissolving the polysilicon with silane gas (SiH4) or disilane gas (Si2H6). In addition, the step of forming the second gateconductive layer 180 may further include performing an impurity doping step, either by ion-implantation or in-situ, in order to ensure that the second gateconductive layer 180 has good conductivity characteristics. Referring now toFIG. 6 , and with reference toFIG. 1A , the second gateconductive layer 180 may be anisotropically etched until the second insulatinglayer 170 is exposed to thereby form thesecond gates 185. Thesecond gates 185 may be disposed on both sidewalls of thefirst gates 120, as shown inFIG. 6 for example. - Referring now to

FIG. 8 , thesecond gates 185 disposed in facing relation on internal sidewalls of the gate pair may serve as another gate electrode of the SONOS type nonvolatile memory. As shown inFIG. 8 , thesecond gate 185 may be connected to the adjoiningfirst gates 120. Meanwhile, and as shown inFIG. 6 , the portions of thesecond gates 185 that are disposed on external sidewalls of the gate pair do not serve as a gate electrode, but may be used as an ion implantation mask in a subsequent process, for example. - A second

ion implantation process 190 may be performed using thesecond gates 185 andfirst gates 120 as a mask. Thus, thesecond impurity region 204 may be formed in the active region between thefirst gates 120 composing the gate pair. Thesecond impurity region 204 may be used as a source of a cell transistor. Additionally, a high-concentration drain region 202, which may be used as a drain of the cell transistor, may also be formed by the secondion implantation process 190 in thefirst impurity region 160, i.e., the active region between the gate pair. - In order to improve efficiency of a programming operation, the impurity concentration in the

second impurity region 204 should be higher than the impurity concentration in the high-concentration drain region 202. Therefore, after forming another mask pattern to screen thefirst impurity region 160, an additional ion implantation process may be performed to inject impurities into thesecond impurity region 204. - Referring to

FIG. 4 andFIG. 6 , and according to an exemplary embodiment where thecharge storage spacer 140 on external sidewalls of thefirst gates 120 have been removed, concentrations of the firstion implantation process 155 and secondion implantation process 190 may be different. Accordingly, the concentrations of the high-concentration drain region 202 and thesecond impurity region 204 may have different concentrations. - Referring now to

FIG. 7 , aninterlayer insulating layer 210 may be formed on an entire surface of thesemiconductor substrate 100, including thesecond impurity region 204. The interlayer insulatinglayer 210 may be patterned to form acontact hole 215 exposing the high-concentration drain region 202. Acontact hole 215 may also be formed to expose thesecond impurity region 204 at a given region or area (not shown). - The interlayer insulating

layer 210 may be composed of silicon oxide, silicon nitride or silicon oxynitride, for example. In addition, theinterlayer insulating layer 210 may be formed by a CVD process, by a spin coating process, or by a physical vapor deposition (PVD) process, for example. - To form the

interlayer insulating layer 210, as illustrated inFIG. 7 , selectedsecond gates 185 may be selectively removed. An etch mask exposes thosesecond gates 185 disposed onfirst impurity region 160 for the selective removal of certainsecond gates 185. Thus, themask pattern 150 used for forming thefirst impurity region 160 may be re-formed and used as an etching mask for the selective removal of certainsecond gates 185. The selective removal may be performed using an etch recipe having an etch selectivity with respect to the interlayer insulating layer 200 such as a silicon oxide layer. In addition, the selective removal may be performed by an isotropic etching process such as wet etching, for example. A resultant structure, where thesecond gates 185 have been selectively removed, has a plan structure as illustrated inFIGS. 1A, 1B , 1C, 1D and 1F. Alternatively, as illustrated inFIGS. 1E, 1G and 1H, aninterlayer insulating layer 210 may be formed without removing thesecond gates 185. - In forming the

contact hole 215, aconnection opening 217 may be formed to expose thefirst gate 120 andsecond gate 185 adjacent to thefirst gate 120, as shown inFIG. 7 , for example. Theconnection opening 217 may be a hole type opening (such as the contact hole 215) or a groove type opening that is not cut in the middle, as illustrated inFIG. 1F , for example. - Referring now to

FIG. 8 and with occasional reference toFIG. 1A , a plug conductive layer may be formed on an entire surface of thesemiconductor substrate 100 to fill thecontact hole 215 andconnection opening 217. The plug conductive layer may be etched to expose a top surface of the interlayer insulatinglayer 210, thereby forming acontact plug 220 that fills contact holes 215, and aconnector 225 that fills theconnection openings 217, respectively. - The plug conductive layer may be composed of a material selected from a group consisting of polysilicon, aluminum, tungsten, titanium, titanium nitride, tantalum and tantalum nitride, for example. The

connector 225 electrically connects thefirst gate 120 and the adjoiningsecond gate 185. Meanwhile, the etching of the plug conductive layer may be performed using a chemical mechanical polishing (CMP) process. In addition, the plug conductive layer may be over etched so as to be lower than a top surface of the interlayer insulatinglayer 210. Thus, the top of thecontact plug 220 and the top of theconnector 225 may be lower than a top surface of the interlayer insulatinglayer 210. Afterwards, another interlayer insulating layer may be formed on an entire surface of the resultant structures to form a bit line to connect the contact plugs 220. - According to the exemplary embodiments of the present invention, a gate electrode of a nonvolatile memory device of a cell transistor may be formed by a process used for forming charge storage spacers that store information in the nonvolatile memory device. The gate electrode may configured so as to be self-aligned to the charge storage spacers, potentially preventing even-odd failure. In addition, a photolithographic process is not required in order to form the second gate electrode, so that production costs can be reduced. Accordingly, a stable SONOS type nonvolatile memory device may be fabricated at low cost. In addition, a voltage Vcc may be applied to a gate electrode during programming in an effort to prevent current from overflowing. Thus, a SONOS type nonvolatile memory device may be fabricated so as to have low or substantially low power consumption.

- The exemplary embodiments of the present invention being thus described, it will be obvious that the same may be varied in many ways. Such variations are not to be regarded as departure from the spirit and scope of the exemplary embodiments of the present invention, and all such modifications as would be obvious to one skilled in the art are intended to be included within the scope of the following claims.

Claims (13)

1.-14. (canceled)

15. A silicon-oxide-nitride-oxide-silicon (SONOS) type nonvolatile memory device, comprising:

a plurality of first gates disposed on a given region of a semiconductor substrate;

a plurality of charge storage spacers disposed on the plurality of first gates so that a given charge storage spacer is on a sidewall of a given first gate; and

a plurality of second gates disposed on the plurality of first gates so that a given second gate is on a sidewall of a given first gate and covers a given charge storage spacer.

16. The device of claim 15 , further comprising:

a plurality of device isolating layers defining an active region disposed in a given region of the semiconductor substrate, wherein the device isolating layers are two-dimensionally disposed along columns and rows.

17. The device of claim 16 , wherein

the plurality of first gates cross over the plurality of device isolating layers and are parallel to each other, and

a given pair of first gates are disposed on each of the device isolating layers.

18. The device of claim 17 , wherein

the charge storage spacers are disposed on internal sidewalls of an adjoining two first gates, and

each first gate of the adjoining two first gates crosses over a different device isolating layer.

19. The device of claim 18 , further comprising:

an impurity region disposed between a given pair of charge storage spacers that are disposed on the internal sidewalls of the adjoining two first gates, wherein the impurity region represents a common source line of adjoining cell transistors.

20. The device of claim 17 , further comprising:

an impurity region disposed between a given pair of first gates crossing over the same device isolating layer, wherein the impurity region is divided by the device isolating layer.

21. The device of claim 20 , further comprising:

a plurality of insulating spacers disposed adjacent to the impurity region, each insulating spacer disposed on another sidewall of a given first gate opposite to the sidewall on which a given charge storage spacer is disposed.

22. The device of claim 20 , further comprising:

a material pattern disposed adjacent to the impurity region and on another sidewall of a given first gate opposite to the sidewall on which a given charge storage spacer is disposed, wherein the material pattern is formed of an material substantially identical to a material of the second gate.

23. The device of claim 15 , wherein the first gates and second gates are composed of at least one material selected from a group comprising polysilicon, silicide and metal.

24. The device of claim 15 , wherein the plurality of charge storage spacers are formed of silicon nitride or silicon oxynitride.

25. The device of claim 16 , wherein each of the charge storage spacers includes a sidewall that is formed on a device isolating layer to isolate a charge storage spacer from another charge storage spacer.

26. The device of claim 15 , further comprising:

a gate insulating layer interposed between the first gates, second gates, charge storage spacers and semiconductor substrate;

a first insulating layer interposed between the plurality of first gates and the plurality of charge storage spacers;

a second insulating layer interposed between the plurality of charge storage spacers and the plurality of second gates; and

a connector connecting the first gates and second gates, wherein the gate insulating layer and the first insulating layer are composed of silicon oxide.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/476,006 US20060244014A1 (en) | 2003-01-22 | 2006-06-28 | Nonvolatile memory device and method of forming same |

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR2003-4223 | 2003-01-22 | ||

| KR10-2003-0004223A KR100521371B1 (en) | 2003-01-22 | 2003-01-22 | Silicon-Oxide-Nitride-Oxide-Silicon (SONOS) Type Nonvolatile Memory And Method Of Fabricating The Same |

| US10/761,250 US7091090B2 (en) | 2003-01-22 | 2004-01-22 | Nonvolatile memory device and method of forming same |

| US11/476,006 US20060244014A1 (en) | 2003-01-22 | 2006-06-28 | Nonvolatile memory device and method of forming same |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US10/761,250 Division US7091090B2 (en) | 2003-01-22 | 2004-01-22 | Nonvolatile memory device and method of forming same |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| US20060244014A1 true US20060244014A1 (en) | 2006-11-02 |

Family

ID=32906506

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US10/761,250 Expired - Fee Related US7091090B2 (en) | 2003-01-22 | 2004-01-22 | Nonvolatile memory device and method of forming same |

| US11/476,006 Abandoned US20060244014A1 (en) | 2003-01-22 | 2006-06-28 | Nonvolatile memory device and method of forming same |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US10/761,250 Expired - Fee Related US7091090B2 (en) | 2003-01-22 | 2004-01-22 | Nonvolatile memory device and method of forming same |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US7091090B2 (en) |

| JP (1) | JP2004228571A (en) |

| KR (1) | KR100521371B1 (en) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20090078984A1 (en) * | 2007-09-20 | 2009-03-26 | Kabushiki Kaisha Toshiba | Semiconductor apparatus and method for manufacturing the same |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI233666B (en) * | 2004-04-13 | 2005-06-01 | Powerchip Semiconductor Corp | Method of manufacturing non-volatile memory cell |

| JPWO2006013931A1 (en) | 2004-08-04 | 2008-05-01 | イビデン株式会社 | Firing furnace and method for producing a porous ceramic fired body using the firing furnace |

| JP4773073B2 (en) * | 2004-08-11 | 2011-09-14 | ルネサスエレクトロニクス株式会社 | Manufacturing method of semiconductor device |

| JP5025140B2 (en) | 2005-03-23 | 2012-09-12 | ルネサスエレクトロニクス株式会社 | Manufacturing method of semiconductor memory device |

| KR100760634B1 (en) * | 2006-10-02 | 2007-09-20 | 삼성전자주식회사 | Nand-type non volatile memory devcie and method of forming the same |

| KR100799722B1 (en) * | 2006-12-12 | 2008-02-01 | 삼성전자주식회사 | Memory device and method for manufacturing the same |

| US8471328B2 (en) | 2010-07-26 | 2013-06-25 | United Microelectronics Corp. | Non-volatile memory and manufacturing method thereof |

| KR101979299B1 (en) * | 2012-12-26 | 2019-09-03 | 에스케이하이닉스 주식회사 | Nonvolatile memory device and method of fabricating the same |

| US9355725B2 (en) | 2013-12-12 | 2016-05-31 | Cypress Semiconductor Corporation | Non-volatile memory and method of operating the same |

| US11437392B2 (en) * | 2020-07-28 | 2022-09-06 | Globalfoundries Singapore Pte. Ltd. | Compact memory cell with a shared conductive select gate and methods of making such a memory cell |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6177318B1 (en) * | 1999-10-18 | 2001-01-23 | Halo Lsi Design & Device Technology, Inc. | Integration method for sidewall split gate monos transistor |

| US6335554B1 (en) * | 1999-03-08 | 2002-01-01 | Kabushiki Kaisha Toshiba | Semiconductor Memory |

| US6413821B1 (en) * | 2001-09-18 | 2002-07-02 | Seiko Epson Corporation | Method of fabricating semiconductor device including nonvolatile memory and peripheral circuit |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06334192A (en) * | 1993-05-21 | 1994-12-02 | Matsushita Electric Ind Co Ltd | Non-volatile semiconductor memory |

| JP3173907B2 (en) * | 1992-12-22 | 2001-06-04 | ローム株式会社 | Nonvolatile memory element and method of manufacturing the same |

| JP3417974B2 (en) * | 1993-06-03 | 2003-06-16 | ローム株式会社 | Nonvolatile storage element and nonvolatile storage device using the same |

| JPH07130884A (en) * | 1993-10-29 | 1995-05-19 | Oki Electric Ind Co Ltd | Manufacture of nonvolatile semiconductor memory |

| JP3060272B2 (en) * | 1993-11-01 | 2000-07-10 | 日本電気株式会社 | Method for manufacturing semiconductor memory device |

| JPH08321564A (en) * | 1995-05-25 | 1996-12-03 | Sanyo Electric Co Ltd | Nonvolatile semiconductor memory and fabrication thereof |

| US5969383A (en) * | 1997-06-16 | 1999-10-19 | Motorola, Inc. | Split-gate memory device and method for accessing the same |

| JPH11354748A (en) * | 1998-06-12 | 1999-12-24 | Hitachi Ltd | Semiconductor integrated circuit and its fabrication |

| JP2000286400A (en) * | 1999-03-31 | 2000-10-13 | Hitachi Ltd | Semiconductor integrated circuit device and its manufacture |

| US6255166B1 (en) * | 1999-08-05 | 2001-07-03 | Aalo Lsi Design & Device Technology, Inc. | Nonvolatile memory cell, method of programming the same and nonvolatile memory array |

| JP3930256B2 (en) | 2001-02-07 | 2007-06-13 | スパンション エルエルシー | Semiconductor device and manufacturing method thereof |

| JP3983094B2 (en) * | 2002-04-25 | 2007-09-26 | Necエレクトロニクス株式会社 | Method for manufacturing nonvolatile semiconductor memory device |

| JP3983105B2 (en) * | 2002-05-29 | 2007-09-26 | Necエレクトロニクス株式会社 | Method for manufacturing nonvolatile semiconductor memory device |

| JP2004199738A (en) * | 2002-12-16 | 2004-07-15 | Seiko Epson Corp | Nonvolatile storage device |

| KR100480645B1 (en) * | 2003-04-01 | 2005-03-31 | 삼성전자주식회사 | Method for manufacturing SONOS memory device with twin-ONO by reverse self-aligning process |

-

2003

- 2003-01-22 KR KR10-2003-0004223A patent/KR100521371B1/en not_active IP Right Cessation

-

2004

- 2004-01-16 JP JP2004008780A patent/JP2004228571A/en active Pending

- 2004-01-22 US US10/761,250 patent/US7091090B2/en not_active Expired - Fee Related

-

2006

- 2006-06-28 US US11/476,006 patent/US20060244014A1/en not_active Abandoned

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6335554B1 (en) * | 1999-03-08 | 2002-01-01 | Kabushiki Kaisha Toshiba | Semiconductor Memory |

| US20030034518A1 (en) * | 1999-03-08 | 2003-02-20 | Kabushiki Kaisha Toshiba | Method for manufacturing semiconductor memory |

| US6177318B1 (en) * | 1999-10-18 | 2001-01-23 | Halo Lsi Design & Device Technology, Inc. | Integration method for sidewall split gate monos transistor |

| US6413821B1 (en) * | 2001-09-18 | 2002-07-02 | Seiko Epson Corporation | Method of fabricating semiconductor device including nonvolatile memory and peripheral circuit |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20090078984A1 (en) * | 2007-09-20 | 2009-03-26 | Kabushiki Kaisha Toshiba | Semiconductor apparatus and method for manufacturing the same |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20040067212A (en) | 2004-07-30 |

| JP2004228571A (en) | 2004-08-12 |

| US7091090B2 (en) | 2006-08-15 |

| KR100521371B1 (en) | 2005-10-12 |

| US20040185628A1 (en) | 2004-09-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6709922B2 (en) | Method of manufacturing semiconductor integrated circuit device including nonvolatile semiconductor memory devices | |

| US20060244014A1 (en) | Nonvolatile memory device and method of forming same | |

| US8269266B2 (en) | Semiconductor device and a method of manufacturing the same | |

| US6891271B2 (en) | Non-volatile memory device | |

| KR100375235B1 (en) | Sonos flash memory device and a method for fabricating the same | |

| US6809385B2 (en) | Semiconductor integrated circuit device including nonvolatile semiconductor memory devices having control gates connected to common contact section | |

| US7521318B2 (en) | Semiconductor device and method of manufacturing the same | |

| US7098109B2 (en) | Multi-level memory cell and fabricating method thereof | |

| US6627491B2 (en) | Method of manufacturing non volatile memory device having two charge storage regions | |

| JP4818061B2 (en) | Nonvolatile semiconductor memory | |

| US6995420B2 (en) | Semiconductor device and method of manufacturing the same | |

| US20060278933A1 (en) | Semiconductor device and manufacturing method thereof | |

| JP2008538867A (en) | Array source line in NAND flash memory | |

| US20070132005A1 (en) | Electrically Erasable and Programmable Read Only Memories Including Variable Width Overlap Regions and Methods of Fabricating the Same | |

| KR100510541B1 (en) | High voltage transistor and method for manufacturing the same | |

| US7592221B2 (en) | Semiconductor memory device and manufacturing method thereof | |

| US6894361B2 (en) | Semiconductor device | |

| KR20080013001A (en) | Semiconductor device and fabrication method thereof | |

| US7645693B2 (en) | Semiconductor device and programming method therefor | |

| JP5415135B2 (en) | Nonvolatile semiconductor memory device | |

| US20100295115A1 (en) | Nonvolatile semiconductor memory device including nonvolatile memory cell | |

| US7144774B1 (en) | Method of fabricating non-volatile memory |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| STCB | Information on status: application discontinuation |

Free format text: ABANDONED -- FAILURE TO RESPOND TO AN OFFICE ACTION |