KR20190126546A - Semiconductor light emitting device - Google Patents

Semiconductor light emitting device Download PDFInfo

- Publication number

- KR20190126546A KR20190126546A KR1020180050568A KR20180050568A KR20190126546A KR 20190126546 A KR20190126546 A KR 20190126546A KR 1020180050568 A KR1020180050568 A KR 1020180050568A KR 20180050568 A KR20180050568 A KR 20180050568A KR 20190126546 A KR20190126546 A KR 20190126546A

- Authority

- KR

- South Korea

- Prior art keywords

- light emitting

- semiconductor light

- emitting device

- encapsulant

- layer

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 246

- 239000000463 material Substances 0.000 claims abstract description 86

- 239000000758 substrate Substances 0.000 claims abstract description 83

- 230000006798 recombination Effects 0.000 claims abstract description 7

- 238000005215 recombination Methods 0.000 claims abstract description 7

- 239000008393 encapsulating agent Substances 0.000 claims description 208

- 230000002265 prevention Effects 0.000 claims description 64

- 229920005992 thermoplastic resin Polymers 0.000 claims description 40

- 238000000034 method Methods 0.000 claims description 39

- 238000002834 transmittance Methods 0.000 claims description 27

- 230000008569 process Effects 0.000 claims description 20

- 229910052751 metal Inorganic materials 0.000 claims description 19

- 239000002184 metal Substances 0.000 claims description 19

- 229920001187 thermosetting polymer Polymers 0.000 claims description 18

- 238000005538 encapsulation Methods 0.000 claims description 13

- 239000007791 liquid phase Substances 0.000 claims description 6

- 230000003667 anti-reflective effect Effects 0.000 claims description 2

- 239000010410 layer Substances 0.000 description 312

- 238000004519 manufacturing process Methods 0.000 description 22

- 230000004888 barrier function Effects 0.000 description 21

- 229920005989 resin Polymers 0.000 description 18

- 239000011347 resin Substances 0.000 description 18

- 239000010931 gold Substances 0.000 description 16

- 239000007788 liquid Substances 0.000 description 16

- 229920002120 photoresistant polymer Polymers 0.000 description 15

- 229920006352 transparent thermoplastic Polymers 0.000 description 13

- 230000008859 change Effects 0.000 description 12

- 239000007769 metal material Substances 0.000 description 10

- 238000000605 extraction Methods 0.000 description 9

- 239000010408 film Substances 0.000 description 9

- 229910052782 aluminium Inorganic materials 0.000 description 7

- 230000007423 decrease Effects 0.000 description 7

- 239000011241 protective layer Substances 0.000 description 7

- 229910052709 silver Inorganic materials 0.000 description 7

- 238000005476 soldering Methods 0.000 description 7

- 238000001723 curing Methods 0.000 description 6

- 229910052737 gold Inorganic materials 0.000 description 6

- 239000007787 solid Substances 0.000 description 6

- 230000005496 eutectics Effects 0.000 description 5

- 238000005259 measurement Methods 0.000 description 5

- 239000003566 sealing material Substances 0.000 description 5

- 238000012546 transfer Methods 0.000 description 5

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 4

- QTBSBXVTEAMEQO-UHFFFAOYSA-N acetic acid Substances CC(O)=O QTBSBXVTEAMEQO-UHFFFAOYSA-N 0.000 description 4

- 239000000853 adhesive Substances 0.000 description 4

- 230000001070 adhesive effect Effects 0.000 description 4

- 238000005520 cutting process Methods 0.000 description 4

- 238000001035 drying Methods 0.000 description 4

- 238000010438 heat treatment Methods 0.000 description 4

- 239000011810 insulating material Substances 0.000 description 4

- 239000002904 solvent Substances 0.000 description 4

- 238000007906 compression Methods 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 238000009826 distribution Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 230000003287 optical effect Effects 0.000 description 3

- 238000007747 plating Methods 0.000 description 3

- 238000002310 reflectometry Methods 0.000 description 3

- 229910052594 sapphire Inorganic materials 0.000 description 3

- 239000010980 sapphire Substances 0.000 description 3

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 230000000903 blocking effect Effects 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 239000011248 coating agent Substances 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 238000006731 degradation reaction Methods 0.000 description 2

- 238000011161 development Methods 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 238000002474 experimental method Methods 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 229910052763 palladium Inorganic materials 0.000 description 2

- 229910052697 platinum Inorganic materials 0.000 description 2

- 229920003229 poly(methyl methacrylate) Polymers 0.000 description 2

- 239000004926 polymethyl methacrylate Substances 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- 230000003252 repetitive effect Effects 0.000 description 2

- 229910052703 rhodium Inorganic materials 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- 239000010935 stainless steel Substances 0.000 description 2

- 229910001220 stainless steel Inorganic materials 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 229910001020 Au alloy Inorganic materials 0.000 description 1

- 229910017770 Cu—Ag Inorganic materials 0.000 description 1

- 229910017767 Cu—Al Inorganic materials 0.000 description 1

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 1

- 239000004809 Teflon Substances 0.000 description 1

- 229920006362 Teflon® Polymers 0.000 description 1

- 230000005856 abnormality Effects 0.000 description 1

- 239000002253 acid Substances 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 229910010293 ceramic material Inorganic materials 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 230000006835 compression Effects 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000005137 deposition process Methods 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000002845 discoloration Methods 0.000 description 1

- 238000000313 electron-beam-induced deposition Methods 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 238000013007 heat curing Methods 0.000 description 1

- 230000017525 heat dissipation Effects 0.000 description 1

- 239000000155 melt Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 150000007522 mineralic acids Chemical class 0.000 description 1

- 229910017604 nitric acid Inorganic materials 0.000 description 1

- 229910052755 nonmetal Inorganic materials 0.000 description 1

- 230000000149 penetrating effect Effects 0.000 description 1

- 238000005240 physical vapour deposition Methods 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 239000002861 polymer material Substances 0.000 description 1

- 230000003449 preventive effect Effects 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 239000002210 silicon-based material Substances 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 229910000679 solder Inorganic materials 0.000 description 1

- 238000003892 spreading Methods 0.000 description 1

- 230000007480 spreading Effects 0.000 description 1

- 238000001029 thermal curing Methods 0.000 description 1

- 229920001169 thermoplastic Polymers 0.000 description 1

- 239000004416 thermosoftening plastic Substances 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/62—Arrangements for conducting electric current to or from the semiconductor body, e.g. lead-frames, wire-bonds or solder balls

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/14—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a carrier transport control structure, e.g. highly-doped semiconductor layer or current-blocking structure

- H01L33/145—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a carrier transport control structure, e.g. highly-doped semiconductor layer or current-blocking structure with a current-blocking structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/36—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes

- H01L33/38—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes with a particular shape

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/52—Encapsulations

- H01L33/54—Encapsulations having a particular shape

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/52—Encapsulations

- H01L33/56—Materials, e.g. epoxy or silicone resin

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Led Device Packages (AREA)

Abstract

Description

본 개시(Disclosure)는 전체적으로 반도체 발광소자에 관한 것으로, 특히 광 추출 효율을 향상시킨 반도체 발광소자에 관한 것이다.The present disclosure relates generally to semiconductor light emitting devices, and more particularly, to semiconductor light emitting devices having improved light extraction efficiency.

여기서는, 본 개시에 관한 배경기술이 제공되며, 이들이 반드시 공지기술을 의미하는 것은 아니다(This section provides background information related to the present disclosure which is not necessarily prior art). This section provides background information related to the present disclosure which is not necessarily prior art.

도 1은 종래의 반도체 발광소자 칩의 일 예를 보여주는 도면이다.1 is a view showing an example of a conventional semiconductor light emitting device chip.

반도체 발광소자 칩은 성장기판(610; 예: 사파이어 기판), 성장기판(610) 위에, 버퍼층(620), 제1 도전성을 가지는 제1 반도체층(630; 예: n형 GaN층), 전자와 정공의 재결합을 통해 빛을 생성하는 활성층(640; 예; INGaN/(In)GaN MQWs), 제1 도전성과 다른 제2 도전성을 가지는 제2 반도체층(650; 예: p형 GaN층)이 순차로 증착되어 있으며, 그 위에 전류 확산을 위한 투광성 전도막(660)과, 본딩 패드로 역할하는 전극(670)이 형성되어 있고, 식각되어 노출된 제1 반도체층(630) 위에 본딩 패드로 역할하는 전극(680: 예: Cr/Ni/Au 적층 금속 패드)이 형성되어 있다. 도 1과 같은 형태의 반도체 발광소자를 특히 레터럴 칩(Lateral Chip)이라고 한다. 여기서, 성장기판(610) 측이 외부와 전기적으로 연결될 때 장착면이 된다. 본 명세서에서 반도체 발광소자 칩 또는 반도체 발광소자가 전기적으로 연결되는 외부는 PCB(Printed Circuit Board), 서브마운트, TFT(Thin Film Transistor) 등을 의미한다.The semiconductor light emitting device chip may include a growth substrate 610 (eg, a sapphire substrate), a

도 2는 미국 등록특허공보 제7,262,436호에 제시된 반도체 발광소자 칩의 다른 예를 보여주는 도면이다. 설명의 편의를 위해 도면기호를 변경하였다.2 is a view showing another example of the semiconductor light emitting device chip disclosed in US Patent No. 7,262,436. For convenience of description, reference numerals have been changed.

반도체 발광소자 칩은 성장기판(610), 성장기판(610) 위에, 제1 도전성을 가지는 제1 반도체층(630), 전자와 정공의 재결합을 통해 빛을 생성하는 활성층(640), 제1 도전성과 다른 제2 도전성을 가지는 제2 반도체층(650)이 순차로 증착되어 있으며, 그 위에 성장기판(610) 측으로 빛을 반사시키기 위한 3층으로 된 전극막(690, 691, 692)이 형성되어 있다. 제1 전극막(690)은 Ag 반사막, 제2 전극막(691)은 Ni 확산 방지막, 제3 전극막(692)은 Au 본딩층일 수 있다. 식각되어 노출된 제1 반도체층(630) 위에 본딩 패드로 기능하는 전극(680)이 형성되어 있다. 여기서, 전극막(692) 측이 외부와 전기적으로 연결될 때 장착면이 된다. 도 2와 같은 형태의 반도체 발광소자 칩을 특히 플립 칩(Flip Chip)이라고 한다. 도 2에 도시된 플립 칩의 경우 제1 반도체층(630) 위에 형성된 전극(680)이 제2 반도체층 위에 형성된 전극막(690, 691, 692)보다 낮은 높이에 있지만, 동일한 높이에 형성될 수 있도록 할 수도 있다. 여기서 높이의 기준은 성장기판(610)으로부터의 높이일 수 있다.The semiconductor light emitting device chip includes a

도 3은 종래의 반도체 발광소자의 일 예를 보여주는 도면이다.3 is a view showing an example of a conventional semiconductor light emitting device.

반도체 발광소자(700)는 리드 프레임(710, 720), 몰드(730), 그리고 캐비티(740) 내에 수직형 반도체 발광소자 칩(750; Vertical Type Light Emitting Chip)이 구비되어 있고, 캐비티(740)는 파장 변환재(160)를 함유하는 봉지재(770)로 채워져 있다. 수직형 반도체 발광소자 칩(750)의 하면이 리드 프레임(710)에 전기적으로 직접 연결되고, 상면이 와이어(780)에 의해 리드 프레임(720)에 전기적으로 연결되어 있다. 수직형 반도체 발광소자 칩(750)에서 나온 광의 일부가 파장 변환재(760)를 여기 시켜 다른 색의 광을 만들어 두 개의 서로 다른 광이 혼합되어 백색광을 만들 수 있다. 예를 들어 반도체 발광소자 칩(750)은 청색광을 만들고 파장 변환재(760)에 여기 되어 만들어진 광은 황색광이며, 청색광과 황색광이 혼합되어 백색광을 만들 수 있다. 도 3은 수직형 반도체 발광소자 칩(750)을 사용한 반도체 발광소자를 보여주고 있지만, 도 1 및 도 2에 도시된 반도체 발광소자 칩을 사용하여 도 3과 같은 형태의 반도체 발광소자를 제조할 수도 있다.The semiconductor

도 3에 기재된 타입의 반도체 발광소자를 일반적으로 패키지(Package) 타입(Type)의 반도체 발광소자라고 하며 반도체 발광소자 칩 크기의 반도체 발광소자를 CSP(Chip Scale Package) 타입의 반도체 발광소자라 한다. CSP 타입의 반도체 발광소자와 관련된 것은 한국 공개특허공보 제2014-0127457호에 기재되어 있다. 최근에는 반도체 발광소자의 크기가 소형화되는 경향에 따라 CSP 타입의 반도체 발광소자에 대한 개발이 활발히 이루어지고 있다.A semiconductor light emitting device of the type described in FIG. 3 is generally called a semiconductor light emitting device of a package type, and a semiconductor light emitting device having a semiconductor light emitting device chip size is called a semiconductor light emitting device of a chip scale package (CSP) type. Related to the CSP type semiconductor light emitting device is disclosed in Korean Patent Laid-Open No. 2014-0127457. Recently, as the size of semiconductor light emitting devices is reduced, development of CSP type semiconductor light emitting devices has been actively performed.

이에 대하여 '발명을 실시하기 위한 구체적인 내용'의 후단에 기술한다.This will be described later in the section titled 'Details of the Invention.'

여기서는, 본 개시의 전체적인 요약(Summary)이 제공되며, 이것이 본 개시의 외연을 제한하는 것으로 이해되어서는 아니된다(This section provides a general summary of the disclosure and is not a comprehensive disclosure of its full scope or all of its features).This section provides a general summary of the disclosure and is not a comprehensive disclosure of its full scope or all, provided that this is a summary of the disclosure. of its features).

본 개시에 따른 일 태양에 의하면(According to one aspect of the present disclosure), 반도체 발광소자에 있어서, 전자와 정공의 재결합에 의해 자외선을 생성하는 활성층을 포함하는 복수의 반도체층과, 복수의 반도체층에 전기적으로 연결된 전극을 구비하는 반도체 발광소자 칩; 반도체 발광소자 칩을 감싸도록 형성되는 봉지재; 그리고, 베이스, 반도체 발광소자 칩의 전극과 전기적으로 연결되는 도전층을 구비하는 외부 기판;을 포함하며, 봉지내 내부에 위치하며 자외선을 반사하는 도전층의 일면이 자외선 반사율이 90% 미만인 물질로 형성되며, 봉지재의 하면 지름은 △Po 값이 봉지내 내부에 위치하며 자외선을 반사하는 도전층의 일면이 자외선 반사율이 90% 이상인 물질로 형성된 때의 △Po 값과 비교했을 때 △Po 값의 차이가 5% 이내가 되는 지름 크기보다 작은 반도체 발광소자가 제공된다.According to one aspect of the present disclosure, in a semiconductor light emitting device, a plurality of semiconductor layers including an active layer that generates ultraviolet light by recombination of electrons and holes, and a plurality of semiconductor layers A semiconductor light emitting device chip having an electrode electrically connected to the semiconductor light emitting device chip; An encapsulant formed to surround the semiconductor light emitting device chip; And an outer substrate having a base and a conductive layer electrically connected to the electrodes of the semiconductor light emitting device chip, wherein one surface of the conductive layer reflecting ultraviolet rays is formed of a material having an ultraviolet reflectance of less than 90%. The difference in the ΔPo value is formed when the diameter of the encapsulant is lower than the ΔPo value when the ΔPo value is located inside the bag and one surface of the conductive layer that reflects ultraviolet rays is formed of a material having an ultraviolet reflectance of 90% or more. A semiconductor light emitting element having a diameter smaller than 5% is provided.

이에 대하여 '발명의 실시를 위한 구체적인 내용'의 후단에 기술한다.This is described later in the section titled 'Details of the Invention.'

도 1은 종래의 반도체 발광소자 칩의 일 예를 보여주는 도면,

도 2는 미국 등록특허공보 제7,262,436호에 제시된 반도체 발광소자 칩의 다른 예를 보여주는 도면,

도 3은 종래의 반도체 발광소자의 일 예를 보여주는 도면,

도 4는 본 개시에 따른 반도체 발광소자의 일 예를 보여주는 도면,

도 5 내지 10은 본 개시에 다른 반도체 발광소자에 있어서 봉지재의 지름 크기와 관련된 특징을 보여주는 도면,

도 11은 본 개시에 따른 반도체 발광소자의 장점을 설명하기 위해 일반적인 반도체 발광소자를 보여주는 도면,

도 12는 본 개시에 따른 반도체 발광소자의 제조 방법의 일 예를 보여주는 도면,

도 13은 본 개시에 따른 예비 봉지재의 일 예를 보여주는 도면,

도 14 내지 도 15는 본 개시에 따른 자외선에 대한 투과율이 80% 이상인 투광성 열가소성 수지로 이루어진 예비 봉지재의 제조 방법의 일 예를 보여주는 도면,

도 16은 종래의 자외선에 대한 투과율이 80% 이상인 액상의 투광성 열가소성 수지를 직접 이용하여 봉지재를 형성하는 경우의 문제점을 보여주는 도면,

도 17은 본 개시에 따른 반도체 발광소자의 제조 방법의 다른 일 예를 보여주는 도면,

도 18은 본 개시에 따른 반도체 발광소자의 제조 방법의 또 다른 일 예를 보여주는 도면,

도 19는 본 개시에 따른 반도체 발광소자의 다른 일 예를 보여주는 도면,

도 20은 본 개시에 따른 반도체 발광소자의 또 다른 일 예를 보여주는 도면.1 is a view showing an example of a conventional semiconductor light emitting device chip;

2 is a view showing another example of the semiconductor light emitting device chip shown in US Patent No. 7,262,436;

3 is a view showing an example of a conventional semiconductor light emitting device;

4 illustrates an example of a semiconductor light emitting device according to the present disclosure;

5 to 10 is a view showing a feature related to the diameter size of the encapsulant in the semiconductor light emitting device according to the present disclosure,

11 is a view showing a general semiconductor light emitting device to explain the advantages of the semiconductor light emitting device according to the present disclosure;

12 illustrates an example of a method of manufacturing a semiconductor light emitting device according to the present disclosure;

13 is a view showing an example of a preliminary encapsulant according to the present disclosure;

14 to 15 are views showing an example of a method of manufacturing a pre-sealing material made of a transparent thermoplastic resin having a transmittance of 80% or more with respect to ultraviolet rays according to the present disclosure,

16 is a view showing a problem in the case of forming an encapsulant using a liquid transparent light-transmitting thermoplastic resin having a transmittance of 80% or more to the conventional ultraviolet ray,

17 is a view showing another example of a method of manufacturing a semiconductor light emitting device according to the present disclosure;

18 illustrates another example of a method of manufacturing a semiconductor light emitting device according to the present disclosure;

19 illustrates another example of a semiconductor light emitting device according to the present disclosure;

20 is a view showing another example of a semiconductor light emitting device according to the present disclosure.

이하, 본 개시를 첨부된 도면을 참고로 하여 자세하게 설명한다(The present disclosure will now be described in detail with reference to the accompanying drawing(s)). 또한 본 명세서에서 상측/하측, 위/아래 등과 같은 방향 표시는 도면을 기준으로 한다.The present disclosure will now be described in detail with reference to the accompanying drawing (s). In addition, in the present specification, direction indications such as up / down, up / down, etc. are based on the drawings.

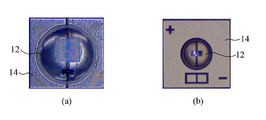

도 4는 본 개시에 따른 반도체 발광소자의 일 예를 보여주는 도면으로서, 도 4(a)는 AA'를 따라 자른 단면도이고, 도 4(b)는 평면도이다.4 is a diagram illustrating an example of a semiconductor light emitting device according to the present disclosure. FIG. 4A is a cross-sectional view taken along line AA ′, and FIG. 4B is a plan view thereof.

반도체 발광소자(1)는 반도체 발광소자 칩(10), 봉지재(12) 및 외부 기판(14)을 포함한다.The semiconductor light emitting device 1 includes a semiconductor light

반도체 발광소자 칩(10)은 전자와 정공의 재결합에 의해 빛을 생성하는 활성층(101)을 포함하는 복수의 반도체층과, 복수의 반도체층에 전기적으로 연결된 전극(102)을 구비한다. 이와 같은 반도체 발광소자 칩(10)은 플립 칩(flip chip)이 바람직하며, 전극(102)은 봉지재(12)로부터 노출되어 있다. 본 실시예에서 반도체 발광소자 칩(10)을 플립 칩으로 예시하였지만, 레터럴 칩(lateral chip)이나 수직형 칩(vertical chip)을 배제하는 것은 아니다. 활성층(101)은 명확히 표시하기 위하여 과장되게 표현하였다. The semiconductor light

봉지재(12)는 반도체 발광소자 칩(10)을 감싸도록 외부 기판(14) 위에 형성된다. 봉지재(12)의 재료는 투광성 열가소성 수지로 이루어진다. 봉지재(12)는 하면의 지름이 최대 4mm을 갖도록 형성될 수 있다. 투광성 열가소성 수지는 자외선(예 : 파장대가 100nm 내지 400nm 인 빛)에 대한 투과율이 80% 이상인 투광성 열가소성 수지가 바람직하다. 더 나아가 바람직하게는 투광성 열가소성 수지는 자외선에 대한 투과율이 90% 이상인 투광성 열가소성 수지가 좋다.The

본 실시예에서 반도체 발광소자 칩(10)은 자외선을 방출할 수 있다. 바람직하게는 UV-C 파장대인 200nm 내지 280nm 인 자외선을 방출한다. 따라서, 반도체 발광소자 칩(10)에서 생성된 빛이 자외선에 대한 투과율이 80% 이상인 투광성 열가소성 수지로 이루어진 봉지재(12)가 렌즈로 역할하여 배광(light distribution)이 원활하게 이루어져 광 추출 효율(extraction efficiency)이 향상될 수 있다.In this embodiment, the semiconductor light emitting

또한, 자외선에 대한 투과율이 80% 이상인 투광성 열가소성 수지는 자외선에 오래 노출된 후에도 손상이 낮은 열가소성 수지가 바람직하다.In addition, the translucent thermoplastic resin having a transmittance of 80% or more to ultraviolet rays is preferably a thermoplastic resin having low damage even after long exposure to ultraviolet rays.

외부 기판(14)은 반도체 발광소자 칩(10)이 실장되는 영역을 제공하는 기판이면 제한되지 않는다. 외부 기판(14)은 반도체 발광소자를 형성하기 위한 기판일 수 있고, 예컨대, 리드 전극들을 포함하는 기판, 인쇄회로기판, 금속 플레이트 기판 등을 포함할 수 있다.The

이와 같은 외부 기판(14)은 베이스(141), 도전층(142, 145), 방지층(143) 및 반사층(144)을 포함할 수 있다.The

베이스(141)는 절연성 물질을 포함할 수 있고, 또한, 열전도율이 높은 물질을 포함할 수 있다. 예를 들어, 고열전도성 폴리머 물질 및/또는 세라믹 물질을 포함할 수 있다. 특히, 베이스(141)는 AlN 세라믹으로 이루어질 수 있다. 따라서, 발광 장치 구동 시, 반도체 발광소자 칩(10)에서 발생하는 열이 베이스(141)를 통해 효과적으로 외부로 방출될 수 있다. The base 141 may include an insulating material and may also include a material having high thermal conductivity. For example, it may comprise a high thermal conductivity polymer material and / or a ceramic material. In particular, the

도전층(142, 145)은 베이스(141)의 상면 및 하면에 형성되며, 상면에 형성된 도전층(142)이 반도체 발광소자 칩(10)의 전극(102)과 전기적으로 연결된다. 상면에 형성된 도전층(142)과 하면에 형성된 도전층(145)은 전기적으로 연결되며 하면에 형성된 도전층(145)을 통해 반도체 발광소자(1)는 외부와 전기적으로 연결된다. 예를 들어 도시된 것과 같이 베이스(141)를 관통하여 베이스(141) 상면에 형성된 도전층(142)과 베이스(141) 하면에 형성된 도전층(145)이 전기적으로 연결될 수 있다. 도전층(142, 145)은 전기적 도전성 물질을 포함할 수 있고, 예를 들어, Ni, Pt, Pd, Rh, W, Ti, Al, Ag, Au, Cu 등과 같은 금속을 포함할 수 있다. 또한 도전층(142, 145)은 단층으로 형성될 수도 있으며 복수의 층으로 형성될 수 도 있다. 여기서, 반도체 발광소자 칩(10)의 전극(102)은 외부 기판(14)의 도전층(142)과 전기적으로 연결되기 위해 외부 기판(14)측으로 향하도록 배치되는 것이 바람직하다. The

방지층(143)은 도전층(142)과 일정 간격 떨어져 베이스(141)의 상면에 위치한다. 예를 들어, Ni, Pt, Pd, Rh, W, Ti, Al, Ag, Au, Cu 등과 같은 금속으로 형성될 수 있다. 방지층(143)이 금속으로 형성된 경우 도전층(142)과 떨어져 위치함으로써, 도전층(142)과의 접촉이 방지되어 쇼트 위험성이 낮아질 수 있다.The

방지층(143)은 봉지재(12) 형성시 봉지재(12)가 방지층(143)을 넘어서 형성되지 않도록 하는 경계턱 즉, 댐(dam)의 역할로 이용될 수 있으며, 방지층(143)은 생략될 수 있다. 방지층(143)은 반도체 발광소자 칩(10)을 보호하는 봉지재(12)의 형태 유지에 좋도록 어느 정도 딱딱한 재질이 바람직하고, 크랙이나 갈라짐 방지에 효과적인 재질로 선택하는 것이 바람직하다.The

이와 달리, 방지층(143)은 반도체 발광소자 칩(10)으로부터 나오는 빛을 봉지재(12)로 반사할 수 있는 유색의 반사 물질로 형성될 수 있지만 이에 한정되는 것은 아니다.In contrast, the

더욱이, 방지층(143)이 실리콘 재질과 다른 물질(예 : 금속 물질)로 이루어질 수 있다. 특히 금속 물질로 방지층(143)이 이루어진 때 외부 기판(14) 및 봉지재(12)와의 접착력이 증가되어 신뢰성이 향상될 수 있다. 게다가 금속 물질인 도전층(142)을 형성할 때 동시에 형성할 수 있음으로써, 제조 공정을 단축시켜 제조 공정 시간 및 제조 비용을 감소시킬 수 있다.In addition, the

방지층(143)은 댐 역할로 이용되지만 봉지재(12)를 형성하는 투광성 열가소성 수지가 흘러나가는 것을 벽처럼 막는 것이 아니라 봉지재(12) 형성시 방지층(143)의 상면과 봉지재(12) 하면 사이에 발생하는 표면 장력에 의해 봉지재(12)가 방지층(143)을 넘어서 형성되지 않도록 하기 때문에 봉지재(12)가 방지층(143)의 상면 전체 또는 일부분만을 덮도록 형성될 수 있다. 바람직하게는 방지층(143)의 상면(1431)과 측면이 만나는 모서리 중 반사층(144) 방향의 방지층(143) 외측면(1432)과 방지층(143) 상면(1431)이 만나는 모서리 부분에서 봉지재(12)와 방지층(143)의 상면(1432) 사이에 발생하는 표면 장력 효과가 극대화되기 때문에 봉지재(12)가 방지층(143)의 상면(1431) 전체를 덮는 것이 좋다. 특히 방지층(143)의 상면(1431)과 외측면(1432)이 이루는 각도(1433)가 수직일 때 봉지재(12)와 방지층(143)의 상면(1431) 사이에 발생하는 표면 장력 효과가 극대화된다. 또한 방지층(143)은 봉지재(12)가 흘러나가는 것을 방지하기 위해서 방지층(143)은 틈이 없는 폐회로 형태로 형성하는 것이 바람직하다. 또한 방지층(143)이 금속 물질로 형성된 경우에 열가소성 수지로 형성된 봉지재(12)와의 사이에 발생하는 표면 장력이 극대화되어 봉지재(12)가 렌즈 형상으로 더 잘 형성될 수 있다. 다만 방지층(143)이 금속 물질로 형성되며, 동시에 폐회로 형태를 형성하는 경우 쇼트 방지를 위해 베이스(141)는 절연성 물질로 형성되는 것이 바람직하다. 이해를 돕기 위해 방지층(143)의 상면(1431)과 외측면(1432)을 확대하여 원 안에 도시하였다. 다만 이때, 방지층(143) 내측면(1434)은 봉지재(12)에 의해 덮이고, 방지층(143) 외측면(1432)은 봉지재(12)에 의해 덮이지 않을 수 있다. 본 개시에서 봉지재(12) 하면의 지름 크기는 중요하며 이유는 도 5에서 설명한다. 따라서 봉지재(12) 하면의 지름 크기를 제어하는 방지층(143)은 중요한 구성요소이다. 또한 본 개시는 방지층(143)이 벽처럼 막는 것을 배제하지는 않는다.The

방지층(143)의 높이(H1)는 반도체 발광소자 칩(10)의 높이보다 낮게 형성되고, 도전층(142)의 높이(H2)와 동일하게 형성되는 것이 바람직하지만, 이에 한정되는 것은 아니다. 예를 들어, 방지층(143)의 높이(H1)는 도전층(142)의 높이(H2)보다 작거나 크게 형성될 수 있다. 방지층(143)의 높이가 도전층(142)의 높이와 같거나 작은 경우에는 반도체 발광소자(1)에서 나오는 빛의 지향각이 방지층(143)의 높이가 도전층(142)의 높이보다 큰 경우보다 넓어질 수 있다.The height H1 of the

방지층(143)의 폭(D1)은 도전층(142)의 폭(D2)의 폭보다 작게 그리고 방지층(143)과 도전층(142)이 떨어진 폭(D3)보다 작게 형성되는 것이 바람직하다. 이에 한정되지 않고, 방지층(143)의 폭(D1)은 방지층(143)과 도전층(142)이 떨어진 폭(D3)보다 크게 또는 동일하게 형성될 수 있다.The width D1 of the

반사층(144)은 베이스(141)의 상면에 형성되며, 반사 물질로 형성될 수 있다. 예를 들어, Al, Ag, Au 등과 같은 금속 물질로 이루어질 수 있다. 도전층(142), 방지층(143) 및 반사층(144)을 모두 동일한 물질(예 : Au)로 형성하는 경우 세 층을 한 번에 형성할 수 있어서 제조공정이 단순화될 수 있다. 베이스(141) 위에 금속 물질로 된 층을 형성하는 방법은 증착이나 도금 등의 방법을 사용할 수 있다. 다만 도전층(142) 내부에는 부분적으로 Al을 형성하는 것이 바람직하다. 여기서, 반사층(144)은 반사층(144)과 봉지재(12) 사이의 열팽창계수 차이를 극복하기 위해 또는 반도체 발광소자 칩(10)과 반사층(144)간의 쇼트(Short) 문제를 방지하기 위하여 반도체 발광소자 칩(10)과 방지층(143)으로부터 소정 구간 떨어져 위치한다.The

반사층(144)은 외부 기판(14)을 향하는 반도체 발광소자 칩(10)에서 나온 광을 반사하여 외부 기판(14) 상측으로 나가도록 하여 광 추출 효율을 향상시킬 수 있다. 특히 반도체 발광소자 칩(10)에서 나온 광이 자외선인 경우 반사 효율이 높은 Al 으로 반사층(144)을 형성하는 것이 바람직하다.The

또한 반사층(144)은 도전층(142)과 방지층(143) 사이에 형성되거나(도 18 참조), 도전층(142)과 방지층(143) 사이에만 형성되거나(도 19 참조), 반사층(144)이 형성되지 않을 수도 있다(도 20 참조).Also, the

한편, 외부 기판(14)은 베이스(141)의 하면에 위치하는 방열 패드(미도시)를 더 포함할 수 있다. 상기 방열 패드는 외부 기판(14)의 열을 더욱 용이하게 외부로 방출시키는 역할을 한다.Meanwhile, the

도 5 내지 도 10은 본 개시에 따른 반도체 발광소자에 있어서 봉지재 하면 지름의 크기와 관련된 특징을 보여주는 도면이다.5 to 10 is a view showing the characteristics related to the size of the lower surface of the encapsulant in the semiconductor light emitting device according to the present disclosure.

반도체 발광소자(1)에서 봉지재(12)의 평면적 크기는 폐회로 형태의 방지층(143)으로 둘러싸인 부분의 평면적 크기와 같거나 작을 수 있다. 도 4에서 기재한 것처럼 봉지재(12)와 방지층(143) 사이의 표면 장력이 가장 큰 경우는 봉지재(12)의 하면이 방지층(143)의 상면 전체를 덮은 경우이기 때문에 봉지재(12)의 평면적 크기는 방지층(143)으로 둘러싸인 부분의 평면적 크기와 같은 것이 바람직하다. 예를 들어 봉지재(12)의 평면과 방지층(143)으로 둘러싸인 부분의 평면이 도 4와 같이 원형인 경우 봉지재(12)의 하면의 지름(1431)과 방지층(143)의 지름(1431)은 같은 크기를 갖는다. 도 5는 실험을 통해 출원인이 발견한 것으로 자외선을 발광하는 반도체 발광소자 칩을 감싸는 봉지재(12)의 하면 지름 크기가 줄어들수록 △Po 값이 증가하는 것을 보여준다. 이것은 봉지재(12)의 하면 지름 크기가 줄어들수록 봉지재(12) 내부에서 반사에 의해 손실되는 빛의 양이 줄어들어 △Po 값이 증가하는 것이다. 봉지재(12)의 내부에 위치하며 반도체 발광소자 칩(10)에서 나오는 빛을 반사하는 것은 반도체 발광소자 칩(10), 도전층(143) 및 방지층(143)이다. 즉 반도체 발광소자 칩(10)에서 나오는 빛이 봉지재(12)의 내부에서 반사되는 면은 반도체 발광소자 칩(10)의 상면과 측면, 도전층(142) 및 방지층(143)의 상면 및 도전층(143)과 방지층(143) 사이에 노출된 베이스(141)의 상면이 될 수 있으며 이러한 다양한 면과의 반사에 의해 봉지재(12)의 내부에서 빛이 손실된다. 종래의 자외선 이외의 빛(예 : 청색광)을 발광하는 경우에는 봉지재의 내부에서 발생하는 빛의 손실이 큰 문제가 되지 않았다. 봉지재 내부에 자외선 이외의 빛에 대해 반사효율이 높은 반사 물질을 사용하여 반사면을 형성할 수 있었기 때문이다. 그러나 파장이 짧은 자외선의 경우 반사효율이 높은 반사 물질이 다양하지 않고 더 나아가 도전층(143)의 경우 자외선에 대한 반사효율이 낮은 물질(예 : Au)을 사용해야 되는 경우가 있어 자외선을 발광하는 반도체 발광소자에 있어서는 봉지재 내부에서 반사에 의한 빛 손실이 큰 문제가 되고 있다. 특히 자외선 중에서도 파장이 가장 짧은 UV-C 대역의 파장을 갖는 자외선을 발광하는 반도체 발광소자에 있어서 봉지재 내부에서 반사에 의한 빛 손실이 더 큰 문제가 된다. 출원인은 봉지재(12)의 하면 지름이 일정 크기 이상으로 작아지면 봉지재 내부에 형성된 반사면이 자외선에 대해 낮은 반사율을 갖는 물질로 이루어진 경우에도 높은 반사율을 갖는 물질로 반사면이 형성된 경우와 비교했을 때 △Po 값의 차이가 작은 것을 발견하였다. 특히 봉지재(12)의 하면 지름이 작아져도 △Po의 값의 차이가 5% 근처에서 큰 변화가 없는 것을 발견하였다. 도 5 내지 도 10을 통해 이를 자세히 설명하고자 한다.The planar size of the

△Po(광증가율)는 렌즈 형상의 봉지재(12)가 형성되지 않은 경우의 반도체 발광소자의 광량을 Po1라 하고 렌즈 형상의 봉지재(12)가 형성된 반도체 발광소자의 광량을 Po2 할 때 Po2/Po1의 값을 의미한다. 예를 들어 △Po가 150%라면 렌즈 형상의 봉지재를 사용하지 않은 경우와 비교했을 때 광량이 50% 증가했다는 것을 의미한다. 즉 렌즈 형상의 봉지재(12)가 형성된 경우 반도체 발광소자의 광량이 증가한다. 특히 렌즈 형상이 반구 형상일 때 광량이 크게 증가할 수 있다. 제1 그래프(15)는 반사층(144), 도전층(142) 및 방지층(143)이 자외선에 대한 반사율이 90% 이상인 물질(예 : Al )로 형성된 경우이며, 제2 그래프(16)는 반사층(144), 도전층(142) 및 방지층(143)이 자외선에 대한 반사율이 40% 이하인 물질(예 : Au )로 형성된 경우이다. 제1 그래프(15) 및 제2 그래프(16)는 렌즈 형상의 봉지재(12)의 내부에서 발생하는 반사에 의한 자외선 손실이 봉지재(12)의 하면 지름이 작아질수록 작아져서 △Po 값이 점차 증가하는 것을 보여준다. 특히 자외선에 대한 반사율이 90% 이상인 물질이 사용된 제1 그래프(15)가 동일한 봉지재(12)의 하면 지름을 가질 때 자외선에 대한 반사율이 40% 이하인 물질이 사용된 제2 그래프(16)보다 더 큰 △Po 값을 보여준다. 다만 봉지재(12)의 하면 지름이 작아질수록 제1 그래프(15)와 제2 그래프(16) 사이의 차이가 작아진다. 예를 들어 봉지재의 하면 지름이 3.4mm인 경우(151, 161), 제1 그래프(15)와 제2 그래프(16) 사이의 차이가 13% 이었지만 봉지재의 하면 지름이 2.1mm인 경우(152, 162), 제1 그래프(15)와 제2 그래프(16) 사이의 차이가 5% 가 되었다. 즉 봉지재 하면 지름이 작아질수록 봉지재(12) 내부에 형성된 방지층(143) 및 도전층(142)을 형성하는 물질의 자외선에 대한 반사율이 봉지재 내부에서 발생하는 반사에 의한 빛 손실에 점점 더 작은 영향을 미쳐서 봉지재 하면 지름이 일정한 크기 이하로 작아지는 경우 봉지재 내부에 형성된 반사면이 자외선에 대해 낮은 반사율을 갖는 경우에도 높은 반사율을 갖는 물질로 반사면이 형성된 경우와 거의 차이가 없어지는 것을 발명자가 발견하였다. 다만 봉지재 하면 지름이 작아질수록 △Po 값의 차이가 지속적으로 작아지지 않으며 △Po 값의 차이가 5% 이하부터는 △Po 값의 차이가 점선(153, 163)과 같이 거의 일정하게 유지되는 특징을 보여주었다.ΔPo (light growth rate) is Po1 when the light amount of the semiconductor light emitting element when the lens-shaped

일반적으로 반도체 발광소자에서 광증가율이 높은 것이 바람직하기 때문에 봉지재 내부에 형성된 자외선 반사면(예 : 도전층, 방지층 등)에는 자외선에 대한 반사율이 높은 물질(예 : 90% 이상인 Al)을 사용하는 것이 예상된다. 그러나 자외선에 대한 반사율이 90% 이상인 물질, 예를 들어 Al으로 도전층(142) 및 방지층(143)을 형성한 경우 특히 도전층(142)이 복수의 층으로 형성될 때 Al으로 이루어진 부분이 도전층(142)의 상부인 경우 자외선을 잘 반사하지만 반도체 발광소자 칩(10)의 전극과 솔더링 또는 유테틱 본딩과 같은 방법으로 접합하여 전기적으로 연결될 때 반도체 발광소자 칩(10)의 전극(102)이 도전층(142)의 Al으로 이루어진 부분과 잘 접합되지 않는 문제가 발생하였다. 이에 본 실시예에서는 반도체 발광소자 칩(10)의 전극(102)이 도전층(142)에 잘 접합될 수 있는 물질인 금(Au)을 사용하여 도전층(142)을 형성하였다. 그러나 금(Au)은 자외선에 대한 반사율이 40% 이하인 물질로 △Po 값이 낮은 문제가 있었다. In general, since it is desirable to have a high light growth rate in a semiconductor light emitting device, a material having a high reflectance against ultraviolet rays (for example, Al having 90% or more) is used for an ultraviolet reflecting surface (for example, a conductive layer or a protective layer) formed inside the encapsulant. It is expected. However, when the

출원인은 본 개시에서 발견한 것을 기초로 자외선에 대한 반사율이 90% 미만으로 낮지만 반도체 발광소자 칩(10)의 전극과 잘 접합되는 물질로 도전층(142)을 형성하면서, 자외선에 대한 반사율이 90% 이상인 물질로 도전층(142)을 형성한 경우와 같은 정도의 △Po 값을 갖도록 봉지재(12)의 하면 지름의 크기를 한정하였다. 바람직하게는 자외선에 대한 반사율이 90% 이상인 물질을 사용한 경우와 자외선에 대한 반사율이 40% 이하인 물질을 사용한 경우의 △Po 값의 차이가 5% 이내가 되는 크기 이내로 봉지재(12)의 하면 지름의 크기가 형성되도록 하였다. 예를 들어 도 5 그래프를 얻기 위해 사용한 반도체 발광소자의 크기를 보여주는 도 6 및 도 7을 보면 봉지재 하면 지름 크기가 2.1mm 일 때 △Po 값이 차이가 5% 이내가 되었다. 도 6 및 도 7에 사용된 반도체 발광소자 칩의 크기는 1.125mm*1.125mm*0.15mm 이며, 도 6은 도전층(142), 반사층(144) 및 방지층(143)에 Au를 사용한 경우이며, 도 7은 도전층(142), 반사층(144) 및 방지층(143)에 Al을 사용한 경우이다. 방지층(143)의 폭은 0.1mm 이다. 또한 반도체 발광소자의 평면적 크기는 외부 기판(14)의 평면적 크기이며 이것은 반도체 발광소자가 적용되는 분야에 따라 일정한 크기가 요구된다. 예를 들어 도 6 및 도 7에 기재된 반도체 발광소자를 보면 외부 기판(14)의 평면적 크기가 6mm*6mm로 일정하게 유지되지만 본 개시에 따라 봉지재(12) 하면의 크기가 작아지기 때문에 △Po 값의 차이가 5% 이내가 되는 경우 봉지재 하면과 접하는 외부 기판의 평면적이 봉지재 하면과 접하지 않는 외부 기판의 평면적보다 작게 될 수 있다. 즉 도 8(a) 및 도 8(b)를 비교해보면 외부 기판(14)의 평면적 크기가 3.5mm*3.5mm인 자외선을 발광하는 반도체 발광소자에서 도 8(a)에 도시된 반도체 발광소자는 종래의 반도체 발광소자로 봉지재(12) 하면과 접하는 외부 기판(14)의 평면적이 봉지재(12) 하면과 접하지 않는 외부 기판(14)의 평면적보다 큰 것을 보여준다. 종래에는 렌즈 형상의 봉지재가 클수록 광량이 커진다고 알려져 있었기 때문이다. 그러나 본 개시에 따른 반도체 발광소자를 보여주는 도 8(b)는 봉지재(12) 하면과 접하는 외부 기판(14)의 평면적이 봉지재(12) 하면과 접하지 않는 외부 기판(14)의 평면적보다 작은 것을 보여준다. 본 개시에서 출원인이 발견한 것에 따르면 반도체 발광소자가 자외선을 발광하는 경우에는 렌즈 형상의 봉지재 하면의 지름이 작을수록 광량이 커지기 때문이다. 특히 본 개시에 따른 반도체 발광소자에서 외부 기판(14)의 평면적이 3.5mm*3.5mm인 도 9(a)와 외부 기판(14)의 평면적이 6mm*6mm인 도 9(b)를 비교해보면 외부 기판(14)의 평면적이 클 때 봉지재(12)의 하면과 접하는 외부 기판(14)의 평면적과 봉지재(12)의 하면과 접하지 않는 외부 기판의 평면적 차이가 더 커진 것을 알 수 있다.Applicant, based on what is found in the present disclosure, reflectance of ultraviolet light is less than 90%, but the

또한 봉지재 내부에서 반사에 의한 빛 손실에 가장 큰 영향을 미치는 부분은 도전층(142)이다. 방지층(143)은 폭이 0.1mm 이내로 자외선에 노출된 부분이 크지 않으며 반도체 발광소자 칩(10)은 플립 칩 구조로 자외선을 반사하는 반사층을 포함하여 자외선에 대한 반사효율이 높은 구조로 형성될 수 있기 때문이다. 다만 도전층(142)의 일부는 반도체 발광소자 칩(10)으로 덮여 있어 자외선에 노출되지 않는 부분이 있다. 따라서 도전층(142) 중 반도체 발광소자 칩(10)으로 덮여 있지 않고 노출된 부분이 봉지재(12) 내부에서 반사에 의한 빛 손실에 큰 영향을 준다. 반도체 발광소자 칩(10)의 평면적 크기는 반도체 발광소자 칩(10)의 종류에 따라 다양하게 변할 수 있다. 일반적으로 반도체 발광소자 칩(10)의 평면적 크기에 따라 대면적 칩과 소면적 칩으로 구분하고 있다. 대면적 칩은 반도체 발광소자 칩(10)의 평면적 크기가 0.8mm2 이상 1.5mm2 이하인 경우를 말하며 소면적 칩은 반도체 발광소자 칩(10)의 평면적 크기가 0.06mm2 이상 0.3mm2 이하인 경우를 말한다. 도 10은 다양한 반도체 발광소자 칩(10)의 종류에 따라 도전층(142)에 자외선에 대한 반사율이 90% 이상인 물질을 사용한 경우와 자외선에 대한 반사율이 40% 이하인 물질을 사용한 경우의 △Po 값의 차이가 5% 이내가 되는 도전층(142)의 전체 면적과 노출된 도전층(142)의 면적의 크기를 보여준다. 예를 들어 대면적 칩의 하나인 반도체 발광소자 칩(10)의 면적이 1.1532mm2 인 경우 도전층(142)의 전체면적이 2.0998mm2이고 노출된 도전층(142) 면적이 0.9466mm2 이하일 때 도전층(142)에 자외선에 대한 반사율이 90% 이상인 물질을 사용한 경우와 자외선에 대한 반사율이 40% 이하인 물질을 사용한 경우의 △Po 값의 차이가 5% 이내인 것을 보여준다. 또한 소면적 칩의 하나인 반도체 발광소자 칩(10)의 면적이 0.105mm2 인 경우 도전층(142)의 전체면적이 0.7054mm2이고 노출된 도전층(142) 면적이 0.6004mm2 이하일 때 도전층(142)에 자외선에 대한 반사율이 90% 이상인 물질을 사용한 경우와 자외선에 대한 반사율이 40% 이하인 물질을 사용한 경우의 △Po 값의 차이가 5% 이내인 것을 보여준다. 또한 도 10을 보면 대면적 칩을 사용한 경우 도전층(142)의 전체면적과 노출된 도전층(142) 면적비가 35% 이상 45% 이하인 경우에 자외선에 대한 반사율이 90% 이상인 물질을 사용한 경우와 자외선에 대한 반사율이 40% 이하인 물질을 사용한 경우의 △Po 값의 차이가 5% 이내인 것을 보여준다. 반면에 소면적 칩을 사용한 경우 도전층(142)의 전체면적과 노출된 도전층(142) 면적비가 70% 이상 85% 이하인 경우에 자외선에 대한 반사율이 90% 이상인 물질을 사용한 경우와 자외선에 대한 반사율이 40% 이하인 물질을 사용한 경우의 △Po 값의 차이가 5% 이내인 것을 보여준다. 본 개시에서 최초로 발견한 실험 결과를 사용하여 반도체 발광소자 칩의 평면적 크기 및 도전층(142)의 전체면적과 노출된 도전층(142) 면적비를 고려하여 자외선에 대한 반사율이 90% 이상인 물질을 사용한 경우와 자외선에 대한 반사율이 40% 이하인 물질을 사용한 경우의 △Po 값의 차이가 5% 이내가 되도록 도전층 전체 면적을 특정할 수 있으며, 도전층의 전체 면적에 따라 도전층을 덮는 봉지재 하면의 지름도 특정할 수 있다. 다만 실험 결과를 보면 대면적 칩 및 소면적 칩의 종류에 상관없이 노출된 도전층(142)의 평면적 크기는 0.45mm2 이상 1.0mm2 이하인 것이 바람직하다. In addition, the portion of the encapsulant having the greatest influence on light loss due to reflection is the

본 개시에서 규정한 것 이외의 평면적 크기를 갖는 반도체 발광소자 칩이 사용되는 경우 반도체 발광소자 칩의 평면적 크기에 따라 자외선에 대한 반사율이 90% 이상인 물질을 사용한 경우와 자외선에 대한 반사율이 40% 이하인 물질을 사용한 경우의 △Po 값의 차이가 5% 이내가 되는 범위를 만족하는 도전층(142)의 전체면적과 노출된 도전층(142) 면적비 또는 노출된 도전층(142)의 평면적 크기가 본 개시에서 규정한 크기를 벗어날 수도 있지만 도전층(142)에 자외선에 대한 반사율이 90% 이상인 물질을 사용한 경우와 자외선에 대한 반사율이 40% 이하인 물질을 사용한 경우의 △Po 값의 차이가 5% 이내가 되는 범위에 해당하는 경우 본 개시의 범위에 포함될 수 있다. When a semiconductor light emitting device chip having a planar size other than that specified in the present disclosure is used, a material having a reflectance of about 90% or more according to the planar size of the semiconductor light emitting device chip and having a reflectance of about 40% or less When the material is used, the total area of the

도 5 내지 도 10에 기재된 실험 결과를 얻은 실험 방법은 유사 또는 동등 성능의 반도체 발광소자 칩을 각각의 반도체 발광소자에 본딩을 한다, 이때 본딩은 솔더링 또는 유태틱 본팅 중 하나이다. 이후 1차 광 측정을 진행하여 Po1의 값을 얻는다. 광 측정의 경우 Instrument systems社의 Spectrometer CAS-140CT와 적분구 ISP-250을 이용하여 측정 하였다. 이후 봉지재를 이용하여 렌즈형태를 구현한다. 이후 2차 광 측정을 진행하여 Po2의 값을 얻는다. 조건의 경우 1차 광 측정과 동일 조건으로 한다. 이후 1, 2차 광 특성을 상대 비교하였다.The experimental method obtained the experimental results described in FIGS. 5 to 10 bonds a semiconductor light emitting device chip of similar or equivalent performance to each semiconductor light emitting device, wherein the bonding is either soldering or Jewish bonding. After that, the first optical measurement is performed to obtain a value of Po1. In the case of optical measurement, the measurement was carried out using Spectrometer CAS-140CT and integrating sphere ISP-250 of Instrument Systems. Since the encapsulation material is implemented to form a lens. The secondary light measurement is then performed to obtain the value of Po2. The conditions are the same as those for the primary light measurement. After that, the primary and secondary optical characteristics were compared.

또한 봉지재(12)를 도전층(142) 위에 형성시키는 것이 봉지재(12)의 하면 지름을 최소로 할 수 있지만, 도 4를 보면 도전층(142)은 쇼트를 방지하기 위해서 도전층(142) 사이에 개방된 부분(1421)이 있다. 개방된 부분(1421)에 절연물질이 충진될 수도 있지만 절연물질이 충진된 경우에도 봉지재(12)는 개방된 부분(1421) 때문에 봉지재(12)의 하면과 도전층(142)의 상면 사이에 발생하는 표면 장력만으로는 봉지재(12)가 도전층(142) 상면에만 형성되지 않고 도전층(142)을 벗어나서 형성되어 렌즈 형상의 봉지재(12)를 도전층(142) 상면에만 한정되게 형성하는데 바람직하지 않다. 이에 도전층(142)으로부터 200um 이내의 간격 내에 개방된 구간이 없이 폐회로 형태의 방지층(143)을 베이스(141) 상면으로부터 돌출되게 형성하였다. 특히 도전층(142)과 방지층(143) 사이에 반사층이 없기 때문에 홈(1422)이 형성되어 방지층(143)이 봉지재(12)가 형성될 때 벽과 같은 댐 기능을 할 수도 있지만 본 실시예에서는 방지층(143)의 높이가 도전층(142)의 높이와 동일하거나 작게 형성되어 벽과 같은 댐 기능을 하기에는 방지층(143)의 높이가 낮다. 그러나 도 4에 기재된 것처럼 방지층(143)의 상면과 봉지재(12)의 하면 사이에 발생하는 표면장력을 이용하여 봉지재(12)가 방지층(143)을 넘어서 형성되지 않도록 하는 댐 역할은 충분히 할 수 있다. 도 4에서 방지층(143)의 폐회로 형태가 원형이지만 사각형 등 필요에 따라 변형될 수 있다. 또한 본 실시예에서는 봉지재 하면과 접하는 도전층 및 방지층을 형성하는 물질로 Au을 예시로 하였지만 Au 이외에 자외선에 대한 반사율이 낮으며 반도체 발광소자 칩과의 솔더링 또는 유테틱 본딩과 같은 방법으로 접합할 때 접합력이 좋은 금속 물질(예 : Ag)도 사용할 수 있다. 또한 본 실시예에서 자외선에 대한 반사율이 40%로 낮은 물질은 본 개시의 바람직한 일 예이며 반도체 발광소자가 자외선을 발광할 때도 높은 △Po 값을 가질 수 있도록 하는 자외선 반사율이 높은 물질(예 : 자외선 반사율이 90% 이상인 Al 등) 이외의 물질(예 : 자외선 반사율이 90% 미만)은 본 개시의 범위에 포함될 수 있다. In addition, although forming the

도 11은 본 개시에 따른 반도체 발광소자의 장점을 설명하기 위해 일반적인 반도체 발광소자를 보여주는 도면이다.11 is a view showing a general semiconductor light emitting device to explain the advantages of the semiconductor light emitting device according to the present disclosure.

도 11(a)를 참고하면 반도체 발광소자에 있어서, 기 성형된 렌즈(L)가 반도체 발광소자 칩(10a) 위에 부착될 수 있다.Referring to FIG. 11A, in the semiconductor light emitting device, a preformed lens L may be attached onto the semiconductor light emitting

하지만, 본 개시는 투광성 열가소성 수지로 이루어진 봉지재(12)를 이용하여 렌즈 형상을 구현함으로써, 별도의 렌즈를 구비하지 않아 반도체 발광소자를 더욱 소형화할 수 있다. 더 나아가 방지층(143)을 사용하여 봉지재(12)의 크기를 효율적으로 제어할 수 있다. 그러나 투광성 열가소성 수지 중 자외선에 대한 투과율이 80% 이상인 투광성 열가소성 수지의 경우 액상에서 경화되어 고형화될 때 솔벤트가 대부분 휘발되어 부피가 90% 이상 줄어들기 때문에 자외선에 대한 투과율이 80% 이상인 액상의 투광성 열가소성 수지를 이용하여 렌즈 형상의 봉지재(12)를 구현하기 어려웠다. 본 개시에서는 이러한 문제를 해결하여 자외선에 대한 투과율이 80% 이상인 투광성 열가소성 수지로 형성된 렌즈 형상의 봉지재(12)를 구현하였다. 더 나아가 자외선에 대한 투과율이 80% 이상인 투광성 열가소성 수지를 사용하여 렌즈 형상의 봉지재(12)를 구현함으로써 반도체 발광소자 칩(10)을 감싸고 있으면서 외부 기판(14)과 접하는 봉지재(12) 하면 부분을 제외하고는 전면이 외부로 노출된 봉지재(12)가 가능하게 되어 반도체 반도체 발광소자 칩(10)에서 나와 봉지재(12)를 통과한 자외선이 외부 기판(14) 방향을 제외하고 전 방향으로 직접 나갈 수 있도록 하였다. 또한 종래의 액상에서 경화될 때 부피 변화가 작아 렌즈 형성이 가능한 투광성 열가소성 수지(예 : PMMA(Poly Methyl Methacrylate), PC(Poly Cabonate) 등)를 사용하여 렌즈를 형성할 수 있지만 반도체 발광소자 칩(10)에서 나오는 빛이 자외선인 경우 투과율이 낮고 열화가 잘되어 사용할 수 없었기 때문에 반도체 발광소자 칩(10)에서 나오는 빛이 자외선인 경우에 종래에는 투광성 열가소성 수지가 아닌 유리, 사파이어 또는 석영과 같은 재질로 형성된 렌즈를 사용하였지만 본 개시에서는 이러한 문제를 해결하기 위해 자외선에 대한 투과율이 80% 이상이며 열화가 잘되지 않는 투광성 열가소성 수지를 사용하여 렌즈 형상의 봉지재(12)를 형성한 것이다.However, the present disclosure implements a lens shape by using the

그리고, 렌즈의 굴절률에 따라 광 추출 효율은 차이를 가지게 되므로, 공기와 접촉하는 최외각 매질의 굴절률과 공기와 굴절률의 차이를 최소로 해주어야 한다. 예를 들어, 도 11(b)를 참고하면 렌즈(L)와 반도체 발광소자 칩(10b) 사이는 빈 공간(A)이고, 렌즈(L)가 1.8의 굴절률을 갖는 사파이어(Sapphire) 또는 1.54의 굴절률을 갖는 석영(quartz)으로 이루어지는 경우, 반도체 발광소자 칩(10b)으로부터 공기로의 굴절률 변화는 1(A) - 1.54(L) 또는 1.8(L) - 1(공기) 순으로 변화하기 때문에 굴절률 변화가 순차적으로 이루어지지 않아 광 손실이 발생할 수 있다.In addition, since the light extraction efficiency is different according to the refractive index of the lens, the difference between the refractive index of the outermost medium in contact with the air and the air and the refractive index should be minimized. For example, referring to FIG. 11B, a sapphire or 1.54 having a refractive index of 1.8 is an empty space A between the lens L and the semiconductor light emitting

하지만, 본 개시에서는 공간이 없이 봉지재(12)가 반도체 발광소자 칩(10)과 접촉하여 감싸고 있어서 투광성 열가소성 수지의 굴절율을 1.3으로 보았을 때, 반도체 발광소자 칩(10)으로부터 공기로의 굴절률 변화는 1.3(12) - 1(공기)로 굴절률 변화가 순차적으로 이루어지기 때문에 광 손실이 발생하지 않는다. 따라서, 굴절률이 큰 매질에서 굴절률이 작은 매질로 광이 입사할 때 계면에서 발생되는 전반사 현상을 효과적으로 방지하여 광 추출 효율을 더욱 개선할 수 있다.However, in the present disclosure, when the

이와 같은 자외선에 대한 투과율이 80% 이상이며 액상에서 경화될 때 부피 변화가 큰 투광성 열가소성 수지로 이루어지는 봉지재(12)를 형성하는 방법은 도 12 내지 도 15를 이용하여 후술한다. 이때, 봉지재(12)의 형상은 반구형의 볼록한 렌즈 형상을 가질 수 있으며, 이에 한정하는 것은 아니다. 예를 들어, 봉지재(12)는 오목한 렌즈 형상, 상면이 평면인 렌즈 형상, 요철의 렌즈 형상, 원뿔의 렌즈 형상 또는 기하학 구조의 렌즈 형상으로 형성될 수 있으며, 렌즈 형상에 등에 따라 배광 특성이 변형되며, 효율 및 배광 특성의 요구에 맞게 변형이 가능하다.Such a method of forming the

도 12는 본 개시에 따른 반도체 발광소자의 제조 방법의 일 예를 보여주는 도면이다.12 is a diagram illustrating an example of a method of manufacturing a semiconductor light emitting device according to the present disclosure.

반도체 발광소자의 제조 방법에 있어서, 도 12(a)에 도시된 바와 같이 먼저, 외부 기판(24)을 준비한 후 외부 기판(24)의 도전층(242)과 반도체 발광소자 칩(20)의 복수의 전극(202)이 서로 맞대응 되도록 반도체 발광소자 칩(20)을 외부 기판(24) 위에 놓는다. 이에 따라, 외부 기판(24)의 도전층(242)과 반도체 발광소자 칩(20)의 복수의 전극(202)이 서로 전기적으로 연결된다. 외부 기판을 준비하는 것은 베이스에 도전층, 방지층 및 반사층을 형성하는 것을 의미한다. In the method of manufacturing a semiconductor light emitting device, as shown in FIG. 12A, first, an

여기서, 외부 기판(24) 위에 형성된 도전층(242), 방지층(243) 및 반사층(244)의 형상, 패턴, 또는 경계 등을 인식하여 소자가 놓일 위치 및 각도를 보정하는 소자 이송 장치(21)를 사용하여, 반도체 발광소자 칩(20)을 외부 기판(24) 위에 놓는다.Here, the

다음으로, 도 12(b)에 도시된 바와 같이 반도체 발광소자 칩(20)을 감싸도록 자외선에 대한 투과율이 80% 이상인 투광성 열가소성 수지로 이루어진 고형의 예비 봉지재(4)를 놓는다. 이때, 예비 봉지재(4)는 소자 이송 장치(21)를 이용하여 외부 기판(24) 및 반도체 발광소자 칩(20) 위에 배치된다. 여기서, 예비 봉지재(4)는 반도체 발광소자 칩(20)으로부터 소정 간격으로 이격되도록 배치될 수 있다다.Next, as shown in FIG. 12B, a solid

예비 봉지재(4)는 자외선에 대한 투과율이 80% 이상인 액상의 투광성 열가소성 수지가 경화되어 고형으로 형성될 수 있다. 예를 들어, 액상의 투광성 열가소성 수지가 경화되어 부피가 약 90% 이상 줄어든 고형의 예비 봉지재(4)를 형성할 수 있다. 구체적으로, 예비 봉지재(4)는 도 13에 도시하였다.The

반도체 발광소자 칩(20)을 감싸도록 예비 봉지재(4)가 배치되기 때문에 본체부(41)의 홈(43)의 폭은 반도체 발광소자 칩(20)의 폭보다 크게 형성되고, 지지부(42)의 높이는 반도체 발광소자 칩(20)의 높이보다 크게 형성되는 것이 바람직하다. 예비 봉지재(4)를 제조하는 방법에 대해서는 도 14 내지 15에서 설명한다.Since the

다음으로, 도 12(c)에 도시된 바와 같이, 예비 봉지재(4)를 열경화하여 반도체 발광소자 칩(20)을 감싸는 반구 형상의 봉지재(22)를 형성한다. 이때, 봉지재(22)의 형상은 반구형의 볼록한 렌즈 형상을 가질 수 있으며, 이에 한정하는 것은 아니다.Next, as shown in FIG. 12 (c), the

봉지재(22)를 형성하기 위해 예비 봉지재(4)를 열경화하는 경우, 예비 봉지재(4)가 봉지재(22)로 될 때 부피가 크게 변화되지 않는다. 도 14 및 도 15에 도시된 바와 같이, 예비 봉지재(4)는 이미 자외선에 대한 투과율이 80% 이상인 액상의 투광성 열가소성 수지(50)의 부피가 90% 이상 줄어들어 형성된 것이므로, 예비 봉지재(4)가 봉지재(22)로 될 때 부피 변화율은 2% 이하일 수 있다. 예비 봉지재(4)가 열경화하여 봉지재(22)를 형성할 때 부피 변화율이 2% 이하이기 때문에 봉지재(22)의 렌즈 형상을 반구형의 볼록한 렌즈 형상 이외에 다양한 렌즈 형상으로 구현할 수 있는 것이다. 즉 예비 봉지재(4)를 녹여 액상으로 만든 후 원하는 렌즈(예 : 볼록한 렌즈 형상, 오목한 렌즈 형상, 원뿔의 렌즈 형상 등)형상으로 만들어 경화하여도 부피 변화가 작기 때문에 원하는 렌즈 형상을 쉽게 제작할 수 있다.In the case where the

예비 봉지재(4)가 열경화될 때, 외부 기판(24)의 방지층(243)과의 표면 장력에 의해 봉지재(22)가 방지층(243)을 넘어서 형성되지 않는다. 이때, 방지층(243)은 외부 기판(24)의 도전층(242) 형성시 동시에 형성될 수 있지만, 이에 한정하지 않고 별도의 공정을 통해 형성될 수도 있다. 방지층(243)과 도전층(242)이 동시에 형성되는 경우, 제조 공정을 단축시켜 제조 공정 시간 및 제조 비용을 감소시킬 수 있다.When the

예비 봉지재(4)를 열경화하기 위한 열처리 및/또는 건조는 고온에서 경화되는 것이 바람직하다. 예를 들어, 200℃ 내지 300℃의 온도에서 대략 4시간 내지 6시간 동안 수행될 수 있다. 상술한 열처리 및/또는 건조 온도 및 시간은 고형의 수지층(4)이 경화되어 균일한 상면을 가지며, 반도체 발광소자 칩(20) 및 외부 기판(24)과 안정적인 결합이 이루어질 수 있도록 한정된 것이나, 이에 한정되는 것은 아니다. 고온에서 경화하는 경우 기포가 발생할 수 있으나, 기포 발생은 진공 오븐을 사용하여 제거할 수 있다.The heat treatment and / or drying for thermosetting the

다음으로, 도 12(d)에 도시된 바와 같이 절단선(26)을 따라 절단하여 개별 반도체 발광소자(2)를 형성한다.Next, as shown in FIG. 12 (d), the individual semiconductor light emitting devices 2 are formed by cutting along the cutting lines 26.

도 13은 본 개시에 따른 예비 봉지재의 일 예를 보여주는 도면이다.13 is a view showing an example of a preliminary encapsulant according to the present disclosure.

예비 봉지재(4)는 홈(43)을 구비하는 본체부(41), 본체부(41)의 일측면과 연결되는 지지부(42)를 포함한다.The

도 14 내지 도 15는 본 개시에 따른 자외선에 대한 투과율이 80% 이상인 투광성 열가소성 수지로 이루어진 예비 봉지재의 제조 방법의 일 예를 보여주는 도면이다.14 to 15 are views showing an example of a method of manufacturing a preliminary encapsulant made of a transparent thermoplastic resin having a transmittance of 80% or more with respect to ultraviolet rays according to the present disclosure.

예비 봉지재(4)는 도 14 및 도 15를 참고하면 수축 및 열압축 방식에 의해 형성된다.The

구체적으로, 도 14(a)에 도시된 바와 같이, 제1 베이스층(30) 위에 포토레지스트층(31, photoresistor layer)을 형성한다. 포토레지스트층(31)은 포토레지스트 페이스트(paste)를 스크린 인쇄법(screen printing) 등을 이용하여 형성될 수 있다.Specifically, as shown in FIG. 14A, a

다음으로, 도 14(b)에 도시된 바와 같이, 소정의 패턴을 가지는 마스크(32)를 포토레지스터층(31) 위에 배치시킨 후, 자외선을 조사하여 노광(exposure) 공정을 수행한다. 마스크(32)는 제1 영역(33)이 노출된 패턴을 갖는다.Next, as shown in FIG. 14B, a

자외선을 포토레지스터층(31)에 조사하면, 마스크(32)에 의해 자외선에 노출된 제1 영역(33)의 포토레지스터층(31)보다 단단하게 과경화되고, 마스크(32)에 의해 자외선에 노출되지 않는 제2 영역(34)의 포토레지스터층(31)은 과경화되지 않는다.When the ultraviolet rays are irradiated onto the

다음으로, 도 14(c)에 도시된 바와 같이 현상(develpoment)을 통해 제1 영역(33)에서 광경화된 포토레지스터층(31)을 제외한 제2 영역(34)에 형성된 포토레지스터층(31)을 제거하는 식각 공정을 수행한다. 예를 들어, 식각 공정은 습식 식각을 통해 이루어질 수 있는데, 예를 들어 불산, 질산, 아세트산, 황산, 염산 중 적어도 하나를 포함하는 무기산 기반의 현상 용액에 시편을 담궈 현상을 하면 노광되지 않은 부분 즉, 제2 영역(34)에 포토레지스터층(31)이 제거되어 제2 영역(34)은 제1 베이스층(30)을 노출하고, 제2 영역(34)을 제외한 제1 영역(33)에는 포토레지스터층(31)이 잔존한다.Next, as shown in FIG. 14C, the

다음으로, 도 14(d)에 도시된 바와 같이 식각공정에 의해 제1 베이스층이 노출된 제2 영역(34)에 금속층(35)을 형성한다. 제1 영역(33)에는 금속층(35)이 형성되지 않는다.Next, as illustrated in FIG. 14D, the

금속층(35)은 포토레지스터층(31)의 높이보다 높게 형성될 수 있지만, 이와 달리 작게 또는 동일한 높이로 형성될 수도 있다. 금속층(35)은 Au, Al, Ag 등과 같은 금속 물질로 이루어질 수 있으며, 전자빔 증착 등의 물리적 기상 증착법(PECVD) 또는 화학적 기상 증착법(CVD) 등의 증착 공정을 통해 형성되는 것이 바람직하지만, 이에 한정되지 않는다.The

다음으로, 도 14(e)에 도시된 바와 같이 리프트 오프(lift off) 공정을 수행하여 제1 영역(33)에 위치하는 포토레지스터층(31)을 제거하여 제1 베이스층(30) 위에 제2 영역(34)에만 형성된 금속층(35)만 위치한다. 금속층(35)은 도 14(f)에 도시한 것처럼 더미(Dummy) 반도체 발광소자 칩(36)과의 솔더링 접착을 할 때 접착력을 향상시키기 위한 것이다.Next, as shown in FIG. 14E, the

리프트 오프 공정을 통해 희석불산(DHF, Dilute HF) 또는 HNO3와 같은 산 용액을 사용하여 제1 영역(33)에 위치하는 포토레지스터층(31)을 제거할 수 있다.Through the lift off process, an acid solution such as dilute hydrofluoric acid (DHF, Dilute HF) or HNO 3 may be used to remove the

다음으로, 도 14(f)에 도시된 바와 같이, 금속층(35) 위에 더미(Dummy) 반도체 발광소자 칩(36)을 배치시킨다. 금속층(35)과 더미 반도체 발광소자 칩(36)은 외력에 의해 가압되어 서로 접착되거나 접착 물질(A)을 이용하여 서로 접착할 수 있다. 예를 들어, 접착 물질(A)은 도전성 페이스트, 절연성 페이스트, 폴리머 접착제, AuSn 솔더 등 다양하게 선택가능하며, 특별히 제한되지는 않는다.Next, as shown in FIG. 14F, a dummy semiconductor light emitting

본 실시예에서는 더미 반도체 발광소자 칩(36)의 크기는 도 4에 도시된 반도체 발광소자 칩(10) 보다 크게 형성되도록 도시하였지만, 이와 달리 동일하거나 작게 형성될 수 있다.Although the size of the dummy semiconductor light emitting

다음으로, 도 14(g)에 도시된 바와 같이, 제1 베이스층(30) 위에 일체로 형성된 더미 반도체 발광소자 칩(36) 및 금속층(35)을 제2 베이스층(37) 위에 배치된 예비 봉지재용 기판(40)과 대응되도록 배치한다. 더미 반도체 발광소자 칩(36)의 상면이 예비 봉지재용 기판(40)의 상면과 마주하도록 배치된다.Next, as shown in FIG. 14G, the dummy semiconductor light emitting

이때, 제2 베이스층(37)은 약 200℃의 고온이 유지되는 핫 플레이트(hot plate)인 것이 바람직하다. 이에 따라, 제2 베이스층(37) 위에 배치된 예비 봉지재용 기판(40)은 플렉시블한 상태이다.At this time, the

예비 봉지재용 기판(40)은 상면 및 하면이 평탄한 면의 형상으로 형성되며, 자외선에 대한 투과율이 80% 이상인 투광성 열가소성 수지로 이루어진다. 구체적으로, 15(a)를 참고하면 자외선에 대한 투과율이 80% 이상인 액상의 투광성 열가소성 수지(50)를 제1 이송부(51)를 이용하여 고정틀(52)에 주입한다.The

고정틀(52)은 리지드(rigid)한 금속 판 또는 비금속 판일 수 있으며 자외선에 대한 투과율이 80% 이상인 액상의 투광성 열가소성 수지(50)의 형태 유지에 좋도록 어느 정도 딱딱한 재질이 바람직하다. 예를 들어, Al, Cu, Ag, Cu-Al 합금, Cu-Ag 합금, Cu-Au 합금, SUS(스테인리스스틸) 등이 사용될 수 있으며, 도금된 판도 물론 사용 가능하다.The fixing

다음, 도 15(b)를 참고하면, 열경화하여 고형으로 이루어진 예비 봉지재용 기판(40)을 형성한다. 예비 봉지재용 기판(40)은 열경화 공정에 의해 자외선에 대한 투과율이 80% 이상인 액상의 투광성 열가소성 수지(50)의 부피가 50% 이상 바람직하게는 90% 이상 줄어들어 형성될 수 있다. 즉, 액상의 투광성 열가소성 수지(50)에서 솔벤트를 휘발시켜 고형화하는 열경화 공정으로 솔벤트가 휘발되면서 부피가 크게 줄어들기 때문이다. Next, referring to FIG. 15 (b), the

이때, 액상의 투광성 열가소성 수지(50)를 경화하기 위한 열경화 공정은 예를 들어, 200℃ 내지 300℃의 온도에서 대략 15시간 내지 20시간 동안 수행될 수 있다. 바람직하게는 250℃의 온도에서 18시간 동안 열경화가 이루어진다. 상술한 열경화 공정에 따른 온도 및 시간은 액상의 투광성 열가소성 수지(50)가 동시에 경화되어 균일하고 평탄한 상면을 가지며, 반도체 발광소자 칩(20)과 안정적인 결합이 이루어질 수 있도록 한정된 것이나, 이에 한정되는 것은 아니다.At this time, the thermosetting process for curing the liquid

다음, 도 15(c)를 참고하면, 예비 봉지재용 기판(40)의 상면 및 하면이 평탄한 모양을 갖도록 고정틀(52)에서 예비 봉지재용 기판(40)을 분리하여 절단선(53)을 따라 절단하여 개별 예비 봉지재용 기판(40)을 형성한다.Next, referring to FIG. 15 (c), the

다음으로, 도 14(h)에 도시된 바와 같이 열압축 공정을 수행하여 더미 반도체 발광소자 칩(36)에 의해 예비 봉지재용 기판(40)을 압축한다. 앞서 살펴본 바와 같이, 예비 봉지재용 기판(40)은 고온을 유지하는 제2 베이스층(37)에 의해 플렉시블한 상태이므로, 열압축 공정을 수행하는 경우 더미 반도체 발광소자 칩(36)에 의해 압축된다.Next, as shown in FIG. 14H, the

다음으로, 도 14(i)에 도시된 바와 같이, 더미 반도체 발광소자 칩(36)의 형상에 따른 복수의 홈(38)을 갖는 고형의 예비 봉지재(4)를 형성한다. 복수의 홈(38)의 깊이는 더미 반도체 발광소자 칩(36)의 높이와 동일하게 형성되는 것이 바람직하지만, 더미 반도체 발광소자 칩(36)의 높이보다 크게 또는 작게 형성될 수 있다.Next, as shown in FIG. 14I, a solid

다음으로, 도 14(j)에 도시된 바와 같이, 예비 봉지재(4)가 각각의 홈(38)을 갖도록 절단선(39)을 따라 절단한다.Next, as shown in FIG. 14 (j), the

도 16은 종래의 자외선에 대한 투과율이 80% 이상인 액상의 투광성 열가소성 수지를 직접 이용하여 봉지재를 형성하는 경우의 문제점을 보여주는 도면이다.16 is a view showing a problem in the case of forming an encapsulant using a liquid transparent light-transmitting thermoplastic resin having a transmittance of 80% or more of the conventional ultraviolet.

자외선에 대한 투과율이 80% 이상인 액상의 투광성 열가소성 수지를 이용하여 직접 봉지재를 형성하는 경우, 액상의 투광성 열가소성 수지를 경화하기 위해 열경화할 때 도포된 액상의 투광성 열가소성 수지의 부피가 약 90% 이상 줄어들기 때문에 원하는 형상의 봉지재를 형성하려면 반복적으로 액상의 투광성 열가소성 수지의 도포 및 열경화 공정을 수행해야만 한다.When the encapsulant is directly formed using a liquid translucent thermoplastic resin having a transmittance of 80% or more to ultraviolet rays, the volume of the liquid translucent thermoplastic resin applied when thermosetting to cure the liquid translucent thermoplastic resin is about 90%. Since the abnormality is reduced, in order to form an encapsulant having a desired shape, it is necessary to repeatedly apply a liquid-transmissive thermoplastic resin and a thermosetting process.

반복적인 액상의 투광성 열가소성 수지의 도포 및 열경화 공정에 의해 제조 공정 시간 및 제조 비용이 증가될 수 있다.The manufacturing process time and manufacturing cost can be increased by the application and thermosetting process of the repetitive liquid translucent thermoplastic resin.

예를 들어, 도 16(a)를 참고하면 반복적인 액상의 투광성 열가소성 수지의 도포 및 열경화 공정에 의해 봉지재(222a)가 방지층(243a)을 넘어서 형성될 수 있다. 이에 따라, 봉지재(222a)가 반구형의 볼록한 렌즈 형상으로 형성되지 못해 배광이 원활하게 이루어지지 않아 광추출 효율이 감소하여 신뢰성이 감소될 수 있다. 더욱이, 봉지재(222a)가 방지층(243a)을 넘어서 형성되는 경우 봉지재(222a)가 반사층(244a)을 덮도록 형성될 수 있어 반사층(244a)의 반사효율이 떨어져 광추출 효율이 감소할 수 있다.For example, referring to FIG. 16 (a), the

그리고, 도 16(b)를 참고하면 반복적인 액상의 투광성 열가소성 수지의 도포 및 열경화 공정에 의해 봉지재(22b) 내에 기포(B, Bubble)가 발생할 수 있다. 즉 봉지재(22b)를 반구형의 볼록한 렌즈 형상으로 형성하기 위해 도포 및 열경화 공정이 반복됨으로써, 경화된 봉지재(22b)가 반복적으로 경화됨으로써, 도포되는 액상의 투광성 열가소성 수지와 경화된 봉지재(22b)의 표면에서 또는 경화된 봉지재(22b) 내부에서 기포(B)가 발생할 수 있다. 봉지재(22b) 내부에 기포(B)가 발생함으로써, 봉지재(22b)가 균일하게 형성되지 못해 반도체 발광소자 칩(20b)으로부터 발생하는 빛이 원활하게 확산되지 못해 신뢰성이 감소될 수 있다.In addition, referring to FIG. 16B, bubbles B and bubbles may be generated in the

도 17은 본 개시에 따른 반도체 발광소자의 제조 방법의 다른 일 예를 보여주는 도면이다.17 illustrates another example of a method of manufacturing a semiconductor light emitting device according to the present disclosure.

도 12(b) 공정 이전에, 즉 반도체 발광소자 칩(20)을 감싸도록 예비 봉지재(4)를 놓기 전에, 도 17(a)를 참고하면, 자외선에 대한 투과율이 80% 이상인 액상의 투광성 열가소성 수지를 도포하여 액상의 수지층(60)을 형성한다. 이때, 자외선에 대한 투과율이 80% 이상인 액상의 투광성 열가소성 수지는 도 15(a)에 도시된 제1 이송부(51)와 동일한 기능을 수행하는 제2 이송부(61)를 통해 반도체 발광소자 칩(62)을 감싸도록 도포한다.Before the process of FIG. 12 (b), that is, before placing the

다음, 도 17(b)를 참고하면, 액상의 수지층(60)을 열경화하여 봉지재층(63)을 형성한다. 봉지재층(63)은 열경화 공정에 의해 솔벤트가 휘발되어 액상의 수지층(60)의 부피보다 50% 이상 바람직하게는 90% 이상 부피가 줄어들어 형성될 수 있다. 본 개시에서, 봉지재층(63)은 약 10um 두께로 형성되는 것이 바람직하다.Next, referring to FIG. 17B, the

다음, 도 17(c)를 참고하면, 봉지재층(63) 위에 예비 봉지재(64)를 놓아 봉지재(22)를 형성한다. 이때, 봉지재층(63)과 예비 봉지재(64)는 동일한 물질로 이루어짐으로써, 봉지재(22)를 형성하기 위해 열경화 공정을 수행할 때 봉지재층(63)은 예비 봉지재(64)에 용융된다. 봉지재층(63)을 형성한 후 예비 봉지재(64)를 사용하는 것이 봉지재층(63)을 사용하지 않고 예비 봉지재(64)를 사용한 경우보다 적은 경화 시간에도 빠르게 렌즈 형태를 만들 수 있다. 또한 반도체 발광소자 칩의 전극 사이에 봉지재층(63)이 잘 채워짐에 따라 외부 기판과 반도체 발광소자 칩 사이의 밀착력 향상에 도움을 준다.Next, referring to FIG. 17 (c), the

예비 봉지재(64)를 이용하여 봉지재(22)를 형성하는 방법은 도 12(b)에 기재된 반도체 발광소자의 제조 방법과 실질적으로 동일하다. 자외선에 대한 투과율이 80% 이상이며 자외선에 의한 열화가 잘 일어나지 않은 투광성의 열가소성 수지에는 Dupont社의 Teflon Af 제품군이 있다.The method of forming the

도 18은 본 개시에 따른 반도체 발광소자의 제조 방법의 또 다른 일 예를 보여주는 도면이다. 18 is a view illustrating still another example of a method of manufacturing a semiconductor light emitting device according to the present disclosure.

반도체 발광소자의 제조 방법에 있어서, 도 18(a)에 도시된 바와 같이 먼저, 상면의 일부분이 노출된 외부 기판(74)을 준비한다. 외부 기판(74)은 베이스(741), 도전층(742), 절연층(743) 및 방지층(745)을 포함한다. 이때, 방지층(745)과 도전층(742)은 동시에 형성될 수 있지만, 별도의 공정을 통해 형성될 수도 있다. 이때, 절연층(743)은 생략될 수 있다. 방지층(745)의 경우 베이스(741)를 관통하는 홈을 Laser로 가공한 뒤 스퍼터(Sputter)를 이용하여 Seed 금속을 증착한다. 이후 Dry photoreist film을 사용하여 패턴을 형성 후 도금을 통하여 도전층(742)을 형성하게 된다. 도금을 통하여 도전층(742)을 형성할 때 방지층(745)을 동시에 형성할 수 있다.In the method of manufacturing a semiconductor light emitting device, as shown in FIG. 18A, first, an

외부 기판(74)은 베이스(741) 위에 복수의 도전층(742)과 복수의 도전층(742) 사이에 절연층(743)이 형성되고, 방지층(745)을 중심으로 베이스(741)의 상면이 노출된다. 이때, 반사층(744)이 형성될 영역에 대응하는 부분의 베이스(741)가 노출된다. The

다음으로, 도 18(b)에 도시된 바와 같이, 노출된 베이스(741) 위에 반사 물질을 이용하여 반사층(744)을 형성한다. 반사층(744)은 봉지재(72)의 하면에 대응하여 형성되는 제1 반사층(7440)과 방지층(745)에 의해 일정 간격으로 떨어져 위치하며 봉지재(72)에 의해 덮이지 않는 제2 반사층(7441)을 포함한다. Next, as shown in FIG. 18B, the

제1 반사층(7440) 및 제2 반사층(7441)은 동일한 물질로 동시에 형성될 수 있지만, 이에 한정되는 것은 아니다.The first

예를 들어, 반도체 발광소자 칩(70)의 측면에 위치하는 제1 반사층(7440)은 반도체 발광소자 칩(70)이 자외선(UV, ultraviolet)을 방출하는 경우, 자외선에 의한 변색이 방지되면서 높은 반사도를 유지하며 절연성을 갖는 화이트 실리콘(White Silicon)으로 이루어지고, 제1 반사층(7440) 및 반도체 발광소자 칩(70)으로부터 소정 간격 떨어져 위치함으로써, 제1 반사층(7440)보다 자외선에 영향을 덜 받는 제2 반사층(7441)은 은(Ag) 또는 알루미늄의 금속 물질로 이루어질 수도 있다.For example, when the semiconductor light emitting

다음으로, 도 18(c)에 도시된 바와 같이, 반도체 발광소자 칩(70)의 전극(702)이 외부 기판(74)의 도전층(742)과 전기적으로 연결되도록 외부 기판(74) 위에 실장한다. 본 예에서, 반도체 발광소자 칩(70)으로는 플립 칩(flip chip)이 적합하지만, 레터럴 칩(lateral chip)이나 수직형 칩(vertical chip)을 배제하는 것은 아니다.Next, as shown in FIG. 18C, the

다음으로, 도 18(d)에 도시된 바와 같이, 반도체 발광소자 칩(70)을 감싸도록 봉지재(72)를 형성한다. 이때, 봉지재(72)의 형상은 반구형의 볼록한 렌즈 형상을 가질 수 있으며, 이에 한정하는 것은 아니다.Next, as shown in FIG. 18D, an

봉지재(72) 형성시 봉지재(72)와 방지층(745) 사이의 표면 장력에 의해 봉지재(72)가 방지층(745)을 넘어서 형성되지 않는다.When the

반도체 발광소자 칩(70)과 외부 기판(74)이 봉지재(72)에 의해 일체로 결합되도록 봉지재(72)를 경화한다. 봉지재(72)를 경화하기 위한 열처리 및/또는 건조는 102℃ 내지 170℃의 온도에서 대략 1시간 내지 5시간 동안 수행될 수 있다. 상술한 열처리 및/또는 건조 온도 및 시간은 봉지재(72)가 균일한 표면과 두께 그리고 봉지재(72) 내부에 기포가 형성되지 않도록 하며, 반도체 발광소자 칩(70) 및 외부 기판(74)과 안정적인 결합이 이루어질 수 있도록 한정된 것이나 형성될 수 있도록 한정된 것이나, 이에 한정되는 것은 아니다. 또한 봉지재(72)가 경화과정에서 부피 변화가 큰 물질로 형성되는 경우에는 도 12에 기재된 예비 봉지재를 사용하여 봉지재(72)를 형성할 수 있다. 본 개시에 따른 반도체 발광소자의 제조 방법의 순서는 당업자가 용이하게 변경할 수 있는 범위에서는 본 개시의 범위에 포함될 수 있다.The

도 19는 본 개시에 따른 반도체 발광소자의 다른 일 예를 보여주는 도면이다.19 is a view illustrating another example of a semiconductor light emitting device according to the present disclosure.

반도체 발광소자(8)는 반사층(844)이 제2 반사층이 없이 제1 반사층(844)만 있는 것을 제외하고, 도 4에 기재된 반도체 발광소자(1)와 실질적으로 동일하다. The semiconductor

도 20은 본 개시에 따른 반도체 발광소자의 또 다른 일 예를 보여주는 도면이다.20 illustrates another example of a semiconductor light emitting device according to the present disclosure.

반도체 발광소자(9)는 반사층이 없는 것을 제외하고, 도 4에 기재된 반도체 발광소자(1)와 실질적으로 동일하다. The semiconductor

이하 본 개시의 다양한 실시 형태에 대하여 설명한다.Hereinafter, various embodiments of the present disclosure will be described.

(1) 반도체 발광소자에 있어서, 전자와 정공의 재결합에 의해 자외선을 생성하는 활성층을 포함하는 복수의 반도체층과, 복수의 반도체층에 전기적으로 연결된 전극을 구비하는 반도체 발광소자 칩; 반도체 발광소자 칩을 감싸도록 형성되는 봉지재; 그리고, 베이스, 반도체 발광소자 칩의 전극과 전기적으로 연결되는 도전층을 구비하는 외부 기판;을 포함하며, 봉지내 내부에 위치하며 자외선을 반사하는 도전층의 일면이 자외선 반사율이 90% 미만인 물질로 형성되며, 봉지재의 하면 지름은 △Po 값이 봉지내 내부에 위치하며 자외선을 반사하는 도전층의 일면이 자외선 반사율이 90% 이상인 물질로 형성된 때의 △Po 값과 비교했을 때 △Po 값의 차이가 5% 이내가 되는 지름 크기보다 작은 반도체 발광소자.(1) A semiconductor light emitting device comprising: a semiconductor light emitting device chip comprising a plurality of semiconductor layers including an active layer for generating ultraviolet rays by recombination of electrons and holes, and electrodes electrically connected to the plurality of semiconductor layers; An encapsulant formed to surround the semiconductor light emitting device chip; And an outer substrate having a base and a conductive layer electrically connected to the electrodes of the semiconductor light emitting device chip, wherein one surface of the conductive layer reflecting ultraviolet rays is formed of a material having an ultraviolet reflectance of less than 90%. The difference in the ΔPo value is formed when the diameter of the encapsulant is lower than the ΔPo value when the ΔPo value is located inside the bag and one surface of the conductive layer that reflects ultraviolet rays is formed of a material having an ultraviolet reflectance of 90% or more. A semiconductor light emitting element having a diameter smaller than 5%.

(2) 봉지내 내부에 위치하며 자외선을 반사하는 도전층의 일면이 자외선 반사율이 40% 이하인 물질로 형성된 반도체 발광소자.(2) A semiconductor light emitting device, wherein the surface of the conductive layer that is located inside the bag and reflects ultraviolet rays is formed of a material having an ultraviolet reflectance of 40% or less.

(3) 봉지내 내부에 위치하며 자외선을 반사하는 도전층의 일면이 Au로 형성된 반도체 발광소자.(3) A semiconductor light emitting element, which is formed inside of an encapsulation layer and has one surface of a conductive layer that reflects ultraviolet rays.

(4) 봉지재의 하면 지름은 △Po 값이 50% 이상일 때 지름보다 작은 반도체 발광소자.(4) The lower surface diameter of the encapsulant is a semiconductor light emitting element smaller than the diameter when the value ΔPo is 50% or more.

(5) 외부 기판은 도전층과 일정거리 떨어져서 폐회로 형태로 형성된 방지층을 포함하며, 봉지재의 하면이 방지층의 상면과 접하는 반도체 발광소자.(5) The external substrate includes a prevention layer formed in a closed circuit form at a predetermined distance away from the conductive layer, and the lower surface of the encapsulant contacts the upper surface of the prevention layer.

(6) 봉지내 내부에 위치하며 자외선을 반사하는 방지층의 일면이 자외선 반사율이 40% 이하인 물질로 형성된 반도체 발광소자.(6) A semiconductor light emitting element, which is located inside the bag and is formed of a material having one surface of an anti-reflective layer that reflects ultraviolet rays with an ultraviolet reflectance of 40% or less.

(7) 봉지내 내부에 위치하며 자외선을 반사하는 도전층 일면 및 방지층 일면이 동일한 금속으로 형성되는 반도체 발광소자.(7) A semiconductor light emitting element, which is located inside the bag and is formed of the same metal on one surface of the conductive layer and the prevention layer that reflects ultraviolet rays.

(8) 봉지재는 자외선에 대한 투과율이 80% 이상인 열가소성 수지로 형성된 반도체 발광소자.(8) The encapsulant is a semiconductor light emitting element formed of a thermoplastic resin having a transmittance of 80% or more against ultraviolet rays.

(9) 열가소성 수지는 액상에서 고형화되는 열경화 공정에서 부피가 90% 이상 줄어드는 반도체 발광소자.(9) A semiconductor light emitting device in which a thermoplastic resin has a volume of 90% or more in a thermosetting step of solidifying in a liquid phase.

(10) 봉지재의 하면과 접하는 외부 기판의 평면적이 봉지재의 하면과 접하지 않는 외부 기판의 평면적보다 작은 반도체 발광소자.(10) A semiconductor light emitting element in which the plane of the outer substrate in contact with the lower surface of the encapsulant is smaller than the plane of the outer substrate not in contact with the lower surface of the encapsulant.

본 개시에 의하면, 자외선 추출 효율이 높으면서 반도체 발광소자 칩과 도전층 사이의 접합력이 높은 반도체 발광소자를 얻을 수 있다.According to the present disclosure, a semiconductor light emitting device having a high ultraviolet extraction efficiency and a high bonding force between the semiconductor light emitting device chip and the conductive layer can be obtained.

본 개시에 의하면, 반도체 발광소자 칩이 실장되는 외부기판의 상면에 형성되는 반사층에 있어서, 반사층을 알루미늄(Al) 또는 화이트 실리콘(White Silicon)으로 형성함으로써, 은(Ag)으로 이루어질 때보다 반도체 발광소자 칩(10)에서 방출되는 자외선에 의해 변색이 방지되면서 높은 반사도를 유지하기 때문에 신뢰성이 향상되는 반도체 발광소자를 얻을 수 있다.According to the present disclosure, in the reflective layer formed on the upper surface of the external substrate on which the semiconductor light emitting device chip is mounted, the reflective layer is formed of aluminum (Al) or white silicon, so that semiconductor light emission is more than that of silver (Ag). Since discoloration is prevented by ultraviolet rays emitted from the

본 개시에 의하면, 봉지재 경화시 외부 기판 위에 방지층에 의해 봉지재가 방지층을 넘어서 형성되지 않도록 하는 반도체 발광소자를 얻을 수 있다.According to the present disclosure, it is possible to obtain a semiconductor light emitting device which prevents the encapsulant from being formed over the antiblocking layer by the prevention layer on the external substrate during encapsulation curing.

본 개시에 의하면 봉지재 내부에 위치하며 자외선을 반사하는 외부 기판의 반사면(예 : 도전층 및 방지층의 상면)을 자외선에 대한 반사율이 90% 이하인 물질로 형성한 경우에도 봉지재의 지름 크기를 조절하여 △Po 값이 50% 이상인 반도체 발광소자를 얻을 수 있다. 더 나아가 봉지재 내부에 위치하며 자외선을 반사하는 외부 기판의 반사면(예 : 도전층 및 방지층의 상면)을 자외선에 대한 반사율이 90% 이하인 물질로 형성된 경우에도 자외선에 대한 반사율이 90% 이상인 물질을 사용한 경우와 비교했을 때 △Po 값의 차이가 5% 이내인 반도체 발광소자를 얻을 수 있다. According to the present disclosure, the diameter of the encapsulant is controlled even when the reflective surface of the external substrate (eg, the upper surface of the conductive layer and the prevention layer) that is located inside the encapsulant and reflects the ultraviolet rays is formed of a material having a reflectance of 90% or less. Thus, a semiconductor light emitting device having a ΔPo value of 50% or more can be obtained. Furthermore, even when the reflective surface of the external substrate (eg, the upper surface of the conductive layer and the prevention layer) that is located inside the encapsulant and is formed of a material having a reflectivity of UV of 90% or less, the material having a reflectance of UV of 90% or more When compared with the case of using the semiconductor light emitting device having a difference of ΔPo value within 5% can be obtained.

본 개시는 파장이 짧은 자외선을 발광하는 반도체 발광소자에 있어서, 봉지재 내부에 위치하며 자외선을 반사하는 반사면은 반사 측면에서는 자외선에 대한 반사율이 높은 물질(예 : Al)을 사용하는 것이 좋지만, 자외선에 대한 반사율이 높은 물질 중에는 반도체 발광소자 칩의 전극과 솔더링 또는 유테틱 본딩과 같은 방법으로 접합할 때 접합력이 떨어지는 문제가 있었다. 반대로 반도체 발광소자 칩의 전극과 솔더링 또는 유테틱 본딩과 같은 방법으로 접합할 때 접합력이 좋은 물질 중에는 자외선에 대한 반사율이 낮은 문제가 있었다. 출원인은 자외선에 대한 반사율이 떨어지지만 반도체 발광소자 칩의 전극과 솔더링 또는 유테틱 본딩과 같은 방법으로 접합할 때 접합력이 좋은 물질을 사용해도 자외선에 대한 반사율이 높은 물질을 사용한 것과 유사한 광 추출 효율을 얻을 수 있는 방법으로 봉지재 하면의 지름 크기를 작게하는 것을 발견하였다. 더 나아가 봉지재 하면의 지름 크기를 조절하기 위해 방지층 구조를 추가하였다. 더 나아가 봉지재 하면의 지름 크기를 조절하여 원하는 형상의 렌즈를 얻기 위해서 열가소성 수지를 사용할 때, 열가소성 수지 중 자외선에 대한 열화가 잘 일어나지 않는 열가소성 수지는 봉지재 형성시 부피 변화가 커서 바람직하지 않았는데 예비봉지재를 사용하여 부피 변화가 크지만 자외선에 대한 열화가 잘 일어나지 않는 열가소성 수지를 사용할 수 있도록 하였다. In the present disclosure, in a semiconductor light emitting device that emits ultraviolet light having a short wavelength, it is preferable to use a material (eg, Al) having a high reflectance with respect to the ultraviolet ray in terms of reflection on the reflection surface positioned inside the encapsulant and reflecting the ultraviolet ray. Among the materials having high reflectance to ultraviolet rays, there is a problem that the bonding strength is poor when bonding the electrode of the semiconductor light emitting device chip by a method such as soldering or eutectic bonding. On the contrary, when the electrode is bonded to the semiconductor light emitting device chip by a method such as soldering or eutectic bonding, there is a problem in that a material having a good bonding strength has a low reflectance against ultraviolet rays. Applicants have similar light extraction efficiencies to those using high-reflectance materials for UV light, even though materials with good bonding strength are used when bonding the electrodes of semiconductor light emitting chips with soldering or eutectic bonding. It was found that the diameter size of the lower surface of the encapsulant was reduced in such a way that it could be obtained. Furthermore, a barrier layer structure was added to adjust the diameter of the bottom surface of the encapsulant. Furthermore, when the thermoplastic resin is used to obtain a lens having a desired shape by adjusting the diameter of the lower surface of the encapsulant, the thermoplastic resin, which does not easily deteriorate to ultraviolet rays, of the thermoplastic resin is not preferable due to the large volume change in forming the encapsulant. The encapsulant was used to allow the use of a thermoplastic resin having a large volume change but little degradation to ultraviolet rays.

반도체 발광소자 : 1, 8, 9, 700

반도체 발광소자 칩 : 10, 10a, 20, 62, 70, 750

봉지재 : 12, 22, 72, 770

외부 기판 : 14, 24, 74

방지층 : 145, 243, 745

반사층 : 144, 244, 744, 844Semiconductor light emitting device: 1, 8, 9, 700

Semiconductor light emitting chip: 10, 10a, 20, 62, 70, 750

Encapsulant: 12, 22, 72, 770

Outer substrate: 14, 24, 74

Protective layer: 145, 243, 745

Reflective layer: 144, 244, 744, 844

Claims (10)

전자와 정공의 재결합에 의해 자외선을 생성하는 활성층을 포함하는 복수의 반도체층과, 복수의 반도체층에 전기적으로 연결된 전극을 구비하는 반도체 발광소자 칩;

반도체 발광소자 칩을 감싸도록 형성되는 봉지재; 그리고,

베이스, 반도체 발광소자 칩의 전극과 전기적으로 연결되는 도전층을 구비하는 외부 기판;을 포함하며,

봉지내 내부에 위치하며 자외선을 반사하는 도전층의 일면이 자외선 반사율이 90% 미만인 물질로 형성되며,

봉지재의 하면 지름은 △Po 값이 봉지내 내부에 위치하며 자외선을 반사하는 도전층의 일면이 자외선 반사율이 90% 이상인 물질로 형성된 때의 △Po 값과 비교했을 때 △Po 값의 차이가 5% 이내가 되는 지름보다 작은 반도체 발광소자.In a semiconductor light emitting device,

A semiconductor light emitting device chip comprising a plurality of semiconductor layers including an active layer for generating ultraviolet rays by recombination of electrons and holes, and electrodes electrically connected to the plurality of semiconductor layers;

An encapsulant formed to surround the semiconductor light emitting device chip; And,

And an outer substrate including a base and a conductive layer electrically connected to electrodes of the semiconductor light emitting device chip.

One surface of the conductive layer that is located inside the bag and reflects ultraviolet rays is formed of a material having a UV reflectance of less than 90%.

The lower surface diameter of the encapsulant is 5% different from the ΔPo value when the ΔPo value is located inside the bag and the ΔPo value when one surface of the conductive layer that reflects ultraviolet rays is formed of a material having an ultraviolet reflectance of 90% or more. The semiconductor light emitting element smaller than the diameter to become within.

봉지내 내부에 위치하며 자외선을 반사하는 도전층의 일면이 자외선 반사율이 40% 이하인 물질로 형성된 반도체 발광소자.The method of claim 1,

A semiconductor light emitting device, wherein the light emitting device is formed of a material having an ultraviolet reflectance of 40% or less on one surface of a conductive layer that reflects ultraviolet rays.

봉지내 내부에 위치하며 자외선을 반사하는 도전층의 일면이 Au로 형성된 반도체 발광소자.The method of claim 2,

A semiconductor light emitting device, which is formed inside an encapsulation layer and has one surface of a conductive layer that reflects ultraviolet rays.

반도체 발광소자 칩이 UV-C를 발광하는 반도체 발광소자.The method of claim 1,

A semiconductor light emitting device in which a semiconductor light emitting device chip emits UV-C.

외부 기판은 도전층과 일정거리 떨어져서 폐회로 형태로 형성된 방지층을 포함하며,

봉지재의 하면이 방지층의 상면과 접하는 반도체 발광소자.The method of claim 1,

The outer substrate includes a prevention layer formed in a closed circuit at a predetermined distance away from the conductive layer,

A semiconductor light emitting element in which the lower surface of the encapsulant contacts the upper surface of the prevention layer.

봉지내 내부에 위치하며 자외선을 반사하는 방지층의 일면이 자외선 반사율이 40% 이하인 물질로 형성된 반도체 발광소자.The method of claim 5,

A semiconductor light emitting device, which is disposed inside a bag and is formed of a material having an ultraviolet reflectance of 40% or less on one surface of the anti-reflective layer.

봉지내 내부에 위치하며 자외선을 반사하는 도전층 일면 및 방지층 일면이 동일한 금속으로 형성되는 반도체 발광소자.The method of claim 6,

A semiconductor light emitting device, which is disposed inside the encapsulation and has one surface of a conductive layer that reflects ultraviolet rays and one surface of a prevention layer formed of the same metal.

봉지재는 자외선에 대한 투과율이 80% 이상인 열가소성 수지로 형성된 반도체 발광소자.The method of claim 1,

The encapsulant is a semiconductor light emitting device formed of a thermoplastic resin having a transmittance of 80% or more against ultraviolet rays.

열가소성 수지는 액상에서 고형화되는 열경화 공정에서 부피가 90% 이상 줄어드는 반도체 발광소자.The method of claim 8,

Thermoplastic resin is a semiconductor light emitting device that the volume is reduced by more than 90% in the thermosetting process is solidified in the liquid phase.

봉지재의 하면과 접하는 외부 기판의 평면적이 봉지재의 하면과 접하지 않는 외부 기판의 평면적보다 작은 반도체 발광소자.The method of claim 1,

A semiconductor light emitting element in which the plane of the outer substrate in contact with the lower surface of the encapsulation material is smaller than the plane of the outer substrate not in contact with the lower surface of the encapsulant.

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020180050568A KR102111642B1 (en) | 2018-05-02 | 2018-05-02 | Semiconductor light emitting device |

| CN201910140687.1A CN110197864B (en) | 2018-02-26 | 2019-02-26 | Semiconductor light emitting device and method of manufacturing the same |

| CN201910140688.6A CN110197867A (en) | 2018-02-26 | 2019-02-26 | Light emitting semiconductor device and its manufacturing method |

| US16/285,471 US20190267526A1 (en) | 2018-02-26 | 2019-02-26 | Semiconductor Light Emitting Devices And Method Of Manufacturing The Same |

| US16/285,446 US20190267525A1 (en) | 2018-02-26 | 2019-02-26 | Semiconductor Light Emitting Devices And Method Of Manufacturing The Same |

| US17/870,475 US11824148B2 (en) | 2018-02-26 | 2022-07-21 | Semiconductor light emitting devices and method of manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020180050568A KR102111642B1 (en) | 2018-05-02 | 2018-05-02 | Semiconductor light emitting device |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20190126546A true KR20190126546A (en) | 2019-11-12 |

| KR102111642B1 KR102111642B1 (en) | 2020-05-15 |

Family

ID=68577563

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020180050568A KR102111642B1 (en) | 2018-02-26 | 2018-05-02 | Semiconductor light emitting device |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR102111642B1 (en) |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20050116373A (en) * | 2003-03-10 | 2005-12-12 | 도요다 고세이 가부시키가이샤 | Solid element device and method for manufacture thereof |

| JP2008071955A (en) * | 2006-09-14 | 2008-03-27 | Nichia Chem Ind Ltd | Light-emitting device |

| KR20140102563A (en) * | 2013-02-14 | 2014-08-22 | 삼성전자주식회사 | Light-emitting device packages |

| KR20150133779A (en) * | 2013-03-15 | 2015-11-30 | 다우 코닝 코포레이션 | A method for making an optical assembly comprising depositing a solid silicone-containing hot melt composition in powder form and forming an encapsulant thereof |

| KR20160146367A (en) * | 2015-06-12 | 2016-12-21 | 서울바이오시스 주식회사 | Light emitting device comprising uv light emitting diode |

-

2018

- 2018-05-02 KR KR1020180050568A patent/KR102111642B1/en active IP Right Grant

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20050116373A (en) * | 2003-03-10 | 2005-12-12 | 도요다 고세이 가부시키가이샤 | Solid element device and method for manufacture thereof |

| JP2008071955A (en) * | 2006-09-14 | 2008-03-27 | Nichia Chem Ind Ltd | Light-emitting device |

| KR20140102563A (en) * | 2013-02-14 | 2014-08-22 | 삼성전자주식회사 | Light-emitting device packages |

| KR20150133779A (en) * | 2013-03-15 | 2015-11-30 | 다우 코닝 코포레이션 | A method for making an optical assembly comprising depositing a solid silicone-containing hot melt composition in powder form and forming an encapsulant thereof |

| KR20160146367A (en) * | 2015-06-12 | 2016-12-21 | 서울바이오시스 주식회사 | Light emitting device comprising uv light emitting diode |

Also Published As

| Publication number | Publication date |

|---|---|

| KR102111642B1 (en) | 2020-05-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11824148B2 (en) | Semiconductor light emitting devices and method of manufacturing the same | |

| JP5526232B2 (en) | Light emitting diode with molded reflective sidewall coating | |

| US9601670B2 (en) | Method to form primary optic with variable shapes and/or geometries without a substrate | |

| US8310023B2 (en) | Light emitting diode package and fabrication method thereof | |

| KR20170036113A (en) | Led with remote phosphor layer and reflective submount | |

| US8487328B2 (en) | Light emitting device | |

| US11329203B2 (en) | Light emitting device including covering member and optical member | |

| US9548434B2 (en) | Wafer level packaging of electronic device | |

| TW202005124A (en) | Light-emitting device and method for manufacturing the same | |

| KR101960432B1 (en) | Semiconductor light emitting device | |

| KR102064540B1 (en) | Semiconductor light emitting device | |

| KR102022463B1 (en) | Semiconductor light emitting device and method of manufacturing the same | |

| CN104966777A (en) | Semiconductor light-emitting device and method of manufacturing the same | |

| KR102121409B1 (en) | Semiconductor light emitting device | |

| KR102111642B1 (en) | Semiconductor light emitting device | |

| KR102051478B1 (en) | Semiconductor light emitting device and method of manufacturing the same | |

| KR102022460B1 (en) | Semiconductor light emitting device and method of manufacturing the same | |

| KR102017730B1 (en) | Method of manufacturing preformed sealant for semiconductor light emitting device | |

| KR102089496B1 (en) | Semiconductor light emitting structure and method ofmanufacturing the same | |

| KR20120012677A (en) | Light emitting device package and fabricating method thereof | |

| JP7252820B2 (en) | Semiconductor light emitting device and manufacturing method thereof | |

| KR101946239B1 (en) | Semiconductor light emitting structure and method ofmanufacturing the same | |

| KR101997806B1 (en) | Semiconductor light emitting device and method of manufacturing the same | |

| US20210265545A1 (en) | Optoelectronic Component and Method for Producing an Optoelectronic Component | |

| JP2017076701A (en) | Optical semiconductor device, lead frame with resin, and production method of phosphor layer |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant |