KR102666831B1 - 표시 장치 - Google Patents

표시 장치 Download PDFInfo

- Publication number

- KR102666831B1 KR102666831B1 KR1020160064127A KR20160064127A KR102666831B1 KR 102666831 B1 KR102666831 B1 KR 102666831B1 KR 1020160064127 A KR1020160064127 A KR 1020160064127A KR 20160064127 A KR20160064127 A KR 20160064127A KR 102666831 B1 KR102666831 B1 KR 102666831B1

- Authority

- KR

- South Korea

- Prior art keywords

- line

- scan

- pixel

- area

- peripheral area

- Prior art date

Links

- 239000000758 substrate Substances 0.000 claims abstract description 78

- 230000002093 peripheral effect Effects 0.000 claims description 165

- 239000010410 layer Substances 0.000 claims description 139

- 239000011229 interlayer Substances 0.000 claims description 71

- 239000000463 material Substances 0.000 claims description 22

- 230000003071 parasitic effect Effects 0.000 description 62

- 239000003990 capacitor Substances 0.000 description 51

- 239000010408 film Substances 0.000 description 43

- 239000012535 impurity Substances 0.000 description 30

- 239000004065 semiconductor Substances 0.000 description 24

- 238000000034 method Methods 0.000 description 16

- 101150026261 ACT7 gene Proteins 0.000 description 11

- 230000000149 penetrating effect Effects 0.000 description 11

- 238000010586 diagram Methods 0.000 description 8

- 230000001360 synchronised effect Effects 0.000 description 7

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 6

- 238000005538 encapsulation Methods 0.000 description 6

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 6

- 101000577105 Homo sapiens Mannosyl-oligosaccharide glucosidase Proteins 0.000 description 4

- 102100025315 Mannosyl-oligosaccharide glucosidase Human genes 0.000 description 4

- 239000004642 Polyimide Substances 0.000 description 4

- 239000011651 chromium Substances 0.000 description 4

- 238000002347 injection Methods 0.000 description 4

- 239000007924 injection Substances 0.000 description 4

- 229920001721 polyimide Polymers 0.000 description 4

- 239000011241 protective layer Substances 0.000 description 4

- 229920008347 Cellulose acetate propionate Polymers 0.000 description 3

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 230000005525 hole transport Effects 0.000 description 3

- 229920003229 poly(methyl methacrylate) Polymers 0.000 description 3

- 239000004926 polymethyl methacrylate Substances 0.000 description 3

- 229920005989 resin Polymers 0.000 description 3

- 239000011347 resin Substances 0.000 description 3

- 229910001887 tin oxide Inorganic materials 0.000 description 3

- 101100014264 Arabidopsis thaliana GCS2 gene Proteins 0.000 description 2

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 2

- 229920002430 Fibre-reinforced plastic Polymers 0.000 description 2

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 2

- 239000004952 Polyamide Substances 0.000 description 2

- 239000004697 Polyetherimide Substances 0.000 description 2

- 239000004793 Polystyrene Substances 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 230000000903 blocking effect Effects 0.000 description 2

- 239000011575 calcium Substances 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- JAONJTDQXUSBGG-UHFFFAOYSA-N dialuminum;dizinc;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Al+3].[Al+3].[Zn+2].[Zn+2] JAONJTDQXUSBGG-UHFFFAOYSA-N 0.000 description 2

- 239000011151 fibre-reinforced plastic Substances 0.000 description 2

- 230000014509 gene expression Effects 0.000 description 2

- 239000010931 gold Substances 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 239000011777 magnesium Substances 0.000 description 2

- 239000012528 membrane Substances 0.000 description 2

- 229910052750 molybdenum Inorganic materials 0.000 description 2

- 239000011733 molybdenum Substances 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 229910052697 platinum Inorganic materials 0.000 description 2

- 229920000090 poly(aryl ether) Polymers 0.000 description 2

- 229920002239 polyacrylonitrile Polymers 0.000 description 2

- 229920002647 polyamide Polymers 0.000 description 2

- 229920001601 polyetherimide Polymers 0.000 description 2

- -1 polyethylene naphthalate Polymers 0.000 description 2

- 229920002223 polystyrene Polymers 0.000 description 2

- 230000006798 recombination Effects 0.000 description 2

- 238000005215 recombination Methods 0.000 description 2

- 238000005070 sampling Methods 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 2

- OYPRJOBELJOOCE-UHFFFAOYSA-N Calcium Chemical compound [Ca] OYPRJOBELJOOCE-UHFFFAOYSA-N 0.000 description 1

- 229920002284 Cellulose triacetate Polymers 0.000 description 1

- 239000004593 Epoxy Substances 0.000 description 1

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- 229910052779 Neodymium Inorganic materials 0.000 description 1

- 239000004695 Polyether sulfone Substances 0.000 description 1

- 239000004734 Polyphenylene sulfide Substances 0.000 description 1

- 239000004372 Polyvinyl alcohol Substances 0.000 description 1

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 229910052791 calcium Inorganic materials 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 230000000994 depressogenic effect Effects 0.000 description 1

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 1

- 238000000605 extraction Methods 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- YZZNJYQZJKSEER-UHFFFAOYSA-N gallium tin Chemical compound [Ga].[Sn] YZZNJYQZJKSEER-UHFFFAOYSA-N 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 125000000623 heterocyclic group Chemical group 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 229910052749 magnesium Inorganic materials 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 1

- 239000012044 organic layer Substances 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- KYKLWYKWCAYAJY-UHFFFAOYSA-N oxotin;zinc Chemical compound [Zn].[Sn]=O KYKLWYKWCAYAJY-UHFFFAOYSA-N 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 238000005192 partition Methods 0.000 description 1

- 229920003207 poly(ethylene-2,6-naphthalate) Polymers 0.000 description 1

- 229920000052 poly(p-xylylene) Polymers 0.000 description 1

- 229920000058 polyacrylate Polymers 0.000 description 1

- 229920001230 polyarylate Polymers 0.000 description 1

- 229920000515 polycarbonate Polymers 0.000 description 1

- 239000004417 polycarbonate Substances 0.000 description 1

- 229920006393 polyether sulfone Polymers 0.000 description 1

- 239000011112 polyethylene naphthalate Substances 0.000 description 1

- 229920000139 polyethylene terephthalate Polymers 0.000 description 1

- 239000005020 polyethylene terephthalate Substances 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 229920000069 polyphenylene sulfide Polymers 0.000 description 1

- 229920002451 polyvinyl alcohol Polymers 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 230000001629 suppression Effects 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 1

- ILJSQTXMGCGYMG-UHFFFAOYSA-N triacetic acid Chemical compound CC(=O)CC(=O)CC(O)=O ILJSQTXMGCGYMG-UHFFFAOYSA-N 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 1

- 239000011787 zinc oxide Substances 0.000 description 1

- 229910001928 zirconium oxide Inorganic materials 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2092—Details of a display terminals using a flat panel, the details relating to the control arrangement of the display terminal and to the interfaces thereto

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

- G02F1/13452—Conductors connecting driver circuitry and terminals of panels

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/131—Interconnections, e.g. wiring lines or terminals

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3266—Details of drivers for scan electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/3406—Control of illumination source

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/121—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements

- H10K59/1213—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements the pixel elements being TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/121—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements

- H10K59/1216—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements the pixel elements being capacitors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/123—Connection of the pixel electrodes to the thin film transistors [TFT]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/30—Devices specially adapted for multicolour light emission

- H10K59/35—Devices specially adapted for multicolour light emission comprising red-green-blue [RGB] subpixels

- H10K59/352—Devices specially adapted for multicolour light emission comprising red-green-blue [RGB] subpixels the areas of the RGB subpixels being different

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/80—Constructional details

- H10K59/88—Dummy elements, i.e. elements having non-functional features

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/133388—Constructional arrangements; Manufacturing methods with constructional differences between the display region and the peripheral region

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

- G02F1/13454—Drivers integrated on the active matrix substrate

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F2201/00—Constructional arrangements not provided for in groups G02F1/00 - G02F7/00

- G02F2201/12—Constructional arrangements not provided for in groups G02F1/00 - G02F7/00 electrode

- G02F2201/123—Constructional arrangements not provided for in groups G02F1/00 - G02F7/00 electrode pixel

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/02—Composition of display devices

- G09G2300/023—Display panel composed of stacked panels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0404—Matrix technologies

- G09G2300/0408—Integration of the drivers onto the display substrate

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0404—Matrix technologies

- G09G2300/0413—Details of dummy pixels or dummy lines in flat panels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0421—Structural details of the set of electrodes

- G09G2300/0426—Layout of electrodes and connections

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0814—Several active elements per pixel in active matrix panels used for selection purposes, e.g. logical AND for partial update

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0819—Several active elements per pixel in active matrix panels used for counteracting undesired variations, e.g. feedback or autozeroing

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0861—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0202—Addressing of scan or signal lines

- G09G2310/0221—Addressing of scan or signal lines with use of split matrices

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0243—Details of the generation of driving signals

- G09G2310/0251—Precharge or discharge of pixel before applying new pixel voltage

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0262—The addressing of the pixel, in a display other than an active matrix LCD, involving the control of two or more scan electrodes or two or more data electrodes, e.g. pixel voltage dependent on signals of two data electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0281—Arrangement of scan or data electrode driver circuits at the periphery of a panel not inherent to a split matrix structure

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0223—Compensation for problems related to R-C delay and attenuation in electrodes of matrix panels, e.g. in gate electrodes or on-substrate video signal electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0233—Improving the luminance or brightness uniformity across the screen

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/04—Display protection

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Computer Hardware Design (AREA)

- Theoretical Computer Science (AREA)

- Mathematical Physics (AREA)

- Crystallography & Structural Chemistry (AREA)

- Chemical & Material Sciences (AREA)

- Optics & Photonics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Geometry (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Electroluminescent Light Sources (AREA)

Abstract

표시 장치는 제1 화소 영역과, 서로 이격되고 상기 제1 화소 영역보다 작은 면적을 가지며 상기 제1 화소 영역에 연결된 제2 화소 영역 및 제3 화소 영역을 포함하는 기판; 상기 제1 내지 제3 화소 영역들에 각각 제공된 제1 내지 제3 화소들; 상기 제1 내지 제3 화소들에 각각 연결된 제1 내지 제3 라인들; 상기 제2 라인 및 상기 제3 라인을 연결하는 라인 연결부들; 및 상기 라인 연결부와 중첩하며, 상기 제1 라인의 로드 값과 상기 제2 라인 및 상기 제3 라인의 로드 값의 차이를 보상하는 더미부를 포함할 수 있다.

Description

본 발명은 표시 장치에 관한 것으로, 상세하게는 서로 다른 면적을 갖는 영역들을 포함하는 표시 장치에 관한 것이다.

표시 장치는 표시 소자를 포함하는 복수 개의 화소를 포함하며, 각 화소에는 배선들과, 상기 배선들에 연결되며 표시 소자를 구동하기 위한 복수 개의 트랜지스터가 형성되어 있다. 상기 배선들은 길이에 따라 다른 정도의 로드 값을 가질 수 있으며, 상기 표시 장치가 제공하는 최종적인 영상에 있어 상기 로드 값에 차이에 의한 휘도 차이가 발생할 수 있다.

본 발명의 일 목적은 영역과 상관없이 균일한 휘도를 갖는 표시 장치를 제공하는 데에 있다.

본 발명의 일 실시예에 따른 표시 장치는 제1 화소 영역과, 서로 이격되고 상기 제1 화소 영역보다 작은 면적을 가지며 상기 제1 화소 영역에 연결된 제2 화소 영역 및 제3 화소 영역을 포함하는 기판; 상기 제1 내지 제3 화소 영역들에 각각 제공된 제1 내지 제3 화소들; 상기 제1 내지 제3 화소들에 각각 연결된 제1 내지 제3 라인들; 상기 제2 라인 및 상기 제3 라인을 연결하는 라인 연결부들; 및 상기 라인 연결부와 중첩하며, 상기 제1 라인의 로드 값과 상기 제2 라인 및 상기 제3 라인의 로드 값의 차이를 보상하는 더미부를 포함할 수 있다. 상기 제1 라인은 상기 제2 라인 및 상기 제3 라인보다 긴 길이를 가질 수 있다.

본 발명의 일 실시예에 있어서, 상기 제1 내지 제3 화소들에 데이터 신호를 제공하는 데이터 라인을 더 포함하고, 상기 제1 라인은 상기 제1 화소에 스캔 신호를 제공하는 제1 스캔 라인이고, 상기 제2 라인 및 상기 제3 라인은 상기 제2 화소 및 상기 제3 화소에 스캔 신호를 제공하는 제2 스캔 라인 및 제3 스캔 라인일 수 있다.

본 발명의 일 실시예에 있어서, 상기 기판은 상기 제1 내지 제3 화소 영역을 각각 둘러싸는 제1 내지 제3 주변 영역을 더 포함하고, 상기 더미부는 상기 제2 주변 영역, 상기 제3 주변 영역, 및 상기 제2 주변 영역과 상기 제3 주변 영역을 연결하는 부가 주변 영역 중 적어도 상기 부가 주변 영역에 제공될 수 있다.

본 발명의 일 실시예에 있어서, 상기 제2 화소 및 상기 제3 화소 각각은 상기 제2 스캔 라인 및 상기 제3 스캔 라인과 상기 데이터 라인들 중 대응하는 데이터 라인에 연결된 트랜지스터를 포함할 수 있다. 상기 트랜지스터는 상기 기판 상에 제공된 액티브 패턴; 게이트 절연막을 사이에 두고 상기 액티브 패턴 상에 제공된 상기 게이트 전극; 상기 게이트 전극을 커버하는 제1 층간 절연막, 및 상기 제2 층간 절연막 상에 배치되는 제2 층간 절연막을 포함하는 층간 절연막; 및 상기 층간 절연막 상에 배치되고, 상기 액티브 패턴에 각각 연결된 소스 전극 및 드레인 전극을 포함할 수 있다.

본 발명의 일 실시예에 있어서, 상기 층간 절연막 상에서, 상기 제1 주변 영역, 상기 제2 주변 영역, 상기 제3 주변 영역 및 상기 부가 주변 영역에 배치되며, 상기 라인 연결부들과 중첩하는 전원 공급 라인을 더 포함하며, 상기 라인 연결부는 제1 층간 절연막 및 상기 제2 층간 절연막 사이에 배치될 수 있다.

본 발명의 일 실시예에 있어서, 상기 더미부는 상기 전원 공급 라인과 연결되고, 상기 제1 층간 절연막 및 상기 제2 층간 절연막 사이에 배치되는 보조 전원 패턴을 포함하며, 상기 라인 연결부는 상기 게이트 절연막 및 상기 제1 층간 절연막 사이에 배치될 수 있다.

본 발명의 일 실시예에 있어서, 상기 표시 장치는 상기 제1 주변 영역, 상기 제2 주변 영역, 상기 제3 주변 영역 및 상기 부가 주변 영역에 배치되며, 상기 층간 절연막 상에 배치되고, 상기 라인 연결부들과 중첩하는 전원 공급 라인을 더 포함하고, 상기 더미 패턴은 상기 전원 공급 라인과 동일한 전압을 인가받을 수 있다.

본 발명의 일 실시예에 있어서, 상기 표시 장치는 상기 제1 내지 제3 화소들에 데이터 신호를 제공하는 데이터 라인들, 상기 제1 내지 제3 화소들에 스캔 신호를 제공하는 제1 내지 제3 스캔 라인들을 더 포함할 수 있다. 여기서, 상기 제1 라인은 상기 제1 화소에 발광 제어 신호를 제공하는 제1 발광 제어 신호 라인이고, 상기 제2 라인 및 상기 제3 라인은 상기 제2 화소 및 상기 제3 화소에 발광 제어 신호를 제공하는 제2 발광 제어 라인 및 제3 발광 제어 라인일 수 있다.

본 발명의 일 실시예에 있어서, 상기 제2 화소 영역 및 상기 제3 화소 영역은 복수의 화소들이 배열된 복수의 행들을 포함할 수 있다. 각 라인 연결부는 동일한 행에 배치된 화소들을 연결하는 상기 제2 라인 및 상기 제3 라인을 연결할 수 있다.

본 발명의 일 실시예에 있어서, 상기 라인 연결부들 중 행 내에 배치된 화소의 수가 적은 제2 라인 및 제3 라인을 연결하는 라인 연결부(이하, 제1 라인 연결부라 칭함)의 길이는 행 내에 배치된 화소의 수가 많은 제2 라인 및 제3 라인을 연결하는 라인 연결부(이하 '제2 라인 연결부'라 칭함)의 길이보다 클 수 있다.

본 발명의 일 실시예에 있어서, 상기 제1 라인 연결부 및 상기 더미 패턴의 중첩 면적은 상기 제2 라인 연결부 및 상기 더미 패턴의 중첩 면적보다 클 수 있다.

본 발명의 일 실시예에 있어서, 상기 더미 패턴 및 상기 전원 공급 라인 중 적어도 하나는 상기 라인 연결부와 중첩하고 서로 이격되어 배치되는 복수의 오픈 영역들을 포함할 수 있다.

본 발명의 일 실시예에 있어서, 상기 제1 화소 영역의 중심선을 기준으로, 상기 제2 화소 영역 및 상기 제2 주변 영역은 상기 제3 화소 영역 및 상기 제3 주변 영역은 선대칭되는 형상을 가질 수 있다.

상술한 바와 같은 표시 장치는 서로 다른 면적을 갖는 2개 이상의 영역을 가지며, 각 영역에서의 휘도가 균일할 수 있다.

도 1a 및 도 1b는 본 발명의 일 실시예에 따른 표시 장치를 나타낸 평면도들이다.

도 2는 도 1a의 제2 화소 영역의 확대도이다.

도 3 및 도 4는 본 발명의 일 실시예에 따른 화소들 및 구동부의 실시예를 나타낸 블록도이다.

도 5는 본 발명의 다른 실시예에 따른 화소들 및 구동부를 나타내는 블록도이다.

도 6은 본 발명의 또 다른 실시예에 따른 화소들 및 구동부를 나타내는 블록도이다.

도 7은 도 3에 도시된 제1 화소의 실시예를 나타내는 도면이다.

도 8은 도 3의 제1 화소를 상세하게 도시한 평면도이다.

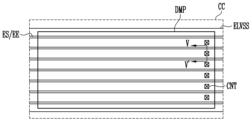

도 9는 도 8의 I-I'선에 따른 단면도이다.

도 10은 도 8의 II-II'선에 따른 단면도이다.

도 11 및 도 12는 본 발명의 일 실시예에 따른 제2 영역, 제3 영역 및 부가 주변 영역을 도시한 평면도들이다.

도 13은 도 12의 AA 영역의 확대도이다.

도 14는 도 13의 III-III' 라인에 따른 단면도이다.

도 15는 본 발명의 일 실시예에 따른 제2 영역, 제3 영역 및 부가 주변 영역을 도시한 평면도이다.

도 16은 도 15의 BB 영역의 확대도이다.

도 17은 도 16의 IV-IV' 라인에 따른 단면도이다.

도 18은 본 발명의 일 실시예에 따른 제2 영역, 제3 영역 및 부가 주변 영역을 도시한 평면도이다.

도 19는 도 18의 CC 영역의 확대도이다.

도 20 내지 도 22는 도 19의 V-V' 라인에 따른 단면도들이다.

도 23은 본 발명의 일 실시예에 따른 제2 영역, 제3 영역 및 부가 주변 영역을 도시한 평면도이다.

도 24는 본 발명의 일 실시예에 따른 제2 영역, 제3 영역 및 부가 주변 영역을 도시한 평면도이다.

도 25는 본 발명의 일 실시예에 따른 더미부가 배치되는 영역을 도시한 평면도이다.

도 26 및 도 27은 도 25의 VI-VI' 라인에 따른 단면도들이다.

도 2는 도 1a의 제2 화소 영역의 확대도이다.

도 3 및 도 4는 본 발명의 일 실시예에 따른 화소들 및 구동부의 실시예를 나타낸 블록도이다.

도 5는 본 발명의 다른 실시예에 따른 화소들 및 구동부를 나타내는 블록도이다.

도 6은 본 발명의 또 다른 실시예에 따른 화소들 및 구동부를 나타내는 블록도이다.

도 7은 도 3에 도시된 제1 화소의 실시예를 나타내는 도면이다.

도 8은 도 3의 제1 화소를 상세하게 도시한 평면도이다.

도 9는 도 8의 I-I'선에 따른 단면도이다.

도 10은 도 8의 II-II'선에 따른 단면도이다.

도 11 및 도 12는 본 발명의 일 실시예에 따른 제2 영역, 제3 영역 및 부가 주변 영역을 도시한 평면도들이다.

도 13은 도 12의 AA 영역의 확대도이다.

도 14는 도 13의 III-III' 라인에 따른 단면도이다.

도 15는 본 발명의 일 실시예에 따른 제2 영역, 제3 영역 및 부가 주변 영역을 도시한 평면도이다.

도 16은 도 15의 BB 영역의 확대도이다.

도 17은 도 16의 IV-IV' 라인에 따른 단면도이다.

도 18은 본 발명의 일 실시예에 따른 제2 영역, 제3 영역 및 부가 주변 영역을 도시한 평면도이다.

도 19는 도 18의 CC 영역의 확대도이다.

도 20 내지 도 22는 도 19의 V-V' 라인에 따른 단면도들이다.

도 23은 본 발명의 일 실시예에 따른 제2 영역, 제3 영역 및 부가 주변 영역을 도시한 평면도이다.

도 24는 본 발명의 일 실시예에 따른 제2 영역, 제3 영역 및 부가 주변 영역을 도시한 평면도이다.

도 25는 본 발명의 일 실시예에 따른 더미부가 배치되는 영역을 도시한 평면도이다.

도 26 및 도 27은 도 25의 VI-VI' 라인에 따른 단면도들이다.

본 발명은 다양한 변경을 가할 수 있고 여러 가지 형태를 가질 수 있는 바, 특정 실시예들을 도면에 예시하고 본문에 상세하게 설명하고자 한다. 그러나, 이는 본 발명을 특정한 개시 형태에 대해 한정하려는 것이 아니며, 본 발명의 사상 및 기술 범위에 포함되는 모든 변경, 균등물 내지 대체물을 포함하는 것으로 이해되어야 한다.

각 도면을 설명하면서 유사한 참조부호를 유사한 구성요소에 대해 사용하였다. 첨부된 도면에 있어서, 구조물들의 치수는 본 발명의 명확성을 위하여 실제보다 확대하여 도시한 것이다. 제1, 제2 등의 용어는 다양한 구성요소들을 설명하는데 사용될 수 있지만, 상기 구성요소들은 상기 용어들에 의해 한정되어서는 안 된다. 상기 용어들은 하나의 구성요소를 다른 구성요소로부터 구별하는 목적으로만 사용된다. 예를 들어, 본 발명의 권리 범위를 벗어나지 않으면서 제1 구성요소는 제2 구성요소로 명명될 수 있고, 유사하게 제2 구성요소도 제1 구성요소로 명명될 수 있다. 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 복수의 표현을 포함한다.

본 출원에서, "포함하다" 또는 "가지다" 등의 용어는 명세서 상에 기재된 특징, 숫자, 단계, 동작, 구성요소, 부품 또는 이들을 조합한 것이 존재함을 지정하려는 것이지, 하나 또는 그 이상의 다른 특징들이나 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것들의 존재 또는 부가 가능성을 미리 배제하지 않는 것으로 이해되어야 한다. 또한, 층, 막, 영역, 판 등의 부분이 다른 부분 "상에" 있다고 할 경우, 이는 다른 부분 "바로 위에" 있는 경우뿐만 아니라 그 중간에 또 다른 부분이 있는 경우도 포함한다. 또한, 본 명세서에 있어서, 어느 층, 막, 영역, 판 등의 부분이 다른 부분 상(on)에 형성되었다고 할 경우, 상기 형성된 방향은 상부 방향만 한정되지 않으며 측면이나 하부 방향으로 형성된 것을 포함한다. 반대로 층, 막, 영역, 판 등의 부분이 다른 부분 "아래에" 있다고 할 경우, 이는 다른 부분 "바로 아래에" 있는 경우뿐만 아니라 그 중간에 또 다른 부분이 있는 경우도 포함한다.

이하, 첨부한 도면들을 참조하여 본 발명의 바람직한 실시예를 보다 상세하게 설명하고자 한다.

도 1a 및 도 1b는 본 발명의 실시예들에 따른 표시 장치를 나타낸 평면도들이며, 도 2는 도 1a의 제2 화소 영역의 확대도이다.

도 1a, 도 1b 및 도 2를 참조하면 본 발명의 일 실시예에 따른 표시 장치는 기판(SUB), 및 상기 기판(SUB) 상에 제공된 화소들(PXL1, PXL2, PXL3; 이하 PXL), 상기 기판(SUB) 상에 제공되며 상기 화소들(PXL)을 구동하는 구동부, 상기 화소들에 전원을 공급하는 전원 공급부 및 상기 화소들(PXL)과 상기 구동부를 연결하는 배선부를 포함할 수 있다.

상기 기판(SUB)은 복수 개의 영역들을 포함하며, 상기 영역들 중 적어도 2개는 서로 다른 면적을 갖가질 수 있다. 일 예에 있어서, 상기 기판(SUB)은 두 개의 영역을 가질 수 있으며, 상기 두 영역은 서로 다른 면적을 가질 수 있다. 또한, 일 예에 있어서, 상기 기판(SUB)은 세 개의 영역을 가질 수 있다. 이 경우, 세 영역 모두가 서로 다른 면적을 가지거나, 세 영역 중 두 개의 영역만 서로 다른 면적을 가질 수 있다. 일 예에 있어서, 상기 기판(SUB)은 4개 이상의 영역을 가질 수도 있다.

이하의 실시예에서는 설명의 편의를 위해 상기 기판(SUB)이 세 개의 영역들, 즉 제1 내지 제3 영역들(A1, A2, A3)을 포함하는 것을 일 예로서 도시하였다.

상기 제1 내지 제3 영역들(A1, A2, A3) 각각은 다양한 형상을 가질 수 있다. 예를 들어, 상기 제1 내지 제3 영역들(A1, A2, A3) 각각은 직선의 변을 포함하는 닫힌 형태의 다각형, 곡선으로 이루어진 변을 포함하는 원, 타원 등, 직선과 곡선으로 이루어진 변을 포함하는 반원, 반타원 등 다양한 형상으로 제공될 수 있다.

본 발명의 일 실시예에 있어서, 제1 내지 제3 영역들(A1, A2, A3)은 각각 대략적으로 사각 형상을 가지며, 사각 형상의 꼭짓점들 중 적어도 하나의 꼭짓점에 인접한 영역이 제거된 형상을 가질 수 있다. 제1 내지 제3 영역들(A1, A2, A3)은 상기 제거된 영역에 대응하는 제1 서브 영역 및 제1 서브 영역 이외의 제2 서브 영역으로 구분될 수 있다. 여기서, 제1 서브 영역의 폭은 제2 서브 영역의 폭보다 클 수 있다.

사각 형상의 꼭짓점들 중 적어도 하나의 꼭짓점에 인접하여 제거된 영역의 형상은 삼각 형상 또는 사각 형상 중 하나일 수 있다. 즉, 도 1a 및 도 1b에 도시된 바와 같이, 제1 내지 제3 영역들(A1, A2, A3)의 제거된 영역에 대응하는 변은 사각 형상의 일 변에 경사진 사선 형상, 또는 꺽인 선분 형상을 가질 수 있다.

상기 제1 내지 제3 영역들(A1, A2, A3)은 각각 화소 영역들(PXA1, PXA2, PXA3; 이하, PXA)과 주변 영역들(PPA1, PPA2, PPA3; 이하 PPA)을 가질 수 있다. 상기 화소 영역들(PXA)은 영상을 표시하는 화소들(PXL)이 제공되는 영역이다. 각 화소(PXL)에 대해서는 후술한다.

본 발명의 일 실시예에 있어서, 각각의 제1 내지 제3 화소 영역들(PXA1, PXA2, PXA3)은 대체적으로 제1 내지 제3 영역들(A1, A2, A3)의 형상에 대응하는 형상을 가질 수 있다.

상기 주변 영역들(PPA)은 상기 화소들(PXL)이 제공되지 않은 영역으로서 영상이 표시되지 않은 영역이다. 상기 주변 영역들(PPA)에는 상기 화소들(PXL)을 구동하기 위한 구동부, 상기 화소들(PXL)에 전원을 인가하는 상기 전원 공급부, 및 상기 화소들(PXL)과 구동부를 연결하는 배선(미도시)의 일부가 제공될 수 있다. 상기 주변 영역들(PPA)은 최종적인 표시 장치에서의 베젤에 대응하며, 상기 주변 영역의 폭에 따라 베젤의 폭이 결정될 수 있다.

상기 제1 내지 제3 영역들(A1, A2, A3)을 각각 설명하면 다음과 같다.

상기 제1 영역(A1)은 상기 제1 내지 제3 영역들(A1, A2, A3) 중 가장 큰 면적을 가질 수 있다. 상기 제1 영역(A1)은 영상이 표시되는 제1 화소 영역(PXA1)과 상기 제1 화소 영역(PXA1)의 적어도 일부를 둘러싸는 제1 주변 영역(PPA1)을 가질 수 있다.

상기 제1 화소 영역(PXA1)은 상기 제1 영역(A1)의 형상에 대응하는 형상으로 제공될 수 있다. 본 발명의 일 실시예에 있어서, 상기 제1 화소 영역(PXA1)은 제1 방향(DR1)으로 제1 폭(W1)을 가지고, 상기 제1 방향(DR1)과 교차하는 제2 방향(DR2)으로 제1 길이(L1)를 가질 수 있다.

상기 제1 주변 영역(PPA1)은 상기 제1 화소 영역(PXA1)의 적어도 일측에 제공될 수 있다. 본 발명의 일 실시예에 있어서, 상기 제1 주변 영역(PPA1)은 상기 제1 화소 영역(PXA1)의 둘레를 둘러싸되, 후술할 상기 제2 영역(A2)과 상기 제3 영역(A3)이 배치된 부분을 제외한 곳에 제공될 수 있다. 본 발명의 일 실시예에 있어서, 상기 제1 주변 영역(PPA1)은 폭 방향으로 연장된 가로부와, 길이 방향으로 연장된 세로부를 포함할 수 있다. 상기 제1 주변 영역(PPA1)의 세로부는 상기 제1 화소 영역(PXA1)의 폭 방향을 따라 서로 이격된 한 쌍으로 제공될 수 있다.

상기 제2 영역(A2)은 상기 제1 영역(A1)보다 작은 면적을 가질 수 있다. 상기 제2 영역(A2)은 영상이 표시되는 제2 화소 영역(PXA2)과 상기 제2 화소 영역(PXA2)의 적어도 일부를 둘러싸는 제2 주변 영역(PPA2)을 가질 수 있다.

상기 제2 화소 영역(PXA2)은 상기 제2 영역(A2)의 형상에 대응하는 형상으로 제공될 수 있다. 본 발명의 일 실시예에 있어서, 상기 제2 화소 영역(PXA2)은 상기 제1 영역(A1)의 제1 폭(W1)보다 작은 제2 폭(W2)을 가질 수 있다. 상기 제2 화소 영역(PXA2)은 상기 제1 영역(A1)의 제1 길이(L1)보다 작은 제2 길이(L2)를 가질 수 있다. 상기 제2 화소 영역(PXA2)은 상기 제1 화소 영역(PXA1)으로부터 돌출된 형태로 제공되며, 상기 제1 화소 영역(PXA1)과 바로 연결될 수 있다. 다시 말해, 상기 제2 화소 영역(PXA2)에 있어서, 상기 제1 화소 영역(PXA1)과 가장 근접한 가장자리 부분은 상기 제1 화소 영역(PXA1)의 가장자리와 일치할 수 있다.

상기 제2 주변 영역(PPA2)은 상기 제2 화소 영역(PXA2)의 적어도 일측에 제공될 수 있다. 본 발명의 일 실시예에 있어서, 상기 제2 주변 영역(PPA2)은 상기 제2 화소 영역(PXA2)을 둘러싸되, 상기 제1 화소 영역(PXA1)과 상기 제2 화소 영역(PXA2)이 연결되는 부분에는 제공되지 않을 수 있다. 본 발명의 일 실시예에 있어서, 상기 제2 주변 영역(PPA2) 또한 폭 방향으로 연장된 가로부와, 길이 방향으로 연장된 세로부를 포함할 수 있다. 상기 제2 주변 영역(PPA2)의 세로부는 상기 제2 화소 영역(PXA2)의 폭 방향을 따라 서로 이격된 한 쌍으로 제공될 수 있다.

상기 제3 영역(A3)은 상기 제1 영역(A1)보다 작은 면적을 가질 수 있다. 상기 제3 영역(A3)은 상기 제2 영역(A2)과 동일한 면적을 가질 수 있다. 상기 제3 영역(A3)은 영상이 표시되는 제3 화소 영역(PXA3)과 상기 제3 화소 영역(PXA3)의 적어도 일부를 둘러싸는 제3 주변 영역(PPA3)을 가질 수 있다.

상기 제3 화소 영역(PXA3)은 상기 제3 영역(A3)의 형상에 대응하는 형상으로 제공될 수 있다. 본 발명의 일 실시예에 있어서, 상기 제3 화소 영역(PXA3)은 상기 제1 영역(A1)의 제1 폭(W1)보다 작은 제3 폭(W3)을 가질 수 있다. 상기 제3 화소 영역(PXA3)은 상기 제1 영역(A1)의 제1 길이(L1)보다 작은 제3 길이(L3)를 가질 수 있다. 상기 제2 폭(W2)과 상기 제3 폭(W3)은 서로 동일할 수 있다. 또한, 상기 제2 길이(L2)와 상기 제3 길이(L3)는 서로 동일할 수 있다.

상기 제3 화소 영역(PXA3)은 상기 제1 화소 영역(PXA1)으로부터 돌출된 형태로 제공되며, 상기 제1 화소 영역(PXA1)과 바로 연결될 수 있다. 다시 말해, 상기 제3 화소 영역(PXA3)에 있어서, 상기 제1 화소 영역(PXA1)과 가장 근접한 가장자리 부분은 상기 제1 화소 영역(PXA1)의 가장자리와 일치할 수 있다.

상기 제3 주변 영역(PPA3)은 상기 제3 화소 영역(PXA3)의 적어도 일측에 제공될 수 있다. 본 발명의 일 실시예에 있어서, 상기 제3 주변 영역(PPA3)은 상기 제3 화소 영역(PXA3)을 둘러싸되, 상기 제1 화소 영역(PXA1)과 상기 제3 화소 영역(PXA3)이 연결되는 부분에는 제공되지 않을 수 있다. 본 발명의 일 실시예에 있어서, 상기 제3 주변 영역(PPA3) 또한 폭 방향으로 연장된 가로부와, 길이 방향으로 연장된 세로부를 포함할 수 있다. 상기 제3 주변 영역(PPA3)의 세로부 또한 상기 제1 화소 영역(PXA1)의 폭 방향을 따라 서로 이격된 한 쌍으로 제공될 수 있다.

본 발명의 일 실시예에 있어서, 상기 제1 영역(A1)의 중심선을 기준으로, 상기 제3 영역(A3)은 상기 제2 영역(A2)과 선대칭되는 되는 형상을 가질 수 있으며, 이 경우 상기 제3 영역(A3)에 제공되는 각 구성 요소의 배치 관계는 일부 배선을 제외하고는 실질적으로 제2 영역(A2)에서와 동일할 수 있다.

따라서, 상기 기판(SUB)은 상기 제2 방향(D2)으로 상기 제1 영역(A1)에서 상기 제2 영역(A2) 및 상기 제3 영역(A3)이 돌출된 형상을 가질 수 있다. 또한, 상기 제2 영역(A2) 및 상기 제3 영역(A3)가 이격되어 배치되므로, 상기 기판(SUB)은 상기 제2 영역(A2) 및 상기 제3 영역(A3) 사이가 함몰된 형상을 가질 수 있다. 즉, 상기 기판(SUB)은 상기 제2 영역(A2) 및 상기 제3 영역(A3) 사이에 노치(notch)를 구비할 수 있다.

본 발명의 일 실시예에 있어서, 상기 제1 주변 영역(PPA1)의 세로부들은 각각 상기 제2 주변 영역(PPA2) 및 상기 제3 주변 영역(PPA3)의 세로부들 중 일부와 연결될 수 있다. 예를 들면, 상기 제1 주변 영역(PPA1)의 좌측 세로부 및 상기 제2 주변 영역(PPA2)의 좌측 세로부는 연결될 수 있다. 상기 제1 주변 영역(PPA1)의 우측 세로부 및 상기 제3 주변 영역(PPA3)의 우측 세로부는 연결될 수 있다. 또한, 상기 제1 주변 영역(PPA1)의 좌측 세로부 및 상기 제2 주변 영역(PPA2)의 좌측 세로부의 폭(W4)은 동일할 수 있다. 상기 제1 주변 영역(PPA1)의 우측 세로부 및 상기 제3 주변 영역(PPA3)의 우측 세로부의 폭(W5)은 동일할 수 있다.

상기 제1 주변 영역(PPA1) 및 상기 제2 주변 영역(PPA2)의 좌측 세로부의 폭(W4)은 상기 제1 주변 영역(PPA1) 및 상기 제3 주변 영역(PPA3)의 우측 세로부의 폭(W5)과 상이할 수 있다. 예를 들면, 상기 제1 주변 영역(PPA1) 및 상기 제2 주변 영역(PPA2)의 좌측 세로부의 폭(W4)은 상기 제1 주변 영역(PPA1) 및 상기 제3 주변 영역(PPA3)의 우측 세로부의 폭(W5)보다 작을 수 있다.

본 발명의 일 실시예에 있어서, 상기 제2 주변 영역(PPA2) 및 상기 제3 주변 영역(PPA3)은 부가 주변 영역(APA)을 통하여 연결될 수 있다. 예를 들면, 상기 부가 주변 영역(APA)은 상기 제2 주변 영역(PPA2)의 우측 세로부 및 상기 제3 주변 영역(PPA3)의 좌측 세로부를 연결할 수 있다. 즉, 상기 부가 주변 영역(APA) 상기 제2 영역(A2) 및 상기 제3 영역(A3) 사이의 상기 제1 화소 영역(PXA1)의 변에 제공될 수 있다.

상기 화소들(PXL)은 상기 기판(SUB) 상의 상기 화소 영역들(PXA)에, 즉, 제1 내지 제3 화소 영역들(PXA1, PXA2, PXA3)에 제공될 수 있다. 각 화소(PXL)는 영상을 표시하는 최소 단위로서 복수 개로 제공될 수 있다. 상기 화소들(PXL)은 컬러광을 출사하는 표시 소자를 포함할 수 있다. 예를 들면, 상기 표시 소자는 액정 표시 소자(liquid crystal display device, LCD device), 전기 영동 표시 소자(electrophoretic display device, EPD device), 전기 습윤 표시 소자(electrowetting display device, EWD device), 및 유기 발광 표시 소자(organic light emitting display device, OLED device) 중 어느 하나일 수 있다. 한편, 하기에서는 설명의 편의를 위하여 상기 표시 소자로 상기 유기 발광 표시 소자를 예로서 설명한다.

각 화소(PXL)는 적색, 녹색, 및 청색 중 하나의 색을 출사할 수 있으나, 이에 한정되는 것은 아니다. 예를 들면, 각 화소(PXL)는 시안, 마젠타, 옐로우, 화이트 등의 색을 출사할 수도 있다.

상기 화소들(PXL)은 상기 제1 화소 영역(PXA1)에 배치된 제1 화소들(PXL1), 제2 화소 영역(PXA2)에 배치된 제2 화소들(PXL2), 및 제3 화소 영역(PXA3)에 배치된 제3 화소들(PXL3)을 포함할 수 있다. 본 발명의 일 실시예에 있어서, 상기 제1 내지 제3 화소들(PXL1, PXL2 PXL3)은 각각 복수 개로 제공되어 제1 방향(DR1)으로 연장된 행과 제2 방향(DR2)으로 연장된 열을 따라 매트릭스(matrix) 형태로 배열될 수 있다. 그러나, 상기 제1 내지 제3 화소들(PXL1, PXL2 PXL3)들의 배열 형태는 특별히 한정된 것은 아니며, 다양한 형태로 배열될 수 있다. 예를 들어, 상기 제1 화소들(PXL1)은 제1 방향(DR1)이 행 방향이 되도록 배열될 수 있으나, 제2 화소들(PXL2)은 제1 방향(DR1)이 아닌 다른 방향, 예를 들어, 상기 제1 방향(DR1)에 비스듬한 방향이 행 방향이 되도록 배열될 수도 있다. 또한, 제3 화소들(PXL3)은 상기 제1 화소들(PXL1) 및/또는 제2 화소들(PXL2)과 서로 동일한 방향 또는 서로 다른 방향으로 배열될 수 있음은 물론이다. 또는 본 발명의 다른 실시예에서는, 상기 행 방향이 제2 방향(DR2)가 되고 상기 열 방향이 제1 방향(DR1)이 될 수 있다.

한편, 상기 제2 영역(A2) 및 상기 제3 영역(A3)에서, 상기 제2 화소들(PXL2) 및 상기 제3 화소들(PXL3)의 수는 행에 따라 달라질 수 있다. 예를 들면, 상기 제2 영역(A2) 및 상기 제3 영역(A3)에 있어서, 상기 경사를 가지는 사선의 변으로 이루어진 모서리에 대응하는 행에 배치된 상기 제2 화소들(PXL2) 및 상기 제3 화소들(PXL3)의 수는 직선의 변으로 이루어진 모서리에 대응하는 행에 배치된 상기 제2 화소들(PXL2) 및 상기 제3 화소들(PXL3)의 수보다 작을 수 있다. 또한, 상기 행 내에 배치된 상기 제2 화소들(PXL2) 및 상기 제3 화소들(PXL3)의 수는 상기 행의 길이가 짧아질수록 감소할 수 있다. 따라서, 상기 제2 화소들(PXL2) 및 상기 제3 화소들(PXL3)을 연결하는 배선의 길이가 짧아질 수 있다.

또한, 상기 제2 영역(A2) 및 상기 제3 영역(A3)에서, 동일한 행에 대응하는 상기 제2 화소들(PXL2) 및 상기 제3 화소들(PXL3)의 스캔 라인(미도시) 또는 발광 제어 라인(미도시)은 스캔 라인 연결부(미도시) 또는 발광 제어 라인 연결부(미도시)를 통하여 전기적으로 연결될 수 있다.

상기 구동부는 배선부를 통해 각 화소에 신호를 제공하며, 이에 따라 상기 각 화소(PXL)의 구동을 제어할 수 있다. 도 1a 및 도 1b에는 설명의 편의를 위해 배선부가 생략되었으며, 상기 배선부에 대해서는 후술한다.

상기 구동부는 스캔 라인을 따라 각 화소에 스캔 신호를 제공하는 스캔 구동부들(SDV1, SDV2, SDV3; 이하 SDV), 발광 제어 라인을 따라 각 화소에 발광 제어 신호를 제공하는 발광 구동부들(EDV1, EDV2, EDV3; 이하 EDV), 및 데이터 라인을 따라 각 화소에 데이터 신호를 제공하는 데이터 구동부(DDV), 및 타이밍 제어부(미도시)를 포함할 수 있다. 상기 타이밍 제어부는 상기 스캔 구동부(SDV), 상기 발광 구동부(EDV), 및 상기 데이터 구동부(DDV)를 제어할 수 있다.

본 발명의 일 실시예에 있어서, 상기 스캔 구동부들(SDV)은 제1 화소들(PXL1)에 연결된 제1 스캔 구동부(SDV1), 제2 화소들(PXL2)에 연결된 제2 스캔 구동부(SDV2), 제3 화소들(PXL3)에 연결된 제3 스캔 구동부(SDV3)를 포함할 수 있다. 본 발명의 일 실시예에 있어서, 상기 발광 구동부들(EDV)들은 제1 화소들(PXL1)에 연결된 제1 발광 구동부(EDV1), 제2 화소들(PXL2)에 연결된 제2 발광 구동부(EDV2), 제3 화소들(PXL3)에 연결된 제3 발광 구동부(EDV3)를 포함할 수 있다.

상기 제1 스캔 구동부(SDV1)는 상기 제1 주변 영역(PPA1) 중 세로부에 배치될 수 있다. 상기 제1 주변 영역(PPA1)의 세로부는 상기 제1 화소 영역(PXA1)의 폭 방향을 따라 서로 이격된 한 쌍으로 제공되므로, 상기 제1 스캔 구동부(SDV1)는 상기 제1 주변 영역(PPA1)의 세로부 중 적어도 어느 한 쪽에 배치될 수 있다. 상기 제1 스캔 구동부(SDV1)는 상기 제1 주변 영역(PPA1)의 길이 방향을 따라 길게 연장될 수 있다.

이와 유사한 방식으로 상기 제2 스캔 구동부(SDV2)는 제2 주변 영역(PPA2)에, 상기 제3 스캔 구동부(SDV3)는 상기 제3 주변 영역(PPA3)에 배치될 수 있다.

본 발명의 일 실시예에 있어서, 상기 스캔 구동부들(SDV)은 상기 기판(SUB) 상에 직접 실장될 수 있다. 상기 스캔 구동부들(SDV)이 상기 기판(SUB) 상에 직접 실장되는 경우, 화소들(PXL)을 형성하는 공정 시에 함께 형성될 수 있다. 그러나, 상기 스캔 구동부들(SDV)의 제공 위치나 제공 방법은, 이에 한정되는 것은 아니다. 예를 들면, 상기 스캔 구동부들(SDV)은 별도의 칩에 형성되어 상기 기판(SUB) 상에 칩 온 글라스 형태로 제공될 수 있으며, 또는 인쇄 회로 기판 상에 실장되어 상기 기판(SUB)에 연결 부재를 통해 연결될 수도 있다.

상기 제1 발광 구동부(EDV1) 또한, 상기 제1 스캔 구동부(SDV1)와 유사하게, 상기 제1 주변 영역(PPA1) 중 세로부에 배치될 수 있다. 상기 제1 발광 구동부(EDV1)는 상기 제1 주변 영역(PPA1)의 세로부 중 적어도 어느 한 쪽에 배치될 수 있다. 상기 제1 발광 구동부(EDV1)는 상기 제1 주변 영역(PPA1)의 길이 방향을 따라 길게 연장될 수 있다.

이와 유사한 방식으로, 상기 제2 발광 구동부(EDV2)는 제2 주변 영역(PPA2)에, 상기 제3 발광 구동부(EDV3)는 상기 제3 주변 영역(PPA3)에 배치될 수 있다.

본 발명의 일 실시예에 있어서, 상기 발광 구동부들(EDV)은 상기 기판(SUB) 상에 직접 실장될 수 있다. 상기 발광 구동부들(EDV)이 상기 기판(SUB) 상에 직접 실장되는 경우, 화소들(PXL)을 형성하는 공정 시에 함께 형성될 수 있다. 그러나, 상기 발광 구동부들(EDV)의 제공 위치나 제공 방법은, 이에 한정되는 것은 아니다. 상기 발광 구동부들(EDV)은 별도의 칩에 형성되어 상기 기판(SUB) 상에 칩 온 글라스 형태로 제공될 수 있으며, 또는 인쇄 회로 기판 상에 실장되어 상기 기판(SUB)에 연결 부재를 통해 연결될 수도 있다.

본 발명의 일 실시예에 있어서, 상기 스캔 구동부들(SDV)과 발광 구동부들(EDV)이 서로 인접하며, 주변 영역들(PPA)의 세로부 쌍 중 어느 한 쪽에만 형성된 것을 일 예로서 도시하였으나, 이에 한정되는 것은 아니다. 상기 스캔 구동부들(SDV)과 발광 구동부들(EDV)의 배치는 다양한 방식으로 변경될 수 있다. 예를 들어, 상기 제1 스캔 구동부(SDV1)는 상기 제1 주변 영역(PPA1)의 세로부 중 일측에 상기 제1 발광 구동부(EDV1)는 상기 제1 주변 영역(PPA1)의 세로부 중 타측에 제공될 수 있다. 또는 상기 제1 스캔 구동부(SDV1)가 상기 제1 주변 영역(PPA1)의 세로부 중 양측에 모두 제공될 수 있으며, 상기 제1 발광 구동부(EDV1)는 상기 제1 주변 영역(PPA1)의 세로부 중 일측에만 제공될 수 있다.

상기 데이터 구동부(DDV)는 제1 주변 영역(PPA1)에 배치될 수 있다. 특히 상기 데이터 구동부(DDV)는 상기 제1 주변 영역(PPA1)의 가로부에 배치될 수 있다. 상기 데이터 구동부(DDV)는 상기 제1 주변 영역(PPA1)의 폭 방향을 따라 길게 연장될 수 있다.

본 발명의 일 실시예에 있어서, 상기 스캔 구동부들(SDV), 상기 발광 구동부들(EDV), 및/또는 상기 데이터 구동부(DDV)의 위치는 필요에 따라 서로 바뀔 수 있다.

상기 타이밍 제어부(미도시)는 다양한 방식으로 상기 제1 내지 제3 스캔 구동부들(SDV1, SDV2, SDV3), 제1 내지 제3 발광 구동부들(EDV1, EDV2, EDV3), 및 상기 데이터 구동부(DDV)에 배선을 통해 연결될 수 있으며, 배치되는 위치는 특별히 한정되는 것은 아니다. 예를 들어, 상기 타이밍 제어부는 인쇄 회로 기판 상에 실장되어, 가요성 인쇄 회로 기판을 통해 상기 제1 내지 제3 스캔 구동부들(SDV1, SDV2, SDV3), 제1 내지 제3 발광 구동부들(EDV1, EDV2, EDV3), 및 상기 데이터 구동부(DDV)와 연결될 수 있으며, 상기 인쇄 회로 기판은 상기 기판(SUB)의 일측, 또는 상기 기판(SUB)의 배면 등 다양한 위치에 배치될 수 있다.

또한, 동일한 행에 대응하는 상기 제2 화소들(PXL2) 및 상기 제3 화소들(PXL3)의 스캔 라인(미도시) 또는 발광 제어 라인(미도시)은 스캔 라인 연결부(미도시) 또는 발광 제어 라인 연결부(미도시)를 통하여 전기적으로 연결되는 구성에서는 상기 제2 및 제3 스캔 구동부들(SDV2, SDV3) 중 하나와, 상기 제2 및 제3 발광 구동부들(EDV2, EDV3) 중 하나는 생략될 수 있다.

상기 전원 공급부는 적어도 하나의 전원 공급 라인(ELVDD, ELVSS)을 포할 수 있다. 예를 들면, 상기 전원 공급부는 제1 전원 공급 라인(ELVDD) 및 제2 전원 공급 라인(ELVSS)을 포함할 수 있다. 상기 제1 전원 공급 라인(ELVDD) 및 상기 제2 전원 공급 라인(ELVSS)은 상기 제1 화소(PXL1), 상기 제2 화소(PXL2) 및 상기 제3 화소(PXL3)에 전원을 공급할 수 있다.

상기 제1 전원 공급 라인(ELVDD) 및 상기 제2 전원 공급 라인(ELVSS) 중 하나, 예를 들면, 상기 제1 전원 공급 라인(ELVDD)은 상기 제1 화소 영역(PXA1)의 일변과 대응하도록 배치될 수 있다. 예를 들면, 상기 제1 전원 공급 라인(ELVDD)은 상기 제1 주변 영역(PPA1)의 상기 데이터 구동부(DDV)가 배치된 영역에 배치될 수 있다. 또한, 상기 제1 전원 공급 라인(ELVDD)은 상기 제1 화소 영역(PXA1)의 폭 방향으로 연장될 수 있다.

상기 제1 전원 공급 라인(ELVDD) 및 상기 제2 전원 공급 라인(ELVSS) 중 다른 하나, 예를 들면, 상기 제2 전원 공급 라인(ELVSS)은 상기 제1 주변 영역(PPA1)의 상기 데이터 구동부(DDV)가 배치된 영역을 제외한 상기 제1 화소 영역(PXA1), 상기 제2 화소 영역(PXA2) 및 상기 제3 화소 영역(PXA3)을 에워싸도록 배치될 수 있다. 예를 들면, 상기 제2 전원 공급 라인(ELVSS)은 상기 제1 주변 영역(PPA1), 상기 제2 주변 영역(PPA2), 상기 제3 주변 영역(PPA3), 및 상기 부가 주변 영역(APA)의 좌측 세로부, 상기 제1 주변 영역(PPA1)의 우측 세로부를 따라 연장된 형상을 가질 수 있다.

상기에서는 상기 제1 전원 공급 라인(ELVDD)이 상기 제1 주변 영역(PPA1) 중상기 제1 화소 영역(PXA1)의 일변에 대응하여 배치되고, 상기 제2 전원 공급 라인(ELVSS)이 나머지 주변 영역들에 배치됨을 예로서 설명하였으나, 이에 한정되는 것은 아니다. 예를 들면, 상기 제1 전원 공급 라인(ELVDD)과 상기 제2 전원 공급 라인(ELVSS)이 상기 제1 화소 영역(PXA1), 상기 제2 화소 영역(PXA2) 및 상기 제3 화소 영역(PXA3)을 에워싸도록 배치될 수 있다.

상기 제1 전원 공급 라인(ELVDD)에 인가되는 전압은 상기 제2 전원 공급 라인(ELVSS)에 인가되는 전압보다 높을 수 있다.

도 3 및 도 4는 본 발명의 일 실시예에 따른 화소들 및 구동부의 실시예를 나타낸 블록도이다.

도 1a, 도 1b, 도 2 내지 도 4를 참조하면, 본 발명의 실시예에 의한 표시 장치는 화소들(PXL), 구동부, 및 배선부를 포함한다.

상기 화소들(PXL)은 제1 내지 제3 화소들(PXL1, PXL2, PXL3)을 포함하고, 구동부는 제1 내지 제3 스캔 구동부(SDV1, SDV2, SDV3), 제1 내지 제3 발광 구동부(EDV1, EDV2, EDV3), 데이터 구동부(DDV), 및 타이밍 제어부(TC)를 포함한다. 도 3에 있어서, 제1 내지 제3 스캔 구동부(SDV1, SDV2, SDV3), 제1 내지 제3 발광 구동부(EDV1, EDV2, EDV3), 데이터 구동부(DDV), 및 타이밍 제어부(TC)의 위치는 설명의 편의를 위해 설정된 것으로서, 실제 표시 장치를 구현할 때는 표시 장치 내에서의 다른 위치에 배치될 수 있다. 예를 들어, 상기 데이터 구동부(DDV)는 제2 영역(A2) 및 제3 영역(A3)보다 제1 영역(A1)에 가까운 곳에 배치되었으나, 이에 한정되지는 않는다. 일례로, 데이터 구동부(DDV)는 도 4에 도시된 바와 같이 데이터 구동부(DDV)는 제2 영역(A2) 및 제3 영역(A3)과 인접되게 배치될 수 있다.

상기 배선부는 상기 구동부의 신호를 각 화소(PXL)에 제공하며, 스캔 라인들, 데이터 라인들, 라인 연결부들(ES, EE), 및 발광 제어 라인들, 전원 라인, 및 초기화 전원 라인(미도시)을 포함한다.

상기 스캔 라인들은 상기 제1 내지 제3 화소들(PXL1, PXL2, PXL3)에 각각 연결된 제1 내지 제3 스캔 라인들(S11 내지 S1n, S21 및 S22, S31 및 S32)을 포함하고, 상기 발광 제어 라인들은 상기 제1 내지 제3 화소들(PXL1, PXL2, PXL3)에 각각 연결된 제1 내지 제3 발광 제어 라인들(E11 내지 E1n, E21 및 E22, E31 및 E32)을 포함한다. 상기 데이터 라인들(D1 내지 Dm)과 상기 전원 라인은 제1 내지 제3 화소들(PXL1, PXL2, PXL3)에 연결된다.

추가적으로, 제2 스캔 라인들(S21 및 S22) 및 제3 스캔 라인들(S31 및 S32)은 스캔 라인 연결부들(ES)에 의하여 전기적으로 접속된다. 일례로, 첫 번째 제2 스캔 라인(S21)은 첫 번째 스캔 라인 연결부(ES)에 의하여 첫 번째 제3 스캔 라인(S31)과 전기적으로 접속된다. 그리고, 두 번째 제2 스캔 라인(S22)은 두 번째 스캔 라인 연결부(ES)에 의하여 두 번째 제3 스캔 라인(S32)과 전기적으로 접속된다.

또한, 제2 발광 제어 라인들(E21 및 E22) 및 제3 발광 제어 라인들(E31 및 E32)은 발광 제어 라인 연결부들(EE)에 의하여 전기적으로 접속된다. 일례로, 첫 번째 제2 발광 제어 라인(E21)은 첫 번째 발광 제어 라인 연결부(EE)에 의하여 첫 번째 제3 발광 제어 라인(E31)과 전기적으로 접속된다. 그리고, 두 번째 제2 발광 제어 라인(E22)은 두 번째 발광 제어 라인 연결부(EE)에 의하여 두 번째 제3 발광 제어 라인(E32)과 전기적으로 접속된다.

제1 화소들(PXL1)은 제1 화소 영역(PXA1)에 위치된다. 상기 제1 화소들(PXL1)은 제1 스캔 라인들(S11 내지 S1n), 제1 발광 제어 라인들(E11 내지 E1n) 및 데이터 라인들(D1 내지 Dm)에 연결된다. 이와 같은 제1 화소들(PXL1)은 제1 스캔 라인들(S11 내지 S1n)로부터 스캔 신호가 공급될 때 데이터 라인들(D1 내지 Dm)로부터 데이터 신호를 공급받는다. 데이터 신호를 공급받은 제1 화소들(PXL1)은 제1 전원(ELVDD)으로부터 유기 발광 소자(미도시)를 경유하여 제2 전원(ELVSS)으로 흐르는 전류량을 제어한다.

제2 화소들(PXL2)은 제2 화소 영역(PXA2)에 위치된다. 상기 제2 화소들(PXL2)은 제2 스캔 라인들(S21, S22), 제2 발광 제어 라인들(E21, E22) 및 데이터 라인들(D1 내지 D3)에 연결된다. 이와 같은 제2 화소들(PXL2)은 제2 스캔 라인들(S21, S22) 및 제3 스캔 라인들(S31, S32)로부터 스캔 신호가 공급될 때 데이터 라인들(D1 내지 D3)로부터 데이터 신호를 공급받는다. 데이터 신호를 공급받은 제2 화소들(PXL2)은 제1 전원(ELVDD)으로부터 유기 발광 소자를 경유하여 제2 전원(ELVSS)으로 흐르는 전류량을 제어한다.

추가적으로, 도 3에서는 두 개의 제2 스캔 라인들(S21, S22), 두 개의 제2 발광 제어 라인들(E21, E22) 및 세 개의 데이터 라인들(D1 내지 D3)에 의하여 제2 화소 영역(PXA2)에 여섯 개의 제2 화소들(PXL2)이 위치되는 것으로 도시하였지만, 본원 발명이 이에 한정되지는 않는다. 즉, 상기 제2 화소 영역(PXA2)의 크기에 대응하여 복수의 제2 화소들(PXL2)이 배치되며, 상기 제2 화소들(PXL2)에 대응하여 제2 스캔 라인들, 제2 발광 제어 라인들, 및 데이터 라인들의 수가 다양하게 설정될 수 있다.

제3 화소들(PXL3)은 제3 스캔 라인들(S31, S32), 제3 발광 제어 라인들(E31, E32) 및 데이터 라인들(Dm-2 내지 Dm)에 의하여 구획된 제3 화소 영역(PXA3)에 위치된다. 이와 같은 제3 화소들(PXL3)은 제3 스캔 라인들(S31, S32) 및 제2 스캔 라인들(S21, S22)로부터 스캔 신호가 공급될 때 데이터 라인들(Dm-2 내지 Dm)로부터 데이터 신호를 공급받는다. 데이터 신호를 공급받은 제3 화소들(PXL3)은 제1 전원(ELVDD)으로부터 유기 발광 소자를 경유하여 제2 전원(ELVSS)으로 흐르는 전류량을 제어한다.

추가적으로, 도 3에서는 두 개의 제3 스캔 라인들(S31, S32), 두 개의 제3 발광 제어 라인들(E31, E32) 및 세 개의 데이터 라인들(Dm-2 내지 Dm)에 의하여 제3 화소 영역(PXA3)에 여섯 개의 제3 화소들(PXL3)이 위치되는 것으로 도시하였지만, 본원 발명이 이에 한정되지는 않는다. 즉, 제3 화소 영역(PXA3)의 크기에 대응하여 복수의 제3 화소들(PXL3)이 배치되며, 제3 화소들(PXL3)에 대응하여 제3 스캔 라인들, 제3 발광 제어 라인들 및 데이터 라인들의 수가 다양하게 설정될 수 있다.

제1 스캔 구동부(SDV1)는 타이밍 제어부(TC)로부터의 제1 게이트 제어 신호(GCS1)에 대응하여 제1 스캔 라인들(S11 내지 S1n)로 스캔 신호를 공급한다. 일례로, 제1 스캔 구동부(SDV1)는 제1 스캔 라인들(S11 내지 S1n)로 스캔 신호를 순차적으로 공급할 수 있다. 제1 스캔 라인들(S11 내지 S1n)로 스캔 신호가 순차적으로 공급되면 제1 화소들(PXL1)이 수평라인 단위로 순차적으로 선택된다.

제2 스캔 구동부(SDV2)는 타이밍 제어부(TC)로부터의 제2 게이트 제어 신호(GCS2)에 대응하여 제2 스캔 라인들(S21, S22)로 스캔 신호를 공급한다. 이때, 제2 스캔 라인들(S21, S22)로 공급된 스캔 신호는 스캔 라인 연결부들(ES)을 경유하여 제3 스캔 라인들(S31, S32)로 공급된다. 제2 스캔 구동부(SDV2)는 제2 스캔 라인들(S21, S22)로 스캔 신호를 순차적으로 공급할 수 있다. 제2 스캔 라인들(S21, S22)로 스캔 신호가 순차적으로 공급되면 제2 화소들(PXL2) 및 제3 화소들(PXL3)이 수평라인 단위로 순차적으로 선택된다.

제3 스캔 구동부(SDV3)는 타이밍 제어부(TC)로부터의 제3 게이트 제어 신호(GCS3)에 대응하여 제3 스캔 라인들(S31, S32)로 스캔 신호를 공급한다. 이때, 제3 스캔 라인들(S31, S32)로 공급된 스캔신호는 스캔 라인 연결부(ES)를 경유하여 제2 스캔 라인들(S21, S22)로 공급된다. 제3 스캔 구동부(SDV3)는 제3 스캔 라인들(S31, S32)로 스캔 신호를 순차적으로 공급할 수 있다. 제3 스캔 라인들(S31, S32)로 스캔 신호가 순차적으로 공급되면 제2 화소들(PXL2) 및 제3 화소들(PXL3)이 수평라인 단위로 순차적으로 선택된다.

한편, 스캔 라인 연결부들(ES)에 의하여 제2 스캔 라인들(S21, S22) 및 제3 스캔 라인들(S31, S32)이 전기적으로 접속되기 때문에 제2 스캔 구동부(SDV2)로부터 공급되는 스캔신호 및 제3 스캔 구동부(SDV3)로부터 공급되는 스캔신호는 서로 동기되도록 공급된다.

일례로, 제2 스캔 구동부(SDV2)로부터 첫 번째 제2 스캔 라인(S21)으로 공급되는 스캔신호는 제3 스캔 구동부(SDV3)로부터 첫 번째 제3 스캔 라인(S31)으로 공급되는 스캔신호와 동시에 공급될 수 있다. 마찬가지로, 제2 스캔 구동부(SDV2)로부터 두 번째 제2 스캔 라인(S22)으로 공급되는 스캔신호는 제3 스캔 구동부(SDV3)로부터 두 번째 제3 스캔 라인(S32)으로 공급되는 스캔신호와 동시에 공급될 수 있다.

이와 같은 제2 스캔 구동부(SDV2) 및 제3 스캔 구동부(SDV3)를 이용하여 제2 스캔 라인들(S21, S22) 및 제3 스캔 라인들(S31, S32)로 스캔신호를 공급하면 제2 스캔 라인들(S21, S22) 및 제3 스캔 라인들(S31, S32)의 RC 딜레이에 의한 스캔신호의 지연을 방지할 수 있고, 이에 따라 제2 스캔 라인들(S21, S22) 및 제3 스캔 라인들(S31, S32)로 원하는 스캔신호를 공급할 수 있다.

추가적으로, 제2 스캔 구동부(SDV2) 및 제3 스캔 구동부(SDV3)는 동기되도록 구동되고, 이에 따라 동일한 게이트 제어 신호(GCS)에 의하여 구동될 수 있다. 일례로, 제3 스캔 구동부(SDV3)로 공급되는 제3 게이트 제어 신호(GCS3)는 제2 게이트 제어 신호(GCS2)와 동일한 신호로 설정될 수 있다.

제1 발광 구동부(EDV1)는 타이밍 제어부(TC)로부터의 제4 게이트 제어 신호(GCS4)에 대응하여 제1 발광 제어 라인들(E11 내지 E1n)로 발광 제어 신호를 공급한다. 일례로, 제1 발광 구동부(EDV1)는 제1 발광 제어 라인들(E11 내지 E1n)로 발광 제어 신호를 순차적으로 공급할 수 있다.

여기서, 발광 제어 신호는 스캔 신호보다 넓은 폭으로 설정될 수 있다. 일례로, i(i는 자연수)번째 제1 발광 제어 라인(E1i)으로 공급되는 발광 제어 신호는 i-1번째 제1 스캔 라인(S1i-1)으로 공급되는 스캔 신호 및 i번째 제1 스캔 라인(S1i)으로 공급되는 스캔 신호와 적어도 일부 기간 중첩되도록 공급될 수 있다.

제2 발광 구동부(EDV2)는 타이밍 제어부(TC)로부터의 제5 게이트 제어 신호(GCS5)에 대응하여 제2 발광 제어 라인들(E21, E22)로 발광 제어 신호를 공급한다. 이때, 제2 발광 제어 라인들(E21, E22)로 공급된 발광 제어 신호는 발광 제어 라인 연결부들(EE)을 경유하여 제3 발광 제어 라인들(E31, E32)로 공급된다. 제2 발광 구동부(EDV2)는 제2 발광 제어 라인들(E21, E22)로 발광 제어 신호를 순차적으로 공급할 수 있다.

제3 발광 구동부(EDV3)는 타이밍 제어부(TC)로부터의 제6 게이트 제어 신호(GCS6)에 대응하여 제3 발광 제어 라인들(E31, E32)로 발광 제어 신호를 공급한다. 이때, 제3 발광 제어 라인들(E31, E32)로 공급된 발광 제어 신호는 발광 제어 라인 연결부들(EE)을 경유하여 제2 발광 제어 라인들(E21, E22)도 공급된다. 제3 발광 구동부(EDV3)는 제3 발광 제어 라인들(E31, E32)로 발광 제어 신호를 순차적으로 공급할 수 있다.

추가적으로, 발광 제어 신호는 화소들(PXL)에 포함되는 트랜지스터가 턴-오프될 수 있도록 게이트 오프 전압(예를 들면, 하이 전압)으로 설정되고, 스캔 신호는 화소들(PXL)에 포함되는 트랜지스터가 턴-온될 수 있도록 게이트 온 전압(예를 들면, 로우 전압)으로 설정될 수 있다.

한편, 발광 제어 라인 연결부들(EE)에 의하여 제2 발광 제어 라인들(E21, E22) 및 제3 발광 제어 라인들(E31, E32)이 전기적으로 접속되기 때문에 제2 발광 구동부(EDV2)로부터 공급되는 발광 제어 신호 및 제3 발광 구동부(EDV3)로부터 공급되는 발광 제어 신호는 서로 동기되도록 공급된다.

일례로, 제2 발광 구동부(EDV2)로부터 첫 번째 제2 발광 제어 라인(E21)으로 공급되는 발광 제어 신호는 제3 발광 구동부(EDV3)로부터 첫 번째 제3 발광 제어 라인(E31)으로 공급되는 발광 제어 신호와 동시에 공급될 수 있다. 마찬가지로, 제2 발광 구동부(EDV2)로부터 두 번째 제2 발광 제어 라인(E22)으로 공급되는 발광 제어 신호는 제3 발광 구동부(EDV3)로부터 두 번째 제3 발광 제어 라인(E32)으로 공급되는 발광 제어 신호와 동시에 공급될 수 있다.

이와 같은 제2 발광 구동부(EDV2) 및 제3 발광 구동부(EDV3)를 이용하여 제2 발광 제어 라인들(E21, E22) 및 제3 발광 제어 라인들(E31, E32)로 발광 제어 신호를 공급하면 제2 발광 제어 라인들(E21, E22) 및 제3 발광 제어 라인들(E31, E32)의 RC 딜레이에 의한 발광 제어 신호의 지연을 방지할 수 있고, 이에 따라 제2 발광 제어 라인들(E21, E22) 및 제3 발광 제어 라인들(E31, E32)로 원하는 발광 제어신호를 공급할 수 있다.

추가적으로, 제2 발광 구동부(EDV2) 및 제3 발광 구동부(EDV3)는 동기되도록 구동되고, 이에 따라 동일한 게이트 제어 신호(GCS)에 의하여 구동될 수 있다. 일례로, 제3 발광 구동부(EDV3)로 공급되는 제6 게이트 제어 신호(GCS6)는 제5 게이트 제어 신호(GCS5)와 동일한 신호로 설정될 수 있다.

데이터 구동부(DDV)는 데이터 제어 신호(DCS)에 대응하여 데이터 라인들(D1 내지 Dm)로 데이터 신호를 공급한다. 데이터 라인들(D1 내지 Dm)로 공급된 데이터 신호는 스캔 신호에 의하여 선택된 화소들(PXL)로 공급된다.

타이밍 제어부(TC)는 외부로부터 공급되는 타이밍 신호들에 기초하여 생성된 게이트 제어 신호들(GCS1 내지 GCS6)을 스캔 구동부들(SDV) 및 발광 구동부들(EDV)로 공급하고, 데이터 제어 신호(DCS)를 데이터 구동부(DDV)로 공급한다.

게이트 제어 신호들(GCS1 내지 GCS6) 각각에는 스타트 펄스 및 클럭 신호들이 포함된다. 스타트 펄스는 첫번째 스캔 신호 또는 첫번째 발광 제어 신호의 타이밍을 제어한다. 클럭 신호들은 스타트 펄스를 쉬프트시키기 위하여 사용된다.

데이터 제어 신호(DCS)에는 소스 스타트 펄스 및 클럭 신호들이 포함된다. 소스 스타트 펄스는 데이터의 샘플링 시작 시점을 제어한다. 클럭 신호들은 샘플링 동작을 제어하기 위하여 사용된다.

한편, 상기 표시 장치가 순차적으로 구동되는 경우, 제1 스캔 구동부(SDV1)는 제2 스캔 구동부(SDV2)의 마지막 출력신호를 스타트 펄스로 공급받을 수 있다. 마찬가지로, 상기 표시 장치가 순차적으로 구동되는 경우, 제1 발광 구동부(EDV1)는 제2 발광 구동부(EDV2)의 마지막 출력신호를 스타트 펄스로 공급받을 수 있다.

도 5는 본 발명의 다른 실시예에 따른 화소들 및 구동부를 나타내는 블록도이다. 도 5를 설명할 때 도 3과 동일한 구성에 대해서는 동일한 도면부호를 할당함과 아울러 상세한 설명은 생략하기로 한다.

도 5를 참조하면, 본 발명의 다른 실시예에 따른 표시 장치는 화소들(PXL), 구동부, 및 배선부를 포함한다.

상기 화소들(PXL)은 제1 내지 제3 화소들(PXL1, PXL2, PXL3)을 포함하고, 구동부는 제1 및 제2 스캔 구동부(SDV1, SDV2), 제1 및 제2 발광 구동부(EDV1, EDV2), 데이터 구동부(DDV), 및 타이밍 제어부(TC)를 포함한다.

이와 같은 도 5를 도 3과 비교하면, 도 5에는 제3 스캔 구동부(SDV3) 및 제3 발광 구동부(EDV3)가 생략할 수 있다.

즉, 본 발명의 다른 실시예에 따른 표시 장치에서는 제2 스캔 구동부(SDV2)를 이용하여 제2 스캔 라인들(S21 및 S22) 및 제3 스캔 라인들(S31 및 S32)을 구동하고, 제2 발광 구동부(EDV2)를 이용하여 제2 발광 제어 라인들(E21 및 E22) 및 제3 발광 제어 라인들(E31 및 E32)을 구동한다.

상세히 설명하면, 제2 스캔 라인들(S21 및 S22) 및 제3 스캔 라인들(S31 및 S32)은 스캔 라인 연결부들(ES)에 의하여 전기적으로 접속되고, 제2 발광 제어 라인들(E21 및 E22) 및 제3 발광 제어 라인들(E31 및 E32)은 발광 제어 라인 연결부들(EE)에 의하여 전기적으로 접속된다. 따라서, 제2 스캔 구동부(SDV2)로부터의 스캔신호는 제2 스캔 라인들(S21 및 S22) 및 스캔 라인 연결부들(ES)을 경유하여 제3 스캔 라인들(S31 및 S32)로 공급될 수 있다. 마찬가지로, 제2 발광 구동부(EDV2)로부터의 발광 제어 신호는 제2 발광 제어 라인들(E21 및 E22) 및 발광 제어 라인 연결부들(EE)을 경유하여 제3 발광 제어 라인들(E31 및 E32)로 공급될 수 있다.

도 6은 본 발명의 또 다른 실시예에 따른 화소들 및 구동부를 나타내는 블록도이다. 도 6을 설명할 때 도 3와 동일한 구성에 대해서는 동일한 도면부호를 할당함과 아울러 상세한 설명은 생략하기로 한다.

도 6을 참조하면, 본 발명의 또 다른 실시예에 의한 표시 장치는 화소들(PXL), 구동부, 및 배선부를 포함한다.

상기 화소들(PXL)은 제1 내지 제3 화소들(PXL1, PXL2, PXL3)을 포함하고, 구동부는 제1 내지 제4 스캔 구동부(SDV1, SDV2, SDV3, SDV4), 제1 내지 제4 발광 구동부(EDV1, EDV2, EDV3, EDV4), 데이터 구동부(DDV), 및 타이밍 제어부(TC)를 포함한다.

제4 스캔 구동부(SDV4)는 타이밍 제어부(TC)로부터 제7 게이트 제어 신호(GCS7)에 대응하여 제1 스캔 라인들(S11 내지 S1n)로 스캔 신호를 공급한다. 일례로, 제4 스캔 구동부(SDV4)는 제1 스캔 라인들(S11 내지 S1n)로 스캔 신호를 순차적으로 공급할 수 있다. 제1 스캔 라인들(S11 내지 S1n)로 스캔 신호가 순차적으로 공급되면 제1 화소들(PXL1)이 수평라인 단위로 순차적으로 선택된다.

한편, 제4 스캔 구동부(SDV4)는 제1 스캔 구동부(SDV1)와 동기되도록 제1 스캔 라인들(S11 내지 S1n)로 스캔 신호를 공급한다. 일례로, 첫 번째 제 1스캔 라인(S11)은 제1 스캔 구동부(SDV1) 및 제4 스캔 구동부(SDV4)로부터 동시에 스캔 신호를 공급받을 수 있다. 마찬가지로, 마지막 제 1스캔 라인(S1n)은 제1 스캔 구동부(SDV1) 및 제4 스캔 구동부(SDV4)로부터 동시에 스캔 신호를 공급받을 수 있다.

이와 같이 제1 스캔 구동부(SDV1) 및 제4 스캔 구동부(SDV4)를 이용하여 제1 스캔 라인들(S11 내지 S1n)로 스캔신호를 공급하면 제1 스캔 라인들(S11 내지 S1n)의 RC 딜레이에 의한 스캔신호의 지연을 방지할 수 있고, 이에 따라 제1 스캔 라인들(S11 내지 S1n)로 원하는 스캔신호를 공급할 수 있다.

추가적으로, 제1스캔 구동부(SDV1) 및 제4 스캔 구동부(SDV4)는 동기되도록 구동되고, 이에 따라 동일한 게이트 제어 신호(GCS)에 의하여 구동될 수 있다. 일례로, 제 4스캔 구동부(SDV4)로 공급되는 제7 게이트 제어 신호(GCS7)는 제1 게이트 제어 신호(GCS1)와 동일한 신호로 설정될 수 있다. 한편, 상기 표시 장치가 순차적으로 구동되는 경우, 제4 스캔 구동부(SDV4)는 제3 스캔 구동부(SDV3)의 마지막 출력신호를 스타트 펄스로 공급받을 수 있다.

제4 발광 구동부(EDV4)는 타이밍 제어부(TC)로부터의 제8 게이트 제어 신호(GCS8)에 대응하여 제1 발광 제어 라인들(E11 내지 E1n)로 발광 제어 신호를 공급한다. 일례로, 제4 발광 구동부(EDV4)는 제1 발광 제어 라인들(E11 내지 E1n)로 발광 제어 신호를 순차적으로 공급할 수 있다.

한편, 제4 발광 구동부(EDV4)는 제 1발광 구동부(EDV1)와 동기되도록 제1 발광 제어 라인들(E11 내지 E1n)로 발광 제어 신호를 공급한다. 일례로, 첫 번째 제 1발광 제어 라인(E11)은 제1 발광 구동부(EDV1) 및 제4 발광 구동부(EDV4)로부터 동시에 발광 제어 신호를 공급받을 수 있다. 마찬가지로, 마지막 제 1발광 제어 라인(E1n)은 제1 발광 구동부(EDV1) 및 제4 발광 구동부(EDV4)로부터 동시에 발광 제어 신호를 공급받을 수 있다.

이와 같이 제1 발광 구동부(EDV1) 및 제4 발광 구동부(EDV4)를 이용하여 제 1발광 제어 라인들(E11 내지 E1n)로 발광 제어 신호를 공급하면 제 1발광 제어 라인들(E11 내지 E1n)의 RC 딜레이에 의한 발광 제어 신호의 지연을 방지할 수 있고, 이에 따라 제 1발광 제어 라인들(E11 내지 E1n)로 원하는 발광 제어 신호를 공급할 수 있다.

추가적으로, 제1발광 구동부(EDV1) 및 제4 발광 구동부(EDV4)는 동기되도록 구동되고, 이에 따라 동일한 게이트 제어 신호(GCS)에 의하여 구동될 수 있다. 일례로, 제 4발광 구동부(SDV4)로 공급되는 제8 게이트 제어 신호(GCS8)는 제4 게이트 제어 신호(GCS4)와 동일한 신호로 설정될 수 있다. 한편, 상기 표시 장치가 순차적으로 구동되는 경우, 제4 발광 구동부(EDV4)는 제3 발광 구동부(EDV3)의 마지막 출력신호를 스타트 펄스로 공급받을 수 있다.

추가적으로, 도 3 내지 도 6에 도시된 구동부들(SDV1 내지 SDV4, EDV1 내지 EDV4)은 개발자에 의하여 다양한 형태로 배치될 수 있다. 일례로, 표시 장치에 제3 스캔 구동부(SDV3), 제4 스캔 구동부(SDV4), 제3 발광 구동부(EDV3) 및 제4 발광 구동부(EDV4)가 배치되고, 제1 스캔 구동부(SDV1), 제2 스캔 구동부(SDV2), 제1 발광 구동부(EDV1) 및 제2 발광 구동부(EDV2)가 삭제될 수 있다.

도 7은 도 3에 도시된 제1 화소의 실시예를 나타내는 도면이다. 도 7에서는 설명의 편의성을 위하여 제m 데이터 라인(Dm) 및 i번째 제1 스캔 라인(S1i)에 접속된 화소를 도시하기로 한다.

도 7을 참조하면, 본 발명의 실시예에 의한 제1 화소(PXL1)는 유기 발광 소자(OLED), 제1 트랜지스터(T1) 내지 제7 트랜지스터(T7) 및 스토리지 커패시터(Cst)를 구비한다.

유기 발광 소자(OLED)의 애노드는 제6 트랜지스터(T6)를 경유하여 제1 트랜지스터(T1)에 접속되고, 캐소드는 제2 전원(ELVSS)에 접속된다. 이와 같은 유기 발광 소자(OLED)는 제1 트랜지스터(T1)로부터 공급되는 전류량에 대응하여 소정 휘도의 빛을 생성한다.

유기 발광 소자(OLED)로 전류가 흐를 수 있도록 제1 전원(ELVDD)은 제2 전원(ELVSS)보다 높은 전압으로 설정될 수 있다.

제7 트랜지스터(T7)는 초기화 전원(Vint)과 유기 발광 소자(OLED)의 애노드 사이에 접속된다. 그리고, 제7 트랜지스터(T7)의 게이트 전극은 i번째 제1 스캔 라인(S1i)에 접속된다. 이와 같은 제7 트랜지스터(T7)는 i번째 제1 스캔 라인(S1i)으로 스캔 신호가 공급될 때 턴-온되어 초기화 전원(Vint)의 전압을 유기 발광 소자(OLED)의 애노드로 공급한다. 여기서, 초기화 전원(Vint)은 데이터 신호보다 낮은 전압으로 설정될 수 있다.

제6 트랜지스터(T6)는 제1 트랜지스터(T1)와 유기 발광 소자(OLED) 사이에 접속된다. 그리고, 제6 트랜지스터(T6) 게이트 전극은 i번째 제1 발광 제어 라인(E1i)에 접속된다. 이와 같은 제6 트랜지스터(T6)는 i번째 제1 발광 제어 라인(E1i)으로 발광 제어 신호가 공급될 때 턴-오프되고, 그 외의 경우에 턴-온된다.

제5 트랜지스터(T5)는 제1 전원(ELVDD)과 제1 트랜지스터(T1) 사이에 접속된다. 그리고, 제5 트랜지스터(T5)의 게이트 전극은 i번째 제1 발광 제어 라인(E1i)에 접속된다. 이와 같은 제5 트랜지스터(T5)는 i번째 제1 발광 제어 라인(E1i)으로 발광 제어 신호가 공급될 때 턴-오프되고, 그 외의 경우에 턴-온된다.

제1 트랜지스터(T1; 구동 트랜지스터)의 제1 전극은 제5 트랜지스터(T5)를 경유하여 제1 전원(ELVDD)에 접속되고, 제2 전극은 제6 트랜지스터(T6)를 경유하여 유기 발광 소자(OLED)의 애노드에 접속된다. 그리고, 제1 트랜지스터(T1)의 게이트 전극은 제1 노드(N1)에 접속된다. 이와 같은 제1 트랜지스터(T1)는 제1 노드(N1)의 전압에 대응하여 제1 전원(ELVDD)으로부터 유기 발광 소자(OLED)를 경유하여 제2 전원(ELVSS)으로 흐르는 전류량을 제어한다.

제3 트랜지스터(T3)는 제1 트랜지스터(T1)의 제2 전극과 제1 노드(N1) 사이에 접속된다. 그리고, 제3 트랜지스터(T3)의 게이트 전극은 i번째 제1 스캔 라인(S1i)에 접속된다. 이와 같은 제3 트랜지스터(T3)는 i번째 제1 스캔 라인(S1i)으로 스캔 신호가 공급될 때 턴-온되어 제1 트랜지스터(T1)의 제2 전극과 제1 노드(N1)를 전기적으로 접속시킨다. 따라서, 제3 트랜지스터(T3)가 턴-온 될 때 제1 트랜지스터(T1)는 다이오드 형태로 접속된다.

제4 트랜지스터(T4)는 제1 노드(N1)와 초기화 전원(Vint) 사이에 접속된다. 그리고, 제4 트랜지스터(T4)의 게이트 전극은 i-1번째 제1 스캔 라인(S1i-1)에 접속된다. 이와 같은 제4 트랜지스터(T4)는 i-1번째 제1 스캔 라인(S1i-1)으로 스캔 신호가 공급될 때 턴-온되어 제1 노드(N1)로 초기화 전원(Vint)의 전압을 공급한다.

제2 트랜지스터(T2)는 제m 데이터 라인(Dm)과 제1 트랜지스터(T1)의 제1 전극 사이에 접속된다. 그리고, 제2 트랜지스터(T2)의 게이트 전극은 i번째 제1 스캔 라인(S1i)에 접속된다. 이와 같은 제2 트랜지스터(T2)는 i번째 제1 스캔 라인(S1i)으로 스캔 신호가 공급될 때 턴-온되어 제m 데이터 라인(Dm)과 제1 트랜지스터(T1)의 제1 전극을 전기적으로 접속시킨다.

스토리지 커패시터(Cst)는 제1 전원(ELVDD)과 제1 노드(N1) 사이에 접속된다. 이와 같은 스토리지 커패시터(Cst)는 데이터 신호 및 제1 트랜지스터(T1)의 문턱전압에 대응하는 전압을 저장한다.