JPWO2013069045A1 - Thin film transistor device manufacturing method, thin film transistor device, and display device - Google Patents

Thin film transistor device manufacturing method, thin film transistor device, and display device Download PDFInfo

- Publication number

- JPWO2013069045A1 JPWO2013069045A1 JP2012518670A JP2012518670A JPWO2013069045A1 JP WO2013069045 A1 JPWO2013069045 A1 JP WO2013069045A1 JP 2012518670 A JP2012518670 A JP 2012518670A JP 2012518670 A JP2012518670 A JP 2012518670A JP WO2013069045 A1 JPWO2013069045 A1 JP WO2013069045A1

- Authority

- JP

- Japan

- Prior art keywords

- layer

- light absorption

- region

- absorption layer

- amorphous silicon

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000010409 thin film Substances 0.000 title claims abstract description 141

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 70

- 230000031700 light absorption Effects 0.000 claims abstract description 271

- 229910021417 amorphous silicon Inorganic materials 0.000 claims abstract description 209

- 229910021419 crystalline silicon Inorganic materials 0.000 claims abstract description 77

- 239000000758 substrate Substances 0.000 claims abstract description 64

- 239000010408 film Substances 0.000 claims description 160

- 238000000034 method Methods 0.000 claims description 68

- 230000020169 heat generation Effects 0.000 claims description 53

- 230000003287 optical effect Effects 0.000 claims description 38

- 238000010438 heat treatment Methods 0.000 claims description 36

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 33

- 229910052710 silicon Inorganic materials 0.000 claims description 33

- 239000010703 silicon Substances 0.000 claims description 33

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 25

- 239000012788 optical film Substances 0.000 claims description 25

- 239000004065 semiconductor Substances 0.000 claims description 24

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 23

- 239000000463 material Substances 0.000 claims description 18

- 238000009826 distribution Methods 0.000 claims description 17

- 230000010355 oscillation Effects 0.000 claims description 17

- 230000008033 biological extinction Effects 0.000 claims description 13

- 239000003795 chemical substances by application Substances 0.000 claims description 12

- 230000001678 irradiating effect Effects 0.000 claims description 11

- 239000004973 liquid crystal related substance Substances 0.000 claims description 8

- 238000011144 upstream manufacturing Methods 0.000 claims description 8

- 238000000137 annealing Methods 0.000 claims description 4

- 238000010030 laminating Methods 0.000 claims description 4

- 238000009792 diffusion process Methods 0.000 claims description 3

- 238000010521 absorption reaction Methods 0.000 abstract description 44

- 239000010410 layer Substances 0.000 description 864

- 238000002425 crystallisation Methods 0.000 description 40

- 238000010586 diagram Methods 0.000 description 34

- 230000008025 crystallization Effects 0.000 description 31

- 230000005540 biological transmission Effects 0.000 description 22

- 239000013078 crystal Substances 0.000 description 22

- 229910052751 metal Inorganic materials 0.000 description 19

- 239000002184 metal Substances 0.000 description 19

- 230000000694 effects Effects 0.000 description 14

- 229910052581 Si3N4 Inorganic materials 0.000 description 13

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 13

- 238000004364 calculation method Methods 0.000 description 11

- 238000004088 simulation Methods 0.000 description 11

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 10

- 238000002834 transmittance Methods 0.000 description 10

- 238000005224 laser annealing Methods 0.000 description 9

- 239000011651 chromium Substances 0.000 description 8

- 230000008569 process Effects 0.000 description 7

- 229910001182 Mo alloy Inorganic materials 0.000 description 6

- 230000008018 melting Effects 0.000 description 6

- 238000002844 melting Methods 0.000 description 6

- 229920006395 saturated elastomer Polymers 0.000 description 6

- 229910052804 chromium Inorganic materials 0.000 description 5

- 238000005530 etching Methods 0.000 description 5

- 229910052750 molybdenum Inorganic materials 0.000 description 5

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 5

- 230000000644 propagated effect Effects 0.000 description 5

- 238000004544 sputter deposition Methods 0.000 description 5

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 4

- 229910052799 carbon Inorganic materials 0.000 description 4

- 239000010949 copper Substances 0.000 description 4

- 239000007769 metal material Substances 0.000 description 4

- 238000009738 saturating Methods 0.000 description 4

- 239000010936 titanium Substances 0.000 description 4

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 3

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 3

- 238000007796 conventional method Methods 0.000 description 3

- 238000000151 deposition Methods 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 238000009413 insulation Methods 0.000 description 3

- 239000011733 molybdenum Substances 0.000 description 3

- PXHVJJICTQNCMI-UHFFFAOYSA-N nickel Substances [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 3

- 230000010287 polarization Effects 0.000 description 3

- 239000003870 refractory metal Substances 0.000 description 3

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 3

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- 239000010937 tungsten Substances 0.000 description 3

- 229910000838 Al alloy Inorganic materials 0.000 description 2

- 101100110009 Caenorhabditis elegans asd-2 gene Proteins 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- 229910000881 Cu alloy Inorganic materials 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- 229910001080 W alloy Inorganic materials 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 230000002301 combined effect Effects 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 239000007789 gas Substances 0.000 description 2

- 238000004093 laser heating Methods 0.000 description 2

- 239000013081 microcrystal Substances 0.000 description 2

- 239000010955 niobium Substances 0.000 description 2

- 239000002245 particle Substances 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- OFIYHXOOOISSDN-UHFFFAOYSA-N tellanylidenegallium Chemical compound [Te]=[Ga] OFIYHXOOOISSDN-UHFFFAOYSA-N 0.000 description 2

- 230000002123 temporal effect Effects 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- 238000002679 ablation Methods 0.000 description 1

- 229910052783 alkali metal Inorganic materials 0.000 description 1

- 150000001340 alkali metals Chemical class 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 239000012298 atmosphere Substances 0.000 description 1

- 239000002585 base Substances 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 238000005336 cracking Methods 0.000 description 1

- 238000006356 dehydrogenation reaction Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 239000007772 electrode material Substances 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 238000012423 maintenance Methods 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 238000003303 reheating Methods 0.000 description 1

- 238000009751 slip forming Methods 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- 230000009466 transformation Effects 0.000 description 1

- 238000001771 vacuum deposition Methods 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Landscapes

- Thin Film Transistor (AREA)

- Recrystallisation Techniques (AREA)

Abstract

本発明の薄膜トランジスタの製造方法等は、基板上に複数のゲート電極を形成する工程(S11)と、複数のゲート電極上にゲート絶縁層を形成する工程(S12)と、ゲート絶縁層上に非晶質性シリコン層を形成する工程(S13)と、非晶質性シリコン層上にバッファー層、光吸収層を形成する工程(S14)と、赤色または近赤外のレーザー光を用いて前記光吸収層を加熱させた熱により非晶質性シリコン層を結晶化させて結晶性シリコン層を生成する工程(S15)と、複数のゲート電極の各々に対応する結晶性シリコン層上の領域にソース電極及びドレイン電極を形成する工程(S20)と、を含み、ゲート絶縁層、非晶質性シリコン層の膜厚、バッファー層、及び、光吸収層の膜厚は、所定の条件式を満たすように形成される。The thin film transistor manufacturing method of the present invention includes a step of forming a plurality of gate electrodes on a substrate (S11), a step of forming a gate insulating layer on the plurality of gate electrodes (S12), A step (S13) of forming a crystalline silicon layer, a step (S14) of forming a buffer layer and a light absorption layer on the amorphous silicon layer, and the light using red or near infrared laser light. A step of crystallizing the amorphous silicon layer by heat generated by absorbing the absorption layer to generate a crystalline silicon layer (S15), and a source in a region on the crystalline silicon layer corresponding to each of the plurality of gate electrodes A step of forming an electrode and a drain electrode (S20), and the thickness of the gate insulating layer, the amorphous silicon layer, the thickness of the buffer layer, and the thickness of the light absorption layer satisfy a predetermined conditional expression. Formed.

Description

本発明は薄膜トランジスタ装置の製造方法、薄膜トランジスタ装置および表示装置に関する。 The present invention relates to a method for manufacturing a thin film transistor device, a thin film transistor device, and a display device.

例えば、液晶パネルまたは有機ELパネルを構成する薄膜トランジスタ(TFT:Thin Film Transistor)がある。薄膜トランジスタのチャネル部は、非晶質シリコンであるa−Siまたは結晶質で多結晶シリコンであるPoly−Siで形成されている。薄膜トランジスタのチャネル部の結晶質シリコン層(Poly−Si層)は、一般的に、非晶質シリコン層(a−Si層)を形成後、その非晶質シリコン層に例えばエキシマ等のレーザー光を照射して瞬間的に温度を上昇させて結晶化することにより、形成される。 For example, there is a thin film transistor (TFT) constituting a liquid crystal panel or an organic EL panel. The channel portion of the thin film transistor is formed of a-Si which is amorphous silicon or Poly-Si which is crystalline and polycrystalline silicon. For the crystalline silicon layer (Poly-Si layer) in the channel portion of the thin film transistor, generally, after forming an amorphous silicon layer (a-Si layer), laser light such as excimer is applied to the amorphous silicon layer. It is formed by irradiating and instantaneously raising the temperature to crystallize.

また、薄膜トランジスタの構造としては、ゲートメタルがチャネル部のx−Si(xは、aまたはPoly)からみて基板側に配置されているボトムゲート構造と、ゲートメタルおよびソース・ドレインメタルがチャネル部のx−Siからみて基板と反対方向に配置されているトップゲート構造とが存在する。ボトムゲート構造は、非晶質シリコン層で形成されたチャネル部を有するa−Si TFTで主に用いられており、トップゲート構造は、結晶質シリコン層で形成されたチャネル部を有するPoly−Si TFTで主に用いられている。なお、大面積の表示装置に用いられる液晶パネルまたは有機ELパネルを構成する薄膜トランジスタの構造としては、ボトムゲート構造が一般的である。 The structure of the thin film transistor includes a bottom gate structure in which the gate metal is disposed on the substrate side when viewed from the x-Si (x is a or poly) of the channel portion, and the gate metal and the source / drain metal of the channel portion. There is a top gate structure arranged in the direction opposite to the substrate as viewed from x-Si. The bottom gate structure is mainly used in an a-Si TFT having a channel portion formed of an amorphous silicon layer, and the top gate structure is a Poly-Si having a channel portion formed of a crystalline silicon layer. Mainly used in TFT. Note that a bottom gate structure is generally used as a structure of a thin film transistor included in a liquid crystal panel or an organic EL panel used in a large-area display device.

さらに、ボトムゲート構造でPoly−Si TFTが用いられる場合も存在し、その場合には、作製コストが抑えられるといった長所を持っている。このようなボトムゲート構造のPoly−Si TFTでは、非晶質シリコン層にレーザーが照射され結晶化されることで結晶質シリコン層が形成される。この手法(レーザーアニール結晶化法)では、レーザー光照射に基づく熱で非晶質シリコン層を結晶化させる。 Furthermore, there is a case where a Poly-Si TFT is used in a bottom gate structure, and in that case, there is an advantage that a manufacturing cost can be suppressed. In such a bottom-gate Poly-Si TFT, the amorphous silicon layer is irradiated with a laser and crystallized to form a crystalline silicon layer. In this method (laser annealing crystallization method), the amorphous silicon layer is crystallized by heat based on laser light irradiation.

レーザーアニール手法の1つとして、非晶質シリコン層上にバッファー層として、例えば酸化珪素層を堆積し、さらにバッファー層の上に光吸収層を堆積し、その吸収層に吸収され熱変換されるレーザー光を照射することにより、非晶質シリコンを間接的に加熱する手法がある。以下、この手法をレーザー間接加熱法という。 As one of laser annealing methods, a silicon oxide layer, for example, is deposited on an amorphous silicon layer as a buffer layer, and a light absorption layer is further deposited on the buffer layer, which is absorbed into the absorption layer and thermally converted. There is a method of indirectly heating amorphous silicon by irradiating a laser beam. Hereinafter, this method is referred to as a laser indirect heating method.

また、レーザー間接加熱法に用いるレーザーとしては、大出力化が可能で、かつ出力の時間安定性が高い赤色、及び近赤外の固定レーザーを用いるのが効果的である。なぜなら、レーザー光の強度に、時間的な変動が存在すると、結晶に均一な温度分布にならず、結晶化によって形成される結晶質シリコン層の結晶性がばらついてしまうが、エキシマレーザーは、エネルギーばらつき(時間的変動)などの問題によって均一な結晶化を図ることが難しいからである。また、固定レーザーは、ガスレーザーであるエキシマレーザーと比較して、メンテナンスコストも低減できるという生産上の利点もあるからである。 Further, as the laser used in the laser indirect heating method, it is effective to use red and near infrared fixed lasers capable of increasing the output and having high output time stability. This is because if there is a temporal variation in the intensity of the laser beam, the crystal will not have a uniform temperature distribution and the crystallinity of the crystalline silicon layer formed by crystallization will vary. This is because it is difficult to achieve uniform crystallization due to problems such as variations (temporal variations). In addition, the fixed laser has an advantage in production that the maintenance cost can be reduced as compared with the excimer laser which is a gas laser.

またレーザー間接加熱法に用いる光吸収層としては、その光学特性が、赤色、及び近赤外の波長、具体的には波長600nm以上2000nm以下の光に対する吸収が大きい特徴を有していることが望ましい。かつ、高温を伴うレーザーアニール結晶化プロセスに耐えうる熱特性も兼ね備えていることが望ましい。 In addition, the light absorption layer used in the laser indirect heating method has a characteristic that its optical characteristics have a large absorption for light of red and near-infrared wavelengths, specifically, wavelengths of 600 nm to 2000 nm. desirable. It is also desirable to have thermal properties that can withstand laser annealing crystallization processes involving high temperatures.

そのような特徴を有する光吸収層の一例として、高融点金属であるMoやCrがある。これらの高融点金属膜は、その消衰係数kが一般的に大きい(2以上)ため、安定に成膜でき、かつレーザー照射による加熱に耐えうる(1500度以上)膜厚では(10nm以上)では、入射したレーザー光に対して5%以下の透過率となる。そのため、下地の層構造による多重干渉の影響が無視できるようになり、下地の層構造によらず(例えば、ゲート電極の存在する領域と存在しない領域とで)、光吸収層の吸収率は一定になる。 As an example of the light absorption layer having such characteristics, there are Mo and Cr which are refractory metals. These refractory metal films generally have a large extinction coefficient k (2 or more), so that they can be stably formed and can withstand heating by laser irradiation (1500 degrees or more) (10 nm or more). Then, the transmittance is 5% or less with respect to the incident laser beam. Therefore, the influence of multiple interference due to the underlying layer structure can be ignored, and the absorption rate of the light absorption layer is constant regardless of the underlying layer structure (for example, the region where the gate electrode exists and the region where it does not exist). become.

しかし、有機ELパネルを構成する薄膜トランジスタには、特に均一な特性が求められるため、上記のレーザーアニール結晶化法をボトムゲート構造の薄膜トランジスタの製造に適用した場合には不都合(問題)が生じてしまう。具体的には、ボトムゲート構造の薄膜トランジスタでは、シリコンや絶縁膜に比して高い熱伝導率の金属材料でゲート電極が先に形成されて、その後に絶縁層及び非晶質シリコン層が形成される。さらに、形成された非晶質シリコン層上に光吸収層が形成された後、レーザー間接加熱法により、上方の光吸収層にレーザー光を照射して、その発熱により間接的に非晶質シリコン層をアニールして結晶化を行う。その結晶化の際、非晶質シリコン層の結晶化に費やされるはずの熱がゲート電極によって吸収、伝播されてしまい、非晶質シリコン層が十分に結晶化されずに結晶性の低下や不均一化が生じてしまう問題がある。 However, since the thin film transistors constituting the organic EL panel are required to have particularly uniform characteristics, inconvenience (problem) occurs when the laser annealing crystallization method is applied to the manufacture of a thin film transistor having a bottom gate structure. . Specifically, in a bottom gate thin film transistor, a gate electrode is first formed of a metal material having a higher thermal conductivity than silicon or an insulating film, and then an insulating layer and an amorphous silicon layer are formed. The Further, after the light absorption layer is formed on the formed amorphous silicon layer, the laser light is irradiated to the upper light absorption layer by the laser indirect heating method, and the amorphous silicon is indirectly indirectly generated by the heat generation. The layer is annealed for crystallization. During the crystallization, heat that should be spent on the crystallization of the amorphous silicon layer is absorbed and propagated by the gate electrode, and the amorphous silicon layer is not sufficiently crystallized. There is a problem that uniformity occurs.

それに対して、ゲート電極の近接領域すなわちチャネル近傍に、ダミーゲートパターンを配置させることにより、ゲート電極及びダミーゲートパターン上方にある非晶質シリコン層におけるそれぞれの熱容量の差を低減させる方法が開示されている(例えば、特許文献1)。また、レーザー光のスキャン上流側にゲート電極を伸長させることにより、伸長させたゲート電極の部分のプリアニール効果を利用して、レーザー光が薄膜トランジスタのゲート電極上方の光吸収層に到達する前に、ゲート電極を熱的に飽和させ、ゲート電極によるシリコン薄膜において発生した熱の吸収を軽減させる方法が開示されている(例えば特許文献2)。 In contrast, a method is disclosed in which a dummy gate pattern is disposed in the vicinity of the gate electrode, that is, in the vicinity of the channel, thereby reducing the difference in heat capacity between the gate electrode and the amorphous silicon layer above the dummy gate pattern. (For example, Patent Document 1). Also, by extending the gate electrode on the upstream side of the laser beam scan, the pre-annealing effect of the extended gate electrode portion is used before the laser beam reaches the light absorption layer above the gate electrode of the thin film transistor. A method of thermally saturating a gate electrode to reduce absorption of heat generated in a silicon thin film by the gate electrode is disclosed (for example, Patent Document 2).

しかしながら、上記従来の方法をレーザー間接加熱法に適用する場合、次に述べるような課題がある。すなわち、特許文献1及び文献2に開示の方法では、ゲート電極上方の光吸収層にレーザー光が到達する前にゲート電極を熱的に飽和させる手段として、ゲート電極周辺、及びゲート電極に接触して電極材料を配置する。そのため、ボトムゲート構造の薄膜トランジスタを用いてより高精細な表示装置を作製する場合には、ゲート電極パターンを密に配置することが困難になるという課題がある。さらに、上記特許文献2に開示の方法では、スキャン方向に対して薄膜トランジスタのチャネル方向が常に平行になるように薄膜トランジスタを配置しなければならないという制約が生じる。これは、表示装置の画素内の回路パターンの設計の自由度を著しく低減させてしまうため、より高精細な表示装置の作製をする場合には、深刻な課題となる。

However, when the conventional method is applied to the laser indirect heating method, there are the following problems. That is, in the methods disclosed in

また、非晶質シリコン層の結晶化を、上記のように、光吸収層を用いて行う場合、すなわち、光吸収層に赤色(または近赤外)の波長領域の連続発振(または擬似連続発振)のレーザーを照射・スキャンし、その発熱により間接的に行う場合、エキシマレーザーのスキャンによって行う場合とは異なる問題が生じる。具体的には、上記の結晶化を行うと、非晶質シリコン層における熱拡散長がより大きくなるので、ゲート電極による熱伝導の影響がより顕著になり、結晶化が不十分となる。これを、図1を用いて説明する。図1は、レーザーアニール結晶化法を可視光領域の固体レーザーのスキャンによって行った場合の結晶ムラを示す図である。 Further, when the crystallization of the amorphous silicon layer is performed using the light absorption layer as described above, that is, continuous oscillation (or quasi-continuous oscillation) in the red (or near infrared) wavelength region in the light absorption layer. ) When the laser is irradiated and scanned, and the heat is indirectly generated, a problem different from the case where the excimer laser is scanned is caused. Specifically, when the above crystallization is performed, the thermal diffusion length in the amorphous silicon layer becomes larger, so that the influence of heat conduction by the gate electrode becomes more remarkable, and the crystallization becomes insufficient. This will be described with reference to FIG. FIG. 1 is a diagram showing crystal unevenness when the laser annealing crystallization method is performed by scanning a solid-state laser in the visible light region.

図1の右図に示すように、結晶ムラは、スキャンの上流側(図中の右方向)に発生しているのがわかる。ここで、図1の左図は、図1の右図の複数のゲートメタルのうちの1つのゲートメタル上の非晶質シリコンに対する結晶化率を示す図である。図1の左図において、例えば結晶化率80%とは、粒径30nm〜40nmの結晶質シリコンであること表しており、例えば結晶化率40%とは、粒径10nm〜20nmの結晶質シリコンであること表している。したがって、図1の左図で示すように、結晶化が不十分(均一でない)である場合に結晶ムラが生じることがわかる。 As shown in the right diagram of FIG. 1, it can be seen that crystal unevenness occurs on the upstream side of the scan (right direction in the diagram). Here, the left figure of FIG. 1 is a figure which shows the crystallization ratio with respect to the amorphous silicon on one gate metal among the several gate metals of the right figure of FIG. In the left diagram of FIG. 1, for example, the crystallization rate of 80% indicates that the crystalline silicon has a particle size of 30 nm to 40 nm. For example, the crystallization rate of 40% indicates that the crystalline silicon has a particle size of 10 nm to 20 nm. It represents that. Accordingly, as shown in the left diagram of FIG. 1, it can be seen that crystal unevenness occurs when crystallization is insufficient (not uniform).

このように、レーザー間接加熱法により非晶質シリコン層の結晶化を行う場合、結晶化が不十分となるので、それを用いた薄膜トランジスタの特性の劣化、個々のトランジスタの特性の不均一化を生じてしまう問題がある。 As described above, when the amorphous silicon layer is crystallized by the laser indirect heating method, the crystallization becomes insufficient. Therefore, the characteristics of the thin film transistor using the amorphous silicon layer are deteriorated and the characteristics of the individual transistors are not uniform. There is a problem that occurs.

本発明は、上記の問題点を鑑みてなされたもので、赤色又は近赤外の波長領域のレーザーを用いて、結晶性の安定した結晶シリコン膜を形成することができる薄膜トランジスタ装置の製造方法、薄膜トランジスタ装置、それを用いた表示装置を提供することを目的とする。 The present invention has been made in view of the above problems, and a method of manufacturing a thin film transistor device capable of forming a crystalline silicon film having stable crystallinity using a laser in a red or near infrared wavelength region, It is an object to provide a thin film transistor device and a display device using the same.

上記目的を達成するために、本発明の一態様に係る薄膜トランジスタ装置の製造方法は、基板を準備する第1工程と、前記基板上に複数のゲート電極を形成する第2工程と、前記複数のゲート電極上にゲート絶縁層を形成する第3工程と、前記ゲート絶縁層上に非晶質シリコン層を積層する第4工程と、前記非晶質シリコン層上にバッファー層を形成する第5工程と、前記バッファー層上に光吸収層を形成する第6工程と、波長が600nm以上である所定のレーザーを前記基板に対して一定の方向に相対移動させて、前記所定のレーザーから照射されるレーザー光を用いて前記光吸収層を加熱させ、加熱により発生した熱により間接的に前記非晶質シリコン層を結晶化させて結晶性シリコン層を生成する第7工程と、前記複数のゲート電極の各々に対応する前記結晶性シリコン層上の領域にソース電極及びドレイン電極を形成する第8工程と、を含み、前記光吸収層の膜厚に前記光吸収層の屈折率を積算した値である前記光吸収層の光学膜厚を、前記レーザー光の波長で除算した値をXとし、前記バッファー層の膜厚に前記バッファー層の屈折率を積算した値である前記バッファー層の光学膜厚と、前記非晶質シリコン層の膜厚と前記非晶質シリコン層の屈折率を積算した値である前記非晶質シリコン層の光学膜厚と、前記ゲート絶縁層の膜厚と前記ゲート絶縁層の屈折率を積算した前記ゲート絶縁層の光学膜厚とを和算した値を前記レーザー光の波長で除算した値をYとし、さらに、前記光吸収層の密度をρ、比熱をcとし、前記ゲート電極の膜厚をdG、密度をρG、比熱をcGとし、前記ゲート電極の上方の光吸収層と前記ゲート電極の上方にない光吸収層の、前記レーザー光に対するそれぞれの光吸収率が等しいときの前記ゲート電極の吸収率の最大値をAGとし、(AG/dG)×(ρ×c)/(ρG×cG)の式にて算出される値をΔA’とおいたとき、前記ゲート絶縁層の膜厚、前記非晶質性シリコン層の膜厚、前記バッファー層の膜厚、及び、前記光吸収層の膜厚は、Y≦−1.06X−0.22ΔA’+1.07、Y≧1.29X+1.61*ΔA’+1.44、Y≧1.06X+0.33ΔA’+0.89、およびY≦1.29X+−0.97*ΔA’−0.95の式により区画される範囲に属する前記X、及び前記Yを満たす。 In order to achieve the above object, a method of manufacturing a thin film transistor device according to one embodiment of the present invention includes a first step of preparing a substrate, a second step of forming a plurality of gate electrodes on the substrate, and the plurality of the plurality of gate electrodes. A third step of forming a gate insulating layer on the gate electrode; a fourth step of stacking an amorphous silicon layer on the gate insulating layer; and a fifth step of forming a buffer layer on the amorphous silicon layer. And a sixth step of forming a light absorption layer on the buffer layer, and a predetermined laser having a wavelength of 600 nm or more is moved relative to the substrate in a certain direction and irradiated from the predetermined laser. A seventh step of generating a crystalline silicon layer by heating the light absorption layer using laser light and indirectly crystallizing the amorphous silicon layer by heat generated by the heating; and the plurality of gate electrodes An eighth step of forming a source electrode and a drain electrode in a region on the crystalline silicon layer corresponding to each, and a value obtained by integrating the refractive index of the light absorption layer to the film thickness of the light absorption layer A value obtained by dividing the optical film thickness of the light absorbing layer by the wavelength of the laser beam is X, and the optical film thickness of the buffer layer, which is a value obtained by adding the refractive index of the buffer layer to the film thickness of the buffer layer; The film thickness of the amorphous silicon layer and the optical film thickness of the amorphous silicon layer, which is a value obtained by integrating the refractive index of the amorphous silicon layer, the film thickness of the gate insulating layer, and the gate insulating layer The value obtained by summing the optical film thickness of the gate insulating layer obtained by integrating the refractive index of the above is divided by the wavelength of the laser light as Y, and the density of the light absorption layer is ρ and the specific heat is c, The thickness of the gate electrode is dG, the density is ρG, and the specific heat is c. And the maximum value of the absorptance of the gate electrode when the light absorptivity of the light absorption layer above the gate electrode and the light absorption layer not above the gate electrode with respect to the laser light is equal to AG, When the value calculated by the equation of (AG / dG) × (ρ × c) / (ρG × cG) is ΔA ′, the film thickness of the gate insulating layer and the film thickness of the amorphous silicon layer The film thickness of the buffer layer and the film thickness of the light absorption layer are Y ≦ −1.06X−0.22ΔA ′ + 1.07, Y ≧ 1.29X + 1.61 * ΔA ′ + 1.44, Y ≧ 1.06 + 0.33ΔA ′ + 0.89 and Y ≦ 1.29X + −0.97 * ΔA′−0.95 satisfy the X and Y belonging to the range defined by the equation.

本発明によれば、赤色または近赤外のレーザーを用いて、結晶性の安定した結晶シリコン膜を形成することができる薄膜トランジスタ装置の製造方法、薄膜トランジスタ、それを用いた表示装置を実現することができる。具体的には、前記シリコン薄膜、ゲート絶縁層、バッファー層、及び、赤色及び近赤外の波長領域のレーザー光に対して所定の光学特性を有する光吸収層を、それぞれの膜厚が所定の条件を満足するように形成することにより、例えば、ゲート電極のパターン形状等、特に薄膜トランジスタ装置の構造に変更を加えることなく、赤色又は及び近赤外のレーザーを用いたレーザー間接加熱法により、結晶性の安定した結晶シリコン層を形成することができる薄膜トランジスタ装置の製造方法、薄膜トランジスタ装置、それを用いた表示装置を実現することができる。 According to the present invention, it is possible to realize a thin film transistor device manufacturing method, a thin film transistor, and a display device using the thin film transistor device capable of forming a crystalline silicon film with stable crystallinity using a red or near infrared laser. it can. Specifically, the silicon thin film, the gate insulating layer, the buffer layer, and the light absorption layer having predetermined optical characteristics with respect to laser light in the red and near-infrared wavelength regions each having a predetermined film thickness. By forming the electrode so as to satisfy the conditions, for example, the crystal shape by the laser indirect heating method using a red or near-infrared laser without changing the structure of the thin film transistor device, such as the pattern shape of the gate electrode. Thin film transistor device manufacturing method, thin film transistor device, and display device using the same can be realized.

第1の態様の薄膜トランジスタ装置の製造方法は、基板を準備する第1工程と、前記基板上に複数のゲート電極を形成する第2工程と、前記複数のゲート電極上にゲート絶縁層を形成する第3工程と、前記ゲート絶縁層上に非晶質シリコン層を積層する第4工程と、前記非晶質シリコン層上にバッファー層を形成する第5工程と、前記バッファー層上に光吸収層を形成する第6工程と、波長が600nm以上である所定のレーザーを前記基板に対して一定の方向に相対移動させて、前記所定のレーザーから照射されるレーザー光を用いて前記光吸収層を加熱させ、加熱により発生した熱により間接的に前記非晶質シリコン層を結晶化させて結晶性シリコン層を生成する第7工程と、前記複数のゲート電極の各々に対応する前記結晶性シリコン層上の領域にソース電極及びドレイン電極を形成する第8工程と、を含み、前記光吸収層の膜厚に前記光吸収層の屈折率を積算した値である前記光吸収層の光学膜厚を、前記レーザー光の波長で除算した値をXとし、前記バッファー層の膜厚に前記バッファー層の屈折率を積算した値である前記バッファー層の光学膜厚と、前記非晶質シリコン層の膜厚と前記非晶質シリコン層の屈折率を積算した値である前記非晶質シリコン層の光学膜厚と、前記ゲート絶縁層の膜厚と前記ゲート絶縁層の屈折率を積算した前記ゲート絶縁層の光学膜厚とを和算した値を前記レーザー光の波長で除算した値をYとし、さらに、前記光吸収層の密度をρ、比熱をcとし、前記ゲート電極の膜厚をdG、密度をρG、比熱をcGとし、前記ゲート電極の上方の光吸収層と前記ゲート電極の上方にない光吸収層の、前記レーザー光に対するそれぞれの光吸収率が等しいときの前記ゲート電極の吸収率の最大値をAGとし、(AG/dG)×(ρ×c)/(ρG×cG)の式にて算出される値をΔA’とおいたとき、前記ゲート絶縁層の膜厚、前記非晶質性シリコン層の膜厚、前記バッファー層の膜厚、及び、前記光吸収層の膜厚は、下記の式1)から式4)により区画される範囲に属する前記X、及び前記Yを満たす。ここで、式1)Y≦−1.06X−0.22ΔA’+1.07、式2)Y≧1.29X+1.61*ΔA’+1.44、式3)Y≧1.06X+0.33ΔA’+0.89、式4)Y≦1.29X+−0.97*ΔA’−0.95。 In the method of manufacturing the thin film transistor device according to the first aspect, a first step of preparing a substrate, a second step of forming a plurality of gate electrodes on the substrate, and forming a gate insulating layer on the plurality of gate electrodes. A third step, a fourth step of laminating an amorphous silicon layer on the gate insulating layer, a fifth step of forming a buffer layer on the amorphous silicon layer, and a light absorbing layer on the buffer layer And a sixth step of forming a light source, a predetermined laser having a wavelength of 600 nm or more is moved relative to the substrate in a predetermined direction, and the light absorption layer is formed using laser light emitted from the predetermined laser. A seventh step of heating and indirectly crystallizing the amorphous silicon layer by heat generated by the heating to generate a crystalline silicon layer; and the crystalline silicon corresponding to each of the plurality of gate electrodes An eighth step of forming a source electrode and a drain electrode in the upper region, and an optical film thickness of the light absorption layer, which is a value obtained by integrating a refractive index of the light absorption layer to a film thickness of the light absorption layer. The value obtained by dividing the wavelength of the laser beam by X is the optical film thickness of the buffer layer, which is a value obtained by adding the refractive index of the buffer layer to the film thickness of the buffer layer, and the film of the amorphous silicon layer. The gate insulation obtained by integrating the optical thickness of the amorphous silicon layer, which is a value obtained by integrating the thickness and the refractive index of the amorphous silicon layer, and the thickness of the gate insulating layer and the refractive index of the gate insulating layer. A value obtained by adding the optical film thickness of the layer divided by the wavelength of the laser beam is Y, and the density of the light absorption layer is ρ, the specific heat is c, and the film thickness of the gate electrode is dG, The density is ρG, the specific heat is cG, and the light absorption above the gate electrode is AG is the maximum value of the absorptance of the gate electrode when the light absorptivity of the light absorption layer not above the layer and the gate electrode is equal to the laser light, and (AG / dG) × (ρ × c ) / (ΡG × cG) when the value calculated by ΔA ′ is set to ΔA ′, the thickness of the gate insulating layer, the thickness of the amorphous silicon layer, the thickness of the buffer layer, and The film thickness of the light absorption layer satisfies X and Y belonging to a range defined by the following formulas 1) to 4). Here, Formula 1) Y ≦ −1.06X−0.22ΔA ′ + 1.07, Formula 2) Y ≧ 1.29X + 1.61 * ΔA ′ + 1.44, Formula 3) Y ≧ 1.06X + 0.33ΔA ′ + 0 .89, Formula 4) Y ≦ 1.29X + −0.97 * ΔA′−0.95.

本態様によれば、ゲート絶縁膜、チャネル層となる非晶質性シリコン層、バッファー層、及び、赤色及び近赤外の波長領域のレーザー光に対して所定の光学特性を有する光吸収層の膜厚が前記上記条件を満たすことにより、1)前記ゲート電極の上方(以下、第1領域、と記述する)の光吸収層の光吸収率より前記ゲート電極の上方にない(以下、第2領域、と記述する)光吸収層の光吸収率が大きく設定され、且つ、2)前記ゲート電極の上方のシリコン層の発熱温度を、前記非晶質性シリコン層の融点より大きく設定することが可能になる。 According to this aspect, the gate insulating film, the amorphous silicon layer serving as the channel layer, the buffer layer, and the light absorption layer having predetermined optical characteristics with respect to laser light in the red and near-infrared wavelength regions. When the film thickness satisfies the above conditions, 1) it is not above the gate electrode (hereinafter referred to as the second region) due to the light absorption rate of the light absorption layer above the gate electrode (hereinafter referred to as the first region). 2) the light absorption rate of the light absorption layer is set to be large, and 2) the heat generation temperature of the silicon layer above the gate electrode is set to be larger than the melting point of the amorphous silicon layer. It becomes possible.

従って、先ず、1)の効果より、前記光吸収層の発熱を受けて、前記第2領域の非晶質性シリコン層の発熱は、前記第1領域の非晶質性シリコン層の発熱より大きくなる。これにより、前記レーザー光が照射され始める第1領域の光吸収層の始端部に、前記所定のレーザーから照射されるレーザー光が到達する前に、前記第2領域上方の光吸収層にて発生する熱が予め前記ゲート電極に伝播され、前記ゲート電極が熱的に飽和した状態となる。 Therefore, first, due to the effect of 1), the heat generation of the amorphous silicon layer in the second region is larger than the heat generation of the amorphous silicon layer in the first region due to the heat generation of the light absorption layer. Become. As a result, before the laser light emitted from the predetermined laser reaches the start end of the light absorption layer in the first region where the laser light starts to be emitted, it is generated in the light absorption layer above the second region. The heat to be transmitted is propagated to the gate electrode in advance, and the gate electrode is in a state of being thermally saturated.

その結果、前記レーザー光が照射され始める前記ゲート電極の始端部から、前記レーザー光が照射され終わる前記ゲート電極の終端部にかけて、前記第1領域の光吸収層より発生した熱が前記ゲート電極により吸収される割合を低減できるので、前記第1領域の非晶質性シリコン層の発熱温度分布をほぼ均一に制御できる。これにより、前記非晶質性シリコン層を結晶化した結晶性シリコン層内に生成される結晶組織をほぼ均一に制御できる。 As a result, heat generated from the light absorption layer in the first region from the start end portion of the gate electrode where the laser beam starts to be irradiated to the end portion of the gate electrode where the laser beam ends being irradiated is caused by the gate electrode. Since the rate of absorption can be reduced, the heat generation temperature distribution of the amorphous silicon layer in the first region can be controlled almost uniformly. Thereby, the crystal structure generated in the crystalline silicon layer obtained by crystallizing the amorphous silicon layer can be controlled almost uniformly.

さらに、2)の効果より、前記第2領域の光吸収層の光吸収率が、前記第1領域の光吸収層の光吸収率より過度に大きい場合、即ち、前記第2領域の光吸収層の発熱が、前記第1領域の光吸収層の発熱より極端に大きくなった場合においても、前記第1領域及び前記第2領域の非晶質性シリコンが溶融し溶融シリコンとなることによって、その熱伝導率が、一般的にゲート電極として用いられる金属の熱伝導率と同程度の値まで増加する。 Furthermore, from the effect of 2), when the light absorption rate of the light absorption layer in the second region is excessively larger than the light absorption rate of the light absorption layer in the first region, that is, the light absorption layer in the second region. Even when the heat generation of the first region and the light absorption layer in the first region is extremely larger than that of the first region, the amorphous silicon in the first region and the second region is melted to form molten silicon. The thermal conductivity increases to a value comparable to that of a metal generally used as a gate electrode.

よって、前記第2領域の溶融したシリコン層より発生した熱は、前記ゲート絶縁層を介して前記ゲート電極に伝播するよりも、前記第1領域の溶融したシリコン層へ伝播するようになるので、前記第2領域の溶融したシリコン層より発生した熱が前記ゲート電極へと過度に伝播することは無い。故に、前記ゲート電極の発熱温度の分布が悪化することは無くなるので、前記ゲート電極の発熱温度の分布の悪化に伴う前記第一領域のシリコン層の発熱温度分布の均一性の低下は避けられる。 Therefore, heat generated from the molten silicon layer in the second region propagates to the molten silicon layer in the first region, rather than to the gate electrode through the gate insulating layer. The heat generated from the molten silicon layer in the second region does not excessively propagate to the gate electrode. Therefore, since the distribution of the heat generation temperature of the gate electrode is not deteriorated, the uniformity of the heat generation temperature distribution of the silicon layer in the first region accompanying the deterioration of the heat generation temperature distribution of the gate electrode can be avoided.

以上により、上記1)と2)の複合効果により、前記非晶質性シリコン層を結晶化した結晶性シリコン層内に生成される結晶組織の均一性が保持され、その結果、前記レーザー光が照射され始めた前記ゲート電極の始端部に対応する結晶性シリコン層から、前記レーザー光が照射され終わる前記ゲート電極の終端部に対応する結晶性シリコン層にかけて、前記結晶性シリコン層内の結晶率のバラツキが抑制された薄膜トランジスタ装置を実現できる。 As described above, the uniformity of the crystal structure generated in the crystalline silicon layer obtained by crystallizing the amorphous silicon layer is maintained by the combined effect of the above 1) and 2). The crystal ratio in the crystalline silicon layer from the crystalline silicon layer corresponding to the start end portion of the gate electrode that has started to be irradiated to the crystalline silicon layer corresponding to the end portion of the gate electrode that has been irradiated with the laser light. Thus, a thin film transistor device in which the variation is suppressed can be realized.

第2の態様の薄膜トランジスタ装置の製造方法として、前記光吸収層は、前記所定のレーザー光の波長範囲において半透明(消衰係数k<1)である。 As a method of manufacturing the thin film transistor device according to the second aspect, the light absorption layer is translucent (extinction coefficient k <1) in the wavelength range of the predetermined laser beam.

第3の態様の薄膜トランジスタ装置の製造方法として、前記第7工程後、且つ、前記第8工程前において、少なくとも前記光吸収層を除去する工程を含む。 The method of manufacturing the thin film transistor device according to the third aspect includes a step of removing at least the light absorption layer after the seventh step and before the eighth step.

第4の態様の薄膜トランジスタ装置の製造方法として、前記第7工程後、且つ、前記第8工程前において、前記バッファー層及び前記光吸収層を除去する工程を含む。 The method of manufacturing the thin film transistor device according to the fourth aspect includes a step of removing the buffer layer and the light absorption layer after the seventh step and before the eighth step.

第5の態様の薄膜トランジスタ装置の製造方法として、前記第6工程において、前記所定のレーザーは、連続発振または擬似連続発振モードの発振モードで前記レーザー光を照射する。 As a method of manufacturing a thin film transistor device according to a fifth aspect, in the sixth step, the predetermined laser irradiates the laser beam in an oscillation mode of a continuous oscillation mode or a pseudo continuous oscillation mode.

第6の態様の薄膜トランジスタ装置の製造方法として、前記所定のレーザーは、固体レーザー装置で構成される。 As a method of manufacturing the thin film transistor device according to the sixth aspect, the predetermined laser is a solid-state laser device.

第7の態様の薄膜トランジスタ装置の製造方法としては、前記所定のレーザーは、半導体レーザー素子を用いたレーザー装置で構成される。 According to a seventh aspect of the thin film transistor device manufacturing method, the predetermined laser is a laser device using a semiconductor laser element.

第8の態様の薄膜トランジスタ装置の製造方法としては、前記第6工程において、前記レーザー光の前記非晶質性シリコン層上における照射エネルギー密度の変動は、5%程度未満である。 As a method of manufacturing the thin film transistor device according to the eighth aspect, in the sixth step, the fluctuation of the irradiation energy density of the laser light on the amorphous silicon layer is less than about 5%.

第9の態様の薄膜トランジスタ装置の製造方法としては、前記所定のレーザーの波長は、600nm〜2000nmである。 In the method of manufacturing the thin film transistor device according to the ninth aspect, the wavelength of the predetermined laser is 600 nm to 2000 nm.

第10の態様の薄膜トランジスタ装置の製造方法として、前記第2工程は、前記基板上に酸化シリコンからなるアンダーコート層を形成する工程と、前記アンダーコート層上に複数のゲート電極を形成する工程とを含む。 As a method of manufacturing a thin film transistor device according to a tenth aspect, the second step includes a step of forming an undercoat layer made of silicon oxide on the substrate, and a step of forming a plurality of gate electrodes on the undercoat layer. including.

第11の態様の薄膜トランジスタは、基板と、前記基板上に形成された複数のゲート電極と、前記複数のゲート電極上に形成されたゲート絶縁層と、前記ゲート絶縁層上に形成された結晶性シリコン層と、前記複数のゲート電極の各々に対応する前記結晶性シリコン層上の領域に形成されたソース電極及びドレイン電極とを備え、前記結晶性シリコン層は、前記ゲート絶縁層上に非晶質性シリコン層を形成後、前記非晶質シリコン層上にバッファー層を形成し、前記バッファー層上に所定の光学特性を有する光吸収層を形成し、波長が600nm以上2000nm以下である所定のレーザーを前記基板に対して一定の方向に相対移動させて、前記所定のレーザーから照射されるレーザー光を用いて前記光吸収層にレーザー光を吸収させ発生した熱により、前記バッファー層を介して間接的に非晶質性シリコン層をアニールし結晶化させて生成され、前記光吸収層の膜厚に前記光吸収層の屈折率を積算した値である前記光吸収層の光学膜厚を、前記レーザー光の波長で除算した値をXとし、前記バッファー層の膜厚に前記バッファー層の屈折率を積算した値である前記バッファー層の光学膜厚と、前記非晶質シリコン層の膜厚と前記非晶質シリコン層の屈折率を積算した値である前記非晶質シリコン層の光学膜厚と、前記ゲート絶縁層の膜厚と前記ゲート絶縁層の屈折率を積算した前記ゲート絶縁層の光学膜厚とを和算した値を前記レーザー光の波長で除算した値をYとし、さらに、前記光吸収層の密度をρ、比熱をcとし、前記ゲート電極の膜厚をdG、密度をρG、比熱をcGとし、前記ゲート電極の上方の光吸収層と前記ゲート電極の上方にない光吸収層の、前記レーザー光に対するそれぞれの光吸収率が等しいときの前記ゲート電極の吸収率の最大値をAG、とし、(AG/dG)×(ρ×c)/(ρG×cG)の式にて算出される値をΔA’とおいたとき、前記ゲート絶縁層の膜厚、前記非晶質性シリコン層の膜厚、前記バッファー層の膜厚、及び、前記光吸収層の膜厚は、下記の式1)から式4)により区画される範囲に属する前記X、及び前記Yを満たす。ここで、式1)Y≦−1.06X−0.22ΔA’+1.07、式2)Y≧1.29X+1.61*ΔA’+1.44、式3)Y≧1.06X+0.33ΔA’+0.89、式4)Y≦1.29X+−0.97*ΔA’−0.95。 A thin film transistor according to an eleventh aspect includes a substrate, a plurality of gate electrodes formed on the substrate, a gate insulating layer formed on the plurality of gate electrodes, and a crystallinity formed on the gate insulating layer. A silicon layer; and a source electrode and a drain electrode formed in a region on the crystalline silicon layer corresponding to each of the plurality of gate electrodes, wherein the crystalline silicon layer is amorphous on the gate insulating layer. After forming the crystalline silicon layer, a buffer layer is formed on the amorphous silicon layer, a light absorption layer having predetermined optical characteristics is formed on the buffer layer, and the wavelength is 600 nm or more and 2000 nm or less. It is generated by moving the laser relative to the substrate in a certain direction and absorbing the laser light in the light absorption layer using the laser light emitted from the predetermined laser. Heat is generated by indirectly annealing and crystallizing the amorphous silicon layer through the buffer layer, and is a value obtained by integrating the refractive index of the light absorption layer to the film thickness of the light absorption layer. The optical film thickness of the light absorbing layer is X divided by the wavelength of the laser beam, and the optical film thickness of the buffer layer, which is a value obtained by adding the refractive index of the buffer layer to the film thickness of the buffer layer, The film thickness of the amorphous silicon layer and the optical film thickness of the amorphous silicon layer, which is a value obtained by integrating the refractive index of the amorphous silicon layer, the film thickness of the gate insulating layer, and the thickness of the gate insulating layer The value obtained by summing the optical film thickness of the gate insulating layer integrated with the refractive index divided by the wavelength of the laser light is Y, and the density of the light absorption layer is ρ, the specific heat is c, The thickness of the gate electrode is dG, the density is ρG, and the specific heat is cG. The maximum value of the absorptance of the gate electrode when the light absorptivity of the light absorbing layer above the gate electrode and the light absorbing layer not above the gate electrode with respect to the laser beam is equal is AG, AG / dG) × (ρ × c) / (ρG × cG) where the value calculated by ΔA ′ is the thickness of the gate insulating layer, the thickness of the amorphous silicon layer, The film thickness of the buffer layer and the film thickness of the light absorption layer satisfy X and Y belonging to the range defined by the following formulas 1) to 4). Here, Formula 1) Y ≦ −1.06X−0.22ΔA ′ + 1.07, Formula 2) Y ≧ 1.29X + 1.61 * ΔA ′ + 1.44, Formula 3) Y ≧ 1.06X + 0.33ΔA ′ + 0 .89, Formula 4) Y ≦ 1.29X + −0.97 * ΔA′−0.95.

第12の態様の表示装置は、液晶パネルまたはELパネルを含む表示装置であって、前記表示装置は、第11の態様に記載の薄膜トランジスタを備え、前記薄膜トランジスタは、前記液晶パネルまたはELパネルを駆動させる。 A display device according to a twelfth aspect is a display device including a liquid crystal panel or an EL panel, and the display device includes the thin film transistor according to the eleventh aspect, and the thin film transistor drives the liquid crystal panel or the EL panel. Let

第13の態様の表示装置として、前記ELパネルは、有機ELパネルである。 As a display device according to a thirteenth aspect, the EL panel is an organic EL panel.

第14の態様の薄膜トランジスタ装置の製造方法は、基板を準備する第1工程と、前記基板上に複数のゲート電極を形成する第2工程と、前記複数のゲート電極上にゲート絶縁層を形成する第3工程と、前記ゲート絶縁層上に非晶質シリコン層を積層する第4工程と、前記非晶質シリコン層上にバッファー層を形成する第5工程と、前記バッファー層上に光吸収層を形成する第6工程と、波長が600nm以上である所定のレーザーを前記基板に対して一定の方向に相対移動させて、前記所定のレーザーから照射されるレーザー光を用いて前記光吸収層を加熱させ、発生した熱により間接的に前記非晶質シリコン層を結晶化させて結晶性シリコン層を生成する第7工程と、前記バッファー層及び光吸収層を除去する第8工程と、前記複数のゲート電極の各々に対応する前記結晶性シリコン層上の領域にソース電極及びドレイン電極を形成する第9工程と、を含み、前記第2工程、前記第3工程、前記第4工程、前記第5工程、及び前記第6工程では、前記第7工程において、前記レーザー光を用いて前記光吸収層を照射した際の、前記ゲート電極外の前記所定のレーザーの相対移動方向の上流領域での前記光吸収層の最高到達温度が、前記レーザー光を用いて前記光吸収層を照射した際の前記ゲート電極上の領域での前記非晶質性シリコン層の最高到達温度より高くなるように、且つ、前記ゲート電極上の領域内では、前記所定のレーザー光を用いて前記光吸収層を照射した際の前記光吸収層の最高到達温度がほぼ一定になるように、構成される。 In a thin film transistor device manufacturing method according to a fourteenth aspect, a first step of preparing a substrate, a second step of forming a plurality of gate electrodes on the substrate, and forming a gate insulating layer on the plurality of gate electrodes. A third step, a fourth step of laminating an amorphous silicon layer on the gate insulating layer, a fifth step of forming a buffer layer on the amorphous silicon layer, and a light absorbing layer on the buffer layer And a sixth step of forming a light source, a predetermined laser having a wavelength of 600 nm or more is moved relative to the substrate in a predetermined direction, and the light absorption layer is formed using laser light emitted from the predetermined laser. A seventh step of heating and indirectly crystallizing the amorphous silicon layer with the generated heat to generate a crystalline silicon layer; an eighth step of removing the buffer layer and the light absorption layer; No A ninth step of forming a source electrode and a drain electrode in a region on the crystalline silicon layer corresponding to each of the first electrode, the second step, the third step, the fourth step, and the fifth step In the step and the sixth step, in the seventh step, in the upstream region in the relative movement direction of the predetermined laser outside the gate electrode when the light absorption layer is irradiated using the laser beam. The highest temperature of the light absorption layer is higher than the highest temperature of the amorphous silicon layer in the region on the gate electrode when the light absorption layer is irradiated using the laser beam; and In the region on the gate electrode, the maximum absorption temperature of the light absorption layer when the light absorption layer is irradiated using the predetermined laser beam is substantially constant.

第15の態様の薄膜トランジスタ装置の製造方法として、前記第3工程、前記第4工程、前記第5工程、前記第6工程及び前記第7工程では、前記第8工程において、前記レーザー光を用いて前記光吸収層を照射した際の、前記ゲート電極外の前記所定のレーザー光の相対移動方向の上流領域での前記光吸収層の最高到達温度が、前記レーザー光を用いて前記光吸収層を照射した際の前記ゲート電極上の領域での前記光吸収層の最高到達温度より高くなるように、且つ、前記ゲート電極上の領域内では、前記所定のレーザー光を用いて前記光吸収層を照射した際の前記光吸収層の最高到達温度がほぼ一定になるように、前記ゲート絶縁層の膜厚、前記非晶質シリコン層の膜厚、前記バッファー層の膜厚、及び、前記光吸収層の膜厚が構成される。 As a method of manufacturing a thin film transistor device according to a fifteenth aspect, in the third step, the fourth step, the fifth step, the sixth step, and the seventh step, the laser light is used in the eighth step. When the light absorption layer is irradiated, the highest temperature of the light absorption layer in the upstream region in the relative movement direction of the predetermined laser light outside the gate electrode is determined by using the laser light. In the region on the gate electrode, the light absorbing layer is formed by using the predetermined laser beam so that the temperature is higher than the highest temperature of the light absorbing layer in the region on the gate electrode when irradiated. The film thickness of the gate insulating layer, the film thickness of the amorphous silicon layer, the film thickness of the buffer layer, and the light absorption so that the maximum temperature reached by the light absorption layer upon irradiation is substantially constant. Layer thickness is composed .

第16の態様の薄膜トランジスタ装置の製造方法は、基板を準備する第1工程と、前記基板上にゲート電極を形成する第2工程と、前記ゲート電極上にゲート絶縁層を形成する第3工程と、前記ゲート絶縁層上に半導体材料を含む半導体材料層を形成する第4工程と、前記半導体材料層上にバッファー層を形成する第5工程と、前記バッファー層上に所定の光学定数を有する光吸収層を形成する第6工程と、前記光吸収層に対して波長が600nm以上2000nm以下である所定のレーザー光を照射し、前記光吸収層にレーザー光を吸収させ、前記光吸収層から発生した熱により、バッファー層を介して間接的に前記半導体材料層を結晶化させて結晶質の半導体層を生成する第7工程と、前記ゲート電極に対応する領域である第1領域とは異なる、前記ゲート電極に対応しない領域である第2領域における前記半導体層上に、ソース電極及びドレイン電極を形成する第8工程と、を含み、前記第3工程、前記第4工程、前記第5工程及び前記第6工程において、前記光吸収層の前記第2領域での単位体積あたりの発熱量が、前記光吸収層の前記第1領域での単位体積あたりの発熱量よりも大きくなるように前記ゲート絶縁層、前記半導体材料層、前記バッファー層及び前記光吸収層を形成することにより、前記第7工程において、前記所定のレーザー光が照射されることによって発熱した前記第1領域の前記光吸収層から、前記ゲート電極に対して熱伝導して、前記ゲート電極に吸収されている熱分を、第2領域の前記半導体材料層に対して熱拡散することを抑えて蓄熱させた状態にさせ、かつ、発熱している前記第1領域の前記光吸収層において、等しい温度分布を有する部位を形成させて、前記半導体材料層を結晶化させる。 A method of manufacturing a thin film transistor device according to a sixteenth aspect includes a first step of preparing a substrate, a second step of forming a gate electrode on the substrate, and a third step of forming a gate insulating layer on the gate electrode. A fourth step of forming a semiconductor material layer including a semiconductor material on the gate insulating layer, a fifth step of forming a buffer layer on the semiconductor material layer, and light having a predetermined optical constant on the buffer layer. A sixth step of forming an absorption layer, and irradiating the light absorption layer with a predetermined laser beam having a wavelength of 600 nm or more and 2000 nm or less, causing the light absorption layer to absorb the laser beam and generating from the light absorption layer A seventh step of generating a crystalline semiconductor layer by indirectly crystallization of the semiconductor material layer through a buffer layer by the heat, and a first region that is a region corresponding to the gate electrode, An eighth step of forming a source electrode and a drain electrode on the semiconductor layer in the second region which is a region not corresponding to the gate electrode, and includes the third step, the fourth step, and the fifth step. In the step and the sixth step, the heat generation amount per unit volume in the second region of the light absorption layer is larger than the heat generation amount per unit volume in the first region of the light absorption layer. By forming the gate insulating layer, the semiconductor material layer, the buffer layer, and the light absorption layer, in the seventh step, the light in the first region generated by irradiation with the predetermined laser light. Heat is transferred from the absorption layer to the gate electrode, and the heat absorbed in the gate electrode is stored in the second region while suppressing thermal diffusion to the semiconductor material layer. Is a, and in the light absorbing layer of the first region that generates heat, to form a portion having an equal temperature distribution, thereby crystallizing the semiconductor material layer.

第17の態様の薄膜トランジスタ装置の製造方法として、前記第3工程、前記第4工程、前記第5工程及び前記第6工程では、前記光吸収層の前記第2領域での単位体積あたりの発熱量が、前記光吸収層の前記第1領域での単位体積あたりの発熱量よりも大きくなるように、前記ゲート絶縁層の膜厚、前記非晶質シリコン層の膜厚、前記バッファー層の膜厚及び前記光吸収層が構成される。 As a manufacturing method of a thin film transistor device according to a seventeenth aspect, in the third step, the fourth step, the fifth step, and the sixth step, the heat generation amount per unit volume in the second region of the light absorption layer Is larger than the calorific value per unit volume in the first region of the light absorption layer, the film thickness of the gate insulating layer, the film thickness of the amorphous silicon layer, the film thickness of the buffer layer And the said light absorption layer is comprised.

第18の態様の薄膜トランジスタ装置の製造方法として、前記光吸収層の前記第2領域は、前記第7工程における前記所定のレーザー光の前記基板に対する相対移動方向において、前記第1領域に対して上流領域および下流領域に対応している。 As a method of manufacturing a thin film transistor device according to an eighteenth aspect, the second region of the light absorption layer is upstream of the first region in the relative movement direction of the predetermined laser beam with respect to the substrate in the seventh step. It corresponds to the region and the downstream region.

第19の態様の薄膜トランジスタ装置の製造方法として、前記第3工程、前記第4工程、前記第5工程及び前記第6工程では、前記第7工程において、前記第2領域における単位体積あたりの発熱量が、前記第1領域における単位体積あたりの発熱量に比べて、前記ゲート電極の単位体積あたりの発熱量以上大きくなるように、構成される。 As a method of manufacturing a thin film transistor device according to a nineteenth aspect, in the third step, the fourth step, the fifth step, and the sixth step, the heat generation amount per unit volume in the second region in the seventh step However, the heat generation amount per unit volume in the first region is larger than the heat generation amount per unit volume of the gate electrode.

第20の態様の薄膜トランジスタ装置の製造方法として、前記第3工程、前記第4工程、前記第5工程及び前記第6工程では、前記第7工程において、前記光吸収層の前記第1領域に形成される前記等しい温度分布を有する部位における大きさが、前記第1領域に対して0.8以上1.0以下となるように構成される。 As a method of manufacturing a thin film transistor device according to a twentieth aspect, in the third step, the fourth step, the fifth step, and the sixth step, in the seventh step, the light absorption layer is formed in the first region. The size of the portion having the same temperature distribution is configured to be 0.8 or more and 1.0 or less with respect to the first region.

以下、本発明の実施形態を、図面を参照しながら説明する。 Embodiments of the present invention will be described below with reference to the drawings.

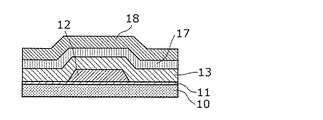

図2は、本発明の実施の形態に係る有機発光表示装置を構成する薄膜トランジスタの構造を示す断面図である。 FIG. 2 is a cross-sectional view illustrating a structure of a thin film transistor constituting the organic light emitting display device according to the embodiment of the present invention.

図2に示す薄膜トランジスタ100は、ボトムゲート構造の薄膜トランジスタであり、基板10と、アンダーコート層11と、ゲート電極12と、ゲート絶縁層13と、結晶質シリコン層17と、非晶質シリコン層18と、n+シリコン層19と、ソース・ドレイン電極20とを備える。

A

基板10は、例えば透明なガラスまたは石英からなる絶縁基板である。

The

アンダーコート層11は、基板10上に形成され、例えば窒化珪素(SiNx)層、酸化珪素(SiOx)層、及びその積層等から構成される。ここで、アンダーコート層11は、1.5<x<2.0の酸化珪素(SiOx)で、300nm以上1500nm以下の膜厚で構成されるのが好ましい。より好ましいアンダーコート層11の膜厚範囲は、500nm以上1000nm以下である。これは、アンダーコート層11の厚みを厚くすると基板10への熱負荷を低減できるが、厚すぎると膜剥がれやクラックが発生しまうことによる。The

ゲート電極12は、アンダーコート層11上に形成され、典型的にはモリブデン(Mo)等の金属やMo合金等(例えばMoW(モリブデン・タングステン合金))の金属からなる。なお、ゲート電極12は、シリコンの融点温度に耐えられる金属であればよいので、W(タングステン)、Ta(タンタル)、Nb(ニオブ)、Ni(ニッケル)、Cr(クロム)およびMoを含むこれらの合金からなるとしてもよい。ゲート電極12の膜厚は、好ましくは30nm以上〜300nm以下であり、より好ましくは、50nm以上〜100nm以下である。これは、ゲート電極12の膜厚が薄いと、ゲート電極12の透過率が増加してしまい、以下に記すレーザー光の反射が低下しやすくなるからである。また、ゲート電極12の膜厚が厚いと以下に説明するゲート絶縁層13のカバレッジが低下してしまい、特にはゲート電極の端部でゲート絶縁膜が段切れすることでゲート電極12とn+シリコン層19とが電気的に導通してしまうなど、薄膜トランジスタ100の特性が劣化しやすくなるからである。

The

ゲート絶縁層13は、ゲート電極12を覆うように形成され、例えば酸化珪素層、もしくは窒化珪素層の単層構造、または、酸化珪素層及び窒化珪素層の積層構造からなる。ゲート絶縁層13の膜厚は、単層構造及び積層構造それぞれにおいて、レーザー間接加熱結晶化法により結晶質シリコン層17を形成する場合に好適な範囲がある。この好適な範囲は、一定の関係式で表現される。この一定の関係式の詳細については、後述する。

The

結晶質シリコン層17は、ゲート絶縁層13上に形成され、多結晶のシリコン層(Poly−Si層)からなる。なお、この結晶質シリコン層17は、次のように形成される。すなわち、まず、ゲート絶縁層13上にa−Siからなる非晶質シリコン層14(不図示)を形成後、その非晶質シリコン層14上に、例えば酸化珪素膜からなるバッファー層15を堆積する。さらにバッファー層15上にレーザー光を吸収して発熱する光吸収層16(例えば、ダイヤモンドライクカーボン膜)を堆積後、レーザー光により光吸収層を照射加熱する。このように、光吸収層の熱により間接的に非晶質シリコン層14が加熱されて非晶質シリコン層14を多結晶質化(微結晶化も含む)することにより結晶質シリコン層17が形成される。

The

ここで、多結晶とは、50nm以上の結晶からなる狭義の意味での多結晶だけでなく、50nm以下の結晶からなる狭義の意味での微結晶を含んだ広義の意味としている。以下、多結晶を広義の意味として記載する。 Here, the term “polycrystal” has a broad meaning including not only a polycrystal in a narrow sense consisting of crystals of 50 nm or more but also a microcrystal in a narrow sense consisting of crystals of 50 nm or less. Hereinafter, polycrystal is described in a broad sense.

なお、レーザー照射に用いられるレーザー光源は、可視光領域のうち赤色または近赤外領域の波長のレーザーである。この赤色または近赤外領域の波長のレーザーは、600nm〜2000nmの波長のレーザーであり、好ましくは800nm〜1100nmの波長のレーザーである。 Note that the laser light source used for laser irradiation is a laser having a wavelength in the red or near infrared region of the visible light region. The laser having a wavelength in the red or near infrared region is a laser having a wavelength of 600 nm to 2000 nm, and preferably a laser having a wavelength of 800 nm to 1100 nm.

この赤色または近赤外領域の波長領域のレーザーは、連続発振または擬似連続の発振モードであればよい。その理由は、このレーザーが連続発振または擬似連続の発振モード以外の発信モードのパルス発振モードである場合、レーザー光は光吸収層16に対して時間的に非連続に照射されることになるため、光吸収層16の発熱状態を時間的に連続的に保持できない。そのため、非晶質シリコン層14を常時溶融状態に保持することできない。また、擬似連続の発振モードも含まれる理由は、非晶質シリコン層14がその融点以下まで冷却しないうちにパルスを光吸収層16に照射し再加熱させることにより、その溶融状態を維持できるからである。すなわち、擬似連続発振モードの好ましい態様は、非晶質シリコン層14がその融点以下まで冷却しないうちにパルスを光吸収層16に照射し再加熱させることができ、かつ、その高温状態を維持できるものである。また、赤色または近赤外領域の波長領域のレーザーは、固体レーザー装置であってもよく、半導体レーザー素子を用いたレーザー装置であってもよい。いずれにせよ、レーザー光を精度良く制御できるため好ましい。さらに、結晶ムラのない結晶質シリコン層17を形成するためには、光吸収層16上に照射したときの赤色または近赤外領域の波長領域のレーザーは、照射エネルギー密度の変動が5%程度未満であれば好ましい。結晶ムラのない結晶質シリコン層17を形成することにより、薄膜トランジスタの当初設計特性が達成でき、また、特性の均一化が実現できることとなる。

The laser in the red or near-infrared wavelength region may be in a continuous oscillation or quasi-continuous oscillation mode. The reason is that when the laser is in a pulse oscillation mode other than the continuous oscillation mode or the pseudo continuous oscillation mode, the laser light is irradiated to the

非晶質シリコン層18は、結晶質シリコン層17上に形成されている。なお、このようにして、薄膜トランジスタ100は、結晶質シリコン層17に非晶質シリコン層18が積層された構造のチャネル層を有する。

The

n+シリコン層19は、非晶質シリコン層18と結晶質シリコン層17の側面とゲート絶縁層13とを覆うように形成されている。

The n +

ソース・ドレイン電極20は、n+シリコン層19上に形成され、例えばMo、若しくはMo合金などの金属、チタニウム(Ti)、アルミニウム(Al)若しくはAl合金などの金属、銅(Cu)若しくはCu合金などの金属、または、銀(Ag)、クロム(Cr)、タンタル(Ta)若しくはタングステン(W)等の金属の材料からなる。

The source /

以上のように薄膜トランジスタ100は、構成されている。

As described above, the

図3は、本発明の実施の形態に係る表示装置の等価回路を示す図である。 FIG. 3 is a diagram showing an equivalent circuit of the display device according to the embodiment of the present invention.

図3に示す有機発光表示装置は、スイッチングトランジスタ1と、駆動トランジスタ2と、データ線3と、走査線4と、電流供給線5と、キャパシタンス6と、有機EL素子7とを備える。

The organic light emitting display device shown in FIG. 3 includes a switching

スイッチングトランジスタ1は、データ線3と走査線4とキャパシタンス6とに接続されている。

The switching

駆動トランジスタ2は、例えば図2に示す薄膜トランジスタ100に相当し、電流供給線5とキャパシタンス6と有機EL素子7とに接続されている。

The drive transistor 2 corresponds to, for example, the

データ線3は、有機EL素子7の画素の明暗を決めるデータ(電圧値の大小)が、有機EL素子7の画素に伝達される配線である。

The

走査線4は、有機EL素子7の画素のスイッチ(ON/OFF)を決めるデータが有機EL素子7の画素に伝達される配線である。

The

電流供給線5は、駆動トランジスタ2に大きな電流を供給するための配線である。

The

キャパシタンス6は、電圧値(電荷)を一定時間保持する。

The

以上のようにして有機発光表示装置は構成されている。 The organic light emitting display device is configured as described above.

次に、上述した薄膜トランジスタ100の製造方法について説明する。

Next, a method for manufacturing the above-described

図4は、本発明の実施の形態に係る有機発光表示装置の薄膜トランジスタの製造工程を示すフローチャートである。この薄膜トランジスタ100は同時に複数製造されるが、以下では、説明を簡単にするため、1つの薄膜トランジスタを製造する方法として説明する。図5A〜図5Lは、本発明の実施の形態に係る有機発光表示装置の薄膜トランジスタの製造方法を説明するための図である。図6は、図4のS15におけるレーザー間接加熱法を模式的に示した図である。

FIG. 4 is a flowchart showing a manufacturing process of a thin film transistor of the organic light emitting display device according to the embodiment of the present invention. A plurality of the

まず、基板10を準備し、基板10上に、アンダーコート層11を形成し(S10)、続いて、アンダーコート層11上にゲート電極を形成する(S11)。

First, the

具体的には、基板10上にプラズマCVD(Chemical Vapor Deposition:気相成長)法により、アンダーコート層11を成膜し、続いて、スパッタ法によりゲート電極となる金属膜を堆積し、フォトリソグラフィーおよびエッチングにより薄膜トランジスタ100におけるゲート電極12を形成する(図5A)。ここで、ゲート電極12は、典型的にはMo等あるいはMo合金等(例えばMoW(モリブデン・タングステン合金))の金属材料で形成される。

Specifically, an

次に、ゲート電極12上にゲート絶縁層13を形成する(S12)。そして、ゲート絶縁層13上に非晶質シリコン層14を形成する(S13)。

Next, the

具体的には、プラズマCVD法により、ゲート電極12の上にすなわちアンダーコート層11とゲート電極12とを覆うように、ゲート絶縁層13を成膜し(図5B)、成膜したゲート絶縁層13上に非晶質シリコン層14を連続的に成膜する(図5C)。

Specifically, a

次に、非晶質シリコン層14上に、バッファー層15を堆積し、堆積したバッファー層15上に、光吸収層16を堆積する(S14)。

Next, the

ここで、バッファー層15は、非晶質シリコン層14をアニールし結晶化する温度領域(1400度以上)においても、シリコンと反応しない物質であることが好ましい。このような物質として例えば、酸化珪素、窒化珪素などがある。また、バッファー層15の堆積は、プラズマCVD法により、ゲート絶縁層13及び非晶質シリコン層14を堆積した後、成膜チャンバーを大気開放することなく、連続的に成膜するのが望ましい。また、バッファー層15の厚さは例えば、5nm〜500nmであり、好ましくは30nm〜400nmである。理由は、5nm以下の膜厚は制御性が悪く、生産上不都合だからである。また500nm以上の膜厚は、レーザー照射にて加熱された光吸収層からの熱の伝わりが悪化し、非晶質シリコン層の結晶化に要する光エネルギーが過剰となってしまうからである。

Here, the

また、光吸収層16は、所定の光学特性を有しており、赤色または近赤外領域のレーザー光波長範囲において半透明(消衰係数k<1)となるよう成膜されることが望ましい。光吸収層16は、真空蒸着法、またはスパッタ法を用いて成膜される。例えば、スパッタ法を用いた場合、カーボンターゲットを使用し、スパッタガスとしてAr等を用いる。ここで、光吸収層16の厚さは、例えば、10nm〜500nmであり、好ましくは20nm〜200nmである。理由は、10nmの膜厚ではレーザー光の透過が大きく、光吸収層に吸収されるエネルギーが低下し、光吸収層の発熱が不十分となってしまうためである。また、500nmの膜厚では、膜自体の応力増大によりクラックの発生確率が高くなってしまい、またクラックが発生した光吸収層にレーザー照射と実施するとアブレーションが起きやすくなり、レーザー間接加熱プロセスには適さないからである。

The

光吸収層16は、上記所定の光学特性を有することにより、入射したレーザー光のある割合が下層に透過し、下層膜で多重干渉が生じる。それにより、光吸収層16の吸収率が、ゲート電極の存在する領域と存在しない領域で差が生じる。言い換えると、上記所定の光学特性を有する光吸収層16を用いることにより、光吸収層16におけるゲート電極が存在する領域とゲート電極が存在しない領域との吸収率を制御できる。なお、このような所定の光学特性を有する光吸収層16は、例えば、ダイヤモンドライクカーボン膜で構成される。

Since the

以下、ゲート絶縁層13の膜厚、非晶質シリコン層14の膜厚、バッファー層15の膜厚、及び光吸収層16の膜厚について、説明する。

Hereinafter, the thickness of the

ゲート絶縁層13、非晶質シリコン層14、バッファー層15、及び光吸収層16の膜厚は、以下の(式1)から(式4)により区画される範囲に属するX、及びYを満たすように形成されるのが好ましい。

The film thicknesses of the

Y≦−1.06X−0.22ΔA’+1.07 (式1)

Y≧1.29X+1.61*ΔA’+1.44 (式2)

Y≧1.06X+0.33ΔA’+0.89 (式3)

Y≦1.29X+−0.97*ΔA’−0.95 (式4)Y ≦ −1.06X−0.22ΔA ′ + 1.07 (Formula 1)

Y ≧ 1.29X + 1.61 * ΔA ′ + 1.44 (Formula 2)

Y ≧ 1.06X + 0.33ΔA ′ + 0.89 (Formula 3)

Y ≦ 1.29X + −0.97 * ΔA′−0.95 (Formula 4)

ここで、Xは光吸収層16の屈折率に光吸収層16の膜厚を乗算した光吸収層16の光学膜厚を所定のレーザー光の波長にて除算した値を表す。一方、Yはゲート絶縁層13の屈折率にゲート絶縁層13の膜厚を乗算したゲート絶縁層13の光学膜厚と、非晶質シリコン層14の屈折率に非晶質シリコン層14の膜厚を乗算した非晶質シリコン層14の光学膜厚と、バッファー層15の屈折率とバッファー層15の膜厚を乗算したバッファー層15の光学膜厚とを和算した値を所定のレーザー光の波長にて除算した値を表す。

Here, X represents a value obtained by dividing the optical film thickness of the

より具体的には、ゲート電極12が形成されている領域(以下、第1領域と呼ぶ)の上方の光吸収層16のレーザー光に対する吸収率をA1とし、その吸収率A1を光吸収層16の膜厚d1で商算(除算)したものを換算吸収率A1’とする。ゲート電極12が形成されていない領域(以下、第2領域と呼ぶ)の上方の光吸収層16のレーザー光に対する光吸収率をA2とし、その吸収率A2を光吸収層16の膜厚d2で商算したものを換算吸収率A2’とする。そのとき、その差A1’−A2’は、後述の説明で定義される値−ΔA’以下である。すなわち、S12、S13およびS14において、(式5)という関係式を成立させる膜厚を有するゲート絶縁層13、非晶質シリコン層14、バッファー層15、及び光吸収層16を形成する。More specifically, the absorption rate of the

A1’−A2’ ≦−ΔA’ (式5)A 1 ′ −A 2 ′ ≦ −ΔA ′ (Formula 5)

なお、詳細は後述するため、ここでの説明を省略するが、光吸収層16の吸収率は、光吸収層16の膜厚及び光学定数、バッファー層15の膜厚及び光学定数、非晶質シリコン層14の膜厚及び光学定数、ゲート絶縁層13の構成、膜厚及び光学定数、さらに下地のゲート電極12を形成する金属材料の光学定数及び基板の光学定数をパラメータとして、レーザー光の多重干渉を考慮した光学計算により導かれる。以下、再び製造工程の説明に戻る。

In addition, although description is omitted here for details, the absorption rate of the

次に、赤色または近赤外領域の波長領域のレーザーにより、光吸収層16を照射・加熱し、その発熱により非晶質シリコン層14をアニールすることで結晶質シリコン層17にする(S15)。

Next, the

具体的には、波長が600nm以上2000nm以下であるレーザーを基板10に対して一定の方向に相対移動させて、このレーザーから照射されるレーザー光を用いて光吸収層16を加熱させ、バッファー層15を介して間接的に非晶質シリコン層14をアニールし結晶化させて結晶質シリコン層17を生成する。より具体的には、先ず、形成された非晶質シリコン層14に対して脱水素処理を実施する。例えば、500℃20分間で、窒素雰囲気中で実施する方法がある。その後、非晶質シリコン層14をレーザー間接加熱法により、多結晶質(微結晶を含む)にすることにより結晶質シリコン層17を形成する(図5D)。

Specifically, a laser having a wavelength of 600 nm or more and 2000 nm or less is moved relative to the

ここで、上記レーザーアニール法において、レーザー照射に用いられるレーザー光源は、上述したように、赤色または近赤外の波長領域のレーザーである。すなわち、約600nm〜2000nmの波長のレーザーであり、好ましくは800nm〜1100nmの波長のレーザーである。また、赤色または近赤外の波長領域のレーザーは、連続発振または擬似連続の発振モードであればよい。また、この波長領域のレーザーは、固体レーザー装置で構成されていてもよく、半導体レーザー素子を用いたレーザー装置で構成されていてもよい。さらに、この波長領域のレーザーは、非晶質シリコン層14上に照射したときの照射エネルギー密度の変動が5%程度未満である。

Here, in the laser annealing method, as described above, the laser light source used for laser irradiation is a laser in a red or near-infrared wavelength region. That is, a laser having a wavelength of about 600 nm to 2000 nm, preferably a laser having a wavelength of 800 nm to 1100 nm. The laser in the red or near infrared wavelength region may be in a continuous oscillation or quasi-continuous oscillation mode. Further, the laser in this wavelength region may be constituted by a solid-state laser device, or may be constituted by a laser device using a semiconductor laser element. Further, in the laser in this wavelength region, the fluctuation of the irradiation energy density when irradiated on the

また、S15の工程すなわち図5Dから図5Eの工程では、図6に示すように、線状に集光されたレーザー光が、非晶質シリコン層14に照射されることで結晶質シリコン層17を生成する。レーザー光を非晶質シリコン層14に照射する方法は、具体的には2つの方法がある。1つは線状に集光されたレーザー光の照射位置は固定され、かつ、非晶質シリコン層14が形成された基板10がステージに載せられており、ステージが移動する方法がある。もう1つは、ステージは固定され、レーザー光の照射位置が移動する方法である。何れの方法においても、レーザー光が光吸収層16に対して相対的に移動しながら照射される。このような方法でレーザー光を照射された光吸収層16は、レーザー光のエネルギーを吸収して温度上昇する。そして、その熱が、バッファー層15を介して、非晶質シリコン層14に伝播し、非晶質シリコン層14がアニールされ結晶化される。このようにして非晶質シリコン層は結晶質シリコン層17になる。

In the step of S15, that is, the steps of FIG. 5D to FIG. 5E, the

次に、光吸収層16、及びバッファー層15をエッチングにより除去する。具体的には、ドライエッチング、またはウェットエッチングにより除去する。なお、光吸収層16、及びバッファー層15は必ずしも除去する必要はない。光吸収層16及びバッファー層15をチャネルエッチストッパ(Channel Etching Stopper:CES)として利用してもよいし、光吸収層のみエッチングして、バッファー層をCESとして利用してもよい。

Next, the

次に、2層目の非晶質シリコン層18を形成し(S17)、薄膜トランジスタ100のチャネル領域のシリコン層をパターニングする(S18)。

Next, a second

具体的には、プラズマCVD法により、ゲート絶縁層13上に、2層目の非晶質シリコン層18を形成する(図5G)。そして、薄膜トランジスタ100のチャネル領域が残るようにシリコン層膜層(結晶質シリコン層17および2層目の非晶質シリコン層18の層)をパターニングし、除去すべき非晶質シリコン層18と結晶質シリコン層17とをエッチングにより除去する(図5H)。それにより、薄膜トランジスタ100において所望のチャネル層を形成することができる。

Specifically, a second

次に、n+シリコン層19とソース・ドレイン電極20とを成膜する(S19)。

Next, an n +

具体的には、プラズマCVD法により、2層目の非晶質シリコン層18と結晶質シリコン層17の側面とゲート絶縁層13とを覆うようにn+シリコン層19を成膜する(図5I)。そして、成膜したn+シリコン層19上に、スパッタ法によりソース・ドレイン電極20となる金属が堆積される(図5J)。ここで、ソース・ドレイン電極は、Mo若しくはMo合金などの金属、チタニウム(Ti)、アルミニウム(Al)若しくはAl合金などの金属、銅(Cu)若しくはCu合金などの金属、または、銀(Ag)、クロム(Cr)、タンタル(Ta)若しくはタングステン(W)等の金属の材料で形成される。

Specifically, an n +

次に、ソース・ドレイン電極20のパターニングを行う(S20)。そして、n+シリコン層19をエッチングし(S21)、その過程で、2層目の非晶質シリコン層18を一部エッチングする(S22)。

Next, the source /

具体的には、ソース・ドレイン電極20をフォトリソグラフィーおよびエッチングにより形成する(図5K)。また、n+シリコン層19をエッチングし、薄膜トランジスタ100のチャネル領域の非晶質シリコン層18を一部エッチングする(図5L)。言い換えると、非晶質シリコン層18は、薄膜トランジスタ100のチャネル領域の非晶質シリコン層18を一部残すようにチャネルエッチングされる。

Specifically, the source /

このようにして、薄膜トランジスタ100は製造される。

In this way, the

以上のように、本実施の形態における薄膜トランジスタ100は、ボトムゲート構造を有するPoly−Si TFTとして形成される。この薄膜トランジスタ100の製造時には、ゲート絶縁層13、非晶質シリコン層14、バッファー層15、及び光吸収層16を、上述した関係式を成立させる膜厚を有するように成膜する。そして、a−Si膜からなる非晶質シリコン層14を、レーザー光を光吸収層16に対して照射・スキャンすることにより生ずる熱によりアニールして結晶化することで、非晶質シリコン層14をPoly−Siからなる結晶質シリコン層17にする。このとき、薄膜トランジスタ100が形成されるチャネル領域(ゲート電極上の領域)の上方の光吸収層16にレーザー光が到達する前にゲート電極12を熱的に飽和させた状態とすることができ、最終的に得るチャネル領域に相当する結晶質シリコン層17の結晶化を均一に行うことができる。

As described above, the

つまり、ゲート絶縁層13、非晶質シリコン層14、バッファー層15、及び光吸収層16の膜厚に、レーザーアニール結晶化法により結晶質シリコン層17を形成する場合に好適な範囲があるということである。

In other words, the film thickness of the

以下、このメカニズムについて説明する。 Hereinafter, this mechanism will be described.

一般的に、非晶質シリコン層を加熱によりアニールした場合、その到達温度と結晶化後の結晶質シリコン層の結晶度とには相関がある。到達温度が高いほど、結晶化後に形成された結晶質シリコン層の結晶度は大きくなる。そこで、薄膜トランジスタの第1領域(ゲート電極が形成されている領域の上方)における非晶質シリコン層を充分かつ均一に結晶化を図るために、薄膜トランジスタの第1領域における非晶質シリコン層の到達温度の分布を均一にすることが必要となる。 Generally, when an amorphous silicon layer is annealed by heating, there is a correlation between the temperature reached and the crystallinity of the crystalline silicon layer after crystallization. The higher the temperature reached, the higher the crystallinity of the crystalline silicon layer formed after crystallization. Therefore, in order to sufficiently and uniformly crystallize the amorphous silicon layer in the first region of the thin film transistor (above the region where the gate electrode is formed), the arrival of the amorphous silicon layer in the first region of the thin film transistor is reached. It is necessary to make the temperature distribution uniform.

しかしながら、ボトムゲート構造の薄膜トランジスタにおいては、非晶質シリコン層の下部にゲート絶縁層を挟んでゲート電極が存在し、かつ、ゲート電極を構成する金属の熱伝導率がゲート絶縁層の熱伝導率に比べて大きい。そのため、レーザー間接加熱法において、非晶質シリコン層の上方にバッファー層を介して形成された光吸収層へレーザー光を照射することによって発生した光吸収層の熱は、非晶質シリコン層を加熱する。また、それと同時に、上記熱は瞬時にゲート絶縁層を介してゲート電極へと伝播してしまう。その結果、ゲート電極が形成されている領域上方の非晶質シリコン層では発熱が不十分となる領域が生じ、その到達温度が不均一となる。このような理由により、図1に示すような結晶化後の結晶質シリコン層の結晶度のムラ(結晶ムラ)が生じる。 However, in a bottom-gate thin film transistor, a gate electrode exists under the amorphous silicon layer with the gate insulating layer interposed therebetween, and the thermal conductivity of the metal constituting the gate electrode is the thermal conductivity of the gate insulating layer. Bigger than Therefore, in the laser indirect heating method, the heat of the light absorption layer generated by irradiating the light absorption layer formed above the amorphous silicon layer via the buffer layer with the laser light is applied to the amorphous silicon layer. Heat. At the same time, the heat instantly propagates to the gate electrode through the gate insulating layer. As a result, a region where heat generation is insufficient occurs in the amorphous silicon layer above the region where the gate electrode is formed, and the temperature reached is nonuniform. For this reason, unevenness in crystallinity (crystal unevenness) of the crystalline silicon layer after crystallization as shown in FIG. 1 occurs.

したがって、この結晶ムラが生じてしまう現象を回避するためには、薄膜トランジスタの第1領域上方の光吸収層にレーザー光が到達する前に、後述するように、ゲート電極を熱的に飽和させた状態にするのが望ましい。そこで、本実施の形態では、上述した薄膜トランジスタ100の構成となるように製造する。すなわち、ゲート絶縁層13、非晶質シリコン層14、バッファー層及光吸収層の膜厚を上述したXおよびYを満たすように形成する。それにより、ゲート電極12が形成されていない領域上方(第2領域)の光吸収層16の発熱をゲート電極12が形成されている領域上方(第1領域)の光吸収層16の発熱より大きくすることができる。

Therefore, in order to avoid the phenomenon that the crystal unevenness occurs, the gate electrode is thermally saturated as described later before the laser beam reaches the light absorption layer above the first region of the thin film transistor. It is desirable to be in a state. Therefore, in this embodiment, the

換言すると、本実施の形態に係る薄膜トランジスタ100の構成となる、ゲート絶縁層13、非晶質シリコン層14、バッファー層、及び非晶質シリコン層膜の膜厚を上述したXおよびYを満たすように形成する。それにより、まず、レーザー光の照射によりゲート電極12が形成されていない領域上方(第2領域)の光吸収層16において発生した熱は、ゲート電極12が形成されている領域上方(第1領域)の光吸収層16にレーザー光が到達する前に、バッファー層15、非晶質シリコン層14、ゲート絶縁層13をそれぞれ介して、ゲート電極12に伝わりゲート電極12の温度を上昇させる。つまり、ゲート電極12は、まず、レーザー光が到達する前に予備加熱されることとなる。これは、第2領域にある光吸収層16にレーザー光が照射されて熱が発生すると、上記構成により、第2領域の温度が、未だレーザー光が到達していない第1領域上方の光吸収層16の温度より高くなるため、第2領域にある非晶質シリコン層14に伝播した熱が、さらにゲート絶縁膜を介してゲート電極12にも伝播し、ゲート電極12の温度を上昇させるからである。次に、レーザー光が第1領域上方の光吸収層16に到達すると、第1領域上方の光吸収層16が発熱し、その熱が非晶質シリコン層14に伝播する。さらに、第1領域での光吸収層16の発熱量に対応した熱がゲート電極12に伝わる(レーザー光による加熱)。ゲート電極12は、このレーザー光による加熱と上記の予備加熱との両方により加熱されて、ゲート電極12を熱的に飽和される。ここで、ゲート電極12を熱的に飽和させるとは、ゲート電極12の面内でゲート電極12の温度が均一化されていることを意味する。

In other words, the film thicknesses of the

このように、本実施の形態に係る薄膜トランジスタの構成によれば、非晶質シリコン層14を結晶化する際に、ゲート電極12を熱的に飽和することができる。それにより、非晶質シリコン層14を結晶化するためのレーザー光照射による光吸収層の発熱が、ゲート電極12に吸収されてしまうことなく、結晶質シリコン層17を形成するために用いられ、結晶ムラのない結晶質シリコン層17を生成することができるという効果を奏する。

Thus, according to the configuration of the thin film transistor according to the present embodiment, the

次に、ΔA’の算出方法について説明する。上述したように、ゲート電極12が形成されている領域上方(第1領域)、及びゲート電極12が形成されていない領域上方(第2領域)それぞれの光吸収層16のレーザー光に対する換算吸収率の差が−ΔA’以下になることにより、本実施の形態に係る効果が得られる。

Next, a method for calculating ΔA ′ will be described. As described above, the equivalent absorptance with respect to laser light of the

ここで、光吸収層16で吸収されるレーザー光の光吸収エネルギーの100%が光吸収層の発熱に寄与すると仮定し、レーザー光の単位面積当たりのエネルギーをエネルギー密度Eとする。以下では、ゲート電極12が形成されている領域上方(第1領域)の光吸収層16を第1領域の光吸収層16と呼び、ゲート電極12が形成されていない領域上方(第2領域)の光吸収層16を第2領域の光吸収層16と呼ぶ。また、第1領域の光吸収層16のレーザー光の波長に対する吸収率をA1、レーザー光を吸収したことによる光吸収層16の発熱量(単位面積当たり)をQ1とする。第2領域の光吸収層16のレーザー光の波長に対する吸収率をA2、レーザー光を吸収したことによる光吸収層16の発熱量(単位面積当たり)をQ2とする。さらに、ゲート電極12上にゲート絶縁層13が形成されており、さらにその上に非晶質シリコン層が形成されており、さらにその上にバッファー層が形成されている本構成において、ゲート電極12のレーザー光吸収率をAG、レーザー光を吸収したことによるゲート電極12の発熱量(単位面積当たり)をQGとする。Here, it is assumed that 100% of the light absorption energy of the laser light absorbed by the

次に、ゲート絶縁層13、非晶質シリコン層14、バッファー層15、及び光吸収層16を所定の膜厚にすることで、第1領域の光吸収層16のレーザー光の波長に対する吸収率と第2領域の光吸収層16のレーザー光の波長に対する吸収率が等しくなる場合を考える。すなわち、A1=A2が成立する場合を考える。その場合には、Q1=Q2が成立する。しかし、実際には光吸収層16を透過した光はゲート電極12にも吸収されてゲート電極も発熱する(QG>0)。そのために第1領域の非晶質シリコン層14の発熱温度は第2領域の非晶質シリコン層14の発熱温度より大きくなる。Next, by setting the

以上を鑑みると、第2領域の光吸収層16の発熱量が第1領域の光吸収層16の発熱量とゲート電極の発熱量との総和以上であれば、第2領域の非晶質シリコン層14の発熱温度が第1領域の非晶質シリコン層14の発熱温度以上になると考えられる。この関係は、(式6)で示すことができる。

In view of the above, if the heat generation amount of the

Q1+QG≦Q2 (式6)Q 1 + Q G ≦ Q 2 (Formula 6)

そして、この(式6)を変形すると、(式7)のように表すことができる。 And if this (Formula 6) is deformed, it can be expressed as (Formula 7).

Q1−Q2≦−QG (式7)Q 1 −Q 2 ≦ −Q G (Formula 7)

ここで、光吸収層16の膜厚、密度、比熱をそれぞれd、ρ、c、ゲート電極の膜厚、密度、比熱をそれぞれdG、ρG、cGと定義すると、第1領域の光吸収層16の発熱量、第2領域の光吸収層16の発熱量およびゲート電極の発熱量はそれぞれ、以下のように表すことができる。Here, when the film thickness, density, and specific heat of the

Q1=E×A1/(d×ρ×c)

Q2=E×A2/(d×ρ×c)

QG=E×AG/(dG×ρG×cG)Q 1 = E × A 1 / (d × ρ × c)

Q 2 = E × A 2 / (d × ρ × c)

Q G = E × A G / (d G × ρ G × c G )

次に、これらの式を(式7)に代入して整理すると、(式8)のようになる。 Next, when these equations are substituted into (Equation 7) and rearranged, (Equation 8) is obtained.

(A1−A2)/d≦−(AG/dG)×(ρ×c)/(ρG×cG) (式8)(A 1 −A 2 ) / d ≦ − (A G / d G ) × (ρ × c) / (ρ G × c G ) (Formula 8)

ここで、吸収率を膜厚で商算したものを換算吸収率と定義し、A1/d=A1’、A2/d=A2’と以下では記載する。さらに(式8)の右辺を−ΔA’と定義する。すると、(式7)は、A1’−A2’≦−ΔA’となり、(式5)が導かれる。Here, the absorption rate divided by the film thickness is defined as a converted absorption rate, and is described below as A 1 / d = A 1 ′ and A 2 / d = A 2 ′. Further, the right side of (Equation 8) is defined as −ΔA ′. Then, (Expression 7) becomes A 1 ′ −A 2 ′ ≦ −ΔA ′, and (Expression 5) is derived.

(式5)は、以下のことを示している。すなわち、第1領域の光吸収層16の換算吸収率と第2領域の光吸収層16の換算吸収率との差が−ΔA’で定義される値以下になる条件を満足させるようにゲート絶縁層13、非晶質シリコン層14、バッファー層、及び光吸収層の膜厚を構成すると、第2領域の非晶質シリコン層14の発熱温度が第1領域の非晶質シリコン層14の発熱温度以上になる。つまり、この条件を満足させるゲート絶縁層13、非晶質シリコン層14、バッファー層、及び光吸収層の膜厚が形成されると、例えば赤色の波長領域のレーザーにより非晶質シリコン層の上方にバッファー層を介して形成された光吸収層を照射・スキャンすることにより発生した熱をもって、非晶質シリコン層を間接的にアニールする場合に、結晶化に対するゲート電極12による熱吸収、伝播の影響を小さくすることができる。そのため、薄膜トランジスタの第1領域における非晶質シリコン層14の発熱による到達温度の分布を均一にできる。

(Formula 5) shows the following. That is, the gate insulation is satisfied so that the difference between the converted absorption rate of the

なお、本効果を生じせしめるためには、層構造(ゲート電極12の有無)、及び、層膜厚の変化により、光吸収層16の吸収率が変化することが必要である。これは、上記所定(赤色または近赤外領域の波長領域)のレーザー光の波長領域において、光吸収層16が半透明、すなわち消衰係数k<1であることが必要である。この光学特性により、光吸収層に入射したレーザー光が下層に透過し、下層膜での多重干渉が生じる。よって、層構造や層膜厚の変化により、多重干渉効果が強弱するため、この現象を利用することで、ゲート電極上の光吸収層16の吸収率とゲート電極12外の光吸収層の吸収率の差を制御できる。

In order to produce this effect, it is necessary that the absorptance of the

逆に、従来のレーザー間接加熱法で多用されていた光吸収層は、MoやCr等の高融点金属である。これら高融点金属は、消衰係数kが2以上と大きいため、入射したレーザー光はほとんど下層膜に透過せず、下層膜での多重干渉が起こりえない(もしくは、非常に小さい)。つまり、層構造や層膜厚の変化によらず、光吸収層の吸収率は一定になるので、本発明の効果を生じさせることはできない。 On the contrary, the light absorption layer that has been widely used in the conventional laser indirect heating method is a high melting point metal such as Mo or Cr. Since these refractory metals have a large extinction coefficient k of 2 or more, the incident laser beam hardly transmits to the lower layer film, and multiple interference cannot occur in the lower layer film (or very small). In other words, the absorptance of the light absorption layer is constant regardless of the change in the layer structure or the layer thickness, so that the effect of the present invention cannot be produced.

以上から、上記所定の波長領域を有するレーザー光において、光吸収層16が半透明であるという光学特性を有するという点が、本発明の効果を生じさせる上で、従来の技術とは異なる。

As described above, the laser light having the predetermined wavelength region has an optical characteristic that the

以上のように、ゲート絶縁層13、非晶質シリコン層14、バッファー層15、及び光吸収層16の膜厚を上述した条件を満たすように形成することで、さまざまな波長のレーザー光、ゲート電極の材質と膜厚であっても、結晶ムラのない結晶質シリコン層17を生成することができる。つまり、例えば、ゲート電極12のパターン形状等、特に薄膜トランジスタ100の構造に変更を加えることなく、ゲート電極12上に形成された結晶質シリコン層17の結晶性のばらつきを低減することができ、安定した結晶化が可能となる。それにより、これを使用した薄膜トランジスタ100の特性のばらつきを抑え、LCDやOLEDなどの表示装置で高精細化が進んでも、その表示品位を向上させることができるという効果を奏する。

As described above, by forming the

なお、以上の記載では、線状に集光されたレーザー光を用いて非晶質シリコン層14が結晶化される場合の例を示したが、本願ではこのほかにもスポット状(円形や楕円形その他も含む)のレーザー光を使ってもよい。その場合は、レーザー光を結晶化に適したスキャン方法で実施することが好ましい。

In the above description, an example in which the

以上のように、本実施の形態における薄膜トランジスタ100の製造方法によれば、ゲート絶縁層13、非晶質シリコン層14、バッファー層15、及び光吸収層16の膜厚が上述した条件を満たすことにより、第1領域における非晶質シリコン層14の発熱による到達温度の分布を均一にして、第1領域おける非晶質シリコン層14を充分かつ均一に結晶化を図ることができる。

As described above, according to the method for manufacturing the

以下、ゲート絶縁層13、非晶質シリコン層14、バッファー層15、及び光吸収層16の膜厚が満たすべき条件を、実施例に詳細に説明する。

Hereinafter, conditions that the film thicknesses of the

(実施例)

まず、光吸収層のレーザー光波長に対する吸収率の算出方法について説明する。(Example)

First, the calculation method of the absorptance with respect to the laser beam wavelength of a light absorption layer is demonstrated.

図7A及び図7Bは、振幅透過率及び振幅透過率の計算方法を説明するための図である。 7A and 7B are diagrams for explaining the amplitude transmittance and the method for calculating the amplitude transmittance.

図7A及び図7Bは、図2に示す薄膜トランジスタ100の構造をモデル化した多層構造のモデル構造を示している。図7Aに示すモデル構造は、複素屈折率N1からなる層401と、複素屈折率N2からなる層402と、複素屈折率N3からなる層403と、複素屈折率N4からなる層404と、複素屈折率N5からなる層405と、複素屈折率N6からなる基板層406とを備える。このモデル構造では、層405、層404、層403、層402及び層401がこの順に基板層406上に積層されたものを示している。なお、図7Bに示すモデル構造は、図7Aの層405がない場合のモデル構造を示している。また、図中に示す複素屈折率N0の領域は、モデル構造の外部であり、レーザー光がモデル構造に入射される側を示している。この領域は、例えば空気であり、その場合、屈折率1、消衰係数0である。7A and 7B show a model structure of a multilayer structure in which the structure of the

基板層406は、例えば透明なガラスまたは石英からなる絶縁基板であり、例えば屈折率1.46を有し、図5Aに示す基板10に対応する。層405は、例えば屈折率3.55、消衰係数3.86を有し、膜厚が50nmのMoWで構成されており、図5Aに示すゲート電極12に対応する。層404は、例えば屈折率1.46、消衰係数0の酸化珪素(SiOx)で構成されており、図5Bに示すゲート絶縁膜13に対応する。層403は、例えば屈折率4.19、消衰係数0のa−Siで構成されており、図5Cに示す非晶質シリコン層14に対応する。層402は、例えば屈折率1.46、消衰係数0の透明膜で構成されており、図5Dで示すバッファー層15に対応する。層401は、例えば屈折率1.9、消衰係数0.6のダイヤモンドライクカーボン膜であり、図5Dの光吸収層16に対応する。The

なお、本モデル構造においては、図5Aに示すアンダーコート層11に対応する層を省略した。なぜなら、アンダーコート層11は透明な層であり、レーザー光に対する吸収がない層であるとすれば、その膜厚は本計算結果に影響を与えないからである。よって、以下、アンダーコート層11に対応する層を省略したモデル構造にて計算を進める。

In this model structure, the layer corresponding to the