JPWO2007080852A1 - 積層コンデンサ - Google Patents

積層コンデンサ Download PDFInfo

- Publication number

- JPWO2007080852A1 JPWO2007080852A1 JP2007553899A JP2007553899A JPWO2007080852A1 JP WO2007080852 A1 JPWO2007080852 A1 JP WO2007080852A1 JP 2007553899 A JP2007553899 A JP 2007553899A JP 2007553899 A JP2007553899 A JP 2007553899A JP WO2007080852 A1 JPWO2007080852 A1 JP WO2007080852A1

- Authority

- JP

- Japan

- Prior art keywords

- main surface

- laminate

- effective layer

- external electrode

- region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 239000003990 capacitor Substances 0.000 title claims abstract description 143

- 230000007717 exclusion Effects 0.000 claims description 7

- 239000000758 substrate Substances 0.000 abstract description 33

- 238000006073 displacement reaction Methods 0.000 abstract description 25

- 230000000694 effects Effects 0.000 description 22

- 239000000919 ceramic Substances 0.000 description 14

- 238000004519 manufacturing process Methods 0.000 description 9

- 230000004048 modification Effects 0.000 description 9

- 238000012986 modification Methods 0.000 description 9

- 230000002159 abnormal effect Effects 0.000 description 6

- 230000006378 damage Effects 0.000 description 5

- 239000000463 material Substances 0.000 description 5

- 229910000679 solder Inorganic materials 0.000 description 5

- 239000003989 dielectric material Substances 0.000 description 4

- 229910045601 alloy Inorganic materials 0.000 description 3

- 239000000956 alloy Substances 0.000 description 3

- 238000010030 laminating Methods 0.000 description 3

- 229910052751 metal Inorganic materials 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 238000005452 bending Methods 0.000 description 2

- 230000008602 contraction Effects 0.000 description 2

- 238000005336 cracking Methods 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000010304 firing Methods 0.000 description 2

- 238000003475 lamination Methods 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 229910052763 palladium Inorganic materials 0.000 description 2

- 238000007747 plating Methods 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000004593 Epoxy Substances 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 230000012447 hatching Effects 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 229910052761 rare earth metal Inorganic materials 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/228—Terminals

- H01G4/232—Terminals electrically connecting two or more layers of a stacked or rolled capacitor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/30—Stacked capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/018—Dielectrics

- H01G4/06—Solid dielectrics

- H01G4/08—Inorganic dielectrics

- H01G4/12—Ceramic dielectrics

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/228—Terminals

- H01G4/232—Terminals electrically connecting two or more layers of a stacked or rolled capacitor

- H01G4/2325—Terminals electrically connecting two or more layers of a stacked or rolled capacitor characterised by the material of the terminals

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Chemical & Material Sciences (AREA)

- Ceramic Engineering (AREA)

- Inorganic Chemistry (AREA)

- Fixed Capacitors And Capacitor Manufacturing Machines (AREA)

- Ceramic Capacitors (AREA)

Abstract

Description

(発明の効果)

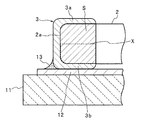

2…積層体

2a,2b…第1,第2の端面

2c…上面(一方主面)

2d…下面(他方主面)

3,4…第1,第2の外部電極

3a,3b…第1,第2の回り込み部

4a,4b…第3,第4の回り込み部

5a,5c,5e,5g,5i,5k…第1の内部電極

5b,5d,5f,5h,5j,5l…第2の内部電極

11…基板

12…電極ランド

13…半田

21…積層コンデンサ

22a〜22l…内部電極

23…積層コンデンサ

24a〜24l…内部電極

25…積層コンデンサ

26a〜26l…内部電極

27…積層コンデンサ

28a〜28l…内部電極

29a〜29d…ダミー電極

30…積層コンデンサ

30a〜30l…内部電極

30…積層コンデンサ

31a〜31d…ダミー電極

32…積層コンデンサ

33a〜33h…ダミー電極

34…積層コンデンサ

35a〜35h…ダミー電極

41…積層コンデンサ

42…積層体

43a〜43c…第1の内部電極

44a〜44c…第2の内部電極

45…第1の外部電極

B…外部電極の積層体幅方向に沿う寸法

A…積層コンデンサの幅

S…第1の領域

X…第2の領域

BaTiO3を主成分とし、希土類元素酸化物としてGd2O3を添加してなる誘電体原料を用い、以下の仕様で積層コンデンサを作製した。外部電極を含む積層体の外形寸法を、長さL=1.6mm、幅W=0.8mm及び厚みT=0.8mmとし、内部電極間に挟まれた誘電体層の厚み=1.8μm、内部電極の厚み=1.0μm、有効層の層数=230とした。内部電極構成材料としては、Niを用い、外部電極はCuからなる厚膜電極層上に、Niめっき膜及びSnめっき膜を積層することにより形成した。

図9にブロック図で示す回路を用い、40mm×100mm×厚み0.5mmのガラスエポキシ基板上に半田を用いて実装された積層コンデンサを駆動し、鳴き音圧を測定した。すなわち、図9に示すように、電源Vdcからダイオード41及びインダクタンス42を介して積層コンデンサ1に通電した。この場合、電源電圧は1.5V、電流値は0.4〜0.8Aの範囲とした。

実験例1と同様にして、ただし、実験例2〜5では、それぞれ、以下の仕様の積層コンデンサを作製した。そして、得られた積層コンデンサにおいて実験例1と同様に第1,第3の領域及び第2,第4の領域における有効層の占有体積割合を変化させ、静電容量及び鳴き音圧を測定した。結果を下記の表3〜表6に示す。

外部電極を含めた積層体寸法は、長さL=2.0mm、幅W=1.25mm及び厚みT=1.25mmとし、内部電極間に挟まれた誘電体層の厚みは1.8μm、内部電極の厚みは1.0μm、有効層の積層数は380、有効層が設けられている部分の上下に配置されている誘電体層の厚みは各80μm、外部電極の端面上の厚みは60μm、回り込み部における厚みは30μm、回り込み部の先端と、積層体端面との間の距離を0.5mmとした。誘電体層、内部電極及び外部電極形成材料は、実験例1と同様とした。

外部電極を含めた積層体寸法は、長さL=3.2mm、幅W=1.6mm及び厚みT=1.6mmとし、内部電極間に挟まれた誘電体層の厚みは1.8μm、内部電極の厚みは1.0μm、有効層の積層数は500、有効層が設けられている部分の上下に配置されている誘電体層の厚みは各100μm、外部電極の端面上の厚みは60μm、回り込み部における厚みは40μm、回り込み部の先端と、積層体端面との間の距離を0.6mmとした。誘電体層、内部電極及び外部電極形成材料は、実験例1と同様とした。

外部電極を含めた積層体寸法は、長さL=3.2mm、幅W=2.5mm及び厚みT=2.5mmとし、内部電極間に挟まれた誘電体層の厚みは1.8μm、内部電極の厚みは1.0μm、有効層の積層数は800、有効層が設けられている部分の上下に配置されている誘電体層の厚みは各100μm、外部電極の端面上の厚みは100μm、回り込み部における厚みは40μm、回り込み部の先端と、積層体端面との間の距離を0.6mmとした。誘電体層、内部電極及び外部電極形成材料は、実験例1と同様とした。

外部電極を含めた積層体寸法は、長さL=1.0mm、幅W=0.5mm及び厚みT=0.5mmとし、内部電極間に挟まれた誘電体層の厚みは1.8μm、内部電極の厚みは1.0μm、有効層の積層数は120、有効層が設けられている部分の上下に配置されている誘電体層の厚みは各60μm、外部電極の端面上の厚みは30μm、回り込み部における厚みは10μm、回り込み部の先端と、積層体端面との間の距離を0.3mmとした。誘電体層、内部電極及び外部電極形成材料は、実験例1と同様とした。

前述した実験例1〜5と同様にして、1005サイズ、1608サイズ、2012サイズ、3216サイズ及び3225サイズの各積層コンデンサを作成した。なお、領域S中の有効層の占有体積割合及び領域X中の有効層占有体積割合は下記の表7に示す通りとした。また、下記の表7に示すように、T0/L0の比を種々変更し、それぞれのサイズについて、条件1〜5のT0/L0比の積層コンデンサを作成した。これらの積層コンデンサの取得容量及び鳴き音圧を実験例1〜5と同様にして評価した。結果を下記の表7に併せて示す。

前述した実験例1〜6と同様にして、1005サイズ、1608サイズ、2012サイズ、3216サイズ及び3225サイズの各積層コンデンサを作成した。なお、領域S中の有効層の占有体積割合及び領域X中の有効層占有体積割合は下記の表8に示す通りとした。また、下記の表8に示すように、外部電極の幅Bの積層コンデンサの幅Aに対する割合B/Aを変更し、それぞれのサイズの積層コンデンサについて、条件1〜5の(B/A)×100(%)の積層コンデンサを作製した。これらの積層コンデンサの取得容量及び鳴き音圧を実験例1〜5と同様にして評価した。結果を下記の表8に合わせて示す。

Claims (8)

- 複数の積層された誘電体層からなり、一方端部、他方端部、一方主面及び他方主面を有する積層体と、

前記積層体の前記一方端部に形成されており、かつ前記積層体の前記一方主面及び他方主面にそれぞれ回り込んでいる第1の回り込み部及び第2の回り込み部を有する第1の外部電極と、

前記積層体の前記他方端部に形成されており、かつ前記積層体の前記一方主面及び前記他方主面にそれぞれ回り込んでいる第3の回り込み部及び第4の回り込み部を有する第2の外部電極と、

前記誘電体層間に形成されており、前記第1の外部電極と接続された第1の内部電極と、

前記誘電体層間に形成されており、前記第2の外部電極と接続された第2の内部電極とを備え、

複数の前記誘電体層の内、前記第1の内部電極と前記第2の内部電極との間に挟まれることにより容量が形成される部分を有効層としたとき、

前記積層体の中で、前記第1の回り込み部と前記第2の回り込み部との間に挟まれた第1の領域において、前記有効層の占有体積割合割合が10%以上であり、

前記第1の領域の内の前記他方主面側に位置する半分を占める第2の領域において、前記有効層の占有体積割合が15%以下であり、

前記積層体の中で、前記第3の回り込み部と前記第4の回り込み部との間に挟まれた第3の領域において、前記有効層の占有体積割合が10%以上であり、

前記第3の領域の内の前記他方主面側に位置する半分を占める第4の領域において、前記有効層の占有体積割合が15%以下であり、

前記積層体、前記第1の外部電極及び前記第2の外部電極を含む構造の外形寸法が、長さ1.6±0.1mm、幅0.8±0.1mm、高さ0.8±0.1mmの範囲にあることを特徴とする、積層コンデンサ。 - 複数の積層された誘電体層からなり、一方端部、他方端部、一方主面及び他方主面を有する積層体と、

前記積層体の前記一方端部に形成されており、かつ前記積層体の前記一方主面及び他方主面にそれぞれ回り込んでいる第1の回り込み部及び第2の回り込み部を有する第1の外部電極と、

前記積層体の前記他方端部に形成されており、かつ前記積層体の前記一方主面及び前記他方主面にそれぞれ回り込んでいる第3の回り込み部及び第4の回り込み部を有する第2の外部電極と、

前記誘電体層間に形成されており、前記第1の外部電極と接続された第1の内部電極と、

前記誘電体層間に形成されており、前記第2の外部電極と接続された第2の内部電極とを備え、

複数の前記誘電体層の内、前記第1の内部電極と前記第2の内部電極との間に挟まれることにより容量が形成される部分を有効層としたとき、

前記積層体の中で、前記第1の回り込み部と前記第2の回り込み部との間に挟まれた第1の領域において、前記有効層の占有体積割合が20%以上であり、

前記第1の領域の内の前記他方主面側に位置する半分を占める第2の領域において、前記有効層の占有体積割合が35%以下であり、

前記積層体の中で、前記第3の回り込み部と前記第4の回り込み部との間に挟まれた第3の領域において、前記有効層の占有体積割合が20%以上であり、

前記第3の領域の内の前記他方主面側に位置する半分を占める第4の領域において、前記有効層の占有体積割合が35%以下であり、

前記積層体、前記第1の外部電極及び前記第2の外部電極を含む構造の外形寸法が、長さ2.0±0.1mm、幅1.25±0.1mm、高さ1.25±0.1mmの範囲にあることを特徴とする、積層コンデンサ。 - 複数の積層された誘電体層からなり、一方端部、他方端部、一方主面及び他方主面を有する積層体と、

前記積層体の前記一方端部に形成されており、かつ前記積層体の前記一方主面及び他方主面にそれぞれ回り込んでいる第1の回り込み部及び第2の回り込み部を有する第1の外部電極と、

前記積層体の前記他方端部に形成されており、かつ前記積層体の前記一方主面及び前記他方主面にそれぞれ回り込んでいる第3の回り込み部及び第4の回り込み部を有する第2の外部電極と、

前記誘電体層間に形成されており、前記第1の外部電極と接続された第1の内部電極と、

前記誘電体層間に形成されており、前記第2の外部電極と接続された第2の内部電極とを備え、

複数の前記誘電体層の内、前記第1の内部電極と前記第2の内部電極との間に挟まれることにより容量が形成される部分を有効層としたとき、

前記積層体の中で、前記第1の回り込み部と前記第2の回り込み部との間に挟まれた第1の領域において、前記有効層の占有体積割合が20%以上であり、

前記第1の領域の内の前記他方主面側に位置する半分を占める第2の領域において、前記有効層の占有体積割合が35%以下であり、

前記積層体の中で、前記第3の回り込み部と前記第4の回り込み部との間に挟まれた第3の領域において、前記有効層の占有体積割合が20%以上であり、

前記第3の領域の内の前記他方主面側に位置する半分を占める第4の領域において、前記有効層の占有体積割合が35%以下であり、

前記積層体、前記第1の外部電極及び前記第2の外部電極を含む構造の外形寸法が、長さ3.2±0.15mm、幅1.6±0.15mm、高さ1.6±0.15mmの範囲にあることを特徴とする、積層コンデンサ。 - 複数の積層された誘電体層からなり、一方端部、他方端部、一方主面及び他方主面を有する積層体と、

前記積層体の前記一方端部に形成されており、かつ前記積層体の前記一方主面及び他方主面にそれぞれ回り込んでいる第1の回り込み部及び第2の回り込み部を有する第1の外部電極と、

前記積層体の前記他方端部に形成されており、かつ前記積層体の前記一方主面及び前記他方主面にそれぞれ回り込んでいる第3の回り込み部及び第4の回り込み部を有する第2の外部電極と、

前記誘電体層間に形成されており、前記第1の外部電極と接続された第1の内部電極と、

前記誘電体層間に形成されており、前記第2の外部電極と接続された第2の内部電極とを備え、

複数の前記誘電体層の内、前記第1の内部電極と前記第2の内部電極との間に挟まれることにより容量が形成される部分を有効層としたとき、

前記積層体の中で、前記第1の回り込み部と前記第2の回り込み部との間に挟まれた第1の領域において、前記有効層の占有体積割合が20%以上であり、

前記第1の領域の内の前記他方主面側に位置する半分を占める第2の領域において、前記有効層の占有体積割合が35%以下であり、

前記積層体の中で、前記第3の回り込み部と前記第4の回り込み部との間に挟まれた第3の領域において、前記有効層の占有体積割合が20%以上であり、

前記第3の領域の内の前記他方主面側に位置する半分を占める第4の領域において、前記有効層の占有体積割合が35%以下であり、

前記積層体、前記第1の外部電極及び前記第2の外部電極を含む構造の外形寸法が、長さ3.2±0.3mm、幅2.5±0.2mm、高さ2.5±0.2mmの範囲にあることを特徴とする、積層コンデンサ。 - 複数の積層された誘電体層からなり、一方端部、他方端部、一方主面及び他方主面を有する積層体と、

前記積層体の前記一方端部に形成されており、かつ前記積層体の前記一方主面及び他方主面にそれぞれ回り込んでいる第1の回り込み部及び第2の回り込み部を有する第1の外部電極と、

前記積層体の前記他方端部に形成されており、かつ前記積層体の前記一方主面及び前記他方主面にそれぞれ回り込んでいる第3の回り込み部及び第4の回り込み部を有する第2の外部電極と、

前記誘電体層間に形成されており、前記第1の外部電極と接続された第1の内部電極と、

前記誘電体層間に形成されており、前記第2の外部電極と接続された第2の内部電極とを備え、

複数の前記誘電体層の内、前記第1の内部電極と前記第2の内部電極との間に挟まれることにより容量が形成される部分を有効層としたとき、

前記積層体の中で、前記第1の回り込み部と前記第2の回り込み部との間に挟まれた第1の領域において、前記有効層の占有体積割合割合が10%以上であり、

前記第1の領域の内の前記他方主面側に位置する半分を占める第2の領域において、前記有効層の占有体積割合が10%以下であり、

前記積層体の中で、前記第3の回り込み部と前記第4の回り込み部との間に挟まれた第3の領域において、前記有効層の占有体積割合が10%以上であり、

前記第3の領域の内の前記他方主面側に位置する半分を占める第4の領域において、前記有効層の占有体積割合が10%以下であり、

前記積層体、前記第1の外部電極及び前記第2の外部電極を含む構造の外形寸法が、長さ1.0±0.05mm、幅0.5±0.05mm、高さ0.5±0.05mmの範囲にあることを特徴とする、積層コンデンサ。 - 前記積層体の前記一方端部と他方端部とを結ぶ直線を含み、かつ前記第1,第2の内部電極に直交する断面から見た場合、前記積層体の一方主面と他方主面とを結ぶ方向である厚み方向中央において、有効層が前記第1,第3の領域に至るように前記第1,第2の内部電極が設けられており、有効層が第1,第3の領域に至るように設けられている部分を中央部としたときに、該中央部よりも前記他方主面側に位置している領域においては、前記有効層が第1の領域又は第3の領域に至らない前記有効層排除部とされており、該有効層排除部において前記中央部と同様にして積層した場合に比べて有効層が排除されている部分の厚み方向寸法をT0、前記積層体の一方端部と他方端部とを結ぶ方向の寸法をL0としたときに、T0/L0が0.5〜1.5の範囲とされていることを特徴とする、請求項1〜5のいずれか1項に記載の積層コンデンサ。

- 前記積層コンデンサにおいて、前記積層体の前記一方端部と他方端部とを結ぶ方向が長さ方向であり、前記積層体の一方主面と他方主面とを結ぶ方向が高さ方向であり、前記積層体の長さ方向及び高さ方向に直交する方向が幅方向とされており、前記第1,2の外部電極の前記幅方向に沿う寸法が、前記積層コンデンサの幅よりも小さくされている、請求項1〜6のいずれか1項に記載の積層コンデンサ。

- 前記外部電極の幅が、前記積層コンデンサの幅の92%以下である、請求項7に記載の積層コンデンサ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007553899A JP4816648B2 (ja) | 2006-01-13 | 2007-01-09 | 積層コンデンサ |

Applications Claiming Priority (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006006132 | 2006-01-13 | ||

| JP2006006132 | 2006-01-13 | ||

| JP2006229570 | 2006-08-25 | ||

| JP2006229570 | 2006-08-25 | ||

| JP2007553899A JP4816648B2 (ja) | 2006-01-13 | 2007-01-09 | 積層コンデンサ |

| PCT/JP2007/050089 WO2007080852A1 (ja) | 2006-01-13 | 2007-01-09 | 積層コンデンサ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2007080852A1 true JPWO2007080852A1 (ja) | 2009-06-11 |

| JP4816648B2 JP4816648B2 (ja) | 2011-11-16 |

Family

ID=38256258

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007553899A Active JP4816648B2 (ja) | 2006-01-13 | 2007-01-09 | 積層コンデンサ |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US7715172B2 (ja) |

| JP (1) | JP4816648B2 (ja) |

| KR (1) | KR101014508B1 (ja) |

| CN (1) | CN101401177B (ja) |

| DE (1) | DE112007000130B4 (ja) |

| TW (1) | TW200741768A (ja) |

| WO (1) | WO2007080852A1 (ja) |

Families Citing this family (41)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8021277B2 (en) | 2005-02-02 | 2011-09-20 | Mad Dogg Athletics, Inc. | Programmed exercise bicycle with computer aided guidance |

| DE112008003104B4 (de) * | 2007-11-22 | 2014-09-25 | Murata Mfg. Co., Ltd. | Keramische Mehrschichtkomponente |

| JP4539713B2 (ja) * | 2007-12-11 | 2010-09-08 | Tdk株式会社 | 積層コンデンサアレイ |

| US8072773B2 (en) * | 2008-04-04 | 2011-12-06 | John Mruz | Ultra-wideband assembly system and method |

| JP5751080B2 (ja) * | 2010-09-28 | 2015-07-22 | 株式会社村田製作所 | 積層セラミック電子部品 |

| JP5201223B2 (ja) * | 2011-01-28 | 2013-06-05 | 株式会社村田製作所 | 電子部品及び基板モジュール |

| KR101823149B1 (ko) * | 2011-04-19 | 2018-01-29 | 삼성전기주식회사 | 적층형 세라믹 커패시터 |

| KR101539808B1 (ko) * | 2011-06-23 | 2015-07-28 | 삼성전기주식회사 | 적층 세라믹 커패시터 |

| JP5899699B2 (ja) * | 2011-08-10 | 2016-04-06 | Tdk株式会社 | 積層型コンデンサ |

| KR101548773B1 (ko) * | 2011-08-22 | 2015-08-31 | 삼성전기주식회사 | 적층 세라믹 커패시터의 회로 기판 실장 구조 |

| DE112013001679B4 (de) * | 2012-03-26 | 2023-03-09 | Kemet Electronics Corporation | Asymmetrischer Hochspannungskondensator |

| KR101309326B1 (ko) * | 2012-05-30 | 2013-09-16 | 삼성전기주식회사 | 적층 칩 전자부품, 그 실장 기판 및 포장체 |

| US8934215B2 (en) * | 2012-07-20 | 2015-01-13 | Samsung Electro-Mechanics Co., Ltd | Laminated chip electronic component, board for mounting the same, and packing unit thereof |

| KR101771730B1 (ko) * | 2012-08-07 | 2017-08-25 | 삼성전기주식회사 | 적층 세라믹 전자부품 및 이의 제조방법 |

| KR101474065B1 (ko) | 2012-09-27 | 2014-12-17 | 삼성전기주식회사 | 적층 칩 전자부품, 그 실장 기판 및 포장체 |

| JP5811152B2 (ja) * | 2012-11-05 | 2015-11-11 | 株式会社村田製作所 | 積層セラミック電子部品、その製造方法、テーピング電子部品連、その製造方法、および積層セラミック電子部品の方向識別方法 |

| KR101452048B1 (ko) * | 2012-11-09 | 2014-10-22 | 삼성전기주식회사 | 적층 세라믹 커패시터, 적층 세라믹 커패시터의 회로 기판 실장 구조 및 적층 세라믹 커패시터의 포장체 |

| KR101444540B1 (ko) * | 2012-11-20 | 2014-09-24 | 삼성전기주식회사 | 적층 세라믹 커패시터, 적층 세라믹 커패시터의 회로 기판 실장 구조 및 적층 세라믹 커패시터의 포장체 |

| KR101452074B1 (ko) | 2012-12-27 | 2014-10-16 | 삼성전기주식회사 | 적층 세라믹 커패시터 및 그 실장 기판 |

| JP5987812B2 (ja) | 2013-01-25 | 2016-09-07 | 株式会社村田製作所 | 積層コンデンサ、テーピング積層コンデンサ連及び積層コンデンサの実装構造 |

| KR101462757B1 (ko) * | 2013-01-29 | 2014-11-17 | 삼성전기주식회사 | 적층 세라믹 커패시터, 그 제조방법 및 적층 세라믹 커패시터가 내장된 인쇄회로기판 |

| WO2014121100A1 (en) * | 2013-02-01 | 2014-08-07 | The Trustees Of Dartmouth College | Multilayer conductors with integrated capacitors and associated systems and methods |

| KR101823174B1 (ko) | 2013-06-14 | 2018-01-29 | 삼성전기주식회사 | 적층 세라믹 커패시터 및 그 실장 기판 |

| KR101477405B1 (ko) * | 2013-07-05 | 2014-12-29 | 삼성전기주식회사 | 적층 세라믹 커패시터 및 그 실장 기판 |

| JP6377957B2 (ja) * | 2014-05-29 | 2018-08-22 | 太陽誘電株式会社 | 積層セラミックコンデンサ |

| JP2016001695A (ja) * | 2014-06-12 | 2016-01-07 | 株式会社村田製作所 | 積層コンデンサ、これを含む積層コンデンサ連および積層コンデンサ実装体 |

| WO2016013339A1 (ja) * | 2014-07-23 | 2016-01-28 | 株式会社 村田製作所 | 積層コイル部品 |

| JP6312633B2 (ja) * | 2014-08-01 | 2018-04-18 | 太陽誘電株式会社 | 積層セラミックコンデンサ |

| KR102048094B1 (ko) * | 2014-10-08 | 2019-11-22 | 삼성전기주식회사 | 전자 부품 및 이의 제조 방법 |

| CA2919466C (en) * | 2015-02-10 | 2023-06-27 | Nova Chemicals Corporation | Stand up pouch |

| KR101808794B1 (ko) * | 2015-05-07 | 2018-01-18 | 주식회사 모다이노칩 | 적층체 소자 |

| JP6690176B2 (ja) * | 2015-10-06 | 2020-04-28 | Tdk株式会社 | 電子部品 |

| JP6522549B2 (ja) | 2016-06-07 | 2019-05-29 | 太陽誘電株式会社 | 積層セラミックコンデンサ |

| JP2018006627A (ja) * | 2016-07-05 | 2018-01-11 | 太陽誘電株式会社 | 積層セラミックコンデンサ |

| JP6616929B2 (ja) * | 2018-02-15 | 2019-12-04 | 太陽誘電株式会社 | 積層セラミックコンデンサ |

| JP6527612B2 (ja) * | 2018-02-15 | 2019-06-05 | 太陽誘電株式会社 | 積層セラミックコンデンサ |

| JP7547694B2 (ja) * | 2018-03-09 | 2024-09-10 | サムソン エレクトロ-メカニックス カンパニーリミテッド. | 積層型キャパシタ |

| KR102185055B1 (ko) * | 2018-10-02 | 2020-12-01 | 삼성전기주식회사 | 적층 세라믹 전자부품 |

| WO2024075402A1 (ja) * | 2022-10-03 | 2024-04-11 | 株式会社村田製作所 | 積層セラミック電子部品 |

| WO2024161743A1 (ja) * | 2023-01-30 | 2024-08-08 | 株式会社村田製作所 | 積層セラミックコンデンサ |

| US11806577B1 (en) | 2023-02-17 | 2023-11-07 | Mad Dogg Athletics, Inc. | Programmed exercise bicycle with computer aided guidance |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11186092A (ja) * | 1997-12-25 | 1999-07-09 | Tdk Corp | チップ状電子部品 |

| JP2003022929A (ja) * | 2001-07-09 | 2003-01-24 | Taiyo Yuden Co Ltd | 積層セラミックコンデンサ |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4241378A (en) * | 1978-06-12 | 1980-12-23 | Erie Technological Products, Inc. | Base metal electrode capacitor and method of making the same |

| JP2993301B2 (ja) * | 1992-11-26 | 1999-12-20 | 松下電器産業株式会社 | 積層セラミックコンデンサ |

| JP2853523B2 (ja) | 1993-07-14 | 1999-02-03 | トヨタ自動車株式会社 | ヘッドランプ照射範囲制御装置 |

| JPH0732936U (ja) * | 1993-11-29 | 1995-06-16 | 太陽誘電株式会社 | 積層セラミック電子部品 |

| JPH07211132A (ja) * | 1994-01-10 | 1995-08-11 | Murata Mfg Co Ltd | 導電性ペーストおよびこれを用いた積層セラミックコンデンサの製造方法 |

| JPH0869939A (ja) | 1994-06-23 | 1996-03-12 | Murata Mfg Co Ltd | 積層セラミックコンデンサおよびその製造方法 |

| US5600533A (en) | 1994-06-23 | 1997-02-04 | Murata Manufacturing Co., Ltd. | Multilayer ceramic capacitor having an anti-reducing agent |

| JPH08181033A (ja) | 1994-12-22 | 1996-07-12 | Tokin Corp | 積層セラミックコンデンサ |

| JPH08180731A (ja) * | 1994-12-26 | 1996-07-12 | Murata Mfg Co Ltd | 導電性厚膜組成物、厚膜電極、セラミック電子部品、および積層セラミックコンデンサ |

| KR100277382B1 (ko) * | 1995-08-18 | 2001-01-15 | 사토 히로시 | 다층전자부품 |

| JPH10261546A (ja) * | 1997-03-19 | 1998-09-29 | Murata Mfg Co Ltd | 積層コンデンサ |

| JPH10312933A (ja) * | 1997-05-09 | 1998-11-24 | Murata Mfg Co Ltd | 積層セラミック電子部品 |

| JPH11150037A (ja) | 1997-11-19 | 1999-06-02 | Tdk Corp | 積層セラミックコンデンサ |

| JP2000124057A (ja) * | 1998-10-12 | 2000-04-28 | Tdk Corp | 積層型セラミックコンデンサ |

| JP2000269066A (ja) * | 1999-03-19 | 2000-09-29 | Taiyo Yuden Co Ltd | 積層セラミックコンデンサ |

| JP2001035738A (ja) * | 1999-07-15 | 2001-02-09 | Murata Mfg Co Ltd | 積層セラミック電子部品 |

| JP2001185437A (ja) * | 1999-12-24 | 2001-07-06 | Taiyo Yuden Co Ltd | 積層セラミックコンデンサ |

-

2007

- 2007-01-09 KR KR1020087016699A patent/KR101014508B1/ko active IP Right Grant

- 2007-01-09 CN CN2007800089916A patent/CN101401177B/zh active Active

- 2007-01-09 JP JP2007553899A patent/JP4816648B2/ja active Active

- 2007-01-09 DE DE112007000130.5T patent/DE112007000130B4/de not_active Expired - Fee Related

- 2007-01-09 WO PCT/JP2007/050089 patent/WO2007080852A1/ja active Application Filing

- 2007-01-11 TW TW096101108A patent/TW200741768A/zh unknown

-

2008

- 2008-07-11 US US12/171,442 patent/US7715172B2/en active Active

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11186092A (ja) * | 1997-12-25 | 1999-07-09 | Tdk Corp | チップ状電子部品 |

| JP2003022929A (ja) * | 2001-07-09 | 2003-01-24 | Taiyo Yuden Co Ltd | 積層セラミックコンデンサ |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20080077273A (ko) | 2008-08-21 |

| DE112007000130T5 (de) | 2008-12-18 |

| US20090002918A1 (en) | 2009-01-01 |

| DE112007000130B4 (de) | 2016-06-09 |

| KR101014508B1 (ko) | 2011-02-14 |

| CN101401177B (zh) | 2011-03-30 |

| WO2007080852A1 (ja) | 2007-07-19 |

| CN101401177A (zh) | 2009-04-01 |

| TW200741768A (en) | 2007-11-01 |

| TWI325597B (ja) | 2010-06-01 |

| JP4816648B2 (ja) | 2011-11-16 |

| US7715172B2 (en) | 2010-05-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4816648B2 (ja) | 積層コンデンサ | |

| JP5485351B2 (ja) | 積層チップ電子部品、その実装基板及び包装体 | |

| JP4953988B2 (ja) | 積層コンデンサおよびコンデンサ実装基板 | |

| JP4905498B2 (ja) | 積層型セラミック電子部品 | |

| JP5206440B2 (ja) | セラミック電子部品 | |

| KR101933412B1 (ko) | 적층 세라믹 커패시터 및 그 실장 기판 | |

| KR101823174B1 (ko) | 적층 세라믹 커패시터 및 그 실장 기판 | |

| JP6309991B2 (ja) | 積層セラミックコンデンサ | |

| JP7308021B2 (ja) | セラミック電子部品、セラミック電子部品の製造方法およびセラミック電子部品実装回路基板 | |

| JP2014027255A (ja) | セラミック電子部品及びセラミック電子装置 | |

| JP2020047908A (ja) | 電子部品 | |

| JP4925779B2 (ja) | 積層コンデンサ | |

| JP6421138B2 (ja) | 積層セラミックコンデンサ | |

| JP4475338B2 (ja) | 積層コンデンサ | |

| JP6201477B2 (ja) | 積層コンデンサ | |

| JP5251834B2 (ja) | 積層コンデンサ | |

| JP2009059888A (ja) | 積層セラミックコンデンサ | |

| JP5120450B2 (ja) | 積層セラミック電子部品 | |

| JP7359019B2 (ja) | 電子部品 | |

| JP2021129007A (ja) | 電子部品 | |

| KR102483617B1 (ko) | 적층형 전자 부품 | |

| JP2000106322A (ja) | 積層セラミックコンデンサ | |

| JP2010098052A (ja) | 積層貫通コンデンサ | |

| JP6064044B2 (ja) | 外部接続部を有する多層デバイス、および外部接続部を有する多層デバイスの製造方法 | |

| KR20210030781A (ko) | 적층형 커패시터 및 그 실장 기판 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080609 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101221 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110221 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110802 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110815 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140909 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4816648 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |