JP4694108B2 - 酸化膜形成方法、酸化膜形成装置および電子デバイス材料 - Google Patents

酸化膜形成方法、酸化膜形成装置および電子デバイス材料 Download PDFInfo

- Publication number

- JP4694108B2 JP4694108B2 JP2003146228A JP2003146228A JP4694108B2 JP 4694108 B2 JP4694108 B2 JP 4694108B2 JP 2003146228 A JP2003146228 A JP 2003146228A JP 2003146228 A JP2003146228 A JP 2003146228A JP 4694108 B2 JP4694108 B2 JP 4694108B2

- Authority

- JP

- Japan

- Prior art keywords

- oxide film

- plasma

- electronic device

- processing chamber

- processing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims description 77

- 239000000463 material Substances 0.000 title claims description 29

- 238000012545 processing Methods 0.000 claims description 108

- 239000007789 gas Substances 0.000 claims description 69

- 239000000758 substrate Substances 0.000 claims description 51

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Chemical compound O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 claims description 46

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 claims description 10

- 229910052710 silicon Inorganic materials 0.000 claims description 8

- 239000010703 silicon Substances 0.000 claims description 8

- 229910052786 argon Inorganic materials 0.000 claims description 6

- 230000001678 irradiating effect Effects 0.000 claims description 4

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 3

- 239000001301 oxygen Substances 0.000 claims description 3

- 229910052760 oxygen Inorganic materials 0.000 claims description 3

- 239000001257 hydrogen Substances 0.000 claims description 2

- 229910052739 hydrogen Inorganic materials 0.000 claims description 2

- 125000004435 hydrogen atom Chemical class [H]* 0.000 claims 1

- 239000010408 film Substances 0.000 description 134

- 230000003647 oxidation Effects 0.000 description 31

- 238000007254 oxidation reaction Methods 0.000 description 31

- 230000008569 process Effects 0.000 description 29

- 235000012431 wafers Nutrition 0.000 description 28

- 238000010438 heat treatment Methods 0.000 description 15

- 239000004065 semiconductor Substances 0.000 description 15

- 238000002955 isolation Methods 0.000 description 13

- 230000015572 biosynthetic process Effects 0.000 description 10

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 10

- 238000001816 cooling Methods 0.000 description 9

- 238000004519 manufacturing process Methods 0.000 description 9

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 7

- 229910052782 aluminium Inorganic materials 0.000 description 7

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 7

- 239000013078 crystal Substances 0.000 description 7

- 238000012546 transfer Methods 0.000 description 7

- 238000011282 treatment Methods 0.000 description 7

- 238000006243 chemical reaction Methods 0.000 description 6

- 239000010453 quartz Substances 0.000 description 6

- 230000006378 damage Effects 0.000 description 5

- 238000005516 engineering process Methods 0.000 description 5

- 230000005284 excitation Effects 0.000 description 5

- 238000005259 measurement Methods 0.000 description 5

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 5

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 229910052681 coesite Inorganic materials 0.000 description 4

- 229910052906 cristobalite Inorganic materials 0.000 description 4

- 238000011156 evaluation Methods 0.000 description 4

- 239000012535 impurity Substances 0.000 description 4

- 230000007246 mechanism Effects 0.000 description 4

- 229920005591 polysilicon Polymers 0.000 description 4

- 239000000377 silicon dioxide Substances 0.000 description 4

- 229910052682 stishovite Inorganic materials 0.000 description 4

- 229910052905 tridymite Inorganic materials 0.000 description 4

- 239000004020 conductor Substances 0.000 description 3

- 238000011109 contamination Methods 0.000 description 3

- 239000011261 inert gas Substances 0.000 description 3

- 238000013441 quality evaluation Methods 0.000 description 3

- 238000007789 sealing Methods 0.000 description 3

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 2

- 230000002159 abnormal effect Effects 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 229910010293 ceramic material Inorganic materials 0.000 description 2

- 238000004140 cleaning Methods 0.000 description 2

- 230000000052 comparative effect Effects 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- 125000002887 hydroxy group Chemical group [H]O* 0.000 description 2

- 229910052743 krypton Inorganic materials 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 229910052756 noble gas Inorganic materials 0.000 description 2

- 230000001590 oxidative effect Effects 0.000 description 2

- 238000009832 plasma treatment Methods 0.000 description 2

- 230000002265 prevention Effects 0.000 description 2

- 230000000644 propagated effect Effects 0.000 description 2

- 230000009257 reactivity Effects 0.000 description 2

- 238000004904 shortening Methods 0.000 description 2

- 230000035882 stress Effects 0.000 description 2

- 230000003685 thermal hair damage Effects 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- VHUUQVKOLVNVRT-UHFFFAOYSA-N Ammonium hydroxide Chemical compound [NH4+].[OH-] VHUUQVKOLVNVRT-UHFFFAOYSA-N 0.000 description 1

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 1

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 1

- QGZKDVFQNNGYKY-UHFFFAOYSA-N ammonia Natural products N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 230000005587 bubbling Effects 0.000 description 1

- 239000012159 carrier gas Substances 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 238000002485 combustion reaction Methods 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 238000012790 confirmation Methods 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 239000003989 dielectric material Substances 0.000 description 1

- 229910001873 dinitrogen Inorganic materials 0.000 description 1

- 229910001882 dioxygen Inorganic materials 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000001035 drying Methods 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 238000000572 ellipsometry Methods 0.000 description 1

- 238000004880 explosion Methods 0.000 description 1

- CPBQJMYROZQQJC-UHFFFAOYSA-N helium neon Chemical compound [He].[Ne] CPBQJMYROZQQJC-UHFFFAOYSA-N 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- 238000007654 immersion Methods 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 238000005121 nitriding Methods 0.000 description 1

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 1

- 239000012788 optical film Substances 0.000 description 1

- 238000005192 partition Methods 0.000 description 1

- 238000003672 processing method Methods 0.000 description 1

- 230000002250 progressing effect Effects 0.000 description 1

- 230000001698 pyrogenic effect Effects 0.000 description 1

- 239000002994 raw material Substances 0.000 description 1

- 239000003507 refrigerant Substances 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

- 238000004611 spectroscopical analysis Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 239000013589 supplement Substances 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

- 230000008646 thermal stress Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/02227—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process

- H01L21/0223—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate

- H01L21/02233—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate of the semiconductor substrate or a semiconductor layer

- H01L21/02236—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate of the semiconductor substrate or a semiconductor layer group IV semiconductor

- H01L21/02238—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate of the semiconductor substrate or a semiconductor layer group IV semiconductor silicon in uncombined form, i.e. pure silicon

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/32009—Arrangements for generation of plasma specially adapted for examination or treatment of objects, e.g. plasma sources

- H01J37/32192—Microwave generated discharge

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02164—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material being a silicon oxide, e.g. SiO2

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/314—Inorganic layers

- H01L21/316—Inorganic layers composed of oxides or glassy oxides or oxide based glass

- H01L21/3165—Inorganic layers composed of oxides or glassy oxides or oxide based glass formed by oxidation

- H01L21/31654—Inorganic layers composed of oxides or glassy oxides or oxide based glass formed by oxidation of semiconductor materials, e.g. the body itself

- H01L21/31658—Inorganic layers composed of oxides or glassy oxides or oxide based glass formed by oxidation of semiconductor materials, e.g. the body itself by thermal oxidation, e.g. of SiGe

- H01L21/31662—Inorganic layers composed of oxides or glassy oxides or oxide based glass formed by oxidation of semiconductor materials, e.g. the body itself by thermal oxidation, e.g. of SiGe of silicon in uncombined form

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/02227—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process

- H01L21/02252—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by plasma treatment, e.g. plasma oxidation of the substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/02227—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process

- H01L21/02255—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by thermal treatment

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Power Engineering (AREA)

- Plasma & Fusion (AREA)

- Chemical & Material Sciences (AREA)

- Analytical Chemistry (AREA)

- Formation Of Insulating Films (AREA)

- Element Separation (AREA)

Description

【発明の属する技術分野】

本願発明は、電子デバイスのプロセスの要素技術の一つである酸化膜形成を好適に行うことができる酸化膜の形成方法、該酸化膜の形成方法に好適に使用可能な酸化膜形成装置、および該形成方法ないし形成装置によって好適に形成可能な電子デバイス材料に関する。本発明の酸化膜形成方法は、例えば、半導体ないし半導体デバイス(例えば、MOS型半導体構造を有するもの、薄膜トランジスタ(TFT)構造を有するもの等)、ないしは液晶デバイスのための材料の形成に好適に使用することが可能である。

【0002】

【従来の技術】

近年の半導体デバイスの高集積化に伴い、素子間分離技術がLOCOS(フィールド酸化膜による分離)からSTI(トレンチ講による分離)に移行して行く傾向にある。これは、STIによれば、より深く、確実な素子分離ができるという利点が容易に得られるからである。

【0003】

このSTIを用いる場合、まず信頼性の高い酵化膜を下地酸化膜としてトレンチ溝表面に形成した後、CVD(化学気相堆積)等を用いた酸化膜でトレンチ溝を埋める。この際、下地酸化膜の形成には、従来より熱酸化法が用いられて来た。

【0004】

【発明が解決しようとする課題】

上記した熱酸化法では、1000℃程度の高温が必要となる。このため、上記STI(トレンチ酸化)はデバイス全工程中で、熱酸化による熱的ダメージが問題とならない極めて初期の工程でしか適応できない。

【0005】

また、上記STIを採用した場合には、これにより得られる構造は必然的に三次元化する。このような三次元構造では、Si基板の異なる結晶方位面を酸化する必要があるが、熱酸化法ではその成長速度が結晶方位に依存するため、熱酸化法により得られた膜を有するトレンチ溝においては、仕上がりの酸化膜厚さがSi基板の結晶方位ごとに異なる傾向が強い。したがって、最低膜厚を確保しようとした場合には、不用意に厚く酸化される結晶方位面ができてしまい、デバイス微細化の妨げとなっていた。

【0006】

更に、酸化膜の信頼性向上のために、熱酸化法においても(H2O)または(H2+O2)を用いたウェット酸化法が用いられ、酸化温度の低速化技術開発も進んではいるものの、依然として熱酸化法では800℃程度以上の温度が必要である。素子分離を確実なものとするために、基板には予め不純物が所定のプロファイルでドーピングされることが通常であるが、熱酸化法による800℃以上の処理では不純均の再拡散等が発生して、問題を引き起こす傾向があった。

【0007】

本発明の目的は、上記した従来技術の欠点を解消した酸化膜形成方法および酸化膜形成装置、および良質な酸化膜を有する電子デバイス材料を提供することにある。

【0008】

本発明の他の目的は、酸化膜の膜厚コントロールが容易で、且つ、良質な酸化膜を与える酸化膜形成方法および酸化膜形成装置、およびこのような良質な酸化膜を有する電子デバイス材料を提供することにある。

【0009】

本発明の更に他の目的は、被処理体に対する熱的ダメージを最小限に抑制することが可能な酸化膜形成方法および酸化膜形成装置、およびこのような良質な酸化膜を有する電子デバイス材料を提供することにある。

【0010】

【課題を解決するための手段】

本発明者は鋭意研究の結果、少なくとも水蒸気を含む処理ガスの存在下で、被処理体にプラズマを照射することが、上記目的の達成のために極めて効果的なことを見出した。

【0011】

本発明の酸化膜形成方法は上記知見に基づくものであり、より詳しくは、水蒸気を少なくとも含む処理ガスの存在下で、プラズマを電子デバイス用基材の表面に照射して、該電子デバイス用基材の表面に酸化膜を形成することを特徴とするものである。

【0012】

本発明によれば、更に、電子デバイス用基材を所定位置に配置するための処理チャンバと;該処理チャンバ内に水蒸気を供給するための水蒸気供給手段と、該水蒸気をプラズマ励起するためのプラズマ励起手段とを少なくとも含み;前記水蒸気に基づくプラズマを電子デバイス用基材の表面に照射すること可能としたことを特徴とする酸化膜形成装置が提供される。

【0013】

本発明によれば、更に、少なくとも1つのトレンチ溝を有する電子デバイス用基材と;該電子デバイス用基材の面の一部であって、且つ前記トレンチ溝の少なくとも1つを含む部分を覆う酸化膜とを有する電子デバイス材料であって、且つ;前記トレンチ溝を覆う酸化膜において、電子デバイス材料の(100)面上に形成された酸化膜の厚さT100と、(110)面上に形成された酸化膜の厚さT110との比(T100/T110)が0.65以上である電子デバイス用基材が提供される。

【0014】

上記構成を有する本発明の酸化膜形成においては、少なくとも水蒸気を含む処理ガス(必要に応じて、O2および/又は(O2+H2)を更に含む)の存在下でプラズマ照射している。本発明者の知見によれば、被処理体を収容する処理チャンバ導入前にH2Oを生成させた際には、そのプラズマ発光の分光分析結果からより多くのOH基が生成していることが確認されている(後述する図20のグラフ)。このような多くのOH基の存在に基づき、本発明においては信頼性の高い酸化膜が例えば500℃以下の低温でも形成可能となると推定される。

【0015】

加えて、本発明によれば、従来の熱反応酸化とは異なり、プラズマにより活性化された酸化種の供給によりシリコンを酸化し、熱反応、熱拡散に依存しない処理方法であるため電子デバイス基材表面の面方位に対する依存性が比較的に小さい酸化が可能となるため、結果として、三次元構造(例えば、トレンチ溝)を有する基材表面上においても、より均一な膜厚の酸化膜を形成することが容易となる。

【0016】

【発明の実施の形態】

以下、必要に応じて図面を参照しつつ本発明を更に具体的に説明する。以下の記載において量比を表す「部」および「%」は、特に断らない限り質量基準とする。

【0017】

(酸化膜の形成方法)

本発明においては、水蒸気を少なくとも含む処理ガスの存在下で、プラズマを電子デバイス用基材の表面に照射して、該電子デバイス用基材の表面に酸化膜を形成する。

【0018】

(電子デバイス用基材)

本発明において使用可能な電子デバイス用基材は特に制限されず、公知の電子デバイス用基材の1種、または該基材の2種以上の組合せから適宜選択して使用することが可能である。このような電子デバイス用基材の例としては、例えば、半導体材料、液晶デバイス材料等が挙げられる。半導体材料の例としては、例えば、単結晶シリコンを主成分とする材料、多結晶シリコンを主成分とする材料、窒化シリコンを主成分とする材料等が挙げられる。

【0019】

(酸化膜)

本発明においては、上記した電子デバイス用基材上に配置されるべき酸化膜は、該電子デバイス用基材の酸化により形成可能である限り、特に制限されない。このような酸化膜は、公知の電子デバイス用酸化膜の1種または2種以上の組合せとすることができる。

【0020】

(処理ガス)

本発明において酸化膜形成の際には、処理ガスは、少なくとも水蒸気を含む。必要に応じて、他のガス(例えば、不活性ガスないし希ガス)を併用してもよい。この際に使用可能な希ガスは特に制限されず、公知の希ガス(ないしはその2種類以上の組合せ)から適宜選択して使用することができる。生産性の点からは、希ガスとしてアルゴン、またはヘリウムネオン、クリプトンが好適に使用可能である。

【0021】

(水蒸気)

本発明においては、マイクロ波プラズマとの併用により電子デバイス用基材上に酸化膜を形成可能な水蒸気(ないし水)である限り、その性状、生成方法、等は特に制限されない。

【0022】

本発明において好適に使用可能な水ないし水蒸気(通常は純水レベル)としては、例えば、以下に示す方法が挙げられる。

【0023】

(1)水蒸気発生器(WVG;Water Vapor Generator)を用いる方法。

【0024】

(2)発熱(pyrogenic)反応を用いる方法。

【0025】

(3)バブリングを用いて、純水から水蒸気を得る方法。

【0026】

(酸化膜の形成条件)

本発明を酸化膜の形成に用いる態様においては、形成されるべき酸化膜の特性の点からは、下記の条件が好適に使用できる。

(1) H2O:1.67×10 −8 〜1.67×10 −7 m 3 /s(1〜10sccm)、より好ましくは8.33×10 −8 m 3 /s(5sccm)(希ガスに対して、0.2〜2体積%程度、更には1体積%程度が好ましい)、

(2) 希ガス(例えば、Kr、Ar、またはHe):4.17×10 −6 〜1.67×10 −5 m 3 /s(250〜1000sccm)、特に好ましくは8.33×10 −6 m 3 /s(500sccm)

(3) 温度:室温(25℃)〜500℃、特に好ましくは400℃

(4) 圧力:6.67〜266Pa(50〜2000mTorr)、特に好ましくは133Pa(1000mTorr)

(5) マイクロ波:2.4〜4.9W/cm2、より好ましくは4.3W/cm2

一般的に、半導体基板上にデバイス素子を形成するために、予め基板に不純物を拡散させ、活性領域、素子分離領域を設ける場合が多い。しかしながら、従来の熱酸化手法では、上述したようにその処理の際の高温により、不純物領域をこわす可能性があり問題であった。

【0027】

これに対して、本発明は低温処理が可能であるため、不純物領域の保護とともに、熱によるダメージ、歪み等も抑制することができる。また、本発明により形成した酸化膜上に、更に所望の膜(例えばCVD)を比較的低温(500℃程度)で成膜した後の酸化工程にも、本発明の酸化膜形成方法は好適に使用可能であるため、工程管理も容易になる。

【0028】

(酸化膜を有する電子デバイス材料)

本発明によれば、少なくとも1つのトレンチ溝を含み、該トレンチ溝を含む電子デバイス用基材の面の少なくとも一部を覆う酸化膜とを有する電子デバイス材料を好適に製造することができる。ここに、「トレンチ溝」とは、電子デバイス材料に形成された溝である。また、このトレンチ溝は、酸化膜形成時には電子デバイス用基材の表面にあるが、酸化膜形成後には、該トレンチ溝の上に他の層、他の構造等が形成されていてもよい。

【0029】

上記電子デバイス材料においては、前記トレンチ溝を覆う酸化膜において、(100)面上に形成された酸化膜の厚さT100と、(110)面上に形成された酸化膜の厚さT110との比(T100/T110)が1に近いことが好ましい。

【0030】

(酸化膜形成装置)

本発明の酸化膜形成装置は、電子デバイス用基材を所定位置に配置するための処理チャンバと;該処理チャンバ内に水蒸気を供給するための水蒸気供給手段と;該水蒸気をプラズマ励起するためのプラズマ励起手段とを少なくとも含み;前記水蒸気に基づくプラズマを電子デバイス用基材の表面に照射すること可能としたものである。本発明において、上記プラズマ励起手段は特に制限されないが、プラズマダメージの点からは、スタンドアローン(電界フリー)型のプラズマ励起手段(例えば、マイクロ波照射を利用するもの)であることが好ましい。また、均一な酸化膜形成を行う点からは、(スタンドアローン型のプラズマの中でも)平面アンテナ部材を介してマイクロ波を照射するプラズマ励起手段であることが特に好ましい。

【0031】

(平面アンテナ部材)

本発明においては、複数のスリットを有する平面アンテナ部材を介してマイクロ波を照射することにより電子温度が低く且つ高密度なプラズマを形成し、このプラズマを用いて前記被処理基体表面に酸化膜形成を行うことが好ましい。このような態様においては、プラズマダメージが小さく、且つ低温で反応性の高いプロセスが可能である。

【0032】

このような多数のスリットを有する平面アンテナを備え、且つ電子温度が低く、プラズマダメージが小さく、また、密度の高いプラズマを発生させる能力を有するマイクロ波プラズマ装置の詳細に関しては、例えば文献(Ultra Clean technology Vol.10 Supplement 1,p.32,1998,Published by Ultra Clean Society)を参照することができる。

【0033】

このような新しいプラズマ装置を用いると、電子温度は1.5eV程度以下、プラズマシース電圧も数V以下のプラズマが容易に得られるため、従来のプラズマ(プラズマシース電圧が50V程度)に対して、プラズマダメージを大幅に低減できる。この平面アンテナを備える新しいプラズマ装置は、300〜700℃程度の温度でも高密度のラジカルを供給できる能力を有しているため、加熱によるデバイス特性の劣化を抑制でき、且つ低温でも高い反応性を有するプロセスが可能となる。

【0034】

(好適なプラズマ)

本発明において好適に使用可能なプラズマの特性は、以下の通りである。

(1) 電子温度:1.0eV以下

(2) 密度:1×1012(1/cm3)以上

(3) プラズマ密度の均一性:平面アンテナ直下で±5%以下

上記したように本発明の方法によれば、膜厚コントロールが容易で(薄い膜、または厚い膜のいずれでも)、しかも良質な酸化膜を形成することができる。したがって、この酸化膜上に他の層(例えば、電極層)を形成することにより、特性に優れた半導体デバイスの構造を形成することが容易となる。

【0035】

本発明のプロセスによれば、膜厚10nm程度の信頼性の高い酸化膜形成が可能であるため、素子分離用トレンチ溝の下地酸化以外にMOS型半導体のゲート酸化膜等にも適用できる。

【0036】

(製造方法の一態様)

次に、本発明の酸化膜形成方法の一態様について説明する。

【0037】

図1は本発明の酸化膜形成方法を実施するための半導体製造装置30の全体構成の一例を示す概略図(模式平面図)である。

【0038】

図1に示すように、この半導体製造装置30のほぼ中央には、ウエハW(図3)を搬送するための搬送室31が配設されており、この搬送室31の周囲を取り囲むように、ウエハに種々の処理を行うためのプラズマ処理ユニット32、33、各処理室間の連通/遮断の操作を行うための二機のロードロックユニット34および35、種々の加熱操作を行うための加熱ユニット36、およびウエハに種々の加熱処理を行うための加熱反応炉47が配設されている。なお、加熱反応炉47は、上記半導体製造装置30とは別個に独立して設けてもよい。

【0039】

ロードロックユニット34、35の横には、種々の予備冷却ないし冷却操作を行うための予備冷却ユニット45、冷却ユニット46がそれぞれ配設されている。

【0040】

搬送室31の内部には、搬送アーム37および38が配設されており、前記各ユニット32〜36との間でウエハW(図3)を搬送することができる。

【0041】

ロードロックユニット34および35の図中手前側には、ローダーアーム41および42が配設されている。これらのローダーアーム41および42は、更にその手前側に配設されたカセットステージ43上にセットされた4台のカセット44との間でウエハWを出し入れすることができる。

【0042】

なお、図1中のプラズマ処理ユニット32、33としては、同型のプラズマ処理ユニットが二基並列してセットされている。

【0043】

更に、これらプラズマ処理ユニット32およびユニット33は、ともにシングルチャンバ型プラズマ処理ユニットと交換することが可能であり、プラズマ処理ユニット32や33の位置に一基または二基のシングルチャンバ型プラズマ処理ユニットをセットすることも可能である。

【0044】

プラズマ処理が二基の場合、例えば、処理ユニット32でSiO2膜を形成した後、処理ユニット33でSiO2膜を表面窒化する方法を行っても良く、また処理ユニット32および33で並列にSiO2膜形成とSiO2膜の表面窒化を行っても良い。或いは別の装置でSiO2膜形成を行った後、処理ユニット32および33で並列に表面窒化を行うこともできる。

【0045】

(ゲート絶緑膜成膜の一態様)

図2は酸化膜の成膜に使用可能なプラズマ処理ユニット32(33)の垂直方向の模式断面図であり、図3は、図2の装置に好適に使用可能な水蒸気供給手段の一例を示すブロック図である。

【0046】

図2を参照して、参照番号50は、例えばアルミニウムにより形成された処理チャンバである。この処理チャンバ50の上面には、基板(例えばウエハW)よりも大きい開口部51が形成されており、この開口部51を塞ぐように、例えば石英や窒化アルミ等の誘電体により構成された偏平な円筒形状の天板54が設けられている。この天板54の下面である処理チャンバ50の上部側の側壁には、例えばその周方向に沿って均等に配置した16ケ所の位置にガス供給管72が設けられており、このガス供給管72から、少なくとも水蒸気H2O(更には、必要に応じて希ガス等の不活性ガス)を含む処理ガスが、処理チャンバ50のプラズマ領域P近傍にムラなく均等に供給されるようになっている。

【0047】

図3を参照して、本発明において好適に使用可能な水蒸気供給手段の一態様たるWVG(水蒸気発生器)の一方の側には、酸素ガスおよび水素ガスが供給可能とされている。WVGの他方は、オリフィスを介して処理チャンバ50に接続され、該処理チャンバ50内に水蒸気が供給可能とされている。

【0048】

このような水分発生器を使用する場合、下記の反応に基づいて被処理体の酸化を行うことができる。

【0049】

【化1】

【0050】

一般的にH2とO2の燃焼反応は、図4に示す圧力−温度特性が知られている。処理の安全性と、水分発生器、酸化処理の各条件を満たすためには、水分発生器は、大気圧付近の操作

酸化処理は、133Pa付近の操作が好ましく、処理チャンバと水分発生器は、オリフィスにより差圧をつける必要がある。

【0051】

天板54の外側には、複数のスリットを有する平面アンテナ部材、例えば銅板により形成されたスロットプレインアンテナ(Slot Plane Antenna)60を介して、高周波電源部をなし、例えば2.45GHzのマイクロ波を発生するマイクロ波電源部61に接続された導波路63が設けられている。この導波路63は、SPA60に下縁が接続された偏平な円形導波管63Aと、この円形導波管63Aの上面に一端側が接続された円筒形導波管63Bと、この円筒形導波管63Bの上面に接統された同軸導波変換器63Cと、この同軸導波変換器63Cの側面に直角に一端側が接続され、他端側がマイクロ波電源部61に接続された矩形導波管63Dとを組み合わせて構成されている。

【0052】

ここで、本発明においては、UHFとマイクロ波とを含めて高周波領域と呼ぶものとする。すなわち、高周波電源部より供給される高周波電力は300MHz以上のUHFや1GHz以上のマイクロ波を含む、300MHz以上2500MHz以下のものとし、これらの高周波電力により発生されるプラズマを高周波プラズマと呼ぶものとする。

【0053】

前記円筒形導波管63Bの内部には、導電性材料からなる軸部62の、一端側がSPA60の上面のほぼ中央に接続し、他端側が円筒形導波管63Bの上面に接続するように同軸状に設けられており、これにより当該導波管63Bは同軸導波管として構成されている。

【0054】

また処理チャンバ50内には、天板54と対向するようにウエハWの載置台52が設けられている。この載置台52には図示しない温調部が内蔵されており、これにより当該載置台52は熱板として機能するようになっている。更に処理チャンバ50の底部には排気管53の一端側が接続されており、この排気管53の他端側は真空ポンプ55に接続されている。

【0055】

(平面アンテナ部材の一態様)

図5は本発明の電子デバイス材料の製造装置に使用可能な平面アンテナ部材60の一例を示す模式平面図である。

【0056】

この図5に示したように、この平面アンテナ部材60では、表面に複数のスロット60a、60a、…が同心円状に形成されている。各スロット60aは略方形の貫通した溝であり、隣接するスロットどうしは互いに直交して略アルファベットの「T」の文字を形成するように配設されている。スロット60aの長さや配列間隔は、マイクロ波電源部61より発生したマイクロ波の波長に応じて決定されている。

【0057】

(加熱反応炉の一態様)

図6は本発明の電子デバイス材料の製造装置に使用可能な加熱反応炉47の一例を示す垂直方向の模式断面図である。

【0058】

図6に示すように、加熱反応炉47の処理室82は、例えばアルミニウム等により気密可能な構造に形成されている。この図6では省略されているが、処理室82内には加熱機構や冷却機構を備えている。

【0059】

図6に示したように、処理室82には上部中央にガスを導入するガス導入管83が接続され、処理室82内とガス導入管83内とが連通されている。また、ガス導入管83はガス供給源84に接続されている。そして、ガス供給源84からガス導入管83にガスが供給され、ガス導入管83を介して処理室82内にガスが導入されている。このガスとしては、ゲート電極形成の原料となる、例えばシラン等の各種のガス(電極形成ガス)を用いることができ、必要に応じて、不活性ガスをキャリアガスとして用いることもできる。

【0060】

処理室82の下部には、処理室82内のガスを排気するガス排気管85が接続され、ガス排気管85は真空ポンプ等からなる排気手段(図示せず)に接続されている。この排気手段により、処理室82内のガスがガス排気管85から排気され、処理室82内が所望の圧力に設定されている。

【0061】

また、処理室82の下部には、ウエハWを載置する載置台87が配置されている。

【0062】

この図6に示した態様においては、ウエハWと略同径大の図示しない静電チャックによりウエハWが載置台87上に載置されている。この載置台87には、図示しない熱源手段が内設されており、載置台87上に載置されたウエハWの処理面を所望の温度に調整できる構造に形成されている。

【0063】

この載置台87は、必要に応じて、載置したウエハWを回転できるような機構になっている。

【0064】

図6中、載置台87の右側の処理室82壁面にはウエハWを出し入れするための開口部82aが設けられており、この開口部82aの開閉はゲートバルブ98を図中上下方向に移動することにより行われる。図6中、ゲートバルブ98の更に右側にはウエハWを搬送する搬送アーム(図示せず)が隣設されており、搬送アームが開口部82aを介して処理室82内に出入りして載置台87上にウエハWを載置したり、処理後のウエハWを処理室82から搬出するようになっている。

【0065】

載置台87の上方には、シャワー部材としてのシャワーヘッド88が配設されている。このシャワーヘッド88は載置台87とガス導入管83との間の空間を区画するように形成されており、例えばアルミニウム等から形成されている。

【0066】

シャワーヘッド88は、その上部中央にガス導入管83のガス出口83aが位置するように形成され、シャワーヘッド88下部に設置されたガス供給孔89を通し、処理室82内にガスが導入されている。

【0067】

(酸化膜形成の態様)

次に、上述した装置を用いて、ウエハW(例えば、シリコン基材)上に酸化膜を形成する方法の好適な一例について説明する。

【0068】

図1を参照して、まずプラズマ処理ユニット32(図1)内の処理チャンバ50の側壁に設けたゲートバルブ(図示せず)を開いて、搬送アーム37、38によりウエハWを載置台52(図2)上に載置する。

【0069】

続いてゲートバルブを閉じて内部を密閉した後、載置台52の温度を調節してウエハWを例えば400℃に加熱する。この際、加熱時間の短縮と均一性を目的として、ガス供給管72より酸化膜形成時の処理ガスであるアルゴン等の希ガスと水蒸気を例えばそれぞれ8.33×10 −6 m 3 /s(500sccm)、8.33×10 −8 m 3 /s(5sccm)の流量で導入して圧力を例えば133Paまで昇圧することで、載置台とウエハ間の熱伝導効率を上げ第1の工程(予備加熱)を実施する。

【0070】

第1工程が終了すると、マイクロ波電源61より、例えば2.45GHz(3500W)のマイクロ波を発生させ、このマイクロ波を導波路より案内して平面アンテナ部材60および天板54を介して処理チャンバ50内に導入し、これにより処理チャンバ50内の上部側のプラズマ領域Pにてプラズマを発生させる。

【0071】

ここでマイクロ波は矩形導波管63D内を矩形モードで伝送し、同軸導波変換器63Cにて矩形モードから円形モードに変換され、円形モードで円筒形同軸導波管63Bを伝送し、更に円形導波管63Aにて拡げられた状態で伝送していき、平面アンテナ部材60のスロット60aより放射され、天板54を透過して処理チャンバ50に導入される。この際マイクロ波を用いているため高密度のプラズマが発生し、またマイクロ波を平面アンテナ部材60の多数のスロット60aから放射しているため、このプラズマが高密度なものとなる。

【0072】

(水蒸気供給の一態様)

図7〜9のグラフを参照しつつ、本発明において好適に使用可能な水蒸気供給の一態様について説明する。この水蒸気供給は、(1)予備排気工程、(2)予熱工程および(3)酸化工程を含むことが好ましい。

【0073】

(予備排気工程)

図7を参照して、少なくとも水蒸気を含む処理ガスを処理チャンバ50に供給するに際しては、該供給の前に、予め処理チャンバ50を真空引き(133mPa程度)して、以前の履歴が残存することを防止することが好ましい。この真空引きの時間は、種々の要因によっても異なるが、履歴の残存防止とプロセス効率とのバランスの点からは、例えば、0.5〜1分程度であることが好ましい。以前の履歴残存防止とプロセス効率のバランスから、例えば133mPa、0.5〜1分が実験的に好ましい。

【0074】

(予熱工程)

次いで、処理チャンバ50内の処置位置に被処理体(例えば、ウエハW)を配置して、水蒸気を含む処理ガスの該処理チャンバ50内への供給を開始する。この際の圧力は、例えば、133Pa程度とすることが好ましい。

【0075】

このように被処理体を配置し、更にガス供給を開始した後に、予熱ステップを開始する。この際、導入ガスの熱伝導を利用して被処理体を加熱するため、より高圧が好ましいが、プロセスフローの簡易化と効率の面から、酸化処理条件と同一条件で予熱工程を実施してもよい。例えば、400℃、133Pa、1.5〜2.0分が実験的に好ましい。

【0076】

(酸化工程)

上記した予熱ステップの後にプラズマを着火して、被処理体の処理を開始する。上記の操作により、処理ガス流量、処理圧力は整っているため、プラズマのみを着火して本工程に移ることができる。

【0077】

(予熱時間と仕上がり酸化膜厚の関係)

所定の酸化処理に対する予熱時間の依存性の一例を図8に示す。

【0078】

予熱が不充分な場合には、仕上がり膜厚が薄く、プロセス再現性等に問題が残る場合がある。

【0079】

(処理ガス導入タイミングとプラズマ発光(酸素発光)の関係)

図9に処理ガス導入タイミングとプラズマ発光との関係の一例を示す。プラズマ着火に際して、充分な酸化ガス雰囲気が形成されない場合には、酸化処理工程の立ち上がりが不安定となり、プロセス安定性に問題が残る場合がある。

【0080】

(水蒸気供給の他の態様)

図10の模式断面図に、本発明における水蒸気供給の他の態様を示す。この態様においては、水蒸気を、プラズマから「隠れた」(すなわち、プラズマから見て影になる)処理チャンバ50の位置から、水蒸気を供給している。一般的に、真空チャンバのガス供給口近傍では、ガス流れから、ガス濃度差、圧力差が発生しやすく、プラズマが不安定になりやすい傾向がある。不安定なプラズマは、場合によっては異常放電へ発展する可能性があり、局在化した異常放電は、その強い電界でチャンバ構成材をたたき、被処理体へのコンタミネーションを発生させる傾向がある。したがって、図10の態様は、プラズマの安定放電に対して有効であり、被処理体へのコンタミネーション防止となる。

【0081】

図10を参照して、このような態様においては、処理チャンバ50の上部は、アルミニウム製のアッパープレート21と、そのアッパープレート21上に配置されたセラミック(例えば、アルミナAl2O3)製の天板22から構成される。図10に示すように、プラズマPから「隠れた」(すなわち、プラズマから見て影になる)チャンバ50の壁の位置に、水蒸気(必要に応じて、更に希ガス)供給用の供給管72が配置されている。

【0082】

(プラズマ処理装置の他の態様)

図11は、本発明に係るプラズマ処理装置の他の例を示す模式断面図である。図11を参照して、この態様は、アンテナ部材として、平面アンテナ部材を用いた例である。

【0083】

図11に示すように、このプラズマ処理装置100は、例えば側壁101aや底部101bがアルミニウム等の導体により構成されて、全体が筒体状に成形されたプラズマ処理室101を有しており、プラズマ処理室101の内部は密閉された処理空間として構成されている。

【0084】

このプラズマ処理室101内には、その上面に被処理体(例えば半導体ウエハW)を載置するための載置台102が収容される。この載置台102は、例えばアルマイト処理したアルミニウム等により凸状に平坦になされた略円柱状に形成されている。

【0085】

上記した載置台102の上面には、ここにウエハWを保持するための静電チャックまたはクランプ機構(図示せず)が設けられる。更に、この載置台102は給電線(図示せず)を介してマッチングボックス(図示せず)およびバイアス用高周波電源(例えば1356MHz用;図示せず)に接続されている。なお、CVDの場合には、このバイアス用高周波電源44を設けなくてもよい。

【0086】

他方、上記プラズマ処理室101の側壁には、ガス供給手段として、容器内に前述した水蒸気含有ガスを導入するためのガス供給ノズル103が設けられる。

【0087】

プラズマ処理室101の天井部は開口されて、ここに例えば石英、Al2O3等のセラミック材からなり、マイクロ波に対しては透過性を有する絶縁板104(例えば厚さが20mm程度)がO−リング等のシール部材(図示せず)を介して気密に設けられる。

【0088】

この絶縁板104の上面に、円板状の平面アンテナ部材105と高誘電率特性を有する遅波材106(石英、Al2O3、AiN等からなる)とが設けられる。この平面アンテナ部材105に対しては、同軸導波管107からマイクロ波が伝播される。マイクロ波の周波数は2.45GHzに限定されず、他の周波数、例えば8.35GHzを用いてもよい。

【0089】

図12は、図11の構成を更に詳細に示した例を示す模式断面図である。図12に示すように、このプラズマ処理装置100aは、例えば側壁101aや底部101bがアルミニウム等の導体により構成されて、全体が筒体状に成形されたプラズマ処理室101を有しており、プラズマ処理室101の内部は密閉された処理空間として構成されている。

【0090】

このプラズマ処理室101内には、その上面に被処理体(例えば半導体ウエハW)を載置するための載置台(ステージ)102が収容される。この載置台102は、ウエハWを必要に応じて加熱するためのヒータ(図示せず)を内蔵している。

【0091】

他方、上記プラズマ処理室101の側壁には、ガス供給手段として、容器内に前述した水蒸気含有ガスを導入するためのガス供給ノズル103が設けられる。この図12においては、処理ガス整流化のために、載置台と同じ高さ程度の位置に、側壁101aとほぼ垂直にガスバッフル板109が配置され、更に、側壁101aおよびガスバッフル板109の内側には、金属汚染防止のためのライナー(石英製)が配置されている。

【0092】

プラズマ処理室101の天井部の開口には、例えば石英、Al2O3等のセラミック材からなり、マイクロ波に対しては透過性を有する絶縁板104(例えば厚さが20mm程度)がO−リング等のシール部材(図示せず)を介して気密に設けられる。

【0093】

この絶縁板104の上面に、円板状の平面アンテナ部材105と高誘電率特性を有する遅波材106(石英、Al2O3、AiN等からなる)とが設けられる。この上記高誘電率特性を有する遅波材106の波長短縮効果により、マイクロ波の管内波長を短くすることができる。

【0094】

この図12においては、遅波材106上に、該遅波材106等を冷却するための冷却プレート112が配置され、その冷却プレート112内部、および側壁101a内部には、これらの部材を冷却するための冷媒通路113が設けられている。

【0095】

上記の平面アンテナ部材105に対しては、上述したように、同軸導波管107からマイクロ波(周波数2.45GHz等)が伝播される。

【0096】

(トレンチ溝利用の一態様)

従来より、電子デバイス基材上に形成された素子間の分離には、該基材上に局所的に形成された酸化膜によって分離する、いわゆるLOCOS(Local Oxidation of Silicon)処理が主流であった(図13にLOCOSにより得られた素子分離の模式断面図を示す)。しかしながら、このLOCOSを用いた際には、リークパスが出来やすく、しかもLOCOSによる素子分離のサイズが小さくならざるを得ないという短所があった。

【0097】

そこで、近年では素子間の位置にトレンチ溝を形成し、該トレンチ溝の内部に酸化膜を形成して素子分離する、いわゆるSTI(Shallow Trench Isolation)が広く用いられつつある(図14にSTIにより得られた素子分離の模式断面図を示す)。このSTI技術を用いた場合には、上記したLOCOSと較べて、より深く、確実な素子分離ができる。しかしながら、他方、従来の熱酸化を用いた際には、この様なトレンチ溝表面に均一な厚さで酸化膜を形成することが困難なため、素子分離機能の観点から、成長速度の遅い面方位に対して最低膜厚を得るためには、不必要に厚い酸化膜が形成される面方位が発生する。

【0098】

酸化膜の膜厚差は応力を発生させ、その膜の信頼性を低下させたり、後の工程でかかる熱ストレスによって破断する可能性もある。また、不必要に厚い膜は、微細化に対する防げともなる。これに対して、本発明では、面方位に依存しない均一で、信頼性の高い酸化膜を形成することができる。

【0099】

【実施例】

以下、実施例により本発明を更に具体的に説明する。

【0100】

実施例1

(酸化膜形成)

本発明の酸化膜形成方法により、シリコン基板上に酸化膜を形成した。この酸化膜形成においては、図1および11〜12に示したような平面アンテナ部材を有する処理チャンバを用いた。

【0101】

(基板)

シリコン基板としては、比抵抗8Ωcm、直径200mmのP型、面方位(100)の単結晶シリコン基板(ウエハ)を用いた。

【0102】

(前洗浄)

シリコン基板を次の手順で洗浄を行った。

【0103】

1.アンモニア過水溶液浸漬(10分)

2.純水リンス

3.塩酸過水溶液浸漬(10分)

4.純水リンス

5.希弗酸溶液浸漬(8分)

6.純水リンス

7.窒素ガス乾燥

(プラズマ酸化処理)

マイクロ波出力:3500W

チャンバ圧力:133Pa

基板温度:400℃

希ガス流量:Ar=8.33×10 −6 m 3 /s(500sccm)

H2O流量:8.33×10 −8 m 3 /s(5sccm)

(処理時間と酸化膜厚の測定)

酸化膜厚は光学式膜厚計(エリプソメトリィ法)を用いて測定を行った。得られた処理時間と膜厚の関係を図15のグラフに示す。

【0104】

実施例2(結晶方位依存性の測定)

予めトレンチ溝が加工されているシリコン基板を用いて、実施例1と同様の前洗浄とプラズマ処理を行った。

【0105】

酸化膜厚の結晶方位依存性は、トレンチ溝の酸化膜断面をTEM観察し測定を行った。測定結果を下記(表1)および図16のTEM写真に示す。

【0106】

【表1】

【0107】

比較例

上記測定により得られたデータを熱酸化法と比較を行った。

【0108】

熱酸化法のデータは、徳山巍著「エレクトロニクス技術全書(3)MOSデバイス」のデータを引用した。

【0109】

本発明により得られた結果と、比較例との比較を図17のグラフに示す。

【0110】

実施例3(酸化膜質の確認)

図18の模式断面図に示したように、実施例1にて作成した酸化膜上にポリシリコンを堆積させ、膜質評価用のサンプルを製作した。

【0111】

上記のサンプルを用いて酸化膜の電気的信頼性評価を実施した。

【0112】

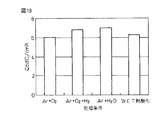

この評価は酸化膜に一定電流(0.1A/cm2)が基板からポリシリコンへ流れるよう(電子はポリシリコンから基板へ流れる)ポリシリコンに電圧を印可して、酸化膜が破壊するまでの時間測定を行った。酸化膜破壊までの電流は一定であるため、評価スケールは、(電流)×(時間)=(電気量:Qbd)で表した。測定結果を図19のグラフに示す。破壊に至るまでの電気量が大きい酸化膜ほど、信頼性の高いものと評価できる。

【0113】

(試験条件)

定電流ストレス:−0.1A/cm2

評価温度:120℃

評価サイズ:10000μm2

【0114】

【発明の効果】

上述したように本発明によれば、酸化膜の膜厚コントロールが容易で、且つ、良質な酸化膜を与える酸化膜形成方法および酸化膜形成装置、およびこのような良質な酸化膜を有する電子デバイス材料が提供される。

【0115】

本発明において、特に低温(500℃以下)の温度を用いて酸化膜形成する態様は、大口径(300mm)の電子デバイス用基材(従来においては、小口径(200mm)のものに比べて、均一に加熱/冷却することが格段に困難であった)を用いる場合に特にメリットがある。すなわち、本発明において低温処理した場合には、このような大口径の電子デバイス用基材(ウエハ)において発生する可能性がある欠陥の発生を最小限とすることが容易である。

【図面の簡単な説明】

【図1】本発明の酸化膜形成方法を実施するための半導体製造装置の一例を示す模式平面図である。

【図2】本発明の酸化膜形成方法に使用可能なスロットプレインンアンテナ(平面アンテナ部材)プラズマ処理ユニットの一例を示す模式的な垂直断面図である。

【図3】本発明の酸化膜形成方法に水蒸気発生器(WVG)の一例を示すブロック図である。

【図4】酸素、水素混合ガスの爆発範囲と、水分発生器操作範囲、プロセス範囲を示すグラフ図である。

【図5】本発明の酸化膜形成方法に使用可能な平面アンテナ部材の一例を示す模式的な平面図である。

【図6】本発明の電子デバイス製造方法に使用可能なプラズマ処理ユニットの模式的な垂直断面図である。

【図7】本発明の酸化膜形成方法において好適に使用可能な真空引き、予熱、プラズマ処理のステップ例の一例を示すグラフである。

【図8】本発明の酸化膜形成方法で得られた酸化膜厚さと、処理ガス予熱時間との関係の一例を示すグラフである。

【図9】本発明の酸化膜形成方法で得られたO2プラズマ発光強度と、処理ガス予熱時間との関係の一例を示すグラフである。

【図10】本発明の酸化膜形成方法に好適に使用可能な水蒸気供給手段の他の例を示す模式斜視図である。

【図11】本発明に係るプラズマ処理装置の他の例を示す模式断面図である。

【図12】図11のプラズマ処理装置の詳細な構成の一例を示す模式断面図である。

【図13】従来のLOCOSにより得られる素子分離の一例を示す模式断面図である。

【図14】STIにより得られるトレンチ溝による素子分離の一例を示す模式断面図である。

【図15】本発明における酸化膜厚と、処理時間との関係の一例を示すグラフである。

【図16】本発明の酸化膜形成方法により得られたトレンチ溝近傍の酸化膜の厚さ分布示すTEM写真である。

【図17】本発明の酸化膜形成方法と、従来の熱酸化法で得られた酸化膜の結晶面方位依存性の比較を示すグラフである。

【図18】実施例3で用いた膜質評価の方法を説明するための模式断面図である。

【図19】実施例3で得られた膜質評価の結果を示すグラフである。

【図20】本発明におけるプラズマ発光の分析結果の例を示すグラフである。

【図21】従来の熱酸化により得られるトレンチ溝上の酸化膜厚さの一例を示す模式断面図である。

【図22】本発明のプラズマ酸化により得られるトレンチ溝上の酸化膜厚さの一例を示す模式断面図である。

【符号の説明】

W…ウエハ(被処理基体)

60…平面アンテナ部材(平面アンテナ部材)

2…酸化膜

2a…窒素含有層

32…プラズマ処理ユニット(プロセスチャンバ)

33…プラズマ処理ユニット(プロセスチャンバ)

47…加熱反応炉

Claims (2)

- トレンチ溝を有する電子デバイス用基材が配置された処理チャンバ内を真空引きにより排気し、

前記処理チャンバ内において、水蒸気及びアルゴンを少なくとも含む処理ガスの存在下で、前記電子デバイス用基材がプラズマ処理の所定の温度に達した後に、更に前記電子デバイス用基材を少なくとも30秒の間予備加熱し、

前記処理チャンバ内において、前記処理ガスの存在下で、水蒸気の濃度はアルゴンに対して0.2〜2体積%であり、温度25〜500℃且つ圧力6.67〜266Paにおいて、複数のスリットを有する平面アンテナ部材を介するマイクロ波照射に基づくプラズマを前記電子デバイス用基材の表面に照射して、該電子デバイス用基材の表面に酸化膜を形成することを特徴とする酸化膜形成方法。 - シリコンの(100)面及び(110)面を含むトレンチ溝を有する電子デバイス用基材が配置された処理チャンバ内を真空引きにより排気し、

前記処理チャンバ内において、酸素及び水素及びアルゴンを少なくとも含む処理ガスの存在下で、前記電子デバイス用基材がプラズマ処理の所定に温度の達した後に、更に前記電子デバイス用基材を少なくとも30秒の間予備加熱し、

前記処理チャンバ内において、前記処理ガスの存在下で、温度25〜500℃且つ圧力6.67〜266Paにおいて、複数のスリットを有する平面アンテナ部材を介するマイクロ波照射に基づくプラズマを前記電子デバイス用基材の表面に照射して、該電子デバイス用基材の表面に、前記トレンチ溝の(100)面上に形成された酸化膜の厚さT100と、(110)面上に形成された酸化膜の厚さT110との比(T100/T110)が0.65以上である酸化膜を形成することを特徴とする酸化膜形成方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003146228A JP4694108B2 (ja) | 2003-05-23 | 2003-05-23 | 酸化膜形成方法、酸化膜形成装置および電子デバイス材料 |

| US10/849,883 US20050005844A1 (en) | 2003-05-23 | 2004-05-21 | Process and apparatus for forming oxide film, and electronic device material |

| US11/508,871 US7632758B2 (en) | 2003-05-23 | 2006-08-24 | Process and apparatus for forming oxide film, and electronic device material |

| US12/612,471 US20100048033A1 (en) | 2003-05-23 | 2009-11-04 | Process And Apparatus For Forming Oxide Film, And Electronic Device Material |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003146228A JP4694108B2 (ja) | 2003-05-23 | 2003-05-23 | 酸化膜形成方法、酸化膜形成装置および電子デバイス材料 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004349546A JP2004349546A (ja) | 2004-12-09 |

| JP2004349546A5 JP2004349546A5 (ja) | 2006-05-18 |

| JP4694108B2 true JP4694108B2 (ja) | 2011-06-08 |

Family

ID=33533147

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003146228A Expired - Fee Related JP4694108B2 (ja) | 2003-05-23 | 2003-05-23 | 酸化膜形成方法、酸化膜形成装置および電子デバイス材料 |

Country Status (2)

| Country | Link |

|---|---|

| US (3) | US20050005844A1 (ja) |

| JP (1) | JP4694108B2 (ja) |

Families Citing this family (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI225668B (en) | 2002-05-13 | 2004-12-21 | Tokyo Electron Ltd | Substrate processing method |

| JP4256340B2 (ja) * | 2002-05-16 | 2009-04-22 | 東京エレクトロン株式会社 | 基板処理方法 |

| TWI235433B (en) * | 2002-07-17 | 2005-07-01 | Tokyo Electron Ltd | Oxide film forming method, oxide film forming apparatus and electronic device material |

| US20080190560A1 (en) * | 2005-03-04 | 2008-08-14 | Caizhong Tian | Microwave Plasma Processing Apparatus |

| EP1865548A4 (en) * | 2005-03-31 | 2011-01-05 | Tokyo Electron Ltd | METHOD FOR PRODUCING A SILICON OXIDE FILM, A CONTROL PROGRAM THEREFOR, A RECORDING MEDIUM AND A PLASMA PROCESSING DEVICE |

| JP2007019191A (ja) * | 2005-07-06 | 2007-01-25 | Fujitsu Ltd | 半導体装置とその製造方法 |

| KR101012910B1 (ko) * | 2006-02-28 | 2011-02-08 | 도쿄엘렉트론가부시키가이샤 | 플라즈마 처리 장치 및 그것에 이용하는 기판 가열 기구 |

| JP4864661B2 (ja) * | 2006-11-22 | 2012-02-01 | 東京エレクトロン株式会社 | 太陽電池の製造方法及び太陽電池の製造装置 |

| JP5229711B2 (ja) * | 2006-12-25 | 2013-07-03 | 国立大学法人名古屋大学 | パターン形成方法、および半導体装置の製造方法 |

| US7645709B2 (en) * | 2007-07-30 | 2010-01-12 | Applied Materials, Inc. | Methods for low temperature oxidation of a semiconductor device |

| US7985695B2 (en) | 2007-09-28 | 2011-07-26 | Canon Kabushiki Kaisha | Forming silicon oxide film from RF plasma of oxidizing gas |

| TW200941579A (en) * | 2008-01-24 | 2009-10-01 | Tokyo Electron Ltd | Method for forming silicon oxide film, storage medium, and plasma processing apparatus |

| US20110052810A1 (en) * | 2008-02-19 | 2011-03-03 | Tokyo Electron Limited | Film forming method and storage medium |

| US7947561B2 (en) * | 2008-03-14 | 2011-05-24 | Applied Materials, Inc. | Methods for oxidation of a semiconductor device |

| JP5560556B2 (ja) * | 2008-11-17 | 2014-07-30 | 東京エレクトロン株式会社 | 処理装置 |

| US8236706B2 (en) * | 2008-12-12 | 2012-08-07 | Mattson Technology, Inc. | Method and apparatus for growing thin oxide films on silicon while minimizing impact on existing structures |

| US20100297854A1 (en) * | 2009-04-22 | 2010-11-25 | Applied Materials, Inc. | High throughput selective oxidation of silicon and polysilicon using plasma at room temperature |

| JP5171969B2 (ja) * | 2011-01-13 | 2013-03-27 | 東京エレクトロン株式会社 | 基板処理装置 |

| US8993458B2 (en) | 2012-02-13 | 2015-03-31 | Applied Materials, Inc. | Methods and apparatus for selective oxidation of a substrate |

| WO2018052476A1 (en) * | 2016-09-14 | 2018-03-22 | Applied Materials, Inc. | Steam oxidation initiation for high aspect ratio conformal radical oxidation |

| EP4313449A1 (en) | 2021-03-31 | 2024-02-07 | 6K Inc. | Systems and methods for additive manufacturing of metal nitride ceramics |

| US20230377848A1 (en) * | 2022-05-23 | 2023-11-23 | 6K Inc. | Microwave plasma apparatus and methods for processing materials using an interior liner |

| US12040162B2 (en) | 2022-06-09 | 2024-07-16 | 6K Inc. | Plasma apparatus and methods for processing feed material utilizing an upstream swirl module and composite gas flows |

| WO2024044498A1 (en) | 2022-08-25 | 2024-02-29 | 6K Inc. | Plasma apparatus and methods for processing feed material utilizing a powder ingress preventor (pip) |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE69130947T2 (de) * | 1991-01-08 | 1999-07-08 | Fujitsu Ltd., Kawasaki, Kanagawa | Verfahren zur bildung eines siliciumoxid-filmes |

| KR100745495B1 (ko) * | 1999-03-10 | 2007-08-03 | 동경 엘렉트론 주식회사 | 반도체 제조방법 및 반도체 제조장치 |

| JP4397491B2 (ja) | 1999-11-30 | 2010-01-13 | 財団法人国際科学振興財団 | 111面方位を表面に有するシリコンを用いた半導体装置およびその形成方法 |

| US6358867B1 (en) * | 2000-06-16 | 2002-03-19 | Infineon Technologies Ag | Orientation independent oxidation of silicon |

| US6399471B1 (en) * | 2001-02-15 | 2002-06-04 | Chartered Semiconductor Manufacturing Ltd. | Assorted aluminum wiring design to enhance chip-level performance for deep sub-micron application |

| JP4406172B2 (ja) | 2001-02-15 | 2010-01-27 | キヤノンアネルバ株式会社 | 基板処理方法 |

| JP5013353B2 (ja) * | 2001-03-28 | 2012-08-29 | 隆 杉野 | 成膜方法及び成膜装置 |

| JP2002289616A (ja) * | 2001-03-28 | 2002-10-04 | Mitsubishi Heavy Ind Ltd | 成膜方法及び成膜装置 |

-

2003

- 2003-05-23 JP JP2003146228A patent/JP4694108B2/ja not_active Expired - Fee Related

-

2004

- 2004-05-21 US US10/849,883 patent/US20050005844A1/en not_active Abandoned

-

2006

- 2006-08-24 US US11/508,871 patent/US7632758B2/en not_active Expired - Fee Related

-

2009

- 2009-11-04 US US12/612,471 patent/US20100048033A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| JP2004349546A (ja) | 2004-12-09 |

| US20100048033A1 (en) | 2010-02-25 |

| US20070128880A1 (en) | 2007-06-07 |

| US20050005844A1 (en) | 2005-01-13 |

| US7632758B2 (en) | 2009-12-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4694108B2 (ja) | 酸化膜形成方法、酸化膜形成装置および電子デバイス材料 | |

| JP4926219B2 (ja) | 電子デバイス材料の製造方法 | |

| US7217659B2 (en) | Process for producing materials for electronic device | |

| KR100745495B1 (ko) | 반도체 제조방법 및 반도체 제조장치 | |

| JP4429300B2 (ja) | 電子デバイス材料の製造方法 | |

| JP4255563B2 (ja) | 半導体製造方法及び半導体製造装置 | |

| US6800830B2 (en) | Chemistry for boron diffusion barrier layer and method of application in semiconductor device fabrication | |

| JP4401290B2 (ja) | 酸化膜形成方法および電子デバイス材料の製造方法 | |

| KR101122347B1 (ko) | 절연막의 형성 방법 및 반도체 장치의 제조 방법 | |

| KR101188574B1 (ko) | 절연막의 형성 방법 및 반도체 장치의 제조 방법 | |

| JP2005150637A (ja) | 処理方法及び装置 | |

| KR20090094033A (ko) | 절연막의 형성 방법 및 반도체 장치의 제조 방법 | |

| KR100945770B1 (ko) | 실리콘 산화막의 형성 방법, 반도체 장치의 제조 방법 및컴퓨터 기억 매체 | |

| US20080233764A1 (en) | Formation of Gate Insulation Film | |

| US20080206968A1 (en) | Manufacturing method of semiconductor device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060324 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060324 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080725 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080812 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081014 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20081111 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081210 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081225 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20090129 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20090220 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110114 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110223 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140304 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |