JP4125387B2 - Semiconductor device manufacturing method - Google Patents

Semiconductor device manufacturing method Download PDFInfo

- Publication number

- JP4125387B2 JP4125387B2 JP31916694A JP31916694A JP4125387B2 JP 4125387 B2 JP4125387 B2 JP 4125387B2 JP 31916694 A JP31916694 A JP 31916694A JP 31916694 A JP31916694 A JP 31916694A JP 4125387 B2 JP4125387 B2 JP 4125387B2

- Authority

- JP

- Japan

- Prior art keywords

- amorphous silicon

- semiconductor device

- manufacturing

- crystallization

- solution containing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Thin Film Transistor (AREA)

- Recrystallisation Techniques (AREA)

- Light Receiving Elements (AREA)

Description

【0001】

【産業上の利用分野】

本発明は結晶性を有する半導体を用いた半導体装置およびその作製方法に関する。

【0002】

【従来の技術】

薄膜半導体を用いた薄膜トランジスタ(以下TFT等)が知られている。このTFTは、基板上に薄膜半導体を形成し、この薄膜半導体を用いて構成されるものである。このTFTは、各種集積回路に利用されているが、特に電気光学装置特にアクティブマトリックス型の液晶表示装置の各画素の設けられたスイッチング素子、周辺回路部分に形成されるドライバー素子として注目されている。

【0003】

TFTに利用される薄膜半導体としては、非晶質珪素膜を用いることが簡便であるが、その電気的特性が低いという問題がある。TFTの特性向上を得るためには、結晶性を有するシリコン薄膜を利用するばよい。結晶性を有するシリコン膜は、多結晶シリコン、ポリシリコン、微結晶シリコン等と称されている。この結晶性を有するシリコン膜を得るためには、まず非晶質珪素膜を形成し、しかる後に加熱によって結晶化さればよい。

【0004】

しかしながら、加熱による結晶化は、加熱温度が600℃以上の温度で10時間以上の時間を掛けることが必要であり、基板としてガラス基板を用いることが困難であるという問題がある。例えばアクティブ型の液晶表示装置に用いられるコーニング7059ガラスはガラス歪点が593℃であり、基板の大面積化を考慮した場合、600℃以上の加熱には問題がある。

【0005】

〔発明の背景〕

本発明者らの研究によれば、非晶質珪素膜の表面にニッケルやパラジウム、さらには鉛等の元素を微量に堆積させ、しかる後に加熱することで、550℃、4時間程度の処理時間で結晶化を行なえることが判明している。

【0006】

上記のような微量な元素(結晶化を助長する触媒元素)を導入するには、プラズマ処理や蒸着、さらにはイオン注入を利用すればよい。プラズマ処理とは、平行平板型あるいは陽光柱型のプラズマCVD装置において、電極として触媒元素を含んだ材料を用い、窒素または水素等の雰囲気でプラズマを生じさせることによって非晶質珪素膜に触媒元素の添加を行なう方法である。

【0007】

しかしながら、上記のような元素が半導体中に多量に存在していることは、これら半導体を用いた装置の信頼性や電気的安定性を阻害するものであり好ましいことではない。

【0008】

即ち、上記のニッケル等の結晶化を助長する元素(触媒元素)は、非晶質珪素を結晶化させる際には必要であるが、結晶化した珪素中には極力含まれないようにすることが望ましい。この目的を達成するには、触媒元素として結晶性珪素中で不活性な傾向が強いものを選ぶと同時に、結晶化に必要な触媒元素の量を極力少なくし、最低限の量で結晶化を行なう必要がある。そしてそのためには、上記触媒元素の添加量を精密に制御して導入する必要がある。

【0009】

また、ニッケルを触媒元素とした場合、非晶質珪素膜を成膜し、ニッケル添加をプラズマ処理法によって行ない結晶性珪素膜を作製し、その結晶化過程等を詳細に検討したところ以下の事項が判明した。

(1)プラズマ処理によってニッケルを非晶質珪素膜上に導入した場合、熱処理を行なう以前に既に、ニッケルは非晶質珪素膜中のかなりの深さの部分まで侵入している。

(2)結晶の初期核発生は、ニッケルを導入した表面から発生している。

(3)蒸着法でニッケルを非晶質珪素膜上に成膜した場合であっても、プラズマ処理を行なった場合と同様に結晶化が起こる。

【0010】

上記事項から、プラズマ処理によって導入されたニッケルが全て効果的に機能していないということが結論される。即ち、多量のニッケルが導入されても十分に機能していないニッケルが存在していると考えられる。このことから、ニッケルと珪素が接している点(面)が低温結晶化の際に機能していると考えられる。そして、可能な限りニッケルは微細に原子状に分散していることが必要であることが結論される。即ち、「必要なのは非晶質珪素膜の表面近傍に低温結晶化が可能な範囲内で可能な限り低濃度のニッケルが原子状で分散して導入されればよい」ということが結論される。

【0011】

非晶質珪素膜の表面近傍のみに極微量のニッケルを導入する方法、言い換えるならば、非晶質珪素膜の表面近傍のみ結晶化を助長する触媒元素を極微量導入する方法としては、蒸着法を挙げることができるが、蒸着法は制御性が悪く、触媒元素の導入量を厳密に制御することが困難であるという問題がある。

【0012】

【発明が解決しようとする課題】

本発明は、触媒元素を用いた600℃以下の熱処理による結晶性を有する薄膜珪素半導体の作製において、

(1)触媒元素の量を制御して導入し、その量を最小限の量とする。

(2)生産性の高い方法とする。

といった要求を満たすことを目的とする。

【0013】

【課題を解決するための手段】

本発明は、上記目的を満足するために以下の手段を用いて結晶性を有した珪素膜を得る。

非晶質珪素膜に接して該非晶質珪素膜の結晶化を助長する触媒元素単体または前記触媒元素を含む化合物を保持させ、前記非晶質珪素膜に前記触媒元素単体または前記触媒元素を含む化合物が接した状態において、加熱処理を施し、前記非晶質珪素膜を結晶化させる。

具体的には、触媒元素を含む溶液を非晶質珪素膜が形成される基板(表面に保護膜糖が形成されていても本明細書では単に基板という)の表面に塗布し、この状態で基板表面に非晶質珪素膜を形成し、さらに加熱処理することで、非晶質珪素膜を結晶化が実現できる。

特に本発明においては、非晶質珪素膜の表面に接して触媒元素が導入されることが特徴である。このことは、触媒元素の量を制御する上で極めて重要である。

【0014】

さらにこの結晶性珪素膜を用いて半導体装置のPN、PI、NIその他の電気的接合を少なくとも1つ有する活性領域を構成することを特徴とする。半導体装置としては、薄膜トランジスタ(TFT)、ダイオード、光センサを用いることができる。

【0015】

本発明の構成を採用することによって以下に示すような基本的な有意性を得ることができる。

(a)溶液中における触媒元素濃度は、予め厳密に制御である。従って結晶性をより高めかつその元素の量をより少なくすることが可能である。

(b)溶液と非晶質珪素膜の表面とが接触していれば、触媒元素の非晶質珪素への導入量は、溶液中における触媒元素の濃度によって決まる。

(c)非晶質珪素膜の表面に接触する触媒元素が主に結晶化に寄与することとなるので、必要最小限度の濃度で触媒元素を導入できる。

【0016】

非晶質珪素膜が形成される基板上に結晶化を助長する元素を含有させた溶液を塗布するにおいて、溶液として水溶液、有機溶媒溶液等を用いることができる。ここで含有とは、化合物として含ませるという意味と、単に分散させることにより含ませるという意味との両方を含む。

【0017】

触媒元素を含む溶媒としては、極性溶媒である水、アルコール、酸、アンモニアから選ばれたものを用いることができる。

【0018】

触媒としてニッケルを用い、このニッケルを極性溶媒に含ませる場合、ニッケルはニッケル化合物として導入される。このニッケル化合物としては、代表的には臭化ニッケル、酢酸ニッケル、蓚酸ニッケル、炭酸ニッケル、塩化ニッケル、沃化ニッケル、硝酸ニッケル、硫酸ニッケル、蟻酸ニッケル、ニッケルアセチルアセトネ−ト、4−シクロヘキシル酪酸ニッケル、酸化ニッケル、水酸化ニッケルから選ばれたものが用いられる。

【0019】

また触媒元素を含む溶媒として、無極性溶媒であるベンゼン、トルエン、キシレン、四塩化炭素、クロロホルム、エーテルから選ばれたものを用いることができる。

【0020】

この場合はニッケルはニッケル化合物として導入される。このニッケル化合物としては代表的には、ニッケルアセチルアセトネ−ト、2−エチルヘキサン酸ニッケルから選ばれたものを用いることができる。

【0021】

また、触媒元素としてFe(鉄)を用いる場合には、その化合物として鉄塩として知られている材料、例えば臭化第1鉄(FeBr2 6H2 O)、臭化第2鉄(FeBr3 6H2 O)、酢酸第2鉄(Fe(C2 H3 O2)3xH2 O)、塩化第1鉄(FeCl2 4H2 O)、塩化第2鉄(FeCl3 6H2 O)、フッ化第2鉄(FeF3 3H2 O)、硝酸第2鉄(Fe(NO3)3 9H2 O)、リン酸第1鉄(Fe3 (PO4)2 8H2 O)、リン酸第2鉄(FePO4 2H2 O)から選ばれたものを用いることができる。

【0022】

触媒元素としてCo(コバルト)を用いる場合には、その化合物としてコバルト塩として知られている材料、例えば臭化コバルト(CoBr6H2 O)、酢酸コバルト(Co(C2 H3 O2)2 4H2 O)、塩化コバルト(CoCl2 6H2 O)、フッ化コバルト(CoF2 xH2 O)、硝酸コバルト(Co(No3)2 6H2 O)から選ばれたものを用いることができる。

【0023】

触媒元素としてRu(ルテニウム)を用いる場合には、その化合物としてルテニウム塩として知られている材料、例えば塩化ルテニウム(RuCl3 H2 O)を用いることができる。

【0024】

触媒元素してRh(ロジウム)を用いる場合には、その化合物としてロジウム塩として知られている材料、例えば塩化ロジウム(RhCl3 3H2 O)を用いることができる。

【0025】

触媒元素としてPd(パラジウム)を用いる場合には、その化合物としてパラジウム塩として知られている材料、例えば塩化パラジウム(PdCl2 2H2 O)を用いることができる。

【0026】

触媒元素としてOs(オスニウム)を用いる場合には、その化合物としてオスニウム塩として知られている材料、例えば塩化オスニウム(OsCl3 )を用いることができる。

【0027】

触媒元素としてIr(イリジウム)を用いる場合には、その化合物としてイリジウム塩として知られている材料、例えば三塩化イリジウム(IrCl3 3H2 O)、四塩化イリジウム(IrCl4 )から選ばれた材料を用いることができる。

【0028】

触媒元素としてPt(白金)を用いる場合には、その化合物として白金塩として知られている材料、例えば塩化第二白金(PtCl4 5H2 O)を用いることができる。

【0029】

触媒元素としてCu(銅)を用いる場合には、その化合物として酢酸第二銅(Cu(CH3 COO)2 )、塩化第二銅(CuCl2 2H2 O)、硝酸第二銅(Cu(NO3)2 3H2 O)から選ばれた材料を用いることができる。

【0030】

触媒元素として金を用いる場合には、その化合物として三塩化金(AuCl3 xH2 O)、塩化金塩(AuHCl4 4H2 O)、テトラクロロ金ナトリウム(AuNaCl4 2H2 O)から選ばれた材料を用いることができる。

【0031】

また触媒元素を含有させた溶液に界面活性剤を添加することも有用である。これは、被塗布面に対する密着性を高め吸着性を制御するためである。この界面活性剤は予め被塗布面上に塗布するのでもよい。

【0032】

触媒元素としてニッケル単体を用いる場合には、酸に溶かして溶液とする必要がある。

【0033】

以上述べたのは、触媒元素であるニッケルが完全に溶解した溶液を用いる例であるが、ニッケルが完全に溶解していなくとも、ニッケル単体あるいはニッケルの化合物からなる粉末が分散媒中に均一に分散したエマルジョンの如き材料を用いてもよい。

【0034】

なおこれらのことは、触媒元素としてニッケル以外の材料を用いた場合であっても同様である。

【0035】

結晶化を助長する触媒元素としてニッケルを用い、このニッケルを含有させる溶液溶媒として水の如き極性溶媒を用いた場合において、非晶質珪素膜が形成される基板となる表面にこれら溶液を直接塗布すると、溶液が弾かれてしまうことがある。この場合は、100Å以下の薄い酸化膜をまず形成し、その上に触媒元素を含有させた溶液を塗布することで、均一に溶液を塗布することができる。また、界面活性剤の如き材料を溶液中に添加する方法により濡れを改善する方法も有効である。なお、ガラス基板上に形成されるTFTの構造において、ガラス基板表面に下地膜として酸化珪素膜や窒化珪素膜を形成する手法が知られているが、この場合は直接溶液を塗布することが可能である。

【0036】

また、溶液として2−エチルヘキサン酸ニッケルのトルエン溶液の如き無極性溶媒を用いることで、下地の酸化膜を形成することなしに溶液を塗布することができる。この場合にはレジスト塗布の際に使用されている密着剤の如き材料を予め塗布することは有効である。

【0037】

溶液に含ませる触媒元素の量は、その溶液の種類にも依存するが、概略の傾向としてはニッケル量として溶液に対して1ppm〜200ppm、好ましくは1ppm〜50ppm(溶液全体に対する触媒元素の重量比率)とすることが望ましい。これは、結晶化終了後における膜中のニッケル濃度や耐フッ酸性に鑑みて決められる値である。

【0038】

また、触媒元素を含んだ溶液を選択的に塗布することにより、結晶成長を選択的に行なうことができる。特にこの場合、溶液が塗布されなかった領域に向かって、溶液が塗布された領域から珪素膜の面に概略平行な方向に結晶成長を行なわすことができる。この珪素膜の面に概略平行な方向に結晶成長が行なわれた領域を本明細書中においては横方向に結晶成長した領域ということとする。

【0039】

またこの横方向に結晶成長が行なわれた領域は、触媒元素の濃度が低いことが確かめられている。半導体装置の活性層領域として、結晶性珪素膜を利用することは有用であるが、活性層領域中における不純物の濃度は一般に低い方が好ましい。従って、上記横方向に結晶成長が行なわれた領域を用いて半導体装置の活性層領域を形成することはデバイス作製上有用である。

【0040】

また本発明においては、被形成面と該被形成面上に形成された薄膜珪素半導体との界面に結晶化を助長する触媒元素が導入されるので、結晶化された薄膜珪素半導体の表面における触媒元素の濃度を低く抑えることができる。

【0041】

一般にTFTは絶縁ゲイト型電界効果トランジスタの構成を有するが、絶縁ゲイト型電界効果トランジスタにおいては、チャネル形成領域とゲイト絶縁膜との界面およびその近傍領域が重要である。

【0042】

絶縁ゲイト型電界効果半導体装置において、チャネル形成領域とゲイト絶縁膜との界面やその近傍領域に準位が存在すると、絶縁ゲイト型電界効果トランジスタの特性が大きく阻害される。このような準位を形成する要因としては、可動イオンや不純物が考えられる。従って、珪素薄膜上にゲイト絶縁膜を形成する構成を採用したTFTを作製する場合には、珪素薄膜表面に不純物等が極力存在しないことが望ましい。

【0043】

さらに本発明は、結晶化した珪素薄膜の全域において、結晶化を助長する触媒元素の濃度を極力少なくすることができるので、極めて有用である。

【0044】

また本発明の方法を採用した場合、プラズマ処理を利用した場合に見られる被処理面の深さ方向における触媒元素の濃度分布が見られないので、加熱処理の際に触媒元素が不要に拡散するようなことがない。

【0045】

前述のように本発明においては、結晶化された珪素薄膜表面に存在する触媒元素の濃度を可能な限り少なくすることができるので、これら触媒元素の影響を極力受けないTFTを形成することができる。すなわち、珪素薄膜の下面に接して結晶化を助長する触媒元素が導入されることで、結晶性珪素膜表面を用いる電子デバイスの特性に触媒元素の影響の少ない構成を実現することができる。

【0046】

本発明においては、触媒元素としてニッケルを用いた場合に最も顕著な効果を得ることができるが、その他利用できる触媒元素の種類としては、好ましくはNi、Pd、Pt、Cu、Ag、Au、In、Sn、Pd、Sn、Pd、P、As、Sbを利用することができる。また、VIII族元素、IIIb、IVb、Vb元素から選ばれた一種または複数種類の元素を利用することもできる。

【0047】

また、触媒元素の導入方法は、水溶液やアルコール等の溶液を用いることに限定されるものではなく、触媒元素を含んだ物質を広く用いることができる。例えば、触媒元素を含んだ金属化合物や酸化物を用いることができる。

【0048】

【実施例】

〔実施例1〕

【0049】

本実施例では、結晶化を助長する触媒元素を水溶液に含有させて、ガラス基板上に塗布し、しかる後に非晶質珪素膜を形成し、加熱処理することにより結晶化させる例である。

【0050】

本実施例においては、基板としてコーニング7059ガラスを用いる。またその大きさは100mm×100mmとする。

【0051】

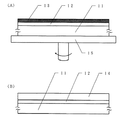

図1に本実施例の作製工程を示す。まず、ガラス基板11上に下地の酸化珪素膜12をスパッタ法によって2000Åの厚さに形成する。そして、汚れ及び自然酸化膜を取り除くためにフッ酸処理を行う。汚れが無視できる場合には、この工程を省略しても良いことは言うまでもない。

【0052】

つぎに、酢酸塩溶液中にニッケルを添加した酢酸塩溶液を作る。ニッケルの濃度は25ppmとする。そしてこの酢酸塩溶液を酸化珪素膜12の表面に5ml滴下し、この状態を5分間保持する。そしてスピナーを用いてスピンドライ(2000rpm、60秒)を行う。(図1(A))

【0053】

酢酸溶液中におけるニッケルの濃度は、1ppm〜50ppmの範囲で用いるのが好ましい。

【0054】

このニッケル溶液の塗布工程を、1回〜複数回行なうことにより、スピンドライ後の酸化珪素膜12の表面に数Å〜数百Åの平均の膜厚を有するニッケルを含む層を形成することができる。この場合、この層のニッケルがその後の加熱工程において、非晶質珪素膜に拡散し、結晶化を助長する触媒として作用する。なお、この層というのは、完全な膜になっているとは限らない。

【0055】

上記溶液の塗布の後、プリベークを窒素雰囲気中において400℃の温度で行なう。この工程は、酸化珪素膜12の表面に吸着した溶液を分解するために行なう。この工程を行なうことによって、後に形成される非晶質珪素膜14の膜質が荒れることを防ぐことができる。このプリベークの温度は、塗布工程の際に用いる溶液の種類によって変更されることはいうまでもない。

【0056】

次に非晶質珪素膜14をプラズマCVD法やLPCVD法によって100〜1500Åの厚さに形成する。ここでは、プラズマCVD法によって非晶質珪素膜12を1000Åの厚さに成膜する。

【0057】

そして、加熱炉を用い、窒素雰囲気中において550度、4時間の加熱処理を行う。この結果、基板11上に形成された結晶性を有する珪素薄膜14を得ることができる。

【0058】

上記の加熱処理は450度以上の温度で行うことができるが、温度が低いと加熱時間を長くしなけらばならず、生産効率が低下する。また、550度以上とすると基板として用いるガラス基板の耐熱性の問題が表面化してしまう。

【0059】

〔実施例2〕

本実施例は、触媒元素であるニッケルを非水溶液であるアルコールに含有させ、非晶質珪素膜上に塗布する例である。本実施例では、ニッケルの化合物としてニッケルアセチルアセトネートを用い、該化合物をアルコールに含有させる。ニッケルの濃度は必要とする濃度になるようにすればよい。

【0060】

後の工程は、実施例1に示したのと同様である。また作製工程の概要は図1に示すにと同様である。以下に具体的な条件を説明する。まず、ニッケル化合物として、ニッケルアセチルアセトネートを用意する。この物質は、アルコールに可溶であり、分解温度が低いため、結晶化工程における加熱の際に容易に分解させることができる。

【0061】

また、アルコールとしてはエタノールを用いる。まずエタノールに前記のニッケルアセチルアセトネートをニッケルの量に換算して50ppmになるように調整し、ニッケルを含有した溶液を作製する。

【0062】

そしてこの溶液を下地膜である酸化珪素膜12上に塗布する。下地の酸化珪素膜上への溶液の塗布は、実施例1の水溶液を用いた場合より、少なくてすむ。これは、アルコールの接触角が水のそれよりも小さいことに起因する。ここでは、100mm角の面積に対し、2mlの滴下とする。

【0063】

そして、この状態で5分間保持する。その後、スピナーを用い乾燥を行う。この際、スピナーは1500rpmで1分間回転させる。この後、非晶質珪素膜を形成し、550℃、4時間の加熱処理を行ない結晶化を行う。こうして結晶性を有する珪素膜を得る。

【0064】

〔実施例3〕

本実施例は、触媒元素であるニッケル単体を酸に溶かし、このニッケル単体が溶けた酸を非晶質珪素膜の下地の酸化膜12上に塗布する例である。なお、作製工程の概要は、図1に示すのと同様である。

【0065】

本実施例においては、酸として0.1mol/lの硝酸を用いる。この硝酸の中にニッケルの濃度が50ppmとなるように、ニッケルの粉末を溶かし、これを溶液として用いる。この後の工程は、実施例1の場合と同様である。

【0066】

〔実施例4〕

本実施例は、本発明の方法を利用して作製した結晶性珪素膜を用いて、アクティブマトリックス型の液晶表示装置の各画素部分に設けられるTFTを作製する例を示す。なお、TFTの応用範囲としては、液晶表示装置のみではなく、一般に言われる薄膜集積回路に利用できることはいうまでもない。

【0067】

図2に本実施例の作製工程の概要を示す。まずガラス基板上に下地の酸化珪素膜(図示せず)を2000Åの厚さに成膜する。この酸化珪素膜は、ガラス基板からの不純物の拡散を防ぐためと、触媒元素を導入する際に濡れ特性を高める機能を有する。

【0068】

そして10ppmのニッケルを含有した酢酸塩溶液を塗布し、5分間保持し、スピナーを用いてスピンドライを行う。その後窒素雰囲気中においてプリベークを行なう。

【0069】

このニッケルを導入する工程は、実施例2または実施例3に示した方法によってもよい。

【0070】

そして、非晶質珪素膜を実施例1と同様な方法で1000Åの厚さに成膜し、550度、4時間の加熱処理によって結晶化を行なう。この工程によって結晶性珪素膜が得られる。

【0071】

次に、結晶化した珪素膜をパターニングして、島状の領域104を形成する。この島状の領域104はTFTの活性層を構成する。そして、厚さ200〜1500Å、ここでは1000Åの酸化珪素105を形成する。この酸化珪素膜はゲイト絶縁膜としても機能する。(図2(A))

【0072】

上記酸化珪素膜105の作製には注意が必要である。ここでは、TEOSを原料とし、酸素とともに基板温度150〜600℃、好ましくは300〜450℃で、RFプラズマCVD法で分解・堆積した。TEOSと酸素の圧力比は1:1〜1:3、また、圧力は0.05〜0.5torr、RFパワーは100〜250Wとした。あるいはTEOSを原料としてオゾンガスとともに減圧CVD法もしくは常圧CVD法によって、基板温度を350〜600℃、好ましくは400〜550℃として形成した。成膜後、酸素もしくはオゾンの雰囲気で400〜600℃で30〜60分アニールした。

【0073】

この状態でKrFエキシマーレーザー(波長248nm、パルス幅20nsec)あるいはそれと同等な強光を照射することで、シリコン領域104の結晶化を助長さえてもよい。特に、赤外光を用いたRTA(ラピットサーマルアニール)は、ガラス基板を加熱せずに、珪素のみを選択的に加熱することができ、しかも珪素と酸化珪素膜との界面における界面準位を減少させることができるので、絶縁ゲイト型電界効果半導体装置の作製においては有用である。

【0074】

その後、厚さ2000Å〜1μmのアルミニウム膜を電子ビーム蒸着法によって形成して、これをパターニングし、ゲイト電極106を形成する。アルミニウムにはスカンジウム(Sc)を0.15〜0.2重量%ドーピングしておいてもよい。次に基板をpH≒7、1〜3%の酒石酸のエチレングリコール溶液に浸し、白金を陰極、このアルミニウムのゲイト電極を陽極として、陽極酸化を行う。陽極酸化は、最初一定電流で220Vまで電圧を上げ、その状態で1時間保持して終了させる。本実施例では定電流状態では、電圧の上昇速度は2〜5V/分が適当である。このようにして、厚さ1500〜3500Å、例えば、2000Åの陽極酸化物109を形成する。(図2(B))

【0075】

その後、イオンドーピング法(プラズマドーピング法ともいう)によって、各TFTの島状シリコン膜中に、ゲイト電極部をマスクとして自己整合的に不純物(燐)を注入した。ドーピングガスとしてはフォスフィン(PH3 )を用いた。ドーズ量は、1〜4×1015cm-2とする。

【0076】

さらに、図2(C)に示すようにKrFエキシマーレーザー(波長248nm、パルス幅20nsec)を照射して、上記不純物領域の導入によって結晶性の劣化した部分の結晶性を改善させる。レーザーのエネルギー密度は150〜400mJ/cm2 、好ましくは200〜250mJ/cm2 である。こうして、N型不純物(燐)領域108、109を形成する。これらの領域のシート抵抗は200〜800Ω/□であった。

【0077】

この工程において、レーザーを用いるかわりに、フラッシュランプを使用して短時間に1000〜1200℃(シリコンモニターの温度)まで上昇させ、試料を加熱する、いわゆるRTA(ラピッド・サーマル・アニール)(RTP、ラピット・サーマル・プロセスともいう)を用いてもよい。

【0078】

その後、全面に層間絶縁物110として、TEOSを原料として、これと酸素とのプラズマCVD法、もしくはオゾンとの減圧CVD法あるいは常圧CVD法によって酸化珪素膜を厚さ3000Å形成する。基板温度は250〜450℃、例えば、350℃とする。成膜後、表面の平坦性を得るため、この酸化珪素膜を機械的に研磨する。さらに、スパッタ法によってITO被膜を堆積し、これをパターニングして画素電極111とする。(図2(D))

【0079】

そして、層間絶縁物110をエッチングして、図1(E)に示すようにTFTのソース/ドレインにコンタクトホールを形成し、クロムもしくは窒化チタンの配線112、113を形成し、配線113は画素電極111に接続させる。

【0080】

プラズマ処理を用いてニッケルを導入した結晶性珪素膜は、酸化珪素膜に比較してバッファフッ酸に対する選択性が低いので、上記コンタクトホールの形成工程において、エッチングされてしまうことが多かった。

【0081】

しかし、本実施例のように10ppmの低濃度で水溶液を用いてニッケルを導入した場合には、耐フッ酸性が高いので、上記コンタクトホールの形成が安定して再現性よく行なうことができる。

【0082】

最後に、水素中で300〜400℃で0.1〜2時間アニールして、シリコンの水素化を完了する。このようにして、TFTが完成する。そして、同時に作製した多数のTFTをマトリクス状に配列せしめてアクティブマトリクス型液晶表示装置として完成する。このTFTは、ソース/ドレイン領域108/109とチャネル形成領域114を有している。また115がNIの電気的接合部分となる。

【0083】

本実施例の構成を採用した場合、活性層中に存在するニッケルの濃度は、3×1018cm-3程度あるいはそれ以下の、1×1016atoms cm-3〜3×1018atoms cm-3であると考えられる。

【0084】

〔実施例5〕

図3に本実施例の作製工程の断面図を示す。まず、基板(コーニング7059)501上にスパッタリング法によって厚さ2000Åの酸化珪素の下地膜502を形成する。基板は、下地膜の成膜の前もしくは後に、歪み温度よりも高い温度でアニールをおこなった後、0.1〜1.0℃/分で歪み温度以下まで徐冷すると、その後の温度上昇を伴う工程(本発明の熱酸化工程およびその後の熱アニール工程を含む)での基板の収縮が少なく、マスク合わせが容易となる。コーニング7059基板では、620〜660℃で1〜4時間アニールした後、0.03〜1.0℃/分、好ましくは、0.1〜0.3℃/分で徐冷し、400〜500℃まで温度が低下した段階で取り出すとよい。

【0085】

次に、実施例1で示した方法により非晶質珪素膜の結晶化を行なった。即ち、下地の酸化珪素膜502上にニッケルを含んだ溶液を塗布し、非晶質珪素膜502の表面にニッケルを吸着させる。

【0086】

次に、プラズマCVD法によって、厚さ500〜1500Å、例えば1000Åの真性(I型)の非晶質珪素膜を成膜する。そして窒素雰囲気(大気圧)、600℃、48時間アニールして結晶化させ、珪素膜を10〜1000μm角の大きさにパターニングして、島状の珪素膜(TFTの活性層)503を形成する。(図3(A))

【0087】

その後、70〜90%の水蒸気を含む1気圧、500〜750℃、代表的には600℃の酸素雰囲気を水素/酸素=1.5〜1.9の比率でパイロジェニック反応法を用いて形成する。かかる雰囲気中において、3〜5時間放置することによって、珪素膜表面を酸化させ、厚さ500〜1500Å、例えば1000Åの酸化珪素膜504を形成する。注目すべきは、かかる酸化により、初期の珪素膜は、その表面が50Å以上減少し、結果として、珪素膜の最表面部分の汚染が、珪素−酸化珪素界面には及ばないようになることである。すなわち、清浄な珪素−酸化珪素界面が得られることである。酸化珪素膜の厚さは酸化される珪素膜の2倍であるので、1000Åの厚さの珪素膜を酸化して、厚さ1000Åの酸化珪素膜を得た場合には、残った珪素膜の厚さは500Åということになる。

【0088】

一般に酸化珪素膜(ゲイト絶縁膜)と活性層は薄ければ薄いほど移動度の向上、オフ電流の減少という良好な特性が得られる。一方、初期の非晶質珪素膜の結晶化はその膜厚が大きいほど結晶化させやすい。したがって、従来は、活性層の厚さに関して、特性とプロセスの面で矛盾が存在していた。本発明はこの矛盾を初めて解決したものであり、すなわち、結晶化前には非晶質珪素膜を厚く形成し、良好な結晶性珪素膜を得る。そして、次にはこの珪素膜を酸化することによって珪素膜を薄くし、TFTとしての特性を向上させるものである。さらに、この熱酸化においては、再結合中心の存在しやすい非晶質成分、結晶粒界が酸化されやすく、結果的に活性層中の再結合中心を減少させるという特徴も有する。このため製品の歩留りが高まる。

【0089】

熱酸化によって酸化珪素膜504を形成したのち、基板を一酸化二窒素雰囲気(1気圧、100%)、600℃で2時間アニールする。(図3(B))

引き続いて、減圧CVD法によって、厚さ3000〜8000Å、例えば6000Åの多結晶珪素(0.01〜0.2%の燐を含む)を成膜する。そして、珪素膜をパターニングして、ゲイト電極505を形成する。さらに、この珪素膜をマスクとして自己整合的に、イオンドーピング法(プラズマドーピング法とも言う)によって、活性層領域(ソース/ドレイン、チャネルを構成する)にN導電型を付与する不純物(ここでは燐)を添加する。ドーピングガスとして、フォスフィン(PH3 )を用い、加速電圧を60〜90kV、例えば80kVとする。ドーズ量は1×1015〜8×1015cm-2、例えば、5×1015cm-2とする。この結果、N型の不純物領域506と507が形成される。

【0090】

その後、レーザー光の照射によってアニール行う。レーザー光としては、KrFエキシマレーザー(波長248nm、パルス幅20nsec)を用いたが、他のレーザーであってもよい。レーザー光の照射条件は、エネルギー密度が200〜400mJ/cm2 、例えば250mJ/cm2 とし、一か所につき2〜10ショット、例えば2ショット照射する。このレーザー光の照射時に基板を200〜450℃程度に加熱することによって、効果を増大せしめてもよい。(図3(C))

【0091】

また、この工程は、近赤外光によるランプアニールによる方法でもよい。近赤外線は非晶質珪素よりも結晶化した珪素へは吸収されやすく、1000℃以上の熱アニールにも匹敵する効果的なアニールを行うことができる。その反面、ガラス基板(遠赤外光はガラス基板に吸収されるが、可視・近赤外光(波長0.5〜4μm)は吸収されにくい)へは吸収されにくいので、ガラス基板を高温に加熱することがなく、また短時間の処理ですむので、ガラス基板の縮みが問題となる工程においては最適な方法であるといえる。

【0092】

続いて、厚さ6000Åの酸化珪素膜508を層間絶縁物としてプラズマCVD法によって形成する。この層間絶縁物としてはポリイミドを利用してもよい。さらにコンタクトホールを形成して、金属材料、例えば、窒化チタンとアルミニウムの多層膜によってTFTの電極・配線509、510を形成する。最後に、1気圧の水素雰囲気で350℃、30分のアニールを行い、TFTを完成する。(図3(D))

【0093】

上記に示す方法で得られたTFTの移動度は110〜150cm2 /Vs、S値は0.2〜0.5V/桁であった。また、同様な方法によってソース/ドレインにホウ素をドーピングしたPチャネル型TFTも作製したところ、移動度は90〜120cm2 /Vs、S値は0.4〜0.6V/桁であり、公知のPVD法やCVD法によってゲイト絶縁膜を形成した場合に比較して、移動度は2割以上高く、S値は20%以上も減少した。

また、信頼性の面からも、本実施例で作製されたTFTは1000℃の高温熱酸化によって作製されたTFTにひけをとらない良好な結果を示した。

【0094】

【効果】

触媒元素を導入して低温で短時間で結晶化させた結晶性珪素膜を用いて、半導体装置を作製することで、生産性が高く、特性のよいデバイスを得ることができる。

【図面の簡単な説明】

【図1】 実施例の作製工程を示す

【図2】 実施例の作製工程を示す。

【図3】 実施例の作製工程を示す。

【符号の説明】

11・・・・ガラス基板

12・・・・酸化珪素膜

13・・・・ニッケルを含有した酢酸溶液膜

14・・・・珪素膜

104・・・活性層

105・・・酸化珪素膜

106・・・ゲイト電極

109・・・酸化物層

108・・・ソース/ドレイン領域

109・・・ドレイン/ソース領域

110・・・層間絶縁膜(酸化珪素膜)

111・・・画素電極(ITO)

112・・・電極

113・・・電極[0001]

[Industrial application fields]

The present invention relates to a semiconductor device using a crystalline semiconductor and a manufacturing method thereof.

[0002]

[Prior art]

A thin film transistor (hereinafter referred to as TFT) using a thin film semiconductor is known. This TFT is formed by forming a thin film semiconductor on a substrate and using this thin film semiconductor. This TFT is used in various integrated circuits, and is particularly attracting attention as a switching element provided with each pixel of an electro-optical device, particularly an active matrix liquid crystal display device, and a driver element formed in a peripheral circuit portion. .

[0003]

As a thin film semiconductor used for a TFT, it is easy to use an amorphous silicon film, but there is a problem that its electrical characteristics are low. In order to obtain improved TFT characteristics, a silicon thin film having crystallinity may be used. The crystalline silicon film is called polycrystalline silicon, polysilicon, microcrystalline silicon, or the like. In order to obtain this silicon film having crystallinity, an amorphous silicon film is first formed and then crystallized by heating.

[0004]

However, crystallization by heating requires a heating temperature of 600 ° C. or more and a time of 10 hours or more, and there is a problem that it is difficult to use a glass substrate as a substrate. For example, Corning 7059 glass used for an active type liquid crystal display device has a glass strain point of 593 ° C., and there is a problem with heating at 600 ° C. or higher in consideration of an increase in area of the substrate.

[0005]

BACKGROUND OF THE INVENTION

According to the study by the present inventors, a small amount of elements such as nickel, palladium, and lead are deposited on the surface of the amorphous silicon film, and then heated, so that the processing time is about 550 ° C. for about 4 hours. It has been found that crystallization can be performed.

[0006]

In order to introduce such a trace amount of element (catalytic element that promotes crystallization), plasma treatment, vapor deposition, or ion implantation may be used. The plasma treatment is a parallel plate type or positive column type plasma CVD apparatus using a material containing a catalytic element as an electrode, and generating a plasma in an atmosphere of nitrogen or hydrogen to form a catalytic element on the amorphous silicon film. It is a method of adding.

[0007]

However, the presence of a large amount of the elements as described above in the semiconductor is not preferable because it impedes the reliability and electrical stability of a device using these semiconductors.

[0008]

That is, the above-mentioned element (catalyst element) that promotes crystallization, such as nickel, is necessary when crystallizing amorphous silicon, but should not be included in crystallized silicon as much as possible. Is desirable. In order to achieve this purpose, a catalyst element that has a strong tendency to be inert in crystalline silicon is selected, and at the same time, the amount of catalyst element required for crystallization is minimized and crystallization is performed with a minimum amount. Need to do. For this purpose, it is necessary to precisely control the amount of the catalyst element added.

[0009]

In addition, when nickel is used as a catalyst element, an amorphous silicon film is formed, a nickel treatment is performed by plasma treatment to produce a crystalline silicon film, and the crystallization process and the like are examined in detail. There was found.

(1) When nickel is introduced onto the amorphous silicon film by plasma treatment, the nickel has already penetrated to a considerable depth in the amorphous silicon film before the heat treatment.

(2) The initial nucleation of the crystal is generated from the surface where nickel is introduced.

(3) Even when nickel is deposited on the amorphous silicon film by vapor deposition, crystallization occurs in the same manner as when plasma treatment is performed.

[0010]

From the above, it can be concluded that not all nickel introduced by plasma treatment is functioning effectively. That is, it is considered that there is nickel that does not function sufficiently even when a large amount of nickel is introduced. From this, it is considered that the point (plane) where nickel and silicon are in contact functions during low-temperature crystallization. It is concluded that nickel must be dispersed as finely as possible in the atomic form. That is, it is concluded that “what is necessary is that nickel as low as possible should be introduced in the form of atoms dispersed in the vicinity of the surface of the amorphous silicon film as long as low-temperature crystallization is possible”.

[0011]

As a method of introducing a very small amount of nickel only in the vicinity of the surface of the amorphous silicon film, in other words, as a method of introducing a very small amount of the catalytic element that promotes crystallization only in the vicinity of the surface of the amorphous silicon film, a vapor deposition method is used. However, the vapor deposition method has a problem of poor controllability, and it is difficult to strictly control the amount of catalyst element introduced.

[0012]

[Problems to be solved by the invention]

In the production of a thin film silicon semiconductor having crystallinity by heat treatment at 600 ° C. or lower using a catalyst element,

(1) A controlled amount of catalyst element is introduced to minimize the amount.

(2) Use a highly productive method.

The purpose is to satisfy such requirements.

[0013]

[Means for Solving the Problems]

In order to satisfy the above object, the present invention obtains a silicon film having crystallinity using the following means.

A catalyst element alone or a compound containing the catalyst element that promotes crystallization of the amorphous silicon film is held in contact with the amorphous silicon film, and the catalyst element alone or the catalyst element is contained in the amorphous silicon film. In the state where the compound is in contact, heat treatment is performed to crystallize the amorphous silicon film.

Specifically, a solution containing a catalytic element is applied to the surface of a substrate on which an amorphous silicon film is formed (even if a protective film sugar is formed on the surface, it is simply referred to as a substrate in this specification). Crystallization of the amorphous silicon film can be realized by forming an amorphous silicon film on the substrate surface and further performing heat treatment.

In particular, the present invention is characterized in that the catalytic element is introduced in contact with the surface of the amorphous silicon film. This is extremely important in controlling the amount of catalytic element.

[0014]

Further, the crystalline silicon film is used to form an active region having at least one electrical junction such as PN, PI, NI or the like of the semiconductor device. As the semiconductor device, a thin film transistor (TFT), a diode, or an optical sensor can be used.

[0015]

By adopting the configuration of the present invention, the following basic significance can be obtained.

(A) The catalyst element concentration in the solution is strictly controlled in advance. Accordingly, it is possible to increase the crystallinity and reduce the amount of the element.

(B) If the solution and the surface of the amorphous silicon film are in contact with each other, the amount of the catalytic element introduced into the amorphous silicon is determined by the concentration of the catalytic element in the solution.

(C) Since the catalytic element in contact with the surface of the amorphous silicon film mainly contributes to crystallization, the catalytic element can be introduced at a necessary minimum concentration.

[0016]

When a solution containing an element that promotes crystallization is applied to a substrate on which an amorphous silicon film is formed, an aqueous solution, an organic solvent solution, or the like can be used as the solution. Here, the inclusion includes both the meaning of inclusion as a compound and the meaning of inclusion by simply dispersing.

[0017]

As the solvent containing the catalyst element, a solvent selected from water, alcohol, acid and ammonia which are polar solvents can be used.

[0018]

When nickel is used as a catalyst and this nickel is included in a polar solvent, nickel is introduced as a nickel compound. Typical nickel compounds include nickel bromide, nickel acetate, nickel oxalate, nickel carbonate, nickel chloride, nickel iodide, nickel nitrate, nickel sulfate, nickel formate, nickel acetylacetonate, 4-cyclohexylbutyric acid. A material selected from nickel, nickel oxide and nickel hydroxide is used.

[0019]

As the solvent containing the catalyst element, a nonpolar solvent selected from benzene, toluene, xylene, carbon tetrachloride, chloroform, and ether can be used.

[0020]

In this case, nickel is introduced as a nickel compound. As this nickel compound, typically, one selected from nickel acetylacetonate and nickel 2-ethylhexanoate can be used.

[0021]

When Fe (iron) is used as the catalyst element, a material known as an iron salt as the compound, for example, ferrous bromide (FeBr) 2 6H 2 O), ferric bromide (FeBr) Three 6H 2 O), ferric acetate (Fe (C 2 H Three O 2 ) Three xH 2 O), ferrous chloride (FeCl 2 4H 2 O), ferric chloride (FeCl Three 6H 2 O), ferric fluoride (FeF) Three 3H 2 O), ferric nitrate (Fe (NO Three ) Three 9H 2 O), ferrous phosphate (Fe Three (PO Four ) 2 8H 2 O), ferric phosphate (FePO Four 2H 2 Those selected from O) can be used.

[0022]

When Co (cobalt) is used as the catalyst element, a material known as a cobalt salt as the compound, for example, cobalt bromide (CoBr6H) 2 O), cobalt acetate (Co (C 2 H Three O 2 ) 2 4H 2 O), cobalt chloride (CoCl 2 6H 2 O), cobalt fluoride (CoF) 2 xH 2 O), cobalt nitrate (Co (No Three ) 2 6H 2 Those selected from O) can be used.

[0023]

When Ru (ruthenium) is used as the catalyst element, the compound is known as a ruthenium salt, such as ruthenium chloride (RuCl). Three H 2 O) can be used.

[0024]

When Rh (rhodium) is used as a catalytic element, a material known as a rhodium salt as the compound, for example, rhodium chloride (RhCl) Three 3H 2 O) can be used.

[0025]

When Pd (palladium) is used as a catalyst element, a material known as a palladium salt as the compound, for example, palladium chloride (PdCl 2 2H 2 O) can be used.

[0026]

When Os (osnium) is used as the catalytic element, a material known as an osnium salt as the compound, for example, osmium chloride (OsCl) Three ) Can be used.

[0027]

When Ir (iridium) is used as a catalyst element, a material known as an iridium salt as the compound, for example, iridium trichloride (IrCl Three 3H 2 O), iridium tetrachloride (IrCl Four ) Can be used.

[0028]

When Pt (platinum) is used as the catalyst element, a material known as a platinum salt as the compound, for example, platinous chloride (PtCl) Four 5H 2 O) can be used.

[0029]

When Cu (copper) is used as the catalyst element, cupric acetate (Cu (CH Three COO) 2 ), Cupric chloride (CuCl 2 2H 2 O), cupric nitrate (Cu (NO Three ) 2 3H 2 Materials selected from O) can be used.

[0030]

When gold is used as the catalytic element, gold trichloride (AuCl) is used as the compound. Three xH 2 O), gold chloride (AuHCl) Four 4H 2 O), sodium tetrachlorogold (AuNaCl) Four 2H 2 Materials selected from O) can be used.

[0031]

It is also useful to add a surfactant to the solution containing the catalyst element. This is for increasing the adhesion to the surface to be coated and controlling the adsorptivity. This surfactant may be applied on the surface to be coated in advance.

[0032]

When nickel simple substance is used as a catalyst element, it is necessary to dissolve in acid to form a solution.

[0033]

The above is an example using a solution in which nickel as a catalyst element is completely dissolved, but even if nickel is not completely dissolved, powder of nickel alone or a compound of nickel is uniformly distributed in the dispersion medium. Materials such as dispersed emulsions may be used.

[0034]

These are the same even when a material other than nickel is used as the catalyst element.

[0035]

When nickel is used as a catalyst element for promoting crystallization, and a polar solvent such as water is used as a solution solvent containing nickel, these solutions are directly applied to the surface to be a substrate on which an amorphous silicon film is formed. Then, the solution may be repelled. In this case, a thin oxide film having a thickness of 100 mm or less is first formed, and a solution containing a catalytic element is applied thereon, whereby the solution can be uniformly applied. Also effective is a method of improving wetting by adding a material such as a surfactant to the solution. In the structure of a TFT formed on a glass substrate, a method of forming a silicon oxide film or a silicon nitride film as a base film on the glass substrate surface is known. In this case, a solution can be applied directly. It is.

[0036]

Further, by using a nonpolar solvent such as a toluene solution of nickel 2-ethylhexanoate as the solution, the solution can be applied without forming an underlying oxide film. In this case, it is effective to apply in advance a material such as an adhesive used in resist application.

[0037]

The amount of the catalytic element contained in the solution depends on the type of the solution, but as a general tendency, the amount of nickel is 1 ppm to 200 ppm, preferably 1 ppm to 50 ppm, based on the solution (weight ratio of the catalytic element to the whole solution) ) Is desirable. This is a value determined in view of the nickel concentration in the film and the hydrofluoric acid resistance after crystallization is completed.

[0038]

Moreover, crystal growth can be selectively performed by selectively applying a solution containing a catalytic element. Particularly in this case, crystal growth can be performed in a direction substantially parallel to the surface of the silicon film from the region where the solution is applied toward the region where the solution is not applied. In this specification, a region where crystal growth is performed in a direction substantially parallel to the surface of the silicon film is referred to as a laterally crystallized region.

[0039]

Further, it has been confirmed that the concentration of the catalytic element is low in the region where the crystal growth is performed in the lateral direction. Although it is useful to use a crystalline silicon film as the active layer region of the semiconductor device, it is generally preferable that the impurity concentration in the active layer region is low. Therefore, it is useful for device fabrication to form the active layer region of the semiconductor device using the region where the crystal is grown in the lateral direction.

[0040]

In the present invention, since a catalytic element for promoting crystallization is introduced into the interface between the surface to be formed and the thin film silicon semiconductor formed on the surface to be formed, the catalyst on the surface of the crystallized thin film silicon semiconductor is used. The element concentration can be kept low.

[0041]

In general, a TFT has a configuration of an insulated gate type field effect transistor. In an insulated gate type field effect transistor, an interface between a channel forming region and a gate insulating film and a region near the interface are important.

[0042]

In the insulated gate field effect semiconductor device, if there is a level at the interface between the channel forming region and the gate insulating film or in the vicinity thereof, the characteristics of the insulated gate field effect transistor are greatly inhibited. As a factor for forming such a level, mobile ions and impurities can be considered. Therefore, when manufacturing a TFT employing a configuration in which a gate insulating film is formed on a silicon thin film, it is desirable that impurities and the like are not present on the silicon thin film surface as much as possible.

[0043]

Furthermore, the present invention is extremely useful because the concentration of the catalytic element that promotes crystallization can be reduced as much as possible in the entire region of the crystallized silicon thin film.

[0044]

In addition, when the method of the present invention is adopted, the concentration distribution of the catalytic element in the depth direction of the surface to be processed, which is seen when using the plasma processing, is not seen, so the catalytic element diffuses unnecessarily during the heat treatment There is no such thing.

[0045]

As described above, in the present invention, since the concentration of the catalytic elements present on the surface of the crystallized silicon thin film can be reduced as much as possible, it is possible to form a TFT that is not affected by these catalytic elements as much as possible. . That is, by introducing a catalytic element that promotes crystallization in contact with the lower surface of the silicon thin film, a configuration in which the catalytic element has less influence on the characteristics of the electronic device using the crystalline silicon film surface can be realized.

[0046]

In the present invention, the most prominent effect can be obtained when nickel is used as the catalyst element, but the other usable catalyst elements are preferably Ni, Pd, Pt, Cu, Ag, Au, In, and the like. , Sn, Pd, Sn, Pd, P, As, Sb can be used. One or more kinds of elements selected from group VIII elements, IIIb, IVb, and Vb elements can also be used.

[0047]

The method for introducing the catalyst element is not limited to using a solution such as an aqueous solution or alcohol, and a substance containing the catalyst element can be widely used. For example, a metal compound or oxide containing a catalyst element can be used.

[0048]

【Example】

[Example 1]

[0049]

In this embodiment, a catalyst element that promotes crystallization is contained in an aqueous solution, applied onto a glass substrate, and then an amorphous silicon film is formed and crystallized by heat treatment.

[0050]

In this embodiment, Corning 7059 glass is used as the substrate. Moreover, the magnitude | size shall be 100 mm x 100 mm.

[0051]

FIG. 1 shows a manufacturing process of this embodiment. First, a base silicon oxide film 12 is formed on a

[0052]

Next, an acetate solution is prepared by adding nickel to the acetate solution. The nickel concentration is 25 ppm. Then, 5 ml of this acetate solution is dropped on the surface of the silicon oxide film 12, and this state is maintained for 5 minutes. Then, spin drying (2000 rpm, 60 seconds) is performed using a spinner. (Fig. 1 (A))

[0053]

The concentration of nickel in the acetic acid solution is preferably used in the range of 1 ppm to 50 ppm.

[0054]

By performing this nickel solution coating step once to a plurality of times, a layer containing nickel having an average film thickness of several to several hundreds of mm can be formed on the surface of the silicon oxide film 12 after spin drying. it can. In this case, nickel in this layer diffuses into the amorphous silicon film in the subsequent heating step, and acts as a catalyst for promoting crystallization. Note that this layer is not necessarily a complete film.

[0055]

After application of the solution, pre-baking is performed at a temperature of 400 ° C. in a nitrogen atmosphere. This step is performed to decompose the solution adsorbed on the surface of the silicon oxide film 12. By performing this step, it is possible to prevent the quality of the amorphous silicon film 14 to be formed later from being deteriorated. Needless to say, the pre-baking temperature is changed depending on the type of solution used in the coating process.

[0056]

Next, an amorphous silicon film 14 is formed to a thickness of 100 to 1500 mm by plasma CVD or LPCVD. Here, the amorphous silicon film 12 is formed to a thickness of 1000 mm by plasma CVD.

[0057]

Then, using a heating furnace, heat treatment is performed at 550 ° C. for 4 hours in a nitrogen atmosphere. As a result, the crystalline silicon thin film 14 formed on the

[0058]

The above heat treatment can be performed at a temperature of 450 ° C. or higher. However, if the temperature is low, the heating time must be lengthened and the production efficiency is lowered. On the other hand, if it is 550 ° or more, the problem of heat resistance of the glass substrate used as the substrate will surface.

[0059]

[Example 2]

In this embodiment, nickel, which is a catalyst element, is contained in alcohol, which is a non-aqueous solution, and applied onto an amorphous silicon film. In this example, nickel acetylacetonate is used as the nickel compound, and the alcohol is contained in the compound. The concentration of nickel may be set to a required concentration.

[0060]

The subsequent steps are the same as those shown in Example 1. The outline of the manufacturing process is the same as that shown in FIG. Specific conditions will be described below. First, nickel acetylacetonate is prepared as a nickel compound. Since this substance is soluble in alcohol and has a low decomposition temperature, it can be easily decomposed during heating in the crystallization step.

[0061]

Further, ethanol is used as the alcohol. First, the above-mentioned nickel acetylacetonate is adjusted to 50 ppm in terms of nickel in ethanol to prepare a solution containing nickel.

[0062]

Then, this solution is applied onto the silicon oxide film 12 which is a base film. The application of the solution onto the underlying silicon oxide film is less than when the aqueous solution of Example 1 is used. This is due to the fact that the contact angle of alcohol is smaller than that of water. Here, it is set as 2 ml dripping with respect to an area of 100 square mm.

[0063]

And it hold | maintains for 5 minutes in this state. Thereafter, drying is performed using a spinner. At this time, the spinner is rotated at 1500 rpm for 1 minute. Thereafter, an amorphous silicon film is formed and subjected to crystallization at 550 ° C. for 4 hours. Thus, a crystalline silicon film is obtained.

[0064]

Example 3

In this embodiment, nickel as a catalytic element is dissolved in an acid, and the acid in which the nickel is dissolved is applied onto the oxide film 12 underlying the amorphous silicon film. The outline of the manufacturing process is the same as that shown in FIG.

[0065]

In this embodiment, 0.1 mol / l nitric acid is used as the acid. Nickel powder is dissolved in this nitric acid so that the concentration of nickel is 50 ppm, and this is used as a solution. The subsequent steps are the same as those in the first embodiment.

[0066]

Example 4

This embodiment shows an example in which a TFT provided in each pixel portion of an active matrix liquid crystal display device is manufactured using a crystalline silicon film manufactured by using the method of the present invention. Needless to say, the application range of the TFT is applicable not only to a liquid crystal display device but also to a generally called thin film integrated circuit.

[0067]

FIG. 2 shows an outline of the manufacturing process of this example. First, a base silicon oxide film (not shown) is formed to a thickness of 2000 mm on a glass substrate. This silicon oxide film has functions of preventing the diffusion of impurities from the glass substrate and improving the wetting characteristics when introducing the catalytic element.

[0068]

Then, an acetate solution containing 10 ppm of nickel is applied, held for 5 minutes, and spin dried using a spinner. Thereafter, pre-baking is performed in a nitrogen atmosphere.

[0069]

The step of introducing nickel may be performed by the method shown in Example 2 or Example 3.

[0070]

Then, an amorphous silicon film is formed to a thickness of 1000 mm by the same method as in Example 1 and crystallized by heat treatment at 550 ° C. for 4 hours. A crystalline silicon film is obtained by this process.

[0071]

Next, the crystallized silicon film is patterned to form island-

[0072]

Care must be taken in the production of the

[0073]

In this state, crystallization of the

[0074]

Thereafter, an aluminum film having a thickness of 2000 to 1 μm is formed by an electron beam evaporation method and patterned to form a

[0075]

Thereafter, an impurity (phosphorus) was implanted into the island-like silicon film of each TFT by the ion doping method (also called plasma doping method) using the gate electrode portion as a mask. As a doping gas, phosphine (PH Three ) Was used. Dose amount is 1-4 × 10 15 cm -2 And

[0076]

Further, as shown in FIG. 2C, irradiation with a KrF excimer laser (wavelength 248 nm, pulse width 20 nsec) is performed to improve the crystallinity of the portion where the crystallinity has deteriorated due to the introduction of the impurity region. Laser energy density is 150-400mJ / cm 2 , Preferably 200 to 250 mJ / cm 2 It is. Thus, N-type impurity (phosphorus)

[0077]

In this process, instead of using a laser, a flash lamp is used to raise the temperature to 1000 to 1200 ° C. (silicon monitor temperature) in a short time and heat the sample, so-called RTA (rapid thermal annealing) (RTP, (Also referred to as a rapid thermal process).

[0078]

Thereafter, a silicon oxide film having a thickness of 3000 mm is formed on the entire surface as an

[0079]

Then, the

[0080]

A crystalline silicon film into which nickel has been introduced by plasma treatment has a low selectivity to buffer hydrofluoric acid compared to a silicon oxide film, and thus is often etched in the contact hole forming step.

[0081]

However, when nickel is introduced using an aqueous solution at a low concentration of 10 ppm as in this embodiment, the resistance to hydrofluoric acid is high, so that the formation of the contact hole can be performed stably and with good reproducibility.

[0082]

Finally, annealing in hydrogen at 300-400 ° C. for 0.1-2 hours completes the hydrogenation of silicon. In this way, the TFT is completed. A large number of TFTs manufactured at the same time are arranged in a matrix to complete an active matrix liquid crystal display device. This TFT has source /

[0083]

When the configuration of this example is adopted, the concentration of nickel present in the active layer is 3 × 10 18 cm -3 1x10 to a degree or less 16 atoms cm -3 ~ 3x10 18 atoms cm -3 It is thought that.

[0084]

Example 5

FIG. 3 shows a cross-sectional view of the manufacturing process of this example. First, a silicon

[0085]

Next, the amorphous silicon film was crystallized by the method shown in Example 1. That is, a solution containing nickel is applied onto the underlying

[0086]

Next, an intrinsic (I-type) amorphous silicon film having a thickness of 500 to 1500 mm, for example, 1000 mm is formed by plasma CVD. Then, it is crystallized by annealing for 48 hours at 600 ° C. in a nitrogen atmosphere (atmospheric pressure), and the silicon film is patterned to a size of 10 to 1000 μm square to form an island-like silicon film (TFT active layer) 503. . (Fig. 3 (A))

[0087]

Thereafter, an atmosphere of oxygen containing 70 to 90% of water vapor, 1 atmosphere, 500 to 750 ° C., typically 600 ° C. is formed using a pyrogenic reaction method at a ratio of hydrogen / oxygen = 1.5 to 1.9. To do. By leaving it in this atmosphere for 3 to 5 hours, the surface of the silicon film is oxidized to form a

[0088]

In general, the thinner the silicon oxide film (gate insulating film) and the active layer, the better the characteristics of improving mobility and reducing off-current. On the other hand, the initial amorphous silicon film is easily crystallized as the film thickness increases. Therefore, conventionally, there has been a contradiction in terms of characteristics and process regarding the thickness of the active layer. The present invention solves this contradiction for the first time. That is, a thick amorphous silicon film is formed before crystallization to obtain a good crystalline silicon film. Next, by oxidizing the silicon film, the silicon film is thinned to improve the characteristics as a TFT. Further, this thermal oxidation has a feature that the amorphous component and the crystal grain boundary in which recombination centers are likely to exist are easily oxidized, and as a result, the number of recombination centers in the active layer is reduced. This increases the product yield.

[0089]

After the

Subsequently, polycrystalline silicon (containing 0.01 to 0.2% phosphorus) having a thickness of 3000 to 8000 mm, for example, 6000 mm is formed by low pressure CVD. Then, the

[0090]

Thereafter, annealing is performed by laser light irradiation. As the laser light, a KrF excimer laser (wavelength 248 nm, pulse width 20 nsec) was used, but other lasers may be used. The laser light irradiation condition is an energy density of 200 to 400 mJ / cm. 2 For example, 250 mJ / cm 2 Then, 2 to 10 shots, for example, 2 shots are irradiated at one place. The effect may be increased by heating the substrate to about 200 to 450 ° C. during the laser light irradiation. (Figure 3 (C))

[0091]

Further, this step may be a method by lamp annealing using near infrared light. Near-infrared rays are more easily absorbed by crystallized silicon than amorphous silicon, and effective annealing comparable to thermal annealing at 1000 ° C. or higher can be performed. On the other hand, the glass substrate (far infrared light is absorbed by the glass substrate, but visible / near infrared light (wavelength 0.5 to 4 μm) is hardly absorbed) is hardly absorbed. Since it is not heated and only a short time is required, it can be said that it is an optimal method in a process where shrinkage of the glass substrate is a problem.

[0092]

Subsequently, a

[0093]

The mobility of the TFT obtained by the method shown above is 110 to 150 cm. 2 / Vs and S value were 0.2 to 0.5 V / digit. Further, when a P-channel TFT in which boron is doped in the source / drain by a similar method was also produced, the mobility was 90 to 120 cm. 2 / Vs and S value are 0.4 to 0.6 V / digit, and the mobility is 20% or more higher than when a gate insulating film is formed by a known PVD method or CVD method, and the S value is 20 More than%.

Also, from the viewpoint of reliability, the TFT manufactured in this example showed a good result that is not inferior to a TFT manufactured by high-temperature thermal oxidation at 1000 ° C.

[0094]

【effect】

By manufacturing a semiconductor device using a crystalline silicon film that is crystallized at a low temperature in a short time by introducing a catalytic element, a device with high productivity and good characteristics can be obtained.

[Brief description of the drawings]

FIG. 1 shows a manufacturing process of an example.

FIG. 2 shows a manufacturing process of the example.

FIG. 3 shows a manufacturing process of the example.

[Explanation of symbols]

11 .... Glass substrate

12 .... Silicon oxide film

13 .... Acetic acid solution film containing nickel

14... Silicon film

104 ... Active layer

105 ... Silicon oxide film

106 ... Gate electrode

109 ... Oxide layer

108 ... Source / drain region

109 ... Drain / source region

110... Interlayer insulating film (silicon oxide film)

111 ... Pixel electrode (ITO)

112 ... Electrodes

113 ... Electrode

Claims (16)

前記酸化膜上に接して非晶質珪素の結晶化を助長する元素を含有させた溶液をスピナーを用いて塗布し、

前記非晶質珪素の結晶化を助長する元素を含有させた溶液を乾燥させ、

前記非晶質珪素の結晶化を助長する元素を含有させた溶液が塗布された面に接して非晶質珪素膜を形成し、

前記非晶質珪素膜を加熱することにより結晶化させることを特徴とする半導体装置作製方法。An oxide film is formed on the glass substrate,

A solution containing an element that promotes crystallization of amorphous silicon in contact with the oxide film is applied using a spinner ,

Drying the solution containing an element that promotes crystallization of the amorphous silicon;

Forming an amorphous silicon film in contact with a surface coated with a solution containing an element that promotes crystallization of the amorphous silicon;

A method for manufacturing a semiconductor device, wherein the amorphous silicon film is crystallized by heating.

前記界面活性剤が混合された非晶質珪素の結晶化を助長する元素を含有させた溶液を乾燥させ、

前記界面活性剤が混合された非晶質珪素の結晶化を助長する元素を含有させた溶液が塗布された面に接して非晶質珪素膜を形成し、

前記非晶質珪素膜を加熱することにより結晶化させることを特徴とする半導体装置作製方法。A solution containing an element that promotes crystallization of amorphous silicon mixed with a surfactant in contact with a glass substrate is applied using a spinner ,

Drying a solution containing an element that promotes crystallization of amorphous silicon mixed with the surfactant;

Forming an amorphous silicon film in contact with a surface coated with a solution containing an element that promotes crystallization of amorphous silicon mixed with the surfactant;

A method for manufacturing a semiconductor device, wherein the amorphous silicon film is crystallized by heating.

前記非晶質珪素の結晶化を助長する元素を含む化合物を無極性溶媒に溶解あるいは分散させた溶液を乾燥させ、

前記非晶質珪素の結晶化を助長する元素を含む化合物を無極性溶媒に溶解あるいは分散させた溶液が塗布された面に接して非晶質珪素膜を形成し、

前記非晶質珪素膜を加熱することにより結晶化させることを特徴とする半導体装置作製方法。 Using a spinner, a solution in which a compound containing an element that promotes crystallization of amorphous silicon in contact with a glass substrate is dissolved or dispersed in a nonpolar solvent is applied.

Drying a solution in which a compound containing an element that promotes crystallization of amorphous silicon is dissolved or dispersed in a nonpolar solvent;

Forming an amorphous silicon film in contact with a surface coated with a solution in which a compound containing an element that promotes crystallization of amorphous silicon is dissolved or dispersed in a nonpolar solvent;

A method for manufacturing a semiconductor device, wherein the amorphous silicon film is crystallized by heating.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP31916694A JP4125387B2 (en) | 1993-12-01 | 1994-11-28 | Semiconductor device manufacturing method |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP5-329763 | 1993-12-01 | ||

| JP32976393 | 1993-12-01 | ||

| JP31916694A JP4125387B2 (en) | 1993-12-01 | 1994-11-28 | Semiconductor device manufacturing method |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH07211634A JPH07211634A (en) | 1995-08-11 |

| JP4125387B2 true JP4125387B2 (en) | 2008-07-30 |

Family

ID=26569625

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP31916694A Expired - Fee Related JP4125387B2 (en) | 1993-12-01 | 1994-11-28 | Semiconductor device manufacturing method |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4125387B2 (en) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007053398A (en) * | 2006-10-18 | 2007-03-01 | Semiconductor Energy Lab Co Ltd | The formation method of crystalline silica film, and the formation method of thin film transistor |

-

1994

- 1994-11-28 JP JP31916694A patent/JP4125387B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JPH07211634A (en) | 1995-08-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3621151B2 (en) | Method for manufacturing semiconductor device | |

| US5585291A (en) | Method for manufacturing a semiconductor device containing a crystallization promoting material | |

| US5923962A (en) | Method for manufacturing a semiconductor device | |

| JP3431041B2 (en) | Method for manufacturing semiconductor device | |

| US5612250A (en) | Method for manufacturing a semiconductor device using a catalyst | |

| JP3431033B2 (en) | Semiconductor fabrication method | |

| JP3562590B2 (en) | Semiconductor device manufacturing method | |

| US5643826A (en) | Method for manufacturing a semiconductor device | |

| US20040005742A1 (en) | Process for fabricating semiconductor device | |

| US6348367B1 (en) | Method for manufacturing a semiconductor device | |

| JP2873669B2 (en) | Semiconductor device and manufacturing method thereof | |

| JP2791635B2 (en) | Semiconductor device and manufacturing method thereof | |

| JP4141508B2 (en) | Method for manufacturing semiconductor device | |

| JP3431034B2 (en) | Method for manufacturing semiconductor device | |

| JP4125387B2 (en) | Semiconductor device manufacturing method | |

| KR100314705B1 (en) | Semiconductor device and manufacturing method thereof | |

| JP3980298B2 (en) | Method for manufacturing semiconductor device | |

| JP4684246B2 (en) | Method for manufacturing semiconductor device | |

| JP4145963B2 (en) | Semiconductor device manufacturing method | |

| JP3973960B2 (en) | Method for manufacturing semiconductor device | |

| JP3241667B2 (en) | Method for manufacturing semiconductor device and electro-optical device | |

| JP3442693B2 (en) | Method for manufacturing insulating gate type field effect semiconductor device | |

| JP3573969B2 (en) | Semiconductor device manufacturing method | |

| JP3618604B2 (en) | Semiconductor device manufacturing method | |

| JP3626102B2 (en) | Integrated circuit fabrication method |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060328 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060522 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20070417 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070515 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20070627 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20070720 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080508 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110516 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110516 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120516 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120516 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130516 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130516 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140516 Year of fee payment: 6 |

|

| LAPS | Cancellation because of no payment of annual fees |