JP3888062B2 - 放電灯点灯装置 - Google Patents

放電灯点灯装置 Download PDFInfo

- Publication number

- JP3888062B2 JP3888062B2 JP2001005706A JP2001005706A JP3888062B2 JP 3888062 B2 JP3888062 B2 JP 3888062B2 JP 2001005706 A JP2001005706 A JP 2001005706A JP 2001005706 A JP2001005706 A JP 2001005706A JP 3888062 B2 JP3888062 B2 JP 3888062B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- output

- circuit

- discharge lamp

- switching element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02B—CLIMATE CHANGE MITIGATION TECHNOLOGIES RELATED TO BUILDINGS, e.g. HOUSING, HOUSE APPLIANCES OR RELATED END-USER APPLICATIONS

- Y02B20/00—Energy efficient lighting technologies, e.g. halogen lamps or gas discharge lamps

Landscapes

- Circuit Arrangements For Discharge Lamps (AREA)

Description

【発明の属する技術分野】

本発明は、直流電源から放電灯が必要とする電圧に変換するDC−DC変換回路を有し、放電灯を安定点灯させる放電灯点灯装置に関するものである。

【0002】

【従来の技術】

図13に従来の放電灯点灯装置の構成図を示し(例えば特開2000−340385公報参照)、図13の放電灯点灯装置の動作波形図を図14,図15に示す。

【0003】

図13において、放電灯点灯装置は、放電灯11を含む負荷回路1と、直流電源2と、この直流電源2から直流電力を取り込み、この直流電力を制御信号に応じた出力レベルの直流電力に変換し、この変換した直流電力を負荷回路1に出力するDC−DC変換回路3PAと、このDC−DC変換回路3PAの出力の検出を行い、この検出結果を利用して上記制御信号を出力する出力制御回路4PAとを備えている。なお、直流電源2は、バッテリにより構成される場合があるほか、商用電源からの交流電力を整流および平滑などして直流電力を得る電源回路などにより構成される場合もある。

【0004】

負荷回路1に含まれる放電灯11には、例えば高輝度放電灯などが使用され、この場合、負荷回路1には、インバータ回路12と、始動回路13とがさらに設けられる。インバータ回路12は、DC−DC変換回路3PAの出力に接続されたフルブリッジ構成のFETQ1〜Q4と、これらFETQ1〜Q4のスイッチング制御を行って、DC−DC変換回路3PAからの直流電力を交流電力に変換して放電灯11に供給する制御を行うドライブ回路121とにより構成されている。ここで、例えばFETQ1,Q4の組みとFETQ2,Q3の組みとを交互にオン/オフする制御を行えば、DC−DC変換回路3PAからの直流電力を交流電力に変換することができる。

【0005】

始動回路13は、インバータ回路12と放電灯11との間に介設され、消灯状態の放電灯11の始動時に高圧パルス電圧を発生して放電灯11に印加するものである。

【0006】

DC−DC変換回路3PAは、1次巻線n31および2次巻線n32を有するトランスT3と、このトランスT3の1次巻線n31とともに直流電源2の出力に直列接続され、出力制御回路4PAからの制御信号(図14,図15では「SW制御信号」)に従ってオン/オフする例えばトランジスタなどのスイッチング素子SW3と、トランスT3の2次巻線n32の両端に直列接続されるダイオードD30およびコンデンサC30とにより構成され、コンデンサC30の両端が直流電力を出力する出力端となっている。図13の例では、DC−DC変換回路3PAで、直流電源2の電圧が放電灯11を安定点灯させるために必要な電圧に昇降圧され、放電灯点灯装置の出力が主にDC−DC変換回路3PAで調整される構成になっている。

【0007】

出力制御回路4PAは、検出部41と、指令作成部42と、比較部43と、発振回路44と、最大オフ時間可変信号発生回路45とにより構成されている。

【0008】

検出部41は、アンプ411,412などにより構成され、DC−DC変換回路3PAの出力電圧および出力電流の検出を行い、これら検出結果をそれぞれアンプ411およびアンプ412を介して出力するとともに、トランスT3の1次巻線n31および2次巻線n32にそれぞれ流れる1次電流I1および2次電流I2の検出を行うものである。

【0009】

指令作成部42は、DC−DC変換回路3PAの出力電力を決定するための電力指令値を発生する電力指令値発生回路421と、出力電圧の検出結果および電力指令値から演算を通じて出力電流の制御目標となる電流指令値を求める電流指令値演算部422と、出力電流の検出結果および電流指令値から1次側ピーク電流指令を作成する誤差増幅器423とにより構成され、検出部41による出力電圧および出力電流の検出結果から1次側ピーク電流指令を作成するものである。

【0010】

比較部43は、コンパレータ431〜433により構成され、検出部41による各検出結果に対して比較を行い、これら比較結果により各種信号を生成するものである。コンパレータ431は、1次電流I1の検出結果および1次側ピーク電流指令をそれぞれ非反転入力端子および反転入力端子に入力し、図14に示す「431の出力」のようにリセット信号を出力する。コンパレータ432は、非反転入力端子が接地された状態で、2次電流I2の検出結果を反転入力端子に入力し、図14に示す「432の出力」のようにセット信号を出力する。コンパレータ433は、検出部41による出力電圧の検出結果および所定の基準電圧VR−NLをそれぞれ非反転入力端子および反転入力端子に入力し、図15に示す「433の出力」のように、スイッチング許可(Lレベル)/スイッチング禁止(Hレベル)を示すSW許否信号を出力する。

【0011】

発振回路44は、フリップフロップ(SR−FF)441、各種論理回路およびタイマなどにより構成され、最小オン時間制限、最大オン時間制限、最小オフ時間制限および最大オフ時間制限の各機能を有し、比較部43からの各種信号に応じて、スイッチング素子SW3をオン/オフするための制御信号をフリップフロップ441のQ端子から出力するものである。最大オフ時間可変信号発生回路45は、入出力状態に応じて発振回路44の最大オフ時間の制御値を調整するものである。

【0012】

基本的には、出力制御回路4PAは、DC−DC変換回路3PAの出力端でランプ電流およびランプ電圧の検出を行い、これら検出結果と電力指令に基づいて、フィードバック制御でスイッチング素子SW3のオン/オフ制御を行う。図14に示すように、出力制御回路4PAのSW制御信号に従って、回路効率を良くするため、定常定格点灯時には、スイッチング素子SW3は、所定時間、すなわち1次側ピーク電流指令に達するまでオンしたあとオフし、2次側に吐き出される電流I2がゼロになった時点で再度オンするように動作する。以下、この動作を境界モード動作と呼ぶ。このスイッチング素子SW3の駆動の場合、PWM信号は周波数およびデューティともに可変となる。

【0013】

そして、発振回路44の各機能は以下の理由で設けられている。すなわち、図13の例のように負荷が放電灯11である場合、負荷電圧が大幅に変動し、直流電源2が電池などであって電圧が広範囲に変動する場合、周波数変動が広範囲に及ぶ。また、始動直後のようにランプ温度が低い状態で、境界モード動作になると、スイッチング素子SW3のオン時にインダクタ(T3)に蓄えられた磁気エネルギーが電流として負荷回路1側に流出するのに要する時間が長くなり、スイッチング周波数が低下して可聴域に入ったり、ピーク電流が上昇するので、トランスT3を大型化する必要が生じる。このため、図13の放電灯点灯装置では、上記変動およびトランスT3の大型化を防止するべく、最大オフ時間の値を所定値にすることによって、2次側に電流I2が流れている状態でも、オフ時間が最大オフ時間に達すれば、スイッチング素子SW3を強制的に再度オンにして動作させるモードに移行する。これにより、スイッチング周波数の大幅な低下を防止することができる。以下、このモードの動作を連続モード動作と呼ぶ。

【0014】

逆に、スイッチング周波数が高すぎることによるスイッチング損失の増加を防止するため、スイッチング素子SW3のオン/オフ時間の最小値が所定値に決められており、トランスT3に電流が流れている期間が所定のスイッチング周期未満になったとき、トランスT3の1次/2次のどちらにも電流が流れていない期間が存在するモードで動作させる。以下、このモードの動作を不連続モード動作と呼ぶ。

【0015】

また、広範囲な負荷変動および電源変動に対応し、安定なスイッチング動作をさせるため、オン/オフ期間の最大値/最小値を状態にあわせて所定値に調整する。

【0016】

特に、電源を投入して回路が動作を開始しても、放電灯11が消灯状態の無負荷状態であるので、DC−DC変換回路3PAの出力が過昇圧してしまう。このため、図13の放電灯点灯装置では、図15に示すように、コンパレータ433において、出力電圧の検出結果に対して比較を行い、出力電圧の検出結果のレベルが所定の過電圧検出レベルを超えると、発振回路(PWM発振回路)44の最小オフ時間の設定値を略無限大に移行させ、オン信号の出力を禁止するのである。この間欠スイッチング動作により、出力電圧が回路の漏れ電流や検出回路およびドライブ回路121などの僅かな消費電力によって出力電圧が過電圧検出レベル以下になるまでスイッチング素子SW3がオンしなくなり、過昇圧が防止されるのである。

【0017】

【発明が解決しようとする課題】

しかしながら、図16に示す構成のDC−DC変換回路3Aの出力に、リプル低減用のLCフィルタF3を設けたり、また、図17に示す構成のDC−DC変換回路3の出力に、スイッチング動作によって生じるリプル電圧を低減するためのLCフィルタF3を設けたりする場合、無負荷時の過昇圧を防止するために間欠スイッチング動作を行ったとき、その間欠発振の周期がLCフィルタ3の共振周期に近づくと、図18に示すように、LCフィルタF3後の出力電圧に共振現象が生じ、過大な電圧が発生することがある。

【0018】

このため、LCフィルタF3の時定数を大きくして、共振周期を間欠発振周期に比べ非常に大きくすれば、共振現象は抑制できるが、LCフィルタF3を構成するインダクタLF3やコンデンサCF3の大型化を招いてしまう。

【0019】

本発明は、上記事情に鑑みてなされたものであり、DC−DC変換回路の出力にLCフィルタを設けても、負荷回路が無負荷状態である場合に発生し得るLCフィルタの共振現象を抑制することができる放電灯点灯装置を提供することを目的とする。

【0020】

【課題を解決するための手段】

上記課題を解決するための請求項1記載の発明の放電灯点灯装置は、放電灯を含む負荷回路と、直流電源と、スイッチング素子を有し、このスイッチング素子を制御信号に従ってオン/オフすることにより、前記直流電源から直流電力を取り込んでその制御信号に応じた出力レベルの直流電力に変換し、この変換した直流電力を、LCフィルタを介して前記負荷回路に出力するDC−DC変換回路と、このDC−DC変換回路の出力の検出を行い、この検出結果を利用して前記制御信号を出力する出力制御回路とを備え、この出力制御回路は、前記DC−DC変換回路の出力電圧の検出を行い、前記放電灯が消灯している無負荷状態において、前記出力電圧の検出結果が所定の第1電圧に達すると、前記スイッチング素子に対するオン/オフ制御を間欠的に行って、前記出力電圧の検出結果が前記第1電圧を超えないように調整し、前記出力電圧の検出結果が高いほど、前記スイッチング素子に対するオンデューティを小さくし、少なくとも、前記無負荷状態において、前記出力電圧の検出結果が前記第1電圧のレベルに達したときには、前記スイッチング素子に対する1回のスイッチング動作で、前記DC−DC変換回路から前記負荷回路に出力されるエネルギー量と同等のエネルギー量を前記無負荷状態時の回路損失で消費する時間が、前記LCフィルタの共振周期に比べ、十分小さくなるまでオンデューティを小さくすることを特徴とする。

【0021】

請求項2記載の発明は、請求項1記載の放電灯点灯装置において、前記出力制御回路は、前記無負荷状態において、前記出力電圧の検出結果が前記第1電圧より低い第2電圧を超えると、少なくとも前記スイッチング素子に対するオンデューティを小さくすることを特徴とする。

【0022】

請求項3記載の発明は、請求項1記載の放電灯点灯装置において、前記出力制御回路は、前記無負荷状態において、少なくとも前記出力電圧の検出結果に応じて前記スイッチング素子に対するオンデューティを連続的に変化させることを特徴とする。

【0023】

請求項4記載の発明の放電灯点灯装置は、放電灯を含む負荷回路と、直流電源と、スイッチング素子を有し、このスイッチング素子を制御信号に従ってオン/オフすることにより、前記直流電源から直流電力を取り込んでその制御信号に応じた出力レベルの直流電力に変換し、この変換した直流電力を、LCフィルタを介して前記負荷回路に出力するDC−DC変換回路と、このDC−DC変換回路の出力の検出を行い、この検出結果を利用して前記制御信号を出力する出力制御回路とを備え、この出力制御回路は、前記DC−DC変換回路の出力電圧の検出を行い、前記放電灯が消灯している無負荷状態において、前記出力電圧の検出結果が所定の第1電圧に達すると、前記スイッチング素子に対するオン/オフ制御を間欠的に行って、前記出力電圧の検出結果が前記第1電圧を超えないように調整し、前記出力電圧の検出結果が高いほど、前記スイッチング素子に対するスイッチング周波数を高くし、少なくとも、前記無負荷状態において、前記出力電圧の検出結果が前記第1電圧のレベルに達したときには、前記スイッチング素子に対する1回のスイッチング動作で、前記DC−DC変換回路から前記負荷回路に出力されるエネルギー量と同等のエネルギー量を前記無負荷状態時の回路損失で消費する時間が、前記LCフィルタの共振周期に比べ、十分小さくなるまでスイッチング周波数を高くすることを特徴とする。

【0024】

請求項5記載の発明は、請求項4記載の放電灯点灯装置において、前記出力制御回路は、前記無負荷状態において、前記出力電圧の検出結果が前記第1電圧より低い第2電圧を超えると、少なくとも前記スイッチング素子に対するスイッチング周波数を高くすることを特徴とする。

【0025】

請求項6記載の発明は、請求項4記載の放電灯点灯装置において、前記出力制御回路は、前記無負荷状態において、少なくとも前記出力電圧の検出結果に応じて前記スイッチング素子に対するスイッチング周波数を連続的に変化させることを特徴とする。

【0026】

請求項7記載の発明は、請求項1〜6のいずれかに記載の放電灯点灯装置において、前記出力制御回路は、前記無負荷状態において、前記出力電圧の検出結果が高いほど、前記スイッチング素子に対するオンデューティを小さくするとともに、前記スイッチング素子に対するスイッチング周波数を高くすることを特徴とする。

【0027】

請求項8記載の発明は、請求項7記載の放電灯点灯装置において、前記出力制御回路は、前記無負荷状態において、前記出力電圧の検出結果が前記第1電圧より低い第2電圧を超えると、前記スイッチング素子に対するオンデューティを小さくし、前記出力電圧の検出結果が前記第1電圧より低い第3電圧を超えると、前記スイッチング素子に対するスイッチング周波数を高くすることを特徴とする。

【0028】

請求項9記載の発明は、請求項8記載の放電灯点灯装置において、前記第2電圧および第3電圧は同一レベルであることを特徴とする。

【0029】

請求項10記載の発明は、請求項8記載の放電灯点灯装置において、前記第2電圧は前記第3電圧よりも高レベルであることを特徴とする。

【0030】

請求項11記載の発明は、請求項8記載の放電灯点灯装置において、前記第3電圧は前記第2電圧よりも高レベルであることを特徴とする。

【0031】

請求項12記載の発明は、請求項8記載の放電灯点灯装置において、前記出力制御回路は、前記無負荷状態において、前記出力電圧の検出結果に応じて、前記スイッチング素子に対するスイッチング周波数およびオンデューティを連続的に変化させることを特徴とする。

【0032】

請求項13記載の発明は、請求項1〜12のいずれかに記載の放電灯点灯装置において、前記DC−DC変換回路内の交番電圧箇所に入力が接続される多倍電圧整流回路をさらに備え、前記出力制御回路は、前記無負荷状態において、前記出力電圧の検出結果がほぼ前記第1電圧のレベルに達するまで、前記多倍電圧整流回路の出力が所定の第4電圧を超えないように、前記スイッチング素子に対してオン/オフ制御を行うことを特徴とする。

【0033】

請求項14記載の発明は、請求項13記載の放電灯点灯装置において、前記出力制御回路は、前記出力電圧の検出結果が前記第2電圧に達するまで、所定値以下のスイッチング周波数で前記スイッチング素子に対してオン/オフ制御を行うことにより、前記多倍電圧整流回路の出力電圧の上昇を抑制し、前記出力電圧の検出結果が前記第2電圧を超えると、前記スイッチング素子に対するスイッチング周波数を増加することにより、前記多倍電圧整流回路の出力電圧の上昇を加速させることを特徴とする。

【0034】

請求項15記載の発明は、請求項1〜14のいずれかに記載の放電灯点灯装置において、前記出力制御回路は、前記直流電源の電圧に対して前記スイッチング素子に対するオンデューティを変化させることを特徴とする。

【0035】

請求項16記載の発明は、請求項15記載の放電灯点灯装置において、前記出力制御回路は、前記直流電源の電圧に対して前記スイッチング素子に対するオンデューティを反比例するように変化させることを特徴とする。

【0036】

【発明の実施の形態】

図1は本発明の第1実施形態に係る放電灯点灯装置の構成図であり、この図を用いて第1実施形態について説明する。

【0037】

図1に示す放電灯点灯装置は、負荷回路1と、直流電源2とを図13の放電灯点灯装置と同様に備えているほか、図13の放電灯点灯装置との相違点として、DC−DC変換回路3と、出力制御回路4とを備えている。

【0038】

DC−DC変換回路3は、1次巻線n31および2次巻線n32を有するトランスT3と、このトランスT3の1次巻線n31とともに直流電源2の出力に直列接続され、出力制御回路4からの制御信号に従ってオン/オフするスイッチング素子SW3と、このスイッチング素子SW3および1次巻線n31の接続点と2次巻線n32の一端との間に接続されるコンデンサC31と、2次巻線n32の他端とグランドとの間に接続されるダイオードD31と、LCフィルタF3とにより構成されている。LCフィルタF3は、2次巻線n32の一端とグランドとの間に直列接続されるインダクタLF3およびコンデンサCF3により構成され、コンデンサCF3の両端がDC−DC変換回路3の出力端となっている。

【0039】

出力制御回路4は、検出部41と、指令作成部42と、比較部43と、発振回路44と、最大オフ時間可変信号発生回路45とを、図13の出力制御回路4PAと同様に備えているほか、この出力制御回路4PAとの相違点として点灯判別回路46を備えている。

【0040】

この点灯判別回路46は、検出部41による出力電圧の検出結果から、放電灯11が消灯状態であって負荷回路1が無負荷状態であるか否かの判別を行い、無負荷状態であれば、発振回路44におけるオン/オフ制御値を無負荷動作時の所定値に切り替えるものである。

【0041】

負荷回路1が無負荷状態であるとき、DC−DC変換回路3の出力がほぼゼロに近く、1次ピーク電流が最大を示すため、スイッチング素子SW3のオン時間を最大オン時間制限の機能で調整でき、また、出力電圧が高いため、2次電流I2が流れる時間が短く、スイッチング素子SW3のオフ時間を最小オフ時間で調整できる。つまり、無負荷時、これら2つの制限値により、スイッチング周波数およびデューティを調整できるのである。

【0042】

ところで、図18に示した出力電圧の共振現象を抑制するためには、間欠スイッチングの周期をLCフィルタF3の共振周期より短くすればよい。いま、無負荷時のスイッチング周期をTSW、LCフィルタ3の共振周期をTLC、1回のスイッチングで出力側に送られるエネルギーをEP、同1回のスイッチング周期内に出力端より消費される回路損失などのエネルギー量をELとしたとき、

(1+EP/EL)×TSW<<TLC

を満足するようにし、無負荷時の1回のスイッチング動作において、出力側へ送られるエネルギーをスイッチング周波数ないしデューティにより調整する。すなわち、1回のスイッチングで出力側に送られるエネルギー量を減らし、出力電圧が過電圧検出レベル以下に低下する時間を短くすることで、間欠スイッチングの周期を短くするのである。負荷回路1が無負荷状態であるとき、このようなスイッチング条件となるように、スイッチング周波数ないしデューティを所定値に切り替えることで、図18に示すような共振現象を抑制することができる。

【0043】

なお、図1の例では、点灯判別による無負荷動作への切替えは、出力電圧の検出結果を利用して行われる構成になっているが、出力電流の検出結果、または出力電流および出力電圧の両検出結果を利用して行われる構成でもよい。

【0044】

図2は本発明の第2実施形態に係る放電灯点灯装置の構成図であり、この図を用いて第2実施形態について説明する。

【0045】

図2に示す放電灯点灯装置は、負荷回路1と、直流電源2と、DC−DC変換回路3とを第1実施形態と同様に備えているほか、第1実施形態との相違点として出力制御回路4Aを備えている。

【0046】

この出力制御回路4Aは、第1実施形態と同様の検出部41、指令作成部42および点灯判別回路46を備えているとともに、コンパレータ431,433により構成される比較部43Aのほか、周波数調整回路47と、発振回路44Aとを備えている。

【0047】

周波数調整回路47は、検出部41による1次電流I1および2次電流I2の検出結果と点灯判別回路46からの無負荷モード切替信号に応じて、スイッチング周波数指令の信号を出力するものである。

【0048】

発振回路44Aは、フリップフロップ441、発振器442および各種論理回路などにより構成され、比較部43Aからの各種信号と周波数調整回路47からのスイッチング周波数指令の信号に応じて、スイッチング素子SW3をオン/オフするための制御信号を出力するものである。

【0049】

つまり、スイッチング周波数は発振器442で決められ、この発振器442の出力信号の立上りでスイッチング素子SW3をオンし、DC−DC変換回路3の1次側に所定の電流が流れると、スイッチング素子SW3をオフするように回路が構成されるのである。また、発振器442の出力信号の立下がりでスイッチング素子SW3を強制的にオフするようにすれば、最大オン時間(最大オンデューティ)を発振器442で決定することができる。

【0050】

負荷回路1が無負荷状態であるとき、出力がほぼゼロであるため、1次側ピーク電流指令が最大値となり、スイッチング周波数およびデューティはほぼ発振器442の条件で決まる。

【0051】

図2の実施形態では、点灯判別回路46により負荷回路1が無負荷状態であると検出されれば、上述のスイッチング条件になるように、周波数調整回路47を通じて発振器442のスイッチング周波数、デューティが切り替えられる。

【0052】

図3は本発明の第3実施形態に係る放電灯点灯装置の構成図、図4は図3の放電灯点灯装置の動作波形図であり、これらの図を用いて第3実施形態について説明する。

【0053】

図3に示す放電灯点灯装置は、負荷回路1と、直流電源2と、DC−DC変換回路3とを第2実施形態と同様に備えているほか、第2実施形態との相違点として、周波数調整回路47に代えて、調整回路(図3では「SW周波数max.ON−Duty調整回路」)47Aを有する出力制御回路4Bを備えている。

【0054】

ここで、前述した実施形態により、DC−DC変換回路3の出力の共振現象を抑制することができるが、無負荷時における回路の損失量が小さいため、上述のスイッチング条件では、DC−DC変換回路3の出力電圧が所定の無負荷電圧まで上昇するのに時間を要し、点灯するまで時間がかかりすぎる。

【0055】

そのため、第3実施形態では、図4に示すように、出力電圧が過電圧検出レベルより低い所定値(図4では「SW条件切替レベル」)になるまでは、図4に示す「無負荷Duty指令」のように、オンデューティを大きくし、昇圧速度を上げる。そして、出力電圧がSW条件切替レベルを越えると、デューティを小さくし、上述のスイッチング条件に切り替えることで、間欠スイッチング状態になった場合の共振現象を抑制することができる。

【0056】

図5は本発明の第4実施形態に係る放電灯点灯装置の動作波形図であり、この図を用いて第4実施形態について説明する。

【0057】

第4実施形態の放電灯点灯装置は、調整回路47Aとは相違する調整回路を有する出力制御回路を備えている以外は第3実施形態の放電灯点灯装置と同様に構成される。つまり、図4では、DC−DC変換回路の出力電圧が過電圧検出レベルより低いSW条件切替レベルに達すると、調整回路47Aを通じて発振回路44Aによるスイッチング素子SW3に対するスイッチングデューティを小さくして、DC−DC変換回路の出力側に送られるエネルギーを減らし、DC−DC変換回路の出力における共振現象を抑制しているが、第4実施形態の調整回路は、図5に示すように、出力電圧がSW条件切替レベルに出力電圧が達すると、図5に示す「無負荷周波数指令」のように、発振回路44Aによるスイッチング素子SW3に対するスイッチング周波数を所定値に上げるのである。この構成でも、間欠スイッチング状態になった場合の共振現象を抑制することができる。

【0058】

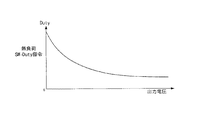

なお、図4では、無負荷Duty指令により、出力電圧に対してスイッチングデューティが段階的に切り替えられる構成になっているが、図6に示すように、無負荷SW−Duty指令により、出力電圧に対してスイッチングデューティが連続的に変化する構成でもよい。

【0059】

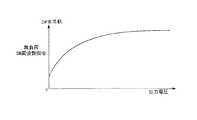

また、図5では、無負荷周波数指令により、出力電圧に対してスイッチング周波数が段階的に切り替えられる構成になっているが、図7に示すように、無負荷SW周波数指令により、出力電圧に対してスイッチング周波数が連続的に変化する構成でもよい。

【0060】

図8は本発明の第5実施形態に係る放電灯点灯装置の動作波形図であり、この図を用いて第5実施形態について説明する。

【0061】

第5実施形態の放電灯点灯装置は、調整回路47Aとは相違する調整回路を有する出力制御回路を備えている以外は第3実施形態の放電灯点灯装置と同様に構成される。

【0062】

第5実施形態の調整回路は、図8に示すように、出力電圧がSW条件切替レベルに出力電圧が達すると、図8に示す「無負荷Duty指令」のように、発振回路44Aによるスイッチング素子SW3に対するスイッチングデューティを小さくするとともに、図8に示す「無負荷周波数指令」のように、発振回路44Aによるスイッチング素子SW3に対するスイッチング周波数を所定値に上げるものである。このように、スイッチング周波数およびデューティの両方を切り替えることで、間欠スイッチング時において、スイッチング素子SW3がスイッチングを行っている場合の出力電圧の上昇率をきめ細かく設定できるようになる。

【0063】

なお、図8の例では、スイッチング周波数およびデューティの切替えは、同一のしきい値レベルで行われる構成になっているが、異なるしきい値レベルで行われる構成でもよい。また、図6および図7の如く、出力電圧に対してスイッチング周波数およびデューティが連続的に変化する構成でもよい。

【0064】

図9は本発明の第6実施形態に係る放電灯点灯装置の構成図、図10は図9の放電灯点灯装置の動作波形図であり、これらの図を用いて第6実施形態について説明する。

【0065】

図9に示す放電灯点灯装置は、直流電源2と、DC−DC変換回路3と、出力制御回路4Bとを第3実施形態と同様に備えているほか、第3実施形態との相違点として負荷回路1Aを備えている。

【0066】

この負荷回路1Aは、第3実施形態と同様のインバータ回路12と、DC−DC変換回路3の2次巻線n32の両端に入力が接続された多倍電圧整流回路14と、始動回路13Aとにより構成されている。始動回路13Aは、多倍電圧整流回路14の出力端とインバータ回路12の一方の出力端との間に接続されるギャップGapと、コンデンサCGと、このコンデンサCGを介してギャップGapの両端に接続される1次巻線n11を有するとともにインバータ回路12の他方の出力端と放電灯11との間に介設される2次巻線n12を有するトランス(パルス・トランス)PT1とにより構成されている。ここで、Gapがオンすることで、コンデンサCGに蓄えられた電荷がトランスPT1の1次巻線n11を介して急速に放電し、トランスPT1の2次巻線n12に発生した高圧パルス電圧が放電灯11に印加し、これにより、放電灯11が放電を開始することになる。

【0067】

GapはコンデンサCGの電圧がそのブレークダウン電圧を超えるとオンになるものであり、図9の例では、コンデンサCGの充電のために、コッククロフト・ワルトンなどの多倍電圧整流回路14が使用されている。

【0068】

この構成では、図10に示すように、無負荷電圧が最大、すなわち過電圧検出レベルに達した後、始動回路13AのコンデンサCGの電圧がGapのブレークダウンの電圧レベルに達するように動作させると、始動しやすく望ましい動作となる。

【0069】

ところで、多倍電圧整流回路14は出力電圧とスイッチング周波数によってコンデンサCGに対する昇圧速度が影響を受け、また、出力電圧はスイッチング周波数とデューティの影響を受ける。すなわち、出力電圧はスイッチング周波数が低くデューティが大きいほど、電圧上昇の速度が上がり、多倍電圧整流回路14の出力はスイッチング周波数が高いほど電圧上昇の速度が上がる。

【0070】

そこで、第6実施形態では、負荷電圧が所定値に達するまでは、スイッチング周波数が低い条件でデューティを大きくして、出力電圧を主に昇圧し、所定値を越えたらデューティを低下させ、スイッチング周波数を上げ、多倍電圧整流回路14の出力の昇圧速度を上げるように構成される。これにより、図10のような動作を実現し、かつ出力の共振現象を抑制することができる。

【0071】

図11は本発明の第7実施形態に係る放電灯点灯装置の構成図、図12は図11の放電灯点灯装置の動作波形図であり、これらの図を用いて第7実施形態について説明する。

【0072】

図11に示す放電灯点灯装置は、負荷回路1と、直流電源2と、DC−DC変換回路3とを第3実施形態と同様に備えているほか、第3実施形態との相違点として出力制御回路4Cを備えている。

【0073】

出力制御回路4Cは、第3実施形態の検出部41および調整回路47Aに代えて、それぞれ、DC−DC変換回路3の入力電圧の検出をさらに行う検出部41A、およびこの検出部41Aによる検出結果をさらに利用する調整回路47Bを有している以外は第3実施形態の出力制御回路4Bと同様に構成されている。

【0074】

図11の放電灯点灯装置は、無負荷条件におけるスイッチング周波数およびデューティのうち、主としてデューティを電流電圧によって可変する。電池などのように電圧の変動範囲が比較的大きな電源を直流電源2に使用する場合、無負荷時のスイッチング条件の設定値を固定するのは困難である。例えば低電圧の入力時で調整すれば、高電圧の入力条件でスイッチングのストレスなどが大きくなる上、共振を抑制する条件から外れる可能性がある。また、高い入力電圧の条件で調整すれば、低電圧の入力時の出力不足から、電圧の立上りが鈍くなり、点灯するまでに時間を要してしまう。

【0075】

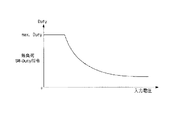

そこで、調整回路47Bは、図12のように、スイッチングデューティを入力電圧に応じて変化させるのであり、入力電圧に対してスイッチングデューティを反比例させるとさらに好適となる。

【0076】

また、調整回路47Bは、図12に示す「max.Duty」により、デューティが必要以上に大きくならないように制限する。そして、このデューティを基準として、上記実施形態と同様、出力電圧によるデューティの切替えないし可変を行う。

【0077】

このように、上記各実施形態によれば、負荷回路1が無負荷状態となるとき、間欠スイッチング状態でのDC−DC変換回路の出力における共振現象を抑制することができ、所定の昇圧速度を得ることができ、放電灯11が点灯するまでの時間を短くできる。

【0078】

【発明の効果】

以上のことから明らかなように、請求項1記載の発明によれば、放電灯を含む負荷回路と、直流電源と、スイッチング素子を有し、このスイッチング素子を制御信号に従ってオン/オフすることにより、前記直流電源から直流電力を取り込んでその制御信号に応じた出力レベルの直流電力に変換し、この変換した直流電力を、LCフィルタを介して前記負荷回路に出力するDC−DC変換回路と、このDC−DC変換回路の出力の検出を行い、この検出結果を利用して前記制御信号を出力する出力制御回路とを備え、この出力制御回路は、前記DC−DC変換回路の出力電圧の検出を行い、前記放電灯が消灯している無負荷状態において、前記出力電圧の検出結果が所定の第1電圧に達すると、前記スイッチング素子に対するオン/オフ制御を間欠的に行って、前記出力電圧の検出結果が前記第1電圧を超えないように調整し、前記出力電圧の検出結果が高いほど、前記スイッチング素子に対するオンデューティを小さくし、少なくとも、前記無負荷状態において、前記出力電圧の検出結果が前記第1電圧のレベルに達したときには、前記スイッチング素子に対する1回のスイッチング動作で、前記DC−DC変換回路から前記負荷回路に出力されるエネルギー量と同等のエネルギー量を前記無負荷状態時の回路損失で消費する時間が、前記LCフィルタの共振周期に比べ、十分小さくなるまでオンデューティを小さくするので、DC−DC変換回路の出力にLCフィルタを設けても、負荷回路が無負荷状態である場合に発生し得るLCフィルタの共振現象を抑制することができる。

【0079】

請求項2記載の発明によれば、請求項1記載の放電灯点灯装置において、前記出力制御回路は、前記無負荷状態において、前記出力電圧の検出結果が前記第1電圧より低い第2電圧を超えると、少なくとも前記スイッチング素子に対するオンデューティを小さくするので、放電灯が点灯するまでの時間を長くすることなく、負荷回路が無負荷状態である場合に発生し得るLCフィルタの共振現象を抑制することができる。

【0080】

請求項3記載の発明によれば、請求項1記載の放電灯点灯装置において、前記出力制御回路は、前記無負荷状態において、少なくとも前記出力電圧の検出結果に応じて前記スイッチング素子に対するオンデューティを連続的に変化させるのであり、この場合も、負荷回路が無負荷状態である場合に発生し得るLCフィルタの共振現象を抑制することができる。

【0081】

請求項4記載の発明によれば、放電灯を含む負荷回路と、直流電源と、スイッチング素子を有し、このスイッチング素子を制御信号に従ってオン/オフすることにより、前記直流電源から直流電力を取り込んでその制御信号に応じた出力レベルの直流電力に変換し、この変換した直流電力を、LCフィルタを介して前記負荷回路に出力するDC−DC変換回路と、このDC−DC変換回路の出力の検出を行い、この検出結果を利用して前記制御信号を出力する出力制御回路とを備え、この出力制御回路は、前記DC−DC変換回路の出力電圧の検出を行い、前記放電灯が消灯している無負荷状態において、前記出力電圧の検出結果が所定の第1電圧に達すると、前記スイッチング素子に対するオン/オフ制御を間欠的に行って、前記出力電圧の検出結果が前記第1電圧を超えないように調整し、前記出力電圧の検出結果が高いほど、前記スイッチング素子に対するスイッチング周波数を高くし、少なくとも、前記無負荷状態において、前記出力電圧の検出結果が前記第1電圧のレベルに達したときには、前記スイッチング素子に対する1回のスイッチング動作で、前記DC−DC変換回路から前記負荷回路に出力されるエネルギー量と同等のエネルギー量を前記無負荷状態時の回路損失で消費する時間が、前記LCフィルタの共振周期に比べ、十分小さくなるまでスイッチング周波数を高くするので、DC−DC変換回路の出力にLCフィルタを設けても、負荷回路が無負荷状態である場合に発生し得るLCフィルタの共振現象を抑制することができる。

【0082】

請求項5記載の発明によれば、請求項4記載の放電灯点灯装置において、前記出力制御回路は、前記無負荷状態において、前記出力電圧の検出結果が前記第1電圧より低い第2電圧を超えると、少なくとも前記スイッチング素子に対するスイッチング周波数を高くするのであり、この場合も、負荷回路が無負荷状態である場合に発生し得るLCフィルタの共振現象を抑制することができる。

【0083】

請求項6記載の発明によれば、請求項4記載の放電灯点灯装置において、前記出力制御回路は、前記無負荷状態において、少なくとも前記出力電圧の検出結果に応じて前記スイッチング素子に対するスイッチング周波数を連続的に変化させるのであり、この場合も、負荷回路が無負荷状態である場合に発生し得るLCフィルタの共振現象を抑制することができる。

【0084】

請求項7記載の発明によれば、請求項1〜6のいずれかに記載の放電灯点灯装置において、前記出力制御回路は、前記無負荷状態において、前記出力電圧の検出結果が高いほど、前記スイッチング素子に対するオンデューティを小さくするとともに、前記スイッチング素子に対するスイッチング周波数を高くするので、DC−DC変換回路の出力電圧の上昇率をきめ細かく設定することができる。

【0085】

請求項8記載の発明によれば、請求項7記載の放電灯点灯装置において、前記出力制御回路は、前記無負荷状態において、前記出力電圧の検出結果が前記第1電圧より低い第2電圧を超えると、前記スイッチング素子に対するオンデューティを小さくし、前記出力電圧の検出結果が前記第1電圧より低い第3電圧を超えると、前記スイッチング素子に対するスイッチング周波数を高くするので、放電灯が点灯するまでの時間を長くすることなく、負荷回路が無負荷状態である場合に発生し得るLCフィルタの共振現象を抑制することができる。

【0086】

請求項9記載の発明によれば、請求項8記載の放電灯点灯装置において、前記第2電圧および第3電圧は同一レベルであり、この場合も、負荷回路が無負荷状態である場合に発生し得るLCフィルタの共振現象を抑制することができる。

【0087】

請求項10記載の発明によれば、請求項8記載の放電灯点灯装置において、前記第2電圧は前記第3電圧よりも高レベルであり、この場合も、負荷回路が無負荷状態である場合に発生し得るLCフィルタの共振現象を抑制することができる。

【0088】

請求項11記載の発明によれば、請求項8記載の放電灯点灯装置において、前記第3電圧は前記第2電圧よりも高レベルであり、この場合も、負荷回路が無負荷状態である場合に発生し得るLCフィルタの共振現象を抑制することができる。

【0089】

請求項12記載の発明によれば、請求項8記載の放電灯点灯装置において、前記出力制御回路は、前記無負荷状態において、前記出力電圧の検出結果に応じて、前記スイッチング素子に対するスイッチング周波数およびオンデューティを連続的に変化させるのであり、この場合も、負荷回路が無負荷状態である場合に発生し得るLCフィルタの共振現象を抑制することができる。

【0090】

請求項13記載の発明によれば、請求項1〜12のいずれかに記載の放電灯点灯装置において、前記DC−DC変換回路内の交番電圧箇所に入力が接続される多倍電圧整流回路をさらに備え、前記出力制御回路は、前記無負荷状態において、前記出力電圧の検出結果がほぼ前記第1電圧のレベルに達するまで、前記多倍電圧整流回路の出力が所定の第4電圧を超えないように、前記スイッチング素子に対してオン/オフ制御を行うので、好適な始動性を確保しつつ、負荷回路が無負荷状態である場合に発生し得るLCフィルタの共振現象を抑制することができる。

【0091】

請求項14記載の発明によれば、請求項13記載の放電灯点灯装置において、前記出力制御回路は、前記出力電圧の検出結果が前記第2電圧に達するまで、所定値以下のスイッチング周波数で前記スイッチング素子に対してオン/オフ制御を行うことにより、前記多倍電圧整流回路の出力電圧の上昇を抑制し、前記出力電圧の検出結果が前記第2電圧を超えると、前記スイッチング素子に対するスイッチング周波数を増加することにより、前記多倍電圧整流回路の出力電圧の上昇を加速させるので、好適な始動性を確保しつつ、負荷回路が無負荷状態である場合に発生し得るLCフィルタの共振現象を抑制することができる。

【0092】

請求項15記載の発明によれば、請求項1〜14のいずれかに記載の放電灯点灯装置において、前記出力制御回路は、前記直流電源の電圧に対して前記スイッチング素子に対するオンデューティを変化させるのであり、この場合も、負荷回路が無負荷状態である場合に発生し得るLCフィルタの共振現象を抑制することができる。

【0093】

請求項16記載の発明によれば、請求項15記載の放電灯点灯装置において、前記出力制御回路は、前記直流電源の電圧に対して前記スイッチング素子に対するオンデューティを反比例するように変化させるのであり、この場合も、負荷回路が無負荷状態である場合に発生し得るLCフィルタの共振現象を抑制することができる。

【図面の簡単な説明】

【図1】 本発明の第1実施形態に係る放電灯点灯装置の構成図である。

【図2】 本発明の第2実施形態に係る放電灯点灯装置の構成図である。

【図3】 本発明の第3実施形態に係る放電灯点灯装置の構成図である。

【図4】 図3の放電灯点灯装置の動作波形図である。

【図5】 本発明の第4実施形態に係る放電灯点灯装置の動作波形図である。

【図6】 DC−DC変換回路の出力電圧に対してスイッチング素子のデューティを連続的を変化させる別の制御例を示す図である。

【図7】 DC−DC変換回路の出力電圧に対してスイッチング素子のスイッチング周波数を連続的を変化させる別の制御例を示す図である。

【図8】 本発明の第5実施形態に係る放電灯点灯装置の動作波形図である。

【図9】 本発明の第6実施形態に係る放電灯点灯装置の構成図である。

【図10】 図9の放電灯点灯装置の動作波形図である。

【図11】 本発明の第7実施形態に係る放電灯点灯装置の構成図である。

【図12】 図11の放電灯点灯装置の動作波形図である。

【図13】 従来の放電灯点灯装置の構成図である。

【図14】 図13の放電灯点灯装置の動作波形図である。

【図15】 図13の放電灯点灯装置の動作波形図である。

【図16】 DC−DC変換回路の出力にLCフィルタを設けた場合の従来の放電灯点灯装置の構成図である。

【図17】 DC−DC変換回路の出力にLCフィルタを設けた場合の従来の放電灯点灯装置の構成図である。

【図18】 図16,図17の放電灯点灯装置のDC−DC変換回路の出力で発生し得る共振現象の例を示す図である。

【符号の説明】

1,1A 負荷回路

11 放電灯

14 多倍電圧整流回路

2 直流電源

3 DC−DC変換回路

SW3 スイッチング素子

4,4A,4B,4C 出力制御回路

Claims (16)

- 放電灯を含む負荷回路と、直流電源と、スイッチング素子を有し、このスイッチング素子を制御信号に従ってオン/オフすることにより、前記直流電源から直流電力を取り込んでその制御信号に応じた出力レベルの直流電力に変換し、この変換した直流電力を、LCフィルタを介して前記負荷回路に出力するDC−DC変換回路と、このDC−DC変換回路の出力の検出を行い、この検出結果を利用して前記制御信号を出力する出力制御回路とを備え、

この出力制御回路は、前記DC−DC変換回路の出力電圧の検出を行い、前記放電灯が消灯している無負荷状態において、前記出力電圧の検出結果が所定の第1電圧に達すると、前記スイッチング素子に対するオン/オフ制御を間欠的に行って、前記出力電圧の検出結果が前記第1電圧を超えないように調整し、前記出力電圧の検出結果が高いほど、前記スイッチング素子に対するオンデューティを小さくし、少なくとも、前記無負荷状態において、前記出力電圧の検出結果が前記第1電圧のレベルに達したときには、前記スイッチング素子に対する1回のスイッチング動作で、前記DC−DC変換回路から前記負荷回路に出力されるエネルギー量と同等のエネルギー量を前記無負荷状態時の回路損失で消費する時間が、前記LCフィルタの共振周期に比べ、十分小さくなるまでオンデューティを小さくする

ことを特徴とする放電灯点灯装置。 - 前記出力制御回路は、前記無負荷状態において、前記出力電圧の検出結果が前記第1電圧より低い第2電圧を超えると、少なくとも前記スイッチング素子に対するオンデューティを小さくすることを特徴とする請求項1記載の放電灯点灯装置。

- 前記出力制御回路は、前記無負荷状態において、少なくとも前記出力電圧の検出結果に応じて前記スイッチング素子に対するオンデューティを連続的に変化させることを特徴とする請求項1記載の放電灯点灯装置。

- 放電灯を含む負荷回路と、直流電源と、スイッチング素子を有し、このスイッチング素子を制御信号に従ってオン/オフすることにより、前記直流電源から直流電力を取り込んでその制御信号に応じた出力レベルの直流電力に変換し、この変換した直流電力を、LCフィルタを介して前記負荷回路に出力するDC−DC変換回路と、このDC−DC変換回路の出力の検出を行い、この検出結果を利用して前記制御信号を出力する出力制御回路とを備え、

この出力制御回路は、前記DC−DC変換回路の出力電圧の検出を行い、前記放電灯が消灯している無負荷状態において、前記出力電圧の検出結果が所定の第1電圧に達すると、前記スイッチング素子に対するオン/オフ制御を間欠的に行って、前記出力電圧の検出結果が前記第1電圧を超えないように調整し、前記出力電圧の検出結果が高いほど、前記スイッチング素子に対するスイッチング周波数を高くし、少なくとも、前記無負荷状態において、前記出力電圧の検出結果が前記第1電圧のレベルに達したときには、前記スイッチング素子に対する1回のスイッチング動作で、前記DC−DC変換回路から前記負荷回路に出力されるエネルギー量と同等のエネルギー量を前記無負荷状態時の回路損失で消費する時間が、前記LCフィルタの共振周期に比べ、十分小さくなるまでスイッチング周波数を高くする

ことを特徴とする放電灯点灯装置。 - 前記出力制御回路は、前記無負荷状態において、前記出力電圧の検出結果が前記第1電圧より低い第2電圧を超えると、少なくとも前記スイッチング素子に対するスイッチング周波数を高くすることを特徴とする請求項4記載の放電灯点灯装置。

- 前記出力制御回路は、前記無負荷状態において、少なくとも前記出力電圧の検出結果に応じて前記スイッチング素子に対するスイッチング周波数を連続的に変化させることを特徴とする請求項4記載の放電灯点灯装置。

- 前記出力制御回路は、前記無負荷状態において、前記出力電圧の検出結果が高いほど、前記スイッチング素子に対するオンデューティを小さくするとともに、前記スイッチング素子に対するスイッチング周波数を高くすることを特徴とする請求項1〜6のいずれかに記載の放電灯点灯装置。

- 前記出力制御回路は、前記無負荷状態において、前記出力電圧の検出結果が前記第1電圧より低い第2電圧を超えると、前記スイッチング素子に対するオンデューティを小さくし、前記出力電圧の検出結果が前記第1電圧より低い第3電圧を超えると、前記スイッチング素子に対するスイッチング周波数を高くすることを特徴とする請求項7記載の放電灯点灯装置。

- 前記第2電圧および第3電圧は同一レベルであることを特徴とする請求項8記載の放電灯点灯装置。

- 前記第2電圧は前記第3電圧よりも高レベルであることを特徴とする請求項8記載の放電灯点灯装置。

- 前記第3電圧は前記第2電圧よりも高レベルであることを特徴とする請求項8記載の放電灯点灯装置。

- 前記出力制御回路は、前記無負荷状態において、前記出力電圧の検出結果に応じて、前記スイッチング素子に対するスイッチング周波数およびオンデューティを連続的に変化させることを特徴とする請求項8記載の放電灯点灯装置。

- 前記DC−DC変換回路内の交番電圧箇所に入力が接続される多倍電圧整流回路をさらに備え、前記出力制御回路は、前記無負荷状態において、前記出力電圧の検出結果がほぼ前記第1電圧のレベルに達するまで、前記多倍電圧整流回路の出力が所定の第4電圧を超えないように、前記スイッチング素子に対してオン/オフ制御を行うことを特徴とする請求項1〜12のいずれかに記載の放電灯点灯装置。

- 前記出力制御回路は、前記出力電圧の検出結果が前記第2電圧に達するまで、所定値以下のスイッチング周波数で前記スイッチング素子に対してオン/オフ制御を行うことにより、前記多倍電圧整流回路の出力電圧の上昇を抑制し、前記出力電圧の検出結果が前記第2電圧を超えると、前記スイッチング素子に対するスイッチング周波数を増加することにより、前記多倍電圧整流回路の出力電圧の上昇を加速させることを特徴とする請求項13記載の放電灯点灯装置。

- 前記出力制御回路は、前記直流電源の電圧に対して前記スイッチング素子に対するオンデューティを変化させることを特徴とする請求項1〜14のいずれかに記載の放電灯点灯装置。

- 前記出力制御回路は、前記直流電源の電圧に対して前記スイッチング素子に対するオンデューティを反比例するように変化させることを特徴とする請求項15記載の放電灯点灯装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001005706A JP3888062B2 (ja) | 2001-01-12 | 2001-01-12 | 放電灯点灯装置 |

| DE10290425T DE10290425B4 (de) | 2001-01-12 | 2002-01-10 | Vorschaltgerät für eine Entladungslampe |

| CNB028000501A CN100456906C (zh) | 2001-01-12 | 2002-01-10 | 放电灯用的镇流器和用dc-dc转换器操作放电灯的方法 |

| PCT/JP2002/000095 WO2002056646A2 (en) | 2001-01-12 | 2002-01-10 | Ballast for a discharge lamp |

| US10/220,639 US6861812B2 (en) | 2001-01-12 | 2002-01-10 | Discharge lamp ballast with DC-DC converter |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001005706A JP3888062B2 (ja) | 2001-01-12 | 2001-01-12 | 放電灯点灯装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2002216988A JP2002216988A (ja) | 2002-08-02 |

| JP3888062B2 true JP3888062B2 (ja) | 2007-02-28 |

Family

ID=18873715

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001005706A Expired - Fee Related JP3888062B2 (ja) | 2001-01-12 | 2001-01-12 | 放電灯点灯装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3888062B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4697051B2 (ja) * | 2006-05-26 | 2011-06-08 | パナソニック電工株式会社 | 点灯装置、灯具、車両 |

| JP2023011144A (ja) * | 2021-07-12 | 2023-01-24 | ウシオ電機株式会社 | 光源装置、誘電体バリア放電ランプの点灯回路、誘電体バリア放電ランプの点灯方法 |

-

2001

- 2001-01-12 JP JP2001005706A patent/JP3888062B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002216988A (ja) | 2002-08-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3829534B2 (ja) | 放電灯点灯装置 | |

| JP3707409B2 (ja) | スイッチング電源装置 | |

| TWI489757B (zh) | 開關電力轉換器及其控制方法 | |

| JP4254884B2 (ja) | 力率改善回路 | |

| JP5920075B2 (ja) | スイッチング電源装置 | |

| CN1778149B (zh) | 放电灯照明控制装置 | |

| JP2008312359A (ja) | スイッチング電源装置、並びにレギュレーション回路 | |

| JP6702010B2 (ja) | スイッチング電源装置 | |

| JP3687528B2 (ja) | 電源装置及び放電灯点灯装置 | |

| US7012381B2 (en) | DC—DC converter and device for operation of a high pressure discharge lamp using the converter | |

| JP2004303689A (ja) | 高圧放電灯点灯装置 | |

| US7078868B2 (en) | DC—DC converter and device for operation of a high pressure discharge lamp using said converter | |

| JPH06113534A (ja) | 電源装置 | |

| US7078867B2 (en) | DC—DC converter and device for operation of a high pressure discharge lamp using said converter | |

| JP3888062B2 (ja) | 放電灯点灯装置 | |

| KR100639483B1 (ko) | 무전극 방전램프의 전원장치 | |

| JPH11332220A (ja) | 直流電源回路 | |

| JP4649729B2 (ja) | 電源装置及び放電灯点灯装置 | |

| JP4003418B2 (ja) | 放電灯点灯装置 | |

| JP4370844B2 (ja) | 直流変換装置 | |

| JP6810150B2 (ja) | スイッチング電源装置および半導体装置 | |

| JP3326955B2 (ja) | 放電灯点灯装置 | |

| JP4649728B2 (ja) | 電源装置及び放電灯点灯装置 | |

| JP4114047B2 (ja) | スイッチング電源回路 | |

| TWI839936B (zh) | 返馳式電源轉換器以及其控制方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040224 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060322 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060522 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20061107 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20061120 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 3888062 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091208 Year of fee payment: 3 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091208 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091208 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101208 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111208 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121208 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121208 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131208 Year of fee payment: 7 |

|

| LAPS | Cancellation because of no payment of annual fees |