CN212969479U - Heric inverter circuit and Heric inverter - Google Patents

Heric inverter circuit and Heric inverter Download PDFInfo

- Publication number

- CN212969479U CN212969479U CN202022187734.9U CN202022187734U CN212969479U CN 212969479 U CN212969479 U CN 212969479U CN 202022187734 U CN202022187734 U CN 202022187734U CN 212969479 U CN212969479 U CN 212969479U

- Authority

- CN

- China

- Prior art keywords

- heric

- inverter

- switching tube

- bridge arm

- topology

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Inverter Devices (AREA)

Abstract

The application provides a Heric inverter circuit and a Heric inverter. The Heric inverter circuit specifically includes: the circuit comprises a Heric topology, an input capacitor branch, an output filter branch and an auxiliary diode. In the inverter circuit, the auxiliary diode is provided between a midpoint of the free-wheeling arm in the herc topology and any one of poles on the direct current side of the herc topology, and the direction of the auxiliary diode is: the midpoint of the follow current bridge arm points to the positive electrode of the Heric topology direct current side, or the negative electrode of the Heric topology direct current side points to the midpoint of the follow current bridge arm, so that when peak voltage occurs in a corresponding switching tube in the follow current bridge arm, namely a follow current tube, the auxiliary diode can clamp the peak voltage, generation of the peak voltage is restrained, and the peak voltage on the follow current tube in the Heric topology is reduced.

Description

Technical Field

The utility model relates to a power electronic technology field especially relates to a heroic inverter circuit and heroic inverter.

Background

At present, a low-power single-phase inverter generally adopts a non-isolated photovoltaic grid-connected inverter with the advantages of high conversion efficiency, high power density, low cost and the like; moreover, the non-isolated photovoltaic grid-connected inverter generally adopts a logic topology with better performance in terms of device cost, conversion efficiency and leakage current.

In the Heric topology, the high-frequency tube and the follow current tube both work in a hard switching state, namely, a large voltage peak is generated on the high-frequency tube and the follow current tube, and the switching loss of the high-frequency tube and the follow current tube is high; especially when the Heric topology is operated in a non-unity power factor condition, the follow current tube therein is damaged by being subjected to an excessively high peak voltage stress.

Therefore, how to reduce the peak voltage of the freewheeling tube in the Heric topology is a problem to be solved.

SUMMERY OF THE UTILITY MODEL

In view of this, the utility model provides a Heric inverter circuit and Heric inverter to reduce the spike voltage on the continuous current tube in Heric topology.

In order to achieve the above object, the embodiment of the present invention provides the following technical solutions:

one aspect of the present application provides a Heric inverter circuit, including: the circuit comprises a Heric topology, an input capacitor branch, an output filter branch and an auxiliary diode; wherein:

the receiving side of the output filtering branch circuit is connected with the alternating current side of the Heric topology, and the output side of the output filtering branch circuit is used as the alternating current side of the Heric inverter circuit;

the input capacitor branch is connected between two poles of the direct current side of the Heric topology, and two ends of the input capacitor branch are used as the direct current side of the Heric inverter circuit;

the auxiliary diode is arranged between the midpoint of a freewheeling bridge arm in the Heric topology and any pole on the DC side of the Heric topology; and the direction of the auxiliary diode is: and pointing the midpoint of the follow current bridge arm to the positive pole of the Heric topology direct current side, or pointing the negative pole of the Heric topology direct current side to the midpoint of the follow current bridge arm.

Optionally, when the direction of the auxiliary diode is from the midpoint of the freewheeling bridge arm to the positive electrode of the Heric topology dc side, the cathodes of the anti-parallel diodes of the two switching tubes in the freewheeling bridge arm are connected.

Optionally, when the direction of the auxiliary diode is from the negative electrode of the current side of the Heric topology to the midpoint of the freewheeling bridge arm, the anodes of the anti-parallel diodes of the two switching tubes in the freewheeling bridge arm are connected.

Optionally, in the two inverter arms of the Heric topology, the switching tubes that are not connected to the auxiliary diode have conduction times that are respectively: and the turn-off time of a switching tube connected with the freewheeling bridge arm is set.

Optionally, in the two inverter arms of the Heric topology, the turn-off time of the switching tube not connected to the auxiliary diode is: and the on-off time of a switching tube connected with the freewheeling bridge arm is set.

Optionally, in the two inverter legs of the Heric topology, the driving signals of the switching tubes connected to the auxiliary diode are respectively connected to: dead time exists in the follow current bridge arm according to the driving signal of the switching tube which is not connected with the follow current bridge arm.

Optionally, the Heric topology includes: the first inverter bridge arm, the second inverter bridge arm and the follow current bridge arm;

the first inverter bridge arm and the second inverter bridge arm are connected in parallel, one end of the first inverter bridge arm and the second inverter bridge arm which are connected in parallel is used as a direct-current side anode of the Heric topology, and the other end of the first inverter bridge arm and the second inverter bridge arm which are connected in parallel is used as a direct-current side cathode of the Heric topology;

the follow current bridge arm is arranged between the midpoint of the first inverter bridge arm and the midpoint of the second inverter bridge arm;

and the midpoint of the first inverter bridge arm and the midpoint of the second inverter bridge arm are respectively used as two ends of the alternating current side of the Heric topology.

Optionally, the first inverter leg includes: the first switching tube and the fifth switching tube; the second inverter leg comprises: a second switching tube and a sixth switching tube; the follow current bridge arm comprises: a third switching tube and a fourth switching tube;

the drain electrode of the first switching tube is used as the first end of the first inverter bridge arm and is connected with the positive electrode of the direct current side of the Heric topology;

the source electrode of the first switching tube is connected with the drain electrode of the fifth switching tube, and the connection point is used as the midpoint of the first inverter bridge arm;

a source electrode of the fifth switching tube is used as a second end of the first inverter bridge arm and is connected with a direct current side negative electrode of the Heric topology;

the drain electrode of the second switching tube is used as the first end of the second inverter bridge arm and is connected with the positive electrode of the direct current side of the Heric topology;

the source electrode of the second switching tube is connected with the drain electrode of the sixth switching tube, and the connection point is used as the midpoint of the second inverter bridge arm;

a source electrode of the sixth switching tube is used as a second end of the second inverter bridge arm and is connected with a direct current side negative electrode of the Heric topology;

the emitter of the third switching tube is used as the first end of the follow current bridge arm and is connected with the midpoint of the first inverter bridge arm;

a collector electrode of the third switching tube is connected with a collector electrode of the fourth switching tube, and a connection point is used as a middle point of the follow current bridge arm;

and an emitter of the fourth switching tube is used as a second end of the follow current bridge arm and is connected with the midpoint of the second inverter bridge arm.

Optionally, the output filtering branch includes: the first output inductor branch circuit, the second output inductor branch circuit and the output capacitor branch circuit; wherein:

a first end of the first output inductance branch circuit is connected with a first end of the Heric topology alternating current side, and a second end group of the first output inductance branch circuit is used as a first end of the alternating current side of the output filtering branch circuit;

a first end of the second output inductance branch circuit is connected with a second end of the Heric topology alternating current side, and a second end of the second output inductance branch circuit is used as a second end of the output filtering branch circuit alternating current side;

the output capacitor branch is arranged between the second end of the first output inductor branch and the second end of the second output inductor branch.

Optionally, each switching tube of the Heric topology is a MOS transistor or an IGBT.

Another aspect of the present application provides a Heric inverter, including: the control circuit comprises a controller, a detection module, N driving circuits and a Heric inverter circuit according to any one of the previous aspects of the application; n is a positive integer; wherein:

the direct current side of the Heric inverter circuit is used as the direct current side of the Heric inverter and is connected with a direct current power supply, and the alternating current side of the Heric inverter circuit is used as the alternating current side of the Heric inverter and is connected with an alternating current power supply;

the output end of the controller is connected with the control end of the corresponding switch tube in the Heric inverter circuit through each drive circuit;

the input end of the controller is connected with the output end of the detection module, and each detection end of the detection module is respectively arranged on the direct current side and the alternating current side of the Heric inverter circuit.

Optionally, the method further includes: a DCDC conversion circuit; wherein:

the DCDC conversion circuit is connected between the direct current side of the Heric inverter and the direct current side of the Heric inverter circuit.

According to the above technical scheme, the utility model provides an inverter circuit, it specifically includes: the circuit comprises a Heric topology, an input capacitor branch, an output filter branch and an auxiliary diode. In the inverter circuit, the auxiliary diode is provided between a midpoint of the free-wheeling arm in the herc topology and any one of poles on the direct current side of the herc topology, and the direction of the auxiliary diode is: the midpoint of the follow current bridge arm points to the positive electrode of the Heric topology direct current side, or the negative electrode of the Heric topology direct current side points to the midpoint of the follow current bridge arm, so that when peak voltage occurs in a corresponding switching tube in the follow current bridge arm, namely a follow current tube, the auxiliary diode can clamp the peak voltage, generation of the peak voltage is restrained, and the peak voltage on the follow current tube in the Heric topology is reduced.

Drawings

In order to more clearly illustrate the embodiments of the present invention or the technical solutions in the prior art, the drawings required to be used in the description of the embodiments or the prior art will be briefly described below, it is obvious that the drawings in the following description are only embodiments of the present invention, and for those skilled in the art, other drawings can be obtained according to the provided drawings without creative efforts.

FIG. 1 is a schematic diagram of a prior art Heric inverter circuit;

FIG. 2 shows a load voltage v in a Heric inverter circuit in the prior artgAnd a load current igA schematic diagram of the waveform of (a);

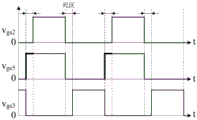

fig. 3 is a schematic diagram of driving signals of a first switching tube, a sixth switching tube and a fourth switching tube when a prior art Heric inverter circuit works in a positive half-cycle reactive current region;

FIG. 4 is a graph showing the results of a simulation test performed on the driving signals shown in FIG. 3;

fig. 5 is a schematic structural diagram of a Heric inverter circuit according to an embodiment of the present application;

FIG. 6 shows the load current igWhen the free-wheeling path is switched to the high-frequency path, the equivalent circuit of the Heric inverter circuit shown in fig. 5;

FIG. 7 shows the load current igWhen a follow current path is switched to a high frequency path, an equivalent circuit of a Heric inverter circuit in the prior art;

FIG. 8 is a schematic diagram of a soft switching circuit according to the prior art;

fig. 9 is a schematic structural diagram of an improved Heric single-phase inverter in the prior art;

FIG. 10 is a schematic diagram of a prior art improved single-phase non-isolated photovoltaic inverter;

fig. 11 is another schematic structural diagram of a Heric inverter circuit according to an embodiment of the present application;

FIG. 12 shows the load current igWhen the follow current path is switched to the high frequency path and another control mode is adopted, the equivalent circuit of the Heric inverter circuit shown in FIG. 5 is adopted;

fig. 13a is a schematic diagram of driving signals of the first switch tube, the sixth switch tube and the fourth switch tube when the Heric inverter circuit shown in fig. 5 operates in the positive half-cycle reactive current region;

FIG. 13b is a graph showing the results of a simulation test performed on the drive signal of FIG. 13 a;

fig. 14a is a schematic diagram of driving signals of the second switch tube, the fifth switch tube and the third switch tube when the Heric inverter circuit shown in fig. 5 operates in the negative half-cycle reactive current region;

FIG. 14b is a graph showing the results of a simulation test performed on the driving signals shown in FIG. 14 a;

fig. 15 is a schematic diagram of driving signals of the first switch tube, the sixth switch tube and the fourth switch tube when the Heric inverter circuit shown in fig. 11 operates in the positive half-cycle reactive current region;

fig. 16 is a schematic diagram of driving signals of the second switching tube, the fifth switching tube and the third switching tube when the Heric inverter circuit shown in fig. 11 operates in the negative half-cycle reactive current region;

fig. 17 is a schematic diagram of another driving signal of the first switch tube, the sixth switch tube and the fourth switch tube when the Heric inverter circuit shown in fig. 5 operates in the positive half-cycle reactive current region;

fig. 18 is a schematic diagram of another driving signal of the second switch tube, the fifth switch tube and the third switch tube when the Heric inverter circuit shown in fig. 5 operates in the negative half-cycle reactive current region;

fig. 19a is a schematic diagram of another driving signal of the first switch tube, the sixth switch tube and the fourth switch tube when the Heric inverter circuit shown in fig. 11 operates in the positive half-cycle reactive current region;

fig. 19b is a schematic diagram of another driving signal of the second switch tube, the fifth switch tube and the third switch tube when the Heric inverter circuit shown in fig. 11 operates in the negative half-cycle reactive current region;

FIGS. 20a and 20b are schematic diagrams of two further configurations of a Heric inverter topology, respectively;

fig. 21 is a schematic structural diagram of a Heric inverter according to an embodiment of the present application;

fig. 22 is another schematic structural diagram of a Heric inverter according to an embodiment of the present application.

Detailed Description

The technical solutions in the embodiments of the present application will be clearly and completely described below with reference to the drawings in the embodiments of the present application, and it is obvious that the described embodiments are only a part of the embodiments of the present application, and not all of the embodiments. All other embodiments, which can be derived by a person skilled in the art from the embodiments given herein without making any creative effort, shall fall within the protection scope of the present application.

In this application, relational terms such as first and second, and the like may be used solely to distinguish one entity or action from another entity or action without necessarily requiring or implying any actual such relationship or order between such entities or actions. Also, the terms "comprises," "comprising," or any other variation thereof, are intended to cover a non-exclusive inclusion, such that a process, method, article, or apparatus that comprises a list of elements does not include only those elements but may include other elements not expressly listed or inherent to such process, method, article, or apparatus. Without further limitation, an element defined by the phrase "comprising an … …" does not exclude the presence of other identical elements in a process, method, article, or apparatus that comprises the element.

In the prior art, the structure of a Heric inverter circuit can be seen in fig. 1, and specifically includes:heric topology 10, input capacitance CbusA first output inductor L1, a second output inductor L2 and an output capacitor Cg。

In the Heric inverter circuit, the DC side of the Heric topology 10 is used as the DC side of the Heric inverter circuit; the first end of the alternating current side of the Heric topology 10 is connected with the first end of the first output inductor L1, and the second end of the first output inductor L1 is used as the first end of the alternating current side of the Heric inverter circuit; the second terminal of the alternating current side of the Heric topology 10 is connected to the first terminal of the second output inductor L2, and the second terminal of the second output inductor L2 serves as the second terminal of the alternating current side of the Heric inverter circuit.

Input capacitance CbusAn output capacitor C connected between two poles at the DC side of Heric topology 10gIs connected between the second terminal of the first output inductor L1 and the second terminal of the second output inductor L2.

Specifically, the circuit structure of the Heric topology 10 is shown in fig. 1, and specifically includes: first inverter leg 11, second inverter leg 12, and freewheeling leg 13.

In the Heric topology 10, a first inverter arm 11 and a second inverter arm 12 are connected in parallel, one end of the parallel connection is used as a direct current side positive electrode of the Heric topology 10, and the other end of the parallel connection is used as a direct current side negative electrode of the Heric topology 10; the follow current bridge arm 13 is arranged between the midpoint of the first inverter bridge arm 11 and the midpoint of the second inverter bridge arm 12; the midpoint of first inverter leg 11 and the midpoint of second inverter leg 12 are respectively set as the two ac-side ends of Heric topology 10.

The first inverter leg 11 is composed of a first switching tube Q1 and a fifth switching tube Q5. Specifically, if the first switching tube Q1 and the fifth switching tube Q5 are MOS transistors with diodes, at this time, the drain of the first switching tube Q1 is used as the first end of the first inverter arm 11 and is connected to the positive electrode of the Heric topology 10 on the dc side; the source electrode of the first switching tube Q1 is connected with the drain electrode of the fifth switching tube Q5, and the connection point is used as the midpoint of the first inverter bridge arm 11; the source of the fifth switching tube Q5 is used as the second end of the first inverter leg 11, and is connected to the negative electrode of the Heric topology 10 on the dc side.

The second inverter bridge arm 12 is composed of a second switching tube Q2 and a sixth switching tube Q6, specifically, if the second switching tube Q2 and the sixth switching tube Q6 are MOS transistors with diodes, at this time, the drain of the second switching tube Q2 is used as the first end of the second inverter bridge arm 12 and is connected to the positive electrode of the Heric topology 10 on the direct current side; the source electrode of the second switching tube Q2 is connected with the drain electrode of the sixth switching tube Q6, and the connection point is used as the midpoint of the second inverter bridge arm 12; the source of the sixth switching tube Q6 is used as the second end of the second inverter leg 12, and is connected to the negative electrode of the Heric topology 10 on the dc side.

The freewheeling arm 13 is composed of a third switching tube Q3 and a fourth switching tube Q4. Specifically, if the third switching tube Q3 and the fourth switching tube Q4 are MOS transistors with diodes, the internal structure of the freewheel arm 13 is as shown in fig. 1: the emitter of the third switching tube Q3 is used as the first end of the freewheeling arm 13 and is connected to the midpoint of the first inverter arm 11; the collector of the third switching tube Q3 is connected with the collector of the fourth switching tube Q4, and the connection point is used as the midpoint of the freewheeling bridge arm 13; the emitter of fourth switching transistor Q4 serves as the second end of freewheeling leg 13 and is connected to the midpoint of second inverter leg 12.

In addition, each switch tube in the Heric topology 10 may also be an IGBT with an anti-parallel diode, or other controllable switch tubes with an anti-parallel diode, and even the implementation form of each switch tube may not be the same, and further, various hybrid combinations may be formed, for example, Q1, Q2, Q5, and Q6 are MOS transistors with diodes, and Q3 and Q4 are IGBTs with anti-parallel diodes (as shown in each structural schematic diagram); the specific selection of each switching tube depends on the application environment, and is within the protection scope of the present application.

In practical application, when the Heric inverter circuit operates under the non-unit-factor working condition, the load voltage v of the Heric inverter circuitgAnd a load current igAs shown in fig. 2, a reactive current region exists regardless of the positive half cycle or the negative half cycle; since the working principle of the Heric inverter circuit in the positive half-cycle reactive current region is similar to that of the Heric inverter circuit in the negative half-cycle reactive current region, and the Heric inverter circuit can be obtained by analogy, the following example only takes the Heric inverter circuit working in the positive half-cycle reactive current region as an example, and the voltages at two ends of the follow current tube in the Heric inverter circuit are carried outAnd (4) explanation.

When the Heric inverter circuit works in a positive half-cycle reactive current region, the second switching tube Q2 and the fifth switching tube Q5 are always turned off, and the third switching tube Q3 is always turned on; driving signal v of first switch tube Q1gs1And a driving signal v of the sixth switching tube Q6gs6And a driving signal v of a fourth switching tube Q4gs4As shown in fig. 3, the first switch transistor Q1 and the sixth switch transistor Q6 are operated synchronously and alternately conduct with the fourth switch transistor Q4.

In addition, as shown in fig. 3, in order to ensure that there is no shoot-through risk of the switching tubes in the above-mentioned Heric inverter circuit, dead zones are provided between the switching tubes that are alternately turned on.

When the fourth switching tube Q4 is turned off and the first switching tube Q1 and the sixth switching tube Q6 are turned on, the load current igFlows through the first switching tube Q1 and the sixth switching tube Q6, namely a high-frequency path; when the fourth switching tube Q4 is turned on and the first switching tube Q1 and the sixth switching tube Q6 are turned off, the load current igFlows through the third switch tube Q3 and the fourth switch tube Q4, i.e. a freewheeling path.

When the Heric inverter circuit is in the dead zone, the fourth switching tube Q4, the first switching tube Q1 and the sixth switching tube Q6 are all turned off; when the Heric inverter circuit is in a dead zone before the fourth switching tube Q4 is turned on, the load current i in the Heric inverter circuitgThe switching process from the high-frequency path to the free-wheeling path is performed; when the Heric inverter circuit is in a dead zone before the first switch tube Q1 and the sixth switch tube Q6 are conducted, the load current i in the Heric inverter circuitgIs in the process of switching from the freewheel path to the high frequency path.

When the driving signals of the first switch Q1, the sixth switch Q6 and the fourth switch Q4 shown in fig. 3 are used to perform a simulation test on the Heric inverter circuit in the positive half-cycle reactive current region, the simulation test result is shown in fig. 4: when the load current igDuring the process of switching from the freewheeling path to the high-frequency path, a voltage is generated across the first switch tube Q1 and the sixth switch tube Q6, as shown by v in fig. 4ds1And vds6The fourth switch tube Q4 is shown producing a voltage spike across it, the thirdNo voltage is generated across the switch tube Q3, as shown by v in FIG. 4ds3As shown.

Since the working principle of the Heric inverter circuit in the negative half-cycle reactive current region is similar to that in the positive half-cycle reactive current region, it can be known from the above description that when the Heric inverter circuit is in the reactive current region, a large spike voltage is generated on the follow current tube, which may endanger the working safety of the follow current tube.

In order to reduce the peak voltage on the freewheeling tube in the Heric topology 10 and ensure the working safety of the freewheeling tube in the Heric topology 10, the embodiment of the present application provides a Heric inverter circuit, an internal circuit structure of which is shown in fig. 5, and specifically includes: a Heric topology 10, an input capacitance branch 20, an output filtering branch 30 and an auxiliary diode Da.

It should be noted that the Heric topology 10 is the same as the Heric topology 10 shown in fig. 1, and details thereof are not repeated here, and reference can be made to the above description.

In the Heric inverter circuit, the receiving side of the output filtering branch circuit 30 is connected with the alternating current side of the Heric topology 10, and the output side of the output filtering branch circuit 30 is used as the alternating current side of the Heric inverter circuit; the input capacitance branch 20 is connected between two poles on the direct current side of the Heric topology 10; the auxiliary diode Da is arranged between the midpoint of the freewheeling arm 13 in the herc topology 10 and the positive electrode on the dc side of the herc topology 10, and the direction of the auxiliary diode Da is as follows: as shown in fig. 5, the dc side positive pole of the Heric topology 10 is pointed by the midpoint of the freewheel leg 13.

Since the working principles of the Heric inverter circuit in this embodiment are similar between the positive half-cycle reactive current region and the negative half-cycle reactive current region when the Heric inverter circuit is in the non-unity-factor working condition, the voltages at the two ends of the follow current tube in the Heric inverter circuit will be described below by taking the Heric inverter circuit in this embodiment as an example when the Heric inverter circuit works in the positive half-cycle reactive current region.

When the Heric inverter circuit provided in this embodiment is in the positive half-cycle reactive current region, the control of each switch tube therein is the same as the control of the corresponding switch tube in the Heric inverter circuit, and details are not repeated here, and reference may be made to the above description.

When the load current i in the Heric inverter circuit provided by this embodiment isgWhen the free-wheeling path is switched to the high-frequency path, the equivalent circuit of the Heric inverter circuit is as shown in fig. 6: load current igThe voltage is input to the direct current side anode of the Heric topology 10 from the third switching tube Q3 and the auxiliary diode Da, and is input to the direct current side cathode of the Heric topology 10 through the sixth switching tube Q6; the collector of the fourth switching tube Q4 is connected to the anode of the auxiliary diode Da, and the emitter is connected to the drain of the sixth switching tube Q6.

In the prior art, when the load current i in the Heric inverter circuitgWhen the free-wheeling path is switched to the high-frequency path, the equivalent circuit of the Heric inverter circuit is as shown in fig. 7: load current igThe direct current side positive electrode of the Heric topology 10 is led into the third switching tube Q3, and the direct current side negative electrode of the Heric topology 10 is led into the sixth switching tube Q6; the collector of the fourth switching tube Q4 is connected to the source of the first switching tube Q1 through the third switching tube Q3, and the emitter is connected to the drain of the sixth switching tube Q6.

In both cases, the emitter of the fourth switch transistor Q4 is connected to the drain of the sixth switch transistor Q6, and the load current igThe dc side negative pole of the Heric topology 10 is connected to the sixth switching transistor Q6, that is, the emitter potential of the fourth switching transistor Q4 is the same in both cases; however, in the present embodiment, the collector of the fourth switching transistor Q4 is connected to the dc side positive electrode of the Heric topology 10 through the auxiliary diode Da, that is, the potential at the collector of the fourth switching transistor Q4 is clamped; in the prior art, the collector of the fourth switching tube Q4 is connected to the positive electrode of the direct current side of the Heric topology 10 through the third switching tube Q3 and the first switching tube Q1, and then it is considered that the parasitic inductance in series with the collector is generated when the first switching tube Q1 and the third switching tube Q3 are turned on, so that the potential fluctuation at the collector of the fourth switching tube Q4 may be caused; therefore, the collector potentials of the fourth switching transistor Q4 are different, and when the emitter potentials of the fourth switching transistor Q4 are the same, the collector potential of the fourth switching transistor Q4 in this embodiment is clamped, i.e., the peak voltage generated across the fourth switching transistor Q4 in this embodiment is reduced, so that when the collector potentials of the fourth switching transistor Q4 are different, the peak voltage generated across the fourth switching transistor Q4 in this embodiment is reducedWhen the Heric inverter circuit provided by the embodiment is in the reactive current region of the positive half cycle, the spike voltage generated at the two ends of the fourth switching tube Q4 can be reduced.

Since the working principle of the Heric inverter circuit in the negative half-cycle reactive current region is similar to that in the positive half-cycle reactive current region in the present embodiment, the following conclusions can be obtained with reference to the above description: when the Heric inverter circuit provided by the embodiment is in the negative half-cycle reactive current region, the spike voltage generated across the third switching tube Q3 can be reduced.

In summary, in the Heric inverter circuit provided in this embodiment, the auxiliary diode Da is provided, so that when a peak voltage occurs in the third switching tube Q3 or the fourth switching tube Q4, i.e., the freewheeling tube, in the freewheeling arm 13, the peak voltage can be clamped, and thus the generation of the peak voltage can be suppressed, and thus the peak voltage on the freewheeling tube in the Heric topology 10 is reduced.

Specifically, taking an example that the inverter itself is in a positive half-cycle reactive current region, a voltage across the fourth switching tube Q4 in the Heric inverter circuit provided in the present embodiment and a voltage across the fourth switching tube Q4 in the Heric inverter circuit in the related art will be described.

When the load current i in the Heric inverter circuit provided by this embodiment isgWhen the free wheel path is switched to the high frequency path, considering that the third switching tube Q3 and the sixth switching tube Q6 can generate parasitic inductances in series with the third switching tube Q3 and the sixth switching tube Q6, as shown in fig. 6, the parasitic inductances are respectively a third parasitic inductance Ls3 and a sixth parasitic inductance Ls 6; voltages are present across the third parasitic inductance Ls3 and the sixth parasitic inductance Ls6, and are respectively expressed as: v. ofLs3And vLs6(ii) a In addition, since the first switching tube Q1 and the sixth switching tube Q6 have a forward recovery phenomenon, the voltage across the sixth switching tube Q6 is respectively expressed as: v. ofds1And vds6(ii) a Therefore, in the Heric inverter circuit of the present embodiment, the voltage v across the fourth switching tube Q4ds4Expressed as:

vds4=Vbus+vLs6+vds6

in the same way, whenWhen the Heric inverter circuit provided in this embodiment is in the negative half-cycle reactive current region, in the Heric inverter circuit of this embodiment, the voltage v across the third switching tube Q3ds3Expressed as:

vds3=Vbus+vLs5+vds5

when the load current i in the prior art Heric inverter circuitgWhen the freewheel path is switched to the high-frequency path, considering that the first switching tube Q1, the third switching tube Q3 and the sixth switching tube Q6 generate parasitic inductances in series with themselves, as shown in fig. 7, they are respectively: a first parasitic inductance Ls1, a third parasitic inductance Ls3 and a sixth parasitic inductance Ls 6; voltages are present across the first parasitic inductance Ls1, the third parasitic inductance Ls3, and the sixth parasitic inductance Ls6, and are respectively expressed as: v. ofLs1、vLs3And vLs6(ii) a In addition, since the first switching tube Q1 and the sixth switching tube Q6 have a forward recovery phenomenon, voltages are present across the first switching tube Q1 and the sixth switching tube Q6, which are respectively described as: v. ofds1And vds6(ii) a Therefore, the voltage v across the fourth switching tube Q4ds4Can be expressed as:

vds4=Vbus+vLs1+vds1+vLs3+vds6+vLs6

similarly, when the prior art Heric inverter circuit is in the negative half-cycle reactive current region, the prior art Heric inverter circuit provides the voltage v across the third switching tube Q3ds3Expressed as:

vds3=Vbus+vLs2+vds2+vLs4+vds5+vLs5

therefore, the voltage peak at the two ends of the freewheeling tube in the Heric inverter circuit, i.e., the third switching tube Q3 or the fourth switching tube Q4, provided in this embodiment is smaller than the voltage peak at the two ends of the freewheeling tube in the Heric inverter circuit in the prior art.

It should be noted that, in the prior art, there is a soft switching circuit, which can implement zero-voltage switching of a high-frequency switching tube in a Heric inverter circuit. Six auxiliary switching tubes, one diode and two inductors are added to the soft switching circuit to form the soft switching auxiliary circuit, and the connection relationship of the soft switching auxiliary circuit is shown in fig. 8. The soft switch auxiliary circuit is matched with a switch control time sequence, the auxiliary inductor is charged before the switching time of the high-frequency tube, the auxiliary inductor is used for discharging the parasitic capacitor of the high-frequency tube before the high-frequency tube is switched on, so that zero voltage switching-on is realized, and the auxiliary inductor is used for discharging the parasitic capacitor of the high-frequency tube before the high-frequency tube is switched off, so that zero voltage switching-off is realized; therefore, according to proper auxiliary switch tube time sequence control, zero voltage switching-on and zero voltage switching-off of 4 high-frequency tubes can be realized, and switching loss is reduced.

However, the circuit adds too many devices, so that the topological structure is more complex, the control complexity, the detection cost and the system reliability are reduced; meanwhile, the added auxiliary current also generates driving loss, switching loss and conduction loss, thereby having an influence on the effect of reducing the switching loss of the method.

In the prior art, there is also an improved Heric single-phase inverter, on the basis of Heric topology, a switching tube and two auxiliary inductors are added, and the connection relationship is shown in fig. 9. When the load current is switched from a high-frequency path to a continuous-current path, the added auxiliary inductance is far higher than the parasitic inductance in the original loop, so that the current change speed in the current conversion process can be greatly reduced, and the conducting current of the switched-on switching tube is almost zero at the initial moment of current conversion, namely the switching tube is switched on and off instantly, so that the switching loss of the switching tube is obviously reduced, or the conducting current of the diode which is forced to be switched on is also almost zero, so that the reverse recovery loss of the diode is obviously reduced.

However, the auxiliary inductor is directly connected in series with the switching tube, and the direction of the inductor current when the switching tube is turned off needs to be ensured, otherwise, the risk of damaging the switching tube is generated. This risk is almost unavoidable when the circuit is operated at non-unity power factor, and therefore there are severe limitations on the application of the circuit. In addition, the added switch tube is connected with the midpoint of the direct current bus, so that additional midpoint potential control is required.

In the prior art, there is also an improved single-phase non-isolated photovoltaic inverter, which has a structure as shown in fig. 10, and the freewheeling arm of the Heric topology is replaced, and a clamping diode is further added to limit the voltage spike of the freewheeling tube. In the photovoltaic inverter, 1 switching tube and 4 diodes are used for replacing two switching tubes which are connected in series in an opposite direction, and bidirectional conduction of a follow current path is achieved. When the follow current path continues current, only 1 switching tube needs to be switched on, and the bidirectional conduction of the follow current path can be realized. In addition, 2 diodes are added to provide a reactive current path and have a clamping effect on the voltage spike of the follow current tube.

However, this approach increases device cost. Meanwhile, as the number of devices in the loop is increased, the conduction loss of the system is increased.

In summary, the Heric inverter circuit provided by the application realizes effective suppression of peak voltages at two ends of the follow current tube only by adding one auxiliary diode, so that the Heric inverter circuit has a simple internal structure, low cost and low control complexity; in addition, the auxiliary diode only plays a clamping role when peak voltage is generated at two ends of the follow current tube, so that obvious loss is not introduced, and the loss of the Heric inverter circuit is not increased.

In practical application, the free-wheeling bridge arm 13 in the Heric topology 10 obviously has another embodiment, and its internal structure is shown in fig. 11, and specifically includes: a third switching tube Q3 and a fourth switching tube Q4.

In the freewheel arm 13, the third switching tube Q3 and the fourth switching tube Q4 are both IGBTs with diodes, and therefore, the collector of the third switching tube Q3 is connected to the midpoint of the first inverter arm 11 as the first end of the freewheel arm 13; the emitter of the third switching tube Q3 is connected with the emitter of the fourth switching tube Q4, and the connection point is used as the midpoint of the freewheeling bridge arm 13; the collector of the fourth switching tube Q4 is used as the second end of the freewheeling leg 13 and is connected to the midpoint of the second inverter leg 12.

When the free-wheeling bridge arm 13 in the herc topology 10 adopts the above embodiment, another embodiment of the present application provides another herc inverter circuit based on the above embodiment, and its internal structure is basically the same as that of the herc inverter circuit provided in the above embodiment except for the following differences.

As shown in fig. 11, the differences are: in the Heric inverter circuit in this embodiment, the auxiliary diode Da is disposed in the herc topology 10, and the midpoint of the freewheeling arm 13 is connected to the negative pole of the herc topology 10 on the dc side, and the direction of the auxiliary diode Da is as follows: the negative pole of the direct current side of Heric points to the midpoint of the freewheeling leg 13.

It should be noted that the working principle of the Heric inverter circuit provided in this embodiment is substantially the same as that of the Heric inverter circuit provided in the above embodiment, and the following is known through simple analogy derivation: in the Heric inverter circuit provided in this embodiment, through the arrangement of the auxiliary diode Da, when a peak voltage occurs in the third switching tube Q3 or the fourth switching tube Q4, that is, the freewheeling tube, in the freewheeling arm 13, the peak voltage can be clamped, so that the generation of the peak voltage is suppressed, and the peak voltage on the freewheeling tube in the Heric topology 10 is reduced, which is not described herein any more.

The two embodiments provide two implementation modes of the logic inverter circuit, but the control mode of each switching tube in the inverter circuit is not changed, and the embodiment of the application provides another implementation mode of the logic inverter circuit.

In this embodiment, the internal configuration of the inverter circuit may be the same as that of the inverter circuit shown in fig. 5, or may be the same as that of the inverter circuit shown in fig. 11, and is not particularly limited and may be selected as appropriate.

However, the difference between the logic inverter circuit in this embodiment and the logic inverter circuits in the two embodiments is specifically that: in the two inverter arms of the Heric topology 10, the switching tubes not connected to the auxiliary diode Da have the conduction times of: and the turn-off time of the switching tube connected with the freewheeling bridge arm 13.

Specifically, when the configuration of the Heric inverter circuit in the present embodiment is the same as that of the Heric inverter circuit shown in fig. 5, the control of each switching tube in the Heric inverter circuit is different from that in the prior art in that: when the Heric inverter circuit in this embodiment is in the non-unity-factor condition, if the Heric inverter circuit is in the positive half cycle, as shown in fig. 13a, in the Heric inverter circuit, after the fourth switching tube Q4 is turned off, the sixth switching tube Q6 may be immediately turned on, and there is no need to wait for the dead time; if the Heric inverter circuit is in the negative half cycle, as shown in fig. 14a, in the Heric inverter circuit, after the third switching tube Q3 is turned off, the fifth switching tube Q5 may be turned on immediately, and there is no need to wait for the dead time.

Next, the voltage across the fourth switching tube Q4 in the Heric inverter circuit will be described by taking as an example that the inverter circuit itself is in the positive half-cycle reactive current region.

When the load current i in the Heric inverter circuitgWhen the free-wheeling path is switched to the high-frequency path, the equivalent circuit of the Heric inverter circuit is as shown in fig. 12: load current igThe path of the positive voltage is the same as that of the positive inverter circuit shown in fig. 6, however, the sixth switching tube Q6 in the positive inverter circuit is turned on, so that the forward recovery phenomenon does not exist on the sixth switching tube Q6, and therefore, the voltage v across the fourth switching tube Q4 in the positive inverter circuitds4Can be expressed as:

vds4=Vbus+vLs6

it should be noted that the working principle of the Heric inverter circuit in the negative half-cycle reactive current region is similar to that in the positive half-cycle reactive current region, and therefore, the detailed description is omitted here, and the description is only given for reference.

When the driving signal v of the first switching tube Q1 shown in fig. 13a is usedgs1And a driving signal v of the sixth switching tube Q6gs6And a driving signal v of a fourth switching tube Q4gs4When the simulation test is performed on the Heric inverter circuit in the positive half-cycle reactive current region, the result of the simulation test is shown in fig. 13 b: when the load current igDuring the process of switching from the free-wheeling path to the high-frequency path, no voltage is still generated across the third switching tube Q3, as shown by v in fig. 13bds3As shown, no voltage is generated across the first Q1 and sixth Q6 switches, as shown by v in FIG. 13bds1And vds6As shown, the peak voltage generated across the fourth switch transistor Q4 is reduced compared to the above embodiment, as shown in fig. 13bMiddle vds4As shown in (a).

When the driving signal v of the second switch tube Q2 shown in fig. 14a is adoptedgs2And a driving signal v of the fifth switching tube Q5gs5And a driving signal v of the third switching tube Q3gs3When the Heric inverter circuit is subjected to a simulation test in the negative half-cycle reactive current region, the result of the simulation test is shown in fig. 14 b: when the load current igDuring the process of switching from the freewheeling path to the high-frequency path, no voltage is still generated across the fourth switching tube Q4, as shown by v in fig. 14bds4As shown, no voltage is generated across the second Q2 and fifth Q5 switches, as shown by v in FIG. 14bds2And vds5The spike voltage generated across the third switch transistor Q3 is further reduced compared to the previous embodiment, as shown by v in fig. 14bds3As shown.

Specifically, when the configuration of the Heric inverter circuit in the present embodiment is the same as that of the Heric inverter circuit shown in fig. 11, the control method of each switching tube in the Heric inverter circuit differs from the prior art in that: if the Heric inverter circuit is in the positive half cycle, as shown in fig. 15, in the Heric inverter circuit, after the fourth switching tube Q4 is turned off, the first switching tube Q1 may be immediately turned on, and there is no need to wait for a dead time; if the Heric inverter circuit is in the negative half cycle, as shown in fig. 16, in the Heric inverter circuit, after the third switching tube Q3 is turned off, the fifth switching tube Q5 may be turned on immediately, and there is no need to wait for the dead time.

It should be noted that, compared to the freewheeling tube in the Heric inverter circuit shown in fig. 11, the freewheeling tube in the Heric inverter circuit, i.e., the third switching tube Q3 or the fourth switching tube Q4, the voltage conversion between the two ends thereof is the same as that in the previous embodiment, and is not repeated here, and reference may be made to the above description.

It should be further noted that, obviously, the driving signal v of the first switch tube Q1 shown in fig. 15 is adoptedgs1And a driving signal v of the sixth switching tube Q6gs6And a driving signal v of a fourth switching tube Q4gs4Simulating the positive half-cycle reactive current region of the Heric inverter circuitThe results of the true test are the same as in the previous embodiment in this example; the driving signal v of the second switching tube Q2 shown in FIG. 16 is adoptedgs2And a driving signal v of the fifth switching tube Q5gs5And a driving signal v of the third switching tube Q3gs3The result of the simulation test performed on the Heric inverter circuit in the negative half-cycle reactive current region is the same as that of the previous embodiment in this embodiment, and details thereof are omitted.

On the basis of the previous embodiment, another embodiment of the present application provides another implementation manner of the logic inverter circuit, wherein the difference between the logic inverter circuit in the present embodiment and the logic inverter circuit in the previous embodiment is as follows: in two inverter arms of the Heric topology 10, the turn-off time of the switching tube which is not connected with the auxiliary diode Da is respectively as follows: and the conduction time of the switching tube connected with the freewheeling bridge arm 13 is set.

Specifically, when the configuration of the Heric inverter circuit in the present embodiment is the same as that of the Heric inverter circuit shown in fig. 5, the control manner of each switching tube in the Heric inverter circuit is different from that of the corresponding embodiment in the previous embodiment in that: when the Heric inverter circuit in this embodiment is in the non-unity-factor condition, if the Heric inverter circuit is in the positive half cycle, as shown in fig. 17, in the Heric inverter circuit, before the fourth switching tube Q4 is turned on, the sixth switching tube Q6 may be turned on all the time; if the Heric inverter circuit is in the negative half cycle, as shown in fig. 18, in the Heric inverter circuit, the fifth switching tube Q5 may be always turned on before the third switching tube Q3 is turned on.

It should be noted that, compared to the freewheeling tube in the Heric inverter circuit shown in fig. 5, the freewheeling tube in the Heric inverter circuit, i.e., the third switching tube Q3 or the fourth switching tube Q4, the voltage conversion between the two ends thereof is the same as that in the previous embodiment, and therefore, it is not repeated here and can be referred to the above description.

It should be further noted that, obviously, the driving signal v of the first switch tube Q1 shown in fig. 17 is adoptedgs1And a driving signal v of the sixth switching tube Q6gs6And a driving signal v of a fourth switching tube Q4gs4The result of the simulation test of the Heric inverter circuit in the reactive current region of the positive half cycle is the same as that of the corresponding embodiment in the previous embodiment; the driving signal v of the second switching tube Q2 shown in FIG. 18 is adoptedgs2And a driving signal v of the fifth switching tube Q5gs5And a driving signal v of the third switching tube Q3gs3The result of the simulation test performed on the Heric inverter circuit in the negative half-cycle reactive current region is the same as that of the corresponding embodiment in the previous embodiment, and details are not repeated here.

Specifically, when the configuration of the Heric inverter circuit in the present embodiment is the same as that of the Heric inverter circuit shown in fig. 11, the control manner of each switching tube in the Heric inverter circuit is different from that of the corresponding embodiment in the previous embodiment in that: if the Heric inverter circuit is in the positive half cycle, as shown in fig. 19a, in the Heric inverter circuit, the first switch Q1 may be always turned on before the fourth switch Q4 is turned on; if the Heric inverter circuit is in the negative half cycle, as shown in fig. 19b, in the Heric inverter circuit, the fifth switching tube Q5 may be turned on until the third switching tube Q3 is turned on, and there is no need to wait for the dead time.

It should be noted that, compared to the freewheeling tube in the Heric inverter circuit shown in fig. 11, the freewheeling tube in the Heric inverter circuit, i.e., the third switching tube Q3 or the fourth switching tube Q4, the voltage conversion between the two ends thereof is the same as that in the previous embodiment, and therefore, it is not repeated here and can be referred to the above description.

It should be noted that, obviously, the driving signal v of the first switch tube Q1 shown in fig. 19a is adoptedgs1And a driving signal v of the sixth switching tube Q6gs6And a driving signal v of a fourth switching tube Q4gs6The result of the simulation test of the Heric inverter circuit in the reactive current region of the positive half cycle is the same as that of the corresponding embodiment in the previous embodiment; the driving signal v of the second switch tube Q2 shown in FIG. 19b is adoptedgs2And a driving signal v of the fifth switching tube Q5gs5And a driving signal v of the third switching tube Q3gs3For the Heric inverter circuit, the reactive current region in the negative half periodThe results of the intra-domain simulation test are the same as those of the previous embodiment, and are not described in detail here.

It is worth to be noted that, in the herc inverter circuits provided in the two embodiments, the improvement is performed on the herc inverter circuit on the premise that the control mode of the herc inverter circuit in the prior art is not affected, so that the peak voltage generated at two ends of the freewheeling tube in the herc inverter circuit in the application, namely the third switching tube Q3 or the fourth switching tube Q4, is reduced, and the freewheeling tube in the herc inverter circuit is prevented from being damaged.

The embodiment of the present application provides a specific implementation for the output filter circuit in the above embodiment, and the internal structure thereof may specifically include, with reference to fig. 20a or fig. 20 b: a first output inductive branch 31, a second output inductive branch 32 and an output capacitive branch 33.

In the output filter branch 30, a first end of a first output inductance branch 31 is connected to a first end on the alternating current side of the Heric topology 10, and a second end of the first output inductance branch 31 serves as a first end on the alternating current side of the output filter branch 30; a first end of the second output inductance branch 32 is connected to a second end of the alternating current side of the Heric topology 10, and a second end group of the second output inductance branch 32 is used as a second end of the alternating current side of the output filtering branch 30; the output capacitor branch 33 is disposed between the second end of the first output inductor branch 31 and the second end of the second output inductor branch 32.

Specifically, the first output inductor branch 31 and the second output inductor branch 32 each include at least one output inductor, and when the number of the output inductors is greater than 1, all the output inductors may be connected in series to form a corresponding output inductor branch; in practical applications, including but not limited to the above connection mode, the connection mode may be determined according to specific situations, and is not limited herein, and is within the protection scope of the present application.

Preferably, as shown in fig. 20a or fig. 20b, the first output inductance branch 31 includes only the first output inductance L1, wherein two ends of the first output inductance L1 are the first end and the second end of the first output inductance branch 31, respectively; the second output inductor branch 32 only includes a second output inductor L2, wherein two ends of the second output inductor L2 are the first end and the second end of the second output inductor branch 32, respectively.

Specifically, the input capacitor branch 20 and the output capacitor branch 33 both include at least one capacitor, and when the number of the capacitors is greater than 1, all the capacitors can be connected in series to form a corresponding capacitor branch; in practical applications, including but not limited to the above connection, the connection is not limited to any specific situation, and is within the scope of the present application.

Preferably, as shown in fig. 20a or 20b, the input capacitive branch 20 comprises only the input capacitance CbusWherein the input capacitance CbusAre the two ends of the input capacitance branch 20, respectively; the output capacitance branch 33 comprises an output capacitance CgWherein an output capacitor CgAre the two ends of the output capacitive branch 33, respectively.

Another embodiment of the present application provides a Heric inverter, an internal structure of which is shown in fig. 21, and specifically includes: the driving circuit comprises a controller 100, a detection module 200, N driving circuits 300 and a Heric inverter circuit 400 provided by the above embodiment.

Wherein, N is a positive integer, and the value thereof may be determined according to specific conditions, and is not specifically limited herein, and is within the scope of the present application.

In the inverter, the dc side of the inverter circuit 400 is connected to a dc power supply as the dc side of the inverter; the alternating current side of the logic inverter circuit 400 is used as the alternating current side of the logic inverter and is connected with an alternating current power supply; the output end of the controller 100 is connected to the control end of the corresponding switching tube in the Heric inverter circuit 400 through each driving circuit 300; the input end of the controller 100 is connected to the output end of the detection module 200, and each detection end of the detection module 200 is respectively disposed on the dc side and the ac side of the inverter circuit.

As shown in fig. 22, the Heric inverter further includes, in addition to the above embodiment: a DCDC conversion circuit 500; the DCDC conversion circuit 500 is connected between the dc side of the logic inverter and the dc side of the logic inverter circuit 400.

It should be noted that, by using the Heric inverter circuit 400 provided in the foregoing embodiment, the Heric inverter can reduce the peak voltage generated at two ends of the self freewheeling tube, thereby ensuring the operation safety of the self internal freewheeling tube, and thus ensuring the operation safety of the self inverter.

The embodiments of the present invention are described in a progressive manner, each embodiment is mainly described as different from the other embodiments, and the same similar parts between the embodiments are referred to each other. The device disclosed by the embodiment corresponds to the method disclosed by the embodiment, so that the description is simple, and the relevant points can be referred to the method part for description.

The above description is only for the preferred embodiment of the present invention, and is not intended to limit the present invention in any way. Although the present invention has been described with reference to the preferred embodiments, it is not intended to limit the present invention. The invention is not limited to the embodiments described herein, but is capable of other embodiments according to the invention, and may be used in various other applications, including, but not limited to, industrial. Therefore, any simple modification, equivalent change and modification made to the above embodiments by the technical entity of the present invention all still fall within the protection scope of the technical solution of the present invention, where the technical entity does not depart from the content of the technical solution of the present invention.

Claims (12)

1. A Heric inverter circuit, comprising: the circuit comprises a Heric topology, an input capacitor branch, an output filter branch and an auxiliary diode; wherein:

the receiving side of the output filtering branch circuit is connected with the alternating current side of the Heric topology, and the output side of the output filtering branch circuit is used as the alternating current side of the Heric inverter circuit;

the input capacitor branch is connected between two poles of the direct current side of the Heric topology, and two ends of the input capacitor branch are used as the direct current side of the Heric inverter circuit;

the auxiliary diode is arranged between the midpoint of a freewheeling bridge arm in the Heric topology and any pole on the DC side of the Heric topology; and the direction of the auxiliary diode is: and pointing the midpoint of the follow current bridge arm to the positive pole of the Heric topology direct current side, or pointing the negative pole of the Heric topology direct current side to the midpoint of the follow current bridge arm.

2. A Heric inverter circuit as claimed in claim 1, characterized in that when the direction of the auxiliary diode is from the midpoint of the freewheel leg to the positive pole of the DC side of the Heric topology, the cathodes of the anti-parallel diodes of the two switching tubes in the freewheel leg are connected.

3. A Heric inverter circuit as claimed in claim 1, characterized in that when the direction of the auxiliary diode is from the negative pole of the DC side of the Heric topology to the midpoint of the freewheel leg, the anodes of the anti-parallel diodes of the two switching tubes in the freewheel leg are connected.

4. A Heric inverter circuit as claimed in any one of claims 1-3, wherein the switching tubes of the two inverter legs of the Heric topology, which are not connected to the auxiliary diode, are turned on at the following times: and the turn-off time of a switching tube connected with the freewheeling bridge arm is set.

5. A Heric inverter circuit as claimed in claim 4, wherein in the two inverter legs of the Heric topology, the switching tubes which are not connected to the auxiliary diodes have the following turn-off times: and the on-off time of a switching tube connected with the freewheeling bridge arm is set.

6. A Heric inverter circuit as claimed in any one of claims 1-3, wherein in the two inverter legs of the Heric topology, the driving signals of the switching tubes connected to the auxiliary diodes are respectively connected to: dead time exists in the follow current bridge arm according to the driving signal of the switching tube which is not connected with the follow current bridge arm.

7. A Heric inverter circuit as claimed in any one of claims 1-3, wherein the Heric topology includes: the first inverter bridge arm, the second inverter bridge arm and the follow current bridge arm;

the first inverter bridge arm and the second inverter bridge arm are connected in parallel, one end of the first inverter bridge arm and the second inverter bridge arm which are connected in parallel is used as a direct-current side anode of the Heric topology, and the other end of the first inverter bridge arm and the second inverter bridge arm which are connected in parallel is used as a direct-current side cathode of the Heric topology;

the follow current bridge arm is arranged between the midpoint of the first inverter bridge arm and the midpoint of the second inverter bridge arm;

and the midpoint of the first inverter bridge arm and the midpoint of the second inverter bridge arm are respectively used as two ends of the alternating current side of the Heric topology.

8. A Heric inverter circuit as claimed in claim 7, wherein the first inverter leg comprises: the first switching tube and the fifth switching tube; the second inverter leg comprises: a second switching tube and a sixth switching tube; the follow current bridge arm comprises: a third switching tube and a fourth switching tube;

the drain electrode of the first switching tube is used as the first end of the first inverter bridge arm and is connected with the positive electrode of the direct current side of the Heric topology;

the source electrode of the first switching tube is connected with the drain electrode of the fifth switching tube, and the connection point is used as the midpoint of the first inverter bridge arm;

a source electrode of the fifth switching tube is used as a second end of the first inverter bridge arm and is connected with a direct current side negative electrode of the Heric topology;

the drain electrode of the second switching tube is used as the first end of the second inverter bridge arm and is connected with the positive electrode of the direct current side of the Heric topology;

the source electrode of the second switching tube is connected with the drain electrode of the sixth switching tube, and the connection point is used as the midpoint of the second inverter bridge arm;

a source electrode of the sixth switching tube is used as a second end of the second inverter bridge arm and is connected with a direct current side negative electrode of the Heric topology;

the emitter of the third switching tube is used as the first end of the follow current bridge arm and is connected with the midpoint of the first inverter bridge arm;

a collector electrode of the third switching tube is connected with a collector electrode of the fourth switching tube, and a connection point is used as a middle point of the follow current bridge arm;

and an emitter of the fourth switching tube is used as a second end of the follow current bridge arm and is connected with the midpoint of the second inverter bridge arm.

9. A Heric inverter circuit as claimed in any one of claims 1-3, wherein the output filter branch comprises: the first output inductor branch circuit, the second output inductor branch circuit and the output capacitor branch circuit; wherein:

a first end of the first output inductance branch circuit is connected with a first end of the Heric topology alternating current side, and a second end group of the first output inductance branch circuit is used as a first end of the alternating current side of the output filtering branch circuit;

a first end of the second output inductance branch circuit is connected with a second end of the Heric topology alternating current side, and a second end of the second output inductance branch circuit is used as a second end of the output filtering branch circuit alternating current side;

the output capacitor branch is arranged between the second end of the first output inductor branch and the second end of the second output inductor branch.

10. A Heric inverter circuit as claimed in any one of claims 1-3, wherein each switching transistor of the Heric topology is a MOS transistor or an IGBT respectively.

11. An inverter for Heric, comprising: a controller, a detection module, N drive circuits and the Heric inverter circuit of any one of claims 1-10; n is a positive integer; wherein:

the direct current side of the Heric inverter circuit is used as the direct current side of the Heric inverter and is connected with a direct current power supply, and the alternating current side of the Heric inverter circuit is used as the alternating current side of the Heric inverter and is connected with an alternating current power supply;

the output end of the controller is connected with the control end of the corresponding switch tube in the Heric inverter circuit through each drive circuit;

the input end of the controller is connected with the output end of the detection module, and each detection end of the detection module is respectively arranged on the direct current side and the alternating current side of the Heric inverter circuit.

12. A Heric inverter as claimed in claim 11, further comprising: a DCDC conversion circuit; wherein:

the DCDC conversion circuit is connected between the direct current side of the Heric inverter and the direct current side of the Heric inverter circuit.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202022187734.9U CN212969479U (en) | 2020-09-29 | 2020-09-29 | Heric inverter circuit and Heric inverter |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202022187734.9U CN212969479U (en) | 2020-09-29 | 2020-09-29 | Heric inverter circuit and Heric inverter |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN212969479U true CN212969479U (en) | 2021-04-13 |

Family

ID=75371291

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN202022187734.9U Active CN212969479U (en) | 2020-09-29 | 2020-09-29 | Heric inverter circuit and Heric inverter |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN212969479U (en) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN113595428A (en) * | 2021-09-30 | 2021-11-02 | 浙江日风电气股份有限公司 | Single-phase three-level inverter circuit |

| CN114825894A (en) * | 2022-06-22 | 2022-07-29 | 锦浪科技股份有限公司 | Wave-by-wave current limiting control method and device for Heric inverter circuit and inverter |

| CN114884329A (en) * | 2021-11-26 | 2022-08-09 | 深圳市首航新能源股份有限公司 | Grid-connected inverter and voltage spike suppression method |

| CN115296556A (en) * | 2022-07-15 | 2022-11-04 | 华为数字能源技术有限公司 | Inverter and control method thereof |

| CN116565980A (en) * | 2023-07-11 | 2023-08-08 | 麦田能源股份有限公司 | Inverter system with reactive support and control method thereof |

-

2020

- 2020-09-29 CN CN202022187734.9U patent/CN212969479U/en active Active

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN113595428A (en) * | 2021-09-30 | 2021-11-02 | 浙江日风电气股份有限公司 | Single-phase three-level inverter circuit |

| CN114884329A (en) * | 2021-11-26 | 2022-08-09 | 深圳市首航新能源股份有限公司 | Grid-connected inverter and voltage spike suppression method |

| CN114884329B (en) * | 2021-11-26 | 2023-02-28 | 深圳市首航新能源股份有限公司 | Grid-connected inverter and voltage spike suppression method |

| CN114825894A (en) * | 2022-06-22 | 2022-07-29 | 锦浪科技股份有限公司 | Wave-by-wave current limiting control method and device for Heric inverter circuit and inverter |

| CN115296556A (en) * | 2022-07-15 | 2022-11-04 | 华为数字能源技术有限公司 | Inverter and control method thereof |

| CN116565980A (en) * | 2023-07-11 | 2023-08-08 | 麦田能源股份有限公司 | Inverter system with reactive support and control method thereof |

| CN116565980B (en) * | 2023-07-11 | 2023-09-19 | 麦田能源股份有限公司 | Inverter system with reactive support and control method thereof |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN212969479U (en) | Heric inverter circuit and Heric inverter | |

| CN101860192B (en) | Three-state three-level PFC circuit and multi-state three-level PFC circuit | |

| CN103001523B (en) | Zero-voltage switching energy storage bridge-type inverter without additional voltage and modulation method for inverter | |

| CN112910244B (en) | Single-phase three-level power factor correction circuit of hybrid bridge arm | |

| CN113422535B (en) | Inverter topology circuit and inverter | |

| CN103916040B (en) | Inverter topological circuit, inverting method and inverter | |

| CN110545048B (en) | Zero-voltage switch and common-mode voltage suppression method for current source type motor driving system | |

| CN212518834U (en) | Neutral point active clamping three-level inverter | |

| CN102983767B (en) | Low auxiliary voltage zero voltage switch Stockbridge vibration inverter and modulator approach | |

| CN108964505B (en) | T-shaped conversion circuit and corresponding three-phase conversion circuit and conversion device | |

| CN212572416U (en) | I-type three-level converter and uninterruptible power supply module | |

| CN105471296A (en) | Inverter circuit | |

| Kumar et al. | Bi-directional clamping based H5, HERIC and H6-type transformerless inverter topologies with improved modulation technique | |

| CN103001522A (en) | Passive lossless soft-switching dual-buck double-bridge inverter | |

| CN113437882B (en) | Three-level rectifier based on parallel multi-diode serial bidirectional switch | |

| CN115765507A (en) | Three-level double-step-down conversion circuit for energy storage and inversion integrated device rear stage | |

| CN112701905B (en) | Single-phase three-level power factor correction circuit based on pseudo totem-pole structure | |

| CN109873570A (en) | Three level T font topological structures of one kind and single-phase inverter and three-phase inverter | |

| CN113437884B (en) | Three-level rectifier based on parallel diode clamp bidirectional switch | |

| CN112865562B (en) | Single-phase three-switch tube pseudo-totem-pole type three-level rectifier | |

| CN110932588B (en) | Improved HERIC photovoltaic inverter and modulation method thereof | |

| CN109861573B (en) | Low switching loss power inverter | |

| CN209709969U (en) | Three level T font topological structures of one kind and single-phase inverter and three-phase inverter | |

| CN113839574A (en) | Three-level circuit for charging handheld electric crank | |

| CN111600490A (en) | DAB auxiliary loop and control time sequence applied to power electronic transformer |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| GR01 | Patent grant | ||

| GR01 | Patent grant |