发明内容

本发明实施例提供了一种基于同轴线缆的阻抗测试方法、装置、设备及存储介质,能够有效解决现有技术仅通过TDR测试法或Smith图测试法对同轴线缆进行测试,没有建立仿真模型进行仿真测试的弊端,从而使得最终得到的测试结果更加准确。

所述方法包括:

获取目标同轴线缆的各电路的实测阻抗特性曲线;

获取目标同轴线缆的等效电路模型并根据所述等效电路模型建立二端口阻抗仿真模型;

根据二端口阻抗仿真模型得到目标同轴线缆的各电路的仿真阻抗特性曲线;

将目标同轴线缆的各电路的实测阻抗特性曲线和目标同轴线缆的各电路的仿真阻抗特性曲线进行对比分析,并根据对比结果得到目标线缆的阻抗特性测试曲线。

进一步地,所述目标同轴线缆的各电路的实测阻抗特性曲线通过测试分析仪对目标线缆的各电路的测试端口进行扫频测试得到。

进一步地,所述目标同轴线缆的各电路的实测阻抗特性曲线包括:芯线层电路的实测阻抗特性曲线、芯线层-屏蔽层电路的实测阻抗特性曲线、屏蔽层电路的实测阻抗特性曲线和屏蔽层-屏蔽层电路的实测阻抗特性曲线。

进一步地,所述获取目标同轴线缆等效电路模型具体包括:

获取目标同轴线缆的供电波长λ;

根据所述供电波长λ得到目标同轴线缆的仿真长度l;

根据目标同轴线缆的仿真长度l生成目标同轴线缆的等效模型;

获取目标同轴线缆的实测长度L,并计算线缆实测长度L与仿真长度l的比值t;

对等效模型按t倍进行阵列处理得到目标同轴线缆的等效电路模型。

进一步地,所述目标同轴线缆的仿真长度l的计算公式为:l=1/10λ。

进一步地,所述根据二端口阻抗仿真模型得到目标同轴线缆的各电路的仿真阻抗特性曲线具体包括:

响应正弦电压源对二端口阻抗仿真模型的各端口的激励;

获取二端口阻抗仿真模型的各端口的求解器的求解结果;

根据所述求解结果得到目标同轴线缆的各电路的仿真阻抗特性曲线。

进一步地,所述目标同轴线缆的各电路的仿真阻抗特性曲线包括芯线层电路的仿真阻抗特性曲线、芯线层-屏蔽层电路的仿真阻抗特性曲线、屏蔽层电路的仿真阻抗特性曲线和屏蔽层-屏蔽层电路的仿真阻抗特性曲线。

在上述方法项实施例的基础上,本发明对应提供了装置项实施例;

本发明一实施例提供了一种基于同轴线缆的阻抗测试装置,包括:实测阻抗特性曲线获取模块、二端口阻抗仿真模型建立模块、仿真阻抗特性曲线获取模块和对比分析模块;

所述实测阻抗特性曲线获取模块,用于获取目标同轴线缆的各电路的实测阻抗特性曲线;

所述二端口阻抗仿真模型建立模块,用于获取目标同轴线缆的等效电路模型并根据所述等效电路模型建立二端口阻抗仿真模型;

所述仿真阻抗特性曲线获取模块,用于根据二端口阻抗仿真模型得到目标同轴线缆的各电路的仿真阻抗特性曲线;

所述对比分析模块,用于将目标同轴线缆的各电路的实测阻抗特性曲线和目标同轴线缆的各电路的仿真阻抗特性曲线进行对比分析,并根据对比结果得到目标线缆的阻抗特性测试曲线。

在上述方法项实施例的基础上,本发明对应提供了一设备项实施例;

本发明一实施例提供了一种设备,包括处理器、存储器以及存储在所述存储器中且被配置为由所述处理器执行的计算机程序,所述处理器执行所述计算机程序时,实现所述的一种基于同轴线缆的阻抗测试方法。

在上述方法项实施例的基础上,本发明对应提供了一存储介质项实施例;

发明一实施例提供了一种存储介质,所述存储介质包括存储的计算机程序,其中,在所述计算机程序运行时,控制所述存储介质所在的设备执行所述的一种基于同轴线缆的阻抗测试方法。

通过实施本发明具有如下有益效果:

本发明实施例提供了一种基于同轴线缆的阻抗测试方法、装置、设备及存储介质,所述基于同轴线缆的阻抗测试方法,通过测试分析仪对目标线缆的各电路的测试端口进行扫频测试生成目标线缆的各电路的阻抗特性曲线,并通过等效电路模型建立二端口阻抗仿真模型以得到各电路的仿真阻抗特性曲线;将各电路的阻抗特性曲线和各电路的仿真阻抗特性曲线进行对比分析,即本发明采用实验测试与仿真模拟的方法将两个结果互相对比,使最终得到的同轴线缆的阻抗特性曲线更加准确。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

如图1所示,本发明一实施例提供了一种基于同轴线缆的阻抗测试方法,包括:

步骤S1:获取目标同轴线缆的各电路的实测阻抗特性曲线;

步骤S2:获取目标同轴线缆的等效电路模型并根据所述等效电路模型建立二端口阻抗仿真模型;

步骤S3:根据二端口阻抗仿真模型得到目标同轴线缆的各电路的仿真阻抗特性曲线;

步骤S4:将目标同轴线缆的各电路的实测阻抗特性曲线和目标同轴线缆的各电路的仿真阻抗特性曲线进行对比分析,并根据对比结果得到目标线缆的阻抗特性测试曲线。

对于步骤S1,在一个优选的实施例中,所述目标同轴线缆的各电路的实测阻抗特性曲线通过测试分析仪对目标线缆的各电路的测试端口进行扫频测试得到,其中,所述测试分析仪对目标线缆的各电路的测试端口进行扫频测试的步骤如下:

对阻抗分析仪进行自动校准;

进入阻抗测试界面,设置扫频范围为1kHz—108MHz,扫描频点1600个(点数已最大);

使用夹具的探测端(端口不分正负)夹持目标线缆的各电路的端口,夹持位置如下表所示:

启动阻抗分析仪进行自动扫描,得到目标同轴线缆的各电路的实测阻抗特性曲线;其中,所述目标同轴线缆的各电路的实测阻抗特性曲线包括:芯线层电路的实测阻抗特性曲线、芯线层-屏蔽层电路的实测阻抗特性曲线、屏蔽层电路的实测阻抗特性曲线和屏蔽层-屏蔽层电路的实测阻抗特性曲线。

本发明一实施例通过使用测试分析仪对目标同轴线缆的各电路进行扫频测试,可获取1kHz—108MHz频段内的阻抗分布,使得实测结果更加准确。

对于步骤S2,在一个优选的实施例中,获取目标同轴线缆的等效电路模型并根据所述等效电路模型建立二端口阻抗仿真模型,具体包括:

获取目标同轴线缆的供电波长λ;

根据所述供电波长λ得到目标同轴线缆的仿真长度l;所述目标同轴线缆的仿真长度l的计算公式为:l=1/10λ;

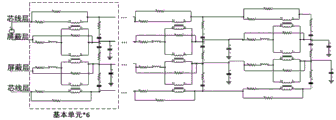

根据目标同轴线缆的仿真长度l生成目标同轴线缆的等效模型,所述目标同轴线缆的等效模型如图2所示;

获取目标同轴线缆的实测长度L,并计算线缆实测长度L与仿真长度l的比值t;所述比值t的计算公式为:t=L/l;

对等效模型按t倍进行阵列处理得到目标同轴线缆的等效电路模型,其中,所述目标同轴线缆的等效电路模型如图3所示;

根据等效电路模型建立二端口阻抗仿真模型,其中,芯线层的二端口阻抗仿真模型如图4所示,屏蔽层-芯线层二端口阻抗仿真模型如图5所示。

本发明一实施例通过电小尺寸原理,即l=1/10λ的公式生成目标同轴线缆的等效模型,并按照t=L/l的计算结果对所述等效模型按t倍进行阵列处理得到目标同轴线缆的等效电路模型,可以使得在仿真模型与实际电路误差较小的情况下还能达到快速建立仿真模型的效果。

对于步骤S3,在一个优选的实施例中,所述根据二端口阻抗仿真模型得到目标同轴线缆的各电路的仿真阻抗特性曲线,具体包括:

使用正弦电压源对二端口阻抗仿真模型的各端口的激励,在各个端口设置求解器,并获取二端口阻抗仿真模型的各端口的求解器的求解结果;根据所述求解结果得到目标同轴线缆的各电路的仿真阻抗特性曲线;其中,所述目标同轴线缆的各电路的仿真阻抗特性曲线包括芯线层电路的仿真阻抗特性曲线、芯线层-屏蔽层电路的仿真阻抗特性曲线、屏蔽层电路的仿真阻抗特性曲线和屏蔽层-屏蔽层电路的仿真阻抗特性曲线。

本发明一实施例基于上述阻抗分析仪测试的目标线缆的各电路的端口对二端口阻抗仿真模型的的各电路的端口添加激励,并设置求解器,从而得到目标同轴线缆的各电路的仿真阻抗特性曲线,使得仿真结果更接近于实测结果。

对于步骤S4,在一个优选的实施例中,将目标同轴线缆的各电路的实测阻抗特性曲线和目标同轴线缆的各电路的仿真阻抗特性曲线进行对比分析,并根据对比结果得到目标线缆的阻抗特性测试曲线;

具体地,将目标同轴线缆的芯线层电路的实测阻抗特性曲线和目标同轴线缆的芯线层电路的仿真阻抗特性曲线进行对比;

将目标同轴线缆的芯线层-屏蔽层电路的实测阻抗特性曲线和目标同轴线缆的芯线层-屏蔽层电路的仿真阻抗特性曲线进行对比;

将目标同轴线缆的屏蔽层电路的实测阻抗特性曲线和目标同轴线缆的屏蔽层电路的仿真阻抗特性曲线进行对比;

将目标同轴线缆的屏蔽层-屏蔽层电路的实测阻抗特性曲线和目标同轴线缆的屏蔽层-屏蔽层电路的仿真阻抗特性曲线进行对比。

本发明一实施例通过使用实测曲线与仿真曲线进行互相对比,可以实现交叉验证同轴线缆的仿真阻抗特性曲线是否与实测阻抗特性曲线符合,进而使得最终得到的结果更准确。

如图6所示,在上述各基于同轴线缆的阻抗测试方法的实施例的基础上,本发明对应提供了装置项实施例;

本发明一实施例提供了一种基于同轴线缆的阻抗测试装置,包括:实测阻抗特性曲线获取模块、二端口阻抗仿真模型建立模块、仿真阻抗特性曲线获取模块和对比分析模块;

所述实测阻抗特性曲线获取模块,用于获取目标同轴线缆的各电路的实测阻抗特性曲线;

所述二端口阻抗仿真模型建立模块,用于获取目标同轴线缆的等效电路模型并根据所述等效电路模型建立二端口阻抗仿真模型;

所述仿真阻抗特性曲线获取模块,用于根据二端口阻抗仿真模型得到目标同轴线缆的各电路的仿真阻抗特性曲线;

所述对比分析模块,用于将目标同轴线缆的各电路的实测阻抗特性曲线和目标同轴线缆的各电路的仿真阻抗特性曲线进行对比分析,并根据对比结果得到目标线缆的阻抗特性测试曲线。

对于所述实测阻抗特性曲线获取模块,在一个优选的实施例中,所述目标同轴线缆的各电路的实测阻抗特性曲线通过测试分析仪对目标线缆的各电路的测试端口进行扫频测试得到。

对于所述实测阻抗特性曲线获取模块,在一个优选的实施例中,所述目标同轴线缆的各电路的实测阻抗特性曲线包括:芯线层电路的实测阻抗特性曲线、芯线层-屏蔽层电路的实测阻抗特性曲线、屏蔽层电路的实测阻抗特性曲线和屏蔽层-屏蔽层电路的实测阻抗特性曲线。

对于所述二端口阻抗仿真模型建立模块,在一个优选的实施例中,所述获取目标同轴线缆等效电路模型具体包括:

获取目标同轴线缆的供电波长λ;

根据所述供电波长λ得到目标同轴线缆的仿真长度l;

根据目标同轴线缆的仿真长度l生成目标同轴线缆的等效模型;

获取目标同轴线缆的实测长度L,并计算线缆实测长度L与仿真长度l的比值t;

对等效模型按t倍进行阵列处理得到目标同轴线缆的等效电路模型。

对于所述二端口阻抗仿真模型建立模块,在一个优选的实施例中,所述目标同轴线缆的仿真长度l的计算公式为:l=1/10λ;

对于所述仿真阻抗特性曲线获取模块,在一个优选的实施例中,所述根据二端口阻抗仿真模型得到目标同轴线缆的各电路的仿真阻抗特性曲线具体包括:

响应正弦电压源对二端口阻抗仿真模型的各端口的激励;

获取二端口阻抗仿真模型的各端口的求解器的求解结果;

根据所述求解结果得到目标同轴线缆的各电路的仿真阻抗特性曲线。

对于所述仿真阻抗特性曲线获取模块,在一个优选的实施例中,所述目标同轴线缆的各电路的仿真阻抗特性曲线包括芯线层电路的仿真阻抗特性曲线、芯线层-屏蔽层电路的仿真阻抗特性曲线、屏蔽层电路的仿真阻抗特性曲线和屏蔽层-屏蔽层电路的仿真阻抗特性曲线。

需说明的是,在这一实施例中所描述的基于同轴线缆的阻抗测试装置的实施例是与本发明上述各基于同轴线缆的阻抗测试方法的实施例相对应的,其能够实现本发明上述任意一所述的基于同轴线缆的阻抗测试方法。此外,上述视基于同轴线缆的阻抗测试装置的的实施例仅仅是示意性的,其中所述作为分离部件说明的模块可以是或者也可以不是物理上分开的,作为模块显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部模块来实现本实施例方案的目的。另外,本发明提供的基于同轴线缆的阻抗测试装置实施例附图中,模块之间的连接关系表示它们之间具有通信连接,具体可以实现为一条或多条通信总线或信号线。

在上述基于同轴线缆的阻抗测试方法的实施例的基础上,本发明另一实施例提供了一种基于同轴线缆的阻抗测试的设备,该基于同轴线缆的阻抗测试设备,包括处理器、存储器以及存储在所述存储器中且被配置为由所述处理器执行的计算机程序,所述处理器执行所述计算机程序时,实现本发明任意一实施例的基于同轴线缆的阻抗测试方法。

示例性的,在这一实施例中所述计算机程序可以被分割成一个或多个模块,所述一个或者多个模块被存储在所述存储器中,并由所述处理器执行,以完成本发明。所述一个或多个模块元可以是能够完成特定功能的一系列计算机程序指令段,该指令段用于描述所述计算机程序在所述基于同轴线缆的阻抗测试设备中的执行过程。

所述基于同轴线缆的阻抗测试设备可以是桌上型计算机、笔记本、掌上电脑及云端服务器等计算设备。所述基于同轴线缆的阻抗测试设备可包括,但不仅限于,处理器、存储器。

所称处理器可以是中央处理单元(Central Processing Unit,CPU),还可以是其他通用处理器、数字信号处理器(Digital Signal Processor,DSP)、专用集成电路(Application Specific Integrated Circuit,ASIC)、现成可编程门阵列(Field-Programmable Gate Array,FPGA)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件等。通用处理器可以是微处理器或者该处理器也可以是任何常规的处理器等,所述处理器是所述基于同轴线缆的阻抗测试设备的控制中心,利用各种接口和线路连接整个基于同轴线缆的阻抗测试设备的各个部分。

所述存储器可用于存储所述计算机程序和/或模块,所述处理器通过运行或执行存储在所述存储器内的计算机程序和/或模块,以及调用存储在存储器内的数据,实现所述基于同轴线缆的阻抗测试设备的各种功能。所述存储器可主要包括存储程序区和存储数据区,其中,存储程序区可存储操作系统、至少一个功能所需的应用程序等;存储数据区可存储根据手机的使用所创建的数据等。此外,存储器可以包括高速随机存取存储器,还可以包括非易失性存储器,例如硬盘、内存、插接式硬盘,智能存储卡(Smart Media Card,SMC),安全数字(Secure Digital,SD)卡,闪存卡(Flash Card)、至少一个磁盘存储器件、闪存器件、或其他易失性固态存储器件。

在上述基于同轴线缆的阻抗测试方法的实施例的基础上,本发明另一实施例提供了一种存储介质,所述存储介质包括存储的计算机程序,其中,在所述计算机程序运行时,控制所述存储介质所在的设备执行本发明任意一实施例的基于同轴线缆的阻抗测试方法。

在这一实施例中,上述存储介质为计算机可读存储介质,所述计算机程序包括计算机程序代码,所述计算机程序代码可以为源代码形式、对象代码形式、可执行文件或某些中间形式等。所述计算机可读介质可以包括:能够携带所述计算机程序代码的任何实体或装置、记录介质、U盘、移动硬盘、磁碟、光盘、计算机存储器、只读存储器(ROM,Read-OnlyMemory)、随机存取存储器(RAM,Random Access Memory)、电载波信号、电信信号以及软件分发介质等。需要说明的是,所述计算机可读介质包含的内容可以根据司法管辖区内立法和专利实践的要求进行适当的增减,例如在某些司法管辖区,根据立法和专利实践,计算机可读介质不包括电载波信号和电信信号。

以上所述是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也视为本发明的保护范围。