CN112531031A - Semiconductor device with a plurality of semiconductor chips - Google Patents

Semiconductor device with a plurality of semiconductor chips Download PDFInfo

- Publication number

- CN112531031A CN112531031A CN202010542982.2A CN202010542982A CN112531031A CN 112531031 A CN112531031 A CN 112531031A CN 202010542982 A CN202010542982 A CN 202010542982A CN 112531031 A CN112531031 A CN 112531031A

- Authority

- CN

- China

- Prior art keywords

- fin

- strain

- implant

- type

- finfet

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 54

- IJGRMHOSHXDMSA-UHFFFAOYSA-N nitrogen Substances N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 claims abstract description 45

- 230000000737 periodic effect Effects 0.000 claims abstract description 24

- 229910052757 nitrogen Inorganic materials 0.000 claims abstract description 23

- 238000002955 isolation Methods 0.000 claims description 43

- 239000000470 constituent Substances 0.000 claims description 15

- 230000005669 field effect Effects 0.000 abstract description 19

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 abstract description 3

- 238000000034 method Methods 0.000 description 129

- 239000007943 implant Substances 0.000 description 120

- 230000008569 process Effects 0.000 description 102

- 239000010410 layer Substances 0.000 description 73

- 125000004429 atom Chemical group 0.000 description 48

- 238000004519 manufacturing process Methods 0.000 description 44

- 239000000463 material Substances 0.000 description 42

- 238000005468 ion implantation Methods 0.000 description 41

- 238000002513 implantation Methods 0.000 description 39

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 33

- 238000000137 annealing Methods 0.000 description 33

- 229910052710 silicon Inorganic materials 0.000 description 31

- 239000010703 silicon Substances 0.000 description 31

- 239000000758 substrate Substances 0.000 description 30

- 125000006850 spacer group Chemical group 0.000 description 25

- 150000001875 compounds Chemical class 0.000 description 24

- 239000002019 doping agent Substances 0.000 description 19

- 230000000873 masking effect Effects 0.000 description 16

- 229920002120 photoresistant polymer Polymers 0.000 description 15

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 14

- 239000011229 interlayer Substances 0.000 description 13

- 230000008901 benefit Effects 0.000 description 12

- 238000000151 deposition Methods 0.000 description 12

- 229910052732 germanium Inorganic materials 0.000 description 12

- 239000000203 mixture Substances 0.000 description 11

- 229910052581 Si3N4 Inorganic materials 0.000 description 10

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 10

- 239000007789 gas Substances 0.000 description 10

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 10

- 238000000059 patterning Methods 0.000 description 9

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 8

- 229910052814 silicon oxide Inorganic materials 0.000 description 8

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 7

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 7

- 229910052738 indium Inorganic materials 0.000 description 6

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 6

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 5

- 229910052785 arsenic Inorganic materials 0.000 description 5

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 5

- 229910052799 carbon Inorganic materials 0.000 description 5

- 238000005229 chemical vapour deposition Methods 0.000 description 5

- 230000001965 increasing effect Effects 0.000 description 5

- 239000011810 insulating material Substances 0.000 description 5

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 5

- 229910010271 silicon carbide Inorganic materials 0.000 description 5

- 239000011800 void material Substances 0.000 description 5

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 4

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 4

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 4

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 4

- 229910052796 boron Inorganic materials 0.000 description 4

- 229910002092 carbon dioxide Inorganic materials 0.000 description 4

- 239000001569 carbon dioxide Substances 0.000 description 4

- 238000000407 epitaxy Methods 0.000 description 4

- 238000005530 etching Methods 0.000 description 4

- 230000009969 flowable effect Effects 0.000 description 4

- 238000002347 injection Methods 0.000 description 4

- 239000007924 injection Substances 0.000 description 4

- 229910052698 phosphorus Inorganic materials 0.000 description 4

- 239000011574 phosphorus Substances 0.000 description 4

- 238000000206 photolithography Methods 0.000 description 4

- ABTOQLMXBSRXSM-UHFFFAOYSA-N silicon tetrafluoride Chemical compound F[Si](F)(F)F ABTOQLMXBSRXSM-UHFFFAOYSA-N 0.000 description 4

- 239000000126 substance Substances 0.000 description 4

- 229910052787 antimony Inorganic materials 0.000 description 3

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 3

- 230000008021 deposition Effects 0.000 description 3

- 239000003989 dielectric material Substances 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- OKZIUSOJQLYFSE-UHFFFAOYSA-N difluoroboron Chemical compound F[B]F OKZIUSOJQLYFSE-UHFFFAOYSA-N 0.000 description 3

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 3

- 238000005498 polishing Methods 0.000 description 3

- PPMWWXLUCOODDK-UHFFFAOYSA-N tetrafluorogermane Chemical compound F[Ge](F)(F)F PPMWWXLUCOODDK-UHFFFAOYSA-N 0.000 description 3

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 2

- 229910000530 Gallium indium arsenide Inorganic materials 0.000 description 2

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- 229910006990 Si1-xGex Inorganic materials 0.000 description 2

- 229910007020 Si1−xGex Inorganic materials 0.000 description 2

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- KXNLCSXBJCPWGL-UHFFFAOYSA-N [Ga].[As].[In] Chemical compound [Ga].[As].[In] KXNLCSXBJCPWGL-UHFFFAOYSA-N 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 239000005380 borophosphosilicate glass Substances 0.000 description 2

- 239000005388 borosilicate glass Substances 0.000 description 2

- 239000004020 conductor Substances 0.000 description 2

- 229910001873 dinitrogen Inorganic materials 0.000 description 2

- 229910052733 gallium Inorganic materials 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 239000005360 phosphosilicate glass Substances 0.000 description 2

- 230000008439 repair process Effects 0.000 description 2

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 2

- 239000005368 silicate glass Substances 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- 239000010936 titanium Substances 0.000 description 2

- IHGSAQHSAGRWNI-UHFFFAOYSA-N 1-(4-bromophenyl)-2,2,2-trifluoroethanone Chemical compound FC(F)(F)C(=O)C1=CC=C(Br)C=C1 IHGSAQHSAGRWNI-UHFFFAOYSA-N 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 229910000881 Cu alloy Inorganic materials 0.000 description 1

- 229910002601 GaN Inorganic materials 0.000 description 1

- 229910005540 GaP Inorganic materials 0.000 description 1

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 1

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- BPQQTUXANYXVAA-UHFFFAOYSA-N Orthosilicate Chemical compound [O-][Si]([O-])([O-])[O-] BPQQTUXANYXVAA-UHFFFAOYSA-N 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 1

- HMDDXIMCDZRSNE-UHFFFAOYSA-N [C].[Si] Chemical compound [C].[Si] HMDDXIMCDZRSNE-UHFFFAOYSA-N 0.000 description 1

- 239000000370 acceptor Substances 0.000 description 1

- MDPILPRLPQYEEN-UHFFFAOYSA-N aluminium arsenide Chemical compound [As]#[Al] MDPILPRLPQYEEN-UHFFFAOYSA-N 0.000 description 1

- 239000006117 anti-reflective coating Substances 0.000 description 1

- 238000000231 atomic layer deposition Methods 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 239000013626 chemical specie Substances 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 238000005137 deposition process Methods 0.000 description 1

- 230000001627 detrimental effect Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000018109 developmental process Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000002708 enhancing effect Effects 0.000 description 1

- VTGARNNDLOTBET-UHFFFAOYSA-N gallium antimonide Chemical compound [Sb]#[Ga] VTGARNNDLOTBET-UHFFFAOYSA-N 0.000 description 1

- HZXMRANICFIONG-UHFFFAOYSA-N gallium phosphide Chemical compound [Ga]#P HZXMRANICFIONG-UHFFFAOYSA-N 0.000 description 1

- IWTIUUVUEKAHRM-UHFFFAOYSA-N germanium tin Chemical compound [Ge].[Sn] IWTIUUVUEKAHRM-UHFFFAOYSA-N 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 239000010931 gold Substances 0.000 description 1

- 229910052735 hafnium Inorganic materials 0.000 description 1

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 1

- 239000002784 hot electron Substances 0.000 description 1

- BHEPBYXIRTUNPN-UHFFFAOYSA-N hydridophosphorus(.) (triplet) Chemical compound [PH] BHEPBYXIRTUNPN-UHFFFAOYSA-N 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 229910052746 lanthanum Inorganic materials 0.000 description 1

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 1

- 238000005224 laser annealing Methods 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 229910052749 magnesium Inorganic materials 0.000 description 1

- 239000011777 magnesium Substances 0.000 description 1

- 238000000691 measurement method Methods 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 229910052914 metal silicate Inorganic materials 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 125000004430 oxygen atom Chemical group O* 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 238000004151 rapid thermal annealing Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000000717 retained effect Effects 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 238000004088 simulation Methods 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- 229910052726 zirconium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/26506—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/1025—Channel region of field-effect devices

- H01L29/1029—Channel region of field-effect devices of field-effect transistors

- H01L29/1033—Channel region of field-effect devices of field-effect transistors with insulated gate, e.g. characterised by the length, the width, the geometric contour or the doping structure

- H01L29/1054—Channel region of field-effect devices of field-effect transistors with insulated gate, e.g. characterised by the length, the width, the geometric contour or the doping structure with a variation of the composition, e.g. channel with strained layer for increasing the mobility

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/785—Field effect transistors with field effect produced by an insulated gate having a channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/22—Diffusion of impurity materials, e.g. doping materials, electrode materials, into or out of a semiconductor body, or between semiconductor regions; Interactions between two or more impurities; Redistribution of impurities

- H01L21/225—Diffusion of impurity materials, e.g. doping materials, electrode materials, into or out of a semiconductor body, or between semiconductor regions; Interactions between two or more impurities; Redistribution of impurities using diffusion into or out of a solid from or into a solid phase, e.g. a doped oxide layer

- H01L21/2251—Diffusion into or out of group IV semiconductors

- H01L21/2252—Diffusion into or out of group IV semiconductors using predeposition of impurities into the semiconductor surface, e.g. from a gaseous phase

- H01L21/2253—Diffusion into or out of group IV semiconductors using predeposition of impurities into the semiconductor surface, e.g. from a gaseous phase by ion implantation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/26506—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors

- H01L21/26513—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors of electrically active species

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/2658—Bombardment with radiation with high-energy radiation producing ion implantation of a molecular ion, e.g. decaborane

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/26586—Bombardment with radiation with high-energy radiation producing ion implantation characterised by the angle between the ion beam and the crystal planes or the main crystal surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/266—Bombardment with radiation with high-energy radiation producing ion implantation using masks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

- H01L21/28017—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon

- H01L21/28026—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor

- H01L21/28114—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor characterised by the sectional shape, e.g. T, inverted-T

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/324—Thermal treatment for modifying the properties of semiconductor bodies, e.g. annealing, sintering

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind

- H01L27/085—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only

- H01L27/088—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate

- H01L27/0886—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate including transistors with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0642—Isolation within the component, i.e. internal isolation

- H01L29/0649—Dielectric regions, e.g. SiO2 regions, air gaps

- H01L29/0653—Dielectric regions, e.g. SiO2 regions, air gaps adjoining the input or output region of a field-effect device, e.g. the source or drain region

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/1025—Channel region of field-effect devices

- H01L29/1029—Channel region of field-effect devices of field-effect transistors

- H01L29/1033—Channel region of field-effect devices of field-effect transistors with insulated gate, e.g. characterised by the length, the width, the geometric contour or the doping structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42372—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the conducting layer, e.g. the length, the sectional shape or the lay-out

- H01L29/42376—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the conducting layer, e.g. the length, the sectional shape or the lay-out characterised by the length or the sectional shape

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66545—Unipolar field-effect transistors with an insulated gate, i.e. MISFET using a dummy, i.e. replacement gate in a process wherein at least a part of the final gate is self aligned to the dummy gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66568—Lateral single gate silicon transistors

- H01L29/66575—Lateral single gate silicon transistors where the source and drain or source and drain extensions are self-aligned to the sides of the gate

- H01L29/6659—Lateral single gate silicon transistors where the source and drain or source and drain extensions are self-aligned to the sides of the gate with both lightly doped source and drain extensions and source and drain self-aligned to the sides of the gate, e.g. lightly doped drain [LDD] MOSFET, double diffused drain [DDD] MOSFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66787—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a gate at the side of the channel

- H01L29/66795—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a gate at the side of the channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7833—Field effect transistors with field effect produced by an insulated gate with lightly doped drain or source extension, e.g. LDD MOSFET's; DDD MOSFET's

- H01L29/7834—Field effect transistors with field effect produced by an insulated gate with lightly doped drain or source extension, e.g. LDD MOSFET's; DDD MOSFET's with a non-planar structure, e.g. the gate or the source or the drain being non-planar

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7842—Field effect transistors with field effect produced by an insulated gate means for exerting mechanical stress on the crystal lattice of the channel region, e.g. using a flexible substrate

- H01L29/7848—Field effect transistors with field effect produced by an insulated gate means for exerting mechanical stress on the crystal lattice of the channel region, e.g. using a flexible substrate the means being located in the source/drain region, e.g. SiGe source and drain

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/785—Field effect transistors with field effect produced by an insulated gate having a channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

- H01L29/7851—Field effect transistors with field effect produced by an insulated gate having a channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET with the body tied to the substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/16—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only elements of Group IV of the Periodic Table

- H01L29/161—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only elements of Group IV of the Periodic Table including two or more of the elements provided for in group H01L29/16, e.g. alloys

- H01L29/165—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only elements of Group IV of the Periodic Table including two or more of the elements provided for in group H01L29/16, e.g. alloys in different semiconductor regions, e.g. heterojunctions

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Ceramic Engineering (AREA)

- High Energy & Nuclear Physics (AREA)

- Toxicology (AREA)

- Health & Medical Sciences (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Spectroscopy & Molecular Physics (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Abstract

The present disclosure relates to semiconductor devices. The fin-shaped field effect transistor device comprises a channel region including a component element belonging to a group of the periodic table and an excess atom, wherein the excess atom is nitrogen or belongs to the group of the periodic table, and a concentration of the excess atom in the channel region is between about 1019cm‑3To about 1020cm‑3In the meantime.

Description

Technical Field

Embodiments of the present invention relate generally to semiconductor manufacturing and, more particularly, to an apparatus and method for manufacturing the same using ion implantation.

Background

In recent developments in the semiconductor industry, fin field effect transistors are employed instead of planar transistors. In a finfet, the transistor channel is formed substantially in a high aspect ratio structure, commonly referred to as a fin. The gate of the finfet covers not only the top of the fin but also the sides of the fin. This arrangement has several advantages over planar transistors, including greater reliability at the same performance and greater control over channel inversion.

Disclosure of Invention

In one embodiment, a semiconductor device includes a transistor and an isolation region adjacent to the transistor. The transistor has a channel region containing a constituent element and an excess atom, and the constituent element belongs to a group of the periodic table of elements, wherein the excess atom is nitrogen or belongs to the group of the periodic table of elements. The concentration of excess atoms in the channel region is between about 1019cm-3To about 1021cm-3In the meantime. The isolation region also contains excess atoms, and the concentration of the excess atoms in the isolation region is between about 1020cm-3To about 1021cm-3In the meantime.

In one embodiment, a semiconductor device includes a gate, wherein a width of an upper side of the gate is greater than a width of a lower side of the gate by more than 1nm, a channel region including a constituent element belonging to a group of the periodic table and an excess atom being nitrogen or belonging to the group of the periodic table, and a concentration of the excess atom in the channel region is between about 1019cm-3To about 1021cm-3In the meantime.

In one embodiment, the finfet includes a channel region including a constituent element belonging to one of the periodic table of elements, and the method of fabricating the finfet includes: placing a channel mask structure on a first portion of the fin to cover the first portion of the fin, the channel mask structure not covering a second portion of the fin, and the first portion of the fin including at least a portion of the channel region, performing a first ion implantation of nitrogen or an element belonging to the group of the periodic table of elements, and annealing the first ion implantation.

Drawings

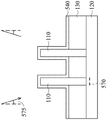

Fig. 1 is a simplified perspective view of a selected cell of a structure including two finfet transistors at a stage in the fabrication process of the finfet transistors.

Fig. 2A, 2B, 3A, 3B, 4A, and 4B are simplified cross-sectional views of selected finfet structures at various stages of a finfet fabrication process.

Figures 5A and 5B are simplified cross-sectional views of selected structures prior to a lightly doped drain process sequence of a finfet fabrication process.

Fig. 6A and 6B are simplified cross-sectional views of a selected p-type finfet structure after a strain implantation in a p-type lightly doped drain process sequence.

Figure 7 is a plan view of stress components in a p-type fin field effect transistor structure after a strain implant in a p-type lightly doped drain process sequence.

Fig. 8A and 8B are simplified cross-sectional views of a selected p-type finfet structure after source/drain recessing in the finfet fabrication process, including a strain implant in a p-type lightly doped drain process sequence.

Fig. 9A and 9B are simplified cross-sectional views of a selected p-type finfet structure after a first interlayer dielectric layer is deposited in a finfet fabrication process that includes a strain implant in a p-type lightly doped drain process sequence.

Fig. 10A and 10B are simplified cross-sectional views of a selected p-type finfet structure after removal of the gate stack in a finfet fabrication process that includes a strain implant in a p-type lightly doped drain process sequence.

Fig. 11A and 11B are simplified cross-sectional views of a selected p-type finfet structure after formation of a replacement gate in a finfet fabrication process that includes a strain implant in a p-type lightly doped drain process sequence.

Fig. 12A and 12B are simplified cross-sectional views of a selected p-type finfet structure after contacts are formed in a finfet fabrication process that includes a strain implant in a p-type lightly doped drain process sequence.

Figure 13 is a table of implantation parameters for strain implantation in a finfet in some embodiments.

FIG. 14 is a flow chart of a method of strain implantation in one embodiment.

Figure 15 is a flowchart of a method for performing a strain implant at the stage of lightly doped drain in one embodiment.

Description of reference numerals:

A-A, B-B, C-C: cutting line

110: fin

120: substrate

130: isolation region

140: dummy gate stack

510: virtual grid

520: silicon nitride layer

530: oxide layer

540: first spacer

550: channel region

560: length direction of channel

565. 575: inclination angle

570: fin width direction

610: upper fin region

625: compressive strain

630: upper side isolation region

633. 635 and 638: component of strain

640: upper side stacking region

655: lower fin portion

710: corner

810: region(s)

820: level of depression

830: second spacer

840: free full fin region

850: side wall

910: source/drain structure

920: air gap

930: contact etch stop layer

940: first interlayer dielectric layer

1010: hollow spaces

1020: width of top

1030: width of bottom

1110: second gate dielectric layer

1120: replacement gate

1210: second interlayer dielectric layer

1220: source/drain contact

1230: gate contact

1240: width of upper side

1250: width of lower side

1400. 1500: method of producing a composite material

1410. 1420, 1430, 1510, 1520, 1530, 1540, 1550: step (ii) of

Detailed Description

The different embodiments or examples provided below may implement different configurations of the present invention. The following embodiments of specific components, and arrangements are provided to simplify the present disclosure and not to limit the same. For example, the description of forming a first element on a second element includes embodiments in which the two are in direct contact, or embodiments in which the two are separated by additional elements other than direct contact. Moreover, various examples of the invention may be repeated using the same reference numerals for brevity, but elements having the same reference numerals in the various embodiments and/or arrangements do not necessarily have the same correspondence.

Furthermore, spatially relative terms such as "below," "lower," "above," "upper," or the like may be used for ease of description to refer to a relationship of one element to another in the figures. Spatially relative terms may be extended to elements used in other orientations than the orientation illustrated. The elements may also be rotated 90 or other angles, and thus directional terms are used only to describe directions in the drawings.

The term "group IV semiconductor element" herein is essentially any semiconductor element consisting of a single element of group IVB of the periodic table, such as silicon or germanium. Likewise, the term "group IV semiconductor compound" is essentially any semiconductor compound of the group IVA elemental composition of the periodic table of elements, including silicon germanium, silicon germanium carbide, or silicon carbide, regardless of whether the composition of the compound is fixed or varies with position. Furthermore, the term "group III-V semiconductor compound" is essentially any semiconductor compound consisting of elements of groups IIIA and VA of the periodic Table of the elements, including gallium arsenide, indium gallium arsenide, or the like. In addition, the chemical formula Si1- xGexPure or substantially pure silicon, pure or substantially pure germanium, or silicon germanium of any composition, whether fixed in composition or varying with position, is meant. In the case of zero germanium content x, Si1-xGexIs pure silicon or substantially pure silicon. Si at a germanium content x of 1 or 100%1-xGexIs pure germanium or substantially pure germanium.

The terms "p-FinFET" and "n-FinFET" are used herein to refer to n-type and p-type fin field effect transistors, respectively. Furthermore, the term "source-drain" is intended to mean either a source or a drain. For example, the source-drain regions are regions that are, or are intended to be, sources or drains of transistors. The term "implant species" refers to an implant species, and the term "implant gas" refers to a gas used to implant a species in an ion implanter. For example, the implant gas silicon tetrafluoride may be used to implant the implant species Si. The strain or stress may be represented by arrows in the figures. However, the length or width of the arrows is not intended to indicate absolute or relative strength of stress or strain unless explicitly stated otherwise in the specification.

In a semiconductor manufacturing process, one or more annealing steps may be performed after the ion implantation step. Here an annealing step that occurs earlier than any other annealing step after the ion implantation step may be considered as annealing the ion implantation.

Some embodiments disclosed herein illustrate fabrication processes for finfet transistors, but the disclosed processes may also be applied to other structures. Figure 1 is a simplified perspective view of a selected cell of a structure containing two finfet channel channels at a stage in the fabrication process of a finfet. In the stage of the fabrication process shown in fig. 1, fins 110 are formed on substrate 120, and isolation regions 130 separate fins 110 from each other and from other fins (not shown). Furthermore, dummy gate stack 140 is along sidewalls of fin 110 and on an upper surface of fin 110. Two transistor channel regions may be formed in the portion of fin 110 covered by dummy gate stack 140. As shown in fig. 1, the cross-sectional line a-a at any stage of the fabrication process is along a plane perpendicular to the substrate 120. Similarly, the cross-section line B-B at any stage of the fabrication process is along a plane perpendicular to the substrate 120. Similarly, the cross-sectional line C-C at any stage of the fabrication process is along a plane perpendicular to the substrate 120. FIGS. 2A to 6A and 8A to 12A refer to section line A-A shown in FIG. 1, and FIGS. 2B to 6B and 8B to 12B refer to section line B-B shown in FIG. 1.

Fig. 2A-4B are simplified cross-sectional views of selected finfet structures at various stages of a finfet fabrication process. As shown in fig. 2A and 2B, an example of a fabrication process begins with substrate 120. The substrate 120 may be a bulk semiconductor substrate, a semiconductor-on-insulator substrate, an insulating substrate, or the like. The bulk semiconductor substrate may be silicon or a semiconductor compound, which may be doped or undoped. The semiconductor-on-insulator substrate may include a layer of semiconductor material formed on an insulating layer, which may be a buried oxide layer, a silicon oxide layer, or the like, and which may be located on an underlying substrate such as a silicon substrate or a glass substrate.

In the fabrication process shown in fig. 2A and 2B, the material layer for fin 110 may be located on substrate 120. In various examples, the material used for fin 110 may include one or more semiconductor layers deposited on substrate 120, and the deposition method may be epitaxy. Fin 110 may be formed from a material that is different than the underlying base material, and may be undoped or doped during or after growth. For example, the material used for fins 110 may be or include silicon, silicon germanium, pure or substantially pure germanium, silicon carbide, group III-V semiconductor compounds, group II-VI semiconductor compounds, or the like.

It is contemplated herein that in other fabrication processes, no material is specifically deposited for fin 110, and fin 110 may be produced from substrate 120. In these processes, the lines between the materials used for fin 110 and substrate 120 in the various figures do not represent changes in material properties, but rather represent the approximate bottom of fin 110 after fabrication of the fin is complete.

In fig. 3A and 3B, fin 110 is located on substrate 120. The fins may be patterned by any suitable method. For example, the fins may be patterned using one or more photolithography processes, including double patterning or multiple patterning processes. In general, double patterning or multiple patterning processes combine photolithography and self-aligned processes that produce a pattern pitch that is smaller than that obtained using a single direct lithography process. For example, a sacrificial layer may be formed on a substrate and patterned using a photolithography process. Spacers may be formed along the sides of the patterned sacrificial layer using a self-aligned process. The sacrificial layer may then be removed and the remaining spacers may be used to pattern the fins.

The fins may be created by a variety of methods, including etching regions of layers on a substrate, or depositing fin material into narrow trenches. Regions of the layer may be etched in the process to create fins, and the fin pattern may be transferred to one or more underlying masking layers. These masking layers may be or include silicon nitride, silicon oxynitride, silicon carbide, silicon carbonitride, the like, or combinations thereof. An anisotropic etch may then be used to remove material outside the fin regions.

In fig. 4A and 4B, isolation region 130 is located between fins 110. The isolation region 130 may comprise or may be an insulating material such as silicon oxide, silicon nitride, the like, or combinations thereof, and may be formed by a suitable deposition process. For example, the isolation region 130 may comprise silicon oxide formed by a flowable chemical vapor deposition process. Other insulating materials formed by any acceptable process may also be used. A planarization process, such as chemical mechanical polishing, may be used to remove excess material such that the insulative material is coplanar with the upper surface of fin 110. The insulating material may then be recessed to form isolation regions 130, such that fins 110 protrude from between isolation regions 130. The recessing of the insulating material may be performed using any acceptable etching process, such as an etching process that is selective to the insulating material. The upper surface of the isolation region 130 may be flat as shown, convex, concave, or present a more complex shape depending on process details.

In other fabrication processes, the fin is formed by depositing fin material into narrow trenches, which is more complex than the above process and involves additional structures not shown. In one example of a process, a dielectric layer may be formed on a top surface of a semiconductor substrate 120, a trench may be etched through the dielectric layer to form a trench, a fin material may be epitaxially grown in the trench, and the dielectric layer may be recessed to allow the fin material to protrude from the dielectric layer and form a fin. The epitaxial material, which may be the same or different from the substrate, may be undoped or doped as grown or after growth. In these processes, it is particularly advantageous to grow different materials for the n-type and p-type finfet transistors, respectively, such as to maximize carrier mobility in each device type. For example, the composition of the fin or portion thereof may be silicon germanium, silicon carbide, pure or substantially pure germanium, a group III-V semiconductor compound, a group II-VI semiconductor compound, or the like. Possible materials for forming the III-V semiconductor compound include, but are not limited to, gallium arsenide, indium gallium arsenide, aluminum arsenide, indium phosphide, gallium nitride, gallium antimonide, aluminum phosphide, gallium phosphide, or the like.

An appropriate well region (not shown) may be formed in fin 110 and/or substrate 120. For example, a p-type well may be formed where the n-type finfet is to be formed, an n-type well may be formed where the p-type finfet is to be formed, or both a p-type well and an n-type well may be formed. The doping for the p-type well and the n-type well may be provided by ion implantation. In summary, fin 110, isolation region 130, substrate 120, and any other structures present on the substrate may contain dopants from the well implant when the well implant. The dopant used to form the n-type well may be phosphorus, arsenic, antimony, or the like. The dopant used to form the p-type well may be boron, boron difluoride, indium, or the like. One or more annealing steps may be performed to activate the implanted dopants. In some processes, the substrate and/or fin material may be doped during crystal growth or deposition, and a well implant may not be necessary.

Fig. 5A and 5B are simplified cross-sectional views of selected structures prior to a lightly doped drain process sequence of a finfet fabrication process, as described below. The dummy gate stack 140 of fig. 1 may include a dummy gate 510 and one or more additional layers, such as a silicon nitride layer 520 and an oxide layer 530. Furthermore, a first gate dielectric layer (not shown) may be located between fin 110 and dummy gate 510. The first gate dielectric layer may comprise or may be silicon oxide, silicon nitride, a high-k dielectric layer, the like, or multiple layers thereof, and may be thermally grown and/or chemically or conformally deposited (by suitable deposition techniques). Once the fabrication process is complete, channel region 550 of fin 110 may serve as a channel for a fin field effect transistor. In some examples of the manufacturing process, first spacers 540 may be located on the sides of fin 110 and dummy gate stack 140. The first spacers 540 may be or include silicon nitride, silicon oxide, silicon oxynitride, or the like. In one embodiment, the first spacers 540 are silicon nitride.

In fig. 5A, the finfet has a channel length direction 560. Further, the tilt angle 565 refers to a tilt angle in a channel length direction of the finfet. Figure 5B also shows fin width direction 570. The inclination angle 575 refers to an inclination angle in the fin width direction. The ion implantation may be performed obliquely and result in a symmetric implantation profile on both sides of the symmetric structure, and is typically performed in two steps. Two halves of the total dose are implanted at an oblique angle of positive and negative values with respect to a plane perpendicular to the substrate. In the tilt-angle-free ion implantation, the total dose is implanted in a single step.

The lightly doped drain process may include an n-type lightly doped drain process sequence and/or a p-type lightly doped drain process sequence. In the case of an n-type lightly doped drain process sequence, a masking layer, such as a photoresist layer, may be deposited and patterned according to an n-type lightly doped drain pattern to cover the p-type finfet structure and expose the n-type finfet structure. Then, n-type dopant is implanted to form n-type lightly doped drain region for n-type fin field effect transistor, which can be used as donor. For example, one or more of phosphorus, arsenic, antimony, or other n-type dopants may be implanted as n-type lightly doped drain dopants to form an n-type lightly doped drain region. This implant can be considered as an n-type lightly doped drain implant. After the n-type lightly doped drain implant, the patterned photoresist layer may be removed and an n-type lightly doped drain anneal performed to activate the dopants. In the p-type lightly doped drain process sequence, a patterned masking layer (e.g., a photoresist layer deposited and patterned according to the p-type lightly doped drain pattern) may cover the n-type finfet structure and expose the p-type finfet structure. P-type dopants are then implanted to form p-type lightly doped drain regions for the p-type fin-shaped field effect transistors, which may serve as receptors. For example, one or more of boron, boron difluoride, indium, or other p-type dopants can be implanted as a p-type lightly doped drain dopant to form a p-type lightly doped drain region. This implant can be considered a p-type lightly doped drain implant. After the p-type lightly doped drain implant, the patterned photoresist layer may be removed and a p-type lightly doped drain anneal performed to activate the dopants. Without the lightly doped drain implant, the doping concentration between the channel and source/drain regions of the transistor varies dramatically, producing harmful hot electrons. A lightly doped drain implant is typically used to make the dopant concentration change between the channel and source/drain regions more gradual. The n-type lightly doped drain process sequence may be performed before or after the p-type lightly doped drain process sequence. In addition, other process steps may be performed between the process sequence of the n-type lightly doped drain and the p-type lightly doped drain. For example, after an n-type lightly doped drain process sequence and before a p-type lightly doped drain process sequence, sidewalls may be formed to advantageously affect the location of the p-type lightly doped drain doping value. In addition, in order to replace the annealing steps of the separated n-type lightly doped drain and the p-type lightly doped drain, a single lightly doped drain annealing step can be adopted to activate the dopants of the p-type lightly doped drain and the n-type lightly doped drain. In various examples of processes, the one or more annealing steps may be a rapid thermal anneal, a spike anneal, a laser anneal, or the like. The terms medium doped drain, n-type medium doped drain, and p-type medium doped drain may sometimes be used in place of the terms lightly doped drain, n-type lightly doped drain, and p-type lightly doped drain to indicate that the doping concentration used in a given process is slightly higher than the historically lower level used in the past technology generations. Other terms such as drain extension may also be used.

In the embodiments described herein, ion implantation may be advantageously performed to affect the strain in the channel region of the finfet. This implant may be referred to herein as a strain implant.

Fig. 6A and 6B are simplified cross-sectional views of a selected p-type finfet structure after a strain implant in a p-type lightly doped drain process sequence. In this embodiment, the strain implant is performed in the presence of a p-type lightly doped drain photoresist pattern. Therefore, the embodiment has the advantage of no need of additional patterning steps, thereby reducing the cost and the process complexity. In addition, the combination of the dummy gate stack 140 and the first spacers 540 may serve as a mask structure for implantation. In various embodiments, the strain implant may be performed before or after any of the one or more p-type lightly doped drain implants performed in the p-type lightly doped drain process sequence. In one embodiment, the material used for fin 110 is silicon, and the implant species used for the strain implant is also silicon. For example, silicon tetrafluoride may be employed as an injection gas to inject silicon. The implant species enter some of upper fin region 610 of fin 110, some of upper isolation region 630 of isolation region 130, and upper stack region 640 of dummy gate stack 140. Any implant species that enter the sidewalls of dummy gate stack 140 and the portion of first spacers 540 on the sidewalls of fin 110 are not shown to simplify the drawing.