CN111863085B - Method and device for controlling programming performance - Google Patents

Method and device for controlling programming performance Download PDFInfo

- Publication number

- CN111863085B CN111863085B CN201910356967.6A CN201910356967A CN111863085B CN 111863085 B CN111863085 B CN 111863085B CN 201910356967 A CN201910356967 A CN 201910356967A CN 111863085 B CN111863085 B CN 111863085B

- Authority

- CN

- China

- Prior art keywords

- programming

- program

- state machine

- operation state

- cycle number

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

- G11C16/12—Programming voltage switching circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/349—Arrangements for evaluating degradation, retention or wearout, e.g. by counting erase cycles

- G11C16/3495—Circuits or methods to detect or delay wearout of nonvolatile EPROM or EEPROM memory devices, e.g. by counting numbers of erase or reprogram cycles, by using multiple memory areas serially or cyclically

Landscapes

- Read Only Memory (AREA)

Abstract

The invention provides a method and a device for controlling programming performance. The method is applied to a NOR flash memory, and the NOR flash memory comprises the following steps: the device comprises a programming cycle number detection unit, a programming operation state machine, a clock frequency generator and a programming storage unit, wherein the programming operation state machine comprises: a counter, the method comprising: and the programming operation state machine receives the programming operation instruction and the data to be programmed, executes programming verification operation according to the programming operation instruction and the data to be programmed, adjusts time according to the cycle number if the verification fails, and completes programming pressurization operation according to the adjusted time. When the NOR flash memory executes the programming pressurization operation, the time of the single programming pressurization operation is adjusted according to the cycle number, the programming pressurization operation is completed, the cycle periods of the programming verification operation and the programming pressurization operation are controlled, and the programming performance of the NOR flash memory is improved.

Description

Technical Field

The present invention relates to the field of storage, and in particular, to a method and apparatus for controlling programming performance.

Background

At present, a programming operation of the NOR flash memory is realized by adopting a channel carrier hot electron injection mode, and research results show that the longer the voltage is applied during programming, the better the programming effect on a memory cell of the NOR flash memory is.

Referring to fig. 1, a schematic diagram of a programming principle of a conventional NOR flash memory is shown, in a programming operation, hot electrons obtained by accelerating a high electric field are injected into a floating gate layer in a hot electron injection manner, so that a threshold value of the floating gate layer is changed to achieve a programming effect, a positive voltage needs to be applied to a drain terminal (D) in order to form a conductive channel, a positive voltage needs to be applied to a gate terminal (G) in order to enable electrons to reach the floating gate layer, and a source terminal (S) and a substrate are grounded.

In the current programming operation process, the maximum value of a counter for controlling programming pressurization time in a programming operation state machine and the frequency of a clock frequency generator (CLK generator) are determined when the chip is delivered from a factory, however, along with the increase of programming and erasing times, due to the existence of various defects, the probability of success of single programming is reduced, the time of the chip for completing the whole programming operation is longer and longer, the programming performance is worse and worse, and even a programming task cannot be completed finally.

Disclosure of Invention

The method and the device for controlling the programming performance solve the problems that the probability of success of single programming is reduced along with the increase of the programming and erasing times, but the time of single programming pressurization operation is fixed, the longer the time required for completing the whole programming operation is, and even the programming task cannot be completed finally.

In order to solve the above technical problem, an embodiment of the present invention provides a method for controlling programming performance, where the method is applied to a NOR flash memory, and the NOR flash memory includes: the device comprises a programming cycle number detection unit, a programming operation state machine, a clock frequency generator and a programming storage unit, wherein the programming operation state machine comprises: a counter, the program cycle number detection unit being connected to the clock frequency generator, the program operation state machine being connected to the clock frequency generator and the program storage unit, respectively, the method comprising:

receiving a programming operation instruction and data to be programmed through the programming operation state machine, wherein the data to be programmed is data required to be written into the programming storage unit;

according to the programming operation instruction and the data to be programmed, executing programming verification operation through the programming operation state machine, wherein the programming verification operation is an operation of verifying whether the data to be programmed is consistent with the data stored in the programming storage unit, if so, the verification is passed, and if not, the verification is not passed;

if the verification is not passed, executing a program pressurization operation by the program operation state machine, wherein the program pressurization operation is an operation of continuously applying a preset voltage value to the program storage unit, and the time of continuously applying the preset voltage value is the product of the maximum value of the counter and the period of the clock frequency generator;

wherein performing a program stress operation by the program operation state machine includes:

the NOR flash memory receives the program verification and program pressurization cycle times sent by the program cycle time detection unit, wherein the cycle times are the times for executing the program verification operation and the program pressurization operation when the program operation corresponding to the program operation instruction is completed, and each cycle time corresponds to one program verification operation and one program pressurization operation;

adjusting the time by the programming operation state machine according to the cycle number;

according to the adjusted time, the programming pressurization operation corresponding to the cycle number of the time is completed through the programming operation state machine;

after the program operation state machine completes the program pressurizing operation corresponding to the current cycle number, the program cycle number detection unit adds one to the cycle number, and the program operation state machine continues to execute the program verifying operation corresponding to the next cycle number.

Optionally, adjusting the time by the programming operation state machine according to the number of cycles includes:

the NOR flash memory calls a relation table of a cycle number section and the generation frequency of the clock frequency generator, wherein the higher the cycle number, the slower the generation frequency of the clock frequency generator corresponding to the section;

the NOR flash memory adjusts the generation frequency of the clock frequency generator according to the cycle times and the relation table;

and adjusting the time through the programming operation state machine according to the adjusted generation frequency of the clock frequency generator.

Optionally, the adjusting, by the NOR flash memory, the generation frequency of the clock frequency generator according to the cycle count and the relation table includes:

the NOR flash memory determines a target cycle time interval to which the cycle times belong from the cycle time interval according to the cycle times;

the NOR flash memory searches a target frequency value corresponding to the target cycle time interval from the relation table;

the NOR flash memory adjusts the generation frequency of the clock frequency generator to the target frequency value.

Optionally, according to the adjusted time, the program pressurization operation corresponding to the cycle number of this time is completed by the program operation state machine, including:

judging whether the count value of the counter reaches the maximum value thereof through the programming operation state machine;

if the counter does not reach the maximum value, continuously executing the programming pressurization operation corresponding to the cycle number within the adjusted time through the programming operation state machine;

and if the counter reaches the maximum value, finishing the programming pressurization operation corresponding to the cycle number by the programming operation state machine.

Optionally, after the program operation state machine completes the program pressing operation corresponding to the current cycle count, the program cycle count detecting unit adds one to the cycle count, and the program operation state machine continues to perform the program verifying operation corresponding to the next cycle count, including:

after the programming pressurization operation corresponding to the cycle number of the current time is finished through the programming operation state machine, the programming operation state machine judges whether the cycle number reaches a first preset value or not;

if the cycle number reaches the first preset value, ending the programming operation corresponding to the programming operation instruction through the programming operation state machine;

and if the cycle times do not reach the first preset value, continuing to execute the program verification operation corresponding to the next cycle time through the program operation state machine.

An embodiment of the present invention further provides a device for controlling programming performance, which is applied to a NOR flash memory, and the NOR flash memory includes: the device comprises a programming cycle number detection unit, a programming operation state machine, a clock frequency generator and a programming storage unit, wherein the programming operation state machine comprises: a counter, the programming cycle number detection unit connected to the clock frequency generator, the programming operation state machine respectively connected to the clock frequency generator and the programming storage unit, the apparatus comprising:

a first receiving module, configured to receive, through the program operation state machine, a program operation instruction and data to be programmed, where the data to be programmed is data that needs to be written into the program storage unit;

the verification module is used for executing programming verification operation through the programming operation state machine according to the programming operation instruction and the data to be programmed, wherein the programming verification operation is the operation of verifying whether the data to be programmed is consistent with the data stored in the programming storage unit, if so, the verification is passed, and if not, the verification is not passed;

an execution module, configured to execute a program voltage application operation by the program operation state machine if the verification fails, where the program voltage application operation is an operation of continuously applying a preset voltage value to the program storage unit, and a time of continuously applying the preset voltage value is a product of a maximum value of the counter and a period of the clock frequency generator;

a number-of-times addition execution module, configured to add one to the cycle number by the programming cycle number detection unit after the programming operation state machine completes the programming pressurization operation corresponding to the current cycle number, and the programming operation state machine continues to execute the program verification operation corresponding to the next cycle number;

wherein, the execution module includes:

a second receiving module, configured to receive, by the NOR flash memory, the number of cycles of program verify and program pressurization sent by the program cycle number detecting unit, where the number of cycles is a number of times that the program verify operation and the program pressurization operation need to be performed to complete a program operation corresponding to the program operation instruction, and each cycle corresponds to one program verify operation and one program pressurization operation;

the adjusting module is used for adjusting the time through the programming operation state machine according to the cycle times;

and the completion module is used for completing the programming pressurization operation corresponding to the circulation times according to the adjusted time through the programming operation state machine.

Optionally, the adjusting module includes:

a calling relation table submodule for calling a relation table of a cycle number block and the generation frequency of the clock frequency generator by the NOR flash memory, wherein the higher the cycle number is, the slower the generation frequency of the clock frequency generator corresponding to the block is;

the frequency adjusting submodule is used for adjusting the generation frequency of the clock frequency generator by the NOR flash memory according to the cycle times and the relation table;

and the time adjusting submodule is used for adjusting the time through the programming operation state machine according to the adjusted generation frequency of the clock frequency generator.

Optionally, the adjusting frequency sub-module includes:

a determination interval slave sub-module, configured to determine, by the NOR flash memory, a target cycle number section to which the cycle number belongs from the cycle number section according to the cycle number;

the searching target slave submodule is used for searching a target frequency value corresponding to the target cycle time interval from the relation table by the NOR flash memory;

and the adjusting frequency slave submodule is used for adjusting the generating frequency of the clock frequency generator to the target frequency value by the NOR flash memory.

Optionally, the completion module includes:

the judging submodule is used for judging whether the counting value of the counter reaches the maximum value through the programming operation state machine;

the continuous execution submodule is used for continuously executing the programming pressurization operation corresponding to the cycle number within the adjusted time through the programming operation state machine if the counter does not reach the maximum value;

and the completion submodule is used for finishing the programming pressurization operation corresponding to the cycle time if the counter reaches the maximum value of the counter through the programming operation state machine.

Optionally, the number-of-times adding execution module includes:

the judgment time submodule is used for judging whether the cycle time reaches a first preset value or not by the programming operation state machine after the programming pressurization operation corresponding to the cycle time of the current time is finished by the programming operation state machine;

the ending submodule is used for ending the programming operation corresponding to the programming operation instruction through the programming operation state machine if the cycle times reach the first preset value;

and the adding times executing submodule is used for continuously executing the programming verification operation corresponding to the next cycle time through the programming operation state machine if the cycle time does not reach the first preset value.

Compared with the prior art, the method and the device for controlling the programming performance provided by the invention have the advantages that when the programming pressurization operation is executed, the programming operation state machine adjusts the time of the single programming pressurization operation according to the cycle times of the programming verification and the programming pressurization sent by the programming cycle time detection unit, completes the programming pressurization operation, controls the cycle periods of the programming verification operation and the programming pressurization operation, and improves the programming performance of the NOR flash memory.

Drawings

In order to more clearly illustrate the technical solutions of the embodiments of the present invention, the drawings needed to be used in the description of the embodiments of the present invention will be briefly introduced below, and it is obvious that the drawings in the following description are only some embodiments of the present invention, and it is obvious for those skilled in the art that other drawings can be obtained according to these drawings without inventive labor.

FIG. 1 is a schematic diagram of a conventional NOR flash memory programming principle;

FIG. 2 is a flow chart of a method of controlling programming performance in accordance with an embodiment of the present invention;

FIG. 3 is a flowchart detailing step 103 of an embodiment of the present invention;

FIG. 4 is a flowchart illustrating step 103b according to an embodiment of the present invention;

FIG. 5 is a flowchart detailing step 103b2 according to an embodiment of the present invention;

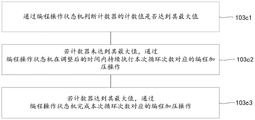

FIG. 6 is a flowchart detailing step 103c of the method according to the present invention;

FIG. 7 is a flowchart illustrating step 103d according to an embodiment of the present invention

Fig. 8 is a schematic diagram of an apparatus of an embodiment of the invention.

Detailed Description

The technical solutions in the embodiments of the present invention will be clearly and completely described below with reference to the drawings in the embodiments of the present invention, and it is obvious that the described embodiments are some, not all, embodiments of the present invention. All other embodiments, which can be derived by a person skilled in the art from the embodiments given herein without making any creative effort, shall fall within the protection scope of the present invention.

FIG. 2 is a flow chart illustrating a method of controlling programming performance in accordance with an embodiment of the present invention. The method is applied to a NOR flash memory, and the NOR flash memory comprises the following steps: the device comprises a programming cycle number detection unit, a clock frequency generator, a programming operation state machine and a programming storage unit, wherein the programming operation state machine comprises: the counter, the programming cycle number detecting unit is connected with the clock frequency generator, the programming operation state machine is respectively connected with the clock frequency generator and the programming storage unit, and the method for controlling the programming performance comprises the following steps:

step 101: and receiving a programming operation instruction and data to be programmed through a programming operation state machine, wherein the data to be programmed is data required to be written into a programming storage unit.

In an embodiment of the present invention, a NOR flash memory includes: the device comprises a programming cycle number detection unit, a clock frequency generator, a programming operation state machine and a programming storage unit, wherein the programming cycle number detection unit is used for: the program loop number detection unit sends the loop number to the NOR flash memory, and the program operation state machine is an element for controlling the program state in the NOR flash memory and comprises: a counter. The clock frequency generator (CLK generator) is the generator generating time period in the programming operation state machine, the counter is the element counted in the programming operation state machine, and the two are combined to control the time of each programming pressurization operation of the programming operation state machine, and the programming storage unit is the storage unit storing the written data in the NOR flash memory.

The program operation state machine receives a program operation instruction and data to be programmed which are sent by a host computer, wherein the data to be programmed are data which are required to be written into a program storage unit in the program operation, the program operation instruction may include an address of the program storage unit, namely the program storage unit which is required to write the data to be programmed into a specified address, the program operation is realized by the program operation state machine from the whole process of receiving the program operation instruction and the data to be programmed and correctly writing the data to be programmed into the program storage unit, namely the process of completing the whole program operation by the NOR flash memory, the time for controlling the program pressurization operation is realized by the frequency of CLK and the maximum value of a counter, the change of the frequency of CLK is realized by a relation table of the NOR flash memory according to the cycle number section and the generation frequency of the clock frequency generator, and a specific operating temperature. The above description is not limited in detail by the embodiments of the present invention, and the embodiments may be set according to actual situations.

Step 102: and executing a program verification operation through a program operation state machine according to the program operation instruction and the data to be programmed, wherein the program verification operation is an operation for verifying whether the data to be programmed is consistent with the data stored in the program storage unit, if so, the verification is passed, and if not, the verification is not passed.

In the embodiment of the invention, after receiving the programming operation instruction and the data to be programmed, the programming operation state machine firstly executes a programming verification operation to verify whether the data to be programmed is consistent with the data stored in the programming storage unit, so that the programming verification operation is executed because the situation that the data to be programmed is already in the programming storage unit possibly exists, if the data to be programmed is already in the programming storage unit, the programming is considered to be successful, and the programming operation state machine finishes the programming operation. Before the program-pressing operation is performed, the program operation state machine needs to perform a program verification operation on the data to be programmed and the stored data of the programmed memory cell, and if the data to be programmed and the stored data of the programmed memory cell are inconsistent, the verification is not passed, and the program-pressing operation is performed. The embodiment of the present invention is not limited in detail, and may be set according to actual situations.

Step 103: if the verification fails, executing a program voltage operation by the program operation state machine, wherein the program voltage operation is an operation of continuously applying a preset voltage value to the program memory cell, and the time of continuously applying the preset voltage value is the product of the maximum value of the counter and the period of the clock frequency generator.

In the embodiment of the present invention, if the program verification fails, the program operation state machine performs a program pressing operation, where the program pressing operation refers to: the program operation state machine continuously applies the preset voltage value to the program storage unit, the time of continuously applying the preset voltage value is the time of the program pressurization operation, the time of the program pressurization operation is the product of the maximum value of the counter and the period of the clock frequency generator, the maximum value of the counter is 100, the generation frequency of the CLK generator is 50 Hz, the period of the CLK generator is 0.02 s, the time of the single program pressurization operation is 0.02 100 s to 2 s, the maximum value of the counter is set by the program operation state machine, the counting rule of the counter is determined by a pulse signal sent by the CLK generator, the counting of the counter is increased by 1 when the pulse signal sent by the CLK generator appears every time, the counting of the counter is cleared and restarted after 100 rising edges, the preset voltage value is the voltage value which is required by the NOR flash memory to finish the program operation under the ordinary condition, the value is obtained by combining a large number of simulation tests, actual tests, empirical formula calculation and the like. The embodiment of the present invention is not limited in detail, and may be set according to actual situations.

Referring to fig. 3, the step of performing the program pressing operation by the program operation state machine specifically includes the following steps:

step 103 a: the NOR flash memory receives the program verification and program pressurization cycle times sent by the program cycle time detection unit, the cycle times are the times for executing the program verification operation and the program pressurization operation when the program operation corresponding to the program operation instruction is completed, and each cycle time corresponds to one program verification operation and one program pressurization operation.

In the embodiment of the invention, a programming cycle number detection unit sends detected cycle numbers of programming verification and programming pressurization to a NOR flash memory, the NOR flash memory firstly executes programming verification operation in the process of executing programming operation, if the verification is not passed, the first programming pressurization operation is executed, and when the first programming pressurization operation is finished, the first programming cycle is the first programming cycle, and the programming cycle refers to: the program operation state machine executes a first program verifying operation, if the program operation state machine does not pass the verifying operation, a first program pressurizing operation is executed, the program pressurizing operation is a first program loop when the program pressurizing operation is finished, the two steps are completed, the first program verifying operation is executed, the program verifying operation loop number is 1, the first program pressurizing operation is executed, the program pressurizing operation loop number is 1, the whole loop number is 1, and the program loop number detecting unit records the program verifying and program pressurizing loop number as 1. After the first programming pressing operation is finished, the programming operation state machine executes the programming verification operation for the second time, if the verification is not passed, the second programming pressing operation is executed, when the second programming pressing operation is finished, namely a second programming cycle, the second programming verification operation is executed, the cycle number of the programming verification operation is 2, the second programming pressing operation is executed, the cycle number of the programming pressing operation is 2, the whole cycle number is 2, and the programming cycle number detection unit records the cycle number of the programming verification and the programming pressing as 1. After the second program pressing operation is finished, the program operation state machine executes third program verifying operation, if the program operation does not pass the verifying, the third program pressing operation is executed, when the third program pressing operation is finished, namely a third program loop, the third program verifying operation is executed, the program verifying operation loop frequency is 3, the third program pressing operation is executed, the program pressing operation loop frequency is 3, the whole loop frequency is 3, and the program loop frequency detecting unit records the program verifying and program pressing loop frequency as 1. And so on, each cycle corresponds to one program verify operation and one program pressure operation. The embodiment of the present invention is not limited in detail, and may be set according to actual situations.

Step 103 b: the time is adjusted by programming the operating state machine according to the number of cycles.

In the embodiment of the invention, after the NOR flash memory receives the cycle times sent by the programming cycle time detection unit, the continuous pressurization time is adjusted through programming pressurization operation according to the cycle times. The embodiment of the present invention is not limited in detail, and may be set according to actual situations.

Alternatively, referring to fig. 4, step 103b comprises:

In the embodiment of the invention, when the programming operation state machine executes the programming pressurization operation, the NOR flash memory calls a relation table of the cycle number section and the generation frequency of the clock frequency generator, the table is a corresponding relation table of the cycle number section and the generation frequency of the CLK generator in the programming operation process of the NOR flash memory, the corresponding relation table is also obtained by combining a large number of simulation tests, actual tests, empirical formula calculation and the like, the lower the frequency of the clock frequency generator corresponding to the cycle number section with higher cycle number is, for example, in the section of the cycle number of 0-10000, the generation frequency of the CLK generator is 40 Hz, in the section of the cycle number of 10001-50000, the generation frequency of the CLK generator is 25 Hz, in the section of the cycle number of 50001-100000, the generation frequency of the CLK generator is 20 Hz, in the section of the cycle number of 100001-200000, the generation frequency of the CLK generator is 10 hz, and the generation frequency of the CLK generator is 5 hz in the period above 200000 cycles, and it should be noted that the above data are only numbers listed for better explaining the embodiments of the present invention, and do not represent specific numbers in practical applications. The embodiment of the present invention is not limited in detail, and may be set according to actual situations.

Step 103b 2: the NOR flash memory adjusts the generation frequency of the clock frequency generator according to the cycle number and the relation table.

In the embodiment of the invention, the NOR flash memory adjusts the generation frequency of the CLK generator according to the relation table of the cycle number interval and the generation frequency of the CLK generator, for example, when the cycle number is 12000, the generation frequency of the corresponding CLK generator in the corresponding relation table is 25 Hz. The embodiment of the present invention is not limited in detail, and may be set according to actual situations.

Alternatively, referring to fig. 5, step 103b2 includes:

103b 21: and the NOR flash memory determines a target cycle number section to which the cycle number belongs from the cycle number sections according to the cycle number.

In the embodiment of the invention, when the program operation state machine executes the program pressurization operation, the NOR flash memory determines the target cycle number section to which the cycle number belongs from the cycle number sections according to the cycle number, for example, if the current cycle number is 60000, the target cycle number section to which the cycle number belongs is the cycle number sections 50001 to 100000, and if the current cycle number is 180000, the target cycle number section to which the cycle number belongs is the cycle number sections 100001 to 200000. The embodiment of the present invention is not limited in detail, and may be set according to actual situations.

103b 22: the NOR flash memory looks up the target frequency value corresponding to the target cycle number interval from the relational table.

In the embodiment of the invention, after the target cycle number interval is determined, the NOR flash memory searches a target frequency value corresponding to the target cycle number interval from the relation table, for example, the target cycle number 50001 to 100000 interval, the target frequency value corresponding to the CLK generator is 20 hz, the target cycle number is 100001 to 200000 interval, and the target frequency value corresponding to the CLK generator is 10 hz. The embodiment of the present invention is not limited in detail, and may be set according to actual situations.

103b 23: the NOR flash memory adjusts the generation frequency of the clock frequency generator to a target frequency value.

In the embodiment of the invention, after the target frequency value of the CLK generator is determined, the NOR flash memory can adjust the generation frequency of the CLK generator in the current pressurizing operation to the target frequency value. The embodiment of the present invention is not limited in detail, and may be set according to actual situations.

Step 103b 3: and adjusting the time by programming the operating state machine according to the adjusted generation frequency of the clock frequency generator.

In the embodiment of the invention, after the NOR flash memory adjusts the generation frequency of the clock frequency generator, the maximum value of the counter is not changed, and the time of the program pressing operation is changed by the program operation state machine, namely, the time of the program pressing operation is adjusted by the program operation state machine.

Step 103 c: and according to the adjusted time, finishing the programming pressurization operation corresponding to the cycle number by the programming operation state machine.

In the embodiment of the invention, the NOR flash memory adjusts the generation frequency of the CLK generator, so that the duration of the current programming pressurization operation is adjusted, and the programming operation state machine executes the programming pressurization operation corresponding to the current cycle number according to the adjusted time. The embodiment of the present invention is not limited in detail, and may be set according to actual situations.

Optionally, referring to fig. 6, step 103c may specifically include:

In the embodiment of the present invention, during a single program pressing operation, the program operation state machine needs to determine whether the count value of the counter reaches its maximum value, because the maximum value of the counter is already set when the program operation state machine leaves the factory, for example, the maximum value is one hundred thousand, and then the program operation state machine determines whether the count value of the counter reaches one hundred thousand during each program pressing operation. The embodiment of the present invention is not limited in detail, and may be set according to actual situations.

Step 103c 2: and if the counter does not reach the maximum value, continuously executing the programming pressurization operation corresponding to the current cycle number within the adjusted time through the programming operation state machine.

In the embodiment of the present invention, if the program operation state machine determines that the counter has not reached its maximum value, assuming that the maximum value is one hundred thousand, and the counter counts to sixty thousand at this time, the program operation state machine continues to perform the program pressurization operation corresponding to the current cycle number until the counter counts to one hundred thousand. For example: when the counter counts to a maximum value of 100 and the generation frequency of the CLK generator is 25 Hz, the period of the CLK generator is 0.04 s, and the adjusted program pressurization operation time is 0.04 x 100 to 4(s); the generation frequency of the CLK generator is 20 Hz, the period of the CLK generator is 0.05 s, and the adjusted programming pressurization operation time is 0.05 x 100 to 5(s); the generation frequency of the CLK generator is 10 hz, the period of the CLK generator is 0.1 sec, and the adjusted program pressing operation time is 0.1 × 100 — 10 (sec). The embodiment of the present invention is not limited in detail, and may be set according to actual situations.

Step 103c 3: and if the counter reaches the maximum value, finishing the programming pressurization operation corresponding to the current cycle number through the programming operation state machine.

In the embodiment of the invention, when the counting of the counter reaches the maximum value, the programming operation state machine ends the programming pressurization operation, namely ends the programming pressurization operation corresponding to the cycle time, executes the programming verification operation of the next cycle time, verifies whether the data stored in the programming storage unit is consistent with the data to be programmed after the programming pressurization operation corresponding to the cycle time, if so, the verification is passed, if not, the verification is not passed, and the programming pressurization operation corresponding to the next cycle time needs to be executed. The embodiment of the present invention is not limited in detail, and may be set according to actual situations.

Step 103 d: after the program operation state machine completes the program pressurizing operation corresponding to the cycle number of the current time, the program cycle number detection unit adds one to the cycle number, and the program operation state machine continues to execute the program verifying operation corresponding to the next cycle number.

In the embodiment of the present invention, after the program operation state machine completes the program pressing operation corresponding to the current cycle count, that is, after completing one program verifying operation and one program pressing operation, the program cycle count detecting unit increases the cycle count by one, and the program operation state machine continues to execute the program verifying operation corresponding to the next cycle count. The embodiment of the present invention is not limited in detail, and may be set according to actual situations.

Optionally, referring to fig. 7, step 103d specifically includes:

step 103d 1: after the programming pressurization operation corresponding to the cycle number of the current time is finished through the programming operation state machine, the programming operation state machine judges whether the cycle number reaches a first preset value or not;

in the embodiment of the present invention, when the counter reaches its maximum value, the program operation state machine will end the program pressurizing operation corresponding to the current cycle number, execute the program verifying operation corresponding to the next cycle number, before the program verify operation of the next cycle count is performed, the program operation state machine first determines whether the cycle count reaches a first preset value, the first preset value is an upper limit value set by a user, the upper limit value is set to enable the NOR flash memory to operate more efficiently, assuming one-time program operation, for various reasons, data to be programmed cannot be written into the programmed memory cells, if there is no upper limit of the cycle number, the program operation state machine needs to perform the program verify operation and the program pressurizing operation endlessly, the NOR flash memory is always in a program operation state, which is equivalent to a dead halt and cannot process any other work. And when the program verification operation corresponding to the next cycle number is executed, if the verification is passed, the data required by the current program operation and written into the program storage unit is completely consistent with the data to be programmed, and the program operation state machine finishes the program operation corresponding to the program operation instruction, namely the current program operation. If the verification fails, the program operation state machine needs to execute the program verification operation and the program pressurization operation corresponding to the next cycle number. The embodiment of the present invention is not limited in detail, and may be set according to actual situations.

Step 103d 2: if the cycle times reach a first preset value, finishing the programming operation corresponding to the programming operation instruction through a programming operation state machine;

in the embodiment of the present invention, if the cycle count reaches the first predetermined value, for example, the first predetermined value is sixty-ten thousand times, the number of cycles is at most sixty thousand cycles and when this value is reached, the program operation state machine will not perform the program verify operation and the program stress operation any more, if the program verify operation passes during the sixty thousand cycles, i.e., the data to be programmed is consistent with the data stored in the programmed memory cell, the programming operation is finished, and the program operation is successful, if the program verify operation fails during the sixty-ten thousand cycles, i.e., the data to be programmed and the data stored in the programmed memory cells are inconsistent, the program operation state machine needs to perform sixty-one-ten-thousand cycles, but the number of cycles has reached a predetermined value, so the program operation is also ended, but the program operation fails, and the data to be programmed is not successfully written into the programmed memory cells. The embodiment of the present invention is not limited in detail, and may be set according to actual situations.

Step 103d 3: and if the cycle times do not reach the first preset value, continuously executing the program verification operation corresponding to the next cycle times through the program operation state machine.

In the embodiment of the present invention, if the cycle count does not reach the first preset value, and if the cycle count does not reach sixty thousand, the program operation state machine will execute the program verification operation corresponding to the next cycle count. The embodiment of the present invention is not limited in detail, and may be set according to actual situations.

Referring to fig. 8, which shows a device schematic diagram of an embodiment of the present invention, a NOR flash memory includes: the device comprises a programming cycle number detection unit, a clock frequency generator, a programming operation state machine and a programming storage unit, wherein the programming operation state machine comprises: the counter is connected with the clock frequency generator, the programming operation state machine is respectively connected with the clock frequency generator and the programming storage unit, the programming operation state machine receives a programming operation instruction and data to be programmed sent by the upper computer, the programming operation instruction possibly comprises an address of the programming storage unit, namely the data to be programmed needs to be written into the programming storage unit with a specified address, before the programming pressurization operation is executed, the programming operation state machine firstly executes a programming verification operation to verify whether the data stored in the programming storage unit with the corresponding address is consistent with the data to be programmed, if so, the programming operation is finished, and the programming operation is successful; if not, the program operation state machine will perform a program press operation.

Assuming that the program operation is executed at a voltage of 2.0V, the program operation state machine receives a program command and data to be programmed, and executes a first program verifying operation, but the first program verifying operation is not passed, the program operation state machine executes a first program pressurizing operation, the NOR flash memory receives the cycle times sent by the program cycle time detection unit, the relationship table is called, since the program verifying and program pressurizing operations are executed for the first time, the cycle times are 0 at this time, the cycle times 0 in the cycle times section are determined to belong to the cycle times 0-10000 section, the generation frequency of the corresponding CLK generator is 40 Hz, the NOR flash memory adjusts the generation frequency of the CLK generator during the first program pressurizing operation to 40 Hz, the cycle time of the CLK generator is 0.025 sec, and the maximum value of the counter is 100, the time of the first program pressurizing operation is 2.5 sec, namely, the program operation state machine continuously pressurizes 2.0V for 2.5 seconds to write the data to be programmed into the program memory cells of the corresponding address, the program pressurizing operation is finished after 2.5 seconds, and the program verifying operation corresponding to the next cycle number is ready to be executed, wherein the cycle number of the program pressurizing operation is 1, the cycle number of the program verifying operation is 1, and the cycle number is 1.

Before executing the second program verifying operation, the program operation state machine firstly judges whether the cycle number reaches the upper limit value, if not, the second program verifying operation is executed. If the second program verifying operation is not verified, the second program pressurizing operation is required to be executed at the moment, the NOR flash memory receives the loop times sent by the program loop time detection unit, the relation table is called, the loop times are 1, the loop times 1 in the loop time section belong to the section of the loop times 0-10000, the generation frequency of the corresponding CLK generator is 40 Hz, the NOR flash memory does not adjust the generation frequency of the CLK generator in the second program pressurizing operation process, the period of the CLK generator is still 0.025 sec, the time of the second program pressurizing operation is 2.5 sec because the maximum value of the counter is 100, namely the program operation state machine continuously pressurizes 2.5 sec by 2.0V voltage to write the data to be programmed into the program storage unit of the corresponding address, the program pressurizing operation is finished after 2.5 sec, and the program verifying operation corresponding to the next loop time is prepared to be executed, the number of program press operation cycles at this time is 2, the number of program verify operation cycles is 2, and the number of program verify operation cycles is 2.

Assuming that the cycle count reaches 10001 times, before executing the program verify operation of the 10002 times, the program operation state machine first determines whether the cycle count reaches the upper limit, and if not, executes the program verify operation of the 10002 times. If the 10002 program verify operation fails, at which time the 10002 program pump operation is required, the NOR flash memory receives the cycle count sent by the program cycle count detection unit, calls the relationship table, at which the cycle count is 10001, determines that the cycle count 10001 belongs to the cycle count sections of 10001-50000 sections, and the generation frequency of the CLK generator is 25 hz, the NOR flash memory adjusts the generation frequency of the CLK generator during the 10002 program pump operation to 25 hz (i.e. the generation frequency of the CLK generator for the program pump operation is adjusted to 25 hz), the cycle of the CLK generator is 0.04 s, and since the maximum value of the counter is 100, the 10002 program pump operation lasts for 4 s, that is, the program operation state machine continues to pump the data to be programmed into the program storage unit corresponding to the address by pressurizing for 4 s at 2.0V, after 4 seconds, the program-pressure operation is finished, and a program-verify operation corresponding to the next cycle number is ready to be executed, where the cycle number of the program-pressure operation is 10002, the cycle number of the program-verify operation is 10002, and the cycle number is 10002.

Before executing the 10003 program verify operations, the program operation state machine first determines whether the loop times reach the upper limit value, and if not, executes the 10003 program verify operations. If the program verification operation of the 10003 th time passes, that is, the data stored in the program storage unit of the corresponding address is consistent with the data to be programmed, the program operation is ended, and the programming is successful.

If the upper limit of the cycle number of the program pressurization operation is 10003 times in the above process, the program operation state machine firstly judges that the cycle number reaches the upper limit value, the program operation state machine will end the program operation, and after the 10003-time program pressurization operation, if the data stored in the program storage unit corresponding to the address is consistent with the data to be programmed, the program operation is successful; and if the data stored in the programming storage unit corresponding to the address is inconsistent with the data to be programmed, the programming operation fails.

An embodiment of the present invention further provides a device for controlling programming performance, which is applied to a NOR flash memory, where the NOR flash memory includes: the device comprises a programming cycle number detection unit, a programming operation state machine, a clock frequency generator and a programming storage unit, wherein the programming operation state machine comprises: the counter, the programming cycle number detecting unit is connected with clock frequency generator, the programming operation state machine is connected with clock frequency generator and programming memory cell separately, the device for controlling programming performance includes:

a first receiving module, configured to receive, through the program operation state machine, a program operation instruction and data to be programmed, where the data to be programmed is data that needs to be written into the program storage unit;

a verification module, configured to perform a program verification operation through the program operation state machine according to the program operation instruction and the data to be programmed, where the program verification operation is an operation of verifying whether the data to be programmed is consistent with data stored in the program storage unit, and if so, passing the verification, and if not, failing the verification;

an execution module, configured to execute a program voltage application operation by the program operation state machine if the verification fails, where the program voltage application operation is an operation of continuously applying a preset voltage value to the program storage unit, and a time of continuously applying the preset voltage value is a product of a maximum value of the counter and a period of the clock frequency generator;

the number adding execution module is used for adding one to the cycle number by the programming cycle number detection unit after the programming pressurization operation corresponding to the cycle number of the current time is finished by the programming operation state machine, and the programming operation state machine continues to execute the programming verification operation corresponding to the next cycle number;

wherein, the execution module includes:

a second receiving module, configured to receive, by the NOR flash memory, the program verify and program pressurization cycle times sent by the program cycle time detecting unit, where the cycle times are times required to execute the program verify operation and the program pressurization operation for completing the program operation corresponding to the program operation instruction, and each cycle time corresponds to one program verify operation and one program pressurization operation;

the adjusting module is used for adjusting the time through the programming operation state machine according to the cycle times;

and the completion module is used for completing the programming pressurization operation corresponding to the circulation times according to the adjusted time through the programming operation state machine.

Optionally, the adjusting module comprises:

a calling relation table submodule for calling a relation table of a cycle number block and the generation frequency of the clock frequency generator by the NOR flash memory, wherein the higher the cycle number is, the slower the generation frequency of the clock frequency generator corresponding to the block is;

the frequency adjusting submodule is used for adjusting the generation frequency of the clock frequency generator by the NOR flash memory according to the cycle number and the relation table;

and the time adjusting submodule is used for adjusting the time through the programming operation state machine according to the adjusted generation frequency of the clock frequency generator.

Optionally, the adjusting frequency sub-module includes:

a determination interval slave submodule, configured to determine, by the NOR flash memory, a target cycle number segment to which the cycle number belongs from the cycle number segment according to the cycle number;

a target slave submodule is searched for, and the NOR flash memory searches for a target frequency value corresponding to a target cycle number interval from the relation table;

and the frequency-adjusting slave sub-module is used for adjusting the generated frequency of the clock frequency generator to the target frequency value by the NOR flash memory.

Optionally, the completion module comprises:

the judging submodule is used for judging whether the counting value of the counter reaches the maximum value through the programming operation state machine;

the continuous execution submodule is used for continuously executing the programming pressurization operation corresponding to the cycle number within the adjusted time through the programming operation state machine if the counter does not reach the maximum value;

and the completion submodule is used for finishing the programming pressurization operation corresponding to the cycle time if the counter reaches the maximum value of the counter through the programming operation state machine.

Optionally, the number-of-times adding execution module includes:

the judgment time submodule is used for judging whether the cycle time reaches a first preset value or not by the programming operation state machine after the programming pressurization operation corresponding to the cycle time of the current time is finished by the programming operation state machine;

the ending submodule is used for ending the programming operation corresponding to the programming operation instruction through the programming operation state machine if the cycle times reach the first preset value;

and the adding times executing submodule is used for continuously executing the programming verification operation corresponding to the next cycle time through the programming operation state machine if the cycle time does not reach the first preset value.

Through the embodiment, in the programming operation, the programming verification operation is executed firstly, whether the data to be programmed is consistent with the data stored in the programming storage unit or not is judged, and if the threshold voltage of the programming storage unit is greater than the verification voltage, the programming operation is directly ended; when the program and the program are inconsistent, the program operation state machine executes the program pressurizing operation, searches the corresponding cycle time interval according to the cycle times sent by the program cycle time detection unit, determines the generation frequency of the clock frequency generator in the single program pressurizing operation by using the relation table, determines the program pressurizing time according to the generation frequency of the clock frequency generator, and determines whether to execute the program verifying operation of the next cycle time according to the cycle times of the program pressurizing operation after the program pressurizing operation is finished, so that the cycle period of controlling the program verifying operation and the program pressurizing operation is achieved, and the program performance of the NOR flash memory is improved.

Finally, it should also be noted that, herein, relational terms such as first and second, and the like may be used solely to distinguish one entity or action from another entity or action without necessarily requiring or implying any actual such relationship or order between such entities or actions. Also, herein, the terms "comprises," "comprising," or any other variation thereof, are intended to cover a non-exclusive inclusion, such that a process, method, article, or apparatus that comprises a list of elements does not include only those elements but may include other elements not expressly listed or inherent to such process, method, article, or apparatus. Without further limitation, an element identified by the phrase "comprising an … …" does not exclude the presence of other identical elements in the process, method, article, or apparatus that comprises the element.

While the present invention has been described with reference to the particular illustrative embodiments, it is to be understood that the invention is not limited to the disclosed embodiments, but is intended to cover various modifications, equivalent arrangements, and equivalents thereof, which may be made by those skilled in the art without departing from the spirit and scope of the invention as defined by the appended claims.

Claims (8)

1. A method of controlling program performance, the method being applied to a NOR flash memory, the NOR flash memory comprising: the device comprises a programming cycle number detection unit, a programming operation state machine, a clock frequency generator and a programming storage unit, wherein the programming operation state machine comprises: a counter, the program cycle number detection unit being connected to the clock frequency generator, the program operation state machine being connected to the clock frequency generator and the program storage unit, respectively, the method comprising:

receiving a programming operation instruction and data to be programmed through the programming operation state machine, wherein the data to be programmed is data required to be written into the programming storage unit;

according to the programming operation instruction and the data to be programmed, executing programming verification operation through the programming operation state machine, wherein the programming verification operation is the operation of verifying whether the data to be programmed is consistent with the data stored in the programming storage unit, if so, the verification is passed, and if not, the verification is not passed;

if the verification is not passed, executing a program pressurization operation by the program operation state machine, wherein the program pressurization operation is an operation of continuously applying a preset voltage value to the program storage unit, and the time of continuously applying the preset voltage value is the product of the maximum value of the counter and the period of the clock frequency generator;

wherein performing a program stress operation by the program operation state machine includes:

the NOR flash memory receives the program verifying and program pressurizing cycle times sent by the program cycle time detecting unit, wherein the cycle times are the times of executing the program verifying operation and the program pressurizing operation when the program operation corresponding to the program operation instruction is completed, and each cycle time corresponds to one program verifying operation and one program pressurizing operation;

adjusting the time by the program operation state machine according to the cycle number, wherein the adjusting the time by the program operation state machine according to the cycle number comprises:

the NOR flash memory calls a relation table of a cycle number section and the generation frequency of the clock frequency generator, wherein the higher the cycle number, the slower the generation frequency of the clock frequency generator corresponding to the section; the NOR flash memory adjusts the generation frequency of the clock frequency generator according to the cycle times and the relation table; adjusting the time by the programming operation state machine according to the adjusted generation frequency of the clock frequency generator;

according to the adjusted time, the programming pressurization operation corresponding to the cycle number of the time is completed through the programming operation state machine;

after the program operation state machine completes the program pressurizing operation corresponding to the current cycle number, the program cycle number detection unit adds one to the cycle number, and the program operation state machine continues to execute the program verifying operation corresponding to the next cycle number.

2. The method of claim 1, wherein the NOR flash memory adjusts the generation frequency of the clock frequency generator according to the relationship between the number of cycles and the table, comprising:

the NOR flash memory determines a target cycle time interval to which the cycle time belongs from the cycle time interval according to the cycle time;

the NOR flash memory searches a target frequency value corresponding to the target cycle time interval from the relation table;

the NOR flash memory adjusts the generation frequency of the clock frequency generator to the target frequency value.

3. The method of claim 1, wherein the performing the program pressing operation corresponding to the current cycle number according to the adjusted time by the program operation state machine comprises:

judging whether the count value of the counter reaches the maximum value thereof through the programming operation state machine;

if the counter does not reach the maximum value, continuously executing the programming pressurization operation corresponding to the cycle number within the adjusted time through the programming operation state machine;

and if the counter reaches the maximum value, finishing the programming pressurization operation corresponding to the current cycle number through the programming operation state machine.

4. The method of claim 1, wherein the program cycle number detection unit increases the cycle number by one after the program pressing operation corresponding to the current cycle number is completed by the program operation state machine, and the program operation state machine continues to perform the program verifying operation corresponding to the next cycle number, and the method comprises:

after the programming pressurization operation corresponding to the cycle number of the current time is finished through the programming operation state machine, the programming operation state machine judges whether the cycle number reaches a first preset value or not;

if the cycle number reaches the first preset value, ending the programming operation corresponding to the programming operation instruction through the programming operation state machine;

and if the cycle times do not reach the first preset value, continuing to execute the program verification operation corresponding to the next cycle time through the program operation state machine.

5. An apparatus for controlling program performance, the apparatus being applied to a NOR flash memory, the NOR flash memory comprising: the device comprises a programming cycle number detection unit, a programming operation state machine, a clock frequency generator and a programming storage unit, wherein the programming operation state machine comprises: a counter, the programming cycle number detection unit connected to the clock frequency generator, the programming operation state machine respectively connected to the clock frequency generator and the programming storage unit, the apparatus comprising:

a first receiving module, configured to receive, through the program operation state machine, a program operation instruction and data to be programmed, where the data to be programmed is data that needs to be written into the program storage unit;

the verification module is used for executing programming verification operation through the programming operation state machine according to the programming operation instruction and the data to be programmed, wherein the programming verification operation is the operation of verifying whether the data to be programmed is consistent with the data stored in the programming storage unit, if so, the verification is passed, and if not, the verification is not passed;

an execution module, configured to execute a program voltage application operation through the program operation state machine if the verification fails, where the program voltage application operation is an operation of continuously applying a preset voltage value to the program memory cell, and a time of continuously applying the preset voltage value is a product of a maximum value of the counter and a period of the clock frequency generator;

a number-of-times addition execution module, configured to add one to the cycle number by the programming cycle number detection unit after the programming operation state machine completes the programming pressurization operation corresponding to the current cycle number, and the programming operation state machine continues to execute the program verification operation corresponding to the next cycle number;

wherein, the execution module includes:

a second receiving module, configured to receive, by the NOR flash memory, the program verify and program pressurization cycle times sent by the program cycle time detecting unit, where the cycle times are times required to execute the program verify operation and the program pressurization operation for completing the program operation corresponding to the program operation instruction, and each cycle time corresponds to one program verify operation and one program pressurization operation;

the adjusting module is used for adjusting the time through the programming operation state machine according to the cycle times;

wherein the adjusting module comprises:

a calling relation table submodule for calling a relation table of the cycle number section and the generation frequency of the clock frequency generator by the NOR flash memory, wherein the generation frequency of the clock frequency generator corresponding to the section with higher cycle number is slower;

the frequency adjusting submodule is used for adjusting the generation frequency of the clock frequency generator by the NOR flash memory according to the cycle times and the relation table;

the time adjusting submodule is used for adjusting the time through the programming operation state machine according to the adjusted generation frequency of the clock frequency generator;

and the completion module is used for completing the programming pressurization operation corresponding to the circulation times according to the adjusted time through the programming operation state machine.

6. The apparatus of claim 5, wherein the adjust frequency sub-module comprises:

a determination interval slave submodule, configured to determine, by the NOR flash memory, a target cycle number segment to which the cycle number belongs from the cycle number segment according to the cycle number;

a target slave submodule is searched for, and the NOR flash memory searches for a target frequency value corresponding to a target cycle number interval from the relation table;

and the adjusting frequency slave submodule is used for adjusting the generating frequency of the clock frequency generator to the target frequency value by the NOR flash memory.

7. The apparatus of claim 5, wherein the completion module comprises:

the judging submodule is used for judging whether the counting value of the counter reaches the maximum value through the programming operation state machine;

the continuous execution submodule is used for continuously executing the programming pressurization operation corresponding to the current cycle number within the adjusted time through the programming operation state machine if the counter does not reach the maximum value;

and the completion submodule is used for finishing the programming pressurization operation corresponding to the current cycle number through the programming operation state machine if the counter reaches the maximum value.

8. The apparatus of claim 5, wherein the add times performing module comprises:

the judgment time submodule is used for judging whether the cycle time reaches a first preset value or not by the programming operation state machine after the programming pressurization operation corresponding to the cycle time of the current time is finished by the programming operation state machine;

the ending submodule is used for ending the programming operation corresponding to the programming operation instruction through the programming operation state machine if the cycle times reach the first preset value;

and the adding times execution submodule is used for continuously executing the programming verification operation corresponding to the next cycle times through the programming operation state machine if the cycle times do not reach the first preset value.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201910356967.6A CN111863085B (en) | 2019-04-29 | 2019-04-29 | Method and device for controlling programming performance |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201910356967.6A CN111863085B (en) | 2019-04-29 | 2019-04-29 | Method and device for controlling programming performance |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN111863085A CN111863085A (en) | 2020-10-30 |

| CN111863085B true CN111863085B (en) | 2022-07-26 |

Family

ID=72966280

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201910356967.6A Active CN111863085B (en) | 2019-04-29 | 2019-04-29 | Method and device for controlling programming performance |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN111863085B (en) |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1905068A (en) * | 2005-07-26 | 2007-01-31 | 三星电子株式会社 | Non-volatile memory device having improved program speed and associated programming method |

| KR20090048754A (en) * | 2007-11-12 | 2009-05-15 | 주식회사 하이닉스반도체 | Flash memory device and its programming and erasing method |

| CN104821183A (en) * | 2014-02-03 | 2015-08-05 | 爱思开海力士有限公司 | Semiconductor device |

| CN105513637A (en) * | 2014-09-26 | 2016-04-20 | 北京兆易创新科技股份有限公司 | Programming monitoring method |

| CN106920571A (en) * | 2015-12-25 | 2017-07-04 | 北京兆易创新科技股份有限公司 | A kind of programmed method of Nand Flash |

| CN106935269A (en) * | 2015-12-29 | 2017-07-07 | 北京兆易创新科技股份有限公司 | A kind of programmed method of memory cell |

| CN107919158A (en) * | 2016-10-10 | 2018-04-17 | 成都锐成芯微科技股份有限公司 | Keep the method and system of non-volatility memorizer memory cell current detection window |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20070096681A (en) * | 2006-03-27 | 2007-10-02 | 삼성전자주식회사 | Nonvolatile memory device and word line voltage control method thereof |

| JP2012027969A (en) * | 2010-07-21 | 2012-02-09 | Toshiba Corp | Nonvolatile semiconductor memory device |

-

2019

- 2019-04-29 CN CN201910356967.6A patent/CN111863085B/en active Active

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1905068A (en) * | 2005-07-26 | 2007-01-31 | 三星电子株式会社 | Non-volatile memory device having improved program speed and associated programming method |

| KR20090048754A (en) * | 2007-11-12 | 2009-05-15 | 주식회사 하이닉스반도체 | Flash memory device and its programming and erasing method |

| CN104821183A (en) * | 2014-02-03 | 2015-08-05 | 爱思开海力士有限公司 | Semiconductor device |

| CN105513637A (en) * | 2014-09-26 | 2016-04-20 | 北京兆易创新科技股份有限公司 | Programming monitoring method |

| CN106920571A (en) * | 2015-12-25 | 2017-07-04 | 北京兆易创新科技股份有限公司 | A kind of programmed method of Nand Flash |

| CN106935269A (en) * | 2015-12-29 | 2017-07-07 | 北京兆易创新科技股份有限公司 | A kind of programmed method of memory cell |

| CN107919158A (en) * | 2016-10-10 | 2018-04-17 | 成都锐成芯微科技股份有限公司 | Keep the method and system of non-volatility memorizer memory cell current detection window |

Also Published As

| Publication number | Publication date |

|---|---|

| CN111863085A (en) | 2020-10-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN104134459B (en) | non-volatile memory (NVM) with variable verify operation | |

| KR100257854B1 (en) | Method of erasing flash memory | |

| JP2002025283A (en) | Erasing method for flash memory element | |

| US7318181B2 (en) | ROM-based controller monitor in a memory device | |

| CN104008777A (en) | Erasing method of nonvolatile memory, and apparatus thereof | |

| CN101800077B (en) | Method and device for programming data of flash memory | |

| CN109273039B (en) | Erasing verification equipment and method for flash memory | |

| CN111863085B (en) | Method and device for controlling programming performance | |

| CN111863082B (en) | Method and device for controlling programming performance | |

| CN111863086B (en) | Method and device for controlling programming performance | |

| CN111863091B (en) | Method and device for controlling erasing performance | |

| CN111863094A (en) | Method and device for controlling erasing performance | |

| CN105702292B (en) | A kind of data reconstruction method and device of nonvolatile storage | |

| CN111863087B (en) | Method and device for controlling programming performance | |

| CN111863090B (en) | Method and device for controlling erasing performance | |

| CN111863092A (en) | Method and device for controlling erasing performance | |

| US6385093B1 (en) | I/O partitioning system and methodology to reduce band-to-band tunneling current during erase | |

| CN107305792B (en) | Method and device for testing memory | |

| CN111863096B (en) | Method and device for reading data of NOR flash memory | |

| CN111785316B (en) | Method, system, storage medium and terminal for overcoming erasure interference | |

| KR100571266B1 (en) | Erasing Flash Memory Cells | |

| CN109390016A (en) | The method for deleting and device of NOR type flash memory | |

| CN111951868A (en) | Method and device for controlling erasing | |

| KR100293633B1 (en) | Method for erasing flash memory device | |

| CN111863081A (en) | Method and device for controlling programming verification of NOR flash memory |

Legal Events

| Date | Code | Title | Description |