CN108258028B - 半导体结构及其形成方法 - Google Patents

半导体结构及其形成方法 Download PDFInfo

- Publication number

- CN108258028B CN108258028B CN201611239033.7A CN201611239033A CN108258028B CN 108258028 B CN108258028 B CN 108258028B CN 201611239033 A CN201611239033 A CN 201611239033A CN 108258028 B CN108258028 B CN 108258028B

- Authority

- CN

- China

- Prior art keywords

- region

- work function

- layer

- function layer

- gate dielectric

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000000034 method Methods 0.000 title claims abstract description 119

- 239000004065 semiconductor Substances 0.000 title claims abstract description 60

- 238000005530 etching Methods 0.000 claims abstract description 85

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims abstract description 64

- 229910052760 oxygen Inorganic materials 0.000 claims abstract description 64

- 239000001301 oxygen Substances 0.000 claims abstract description 64

- 238000002161 passivation Methods 0.000 claims abstract description 33

- 239000000758 substrate Substances 0.000 claims description 50

- 239000000463 material Substances 0.000 claims description 46

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 claims description 26

- 238000001039 wet etching Methods 0.000 claims description 17

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 claims description 14

- 229910052718 tin Inorganic materials 0.000 claims description 14

- 229910004166 TaN Inorganic materials 0.000 claims description 8

- 229910004200 TaSiN Inorganic materials 0.000 claims description 8

- 229910008482 TiSiN Inorganic materials 0.000 claims description 8

- QRXWMOHMRWLFEY-UHFFFAOYSA-N isoniazide Chemical compound NNC(=O)C1=CC=NC=C1 QRXWMOHMRWLFEY-UHFFFAOYSA-N 0.000 claims description 8

- 229910010038 TiAl Inorganic materials 0.000 claims description 7

- 239000003989 dielectric material Substances 0.000 claims description 7

- 239000007788 liquid Substances 0.000 claims description 6

- ITWBWJFEJCHKSN-UHFFFAOYSA-N 1,4,7-triazonane Chemical compound C1CNCCNCCN1 ITWBWJFEJCHKSN-UHFFFAOYSA-N 0.000 claims description 4

- 229910004491 TaAlN Inorganic materials 0.000 claims description 4

- 229910010037 TiAlN Inorganic materials 0.000 claims description 4

- 229910010041 TiAlC Inorganic materials 0.000 claims description 3

- 230000001590 oxidative effect Effects 0.000 claims description 3

- 239000010410 layer Substances 0.000 description 367

- 239000000243 solution Substances 0.000 description 27

- 150000002500 ions Chemical class 0.000 description 7

- 230000000694 effects Effects 0.000 description 5

- 239000011229 interlayer Substances 0.000 description 5

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 229910052751 metal Inorganic materials 0.000 description 4

- 239000002184 metal Substances 0.000 description 4

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 3

- 230000002411 adverse Effects 0.000 description 3

- 239000007864 aqueous solution Substances 0.000 description 3

- 238000000231 atomic layer deposition Methods 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 230000007547 defect Effects 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- 238000002955 isolation Methods 0.000 description 3

- 238000004519 manufacturing process Methods 0.000 description 3

- 238000005240 physical vapour deposition Methods 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- 239000010703 silicon Substances 0.000 description 3

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 229910052732 germanium Inorganic materials 0.000 description 2

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- VHUUQVKOLVNVRT-UHFFFAOYSA-N Ammonium hydroxide Chemical compound [NH4+].[OH-] VHUUQVKOLVNVRT-UHFFFAOYSA-N 0.000 description 1

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- 229910000530 Gallium indium arsenide Inorganic materials 0.000 description 1

- 229910004129 HfSiO Inorganic materials 0.000 description 1

- MCMNRKCIXSYSNV-UHFFFAOYSA-N ZrO2 Inorganic materials O=[Zr]=O MCMNRKCIXSYSNV-UHFFFAOYSA-N 0.000 description 1

- KXNLCSXBJCPWGL-UHFFFAOYSA-N [Ga].[As].[In] Chemical compound [Ga].[As].[In] KXNLCSXBJCPWGL-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 1

- 235000011114 ammonium hydroxide Nutrition 0.000 description 1

- 229910052787 antimony Inorganic materials 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- 230000009918 complex formation Effects 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 229910052593 corundum Inorganic materials 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 239000007772 electrode material Substances 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 238000000227 grinding Methods 0.000 description 1

- CJNBYAVZURUTKZ-UHFFFAOYSA-N hafnium(IV) oxide Inorganic materials O=[Hf]=O CJNBYAVZURUTKZ-UHFFFAOYSA-N 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 238000011112 process operation Methods 0.000 description 1

- 239000011241 protective layer Substances 0.000 description 1

- 230000000717 retained effect Effects 0.000 description 1

- 230000009291 secondary effect Effects 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 229910001845 yogo sapphire Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0684—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape, relative sizes or dispositions of the semiconductor regions or junctions between the regions

- H01L29/0688—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape, relative sizes or dispositions of the semiconductor regions or junctions between the regions characterised by the particular shape of a junction between semiconductor regions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Abstract

一种半导体结构及其形成方法,形成方法包括:刻蚀第一功函数层,保留位于第二P区、第一N区以及第二N区的第一功函数层;在刻蚀第一功函数层之后,在第一N区、第二N区、第一P区以及第二P区上形成第二功函数层;刻蚀去除第二N区的第二功函数层,直至暴露出所述第二N区的栅介质层;对所述第二N区的栅介质层进行氧空位钝化处理,降低所述第二N区的栅介质层内的氧空位含量;刻蚀去除所述第一N区的第二功函数层,直至暴露出所述第一N区的栅介质层;在所述第一N区和第二N区的栅介质层上、以及所述第一P区和第二P区的第二功函数层上形成第三功函数层。本发明降低了半导体结构形成工艺复杂性,节约了工艺步骤。

Description

技术领域

本发明涉及半导体制造技术领域,特别涉及一种半导体结构及其形成方法。

背景技术

集成电路尤其超大规模集成电路的主要半导体器件是金属-氧化物-半导体场效应管(MOS晶体管)。随着集成电路制作技术的不断发展,半导体器件技术节点不断减小,半导体结构的几何尺寸遵循摩尔定律不断缩小。当半导体结构尺寸减小到一定程度时,各种因为半导体结构的物理极限所带来的二级效应相继出现,半导体结构的特征尺寸按比例缩小变得越来越困难。其中,在半导体制作领域,最具挑战性的是如何解决半导体结构漏电流大的问题。半导体结构的漏电流大,主要是由传统栅介质层厚度不断减小所引起的。

当前提出的解决方法是,采用高k栅介质材料代替传统的二氧化硅栅介质材料,并使用金属作为栅电极,以避免高k材料与传统栅电极材料发生费米能级钉扎效应以及硼渗透效应。高k金属栅的引入,减小了半导体结构的漏电流。

尽管高k金属栅极的引入能够在一定程度上改善半导体结构的电学性能,但是现有技术形成的半导体结构工艺复杂。

发明内容

本发明解决的问题是提供一种半导体结构及其形成方法,在满足半导体结构对阈值电压不同需求的同时,简化工艺步骤。

为解决上述问题,本发明提供一种半导体结构的形成方法,包括:提供基底,所述基底包括用于形成第一N型器件的第一N区、用于形成第二N型器件的第二N区、用于形成第一P型器件的第一P区以及用于形成第二P型器件的第二P区,且所述第一N型器件的阈值电压小于第二N型器件的阈值电压,所述第一P型器件的阈值电压大于第二P型器件的阈值电压;在所述第一N区、第二N区、第一P区以及第二P区的基底上形成栅介质层以及位于所述栅介质层上的第一功函数层;刻蚀所述第一功函数层,保留位于所述第二P区、第一N区以及第二N区的第一功函数层;在刻蚀所述第一功函数层之后,在所述第一N区、第二N区、第一P区以及第二P区上形成第二功函数层;刻蚀去除所述第二N区的第二功函数层以及第一功函数层,直至暴露出所述第二N区的栅介质层,直至暴露出所述第二N区的栅介质层;对所述第二N区的栅介质层进行氧空位钝化处理,降低所述第二N区的栅介质层内的氧空位含量;刻蚀去除所述第一N区的第二功函数层以及第一功函数层,直至暴露出所述第一N区的栅介质层;在所述第一N区和第二N区的栅介质层上、以及所述第一P区和第二P区的第二功函数层上形成第三功函数层。

可选的,采用湿法刻蚀工艺,刻蚀去除所述第二N区的第二功函数层,直至暴露出所述第二N区的栅介质层,且所述湿法刻蚀工艺的刻蚀液体具有氧化性。

可选的,所述湿法刻蚀工艺包括主刻蚀工艺以及过刻蚀工艺,其中,利用所述过刻蚀工艺进行所述氧空位钝化处理。

可选的,所述湿法刻蚀工艺采用的刻蚀液体为SC1溶液、SC2溶液或者SPM溶液。

可选的,所述过刻蚀工艺的刻蚀时长为10s~2min。

可选的,采用含有过氧化氢的处理溶液,进行所述氧空位钝化处理。

可选的,所述处理溶液中,过氧化氢质量浓度为5%~20%,处理溶液温度为20℃~50℃。

可选的,所述处理溶液为SC1溶液、SC2溶液或者SPM溶液。

可选的,先进行所述氧空位钝化处理,后刻蚀去除所述第一N区的第二功函数层以及第一功函数层。

可选的,所述栅介质层的材料为高k栅介质材料。

可选的,在形成所述栅介质层之前,还在所述第一N区、第二N区、第一P区以及第二P区的基底上形成界面层。

可选的,所述第一功函数层的材料、第二功函数层以及第三功函数层的材料均为P型功函数材料。

可选的,所述P型功函数材料包括Ta、TiN、TaN、TaSiN或TiSiN中的一种或几种。

可选的,还包括步骤:在所述第一N区、第二N区、第一P区和第二P区的第三功函数层上形成N型功函数层,且所述N型功函数层的材料功函数类型与所述第三功函数层的材料功函数类型不同;在所述N型功函数层上形成栅电极层。

可选的,所述N型功函数层的材料为TiAl、TiAlC、TaAlN、TiAlN、TaCN和AlN中的一种或几种。

可选的,刻蚀所述第一功函数层的工艺步骤包括:在所述第一N区、第二N区和第二P区的第一功函数层上形成第一图形层;以所述第一图形层为掩膜,刻蚀去除位于所述第一P区的第一功函数层;去除所述第一图形层。

可选的,刻蚀去除所述第一N区的第二功函数层以及第一功函数层的工艺步骤包括:在所述第二N区的栅介质层上、以及所述第一P区和第二P区的第二功函数层上形成第二图形层;以所述第二图形层为掩膜,刻蚀去除所述第一N区的第二功函数层以及第一功函数层;去除所述第二图形层。本发明还提供一种半导体结构,包括:基底,所述基底包括具有第一N型器件的第一N区、具有第二N型器件的第二N区、具有第一P型器件的第一P区以及具有第二P型器件的第二P区,且所述第一N型器件的阈值电压小于第二N型器件的阈值电压,所述第一P型器件的阈值电压大于第二P型器件的阈值电压;位于所述第一N区、第二N区、第一P区以及第二P区的基底上的栅介质层,其中,所述第一N区的栅介质层内氧空位含量大于所述第二N区的栅介质层内氧空位含量;位于所述第二P区的栅介质层上的第一功函数层;位于所述第一P区的栅介质层上以及第二P区的第一功函数层上的第二功函数层;位于所述第一N区和第二N区的栅介质层上、以及所述第一P区和第二P区的第二功函数层上的第三功函数层。

可选的,所述第一功函数层的材料、第二功函数层的材料以及第三功函数层的材料均为P型功函数材料。

可选的,所述半导体结构还包括:位于所述第三功函数层上的N型功函数层;位于所述N型功函数层上的栅电极层。

与现有技术相比,本发明的技术方案具有以下优点:

本发明实施例提供的半导体结构的形成方法的技术方案中,在形成具有不同阈值电压的第一N型器件以及第二N型器件,具有不同阈值电压的第一P型器件以及第二P型器件的工艺过程中,对第二N区的栅介质层进行氧空位钝化处理,使得第一N区的栅介质层内氧空位含量大于第二N区的栅介质层内氧空位含量,通过氧空位含量的不同使得第一N型器件和第二N型器件的阈值电压具有差异性;因此,形成的第三功函数层既位于第一N区还位于第二N区,避免了刻蚀去除第一N区的第三功函数层的工艺步骤,且无需形成第四功函数层,从而简化了工艺步骤,且满足第一N型器件阈值电压小于第二N型器件阈值电压的需求。并且,本发明减少了形成的功函数层膜层的数量,使得形成的半导体结构更加简单,且使得后续形成栅电极层的工艺窗口增加。

可选方案中,采用湿法刻蚀工艺刻蚀去除位于所述第二N区的第二功函数层,且所述湿法刻蚀工艺包括主刻蚀工艺以及过刻蚀工艺,利用所述过刻蚀工艺进行所述氧空位钝化处理,因此无需额外的工艺步骤进行所述氧空位钝化处理。

附图说明

图1至图3为一种半导体结构形成方法各步骤对应的剖面结构示意图;

图4至图11为本发明实施例提供的半导体结构形成方法各步骤对应的剖面结构示意图。

具体实施方式

由背景技术可知,现有技术形成的半导体结构的电学性能有待提高。尤其是当半导体结构中包括具有不同阈值电压(Threshold Voltage)的P型器件以及具有不同阈值电压的N型器件时,所述半导体结构形成工艺复杂的问题尤为显著。

为了同时满足NMOS管和PMOS管改善阈值电压的要求,通常采用不同的金属材料作为NMOS管和PMOS管的栅极结构中的功函数(WF,Work Function)层材料,NMOS管中的功函数层材料可称为N型功函数材料,PMOS管中的功函数层材料可称为P型功函数材料。通常采用调整栅介质层与N型功函数层之间的P型功函数层的厚度的方式,实现满足器件不同阈值电压的需求。

图1至图3为一种半导体结构形成方法各步骤对应的剖面结构示意图。

参考图1,提供基底11,所述基底11包括第一N区101以及第二N区102,第一N区101用于形成第一N型器件,第二N区102用于形成第二N型器件,且第一N型器件的阈值电压小于第二N型器件的阈值电压;在所述基底11上形成界面层12;在所述界面层12上形成栅介质层13;在所述第一N区101栅介质层13上形成第一功函数层14以及位于第一功函数层14上的第二功函数层15;在所述第一N区101的第二功函数层15上以及第二N区102的栅介质层13上形成第三功函数层16。

所述基底还包括第一P区和第二P区,且第一P区形成的P型器件阈值电压与第二P区形成的P型器件阈值电压不同。

参考图2,刻蚀去除位于所述第一N区101上的第三功函数层16、第二功函数层15(参考图1)以及第一功函数层14,暴露出所述第一N区101的栅介质层13表面。

参考图3,在所述第一N区101的栅介质层13上以及第二N区102的第三功函数层16上形成第四功函数层17。

上述形成方法复杂,且为了满足第一N型器件、第二N型器件、第一P型器件以及第二P型器件对阈值电压的不同需求,需要形成至少四层功函数层。

为解决上述问题,本发明提供一种半导体结构的形成方法,包括:提供基底,所述基底包括用于形成第一N型器件的第一N区、用于形成第二N型器件的第二N区、用于形成第一P型器件的第一P区以及用于形成第二P型器件的第二P区,且所述第一N型器件的阈值电压小于第二N型器件的阈值电压,所述第一P型器件的阈值电压大于第二P型器件的阈值电压;在所述第一N区、第二N区、第一P区以及第二P区的基底上形成栅介质层以及位于所述栅介质层上的第一功函数层;刻蚀所述第一功函数层,保留位于所述第二P区的第一功函数层;在刻蚀所述第一功函数层之后,在所述第一N区、第二N区、第一P区以及第二P区上形成第二功函数层;刻蚀去除所述第二N区的第二功函数层,直至暴露出所述第二N区的栅介质层;对所述第二N区的栅介质层进行氧空位钝化处理,降低所述第二N区的栅介质层内的氧空位含量;刻蚀去除所述第一N区的第二功函数层,直至暴露出所述第一N区的栅介质层;在所述第一N区和第二N区的栅介质层上、以及所述第一P区和第二P区的第二功函数层上形成第三功函数层。

本发明在形成具有不同阈值电压的第一N型器件、第二N型器件、第一P型器件以及第二P型器件的同时,节约了工艺步骤,简化了工艺复杂性,且使得形成的功函数层膜层数量少。

为使本发明的上述目的、特征和优点能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

图4至图11为本发明实施例提供的半导体结构形成方法各步骤对应的剖面结构示意图。

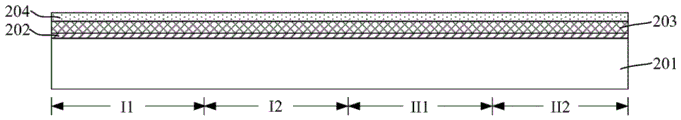

参考图4,提供基底201。

所述基底201包括用于形成第一N型器件的第一N区I1、用于形成第二N型器件的第二N区I2、用于形成第一P型器件的第一P区II1以及用于形成第二P型器件的第二P区II2,且所述第一N型器件的阈值电压小于第二N型器件的阈值电压,所述第一P型器件的阈值电压大于第二P型器件的阈值电压。

以所述第一N区I1与第二N区I2相邻接,所述第二N区I2与第一P区II1相邻接,所述第一P区II1与第二P区II2相邻接作为示例。

本实施例中,以形成的半导体结构为平面器件为例,所述基底201为平面衬底;所述基底201的材料为硅、锗、锗化硅、碳化硅、砷化镓或镓化铟,所述基底201还能够为绝缘体上的硅衬底或者绝缘体上的锗衬底。

在其他实施例中,形成的半导体结构为鳍式场效应管时,所述基底包括衬底以及位于所述衬底上的鳍部,所述基底还包括,位于所述鳍部露出的衬底上的隔离结构,所述隔离结构覆盖鳍部的部分侧壁,且所述隔离结构顶部低于所述鳍部顶部。

本实施例中,所述第一N区I1包括N型超低阈值电压(ULVT,Ultra-low VT)区以及N型低阈值电压(low VT)区;所述第二N区I2为N型标准阈值电压区(Standard VT)。在其他实施例中,所述第一N区还可以仅包括N型低阈值电压区或者N型超低阈值电压区中的一种。

本实施例中,所述第一P区II1为P型标准阈值电压区,所述第二P区II2包括P型超低阈值电压区以及P型低阈值电压区。在其他实施例中,所述第二P区还可以仅包括P型超低阈值电压区或者P型低阈值电压区中的一种。

需要说明的是,本实施例中,在后续形成栅介质层203之前,还包括:对所述N型超低阈值电压区对应的基底201进行第一N型阈值调节掺杂处理,对所述N型低阈值电压区对应的基底201进行第二N型阈值调节掺杂处理;对所述P型超低阈值电压区对应的基底201进行第一P型阈值调节掺杂处理,对所述P型低阈值电压区对应的基底201进行第二P型阈值调节掺杂处理。

具体地,所述第一N型阈值调节掺杂处理和第二N型阈值调节掺杂处理的掺杂离子为N型离子,N型离子包括P、As或Sb,所述第一N型阈值调节掺杂处理的掺杂浓度小于所述第二N型阈值调节掺杂处理的掺杂浓度。所述第一P型阈值调节掺杂处理和第二P型阈值调节掺杂处理的掺杂离子为P型离子,P型离子包括B、Ga或In,所述第一P型阈值调节掺杂处理的掺杂浓度小于所述第二P型阈值调节掺杂处理的掺杂浓度。

本实施例中,以采用后形成高k栅介质层后形成栅电极层(high k last metalgate last)的工艺,形成半导体结构的栅极结构为例。在形成栅介质层203之前,还包括:

在所述第一N区I1、第二N区I2、第一P区II1以及第二P区II2的基底201上形成伪栅结构,其中,由于所述第一N区I1与第一P区II1相邻接,因此所述伪栅结构横跨所述第一N区I1以及第一P区II1,相应的,后续形成的栅电极层横跨所述第一N区I1以及第一P区II1。

在形成所述伪栅结构之后,在各区域伪栅结构两侧的基底201内形成各器件的源漏掺杂区;在形成所述源漏掺杂区之后,在所述伪栅结构暴露出的基底201上形成层间介质层,所述层间介质层露出所述伪栅结构的顶部;在形成所述层间介质层之后,去除所述伪栅结构。

后续在所述第一N区I1、第二N区I2、第一P区II1以及第二P区II2的部分基底201上形成所述栅介质层203。需要说明的是,在其他实施例中,还可以采用先形成高k栅介质层后形成栅电极层(high k first metal gate last)的工艺,形成所述半导体结构。

继续参考图4,在所述第一N区I1、第二N区I2、第一P区II1以及第二P区II2的基底201上形成栅介质层203以及位于所述栅介质层203上的第一功函数层204。

所述栅介质层203的材料为高k栅介质材料,其中,高k栅介质材料为相对介电常数大于氧化硅相对介电常数的栅介质材料。

本实施例中,所述栅介质层203的材料为HfO2。在其他实施例中,所述栅介质层的材料还可以为HfSiO、HfSiON、HfTaO、HfTiO、HfZrO、ZrO2或Al2O3。

为了提高所述基底201与所述栅介质层203之间的界面性能,在形成所述栅介质层203之前,还在所述基底201上形成界面层202,相应的,所述栅介质层203位于所述界面层202表面。

所述界面层202为形成所述栅介质层203提供良好的界面基础,从而提高形成的栅介质层203的质量,减小所述栅介质层203与所述基底201之间的界面态密度,且避免所述栅介质层203与所述基底201直接接触造成的不良影响。

本实施例中,所述界面层202的材料为氧化硅。在其他实施例中,所述界面层的材料还可以为氮化硅或者氮氧化硅。

所述第一功函数层204的材料为P型功函数材料。具体地,位于所述第二P区II2上的第一功函数层204作为第二P型器件对应的功函数层的一部分,用于调节所述第二P型器件的阈值电压。

所述P型功函数材料功函数范围为5.1eV至5.5eV,例如,5.2eV、5.3eV或5.4eV。所述第一功函数层204的材料为Ta、TiN、TaN、TaSiN或TiSiN中的一种或几种,可以采用化学气相沉积工艺、物理气相沉积工艺或原子层沉积工艺形成所述第一功函数层204。

本实施例中,所述第一功函数层204的材料为TiN,所述第一功函数层204的厚度为10埃~30埃。

参考图5,刻蚀所述第一功函数层204,保留位于所述第二P区II2、第一N区I1以及第二N区I2的第一功函数层204。

本实施例中,刻蚀所述第一功函数层204,保留位于所述第一P区II2的第一功函数层204,包括:刻蚀去除所述第一P区II1的第一功函数层204,保留位于所述第一N区I1、第二N区II2以及第二P区II2的第一功函数层204。

具体地,刻蚀所述第一功函数层204的工艺步骤包括:在所述第一N区I1、第二N区I2和第二P区II2的第一功函数层204上形成第一图形层;以所述第一图形层为掩膜,刻蚀去除位于所述第一P区II1的第一功函数层204;去除所述第一图形层。

本实施例中,在刻蚀所述第一功函数层204的工艺过程中,保留位于所述第一N区I1以及第二N区I2的第一功函数层204,避免对第一N区I1以及第二N区I2的栅介质层203造成刻蚀损伤,减少第一N区I1以及第二N区I2的栅介质层203在工艺过程中受到的损伤。

参考图6,在刻蚀所述第一功函数层204之后,在所述第一N区I1、第二N区I2、第一P区II1以及第二P区II2上形成第二功函数层205。

本实施例中,形成所述第二功函数层205,包括:在所述第一N区I1、第二N区I2和第二P区II2的第一功函数层204上、以及第一P区II1的栅介质层203上形成所述第二功函数层205。

所述第二功函数层205的材料为P型功函数材料。位于所述第一P区II1上的第二功函数层205为第一P型器件对应的功函数层的一部分,起到调节所述第一P型器件的阈值电压的作用;位于所述第二P区II2上的第二功函数层205为第二P型器件对应的功函数层的一部分,起到调节所述第二P型器件的阈值电压的作用。

所述第二功函数层205的材料为Ta、TiN、TaN、TaSiN或TiSiN中的一种或几种。

本实施例中,所述第二功函数层205的材料为TiN,所述第二功函数层205的厚度为10埃~30埃。

参考图7,刻蚀去除所述第二N区I2的第二功函数层205以及第一功函数层204,暴露出所述第二N区I2的栅介质层203。

本实施例中,由于前述在形成第二功函数层205之前,保留了位于所述第二N区I2的第一功函数层204;因此,刻蚀去除所述第二N区I2的第二功函数层205,包括:刻蚀去除所述第二N区I2的第二功函数层205,且还刻蚀去除所述第二N区I2的第一功函数层204。

在刻蚀去除所述第二N区I2的第二功函数层205之前,还包括:在所述第一N区I1、第一P区II1和第二P区II2的第二功函数层205上形成掩膜层200。

本实施例中,所述掩膜层200的材料为氮化硅。在其他实施例中,所述掩膜层的材料还可以为光刻胶材料。

所述掩膜层200起到保护第一N区I1、第一P区II1以及第二P区II2的第二功函数层205不被刻蚀的作用。并且,本实施例中,在后续进行氧空位钝化处理之后,去除所述掩膜层200,所述掩膜层200还在氧空位钝化处理过程中对第一N区I1、第一P区II1以及第二P区II2起到保护作用。

采用湿法刻蚀工艺,刻蚀去除所述第二N区I2的第二功函数层205以及第一功函数层204,直至暴露出所述第二N区I2的栅介质层203。

本实施例中,所述湿法刻蚀工艺的刻蚀液体具有氧化性。其好处在于:所述湿法刻蚀工艺不仅可以刻蚀去除所述第二N区I2的第二功函数层205以及第一功函数层204,且还可以对第二N区I2暴露出的栅介质层203进行氧空位钝化处理。

具体地,所述湿法刻蚀工艺包括主刻蚀工艺(main etch)以及过刻蚀工艺(overetch),其中,利用所述过刻蚀工艺进行后续的氧空位钝化处理。

所述湿法刻蚀工艺采用的刻蚀液体为SC1溶液、SC2溶液或者SPM溶液。

其中,SC1溶液为氨水和双氧水的水溶液;SC2溶液为盐酸和双氧水的水溶液;SPM溶液为硫酸和双氧水的水溶液。

参考图8,对所述第二N区I2的栅介质层203进行氧空位钝化处理206,降低所述第二N区I2的栅介质层203内的氧空位含量。

所述栅介质层203内易形成缺陷,所述缺陷包括氧空位、悬挂键或者未成键离子中的一种或多种。本实施例中,所述栅介质层203内含有氧空位缺陷。

对所述第二N区I2的栅介质层203进行氧空位钝化处理206,有利于降低所述第二N区I2的栅介质层203内的氧空位含量,使得第一N区I1的栅介质层203内的氧空位含量大于第二N区I2的栅介质层203内的氧空位含量。

由于所述第一N区I1的栅介质层203内的氧空位含量大于第二N区I2的栅介质层203内的氧空位含量,使得第一N区I1的栅介质层203内的偶极子数量大于第二N区I2的栅介质层203内偶极子数量;相应的,第一N型器件后续形成的栅极结构与基底201之间的平带电压高于第二N型器件后续形成的栅极结构与基底201之间的平带电压,从而使得形成的第一N型器件阈值电压高于第二N型器件阈值电压。

本实施例中,通过延长前述湿法刻蚀工艺中的过刻蚀工艺的刻蚀时长,进行所述氧空位钝化处理206,使得所述氧空位钝化处理206的工艺操作简单,无需额外的工艺步骤。

具体地,所述过刻蚀工艺的刻蚀时长不宜过短,也不宜过长。若所述过刻蚀工艺的刻蚀时长过短,则所述第二N区I2的栅介质层203内的氧空位含量减少程度低;若所述过刻蚀工艺的刻蚀时长过长,则所述氧空位钝化处理206会对所述第二N区I2的栅介质层203造成不良影响。

为此,本实施例中,所述过刻蚀工艺的刻蚀时长为10s~2min。

在其他实施例中,还可以在刻蚀去除所述第二N区的第二功函数层和第一功函数层之后,采用含有过氧化氢的处理溶液,进行所述氧空位钝化处理,所述处理溶液可以为SC1溶液、SC2溶液或者SPM溶液。

需要说明的是,所述处理溶液中,过氧化氢含量不宜过低,也不宜过高。若所述过氧化氢含量过低,则所述氧空位钝化处理的效率低下;若所述过氧化氢含量过高,所述氧空位钝化处理易对第二N区的栅介质层造成不良影响。相应的,所述处理溶液温度也不宜过低且不宜过高。

为此,当采用含有过氧化氢的处理溶液进行所述氧空位钝化处理时,所述处理溶液中,过氧化氢质量浓度为5%~20%,处理溶液温度为20℃~50℃。

在进行所述氧空位钝化处理206之后,去除所述掩膜层200。

参考图9,刻蚀去除所述第一N区I1的第二功函数层205以及第一功函数层204,直至暴露出所述第一N区I1的栅介质层203。

本实施例中,由于在形成所述第二功函数层205之前,保留了位于所述第一N区I1上的第一功函数层204,为此,刻蚀去除所述第一N区I1的第二功函数层205包括:刻蚀去除所述第一N区I1的第二功函数层205,且还刻蚀去除所述第一N区I1的第一功函数层204。

采用湿法刻蚀工艺,刻蚀去除所述第一N区I1的第二功函数层205以及第一功函数层204。具体地,刻蚀去除所述第一N区I1的第二功函数层205以及第一功函数层204的工艺步骤包括:在所述第二N区I2的栅介质层203上、以及所述第一P区II1和第二P区II2的第二功函数层205上形成第二图形层;以所述第二图形层为掩膜,刻蚀去除所述第一N区I1的第二功函数层205以及第一功函数层204;去除所述第二图形层。

本实施例中,先进行所述氧空位钝化处理206(参考图8),后刻蚀去除所述第一N区I1的第二功函数层205以及第一功函数层204,避免所述氧空位钝化处理对所述第一N区I1的栅介质层203造成影响。

还需要说明的是,在其他实施例中,还可以在进行所述氧空位钝化处理之前,刻蚀去除所述第一N区的第二功函数层以及第一功函数层;其中,在同一道工艺步骤中,刻蚀去除所述第一N区和第二N区的第二功函数层以及第一功函数层;且在进行所述氧空位钝化处理之前,还包括,在所述第一N区的栅介质层上形成保护层。

参考图10,在所述第一N区I1和第二N区I2的栅介质层203上、以及所述第一P区II1和第二P区II2的第二功函数层205上形成第三功函数层207。

位于所述第一N区I1上的第三功函数层204作为第一N型器件对应的功函数层的一部分,起到调节第一N型器件阈值电压的作用;位于所述第二N区I2上的第三功函数层204作为第二N型器件对应的功函数层的一部分,起到调节第二N型器件阈值电压的作用。

位于所述第一P区II1上的第二功函数层205和第三功函数层207作为第一P型器件对应的功函数层,起到调节第一P型器件阈值电压的作用;位于所述第二P区II2上的第一功函数层204、第二功函数层205和第三功函数层207作为第二P型器件对应的功函数层,起到调节第二P型器件阈值电压的作用。

对于P型器件而言,功函数层的厚度越厚,相应形成的P型器件阈值电压越小。由于所述第一P型器件对应的功函数层的厚度较第二P型器件对应的功函数层的厚度更薄,因此后续形成的第一P型器件阈值电压大于第二P型器件阈值电压。

所述第三功函数层207的材料为P型功函数材料;所述第三功函数层207的材料为Ta、TiN、TaN、TaSiN或TiSiN中的一种或几种。

本实施例中,所述第三功函数层207的材料为TiN,所述第三功函数层207的厚度为10埃~30埃。

采用化学气相沉积工艺、物理气相沉积工艺或者原子层沉积工艺,形成所述第三功函数层207。

所述第一N型器件的栅极结构与基底201之间的平带电压Vfb与所述第一N型器件的功函数层的厚度有关,且所述第一N型器件的平带电压还与第一N区I1的栅介质层203内的偶极子(dipole)数量有关;所述第二N型器件的栅极结构与所述基底201之间的平带电压Vfb与所述第二N型器件的功函数层的厚度有关,且所述第二N型器件的平带电压还与第二N区I2的栅介质层203内的偶极子数量有关。

由于前述对第二N区I2的栅介质层203进行了氧空位钝化处理206,所述第二N区I2的栅介质层203内氧空位含量低于所述第一N区I1的栅介质层203内氧空位含量,使得第二N区I2的栅介质层203内的偶极子较第一N区I1的栅介质层203内的偶极子量少。因此,即使第一N型器件的功函数层厚度与第二N型器件的功函数层厚度相等,所述第一N型器件的平带电压大于第二N型器件的平带电压,从而使得形成的第一N型器件阈值电压高于第二N型器件阈值电压。

为此,本实施例中,在后续形成N型功函数层之前,位于所述第一N区I1和第二N区I2上的功函数层的厚度相同,无需进行刻蚀去除第一N区的第三功函数层207以及在第一N区和第二N区上形成第四功函数层的工艺步骤,从而简化了半导体结构的形成工艺步骤,使得半导体结构中的功函数膜层数量减少。

参考图11,在所述第一N区I1、第二N区I2、第一P区II1和第二P区II2的第三功函数层207上形成N型功函数层208,且所述N型功函数层208的材料功函数类型与所述第三功函数层207的材料功函数类型不同;在所述N型功函数层208上形成栅电极层(未图示)。

位于所述第一N区I1上的第三功函数层207和N型功函数层208作为第一N型器件对应的功函数层,起到调节第一N型器件阈值电压的作用;位于所述第二N区I2上的第三功函数层207和N型功函数层208作为第二N型器件对应的功函数层,起到调节第二N型器件阈值电压的作用。

对于N型器件而言,由于第二N区I2的栅介质层203内氧空位含量少于第一N区I1的栅介质层203内氧空位含量,且所述第一N型器件对应的功函数层的厚度与第二N型器件对应的功函数层的厚度相等,因此后续形成的第二N型器件的阈值电压大于第一N型器件的阈值电压。

需要说明的是,为了减少工艺步骤、节约光罩,本实施例中,在形成所述N型功函数层208之后,保留位于所述第一P区II1以及第二P区II2上的N型功函数层208。

所述N型功函数层208的材料为N型功函数材料,N型功函数材料功函数范围为3.9eV至4.5eV,例如为4eV、4.1eV或4.3eV。所述N型功函数层208的材料为TiAl、TiAlC、TaAlN、TiAlN、TaCN和AlN中的一种或多种,可以采用化学气相沉积工艺、物理气相沉积工艺或原子层沉积工艺形成所述N型功函数层208。

本实施例中,所述N型功函数层208的材料为TiAl,所述N型功函数层208的厚度为10埃~50埃。

后续的工艺步骤还包括:在所述N型功函数层208上形成栅电极层。

本实施例中,所述栅电极层横跨所述第一N区I1、第一P区II1、第二P区II2以及第二N区I2,相应的,所述第一N区I1、第一P区II1、第二P区II2以及第二N区I2共用同一个栅电极层。在其他实施例中,位于所述第一N区、第二N区、第一P区以及第二P区的栅电极层还可以相互独立。

所述栅电极层的材料包括Al、Cu、Ag、Au、Pt、Ni、Ti或W中的一种或多种。

具体地,形成所述栅电极层的工艺步骤包括:在所述N型功函数层208上形成栅电极膜,所述栅电极膜顶部高于所述层间介质层(未图示)顶部;研磨去除高于所述层间介质层顶部的栅电极膜,形成所述栅电极层。

本发明实施例提供的半导体结构的形成方法的技术方案中,在形成具有不同阈值电压的第一N型器件以及第二N型器件,具有不同阈值电压的第一P型器件以及第二P型器件的工艺过程中,对第二N区I2的栅介质层203进行氧空位钝化处理,使得第一N区I1的栅介质层203内氧空位含量大于第二N区I2的栅介质层203内氧空位含量,通过氧空位含量的不同使得第一N型器件和第二N型器件的阈值电压具有差异性;因此,形成的第三功函数层既位于第一N区I1还位于第二N区I2,避免了刻蚀去除第一N区I1的第三功函数层207的工艺步骤,且无需形成第四功函数层,从而简化了工艺步骤,且满足第一N型器件阈值电压小于第二N型器件阈值电压的需求。

相应的,本发明还提供一种半导体结构,参考图11,所述半导体结构包括:

基底,所述基底包括具有第一N型器件的第一N区I1、具有第二N型器件的第二N区I2、具有第一P型器件的第一P区II1以及具有第二P型器件的第二P区II2,且所述第一N型器件的阈值电压小于第二N型器件的阈值电压,所述第一P型器件的阈值电压大于所述第二P型器件的阈值电压;

位于所述第一N区I1、第二N区I2、第一P区II1以及第二P区II2的基底上的栅介质层203,其中,所述第一N区I1的栅介质层203内氧空位含量大于所述第二N区I2的栅介质层203内氧空位含量;

位于所述第二P区II2的栅介质层203上的第一功函数层204;

位于所述第一P区II1的栅介质层203上以及第二P区II2的第一功函数层204上的第二功函数层205;

位于所述第一N区I1和第二N区I2的栅介质层203上、以及第一P区II1和第二P区II2的第二功函数层205上的第三功函数层207。

以下将结合附图对本发明实施例提供的半导体结构进行详细说明。

有关所述基底201以及栅介质层203的描述可参考前述实施例的相应说明,在此不再赘述。本实施例中,所述半导体结构还包括:位于所述基底201与所述栅介质层203之间的界面层202。

所述半导体结构还包括:位于所述第三功函数层207上的N型功函数层208;位于所述N型功函数层208上的栅电极层。

所述第一功函数层204的材料为Ta、TiN、TaN、TaSiN或TiSiN中的一种或几种;所述第二功函数层205的材料为Ta、TiN、TaN、TaSiN或TiSiN中的一种或几种;所述第三功函数层207的材料为Ta、TiN、TaN、TaSiN或TiSiN中的一种或几种;所述N型功函数层208的材料为TiAl、TiAlC、TaAlN、TiAlN、TaCN和AlN中的一种或几种。

本实施例中,所述第一功函数层204的材料为TiN,所述第二功函数层205的材料为TiN,所述第三功函数层207的材料为TiN,所述N型功函数层208的材料为TiAl。所述第一功函数层204的厚度为10埃~30埃;所述第二功函数层205的厚度为10埃~30埃;所述第三功函数层207的厚度为10埃~30埃;所述N型功函数层208的厚度为10埃~50埃。

本实施例中,由于所述第一N区I1的栅介质层203内氧空位含量大于第二N区I2的栅介质层203内氧空位含量,且第三功函数层207以及N型功函数层208均位于第一N区I和第二N区I2上,使得第一N区I1和第二N区I2上的功函数层厚度相同,且还满足第一N型器件阈值电压小于第二N型器件阈值电压的需求。

虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

Claims (20)

1.一种半导体结构的形成方法,其特征在于,包括:

提供基底,所述基底包括用于形成第一N型器件的第一N区、用于形成第二N型器件的第二N区、用于形成第一P型器件的第一P区以及用于形成第二P型器件的第二P区,且所述第一N型器件的阈值电压小于第二N型器件的阈值电压,所述第一P型器件的阈值电压大于第二P型器件的阈值电压;在所述第一N区、第二N区、第一P区以及第二P区的基底上形成栅介质层以及位于所述栅介质层上的第一功函数层;

刻蚀所述第一功函数层,保留位于所述第二P区、第一N区以及第二N区的第一功函数层;

在刻蚀所述第一功函数层之后,在所述第一N区、第二N区、第一P区以及第二P区上形成第二功函数层;

刻蚀去除所述第二N区的第二功函数层以及第一功函数层,直至暴露出所述第二N区的栅介质层;

对所述第二N区的栅介质层进行氧空位钝化处理,降低所述第二N区的栅介质层内的氧空位含量;

刻蚀去除所述第一N区的第二功函数层以及第一功函数层,直至暴露出所述第一N区的栅介质层;

在所述第一N区和第二N区的栅介质层上、以及所述第一P区和第二P区的第二功函数层上形成第三功函数层。

2.如权利要求1所述的半导体结构的形成方法,其特征在于,采用湿法刻蚀工艺,刻蚀去除所述第二N区的第二功函数层以及第一功函数层,直至暴露出所述第二N区的栅介质层,且所述湿法刻蚀工艺的刻蚀液体具有氧化性。

3.如权利要求2所述的半导体结构的形成方法,其特征在于,所述湿法刻蚀工艺包括主刻蚀工艺以及过刻蚀工艺,其中,利用所述过刻蚀工艺进行所述氧空位钝化处理。

4.如权利要求3所述的半导体结构的形成方法,其特征在于,所述湿法刻蚀工艺采用的刻蚀液体为SC1溶液、SC2溶液或者SPM溶液。

5.如权利要求3所述的半导体结构的形成方法,其特征在于,所述过刻蚀工艺的刻蚀时长为10s~2min。

6.如权利要求1所述的半导体结构的形成方法,其特征在于,采用含有过氧化氢的处理溶液,进行所述氧空位钝化处理。

7.如权利要求6所述的半导体结构的形成方法,其特征在于,所述处理溶液中,过氧化氢质量浓度为5%~20%,处理溶液温度为20℃~50℃。

8.如权利要求6所述的半导体结构的形成方法,其特征在于,所述处理溶液为SC1溶液、SC2溶液或者SPM溶液。

9.如权利要求1所述的半导体结构的形成方法,其特征在于,先进行所述氧空位钝化处理,后刻蚀去除所述第一N区的第二功函数层以及第一功函数层。

10.如权利要求1所述的半导体结构的形成方法,其特征在于,所述栅介质层的材料为高k栅介质材料。

11.如权利要求10所述的半导体结构的形成方法,其特征在于,在形成所述栅介质层之前,还在所述第一N区、第二N区、第一P区以及第二P区的基底上形成界面层。

12.如权利要求1所述的半导体结构的形成方法,其特征在于,所述第一功函数层的材料、第二功函数层以及第三功函数层的材料均为P型功函数材料。

13.如权利要求12所述的半导体结构的形成方法,其特征在于,所述P型功函数材料包括Ta、TiN、TaN、TaSiN或TiSiN中的一种或几种。

14.如权利要求1所述的半导体结构的形成方法,其特征在于,还包括步骤:在所述第一N区、第二N区、第一P区和第二P区的第三功函数层上形成N型功函数层,且所述N型功函数层的材料功函数类型与所述第三功函数层的材料功函数类型不同;在所述N型功函数层上形成栅电极层。

15.如权利要求14所述的半导体结构的形成方法,其特征在于,所述N型功函数层的材料为TiAl、TiAlC、TaAlN、TiAlN、TaCN和AlN中的一种或几种。

16.如权利要求1所述的半导体结构的形成方法,其特征在于,刻蚀所述第一功函数层的工艺步骤包括:在所述第一N区、第二N区和第二P区的第一功函数层上形成第一图形层;以所述第一图形层为掩膜,刻蚀去除位于所述第一P区的第一功函数层;去除所述第一图形层。

17.如权利要求1所述的半导体结构的形成方法,其特征在于,刻蚀去除所述第一N区的第二功函数层以及第一功函数层的工艺步骤包括:在所述第二N区的栅介质层上、以及所述第一P区和第二P区的第二功函数层上形成第二图形层;以所述第二图形层为掩膜,刻蚀去除所述第一N区的第二功函数层以及第一功函数层;去除所述第二图形层。

18.一种半导体结构,其特征在于,包括:

基底,所述基底包括具有第一N型器件的第一N区、具有第二N型器件的第二N区、具有第一P型器件的第一P区以及具有第二P型器件的第二P区,且所述第一N型器件的阈值电压小于第二N型器件的阈值电压,所述第一P型器件的阈值电压大于第二P型器件的阈值电压;

位于所述第一N区、第二N区、第一P区以及第二P区的基底上的栅介质层,其中,所述第一N区的栅介质层内氧空位含量大于所述第二N区的栅介质层内氧空位含量;

位于所述第二P区的栅介质层上的第一功函数层;

位于所述第一P区的栅介质层上以及第二P区的第一功函数层上的第二功函数层;

位于所述第一N区和第二N区的栅介质层上、以及所述第一P区和第二P区的第二功函数层上的第三功函数层。

19.如权利要求18所述的半导体结构,其特征在于,所述第一功函数层的材料、第二功函数层的材料以及第三功函数层的材料均为P型功函数材料。

20.如权利要求18所述的半导体结构,其特征在于,所述半导体结构还包括:位于所述第三功函数层上的N型功函数层;位于所述N型功函数层上的栅电极层。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201611239033.7A CN108258028B (zh) | 2016-12-28 | 2016-12-28 | 半导体结构及其形成方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201611239033.7A CN108258028B (zh) | 2016-12-28 | 2016-12-28 | 半导体结构及其形成方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN108258028A CN108258028A (zh) | 2018-07-06 |

| CN108258028B true CN108258028B (zh) | 2020-06-09 |

Family

ID=62720392

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201611239033.7A Active CN108258028B (zh) | 2016-12-28 | 2016-12-28 | 半导体结构及其形成方法 |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN108258028B (zh) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN112242299B (zh) * | 2019-07-18 | 2024-10-22 | 中芯国际集成电路制造(上海)有限公司 | 半导体结构及其形成方法 |

| CN111554679B (zh) * | 2020-04-09 | 2023-03-31 | 中国科学院微电子研究所 | 一种SOI FinFET器件及其制作方法 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103594365A (zh) * | 2012-08-14 | 2014-02-19 | 中芯国际集成电路制造(上海)有限公司 | Pmos晶体管的形成方法 |

| CN104425384A (zh) * | 2013-09-10 | 2015-03-18 | 中芯国际集成电路制造(上海)有限公司 | 一种半导体器件及其制造方法 |

| CN104916589A (zh) * | 2014-03-12 | 2015-09-16 | 中芯国际集成电路制造(上海)有限公司 | 一种制作半导体器件的方法 |

| CN105518848A (zh) * | 2013-07-18 | 2016-04-20 | 格罗方德半导体股份有限公司 | 具有多个阈值电压的鳍式场效应晶体管 |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102235612B1 (ko) * | 2015-01-29 | 2021-04-02 | 삼성전자주식회사 | 일-함수 금속을 갖는 반도체 소자 및 그 형성 방법 |

| US9553092B2 (en) * | 2015-06-12 | 2017-01-24 | Globalfoundries Inc. | Alternative threshold voltage scheme via direct metal gate patterning for high performance CMOS FinFETs |

-

2016

- 2016-12-28 CN CN201611239033.7A patent/CN108258028B/zh active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103594365A (zh) * | 2012-08-14 | 2014-02-19 | 中芯国际集成电路制造(上海)有限公司 | Pmos晶体管的形成方法 |

| CN105518848A (zh) * | 2013-07-18 | 2016-04-20 | 格罗方德半导体股份有限公司 | 具有多个阈值电压的鳍式场效应晶体管 |

| CN104425384A (zh) * | 2013-09-10 | 2015-03-18 | 中芯国际集成电路制造(上海)有限公司 | 一种半导体器件及其制造方法 |

| CN104916589A (zh) * | 2014-03-12 | 2015-09-16 | 中芯国际集成电路制造(上海)有限公司 | 一种制作半导体器件的方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN108258028A (zh) | 2018-07-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7927943B2 (en) | Method for tuning a work function of high-k metal gate devices | |

| US10411023B2 (en) | Semiconductor structure | |

| US8093116B2 (en) | Method for N/P patterning in a gate last process | |

| US8105931B2 (en) | Method of fabricating dual high-k metal gates for MOS devices | |

| US8357603B2 (en) | Metal gate fill and method of making | |

| KR102128450B1 (ko) | 트랜지스터의 문턱전압조절을 위한 방법 및 게이트구조물 | |

| US7977181B2 (en) | Method for gate height control in a gate last process | |

| US7776757B2 (en) | Method of fabricating high-k metal gate devices | |

| CN108010884B (zh) | 半导体结构及其形成方法 | |

| US20100044803A1 (en) | Sealing structure for high-k metal gate and method of making | |

| EP3267472B1 (en) | Semiconductor device and fabrication method thereof | |

| CN106653605B (zh) | 半导体结构的形成方法 | |

| US9142414B2 (en) | CMOS devices with metal gates and methods for forming the same | |

| JP2009267180A (ja) | 半導体装置 | |

| CN107437562B (zh) | 半导体器件的形成方法 | |

| CN108258028B (zh) | 半导体结构及其形成方法 | |

| CN108257918B (zh) | 半导体结构及其形成方法 | |

| CN106847755B (zh) | 改善sram性能的方法 | |

| CN111211055B (zh) | 半导体结构及其形成方法 | |

| CN108155235B (zh) | 半导体结构及其形成方法 | |

| CN108987248B (zh) | 半导体结构及其形成方法 | |

| CN108389835B (zh) | 半导体结构及其形成方法 | |

| CN107393868B (zh) | 半导体结构的形成方法 | |

| CN109309050B (zh) | 半导体结构及其形成方法 | |

| CN107492522B (zh) | Cmos器件、pmos器件及nmos器件的形成方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant |