CN100466434C - Pwm controller with dual-edge modulation using dual ramps - Google Patents

Pwm controller with dual-edge modulation using dual ramps Download PDFInfo

- Publication number

- CN100466434C CN100466434C CNB200610008501XA CN200610008501A CN100466434C CN 100466434 C CN100466434 C CN 100466434C CN B200610008501X A CNB200610008501X A CN B200610008501XA CN 200610008501 A CN200610008501 A CN 200610008501A CN 100466434 C CN100466434 C CN 100466434C

- Authority

- CN

- China

- Prior art keywords

- signal

- ramp

- pwm

- circuit

- asserted

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Dc-Dc Converters (AREA)

Abstract

A dual-edge modulation controller for fast response to fast load transitions including first and second ramp circuits, first and second comparators, an error amplifier and pulse control logic. The first ramp circuit provides a leading-edge ramp synchronous with a clock. The error amplifier compares a feedback signal with a reference and provides a compensation signal. The first comparator compares the leading-edge ramp with the compensation signal and asserts a set signal. The second ramp circuit provides a trailing-edge ramp that begins ramping when the set signal is asserted. The second comparator compares the trailing-edge ramp with the compensation signal and asserts a reset signal. The pulse control logic asserts a PWM signal when the set signal is asserted and de-asserts the PWM signal when the reset signal is asserted. The controller may control multiple phases with current balancing. The slew rate of the ramps may be adjusted based on the number of PWM signal asserted.

Description

The mutual reference of related application

This application requires the U.S. Provisional Application sequence number 60/651 of application on February 10th, 2005, the U.S. Provisional Application sequence number 60/696 of application on July 5th, 599 and 2005,680 priority, these U.S. Provisional Applications are included in this as a reference at institute is intentional with purpose.

Technical field

The present invention is relevant for power regulator or transducer, and more especially relevant for a kind of bilateral power-supply controller of electric of being realized along modulation that utilizes the double slanted signal in order to respond fast.

Background technology

The load current of modern CPU (CPU) is highly dynamic, and changes to high electric current and change to low current from high electric current from low current very apace.For example, the current transients of CPU may take place in 1 microsecond (μ s), this is less than the typical switching cycle of known voltage adjuster.Be desirable to provide to one of the power regulator of dc-dc for the control loop that when load transition fast takes place, all has the sufficient response time.

In the structure of known pulse width modulation (PWM), the compensation of error amplifier (COMP) output typical case comes and a fixing ramp signal compares by a PWM comparator, and this of PWM comparator generation is used to control the pwm signal of switching of the power regulator of dc-dc.For the noise immunity of switching is provided, couple of the output of a replacement-setting (R-S) trigger usually to this comparator, have only a pulse to guarantee each switching cycle.The modulation system in forward position (leading-edge) is good for the transient event that adds load, but not always in response to the transient event that discharges load, then the modulation system along (trailing-edge) is good for the transient event that discharges load, but not always in response to the transient event that adds load.Therefore, these known modes all increase clock signal delay respectively under the situation of some load variations.Since this slope be fix and because the forward position of pwm pulse is then interim along only occurring in second half in the half period before only occurring in, so known bilaterally also present conducting or turn-off delay along modulation system.

Summary of the invention

According to an embodiment of the inventionly bilaterally comprise first and second ramp circuit, first and second comparator, error amplifier and pulse control logic along modulation controller.This first ramp circuit provides the leading-edge ramp signal with a clock signal Synchronization.This error amplifier is a feedback signal and a reference signal relatively, and the compensating signal of indicating it is provided.This first comparator is this leading-edge ramp signal and this compensating signal relatively, and asserts that (assert) indicates its setting signal.This second ramp circuit provides the back along ramp signal, and this back begins to do the slope along ramp signal and changes (ramping) when this setting signal is asserted.This second comparator relatively this back along ramp signal and this compensating signal and assert its reset signal of indication.This pulse control logic is asserted pulse-width modulated (PWM) signal and remove to assert (de-assert) this pwm signal when this reset signal is asserted when this setting signal is asserted.

This first ramp circuit can begin in each pulse of this clock signal to change this leading-edge ramp signal from default voltage level slope.This second ramp circuit can begin to change this back along ramp signal from default voltage level slope when this pwm signal is asserted, and this first voltage level is got back to along ramp signal in this back of can resetting when this pwm signal is gone to assert.This first ramp circuit is downward ramp generator more in the certain embodiments at one, and this second ramp circuit is the acclivity generator.This pulse control logic can be implemented as R-S trigger or fellow.

In one embodiment, this pwm signal control commutation circuit, this commutation circuit is coupled to output inductor at the phase node place, becomes output voltage to change input voltage by this output inductor.This second ramp circuit can be according to this input voltage, phase node voltage, control the switching rate (slew rate) of this back along ramp signal across any combination of the voltage of this output inductor and the electric current by this output inductor.

Power inverter according to an embodiment of the invention comprises first phase circuit and bilateral along modulation controller.This is bilateral to comprise error amplifier, oscillator, first and second comparator, first ramp circuit and the first pulse control logic along modulation controller.This first phase circuit is controlled by first pwm signal, becomes output voltage to be used for changing input voltage via first inductor.This bilateral PWM output that has the feedback input that is used for this output voltage of sensing and be used to provide this first pwm signal along modulation controller.This error amplifier has first input that is coupled to this feedback input, second input that receives a reference voltage and the output that a compensating signal is provided.This oscillator provides the first leading-edge ramp signal with repetition slope.This first comparator is this first leading-edge ramp signal and this compensating signal relatively, and asserts its first setting signal of indication.This first ramp circuit makes first back do the slope variation along ramp signal when this first pwm signal is asserted.Relatively this first back is along ramp signal and this compensating signal for this second comparator, and it asserts first reset signal of indicating it.This first pulse control logic is asserted this first pwm signal when this first setting signal is asserted, and removes to assert this first pwm signal when this first reset signal is asserted.

In one embodiment, this oscillator begins to make this first leading-edge ramp signal to descend from the first voltage level slope in each pulse of clock signal, and this first ramp circuit makes this first back rise from the second voltage level slope along ramp signal when this first pwm signal is asserted.

This power inverter can comprise second phase circuit, and this second phase circuit is controlled by second pwm signal, becomes this output voltage to be used for changing this input voltage via second inductor that is coupled to this first inductor.In this example, this is bilateral to have the 2nd PWM output that is used to provide this second pwm signal along modulation controller, and comprises the 3rd and the 4th comparator, second ramp circuit and the second pulse control logic.This oscillator provides the second leading-edge ramp signal with repetition slope.The 3rd comparator is this second leading-edge ramp signal and this compensating signal relatively, and asserts its second setting signal of indication.This second ramp circuit makes second back do the slope variation along ramp signal when this second pwm signal is asserted.The 4th comparator relatively this second back and is asserted second reset signal of indicating it along ramp signal and this compensating signal.This second pulse control logic is asserted this second pwm signal when this second setting signal is asserted, and removes to assert this second pwm signal when this second reset signal is asserted.

In one embodiment, this first leading-edge ramp signal and first clock signal are synchronous, this second leading-edge ramp signal and second clock signal Synchronization, and this first and second clock signal is separated a phase angle.

This power inverter can further comprise current balance system, and this system adjusts this compensating signal according to the electric current that senses of this first and second inductor.This current balance system can comprise first and second current balance circuit.This first current balance circuit receives this compensating signal and provides the first adjusted compensating signal to this second comparator.This second current balance circuit receives this compensating signal and provides the second adjusted compensating signal to the 4th comparator.

This first and second ramp circuit can produce have in fact the switching rate that equates first and second back along ramp signal.Or this first ramp circuit increases the switching rate of this first back along ramp signal when this second pwm signal is asserted, and this second ramp circuit increases the switching rate of this second back along ramp signal when this first pwm signal is asserted.This power inverter can comprise the impulse summation device, the output that this impulse summation utensil has first and second input that receives this first and second pwm signal and the number of phases of the pwm signal sum that an indication is asserted simultaneously is provided.In this example, this first ramp circuit is adjusted the switching rate of this first back along ramp signal according to this number of phases, and this second ramp circuit is adjusted the switching rate of this second back along ramp signal according to this number of phases.

The first leading-edge ramp signal that provides with a clock signal Synchronization is provided the method that is used to control DC-DC converter according to an embodiment of the invention, compare feedback signal and reference signal and the compensating signal of indicating it is provided, relatively this first leading-edge ramp signal and this compensating signal and assert its first commencing signal of indication, the slope changes first back along ramp signal when first pwm signal is asserted, relatively this first back is along ramp signal and this compensating signal and assert first stop signal of indicating it, and asserts this first pwm signal and remove to assert this first pwm signal when this first stop signal is asserted when this first commencing signal is asserted.

Each pulse that this method can be included in this clock signal this first leading-edge ramp signal that begins to descend from the first voltage level slope, and when this first pwm signal is asserted, begin to rise this first back along ramp signal from the second voltage level slope.This method can comprise first end that switches output inductor according to this first pwm signal between the polarity of input voltage, producing output voltage at second end of this output inductor, and according to the voltage of first end of this input voltage, this output inductor, control the switching rate of this first back along ramp signal across any combination of the voltage of this output inductor and the electric current by this output inductor.

This method can comprise provide with this clock signal synchronously and with the second leading-edge ramp signal of this first leading-edge ramp signal out-phase, relatively this second leading-edge ramp signal and this compensating signal and assert its second commencing signal of indication, the slope changes second back along ramp signal when second pwm signal is asserted, relatively this second back is along ramp signal and this compensating signal and assert second stop signal of indicating it, and asserts this second pwm signal and remove to assert this second pwm signal when this second stop signal is asserted when this second commencing signal is asserted.

This method can comprise to be utilized this first pwm signal to control first phase circuit of this DC-DC converter and utilizes this second pwm signal to control second phase circuit of this DC-DC converter, and wherein this first and second phase circuit is coupled in together.This method can comprise the electric current of this first and second phase circuit of sensing, and adjusts the electric current of this compensating signal with this first and second phase circuit of balance.This method can comprise according to the electric current that senses adjusts this compensating signal so that the first adjusted compensating signal to be provided, adjust this compensating signal so that the second adjusted compensating signal to be provided according to the electric current that senses, relatively this first back is along ramp signal and this first adjusted compensating signal, and relatively this second afterwards along ramp signal and this second adjusted compensating signal.This method can comprise with first switching rate comes the slope to change this first back along ramp signal, and comes the slope to change this second back along ramp signal with second switching rate that is equal to this first switching rate in fact.This method can be included in adjusts the switching rate of this first back along ramp signal when this second pwm signal is asserted, and adjusts the switching rate of this second back along ramp signal when this first pwm signal is asserted.This method can comprise this first and second pwm signal addition.

Description of drawings

Benefit of the present invention, characteristics and advantage are more readily understood in reference the following description and appended will becoming under graphic, wherein:

Fig. 1 is a series of sequential chart of describing according to a kind of known leading edge modulation mode of known technology;

Fig. 2 is a kind of known back a series of sequential chart of describing according to known technology along modulation system;

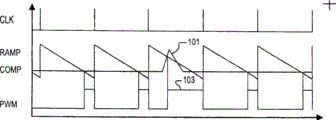

Fig. 3 is a kind of known bilateral a series of sequential chart of describing according to known technology along modulation system;

Fig. 4 is a kind of bilateral a series of sequential chart along modulation system that utilizes double slanted of describing according to the embodiment of an example of the present invention;

Fig. 5 is the block diagram of employing according to the dc-dc step-down controller of an example of the single-phase voltage mode controller of the embodiment realization of an example of the present invention;

Fig. 6 is according to the embodiment of an example of the present invention block diagram with the simplification of the embodiment of an example of the single-phase voltage mode controller of a kind of bilateral Fig. 5 that realizes along modulation system that utilizes double slanted;

Fig. 7 is the schematic block diagram of simplification of embodiment of an example of the oscillator of Fig. 6;

Fig. 8 is the block diagram of employing according to the dc-dc step-down controller of an example of the two-phase voltage mode controller of the embodiment realization of an example of the present invention;

Fig. 9 is the block diagram according to the simplification of the embodiment of an example of the two-phase voltage mode controller of Fig. 8 that utilizes the realization of double slanted signal of the embodiment of an example of the present invention;

Figure 10 is a series of sequential chart of describing according to the example operations of the two-phase voltage mode controller of Fig. 9 of several embodiment of the present invention;

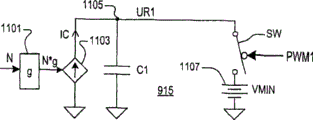

Figure 11 is the block diagram according to the simplification of the acclivity generator of Figure 10 of the embodiment of an example of the present invention; And

Figure 12 is the block diagram according to the simplification of the embodiment of an example of the N phase voltage mode controller that utilizes the realization of double slanted signal of the embodiment of an example of the present invention.

Embodiment

The following description is suggested to make that the common skill able one with this technology can finish and utilize the present invention who is proposed as under the background of a specific application and necessary condition thereof.Yet various modifications for this preferred embodiment will be significantly to those skilled in the art, and may be used on other embodiment in this defined general principle.Therefore, the present invention does not plan to be subject to specific embodiment shown here and described, but desire based on in this disclosed principle and features of novelty the widest consistent scope.

Fig. 1 is an a series of sequential chart of describing a kind of known leading edge modulation mode.Clock (CLK) pulse is illustrated in the top, and in the middle of sawtooth waveforms waveform signal RAMP and compensating signal COMP are illustrated in together and the value to point out that it is relative of overlapping, and the pulse width modulation that is produced (PWM) signal is illustrated in below.The RAMP signal that is used for this mode presents the repetition negative ramp and also is known as downward ramp signal.In this mode, the forward position of each pulse of this pwm signal (rising edge along) be by this RAMP signal and this COMP signal compare determine that the back edge of each pulse of this pwm signal (trailing edge along) then is to decide according to this CLK signal.Load transient causes corresponding transformation on this COMP signal, promptly as shown in 101.This COMP changes 101 makes the conducting relatively apace of this pwm signal.Yet the pwm pulse 103 that this produced is kept conducting, when present switching cycle finishes in next CLK pulse generation till, this produces turn-off delay.This turn-off delay causes undesirable result, for example, in the fast-transient applications of reality (VRM (voltage regulator module) such as CPU uses), can cause ring ripple (ring-back), higher release load voltage spike, or the like.

Fig. 2 describes a kind of known back a series of sequential chart along modulation system.Similarly, this CLK pulse is illustrated in the top, and in the middle of this RAMP and COMP signal be illustrated in with being overlapped, and the pwm signal that this produced is illustrated in below.The RAMP signal that is used for this mode presents the repeated forward slope and also is known as the acclivity signal.As shown in the figure, this each pwm pulse of CLK signal conduction, and determined along comparing by this RAMP signal and this COMP signal after each pulse of this pwm signal.Similarly load transient causes corresponding transformation on this COMP signal, promptly as shown in 201.Yet, in case after previous pwm pulse 203 was turned off, this pwm signal can remain in the off state, when this switching cycle finishes in next CLK pulse till, this produces on-delay.In this example, for occur in this back along after and the next rising edge of the pwm signal of next pulse 205 along before COMP change 201 almost not response or basic not responses.This on-delay produces the higher voltage spike during applying the transient event of load.

Fig. 3 describes a kind of known bilateral a series of sequential chart along modulation system.Similarly, this CLK pulse is illustrated in the top, and in the middle of this RAMP and COMP signal be illustrated in with being overlapped, and the pwm signal that this produced is illustrated in below.As well known by persons skilled in the art, the RAMP that is used for this mode is the repeated forward slope and the negative ramp of symmetry, and wherein this RAMP voltage of signals reduced in the preceding half period, and in the interim increase of second half.Being used for this known bilateral RAMP signal along modulation system is " fixing ", makes the switching rate of its frequency and rise and fall pulse preset.Before in any one switching cycle, have a plurality of pulses, the forward position of each pulse of this pwm signal to occur over just in the half period, and should edge, back to occur over just second half interim.Similarly load transient causes the transformation of the correspondence shown in 301 on this COMP signal.If this COMP changes 301 and begins as shown in figure after the back edge of previous pulse 301, and end then still existed conducting and turn-off delay before the rising edge of the following edge of the next pulse 305 of this pwm signal.This kind transformation is asynchronous for this RAMP signal.

Fig. 4 is a kind of bilateral a series of sequential chart along modulation system that utilizes double slanted of describing according to the embodiment of an example of the present invention.In this example, this CLK pulse is illustrated in the top, then be with this COMP signal overlap to down-slope waveform signal DR, then be the acclivity waveform signal UR that overlaps with this COMP signal, then be the pwm signal that is produced, all signals are all drawn with respect to the time.This COMP signal pin is for this UR and DR signal and be repeated and overlap, to point out the relative switching point of this pwm signal.As being painted by the solid line of downward ramp signal DR, for each clk cycle, this DR signal begins and reduces with fixing speed from the voltage V1 of its maximum level when the next pulse of CLK signal, and gets back to V1 during then at DR=COMP or in next CLK pulse generation.In this first embodiment, this DR signal all remains on V1 in the remaining time of this clk cycle, till the CLK pulse begins next clk cycle once again.Or this DR slope is shaped as just as the known leading edge modulation RAMP signal shown in the dotted line, and therefore continues slope decline, till next CLK pulse.When this DR signal becomes (or when next CLK pulse) when equaling COMP, this pwm signal is asserted to height.Therefore, this DR signal is the leading-edge ramp signal in forward position that is used to determine each pulse of this pwm signal.This acclivity signal UR begins to rise on voltage V2 and the beginning slope, place, forward position at each pwm pulse, and stops the slope variation when UR=COMP.When this UR signal becomes when equaling COMP, this pwm signal de-asserted as low, and this UR signal is got back to V2.Therefore, this UR signal is back edge back along ramp signal that is used to determine each pulse of this pwm signal.

Similarly load transient causes corresponding transformation on this COMP signal, promptly as shown in 401.When this COMP signal changes when changing shown in 401 as this COMP under this transient event, this COMP signal intersects this DR signal at time t1, promptly as shown in 403, to begin the forward position of this pwm signal.In this way, this pwm signal triggers quickly in a kind of mode that is similar to the leading edge modulation mode in this clk cycle.Yet, in this example, this pwm signal trigger ahead of time also rising edge edge at initial this UR signal of time t1.Suppose this COMP signal as descending apace shown in 405, then this UR signal intersects this COMP signal at time t2 relatively apace, thereby this pwm signal is gone to assert at time t2.

The conducting that this sequential chart is described this pwm signal has short significantly delay with shutoff transformation both, thereby thing and the delay of having avoided known PWM modulation system to be worried.In this way, according to the embodiment of an example of the present invention a kind of utilize double slanted bilateral along modulation system in conjunction with forward position and back benefit along modulation system.The ramp signal of the forward position of each pwm pulse in this forward position takes place when intersecting the COMP signal.The ramp signal on this edge, back begins to do the slope and changes in the forward position of each pwm pulse.The ramp signal of the back edge of each pwm pulse on this edge, back takes place when intersecting the COMP signal.In this way, each pwm pulse begin and halt all related with the CLK signal relief, thereby this pwm pulse just begins where necessary, just stops where necessary, and have one section suitably and fixed the duration, but not artificially according to this CLK signal according to this COMP signal.

Fig. 5 is the block diagram of a kind of employing according to the dc-dc step-down controller 500 of the example of the single-phase voltage mode controller 501 that embodiment realized of an example of the present invention.This controller 501 has the PWM pin of the input that is coupled to drive circuit 503, and this PWM pin drives the grid of electronic switch Q1 and Q2, and this switch Q1 and Q2 have the controlled current flow path between input voltage VIN of being coupled in and the power ground (PGND).Switch Q1, Q2 call with the Q label, and be shown as to example the expression of the simplification of field-effect transistor (FET), be appreciated that wherein this switch Q1, Q2 can be implemented as any suitable electronic switching device, for example, N passage device, P passage device, metal-oxide semiconductor (MOS) FET (MOSFET), bipolar junction transistor (BJT), igbt (IGBT) or any other dispose as the known electronic switch of those skilled in the art.In this example, the drain electrode of Q1 is coupled to VIN and its source electrode is coupled to phase node PH, and this phase node PH is coupled to the drain electrode of Q2.The source electrode of Q2 is coupled to PGND.Unless otherwise, otherwise node and the signal that is loaded with thereof adopt identical title.This PH node is coupled to the end of output inductor L, and this output inductor L makes its other end be coupled to output voltage node V0 (producing output signal V0).V0 comes filtering in addition by resistor-capacitor circuit circuit RC1, and is provided across being coupled in the loading resistor RL between V0 and the PGND.V0 is fed to the feedback pin FB of controller 501 by resistor R 1.Another resistor-capacitor circuit circuit RC2 is coupled between the FB pin and compensation pin COMP of controller 501.Frequency setting resistor R FS is coupled between the frequency setting pin FS and signal ground (GND) of controller 501.As understood by one of ordinary skill in the art, conducting when Q1 turn-offs at Q2, to produce this output signal V0 by inductor L coupling VIN, then Q1 is turned off and Q2 is switched on coupling L to GND, and this handoff procedure is repeated under the PWM of controller 501 output control.The frequency of the clock signal in general this PWM cycle of control is programmable in the particular range that is determined by resistor R FS.

Fig. 6 is the block diagram of simplification of embodiment that utilizes an example of the bilateral single-phase voltage mode controller of realizing along modulation system 501 that utilizes double slanted according to the embodiment of an example of the present invention a kind of.This FB pin is provided to anti-phase (-) input of error amplifier (E/A) 601, and the reference voltage V REF that is provided by reference circuit 603 is provided in its noninverting (+) input this error amplifier (E/A) 601.This COMP pin is coupled to the output of E/A601, and it further is coupled to noninverting (+) input of first comparator 605 and anti-phase (-) input of another comparator 607.This FS pin is coupled to pierce circuit 609, and this pierce circuit 609 has first output and exports so that this acclivity signal UR to be provided the noninverting input to comparator 607 so that the anti-phase input and second of this downward ramp signal DR to comparator 605 to be provided.The output that comparator 605 produces " setting " signal CS is provided to the setting input S of R-S trigger 611, and the output of comparator 607 generation " replacement " signal CR is provided to the replacement input R of R-S trigger 611.The Q of this R-S trigger 611 output produces and is provided to the pwm signal of the PWM pin of (and be via) controller 501.This R-S trigger 611 is used as the pulse control logic to control the state of this pwm signal according to the output of comparator 605 and 607.This pwm signal arrives pierce circuit 609 in internal feedback.

Fig. 7 is the general block diagram according to the simplification of the pierce circuit 609 of the embodiment of an example of the present invention.This pierce circuit 609 comprises and is used to second ramp circuit 708 that produces first ramp circuit 706 of this downward ramp signal DR and be used to produce this acclivity signal UR.For this first ramp circuit 706, voltage source 701 provides the terminal of V1 voltage to single-pole single-throw(SPST (SPST) switch S 1, and switch S 1 makes its another terminal be coupled to the node 702 that produces the DR signal that is provided to this comparator 605.Node 702 is coupled to the input of an end and the current sink IC1 of capacitor CP1.The other end of this capacitor CP1 and the output of current sink IC1 are coupled to GND respectively.For this second ramp circuit 708, another voltage source 703 provides the terminal of V2 voltage to another spst switch S2, and switch S 2 makes its another terminal be coupled to the node 704 that produces the UR signal that is provided to this comparator 607.Node 704 is coupled to the input of an end and the current source IC2 of capacitor CP2.The other end of this capacitor CP2 and the input of current source IC2 are coupled to GND respectively.The second clock signal T2 that sequential control circuit 705 produces the first clock signal T1 of the control input that is provided to switch S 1 and is provided to the control input of switch S 2.The CLK signal that is produced by oscillator 707 is provided to sequential control circuit 705, and has the frequency that resistor R FS determined that couples by outside as discussed previously.This pwm signal is provided to sequential control circuit 705 to be used to control the sequential of this DR and UR ramp signal.In an alternative embodiment, can utilize CS and CR signal to substitute pwm signal.

This sequential control circuit 705 asserts that the T1 signal is high, resets this DR signal to the V1 voltage level with Closing Switch S1.This sequential control circuit 705 asserts that the T1 signal is low, and with cut-off switch S1, thereby this current sink IC1 discharges to produce the negative ramp of this DR signal for this capacitor CP1.In one embodiment, it is low that this sequential control circuit 705 keeps this T1 signal, till the next pulse of this CLK signal, thereby this DR signal is similar to the slope decline constantly of known leading edge modulation mode, and assert that then this T1 signal gets back to this V1 voltage level for high with the Closing Switch S1 DR that resets, to begin next clk cycle.In an alternative embodiment, this sequential control circuit 705 becomes Closing Switch S1 when high at pwm signal, gets back to V1 with this DR signal of early resetting in this clk cycle.When if this DR signal was reset before next CLK pulse, then it keeps till the next pulse of CLK.

This sequential control circuit 705 asserts that the T2 signal is high, resets this UR signal to the V2 voltage level with Closing Switch S2.This sequential control circuit 705 asserts that this T2 signal is low, and with cut-off switch S2, thereby this current source IC2 charges to produce the forward slope of this UR signal for capacitor CP2.This sequential control circuit 705 according to this pwm signal (or CS and CR signal) to come control switch S2 via the T2 signal.When this pwm signal is low, this sequential control circuit 705 comes Closing Switch S2 so that this UR signal is remained on V2 via the T2 signal.When this pwm signal is asserted to when high, it is the CP2 charging to allow that IC2 comes that this sequential control circuit 705 comes cut-off switch S2 via this T2 signal, to produce the acclivity of this UR signal.

The operation that is subjected to the pierce circuit 609 of sequential control circuit 705 controls is described by the sequential chart of Fig. 4 and the block diagram of Fig. 6.When this DR signal dropped to COMP voltage of signals level, this CS signal was asserted to high setting this R-S trigger 611, thereby this R-S trigger 611 asserts that this pwm signal is for high.This sequential control circuit 705 disconnects this switch S 2 to begin the rate of rise of this UR signal.When this UR signal rose to COMP voltage of signals level, this CR signal was asserted to high with replacement R-S trigger 611, thereby this R-S trigger 611 is withdrawn into this pwm signal low.These sequential control circuit 705 closed these switch S 2 are got back to V2 with this UR signal of resetting.This DR signal and COMP signal relatively trigger asserting of this pwm signal, this pwm signal then triggers the rate of rise of this UR signal.This this pwm signal of UR signal deciding the duration, this pwm signal is pulled back to low when this UR signal rises to the level of COMP signal.

The switching rate of this UR signal in proportion to this input voltage VIN, PH node voltage, across the voltage of output inductor L or any selected combination of peak value, mean value or immediate current by this output inductor L.This VIN and/or PH voltage can directly feed back to controller 501 or be judged by various sensing apparatus indirectly.The technology that many kinds are used for the electric current of sensing output inductor L is known.

Fig. 8 is the block diagram of employing according to the dc-dc step-down controller 800 of an example of the two-phase voltage mode controller 801 that embodiment realized of an example of the present invention.This dc-dc step-down controller 800 is similar to this dc-dc step-down controller 500, thereby similar assembly or the identical label of assembly employing.This two-phase voltage mode controller 801 is similar to this single-phase voltage mode controller 501, and comprises FS, FB and COMP pin.Yet this controller 801 comprises first and second PWM pin PWM1 and PWM2, is used to control first and second phase circuit 802,804 of this two-phase system.The PWM1 pin of controller 801 is coupled to the input of first drive circuit 803 (DRIVER1) of first phase circuit 802, wherein this first drive circuit 803 drives the grid of (this first phase circuit 802) electronic switch Q1 and Q2, and this switch Q1 and Q2 have the in check current path between input voltage VIN of being coupled in and the PGND.This drive circuit 803 and switch Q1 and Q2 are configured and are coupled to the drive circuit 503 that is same as this dc-dc step-down controller 500 in fact and the mode of switch Q1 and Q2 operates.The PWM2 pin of controller 801 is coupled to the input of second drive circuit 805 (DRIVER2) of second phase circuit 804, wherein this second drive circuit 805 drives the grid of (this second phase circuit 804) electronic switch Q3 and Q4, and this switch Q3 and Q4 have the in check current path between input voltage VIN of being coupled in and the PGND.This drive circuit 805 and switch Q3 and Q4 also are configured and are coupled to the drive circuit 503 that is same as this dc-dc step-down controller 500 in fact and the mode of switch Q1 and Q2 operates.Yet for dc-dc step-down controller 800, the source electrode of Q1 and the drain electrode of Q2 are coupled in together at the first phase node PH1 place, and are coupled to the end of (this first phase circuit 802) the first output inductor L1.Similarly, the source electrode of Q3 and the drain electrode of Q4 are coupled in together at the second phase node PH2 place, and are coupled to the end of (this second phase circuit 804) the second output inductor L2.The other end of this output inductor L1 and L2 is coupled in together at the output node place that produces output signal V0.

All the other of this dc-dc step-down controller 800 partly are to be same as dc-dc step-down controller 500 in fact.Especially, V0 comes filtering in addition by resistor-capacitor circuit circuit RC1, and is provided across being coupled in the loading resistor RL between V0 and the PGND.V0 is fed to the feedback pin FB of controller 801 by resistor R 1.Another resistor-capacitor circuit circuit RC2 is coupled between the FB pin and compensation pin COMP of controller 801.Frequency setting resistor R FS is coupled between the frequency setting pin FS and GND of controller 801.The frequency of the clock signal in general this PWM cycle of control is programmable in the particular range that is determined by resistor R FS.The suitably correct of specific component value of RC1, RL, R1, RFS and RC2.As understood by one of ordinary skill in the art, except these two phase places were the running out of phase of 180 degree each other, each phase place operated at dc-dc step-down controller 500 described modes to be same as in fact as above.Electric current by this output inductor L1 is illustrated as the first phase current I1, and the electric current by this output inductor L2 is illustrated as the second phase current I2, and total output current of two phase places is illustrated as flowing into the total current IT of the output node that produces the V0 signal.Electric current by this loading resistor RL is illustrated as load current IL.

Fig. 9 is the block diagram according to the simplification of the embodiment of an example of the two-phase voltage mode controller 801 that utilizes the realization of double slanted signal of the embodiment of an example of the present invention.This FB pin is provided to the anti-phase input of error amplifier (E/A) 901, and the reference voltage V REF that is provided by reference circuit 903 is provided in its noninverting input this error amplifier (E/A) 901.This COMP pin is coupled to the output (this COMP signal is provided) of this E/A901, and this output further is coupled to the noninverting input of first comparator 907 and another comparator 917, and is coupled to the input of current balance circuit 913 and 923.This FS pin is coupled to oscillator and downward ramp generator circuit 905, and this downward ramp generator circuit 905 has first output that the anti-phase input of the first downward ramp signal DR1 to comparator 907 is provided and second output that the anti-phase input of the second downward ramp signal DR2 to comparator 917 is provided.The output of current balance circuit 913 provides the first adjusted compensating signal CMP1, and this first adjusted compensating signal CMP1 is provided to the anti-phase input of another comparator 909.The output of current balance circuit 923 provides the second adjusted compensating signal CMP2, and this second adjusted compensating signal CMP2 is provided to the anti-phase input of another comparator 919.The output of comparator 907 generations, first setting or " beginning " signal CS1 is provided to the setting input S of a R-S trigger 911.The output of comparator 909 generations, first replacement or "signal for " stop " CR1 is provided to the replacement input R of R-S trigger 911.The output of comparator 917 generations, second setting or commencing signal CS2 is provided to the setting input S of the 2nd R-S trigger 921.The output of comparator 919 generations, second replacement or stop signal CR2 is provided to the replacement input R of R-S trigger 921.

The Q of this R-S trigger 911 output produces and is provided to the PWM1 signal of the PWM1 pin of (and for via) controller 801, and the Q of this R-S trigger 921 output produces and be provided to the PWM2 signal of the PWM2 pin of (and for via) controller 801.This PWM1 and PWM2 signal are provided to the corresponding input of impulse summation device 927, this impulse summation device 927 has output so that number of phases or pulse counting signal " N " first input to the first acclivity generator 915 to be provided, and this first acclivity generator 915 has second input that receives this PWM1 signal.This acclivity generator 915 has the output of the noninverting input that is coupled to comparator 909, to be used to provide the first acclivity signal UR1.This n-signal and PWM2 signal are provided to the corresponding input of the second acclivity generator 925, and this second acclivity generator 925 has the output of the noninverting input that is coupled to comparator 919, to be used to provide the second acclivity signal UR2.In the embodiment that is enumerated, N is the integer that determines the sum (or sum of deputy activity phase place) of the pwm signal that is switched on simultaneously.Therefore, when PWM1 and PWM2 both when low, this impulse summation device 927 output N=0, any in PWM1 and PWM2 signal (but non-both) be when being high, N=1, and as PWM1 and PWM2 signal both when being high, N=2.

This current balance circuit 913 and 923 integrally constitutes current balance system, and wherein the running of each current balance circuit is adjusted this COMP signal with the phase current according to the correspondence of the total current IT of two phase places and respective phase I1 or I2.In one embodiment, for phase place 1, the output of this current balance circuit 913 is COMP+k* (I2-I1), and wherein " k " is the gain factor of fixing, and I1 is the electric current (by output inductor L1) of phase place 1, and multiplication represented in this asterisk " * ".Similarly, for phase place 2, the output of this current balance circuit 923 is COMP+k* (I1-I2), and wherein I2 is the electric current (by output inductor L2) of phase place 2.Corresponding current signal can utilize in the certain methods well known by persons skilled in the art any to come in addition sensing.In this embodiment, when I1 and I2 were equal to each other, this current balance circuit 913 and 923 did not influence running.

Figure 10 is a series of sequential chart of describing according to the action of the example of the two-phase voltage mode controller 801 of several embodiment of the present invention.This current balance circuit 913 and 923 action are left in the basket, to simplify the action explanation of leggy example.This IL electric current is illustrated in the top, it then is first clock signal clk 1, then be the first downward ramp signal DR1 that overlaps with this COMP signal, then be the first acclivity signal UR1 that overlaps with this COMP signal, it then is the first phase place PWM1 signal, then be second clock signal CLK2, then be the second downward ramp signal DR2 that overlaps with this COMP signal, then be the second acclivity signal UR2 that overlaps with this COMP signal, then be the second phase place PWM2 signal, draw with respect to the time all.This COMP signal is repeated and overlaps with this UR1, UR2, DR1 and DR2 signal, to point out the relative switching point of this PWM1 and PWM2 signal.This UR1 and UR2 signal begin at initial voltage level VMIN place.This oscillator produces first and second clock signal clk 1 and the CLK2 of the pulse with 180 degree out-phase with downward ramp generator circuit 905 in inside.This first downward ramp signal DR1 and this CLK1 signal Synchronization, and this second downward ramp signal DR2 and this CLK2 signal Synchronization.This DR1 and DR2 signal generally have identical form and switching rate.Therefore switching rate is configured to approaching as much as possible, and is regarded as impartial in fact.This IL electric current upwards steps to higher current level IL2 at time t1 from lower current level IL1, and this represents load transient, and this load transient causes corresponding transformation on this COMP signal, promptly as shown in 1001.This IL electric current rolls back IL1 under follow-up time t10, this causes the decline a little of the COMP signal shown in 1003.

In first embodiment, this acclivity signal UR1 and UR2 have identical general type and switching rate (impartial in fact) m1, and promptly shown in dotted line.At time t1, the transformation 1001 big risings very apace when this DR2 signal has almost dropped to the original level of this COMP signal of this COMP signal.Therefore, greatly about time t1, COMP rises to and intersects DR2, makes comparator 917 switch to this CS2 signal drawn to be height, and this sets R-S trigger 921 and at time t1 the PWM2 signal is drawn and is height.Soon time t2 after time t1, this COMP rises to DR1, and this switches comparator 907.Comparator 907 draws the CS1 signal and is height, and this sets R-S trigger 907 and at time t2 the PWM1 signal is drawn and is height.In this first embodiment, the UR2 signal rises with switching rate m1 as continuing shown in 1005,, is transformed into downwards between at this moment till follow-up time t5 intersects this COMP signal up to it.When this UR2 signal when the time, t5 rose to COMP, comparator 919 assert the CR2 signal for high with replacement R-S trigger 921, thereby this R-S trigger 921 draws the PWM2 signal into low at time t5.In the near future, the UR1 signal rises to COMP at time t6, makes comparator 909 assert the CR1 signal with replacement R-S trigger 911, and at time t6 the PWM1 signal is drawn to low.

The sequential chart of Figure 10 describes to be applied to the General Principle of the double slanted system of two phase places.For the transformation of the conducting of the pwm signal of correspondence and shutoff, each phase place all presents significantly short delay, thereby the thing worried of known PWM modulation system and postpone all to be avoided.Although have only two phase places to be demonstrated, those skilled in the art can recognize that now the number of phases of any reality all can be implemented.The running of those phase places is in the phase angle side-play amount of relative to each other correspondence.For example, for four phase places, phase place is the 90 degree phase differences that operate relative to each other.In this way, according to the double slanted modulation system of the embodiment of an example of the present invention in conjunction with this forward position and back along the benefit of modulation system to be used to have the Power Conversion of arbitrary phase number.

Institute will be appreciated that whenever load transient takes place, and at least one phase place respond very apace, and according to this transformation the duration, a plurality of phase places respond fast and effectively to handle the increase of this load under the delay of significantly shortening.As above at shown in this two-phase example, two phase places all change 1001 in response to this quite apace, thereby two pwm pulses all are the while conducting in the duration of this transformations 1001 most.Because two phase places are to act on simultaneously, wish the shutoff of fast more this PWM1 of shortening and PWM2 pulse in certain embodiments, to reduce ring ripple or voltage spike or similar any possibility.In second embodiment that utilizes solid line to describe, the switching rate of UR1 and UR2 signal all be according to as by from the output of the n-signal of impulse summation device 927 pointed the time pwm pulse number of effect increase.At time t1, the PWM2 signal is high and this PWM1 signal still is low, thereby the UR2 signal begins to rise with common switching rate m1.Yet at time t2, the PWM1 signal is also drawn to be height, thus PWM1 and PWM2 both be high simultaneously.In this second embodiment, the switching rate of UR2 signal is increased to as the m2 shown in 1009.And because PWM1 becomes height at PWM2 when high, so the UR1 signal rises with the switching rate m2 shown in 1011.The UR2 signal time t3 before time t5 ahead of time rises to COMP.And the UR2 signal time t4 before time t6 ahead of time rises to COMP.In this way, the switching rate of UR1 and UR2 signal is adjusted (for example, increasing) according to the pwm signal sum of effect simultaneously.

Figure 11 is the block diagram according to the simplification of the acclivity generator 915 of the embodiment of an example of the present invention.This acclivity generator 925 is configured in identical in fact mode, thereby is no longer further described.N-signal is provided to gain circuitry 1101, and this gain circuitry 1101 is multiplied by gain factor " g " with N and exports the control input of this value N*g to controlled current source 1103.The output that this current source 1103 has the input that is coupled to GND and is coupled to the node 1105 that produces acclivity signal UR1.Node 1105 is coupled to the end of capacitor C1 and the terminal of spst switch SW.The other end of this capacitor C1 is coupled to GND, and second terminal of this switch SW is coupled to the plus end of the voltage source 1107 that produces VMIN voltage.The negative terminal of this voltage source 1107 is coupled to GND.This switch SW has the anti-phase control terminal that receives this PWM1 signal.

In operation, when the PWM1 signal when low, switch SW closure, thereby the UR1 signal is pulled down to voltage level VMIN.Recall in Figure 10, when the PWM1 signal when low, the UR1 signal is reset and is got back to VMIN.When the PWM1 signal is drawn when high, its cut-off switch SW, thereby current source 1103 produces charging current IC and comes the charging for this capacitor C1.When switch SW was disconnection, the voltage of UR1 increased according to the amplitude of IC.The amplitude of IC is the default nominal value that is multiplied by factor N*g.As discussed previously, for N=1, the switching rate of UR1 is m1, and when N=2, the switching rate of UR1 is m2.In the embodiment that is described, m2 is the twice of m1.Although be not shown, another higher voltage source can in be contained in wherein, and be coupled to node 1105 via diode or like, with the voltage level of restriction UR1 to default maximum level.

Figure 12 is the block diagram according to the simplification of the embodiment of an example of the voltage mode controller 1200 that utilizes the N phase place that the double slanted signal realized of the embodiment of an example of the present invention.The voltage mode controller 1200 of N phase place is similar to two-phase voltage mode controller 801 in configuration and action, except it is controlled up to " N " individual phase place, wherein N is any greater than 0 positive integer (and if desired words, it can be utilized to control single phase place).This controller 1200 comprises FS, FB and COMP pin in a kind of mode that is similar to controller 801.This controller 1200 comprises E/A 1201 (being similar to E/A 901), and its anti-phase input is coupled to the FB pin and its noninverting input receives reference voltage V REF.VREF provides by reference circuit 1203 (being similar to reference circuit 903).The output of E/A 1201 provides this COMP signal, this COMP signal further is provided to each in COMP pin and N the PWM controller 1207, this N PWM controller 1207 be denoted as respectively PWM1 controller, PWM2 controller, PWM3 controller ..., the PWMN controller.These PWM controllers 1207 have output respectively so that the pwm signal of a correspondence among N the pwm signal PWM1-PWMN to be provided, and this N pwm signal is provided to corresponding pin PWM1-PWMN.The PWM1-PWMN signal also is provided to the corresponding input of impulse summation device 1209, and this impulse summation device 1209 has output to provide N number of phases signal to each PWM controller 1207.This impulse summation device 1209 operates in a kind of mode that is similar to impulse summation device 927, except the pwm pulse of addition effect simultaneously up to N.Oscillator is replaced by similar oscillator and downward ramp generator circuit 1205 with downward ramp generator circuit 905, this oscillator have the input that is coupled to the FS pin with downward ramp generator circuit 1205 and provide corresponding downward ramp signal DR1, DR2, DR3 ..., N the output of DRN, wherein each downward ramp signal DR1-DRN is provided to a PWM controller of this N the correspondence in the PWM controller 1207.

This generator circuit 1205 operates in a kind of mode that is similar to generator circuit 905, except it separates the suitable nominal phase angle of these downward ramp signals, this phase angle according to effect in operation or selected number of phases and deciding.For example, for two phase places, two downward ramp signal DR1 and DR2 divide and (for example open 180 degree, 0,180), for four phase places, four downward ramp signal DR1, DR2, DR3 and DR4 branches (are for example opened 90 degree, 0,90,180,270), for six phase places, six downward ramp signal DR1-DR6 separately 60 degree (for example, 0,60,120,180,240,320), the rest may be inferred.Each PWM controller 1207 (for example comprises current balance circuit, be similar to 913), it receives the COMP signal and corresponding amended compensating signal is provided, the acclivity generator (for example, be similar to 915), it has the input of the pwm signal that receives N number of phases signal and correspondence and the output that the acclivity signal of correspondence is provided, first comparator (for example, be similar to 907), downward ramp signal that it is relatively corresponding and COMP signal and setting signal is provided, second comparator (for example, be similar to 909), its relatively corresponding amended compensating signal is with corresponding acclivity signal and reset signal is provided, and the PWM logic (for example, be similar to R-S trigger 911), it receives setting and reset signal and corresponding pwm signal is provided.The pwm pulse signal sum that the switching rate of each acclivity signal of each phase place is switched on when being determined as the N number of phases signal that is provided by impulse summation device 1209 is adjusted.

Although the present invention is at length described with reference to its some preferable form, other form and variation remain feasible and are taken into account.For example, this slope and comparator can be inverted, and these signals can be replicated for realization and be offset, this control method can correspond to the digital control approach that is equal to, or the like.The present invention may be used on some synchronous and asynchronous suitching type adjuster topology.In addition, polarity can be exchanged to be used for negative voltage regulator.Those skilled in the art are to be appreciated that it can use disclosed notion and certain embodiments as the basis that is used to design or revise other structure easily, with the purpose of the present invention that is used to provide identical, and do not break away from as following purport of the present invention and scope that claim limited.

Claims (24)

- One kind bilateral along modulation controller, it comprises:First ramp circuit, it provides the leading-edge ramp signal with a clock signal Synchronization;Error amplifier, it compares feedback signal and reference signal, and the signal that affords redress;First comparator, it compares described leading-edge ramp signal and described compensating signal, and asserts setting signal;Second ramp circuit, it provides the back along ramp signal, and described back begins to do the slope along ramp signal and changes when described setting signal is asserted;Second comparator, it compares described back along ramp signal and described compensating signal, and asserts reset signal; AndThe pulse control logic, it asserts pwm signal when described setting signal is asserted, and removes to assert described pwm signal when described reset signal is asserted.

- 2. as claimed in claim 1 bilateral along modulation controller, it is characterized in that described first ramp circuit begins to make described leading-edge ramp signal to do the slope variation from first voltage level in each pulse of described clock signal.

- 3. as claimed in claim 1 bilateral along modulation controller, it is characterized in that when described pwm signal is asserted, described second ramp circuit begins to make described back to do the slope along ramp signal from first voltage level and changes, and described first voltage level is got back to along ramp signal in the described back of resetting when described pwm signal is gone to assert.

- 4. as claimed in claim 1 bilateral along modulation controller, it is characterized in that described first ramp circuit is downward ramp generator, and wherein said second ramp circuit is the acclivity generator.

- 5. as claimed in claim 1 bilateral along modulation controller, it is characterized in that described pulse control logic comprises the R-S trigger.

- 6. as claimed in claim 1 bilateral along modulation controller, it is characterized in that described pwm signal control commutation circuit, described commutation circuit is coupled to output inductor at a phase node place, by described output inductor input voltage being converted to output voltage, and wherein said second ramp circuit is according to described input voltage, phase node voltage, control the switching rate of described back along ramp signal across any combination of the voltage of described output inductor and the electric current by described output inductor.

- 7. power inverter, it comprises:First phase circuit, it is controlled by first pwm signal, to be used for via first inductor input voltage being converted to output voltage; AndThe PWM output bilateral along modulation controller, that it has the feedback input that is used for the described output voltage of sensing and is used to provide described first pwm signal, described bilaterally comprise along modulation controller:Error amplifier, it has first input that is coupled to described feedback input, second input that receives reference voltage and the output of the signal that affords redress;Oscillator, it provides the first leading-edge ramp signal with repetition slope;First comparator, it compares described first leading-edge ramp signal and described compensating signal, and asserts first setting signal;First ramp circuit, it makes first back do the slope variation along ramp signal when described first pwm signal is asserted;Second comparator, its more described first back be along ramp signal and described compensating signal, and assert first reset signal; AndThe first pulse control logic, it asserts described first pwm signal when described first setting signal is asserted, and removes to assert described first pwm signal when described first reset signal is asserted.

- 8. power inverter as claimed in claim 7 is characterized in that:Described oscillator begins to make the described first leading-edge ramp signal to descend from the first voltage level slope in each pulse of clock signal; AndWherein said first ramp circuit makes described first back rise from the second voltage level slope along ramp signal when described first pwm signal is asserted.

- 9. power inverter as claimed in claim 7 is characterized in that also comprising:Second phase circuit, it is controlled by second pwm signal, to be used for via second inductor that is coupled to described first inductor described input voltage being converted to described output voltage; AndWherein said bilaterally have the 2nd PWM output that is used to provide described second pwm signal along modulation controller, and wherein said bilaterally also comprise along modulation controller:Described oscillator, it provides the second leading-edge ramp signal with repetition slope;The 3rd comparator, it compares described second leading-edge ramp signal and described compensating signal, and asserts second setting signal;Second ramp circuit, it makes second back do the slope variation along ramp signal when described second pwm signal is asserted;The 4th comparator, it compares and asserts second reset signal with described second back along ramp signal and described compensating signal; AndThe second pulse control logic, it asserts described second pwm signal when described second setting signal is asserted, and removes to assert described second pwm signal when described second reset signal is asserted.

- 10. power inverter as claimed in claim 9, it is characterized in that the described first leading-edge ramp signal and first clock signal are synchronous, wherein said second leading-edge ramp signal and second clock signal Synchronization, and wherein said first and second clock signal is separated a phase angle.

- 11. power inverter as claimed in claim 9 is characterized in that also comprising current balance system, described current balance system is adjusted described compensating signal according to the electric current that senses of described first and second inductor.

- 12. power inverter as claimed in claim 11, it is characterized in that described current balance system comprises first current balance circuit and second current balance circuit, described first current balance circuit receives described compensating signal and provides the first adjusted compensating signal to described second comparator, and described second current balance circuit receives described compensating signal and provide the second adjusted compensating signal to described the 4th comparator.

- 13. power inverter as claimed in claim 11, it is characterized in that described first and second ramp circuit produce described first and second back along ramp signal to have the switching rate that equates basically.

- 14. power inverter as claimed in claim 11, it is characterized in that described first ramp circuit increases the switching rate of described first back along ramp signal when described second pwm signal is asserted, and wherein said second ramp circuit when being asserted, described first pwm signal increases the switching rate of described second back along ramp signal.

- 15. power inverter as claimed in claim 11 is characterized in that also comprising:The impulse summation device, it has first and second input that receives described first and second pwm signal and the output that a number of phases is provided, the pwm signal sum that described number of phases indication is asserted simultaneously;Wherein said first ramp circuit is adjusted the switching rate of described first back along ramp signal according to described number of phases; AndWherein said second ramp circuit is adjusted the switching rate of described second back along ramp signal according to described number of phases.

- 16. a method that is used to control DC-DC converter, it comprises:The first leading-edge ramp signal synchronous with clock signal is provided;With feedback signal and the reference signal signal that compares and afford redress;The described first leading-edge ramp signal and described compensating signal are compared and assert first commencing signal;When first pwm signal is asserted, makes first back do the slope and change along ramp signal;Described first back is compared and asserts first stop signal along ramp signal and described compensating signal; AndWhen described first commencing signal is asserted, assert described first pwm signal, and when described first stop signal is asserted, remove to assert described first pwm signal.

- 17. method as claimed in claim 16, it is characterized in that described each pulse that provides the first leading-edge ramp signal to be included in described clock signal begins to make the described first leading-edge ramp signal to descend from the first voltage level slope, and wherein saidly make first back do the slope to change and to be included in described first pwm signal when being asserted, begin to make described first back to rise from the second voltage level slope along ramp signal along ramp signal.

- 18. method as claimed in claim 16 is characterized in that also comprising:Between the polarity of input voltage, to switch first end of output inductor, produce output voltage according to described first pwm signal with the second end place at described output inductor; AndAccording to the voltage of first end of described input voltage, described output inductor, control the switching rate of described first back along ramp signal across any combination of the voltage of described output inductor and the electric current by described output inductor.

- 19. method as claimed in claim 16 is characterized in that also comprising:Provide with described clock signal synchronously and with the second leading-edge ramp signal of the described first leading-edge ramp signal out-phase;The described second leading-edge ramp signal and described compensating signal are compared and assert second commencing signal;When second pwm signal is asserted, makes second back do the slope and change along ramp signal;Described second back is compared and asserts second stop signal along ramp signal and described compensating signal; AndWhen described second commencing signal is asserted, assert described second pwm signal, and when described second stop signal is asserted, remove to assert described second pwm signal.

- 20. method as claimed in claim 19 is characterized in that described DC-DC converter comprises first and second phase circuit that is coupled in together, described method also comprises:Utilize described first pwm signal to control described first phase circuit and utilize described second pwm signal to control described second phase circuit;The electric current of described first and second phase circuit of sensing; AndAdjust the electric current of described compensating signal with described first and second phase circuit of balance.

- 21. method as claimed in claim 20 is characterized in that described adjustment compensating signal comprises:Adjust described compensating signal so that the first adjusted compensating signal to be provided according to the electric current that senses;Adjust described compensating signal so that the second adjusted compensating signal to be provided according to the electric current that senses;Described first back is compared along ramp signal and described compensating signal comprises and then comparing along the ramp signal and the described first adjusted compensating signal described first; AndDescribed second back is compared along ramp signal and described compensating signal comprises and then comparing along the ramp signal and the described second adjusted compensating signal described second.

- 22. method as claimed in claim 19, it is characterized in that describedly making first back do the slope to change and to comprise that making described first back do the slope along ramp signal with first switching rate changes, and wherein saidly make second back do the slope to change and comprise that making described second back do the slope along ramp signal with second switching rate that is equal to described first switching rate basically changes along ramp signal along ramp signal.

- 23. method as claimed in claim 19 is characterized in that also comprising:When described second pwm signal is asserted, adjust the switching rate of described first back along ramp signal; AndWhen described first pwm signal is asserted, adjust the switching rate of described second back along ramp signal.

- 24. method as claimed in claim 23 is characterized in that also comprising described first and second pwm signal of addition.

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US65159905P | 2005-02-10 | 2005-02-10 | |

| US60/651,599 | 2005-02-10 | ||

| US60/696,680 | 2005-07-05 | ||

| US11/318,081 | 2005-12-23 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1822479A CN1822479A (en) | 2006-08-23 |

| CN100466434C true CN100466434C (en) | 2009-03-04 |

Family

ID=36923593

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB200610008501XA Active CN100466434C (en) | 2005-02-10 | 2006-02-10 | Pwm controller with dual-edge modulation using dual ramps |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN100466434C (en) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104158387A (en) * | 2013-05-13 | 2014-11-19 | 力智电子股份有限公司 | DC-DC controller and operation method of multi-ramp signal thereof |

| TWI683520B (en) * | 2019-02-25 | 2020-01-21 | 茂達電子股份有限公司 | Multi-phase dc-dc power converter and driving method of the same |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7629823B2 (en) * | 2006-10-04 | 2009-12-08 | Power Integrations, Inc. | Method and apparatus for pulse width modulation |

| US7812581B2 (en) * | 2007-05-04 | 2010-10-12 | Intersil Americas Inc. | Pulse adding scheme for smooth phase dropping at light load conditions for multiphase voltage regulators |

| CN101325033B (en) * | 2007-06-12 | 2011-10-26 | 台达电子工业股份有限公司 | Light source drive device as well as signal conversion circuit and impulse control circuit thereof |

| JP5386801B2 (en) * | 2007-07-27 | 2014-01-15 | 株式会社リコー | Switching regulator and operation control method thereof |

| CN101499791B (en) * | 2008-01-29 | 2012-05-02 | 力博特公司 | PWM control method |

| US8188721B2 (en) * | 2008-08-05 | 2012-05-29 | Intersil Americas Inc. | Active pulse positioning modulator |

| US8076913B2 (en) * | 2008-12-22 | 2011-12-13 | Mediatek Inc. | Voltage converters and voltage generating methods for generating output voltage signals according to a pulse width modulation signal |

| CN102055306B (en) * | 2009-11-03 | 2015-02-11 | 立锜科技股份有限公司 | Saw tooth wave generator of boost-buck power supply converter and method |

| TWI434496B (en) | 2010-12-08 | 2014-04-11 | Richtek Technology Corp | Voltage regulator and pulse width modulation signal generation method thereof |

| CN102541131B (en) * | 2011-01-04 | 2014-06-04 | 立锜科技股份有限公司 | Voltage regulator and method for generating pulse width modulation signal thereof |

| TWI465011B (en) * | 2011-06-02 | 2014-12-11 | Richtek Technology Corp | Control circuit and method for a pwm voltage regulator |

| CN102377342B (en) * | 2011-08-12 | 2015-08-26 | 成都芯源系统有限公司 | Control circuit and control method for DC-DC conversion circuit |

| CN102570811B (en) * | 2012-01-09 | 2014-04-23 | 西安交通大学 | Inductance-free dual-output step-down DC-DC (Direct Current-Direct Current) converter |

| TWI496389B (en) * | 2013-05-16 | 2015-08-11 | Upi Semiconductor Corp | Timing generator and timing signal generation method for power converter |

| US9793804B2 (en) * | 2014-10-23 | 2017-10-17 | Qualcomm Incorporated | Circuits and methods for controlling a three-level buck converter |

| US9680459B2 (en) * | 2014-12-11 | 2017-06-13 | Intel Corporation | Edge-aware synchronization of a data signal |

| CN107342676B (en) * | 2017-07-26 | 2019-03-12 | 成都市易冲半导体有限公司 | A kind of method and system of control power bridge output |

| CN110932524B (en) * | 2018-08-30 | 2022-06-17 | 力智电子股份有限公司 | Controller for multi-phase power supply conversion and current balancing method |

| CN109787473B (en) * | 2019-02-19 | 2024-03-29 | 西南交通大学 | Control method and device for dual-edge modulation output voltage of boost converter |

| CN114157144B (en) * | 2021-12-07 | 2024-08-09 | 江阴市新际科技有限公司 | PWM control circuit based on multiphase DC-DC buck converter |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1128914A (en) * | 1994-08-24 | 1996-08-14 | 东芝株式会社 | Control system for single phase pulsation width modulation converter |

| CN1447506A (en) * | 2002-03-26 | 2003-10-08 | 精工爱普生株式会社 | Power circuit and PVVM circuit |

| US20040130307A1 (en) * | 2002-12-31 | 2004-07-08 | Intersil Americas Inc. State Of Incorporation: Delaware | PWM-based DC-DC converter with assured dead time control exhibiting no shoot-through current and independent of type of fet used |

| CN1529931A (en) * | 2002-07-18 | 2004-09-15 | ������������ʽ���� | Power changing device |

| US20050001597A1 (en) * | 2002-09-06 | 2005-01-06 | Intersil Americas Inc. | Synchronization of multiphase synthetic ripple voltage regulator |

-

2006

- 2006-02-10 CN CNB200610008501XA patent/CN100466434C/en active Active

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1128914A (en) * | 1994-08-24 | 1996-08-14 | 东芝株式会社 | Control system for single phase pulsation width modulation converter |

| CN1447506A (en) * | 2002-03-26 | 2003-10-08 | 精工爱普生株式会社 | Power circuit and PVVM circuit |

| CN1529931A (en) * | 2002-07-18 | 2004-09-15 | ������������ʽ���� | Power changing device |

| US20050001597A1 (en) * | 2002-09-06 | 2005-01-06 | Intersil Americas Inc. | Synchronization of multiphase synthetic ripple voltage regulator |

| US20040130307A1 (en) * | 2002-12-31 | 2004-07-08 | Intersil Americas Inc. State Of Incorporation: Delaware | PWM-based DC-DC converter with assured dead time control exhibiting no shoot-through current and independent of type of fet used |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104158387A (en) * | 2013-05-13 | 2014-11-19 | 力智电子股份有限公司 | DC-DC controller and operation method of multi-ramp signal thereof |

| CN104158387B (en) * | 2013-05-13 | 2016-09-21 | 力智电子股份有限公司 | DC-DC controller and operation method of multi-ramp signal thereof |

| TWI683520B (en) * | 2019-02-25 | 2020-01-21 | 茂達電子股份有限公司 | Multi-phase dc-dc power converter and driving method of the same |

Also Published As

| Publication number | Publication date |

|---|---|

| CN1822479A (en) | 2006-08-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100466434C (en) | Pwm controller with dual-edge modulation using dual ramps | |

| EP1691473B1 (en) | PWM controller with dual-edge modulation using dual ramps for fast response | |

| US10892686B2 (en) | Hysteretic control for transformer based power converters | |

| CN100394342C (en) | Synchronization of multiphase synthetic ripple voltage regulator | |

| US8148967B2 (en) | PWM clock generation system and method to improve transient response of a voltage regulator | |

| CN202889198U (en) | Switch type power supply and slope compensation signal generating circuit thereof | |

| CN102801288B (en) | Control circuit, switch mode converter and control method | |

| US7598715B1 (en) | Apparatus and method for reverse current correction for a switching regulator | |

| US7777460B2 (en) | Multi-phase converter with improved current sharing | |

| US7456620B2 (en) | Determining dead times in switched-mode DC-DC converters | |

| US7492136B2 (en) | Multi-phase converter with improved load step-up transient response | |

| CN107112895B (en) | Switching regulator and control method thereof | |

| US10554127B2 (en) | Control circuit and control method for multi-output DC-DC converter | |

| US9136760B2 (en) | Digital switched mode voltage regulator | |

| JP6993548B2 (en) | Transition event detector circuit and method | |

| CN103986445A (en) | Active pulse positioning modulator | |

| JP2005110498A (en) | Synchronizing of multi-phase composite ripple voltage regulator | |

| CN112688538B (en) | Quasi-constant on-time control circuit and switch converter and method thereof | |

| US20090174380A1 (en) | Fixed frequency ripple regulator | |

| WO2020205918A1 (en) | On-time timer circuit with external clock for switching converter control | |

| CN103560669A (en) | Step-up/step-down type dc-dc converter, and control circuit and control method of the same | |

| Chen et al. | Digital control for efficiency improvements in interleaved boost PFC rectifiers | |

| US20230318453A1 (en) | Control of two-stage dc-dc converter | |

| EP3312982B1 (en) | Step-up/step-down dc/dc converter | |

| CN117223205A (en) | Frequency synchronization for voltage converters |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant |