Introduction in Reconfigurable Computing using reconfigurable Systems-on-Chip. This project is an educational implementation of a custom IP module that communicates with DMAe using the AXI4 Stream Protocol. It consists of 3 different phases (Milestones).

Use VHDL to design a FIFO queue that will feed later the custom IP module with packets.

Using HLS implement a custom IP module that filters incoming packets based on predefined rules.

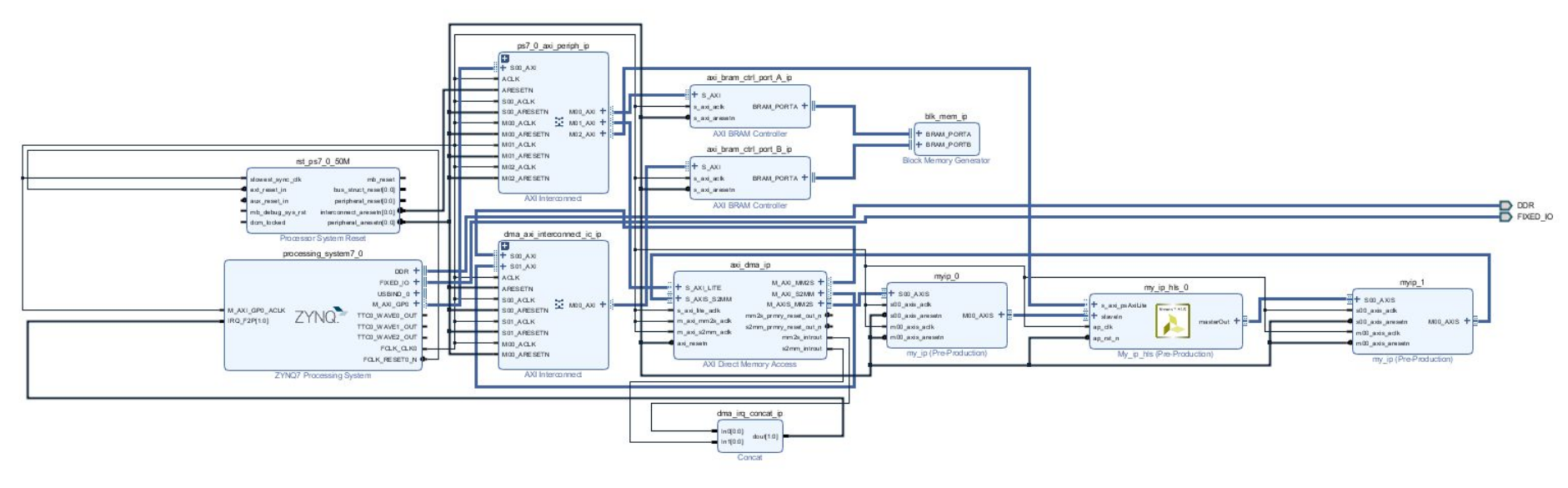

Combine IPs from the first two Milestones upon a complete - reference - system and establish communication with DMAe to transfer, filter packets and write back valid ones to BRAM.

This project was developed using both Xilinx Vivado 2017.4 and Xilinx Vivado HLS 2017.4