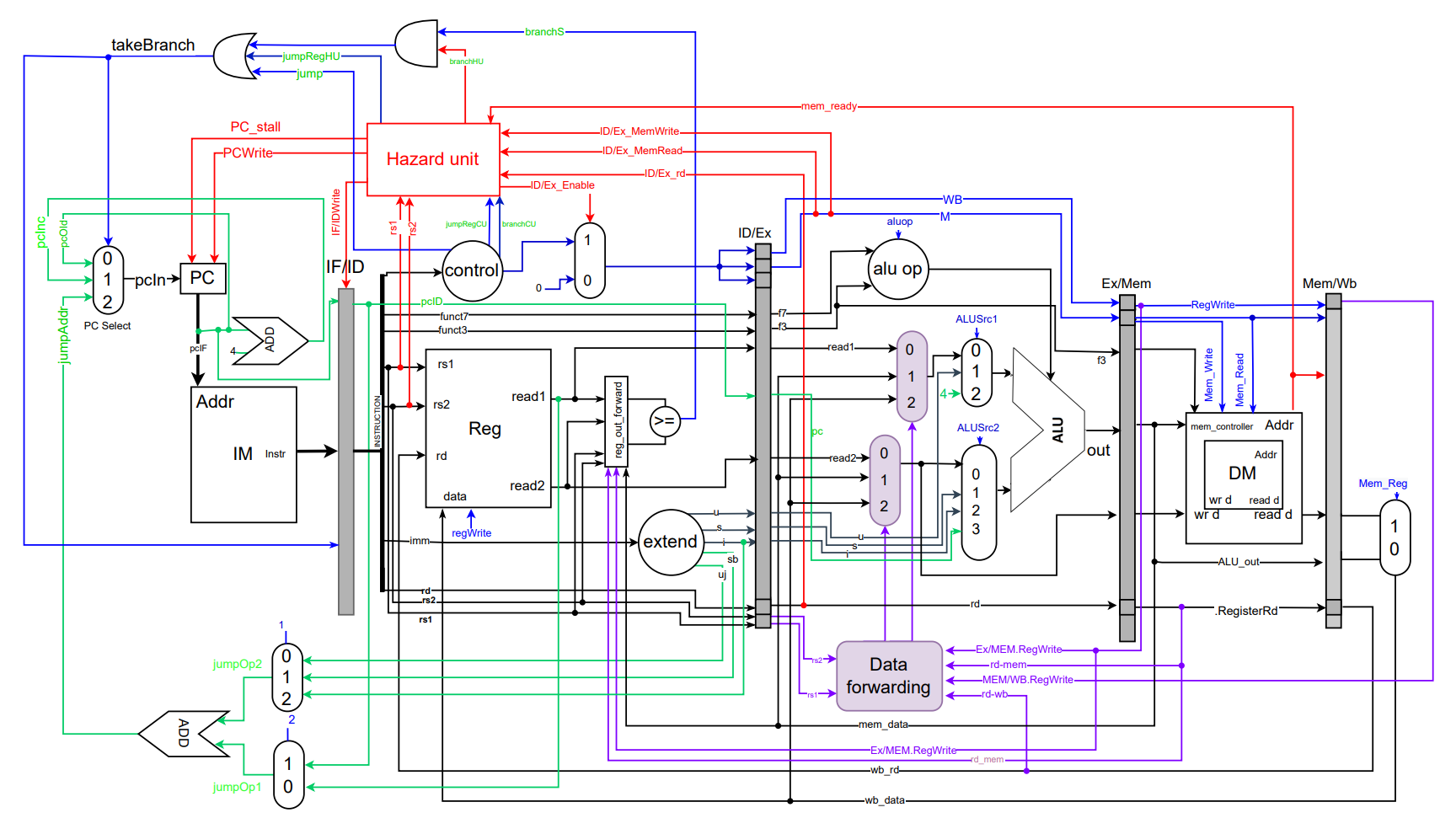

This is a RISC-V 32I processor which also supports the M extension.

- Inlude all the src/ .sv files to the project

- Add the absolute path of src/ins_mem_init.txt file to ins_memory.sv

D:\\ACA\\SEM7_TRONIC_ACA\\17 - Advance Digital Systems\\2020\\assignment_2\\SoC_project\\src\\ins_mem_init.txt(line 23) - Add the absolute path of src/data_mem_init.txt file to data_memory.sv

D:\\ACA\\SEM7_TRONIC_ACA\\17 - Advance Digital Systems\\2020\\assignment_2\\SoC_project\\src\\data_mem_init.txt(line 21) - Add the absolute path of src/data_mem_final.txt file to data_memory.sv

D:\\ACA\\SEM7_TRONIC_ACA\\17 - Advance Digital Systems\\2020\\assignment_2\\SoC_project\\src\\data_mem_final.txt(line 37) - Add the absolute path of src/reg_file_final.txt file to reg_file.sv

D:\\ACA\\SEM7_TRONIC_ACA\\17 - Advance Digital Systems\\2020\\assignment_2\\SoC_project\\src\\reg_file_final.txt(line 54) - Set top.sv as top module and compile the Project.

- For the simulation run the top_tb.sv

-

To test the processor we have supplied with 4 programs which are available in the testing folder.

-

Each folder consists of 3 files. These include;

- The assembly code.

- The generated machine code (instructions) for the respective assembly code.

- The expected instructions in the instruction memory for that particular program. (***instruction_memory.txt)

-

To test any of these programs, you can either;

- Replace the all instructions in the ins_mem_init.txt which is available in src folder with the instructions found in the ***instructionmemory.txt file mentioned above,

- Change the relevant 1st n instructions of the ins_mem_init.txt relative to the instructions available in the ***machine_code.txt.

-

The result of these programs can be checked by;

- Looking at the 1st location of the data memory (data_mem_final), after the process is over.

-

For futher testing of the aforementioned test cases follow the instuction mentioned in Testing Document