EN | 中文

Try to implement a RISC-V CPU for learning RISC-V architecture and microarchitecture by Python language

The bootloader program is stored in ROM, and which is the first program to run on CPU. So here will need ROM

Program also need RAM to store heap and stack

External flash is used to store applicaton program

- Used to connect to UART, and support input and output

- Used to control exteral LED

├── docs

│ └── images

├── fpga

├── rtl

├── src

│ ├── pipeline

├── test

│ ├── hw_tests

│ │ ├── common

│ │ ├── led_test

│ │ └── pwm_test

│ ├── rv32i_compliance

│ └── test_rom

└── tutorial

├── formal_verification

└── simulator-framework\

Storing FPGA related source code which is converted by Python code

This script is used to generate RTL code based on Python code, and will output it in rtl folder

Storing the generated verilog code

Storing software code

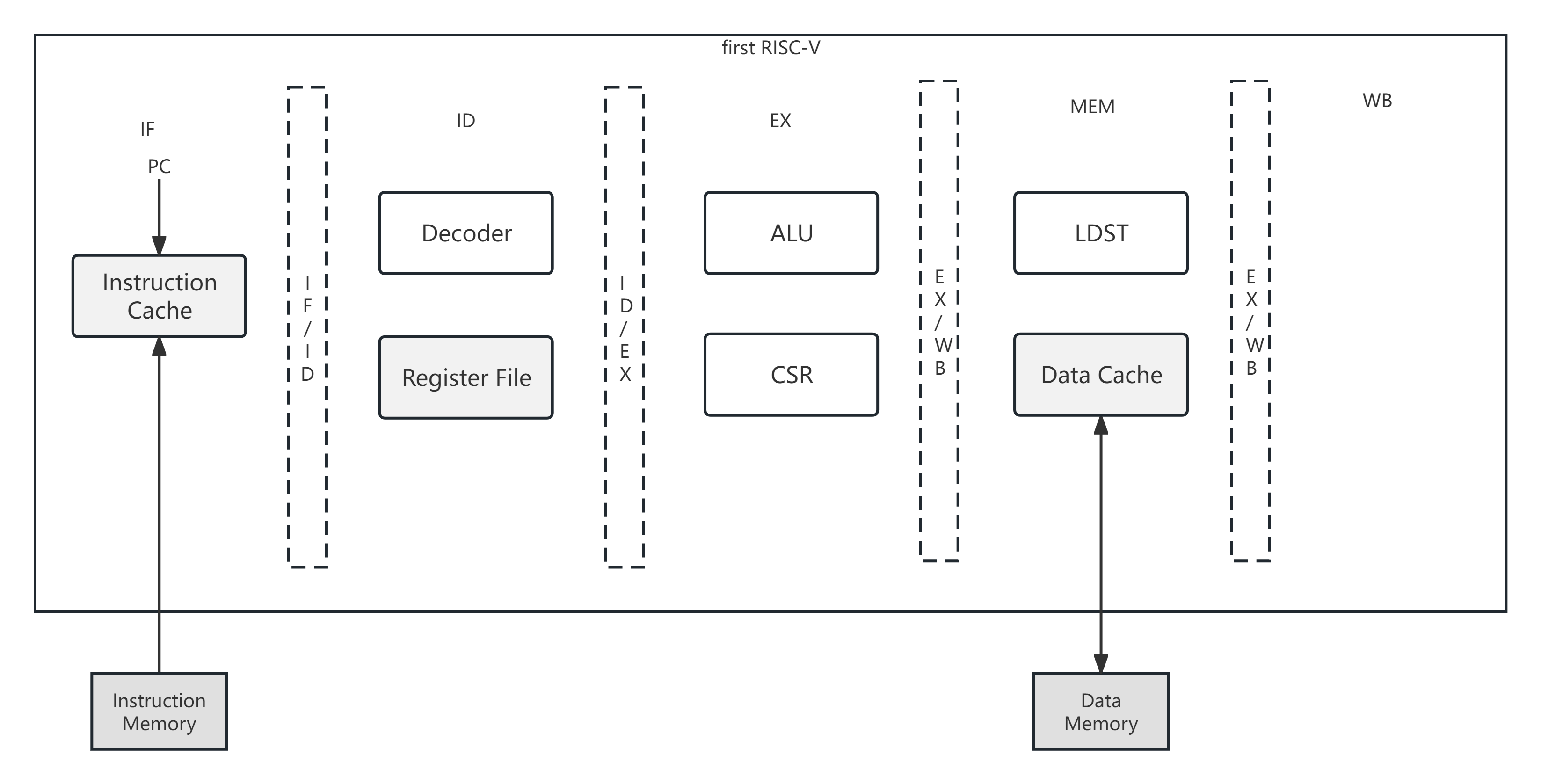

Python source code which implemente the first rsic-v

Used to test and verify the Python code in the 'src' folder, and generate waveform file