- Logikai áramkörök elmélete hülyéknek

- Könyvek

- Téma 1 - bevezetés, FPGA alapok

- Téma 2 - FPGA áramkörök szerkezete

- Téma 3 - Áramköri leírási modellek és hierarchikus alrendszerek

- Téma 4 - FPGA alapú tervezés lépései és a VHDL programok szerkezete

- Téma 5 - VHDL szekvenciális kifejezések

- a

processekről, szekvenciális áramkörökről, D típusú tárolókról - a

SIGNALokról - változók szerepe

IFfeltétel - számláló megvalsóításaIFfelCASEés multiplexer áramkörCASEhasználatávalWAIT- jelre várakozás

WAIT ONnal - adott ideg várakozás

WAIT FORral - ciklusok:

LOOP,FOR/LOOP,WHILE/LOOP,EXIT,NEXT - felhasználási példa: véges állapotú automata

- a

- Téma 7 - Konkurens VHDL utasítások

- Téma 8 - Tesztelés - eredeti pdf

- Téma 9 - System Generator alapú hardver tervezés

- Téma 10 - Hardver ko-szimuláció

- Téma 11 - Magas szintű szintézis - Bevezető

- Téma 12 - Magas szintű szintézis II

- Téma 13 - Magas szintű szintézis III

Az eredeti a Sulineten: Logikai áramkörök információelméleti alapjai alább ennek a jegyzete.

Két fizikai mennyiség (áram, feszültség) egymással való leképezése lehet

- analóg: a leképző mennyiség változása folyamatos, tehát bármilyen értéket felvehet

- digitális: a leképző mennyiség változása nem folyamatos, hanem ugrásszerű, tehát csak diszkrét értéket vehet fel. Ezt használjuk a digitális technikában, azaz az integrált áramkörökben amirtől G.Moore híres megállapítása született. Mindkét esetben az időben lefolyás függvénykapcsolattal megoldható.

Bináris számrendszer röviden

Mivel a kétállaopotú áramkörben a kettes számrendszer a legkönyebben alkalmazható így nem megkerülhető számunkra. Egy bináris szám megadása:

* ahol

a=0vagya=1Hogyan lesz az információból adat és az adatból kód

Az infomráció alapvetően bizonyos fokú tájékozatlanságot szüntet meg és szimbólumokból áll, a beszéd esetében szavak, írás esetében betűk és így tovább. Így az információ digitális rendszerekben való formája az adat, ami a logikai áramkörökben kód formájában jelenik meg, azaz kódolás tehát két szimbólumhalmaz egymáshoz rendelése. Erre több módszer is rendelkezésünkre áll, van amelyik egy menetben végzi el a kódolást: BCD, Aiken stb, vag több menetben mint a Johnson vagy a Gray kód. Mivel a jel minősége romolhat, azaz a bináris helyiértékekben változás történik ezért a kód redundanciát növeljük, azaz, olyan plusz biteket adunk hozzá ami vagy ellenőrzik a hibát, vagy ki is javítják. Ellenőrzésre alkalmas a paritás bit, míg javításra több speciálisan használt paritás bit használható, például a Haming féle távolság segítségével.

Logikai függvények

Az időfüggetlen logikai függvények közös jellemzője, hogy a függő (kimeneti) változó értéke csak a független (bemeneti) változó értékétől függ. Az ilyen típusú függvényeket valósítják meg a kombinációs logikai hálózatok.

Az időfüggő logikai függvények jellemzője, hogy a függő (kimeneti) változó aktuális értékét nemcsak a független változók adott időpontban felvett értéke, hanem más időpillanatban felvett értékei is meghatározzák. Ez azt jelenti, hogy az események sorrendje is befolyásolja a kimenet állapotát. Az ilyen típusú függvényeket megvalósító hálózatokat nevezzük szekvenciális hálózatoknak.

- Diszjunktív szabályos alak olyan logikai függvény, amely mintermek VAGY kapcsolatából áll.

- Konjunktív szabályos alak olyan logikai függvény, amely maxtermek ÉS kapcsolatából áll.

- Term: a független változók azon csoportja, amelyeket azonos logikai kapcsolatra jellemző szimbólummal kapcsolunk össze.

- Minterm: a független változók logikai ÉS kapcsolata, amelyben minden változó (igaz vagy tagadott formában) egyszer és csakis egyszer szerepel.

- Maxterm: a független változók logikai VAGY kapcsolata, amelyben minden változó (igaz vagy tagadott formában) egyszer és csakis egyszer szerepel.

A felhasználás jellegétől függően ugyanazt a műszaki feladatot diszkrét elemekkel (jelfogó, dióda, ellenállás, tranzisztor) felépített hálózattal, vagy integrált áramkörökkel is megoldhatjuk. A tervezés során meghatározzuk, hogy a megvalósításhoz szükséges logikai függvények eredménye a bemeneti változókon kívül függ-e az események bekövetkezési sorrendjétől. A kombinációs hálózatok időfüggetlen logikai függvényeket valósítanak meg. A sorrendi (szekvenciális) hálózatok időfüggő logikai függvényeket valósítanak meg, ezek memóriával is rendelkező logikai áramkörök. A sorrendi (szekvenciális) logikai hálózatban a bemeneti logikai változók kapcsolatban vannak a kimeneti logikai változókkal, vagyis a rendszerben visszacsatolás van. A kimeneti jel függ az események sorrendjétől.

Logikai kapuk

A kombinációs hálózatok legfontosabb tulajdonsága, hogy a bemeneti események az időtől függetlenül egyértelműen meghatározzák a kimeneti eseményeket. Logikai kapuknak (logic gates) nevezzük a logikai alapfüggvényeket megvalósító áramköri elemeket. Egy digitális integrált áramkörben – az áramkör bonyolultságától függően – egy vagy több logikai kapu található. A továbbiakban az alapműveleteknek megfelelően bemutatjuk a különböző logikai kapuk rajzjelét és igazságtáblázatát

ÉS kapu

NEM kapu

VAGY kapu

ÉS-NEM (NAND) kapu

NAND kapcsolatot megvalósító áramköri elem. Tehát a NAND kapu kimenő jele akkor és csakis akkor 0, ha mindkét bemenő jel értéke egyidejűleg 1 értékű, ezért a NAND kapu bemenetén a 0 jel a meghatározó.

VAGY-NEM (NOR) kapu

NOR kapcsolatot megvalósító áramköri elem. Tehát a NOR kapu kimenő jele akkor és csakis akkor 1, ha mindkét bemenő jel értéke egyidejűleg 0 értékű, ezért a VAGY kapu bemenetén az 1 jel a meghatározó.

Ekvivalencia kapu

Az EKVIVALENCIA kapu kimenő jele akkor 1, ha a bemenő jelek logikai értéke megegyezik. A kapu a logikai hálózatok leegyszerűsítését szolgálja.

ANTIVALENCIA (KIZÁRÓ-VAGY) kapu

kimenő jele akkor 1, ha a bemenő jelek logikai értéke különböző.

Funkcionálisan teljes rendszernek nevezzük azokat a logikai függvényeket, megvalósító kapukat, amelyekből bármilyen tetszőleges hálózat megvalósítható. A funkcionálisan teljes rendszer másik fontos előnye, hogy a logikai áramkör megvalósításához csak meghatározott típusú kapuáramkör szükséges.

NEM-ÉS-VAGY rendszer: Tetszőleges logikai függvény kifejezhető az ÉS, a VAGY és a NEGÁCIÓ műveletet megvalósító logikai kapuk megfelelő kombinációjával. Gyakorlati megvalósítás szempontjából a nem terjedt el, mivel áramköri szempontból sokkal egyszerűbb az ÉS és a VAGY kapu helyett a NEM-ÉS (NAND), illetve a NEM-VAGY (NOR).

NAND-rendszer: Tetszőleges logikai függvény kifejezhető a NEM-ÉS (NAND) műveletet megvalósító logikai kapuk megfelelő összekapcsolásával. Az ilyen áramköri megvalósítást nevezzük NAND-rendszernek.

Kétszintes hálózat: Ha a bemeneti változók a kimenetre két kapuáramkörön keresztül jutnak el, akkor kétszintű hálózatról beszélünk. Háromszintű logikai hálózat: Ha egy diszjunktív vagy konjunktív alakban megadott logikai függvényt – újabb logikai művelettel – egy vagy több másik függvénnyel bővítjük, akkor az új logikai függvény már nem valósítható meg kétszintű hálózattal. Az ilyen típusú logikai függvényeket megvalósító hálózatokat többszintű logikai hálózatoknak nevezzük. Négyszintű logikai hálózat:

CLB - konfigurálható logikai tömbök amiket a

switch matrix - összekötő vezeték köt össze az

IOB modulokkal - amik a jelek ki/be vitelére használhatóak

RAM alapú FPGAba a bekapcsolás után be kell konfigurálni a bitfolyamot ami meghatározza, hogy milyen útvonalon áramlanak a jelek a CLB, azaz a logikai tömbök belsejében. Ezért ez lehet egyszer, vagy többször programozható.

fájl: MEMÓRIA ELEMEK.png

- konfigurálható logikai tömbök: logikai kapuk, kereső táblázat, osztott memória, bistabil áramkörök, multiplexxer áramkörök.

- ki/be meneti tömbök

- blockRAM (BRAM)

- digitális jelfeldolgozó modul (DSP) vagy szorzó áramkör (MUL)

- órajel menedzselő áramkör (DCM - digital clock manager)

- beágyazott processzormagok

- Gigabit tranceiver modulok

Teljesítmény

- hardveres párhuzamosítás => órajelenként több művelet, ki/be menet hardverszintű vezérlése => gyorsabb vezérlés Piacra kerülési idő

- gyors modellezés Költség

- olcsóbb mint az ASIC Megbízhatóság

- több a bsztrakciós réteg => jobb folyamat ütemezés => minimális megbízhatósági aggály Hosszútávú karbantartás

- elég az FPGA újrakonfigurálása, nem szükséges az áramkör újratervezése

=> magas fokú párhuzamosítás

=> pipeline és párhuzamos pipeline

=> műkődés közbeni újrakonfigurálás

=> jó sebesség

=> időkritikus egységek külön hardveregységben

=> egyszerű illesztés létező eszközzel

- állapotautomaták, adatutas automaták

- beágyazott processzort tartalmazó rendszerek akár operációs rendszerrelhttps://en.wikipedia.org/wiki/Advanced_Boolean_Expression_Language

- kapcsolási rajz laapú tervezés

Nyelvek:

- egyszer/többször programozható

- indulás master/slave módban

- működés közbeni újrakonfigurálás: részleges, dinamikus újrakonfigurálás / teljes átkapcsolás

- magas szintű programozási nyelvek (HLS) alkalmazása

Ebben a részben a hallgató megismerheti az FPGA áramkörök szerkezetét, a fontosabb részeit, valamint egy FPGA áramkörben megtalálható vezetékhálózatokat. A téma keretében szemléltetjük a feladatnak az FPGA áramkörbe való programozásának lehetséges változatait.

- konfigurálható logikai tömbök (CLB)

- LUT kereső táblázat (look up tables)

- Bistabil áramkörök

- osztott RAM

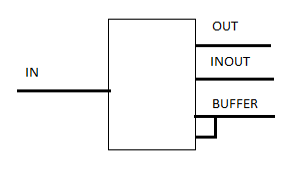

- I/O gyűrű

- kétirányú adatfolyam

- 3 state logika

- DDR (Double Data Rate) regiszterek

- Funkcionális blokk

- Block RAM

- Multiplier blocks

- DCM (digital clock manage) modul

- oszlopokba szervezve konfigurálható logikai tömbök (CLB) mellett

- különálló egységként, rugalmasan méretezhető az adatsínszélesség/címtartomány

- alkalmazható kétportos memóriaként

- Spartan 3E -> 1 BRAM = 18 Kbit

- biztosítja az adatfolyamot a DSP/szorzó áramköröknek

- Logikai függvény megvalóstása

- Osztott memória

- Léptető regiszter

- különböző órajelek szétosztása, szintézise

- órajelek stabilizálása, szinkronizálása

-

elemei: LUT kereső táblázat, Bistabil áramkör, logikai kapuk, multiplexer áramkörök

-

egy CLB 4 szeletet tartalmaz

-

bal oldali szelet (SLICE M): memória elemeket is tartalmaz => osztott memória, a kerresőtáblázat használható 16 bites shiftregiszternek

-

jobb oldali szelet (SLICE R):

-

keresőtáblázat: logikai függvények (LUT) megvalósítására

-

multiplexer áramkörök

-

az adatok balról jobbra, lentről flelfele áramlanak

-

osztott memória: pár bit memória szétosztva a logikai tömbökre

- adatfoylam vezérlés I/O láb és belső logika között

- kétirányú adatfolyam

- magas impedanciás kimenet alkalmazása

- kimenet/bemenet/kibemenet

- felhúzó/lehúzó ellenálások alkalmazása

megkülönböztetve: kimeneti/bemeneti/magas impedancia

- több áramkör áll rendellkezésre

- adatok: konfigurálható tömbök száma, DCM, DRAM, BRAM, ki/beneeti lábak,

adattárolásra szolgál max: 18 Kbit kiseb sínszélesség mellett, több címbit/ szélesebb adatbit adatbitek: egyszerű adatbit: DI/DO

- ha duplázzuk az adatbiteket akkor csökkenteni kell a címbiteket

- csak a 8-16 sínszélesség mellett használható a paritásbitek

- dualportos memória alklmazás: mind a két egyportos memórialkalmazásnál növeljük a memória méretét

WE - írás engedélyezése

EN - órajel engedélyezése

CLK - órajel

DI - bemeneti adatvonalak

DO - kimeneti adatvonalak

DIP - bemeneti paritás bit

DOP - kimeneti paritás bit

WRITE_FIRST - először írás

READ_FIRST - először olvasás

NO_CHANGE - csak írás

- olvasás esetén

EN = '1' - írás esetén

WE = '1'

a CLB-k kapcsolására töb lehetőség van:

- közvetlen: egy CLB közvetlen a bal-jobb, felső-alsó tömbhöz

- függőleges/vízszintes hex huzalozás

DCM: Digitális órajel menedzser

- órajel bemenetek

- órajel buffer az órajelek szétosztására az órajelek között, mert különböző órajelekre van szükség => órajelek szétosztása, késleltetése külső órajel bemenetek/half clock bemeneteken külső órajele megadása

- BUFG

- BUFGMUX

- BUFGCE

Bit file: konfigurációs fájl

-

konfigurációs adat: meghat a programozható logikai elem állapotát

-

konfigurációs parancs: meghat, hogy az adattal mit kezdjünk

-

küön hálózat a konfigurálásra, amin keresztül minden egyes komponens elérhető a hálózaton

-

JTAG interfészen feltöltés

-

soros/párhuzmos feltölés

TDIbemeneti adatvonal -> itt lehet betölteni az adatokat az áramkörbeTDOaz adatok visszaolvasásaTMSparancsok küldése a rendszerreTRSJTAG modul kezdőállapotba szinkronizálásaTCKórajel

megjegyzés

--entitások

entity [NÉV] is Port(...); end [NÉV];architektura rész

architecture Behavioral of [NÉV] is -- deklarációs rész begin -- implementációs rész end Behavioral;

A fejezetben a hallgató megismerheti az FPGA alapú áramkör tervezésnél alkalmazott áramköri modelleket és absztrakciós rétegeket. Egy áramkört tekinthetünk fekete doboznak, amelynek nem ismerjük a belső felépítését, szerkezetét, de ismerjük a viselkedését. Ismerjük a bemenetek és kimenetek közötti összefüggést. Egy másik megközelítés, hogy ismerjük a részletes felépítését, modulárisan milyen alegységeket, modulokat, komponenseket tartalmaz és a komponensek közötti kapcsolatokat. Egy áramkörnek a tervezés során meghatározhatjuk a viselkedését vagy felépíthetjük az áramköri elemekből, amely ugyanazt a viselkedést eredményezi.

Egy elektronikus hardver különböző absztrakciós szinten írható le. A tervezendő hardver rendszer specifikációja során, általában, egy magasabb hierarchikus szintről lépegetve alacsonyabb hierarchikus szintekre, eljutunk az áramkör hardver szintű megvalósításáig.

Ismerve a hierarchikus szinteket és megértve az áramkör leírási modellek (strukturális, viselkedési) közötti összefüggéseket, a hallgató átlátja a különböző specifikációs modellekből kiindulva a hardver kialakítását.

- leírja a rendszer vagy részrendszer viselkedését

- úgy tekint a rendszerre akár egy fekete dobozra

- bemeneti és kimeneti adatok összefüggéseire koncentrál

=> bemeneti portok => vezetékek => modell komponensei => kimeneti portok

- nem kell mindne szintet pontosan definiálni

- elegendő a tervezést a legfelsőbb siznteken elvégezni

- => EDIF (Ectronic Design Interchange Format) - semleges adatcsere formátum => automatizált elektronikus tervezés

- EDAXML

- NGC (native GEneric Circuit) - Xilninx saját formátum

felsorolja a komponeneseket

- hardver erőforrásokat ábrázol

- újabb fizikai információkkal bővíti a strukturális nézetet: alkatrészek mérete, helye, összekötő vonalak

LUT3 - Q_F

O = ((I0 * I2) + (!I0 * I1));LUT3 - Q_G

O = ((I0 * I2) + (!I0 * I1));4 bemenetes multiplexer áramkör megvalósításához:

- két keresőtáblázat

- egy két bemenetes multiplexer áramkör -> függvényben kijelöli, hogy melyik LUT eredményét alklamazza a LUT elemekben szintén 2 bementes multiplexer áramkör, keresőtáblázatokban a multiplexert leíró Boole függvény.

=> bemeneti buffferek => adat bementek/kiválasztó bemenetek => kimenetei bufferek egy multiplexer megvalósítás és még több lejebb a

caseutasításnál:[CASE](https://github.com/gabboraron/ujrakonfiguralhato_digitalis_aramkorok/blob/master/README.md#case)

- alap elemek: tranzisztor, ellenállás, kondnezátor, tekercs

- viselkedése differenciál egyenletekkel van leírva

- digitális áramkör = analóg áramkör

- a jel időben változó

- a gyártó feladata

- logiaki kapukból áll

- a jelek 1 vagy 0-k

- bemeneti-kimeneti kapcsolatokat Boole egyenletekkel írjuk le

- időzítéssel kapcsolatos információk egyszerűsítve:

propagation delayfizikai nézetben: a kapuk elhelyezése, a kapukat összekötő vonalak huzalozása

- kapukból épített modulok

- összeadók, komperátorok, tárak, regiszterek, multiplexerek

- jelek speciális adatként: unsigned integer, float, stb..

- véges állapotú automata írja le

- strukturális nézet: kettes komplemensű bitsorozat

- jelek továbbítására alkalmazott sínrendszer

- processzorok, memória, sínrendszer

- leírás: a program sázmolási lépéseivel, folyamatokkal

- IP alaprajz feleltethető meg neki a fizikai tarotmányban alaprajz: logiaki cellák + makrocellák és összeköttetéseik

fájl: 4. ppt

Ebben a részben a hallgató megismerheti az FPGA alapú tervezés lépéseit, tervezési módszereket és a tervezés különböző fázisaiban alkalmazható ellenőrzési módszereket.

A hallgató egy átfogó képet kap a tervezés különböző fázisai után alkalmazható tesztelési módszerekről. A téma elsajátítását követően a hallgató képes lesz a tervezőeszközben alkalmazni az ellenőrzés különböző szintjeit.

- Magas szintű

- átalakítja a regiszter műveletekre (regiszter szintű leírásra)

- Regiszter szintű

- regiszter szintű viselkedési leírás analízise alapján felépíti az áramkört a regiszter szintű elemeket használva

- Kapu szintű

- a strukturális megvalósítás kapu szintű elemekre épül

- két vagy többszintes optimalizálási eljárás alklamazása az áramkör méretének minimalizálására

- Technológiai leképezés

- minden rendszer tartalmaz előre lekészített kapu szerű primitív elemeket amiket egy cella standard célkönyvtárból vagy logikai cella az FPGA rendszeréből

- a kapu szint implementálásához egy partikuláris rendszeren az elemeket le kell képezni a kiválasztott célrendszerre => ez a technológiai leképezés

- finomítási folyamat

- Particionálás

- Alaprajzi tervezés

- létrehoz egy tevet processzor és regiszter szinten

- Elehelyezés és huzalozás

- terv cella szinten, az áramkör primitív elemeiből és elvégzi a huzalozást

- circuit parameter extraction

- az elhelyezés és routolás után mind kapcsolat helye és hossza ismert

- az asszociált parazita kapacitás és ellenállás kiszámítható

- funkcionális: a rendszer az elvárt kimenetet szolgáltatja?

- időzítés: teljesíti az időbeli korlátokat?

- teljesítmény: betartja a részegységek meghatározott áramkorlátokat?

- szimuláció

- időanalízis

- teljesítmény analízis

- hardver emuláció

- prototípus áramkör FPGA-n

- beépített analizátor

- Kapu szintű

- regiszter szintű

- processzor szintű

- Szintézis során a

VHDLvagyVerilogprogramkód lefordítódiknetlist(NGC - Native Generic CircuitvagyEDIF-Standard Electronic Interchnage Format) formátumra. Szintetzáció során aHDLleírás kapu sizntű netlist állománnyá amit azUNISMkönyvtárra képez le.

- több alegység esetén minden alegységhez tartozik egy ilyen állomány

- szintaxis ellenőrzés

- analizálja a terv hierarchiáját

- több külöböző hardver leíró nyelven készítettállomány egyesítése egyelten

netlist(EDIF) fájlba- kombinálja az

NGCfájlokat és a megkötéseketUser Constraints Fileamiből létrejön egy logikai fájl, azNGD- Native Generic Database azNGD Buildsegítségével.

- a

User Constraints Filehozzárendeli a ki/bemeneti portokat az FPGA lábakhoz és meghatározza az időzítési követelményeket => Ha azNGCazUNISMkönyvtárra alapoz akkor szintézis után viselkedési szimulációt végez=> Ha az

NGDazSIMPRIMkönyvtárra alapoz akkor fordítás után időalapú szimulációt végez

NGD=> leképezés =>NCD

- a logikai elemeket tartalmazó áramköröket alegységekre osztja

- az

NGDben definiált logikát képzi le az FPGA elemeire: CLB, IOB, Block RAM, DSP, stb ami egyNCD - Native Circuit Descriptionállományt generál, amely leírja fizikailag az áramkör elemeit- ismerjük az FPGAból, hogy milyen elemket használunk, csak nem tudjuk melyiket, ezt oldja meg a MAP

NCD=> elhelyezés és huzalozás => huzalozottNCD

PARprogram végziAz előző fázis eredményeként kapott alegységeket elhelyezi az FPGA blokkba, figyelembe véve a megkötéseket, és összehuzalozza ezeket.

A folyamat során figyelmebe veszi és feloldja a kényszerfeltételek közti ellentéteket.

Az eszköz beprogramozása:

BITGENprogram generál azNCDbőlBITtípusú állományt ami feltölthető az FPGAba egy feltöltő programmal mint azIMPACT

- Szimuláció

- viselkedési

- funkcionális

- fordítás után

- leképezés után

- időzítési

- elhelyezés és huzalozás utáni

- verifikáció

- logikai analizátor

- Hardver co-szimuláció

fájl: ppt 5

A fejezetben a hallgató megismerheti a VHDL program szerkezetét: alkalmazott könyvtárak meghatározása, tervezett modul portjeleinek meghatározása valamint a tervezett hardver strukturális szinten vagy viselkedési szinten való leírása.

A

HDLegy speciális számítógépes programozási nyelv, amelyet elektronikus áramkörök, a leggyakrabban digitális áramkörök, struktúrájának és viselkedésének a leírására

Egy tervezőeszköz alkalmazásával lehetővé teszi a HDL-leírás szintetizálását netlist formátumba. A netlist formátum tartalmazza az elektronikai komponensek specifikációját és azok összekapcsolását. A netlist állományban meghatározott komponensek elhelyezhetőek és huzalozhatóak az FPGA áramkörben a céláramkör létrehozására vagy alkalmazható maszkok létrehozására és az integrált áramkör legyártására. Összehasonlítva programozási nyelvekkel, a HDL nyelvek magukba foglalják az idő fogalmát.

A HDL programozási nyelvek szerves részét képezik az

EDA (Automatizált Elektronikus Tervezés)rendszereknek.

A VHDL és a Verilog a leggyakrabban alkalmazott, digitális rendszerek tervezésére használt hardver leíró nyelv. A kurzus során a rendszerek tervezésére a VHDL-t alkalmazzuk. A VHDL-ből könnyen át lehet térni a Verilog alapú tervezésre.

A VHDL hardver leíró nyelv alkalmazásával, CPLD makro cellákból és FPGA áramkörök konfigurálható logikai tömbjeiből igen bonyolult működésű áramköröket lehet létrehozni/tervezni.

A

VHSIC- Very High Speed Integrated CircuitVHDL-VHSICHardware Description LanguageADAésPASCALnyelvekből származik

- újrahasználható

- technológia független

- létező tervekbe új technológiák is beépíthetőek

{’U’, ’X’, ’0’, ’1’, ’Z’, ’W’, ’L’, ’H’, ’-’} U - Nem inicializált, a jelhez vagy változóhoz nincsen értéke rendelve (Szimulációban alkalmazott)

X - Határozatlan logikai állapot

W - Gyenge határozatlan logikai állapot, jel, egy olyan értéket vesz fel amit nem lehet sem logikai 0-nak sem logikai 1-nek értelmezni.

0 - Határozott logikai 0, akkor veszi egy jel ezt az értéket, ha szabványos meghajtó áramkör vezérli

1 - Határozott logikai 1, akkor veszi egy jel ezt az értéket, ha szabványos meghajtó áramkör vezérli

Z - Nagy impedanciás érték, háromállapotú meghajtó áramkör

L - Gyenge logikai 0, a meghajtó vezérlő áramkör gyenge meghajtó áramot szolgáltat

H - Gyenge logikai 1, a meghajtó vezérlő áramkör gyenge meghajtó áramot szolgáltat

- - Redundáns érték

Megjegyzések - --

Azonosítók

- Alkalmazható karakterek

- Latin ABC betűi

- Számok

- Aláhúzás

Operátorok: +, -, &, *, /, ., <, =, >, |, /=, :=, >=, <=, <>

Tömkbök: []

Karakterek

Karakterláncok

Konstansok: constant e: real :=2.71828;, constant delay: Time :=5ns;, constant max_size : natural;, variable intr: bit_vector(31 downto 0);

Számok

- Egész

- Lebegőpontos: pl:

Type jelszint is range -10.00 to 10.00;vagyType valoszinuseg is range 0.0 to 1.0;, előre definiált:Real-1E38 tól 1E38–ig - Valós

- N alapú:

-

Based_literal::=base#basedinteger[.basedinteger]#[exponent]2#1100_0100# 16#C4# 4#301#E2= 1962#1.1111_1111_111#E+11 16#F.FFFE2= 4095.0

- Bit string

Bit_string_literal:==base_specifier”bit_value”base_speifier::=B|O|Xbit_value::=extended_digit{[underline]extended_digit}B”10101100”= 8 bitO”126” = 3 x 3 bit =B”001_010_110”`X”56”= 2 x 4 bit =B”0101_0110”

- N alapú:

-

Kulcsszavak:abs, access, after, alias, and, architecture, array, assert, attribute, begin, block, body, buffer, bus, case, component, configuration, constant, disconnect, downto, else, elsif, end, entity, exit, file, for, function, generate, generic, guarded, if, impure, in, inertial, inout, is, label, library, linkage, literal, loop, map, mod, nand, new, next, nor, not, null, of, on, open, or, others, package, port, postponed, procedure, process, pure, range, record, register, eject, rem, report, return, rol, ror, select, severity, shared, signals, sra, srl, subtype, then, to, transport, type unaffected, units, until, use, variable, wait, when, while, with, xnor, xor

Objektumok:

- Jel (signal) –összeköttetés (vezeték)

- Változó (variable)

- csak folyamatokban (process)

- Helyi tároló elem

- Állandó

- fájl

LIBRARY konyvtar_neve

USE konyvtar_neve.csomag_neve.csomag_reszeMinimálisan három könyvtárra van szükség:

ieee.std_logic_1164(ieee könyvtárból)stdstandard könyvtárbólworksaját munkakönyvtárból

LIBRARY ieee;

USE ieee.std_logic_1164.cell;

LIBRARY work;

USE work.all;Std_logic_1164 std_logic(8 szint) ésstd_ulogic(9 szint) többszintű logikai rendszerekStd_logic_arith–signed és unsigned adattípusok és erre vonatkozó aritmetikai és összehasonlító és adatkonverzióra használt műveletek:conv_integer(p),conv_unsigned(p,b),conv_signed(p,b),conv_std_logic_vector(p,b)Std_logic_signed STD_LOGIC_VECTORadaton értelmezett függvényeket tartalmaz ha az adatSIGNEDtipusú, inkrementálás, dekrementálás támogatásastd_logic_vectortípusokonStd_logic_unsigned-STD_LOGIC_VECTORadaton értelmezett függvényeket tartalmaz, ha az adatUNSIGNEDtípusúNumeric_std:signedésunsignedadattípusok és erre vonatkozó aritmetikai és összehasonlító és adatkonverzióra használt műveletek

Típusok: unsigned, signed

Aritmetikai: +, -, *

Összehasonlító műveletek: <, <=, >, >=, =, /=

Eltolás: shl, shr

Konverzió conv_integer, conv_unsigned, conv_signed

Aritmetikai: +, - , *, /, remm, mod

Összehasonlító műveletek: <, <=, >, >=, =, /=

Eltolás: SHIFT_LEFT, SHIFT_RIGHT, ROTATE_LEFT, ROTATE_RIGHT, sll, srl, rol, ror

Konverzió TO_INTEGER, TO_UNSIGNED, TO_SIGNED

Logikai műveletek: Not, and, or, nand, nor, xor, xnor

PORT: egy listát tartalmaz az összes ki és bemeneti, meghatározva a jel típusát és iránáyát

ENTITY entitás_neve IS

GENERIC

(GENERIC-us paraméterek);

PORT (

jel1_neve: jel_modjel1_típus;

jel2_neve:jel2_modjel2_tipus;

…);

END entitás_neve;A jel típusa lehet: Bit, STD_LOGIC, INTEGER stb

A jel iránya: In, out, Inout, buffer

Az AND entity:

ENTITY es_kapu IS

PORT ( X1: IN bit;

X2: IN bit;

Y: OUT bit;)

END es_kapu

ENTITY es_kapu IS

PORT

(X: IN std_logic_vector(1 downto 0);

Y: OUT std_logic;

END es_kapu;ARCHITECTURE az_architektura_neve OF entitás_neve

[Deklarációs rész szignálok:, komponensek (COMPONENT) , függvény FUNCTION, jelek (SIGNAL), konstansok (CONSTANT), változok (VARIABLE), típusok (TYPE)]

BEGIN

Programkód rész;

END az_architektura_neve;ENTITY mux

Port(I0: IN bit;

I1: IN bit;

S0: IN bit;

O: OUT bit);

END mux;

ARCHITECTURE arch1 OF mux IS

BEGIN

O<= ((not S0) and I0) or (S0 and I1);

END arch1ARCHITECTURE arch2 OF mux IS

Signal p1:bit;

Signal p2:bit;

BEGIN

p1<=(not S0)and I0;

P2<= S0 and I1;

0 <= p1+p0;

END arch2;Integer– egész típus [-231-1, 231-1], műveletei:+,-,*,/,modmodulo,remegésszel osztás maradéka,absabszolútérték,**hatványozásBoolean– Boole típus {true, false}bittípus: {’0’, ’1’}, egy jelhez nem csupán kétállapotú jelszinteket lehet rendelni (nagyimpedanciás állapot, jelkonfliktus)bit_vectortípus –bit típusú elemekből álló tömb, egy jelhez nem csupán kétállapotú jelszinteket lehet rendelni (nagyimpedanciás állapot, jelkonfliktus)bitésbit_vectorhelyett lehetSTD_LOGICésSTD_LOGIC_VECTORreal- Felsorolás (

enumeration) - Vektorok (

Arrays) - Rekordok

- fizikai mennyiségek:

nm,um,mm,cm,dm,m,kmstbtype Time is range --im plementation defined-- ; units fs; -- femtosecond ps = 1000 fs; -- picosecond ns = 1000 ps; -- nanosecond us = 1000 ns; -- microsecond ms = 1000 us; -- millisecond sec = 1000 ms; -- second min = 60 sec; -- minute hr = 60 min; -- hour end units; type CAPACITANCE is range 0 to 1000000000 -- set up system for capacitance units pf ; -- smallest allowable unit is nf = 1000 pf; -- nanofarad, uf = 1000 pf; -- microfarad mf = 1000 uf; -- millifarad f = 1000 mf; -- farad end units CAPACITANCE ;

Type utasitas is

Record

utasitas_kod : processzor_utasitas;

cimzesi_mod: cimzesi_mod_tipus;

operandus_1 : integer range 0 to 15;

operandus_2: integer range 0 to 31;

End record utasitas;type DATUM is record

HONAP : STRING (0 to 20);

NAP : INTEGER range 1 to 31;

EV : INTEGER range 1800 to 2050;

end record DATUM; Type CIM is record

UTCA : STRING (0 to 50);

IRANYITOSZAM : INTEGER range 0 to 99999;

HELYSÉG : STRING (0 to 50);

ORSZÁG : STRING (0 to 40);

end record ADDRESS; lehetővé teszi, hogy az objektum által felvehető értékeket korlátozzuk az alaptípus csak egy bizonyos részére

Subtype kimenetek_szama is integer range 0 t0 400;

Subtype digits is character range ‘0’ to ‘9’;

subtype MEM_ADR is INTEGER range 0 to 1023;

subtype BUS_VAL is INTEGER range 0 to 65535;- típushoz kapcsolódó attribútumok (scalar attribute):

T'BASE is the base type of the type T - signal-hoz kapcsolódó attribútumok (signal atribute):

T'last_value -visszatéríti az utolsó esemény előtti értéket - vektor-hoz kapcsolódó attribútumok (array atributes):

T'length -vektor mérete - saját attrbútumok:

- Deklarálni kell az attribútumot:

ATTRIBUTE attribútum_neve : attributum_tipusa - Specifikálni kell az attribútumot

ATTRIBUTE attributum_neve: OF cel_elem_neve : osztaly IS ertek;

- attribútum típusa: bámely adattípus:

BIT,INTEGER,STDÜLOGIC_VECTOR,STRINGstb - Osztály

Type,SIGNAL,FUNCTION - Értek: “11111”, 27, “WRITE_FIRST”, “READ_FIRST”

ATTRIBUTE bemenetek_szama : integer; ATTRIBUTE bemenetek_szama of nand3 : SIGNAL is 3; Inputs <- nand3’bemenetek_szama;

- Deklarálni kell az attribútumot:

- signálnak:

<= - változók/konstansok:

:= - vektor elemeinek:

=>példák:

SIGNAL x:std_logic;

VARIABLE y: STD_LOGIC_VECTOR(3 downto 0);

SIGNAL w:std_logic_vector(0 to 7);

x<='1';

y:="0000";

w<="10000000"

w<=(0=>'1', others=>'0')fájl: 5.ppt

példaprogramok: 5.téma példaprogramjai

Ebben a részben a hallgató megismerheti a VHDL-ben alkalmazható fontosabb szekvenciális kifejezéseket: process, feltételes értékadás, ciklusok, signal (jel) és variable (változó) közötti különbség.

Egyszerű szekvenciális és kombinációs áramkörökre bemutatott példák alapján felismerheti az egyes kódolási módszerek sajátosságait.

A hallgató képes lesz az ismeretek elsajátítását követően kombinációs és szekvenciális áramkörök modellezésére.

- a konkurens rész az

architectureáltal van képviselve amely, tartalmaz:

process-t- konkurens eljárás hívást (

procedure)- konkurens jelhozzárendelés

- komponens példányosítást

process(folyamatban) vagy alprogramrészben található szekvenciális kifejezések- a szekvenciális kifejezések abban a sorrendben vannak végrehajtva, ahogy megjelennek a process vagy alprogram részekben

VHDL PROCESS– legegyszerűbb megoldás szekvenciális áramkörök tervezésére

- Szekvenciális kifejezés

- Minden

PROCESSegyetlen kifejezés- Az

architecture-ben minden processzus egyszerre (konkurensen) hajtódik végreA

PROCESSa terv többi részével aPROCESS-en kívül deklaráltSIGNAL-okon ésPORT-okon kommunikál

szekvenciálisan végrehajtódó utasítások: PROCESS, FUNCTION, PROCEDURES, IF, WAIT, CASE LOOP, VARIABLE - szintén csak szekvenciális kódgenerálásban vagy lokálisan, SIGNAL –globálisan alkalmazható, bővebben: vhdl-online.de/vhdl_reference_93

értékadás (hozzárendelés, assignment): változóknak, jeleknek

folyamatirányító kifejezések (utasítások):

- feltételes:

IF,CASE,LOOP- ciklus:

FOR...LOOP,WHILE LOOP,UNTIL- ugrás:

NEXT,EXITalprogramrészek:

FUNCTION,PROCEDURESvárakozás, amíg egy esemény történik:

WAITsemmi sem történik:

NULL

- egy szekvenciális algoritmust implementál

- Tartalmazhat szekvenciális és konkurens kifejezéseket

- Szekvenciális kifejezések csak a

PROCESS-en belül alkalmazhatók

szerkezete:

[címke]:PROCESS (érzékenységi lista)

[típus deklarálás]

[konstans deklarálás]

[változó deklarálás]

[VARIABLE változó_neve típus [intervallum] [:=kezdeti_érték]]

[alprogram deklarálás]

BEGIN

-- implementációs rész --meghatározzák mely signal értékadása fog végrehajtódni.

……..

szekvenciális kifejezések

-- IF, WAIT, CASE, LOOP

……..

END PROCESS [címke];A PROCESS aktiválódik, ha

- a

PROCESS-t követő listából (érzékenységi lista) a jelek értéket váltanak - a

WAITkifejezésből a jelek értéket váltanak

PROCESS – (explicit) érzékenységi listával

- aktiválódnak amikor az élesítő listából bármely jel állapotot vált

- nem tartalmazhat

WAIT-et - végén van egy implicit

WAIT ON - kiértékelése a végén függesztődik fel

PROCESS élesítő lista nélkül

- tartalmaznia kell legalább egy

WAIT-et- Egyes tervező eszközök esetében a

WAITkifejezés rögtön aBEGINután kell következzen - A

PROCESSaz elsőWAIT–ig fut

- Egyes tervező eszközök esetében a

- A

WAITkifejezés meghatározza asignal–okat, amelyek változását monitorizáljuk - A

PROCESS–ek akkor aktiválódnak, amikor aWAITkifejezés után meghatározottsignal-ok értéket váltanak - A

PROCESSa következőWAITkifejezésig fut - Egyes tervezőeszközök

PROCESS–enként többWAITkifejezést engedélyeznek

PROCESS kiértékelése:

- A már egyszer aktiválódott

processkiértékelése a legutolsó felfüggesztéstől kezdődik - fentről lefele hajtódik végre

- Ha a process végéig nincs (még) egy

WAIT(újabbWAIT), a kiértékelés visszaugrik aPROCESSelejére és folytatódik (aWAIT-ig)

A hivatkozott jelek állapota a jelek (signalok) állapota a PROCESS inditásakor:

- Az összes

signalértékadás csak lehetséges értékadás - A

PROCESS-en belül asignal-ra az utolsó értékadás érvényesül - a

signalértékadása csak aPROCESSkiértékelésének végén történik

Kombinációs áramkört megvalósító process

entity log_lut is

Port (-- S0 : in STD_LOGIC;

--S1 : in STD_LOGIC;

I0 : in STD_LOGIC;

I1 : in STD_LOGIC;

I2 : in STD_LOGIC;

I3 : in STD_LOGIC;

q : out STD_LOGIC);

end log_lut;

architecture Behavioral of log_lut is

begin

process (I0, I1, I2, I3)

begin

q<=((I0 and I1) or (not I2)) and I3;

end process;

end Behavioral;Szekvenciális áramkört megvalósító process

Szekvinciális áramkörök/hálózatok

A sorrendi hálózatok, vagy más néven a szekvenciális hálózatok feladata, az időfüggő logikai függvények megvalósítása.

Fontos tulajdonságuk, hogy a kimeneti események állapotát nem csak a bemeneti feltételek, hanem már a korábban végbement kimeneti események is befolyásolják.

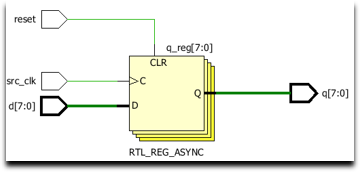

Aszinkron szekcinciális hálózatok: Ez a szekvenciális hálózat azon fajtája, amelynél a kimenet előző állapotától való függését visszacsatolással vagy tárolókkal valósítják meg. A bementi jellemző megváltozására a kimenti jellemző azonnal reagál.

Szinkron szekvenciális hálózatok: Az állapotváltozás egy engedélyező jel hatására, azzal azonos fázisban zajlik le. Ezt az engedélyező jelet órajelnek, vagy más néven ütemjelnek nevezzük. A kimenet előző állapotától való függést tárolók segítségével valósítják meg.

process (src_clk, reset)

variable counter : std_logic_vector(BIT_SZAM-1 downto 0);

begin

if reset='1' then

counter := (others=>'0');

elsif src_clk'event and src_clk='1' and CE='1' then

counter := counter+1;

end if;

q<=counter;

end process;

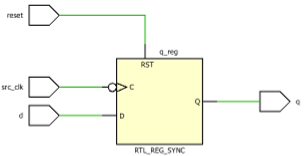

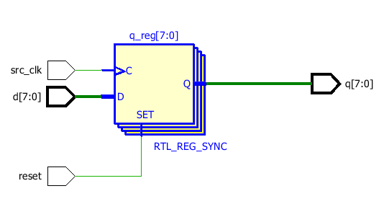

end Behavioral;Reset nélküli D típusú tároló

A D típusú tároló

Bementére adott információ a kimenetén egy vezérlőjel időtartamával késleltetve jelenik meg. Akkor kapunk

D tárolót, ha aJ=Kértékkombinációkat kizárjuk.igazságtáblázata és rajzjele:

process (src_clk)

begin

if src_clk'event and src_clk='0' then --Felfutó él detektálás

q <= d;

end if;

end process;

end Behavioral;D típusú tároló Reset jellel

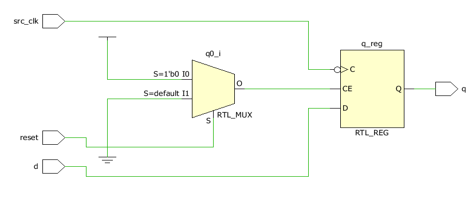

Példa: aszinkron reset a lefutó óraélen, szinkron reset a lefutó óraélen, szinkron reset felfutó óraélen, szinkron reset felfutó óraélen órajel engedélyezéssel

process (src_clk, reset)

begin

if src_clk'event and src_clk='0' then --Felfutó él detektálás

--Szinkron reset

if reset='1' then

q <= '0';

else

-- Szinkron reset kezelés vége

q<=d;

end if;

end if;

end process;

end Behavioral;példa:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-------------------------------------------

entity pelda_2 is

Port (src_clk: in std_logic;

reset : in std_logic;

d : in std_logic;

q : out std_logic);

end pelda_2;

--------------------------------------------

architecture Behavioral of pelda_2 is

begin

process (src_clk, reset)

begin

-- Szinkron reset

if reset='1' then

elsif src_clk'event and src_clk='0' then

-- Szinkron reset eddig

q <= d;

end if;

end process;

end Behavioral;- vezeték szerepe komponensek között összekapcsolásra

- deklarálható:

PACKAGE-benENTITY-ben (porttípusú szignál)ARCHITECTURE-ban

- módosítása csak

PROCESSvégén történik SIGNALértékadás:jel<=kifejezes

- csak

PROCESS-en belül deklarálható, és tartalmaPROCESS-en kívül nem érhető el - Alkalmazható köztes eredmények tárolására.

- módosítása azonnali

- Változó értékadás:

valtozo_neve:=kifejezes

IF feltétel THEN

értékadás ha a feltétel igaz

ELSE

értékadás ha a feltétel hamis

END IF;IF (x<y) THEN temp:=“11111111”;

ELSIF (x=y and w=‘0’) THEN temp:=“11110000”;

ELSE temp:=(OTHERS=>’0’);

END IF;Számláló megvalósítása példa:

fájl:bináris felfele számláló szinkron resettel felfutó óraélen órajel enegdélyezővel, bináris felfele számláló aszinkron resettel felfutó óraélen órajel engedélyezővel

LIBRARY ieee;

USE ieee.std_logic_vector;

----------------------------------------------

ENTITY counter IS

PORT (clk: IN STD_LOGIC;

digit: OUT INTEGER RANGE 0 TO 9); --Változó deklarálás

END counter

----------------------------------------------

ARCHITECTURE counter OF counter IS

BEGIN

count:PROCESS(clk)

VARIABLE temp : INTEGER RANGE 0 TO 10; --Változó deklarálás

BEGIN

IF (clk’EVENT AND clk=‘1’) THEN --Felfutó él detektálás

temp:=temp+1;

IF (temp=10) THEN --Változó visszaállítása nullára

temp:=0;

END IF; --

END IF

digit <=temp;

END PROCESS count;

END COUNTER- Csak szekvenciális kódgenerálásra alkalmazzuk!

példa: D típusú tároló esetében

[ cimke: ] case kifejezés is

when K1 => szekvenciális kifejezések;

when K2 => szekvenciális kifejezések;

when others => szekvenciális kifejezések;

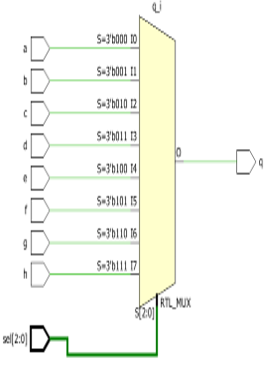

end case [ cimke ] ; multiplexer áramkör esetében case when megvalósítás: fájl

process (sel)

variable counter : std_logic_vector(BIT_SZAM-1 downto 0);

begin

case (sel) is

when "000" =>

q<=a;

when "001" =>

q<=b;

when "010" =>

q<=c;

when "011" =>

q<=d;

when "100" =>

q<=e;

when "101" =>

q<=f;

when "110" =>

q<=g;

when "111" =>

q<=h;

when others =>

q<='X';

end case;

end process;

end Behavioral;Ha a PROCESS-en belül alkalmazzuk a WAIT parancsot, a PROCESS-nek nem lehet érzékenységi paramétere

- A program végrehajtódik a következő

WAIT–ig - A program végrehajtása felfüggesztődik, amíg a

WAIT feltételeteljesül

A WAIT parancs formái:

WAIT UNTIL signal_condition;

WAIT ON signal1 [, signal2,…] ;

WAIT FOR time;

- a

PROCESS-nek nincs érzékenységi listája, aWAIT UNTILparancs kell az első kifejezés legyen aPROCESSfolyamaton belül - a

PROCESSminden alkalommal végrehajtódik, mikor a feltétel teljesül

PROCESS --nincs erzékenyégi lista!!!!!!!

WAIT UNTIL (clk’EVENT AND clk=‘1’);

IF (rst=‘1’) THEN

output <=“00000000”;

ELSIF (clk’EVENT AND clk=‘1’) THEN

output <=input;

END IF;

END PROCESS;D típusú tároló WAIT UNTILlal: fájl

entity pelda_8d is

GENERIC (BIT_SZAM : natural :=8);

Port ( src_clk : in std_logic;

reset : in std_logic;

d : in std_logic_vector(BIT_SZAM-1 downto 0);

q : out std_logic_vector(BIT_SZAM-1 downto 0)

);

end pelda_8d;

architecture Behavioral of pelda_8d is

begin

PROCESS --nincs erzékenyégi lista!!!!!!!

begin

WAIT UNTIL src_clk'EVENT AND src_clk='1';

IF (reset='1') THEN

q <=(others=>'1');

ELSE

q <=d;

END IF;

END PROCESS;

end Behavioral;Várakozik mindaddig amíg valamelyik jel változik

PROCESS

BEGIN

WAIT ON clk, rst

IF (rst=‘1’) THEN

output <=“00000000”;

ELSIF (clk’EVENT AND clk=‘1’) THEN

output <=input;

END IF;

END PROCESSCASE és WAIT ON plda:

példa D típusú tároló esetében: fájl

entity pelda_8 is

GENERIC (BIT_SZAM : natural :=8);

Port ( src_clk : in std_logic;

reset : in std_logic;

d : in std_logic_vector(BIT_SZAM-1 downto 0);

q : out std_logic_vector(BIT_SZAM-1 downto 0)

);

end pelda_8;

architecture Behavioral of pelda_8 is

begin

PROCESS

BEGIN

WAIT ON src_clk, reset;

IF (reset='1') THEN

q <="00000000";

ELSIF (src_clk'EVENT AND src_clk='1') THEN

q <=d;

END IF;

END PROCESS;if helyett case esettel:fájl

entity pelda_8c is

GENERIC (BIT_SZAM : natural :=8);

Port ( src_clk : in std_logic;

reset : in std_logic;

d : in std_logic_vector(BIT_SZAM-1 downto 0);

q : out std_logic_vector(BIT_SZAM-1 downto 0)

);

end pelda_8c;

architecture Behavioral of pelda_8c is

begin

PROCESS

BEGIN

WAIT ON src_clk, reset;

CASE reset IS

WHEN '1' => q<=(others=>'0');

WHEN '0' => IF (src_clk'EVENT AND src_clk='1') THEN

q<=d;

END IF;

WHEN OTHERS => NULL;

END CASE;

END PROCESS;

END Behavioral;- csak szimulációra alkalmazzuk

WAIT FOR idő;- Várakozik hogy elteljen a WAIT FOR után meghatározott idő Órajel generálása szimulációhoz

<clock>_process :process

begin

<clock> <= '0';

wait for <clock>_period/2;

<clock> <= '1';

wait for <clock>_period/2;

end process;A bemeneti jelek megadása az idő függvényében.

stim_proc: process

begin

-- hold reset state for 100 ns.

reset=‘1’;

wait for 100 ns;

reset=‘0;’

wait for <clock>_period;

start=‘1’;

-- egyéb bemenetek

wait;

end process;FOR / LOOP – véges ciklusszám

[címke:] FOR azonosito IN intervallum LOOP

(szekvenciális kifejezés)

END LOOP [címke];WHILE / LOOP -a ciklus addig ismétlődik, amíg a feltétel igaz

[címke:] WHILE feltétel LOOP

(szekvenciális kifejezés)

END LOOP [címke];EXIT- ciklus vége

[címke:] EXIT [címke_b] [WHEN feltétel];NEXT átugorhatunk lépéseket a ciklusból

[címke:] NEXT [cimke_b] [WHEN feltétel];Pl: fájl

FOR i IN 0 TO 5 LOOP

x(i)<=enable AND W(i+2);

y(0,i)<=w(i);

END LOOP;

WHILE (i<10) LOOP

WAIT UNTIL clk’EVENT AND clk=‘1’;

other statements

END LOOP;FOR I IN data’RANGE LOOP

CASE data(i) IS

WHEN ‘0’ => count:=count+1;

WHEN OTHERS =>EXIT;

END CASE;

END LOOP;

FOR I IN 0 TO 7 LOOP

NEXT WHEN i=skip;

…

END LOOPnext pl:

next;next cimke;- `next when A>B;

Next cimke when C=D or done;-- done is a Boolean variable

exit pl:

exit statementexit;exit cimke;exit when A>B;nexit cimke when C=D or done;-- done – boole változó

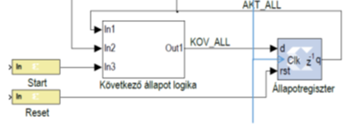

process (AKT_ALL_reg,start,cont)

Begin

case (AKT_ALL) is

when 0 => if start = '1' then

KOV_ALL <= 1;

else

KOV_ALL <= 0;

end if;

when 1 => if cont ='1' then

KOV_ALL <= 4;

else

KOV_ALL <= 2;

end if;

when 2 => KOV_ALL <= 3;

when 3 => if cont = '1' then

KOV_ALL <= 4;

else

KOV_ALL<=3;

end if;

when 4 => KOV_ALL<= 5;

when 5 => KOV_ALL<= 0;

when others => KOV_ALL <= 0;

end case;

end process;process (clk,reset)

begin

If reset='1' then

AKT_ALL<=0;

elsif clk'event and clk='0' then

AKT_ALL <= KOV_ALL;

end if;

end process;fájlok: téma 7 ppt, VHDL mintakód generate-re

Ebben a fejezetben a hallgató megismerheti a konkurens VHDL utasításokat. Összehasonlítva a szekvenciális utasításokkal, több típusú áramkör szekvenciális és konkurens utasítással is megvalósítható.

Példaprogramok tanulmányozásával elsajátíthatja a fontosabb utasítások működését és különböző gyakorlati alkalmazását.

A generikus (

GENERIC) paraméterek valamint aFOR GENERATEésIF GENERATEutasítások alkalmazásával lehetőség van egyszerű módon bonyolultabb áramköröket is megtervezni.A

Blocktípusú utasítás működését is megismerheti a hallgató, viszont a kurzus keretében nem alkalmazzuk. A kurzus terjedelme ugyanakkor nem teszi lehetővé a függvények (FUNCTION) és eljárások bemutatását.

- A szekvenciális processzen belül abban a sorrendben ahogy jönnek a processzen belül.

- A konkurens utasítások egymással párhuzamosan hajtódnak végre.

Két külön process párhuzamosan hajtódik végre, a bennük levő utasítások viszont egymás után egymáshoz képest.

SIGNAL hozzárendelés konkurensen, feltétel nélküli: a <= b - azonnali utasítás

SIGNAL hozzárendelés konkurensen, feltétellel: WHEN-el, ezzel lehet kétirányú síneket megadni:

jel <= [kifejezes when feltetel

else ...]

kifejezés;pl: x<=a when c ='0'; vagy x<=a when c = '0' else b;

Az összes eset lekezelése:

with szelekcios_bemenet select

jel<= kifejezes_1 when választási_lehetőségek_1,

...

kifejezés_n when választási_lehetőségek_n,

[kifejezés when others];Az others akkor kell ha minden egyéb jelet kezelünk és nem adjuk meg pontosan a bemenő jelet.

Block utasításokban párhuzamosíthatunk, mint alábba példa, vagy a következőket is megtehetjük:

- Port és generikus változok deklarálása

- (port map és generic map)

- Típus és alltípus deklarációs

- Allprogramrészek deklaráslás + megvalósítás

- Konstans változó és signal deklarálás

- Komponens deklarálás

- File, attributum és konfiguráció deklarálás

- többszintes egymásba ágyazás: block a blockban

entity pelda is

Port (-- S0 : in STD_LOGIC;

--S1 : in STD_LOGIC;

I0 : in STD_LOGIC;

I1 : in STD_LOGIC;

I2 : in STD_LOGIC;

I3 : in STD_LOGIC;

q : out STD_LOGIC);

end pelda;

architecture Behavioral of pelda is

Signal s0, s1 : std_logic;

Begin

-- párhuzamosan a következők:

RTL_AND_1: process(I0, I1)

Begin

S0<= I0 and I1;

end process;

RTL_OR: process(S0, I2)

Begin

S1<= S0 or (not I2);

end process;

RTL_AND_2: process(S1, I3)

Begin

q<= S1 and (not I2);

end process;

-- párhuzamosítás vége

End process;Label: BLOCK (guard expression)

[declarative part]

BEGIN

(concurrent guarded and unguarded statements)

END BLOCK label;- lehetővé tenni közös részek megosztását és újrahasznosítását

- elemeket a könyvtárba (

LIBRARY) helyezni - kódrészek megírhatóak:

- komponens

- függvényként

- eljárásként

mintafájl: pelda_12_generate.vhd

Két verzióval: FOR ... GENERATE és IF ... GENERATE. Előbbi egy ciklusként adott számszor rakja be a modult, utóbbi kivételeket kezelehet le.

pl FORos verzióra:

Label1: FOR azonosító IN intervallum GENERATE

(konkurens hozzárendelés)

END GENERATE;péld IFes verzióra:

Label2: IF feltétel GENERATE

(konkurens hozzárendelés)

END GENERATE;természetesen egymásban is használható egyik a másikkal pl:

Cimke1: FOR ciklus_azonosító IN intervallum GENERATE

...

Cimke2: IF feltétel GENERATE

(konkurens hozzárendelés)

END GENERATE;

...

END GENERATE;- komponensek (

COMPONENTS) - függvények (

FUNCTIONS) - eljárásokon (

PROCEDURES) - típusok

TYPE - konstansok

CONSTANT

Szerkezete, a két csomag_neve attribútum meg kell egyezzen, ha ugynahhoz a csomaghoz tartozik:

PACKAGE csomag_neve IS

(Deklarációs rész;)

END PACKAGE

[PACKAGE BODY csomag_neve IS

(Függvények és eljárások leírása;)

END csomag_neve;]példa:

LIBRARY ieee;

USE ieee. Std_logic_vektor.all;

PACKAGE példa_csomag IS

TYPE állapot IS (st1, st2, st3, st4);

TYPE szín IS (red, green, blue, black);

CONSTANT vector : STD_LOGIC_VECTOR (3 downto 0):=”1111”;

END példa_csomag;fájlok: pdf, mintaprogramok

Ebben a részben a hallgató megismerkedhet az FPGA-ban elkészített modulok tesztelési lehetőségeivel. A témában részletesen van tárgyalva egy FPGA-ba betöltött modul működés közbeni tesztelése.

A példaprogram alapján egy tcl szkript programban van megvalósítva egy áramkör működés közben való tesztelése. A tesztelés során a tesztelendő jelek az FPGA-ba integrált ILA modulon keresztül vannak kivezetve az FPGA laphoz csatolt számítógépen futó grafikus felületre.

A VIvado programból a tcl szkrip futtatásával automatikusan létrejön a tesztkörnyezet.

Javasolt, hogy a minta alapján a hallgató akár egy általa elkészített VHDL modulra, vagy a példaprogramok közül kiválasztott modulra készítse elő a szimulációs környezetet.

Tesztelésre több lehetőség is van:

- áramkör szimulációja

- külső méréssel

- logikai analizálás az FPGA-n

Szimulációk:

- behavioral simulation - viselkedési szimuláció szintezést követően

- functional simulation - funkcionális szimuláció fordítást követően

- static timing analysis - statikus időanalízis leképzésifázis után

- timing analysis - az elhelyezéstés huzalozástkövetően

- az áramkör teljesítményanalízise (szimuláción kívül)

Sokszor az FPGA áramkör helyes működést mutat önmagában, bekötés után viszont helytelent. A probléma megoldásához működés közben kell vizsgálni a jeleket.

Az adatok az FPGA áramkörből a JTAG láncon vannak kivezetve ami USB vagy Ethernettel csatlakozik a számítógéphez ahol a jelek megjelenhetnek grafikusan ábrázolva.

- előosztó és számlálóból álló áramkör teljes fájl: téma 8.../top_level_2.vhd

modulo : process(src_clk)

variable x: integer range 1023 downto 0 := 0;

variable q_div: STD_LOGIC:= '0';

begin

if src_clk'event and src_clk='1' then

if x<div_val then

x:=x+1;

--q_div:=q_div;

else

x:=0;

q_div:=not(q_div);

end if;

q_clk<=q_div;

end if;

end process modulo;szamlalo: process(q_clk, reset)

variable sz: std_logic_vector(3 downto 0);

begin

if q_clk'event and q_clk='1' and start='1' then

if reset='1' then

sz:=(others=>'0');

else

sz:=sz+1;

end if;

end if;

q<=sz;

end process szamlalo;Tesztelés Vivadoban:

- Set Up Debug varázsló (Debug Cores integrálással)

- XDC modul a tervhez kapcsolása

Tesztelés áramkörben működés közben:

- tesztelendő jelek kijelölése

- jel HDL forrásodban megjelölése

- megjelölésszintetizált áramkörben

- jelek megjelölése

tclparanccsal való megjelölésre

- implementációs fázis: tesztelésre használt IP magok terve implementálása, konfigurációs fájl létrehozása

- Analízis fázis: jelek kiolvasása működés közben

- SetUpDebug varázslóhasználata

- jelek megjelölése és IP modulhoz rendelése

unassigned netslistából kiválasztás- jelek megjelölése szintetizált áramkörben - jobb klikka vezetékre a Sinthesized Design nézetben

Set UP Debugparancs végrehajtása:- Flow navigátor ablak -> Synthesis -> Synthetized Design -> Set Up Debug vagy Tools -> Set Up Design

- Window menü -> Debug nézet -> jelek kijelölése Unassigned Debu Nets lista -> Set Up Debug

-újabb jelek hozzáadása/meglévő elvetése:

Find Nets to ADD

- órajel kiválasztása -trigger/capture mód megadása

Finishgomb

TCL prancsokkal terv létrehozása, az alábbi scriptet futtatvamindne lépés automatikusan végrehajtódik, és az eszköz kész a tesztelésre:

teljes fájl: teszt_debug_3.tcl

set terv_nev teszt_7

set konyvtar C:/Munka/I_Felev/UKDA_2017/L6

start_gui

create_project ${terv_nev} ${konyvtar}/${terv_nev} -part xc7z010clg400-1

VHDL hardver leíró nyelv beállítása

set_property target_language VHDL [current_project]

VHDL forráskódnak a tervhez való csatolása

add_files -norecurse ${konyvtar}/top_level_2.vhd

Megkötés állománynak a tervhez valócsatolása

add_files -fileset constrs_1 -norecurse ${konyvtar}/system_4.xdc

update_compile_order -fileset sources_1

update_compile_order -fileset sim_1

Szintézis futtatás

launch_runs synth_1

Várakozás a szintézis befejezésére

wait_on_run synth_1

Synthesized Design megnyitása

pen_run synth_1

Debug core magnak a tervhez való csatolása

create_debug_core u_ila_0 ila

ILA modul konfigurálása

set_property C_DATA_DEPTH 65536 [get_debug_cores u_ila_0]

set_property C_TRIGIN_EN true [get_debug_cores u_ila_0]

set_property C_TRIGOUT_EN false [get_debug_cores u_ila_0]

set_property C_ADV_TRIGGER true [get_debug_cores u_ila_0] #enable advanced trigger mode

set_property C_INPUT_PIPE_STAGES 0 [get_debug_cores u_ila_0]

set_property C_EN_STRG_QUAL true [get_debug_cores u_ila_0] #enable Basic capture mode

set_property ALL_PROBE_SAME_MU true [get_debug_cores u_ila_0]

set_property ALL_PROBE_SAME_MU_CNT 1 [get_debug_cores u_ila_0]

set_property port_width 1 [get_debug_ports u_ila_0/clk

ILA modul órajelének meghatározása

connect_debug_port u_ila_0/clk [get_nets [list src_clk_IBUF_BUFG]]

A Testmodulon probe0 sínszélességének meghatározás

set_property port_width 3 [get_debug_ports u_ila_0/probe0]

probe0 bemenetre a start, reset és q_div jelek csatolása

A forráskódban meghatározott jelek nem érhetőek el tesztelésre a szintézist követően, hanem a bemenetek esetében a start_IBUF reset_IBUF jeleket alkalmazzuk, kimenetek esetében pedig a q_OBUF jeleket connect_debug_port u_ila_0/probe0 [get_nets [list start_IBUF reset_IBUF q_div]]jeleket kell alkalmazni

Egy újabb bemenet (probe1) létrehozása a tesztmodul bemenetére

create_debug_port u_ila_0 probe

Sínszélesség beállítása

set_property port_width 4 [get_debug_ports u_ila_0/probe1]

q_OBUF[0], q_OBUF[1], q_OBUF[2], q_OBUF[3] kimenetekneka probe1 bemeneti portra való csatolása

connect_debug_port u_ila_0/probe1 [get_nets [list q_O*]]

Megkötés fájl mentése

save_constraints_as system_${terv_nev}.xdc

set_property constrset system_teszt_6.xdc [get_runs synth_1]

set_property constrset system_teszt_6.xdc [get_runs impl_1

Implementáció lefuttatása

aunch_runs impl_1

wait_on_run impl_1

Konfigurációs fájl generálás

launch_runs impl_1 -to_step write_bitstream

wait_on_run impl_1

harver megnyitás

open_hw

Szerver indítása az FPGA áramkörre való kapcsolódás céljábó

onnect_hw_server

Célhardver megnyitása

open_hw_target

Konfigurációs.bit fájl és debug_net.ltx beállítása

set_property PROGRAM.FILE

${konyvtar}/${terv_nev}/${terv_nev}.runs/impl_1/top_level_2.bit [lindex [get_hw_devices] 1]

set_property PROBES.FILE

${konyvtar}/${terv_nev}/${terv_nev}.runs/impl_1/debug_nets.ltx [lindex [get_hw_devices] 1]

current_hw_device [lindex [get_hw_devices] 1

hardver frisítése

refresh_hw_device [lindex [get_hw_devices] 1

Hardver programozása

program_hw_devices [lindex [get_hw_devices] 1]

refresh_hw_device [lindex [get_hw_devices] 1

A tesztelés lépései:

- A top_level.vhd modul alapján egy terv létrehozása

- Atesztelendő jelek kiválasztása, a debug interfésznek a tervbe való csatolása, a jeleknek a tesztmodulba való csatolása

- Órajeltartomnyok kiválasztása

- tesztelő ILA IP modul paraméterezése

- terv implementálása, implementáció elindításaa

tclparancsablakból:launch_runs impl_1 - Konfigurációs fájl létrehozása:

launch_runs impl_1 -to_step write_bitstream - Hardver menedzser megnyitása, kapcsolódás hardvereszközhöz

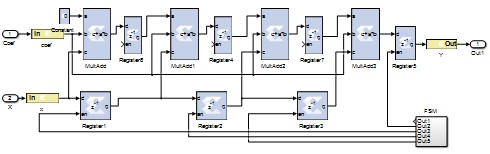

Ebben a részben a hallgatók megismerhetik a System Generator környezetet, a megvalósítható feladatokat, tapasztalatot szereznek System Generator típus terv kialakításában. Megismerkednek a fontosabb modulokkal, adat típusok konverziójával a Simulink környezetből System Generatorba és vissza.

A tapasztalatok alapján a hallgatók képesek lesznek egyszerű modelleknek System Generatorban való kialakítására és szimulációjára.

Az alapötletek elsajátítását követően komplexebb feladatokat is meg tudnak valósítani

- pontos lebegő és fixpontos implementáció bit és ciklus segítségével

- Simulinkből HDL kódot generál

- Hardver ko-szimuláció

DSP modellezés:

- Jelfeldolgozás (CORDIC, Cascaded Integrator-Comb (CIC) filters, FFT, IFFT, FIR filter)

- Aritmetikai és logikai művelet alapú rendszerek

- Memória alapú rendszerek

- Interfész

Teszteléskor az FPGA lábairea kell csatolni:

- a jeleket, amelyeket egy külső oszcilloszkóppal szeretnénk tanulmányozn

- a jeleket, amelyeket egy külső logikai analizátorral szeretnénk tanulmányozni

Fontosabb alkalmazási területek -jelfeldolgozás: trigonometirai függvények generálása újrakonfigurálható logikában -szűrőalgoritmusok: FIR, CIC -Gyors Fourier transzformáció

alkalmazásának előnyei:

- Stimulus generálása (Simulink töbökkel)

- tervezett rendszer analízise (az összes kimenő és átmeneti jel analizálása)

- DSP tervezés (összetett számítások esetében is)

The Xilinx Blockset is a family of libraries that contain basic System Generator blocks. Some blocks are low-level, providing access to device-specific hardware. Others are high- level, implementing (for example) signal processing and advanced communications algorithms.

- egyszerű áramköri elemek: regiszterek, összeadók, számlálók,

- digitális jelprocesszálásra szolgáló modulok: DSP modul, FIR szűrő, Komplex szorzómodul, FFT, Inverz FFT

- memória modulok: FIFO, BRAM, Dual port BRAM, FIFO

- kommunikációs modulok: Reed-Solomon Encoder, Reed-Solomon Decoder

- típuskonverzió

Könyvtár elérése: Tools->Xilinx->Block Add vagy Xilinx Block Add gyorsmenüvel

System Generator tömbök adattípusai:

- Boolean

- Tetszőleges pontosságú fix-pontos

- Lebegőpontos: IEEE-754 Standard ábrázolással:

Single,Double,Custom- a pontosságtól függően, a tetszőlegesnek a legnagyobb hardverígénye de a elgnagyobb pontossága is Simulink alap adattípus (double dupla pontosságú lebegőpontos) Gateway tömbök:

Gateway out modul a Xilinx jeleket visszaalakítják double jelekké

- Gateway In - a

dobletípusú Simulink jelet átalakítjákXILINX System Generatorjellé és mintavételezési szerepe is van, mintavételezi a folytonos Simulink jeleket - Gateway out - modul a Xilinx jeleket visszaalakítják double jelekké

Quantization in this context refers to how the tools handle the LSBs of numbers. When a large floating point number is converted to a fixed point number, a lot of “unnecessary” precision is lost. Users must decide whether to “cut the precision off” (truncate) or to round the result for the nearest precision value.

Overflow in this context refers to how the tools handle the MSBs of numbers. When a large floating point number is converted to a fixed point number and the number is too large to be represented by the fixed point number scheme, users must decide whether to allow Wrap (the MSBs are dropped) or to Saturate the result (like when a counter reaches its max value) so that the maximum number is used for values greater than it

A `Gateway IN` valósítja meg a típuskonverziót a Simulink és FPGA között.

Az átmentet az FPGA lap és a Simulink szimulációs program között automatikusan hozza létre a System Generator környezet.

- Előjel nélküli:

Ufix_5_3- 5 biten ábrázolt: 2 bit az egész részre és 3 bit a törtrészre - Előjeles:

Fix_16_8- kettes komplemens 16 biten ábrázolva: 8 bit a törtrész Lebegőpontos szám fixpontossá alakításakor veszít a pontosságból, el kell dönteni, hogy kerekítjük, vagy levágjuk a biteket, ezt előre a pontossággal adjuk meg. Pontosságuk lehet: - full precision

- User-specified precision

- kvantálással: Truncate, Round

- Túlcsordulással: Wrap, Saturate, Flag as error

Bit szintű műveletek: Reinterpret, Combine, Convert, Extract

Bit pontos (bit-true): System Generator és a Simulink tömbök határánál, a szimuláció során előállított érték bit szinten tökéletesen megegyezik a megfelelő pontban a hardver által generált értékkel

ciklus pontos (cycle true): a határoknál a megfelelő értékek a megfelelő időben generálódnak

System generator fordítás után a megfelelő rész a megfelelő mintavételezéssel működjön..

- mintavétlezési periódus egy órajelből (

clk) és az órajelhez kapcsolódó órajel engedélyező (CE) jelből áll elő. Az órajelet engedélyező jel periódusa az órajel periódusának egész számú többszöröse. - a mintavételezési periódus alapján határozza meg, milyen órajel engedélyező jel kell

- felhasználó két paramétert ad meg:

Simulink system periodandFPGA clock period- Meghatározza a skálázási tényezőt a Simulink szimulációs idő és a hardveres implementációnak megfelelő idők között

Simulink system period: a mintevételezési periódus legnagyobb közös osztója példa:P- Simulink modell periódusaC- FPGA rendszer órajelének periódus- Egy szimuláció amely

k*pegységet igényel a Simulink szimulációban,kórajelet igényel a hardverben (k*c [ns])

Hibakezelés

- Clock Probe

- Clock Enable Probe

- entitások nevei nem egyezhetnek

- Két irányú portok nem jelennek meg a System Generatorban mint portok csak a HDL black box modulban

- órajel (clk) és órajel engedélyező (CE) csak párban működik,

Clk,ce std_logictípusúak - Lemenő élre triggerelt kimeneti adat nem alkalmazható

HDL modul a BlackBox tömbbel importálható

Top_levelmodul neve- Meg kell határozni a

top level entity-t és meg kell adni az alkalmazott Hardver Leíró Nyelvet:this_block.setEntityName(‘proba’); - VHDL Module:

this_block.setTopLevelLanguage('VHDL'); - Verilog Module:

this_block.setTopLevelLanguage('Verilog');

- Meg kell határozni a

- alkalmazott HDL nyelv (VHDL/Verilog)

- portok

- Bemeneti port hozzáadása:

this_block.addSimulinkInport('din'); - Kimeneti Port hozzáadása:

this_block.addSimulinkOutport('dout'); - Kétirányú port hozzáadása

config_phase = this_block.getConfigPhaseString; if (strcmpi(config_phase,'config_netlist_interface')) this_block.addInoutport('bidi'); -- Rate and type info should be added here as well end- Szimulációban nem jelenik meg !! - portok leírása:

Vagydin = this_block.port('din'); dout = this_block.port('dout'); dout.setWidth(12); dout.setBinPt(8); dout.makeUnsigned();

Kétirányú port esetében szimulációs adat mentésedout = this_block.port('dout'); dout.setType('Ufix_12_8');

if (strcmpi(this_block.getConfigPhaseString,'config_netlist_interface')) bidi_port = this_block.port('bidi'); bidi_port.setGatewayFileName('bidi.dat'); end

- mintavételezési ráta megadása:

setRatehatározható meg egy jel mintavételezési rátája

setRate, dout.setRate(3); --Kimeneti portok típusa és kimeneti ráta a bemenet függvényében: input_width = this_block.port('din').width; input_rate = this_block.port('din').rate; if (this_block.inputTypesKnown) dout.setWidth(this_block.port('din').width); end if (this_block.inputRatesKnown) dout.setRate(this_block.port('din').rate*2); end

- Bemeneti port hozzáadása:

- generikus paraméterek:

addGeneric('dout_width','Integer','12');- konfigurációs függvényben a Generic paraméter beállításával skálázható a hardver

- órajel konfig: Egy szinkron órajel (single clock) vagy több aszinkron (multilpe independent clock)

- órajel (

clk) és az órajel engedélyező (ce) párban kell létezzenek, - a ce és clk a névben is szerepelnie kell:

src_clkés a párjasrc_ceaddClkCEPair('clk_3','ce_3',3);

- órajel (

- mintavételezési ráta

- kapcsolódó állományok

- van-e benne kombinációs logika

IP Catalog- IP mag hozható létre, hozzáadható a Vivado IP katalógusához, más tervben való alkalmazás céljábólHardware Co-Simulation(JTAG or Point-to-point Ethernet) - A ko-szimuláció során a Xilinx tömbökkel megadott rész, a szimuláció futása során az FPGA áramkörben hajtódik végreSynthesized Checkpoint- Creates a design checkpoint file (synth_1.dcp) that can then be used in any Vivado IDE project.HDL Netlist- Létrejön egy HDL netliszt, amely szintén felhasználható más tervekben

fájlok: System Generator_ERASMUS_2017_laptoprol_B_2017_12_01.pptx

Ebben a részben a hallgató megismerkedik a harver ko-szimulációval. Simulink (System Generator) környezetben megvalósított hardverre lehetőség van a szimuláció futtatása során, hogy a Simulink modelből az az FPGA modulok a szimuláció közben az FPGA áramkörben fussanak le.

Ebben a részben System Generator hardver ko-szimuláció típusú terv létrehozása van bemutatva. Ez az üzemmód lehetővé teszi például egy eszköznek: robot kar, adatgyűjtésre szolgáló modul, Simulink környezethez való csatolását és a rendszereken futó feladatok gyors tesztelését.

Nagyon rövid idő alatt van lehetőség ötletek kivitelezésére, megvalósíthatóságának tesztelésére. A System Generatorban tervezett FPGA egységből létrehozható egy IP modul, amely például a Vivado eszközzel integrálható egy nagyobb tervbe. A diákok a modul elsajátítása után képesek lesznek hardver ko-szimulációs típusú feladatok megvalósítására és ötleteikből kiindulva FPGA áramkörbe konkrét feladatokat gyakorlatba ültetni.

- Simulink szimuláció során a modell egy részének az FPGA áramkörben való végrehajtását

- Simulink és FPGA eszköz közötti kommunikációs interfészt automatikusan létrehozza a System Generator tervezőeszköz, lehet:

JTAG,Ethernet - fordítás után létrejön egy Simulink tömb, ezen keresztül megy a kommunikáció a lappal

FONTOS: Az FPGA fejlesztőlapot, amelyen szeretnénk a hardver ko-szimulációt futtatni, fel kell telepíteni a számítógépre: telepítés instrukciók, master-board fájl letölltés

Alapértelmezetten a szimuláció csak a JTAG órajelre működik, ezért Multiple clock domain-t kell létrehozni, a tervet két modulra kell bontani, az egyikben JTAG interfész en átvitt jelek kerülnek, a másikon rendszer órajelén működő részek.

Mindkét modulon külön órajelre sznikronizáljuk a Simulinkhez kapcsolódó jeleket (modulok) I/O portokat JTAG órajeleket (jtag_clk) és az FPGA-hoz kapcsolódó kimeneti jeleket (modulok) sys_clock

Órajel létrehozása:

set_property -dict { PACKAGE_PIN L16 IOSTANDARD LVCMOS33 } [get_ports { sys_clock }];

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports { sys_clock }];be kell másolni az .xdc állományba:

netlist_mclk\hwcosim\pwm_mclk.srcs\constrs_1\imports\sysgen\pwm_mclk_clock

fájl: High_Level_Synthesis_SZIR_FMR_2017_okt_31_hu_2017_12_01.pptx

Ebben a részben a hallgató megismerkedhet a magas szintű szintézissel. A téma keretében rámutatunk a magas szintű szintetizáló eszközök lényegére, vagyis egy maga szintű programozási nyelven specifikált feladatból lehetőség van hardver modulok létrehozására. A téma keretében részletezve vannak a magas szintű szintetizáló eszközök alkalmazásának előnyei. A hallgatónak a téma elsajátítását követően rálátása lesz a magas szintű szintézisre: milyen szintetizáló eszközök alkalmazhatóak, a fontosabb lépések, részfeladatok, melyeket a HLS eszközök követnek a C, C++, System C specifikációból kiindulva az RTL szintű modell létrehozásáig.

Megmutatjuk a HLS eszközökkel kapcsolatosan felmerülő kérdéseket. Tárgyalva vannak a HLS alapú tervezésben alkalmazott architektúra szintű kényszer típusok, modul hierarchia, interfész, memória, ciklus szintű kényszerek, időkorlátok, iteráció szintű kényszerek.

A magas szintű szintézisről három előadás keretében mélyítheti el ismereteit a hallgató.

Az első, bevezető részt követő részben részletekbe menően tárgyaljuk a HLS szintetizálás során a feladatok ütemezését, erőforrás kiosztást, tömb és ciklusoptimalizálási ötleteket.

A harmadik részben konkrét feladatnak Vivado HLS környezetben való bemutatására kerül sor.

- Bonyolult SoC és multimédia alkalmazások (Hosszú tervezési idő)

- Hálózat az integrált áramkörben

- Több intelligens erőforrás (több master egység) (CPU, DMA,…)

- Több megabájtnyi programkód

- A beágyazott rendszeren futó beágyazott operációs rendszer

- Osztott memória

- SoC tervezési problémák

- A szoftver komplexitása (az algoritmus komplexitása)

- Eszközök a beágyazott hardver tervezéshez/beágyazott szoftver (OP) tervezéshez

- A piacra kerülési idő (a hagyományos módszerekkel hosszú )

- IP magok újra felhasználása

- Magas szintű szintetizáló eszközök alkalmazása

- Tervezési lehetőségek felkutatása

- A magas szintű szintézis csak egy kis része a magas szintű tervezésnek

tervező eszköz hozza létre az RTL szintű implementációt

- Vivado HLS (XILINX)

- Synopsys (Synphony C Compiler High-Level Synthesis from C/C++ to RTL)

- Cadence® Stratus™ High-Level Synthesis (HLS)

wikipedia, xilinx.com/.../esl-design.html

- Vivado HLS meghatározza melyik műveletet melyik ciklusban kell elvégezni (ütemezés)

- Meghatározza melyik művelet végrehajtására, milyen hardveregységet alkalmaz

- Ehhez:

- Beépített alapértelmezések betartása

- meghatározott alapelvek (direktívák) és kényszerfeltételek felülírják az alapértelmezett beállításokat

- Késleltetések és területhasználat kiszámítása az alkalmazott technológia/eszköz függvényében

Meghatározás: automata vagy félautomata módon létrehoz egy RTL szintű leírást egy viselkedési szinten megadott specifikációból.

Bemenet:

- Viselkedés szintű specifikáció

- Tervezési kényszerek

- Könyvtárelemek az elérhető RTL komponensekkel

Kimenet:

- RTL leírás

- Teljesítmény értékelés

- Milyen gyorsan sikerül a számítást elvégezni?

- Mennyi hardver erőforrásra van szükség?

- Mennyire hatékonyan sikerült létrehozni egy pipeline struktúrát?

**Direktívák prioritása:

- Teljesítmény teljesítése (idő & áteresztőképesség)

- Késleltetés (latency)

- Területhasználat optimalizálása**

Magas szintű szintézis –az algoritmus leírása valamilyen magas szintű programozási nyelven (System C, Ansi C/C++, Matlab)

A magas szintű kód analízise, architektúra szinten kényszereknek való alávetése és megfelelő ütemezése után létrejön egy terv RTL (Register Transfer Level) absztrakciós szinten, valamilyen hardver leíró nyelven (például VHDL, Verilog).

Tervező eszköz által hardver leíró nyelven létrehozott tervet egy logikai szintetizáló eszközzel szintetizálva elkészül a hardver

A hardver tervezés történhet különböző absztrakciós szinten. Általában alkalmazott absztrakciós szintek:

- Kapu szintű absztrakció

- Regiszter szintű absztrakció

- Algoritmus szintű absztrakció

A tervező leírja a modulok funkcionalitását és megtervezi a modulok közötti kommunikációhoz a protokollt A magas szintű szintetizáló eszköz kezeli a mikro-architektúrát (RTL), átalakítja az időkorlát nélküli vagy részlegesen időzített funkcionális kódot teljesen időzített RTL megvalósításra, automatikusan létrehozza az órajel szintű részletes hardvert. Az elért (RTL) megvalósításhoz használnak egy hagyományos logikai szintetizáló eszközt, amely létrehozza a kapu-szintű megvalósítást.

Automatizált tervezés:

- értelmezi egy kívánt viselkedés algoritmus szinten való leírását

- létrehoz egy digitális hardvert, amely megvalósítja a tervet

HLS-re szakirodalomban alkalmazott kifejezések:

- C synthesis

- electronic system-level (ESL) synthesis,

- algorithmic synthesis

- behavioral synthesis

Gyakran alkalmazott programozási nyelvek: C, C++, SystemC, Matlab kódból képesek hardvert szintetizálni.

célja: hardver tervezők sázmára biztosítja a hardver tervezését, tesztelését, ellenőrzését, feladat leírás magas absztrakciós szinten.

**részfeladatai: **

- Lexikális feldolgozás (Lexical processing)

- Algoritmus optimalizálása (Algorithm optimization)

- Vezérlés/Adatfolyam analízis (Control/Dataflow analysis)-

- Elvégzendő műveletek felderítése

- Adatfüggőségek felderítése

- Könyvtár processzálás (Library processing) –lehetséges erőforrások keresése az elvégzendő műveletek megvalósításhoz

- Erőforrás kiosztása (Resource allocation) -az erőforrások hozzárendelése az elvégzendő műveletekhez (az adatút kialakítása)

- Erőforrások ütemezése (Scheduling)

- Az erőforrások ütemezése (melyik műveletvégző egységet mikor kell működtetni)

- Alegységek szinkronizálása

- A vezérlőegység kialakítása

- Funkcionális egységek hozzárendelése (Functional unit binding )

- Regiszterek csatolása (Register binding)

- Kimenetek processzálása

automatikusan alkalmazhatóak kényszerek (megszorítások) az architektúrára:

- Hierarchia – a modulok hogyan épülnek hierarchikusan egymásra

- Interfész (Interface): Meghatározni milyen interfészen valósul meg kommunikáció különböző modulok között

- Memória (Memory) - Milyen méretű memóriából lehet kialakítani egy tömböt, ha egy adatsort memóriába tároltam, akkor csak szekvenciálisan tudom kiolvasni vagy beírni az adatokat

- Ciklus szintű kényszerek (Loop) - Egy adott ciklust hogyan szeretnék megvalósítani (pipeline, párhuzamos)

- Alacsony szintű időkorlátok (Low-level timing constraints) - Milyen frekvencián működik a rendszer?, Két jel között mekkora lehet a maximális késés? Minimum milyen frekvencián mintavételezek egy jelet?

- Iteráció szintű kényszerek

A bemeneteket leírva egyszerűen C/C++ nyelven és alkalmazva egy automatizált interfész szintetizáló technológiát, amely az interfészen megoldja az időzítéseket (szinkronizálást) és az interfészhez hozzárendeli a kommunikációs protokollt

Kiválasztom a tervezés során az interfész típusát => a tervezőeszköz létrehozza.

Hardver interfész opciók:

- Adatfolyam (streaming)

- Egy portos BRAM memória

- Két portos BRAM memória

- FIFO modulok

- Kézfogás alapú mechanizmusok

- Algoritmus szintű absztrakció, Adat típusok (egész, fix pontos, lebegőpontos aritmetika Interfészek (FIFO, AXI4, AXI4-Lite, AXI4-Stream)

- Könyvtár elemek széleskörű választéka tetszőleges pontosságú adattípusok Video feldolgozáshoz könyvtári elemek DSP Memóriamodulok

- Kényszerfeltételekkel definiált architektúra Leghatékonyabb megoldás feltárása

- Gyorsított ellenőrzés C / C ++ programkód használatával Tesztpad létrehozása Szimuláció Szintézis

- Hatalmas tervezési tér

- Komplex tervezési tér feltárás

- Több kritériumon alapuló optimalizáló technikák

- Minél gyorsabb legyen az algoritmus

- Lehető legkevesebb elemet alkalmazzak

- Adatcserére alkalmazott szabványok hiánya

- SoC szimulációs idő kulcsfontosságú kérdés

- A HLS technikának a tervezők által való elfogadása! (nem kis gond)

- A beágyazott rendszert tervező (HDL) és a HLS eszközt tervező (C,C++) között egy közös nyelv találása

- Beágyazott rendszer tervező HDL

- HLS eszköztervező C stb.

- A beágyazott rendszert tervező (HDL) és a HLS eszközt tervező (C,C++) között egy közös nyelv találása

- PC: Kompilálás: a cél architektúra teljes mértékben ismert

- HLS-sel való tervezés: a cél architektúra csak parciálisan ismert

- Adatfolyam/szisztolikus tömbök: RTL leírás

- Adat utat tartalmazó véges állapotú automata: processzoron futó alkalmazáshoz közel álló leírás

- HLS technikai kérdések:

- Kezdeti specifikáció formátum / nyelv?

- Specifikáció finomítása : egész számok (előjeles, előjel nélküli, fixpontos aritmetika, lebegőpontos aritmetika)

- Matlabban nem igazán foglalkozunk az adattípussal (double)

- Ütemezés/Erőforrás hozzárendelés finomítása: erőforrás kényszerek

- Technológiai erőforrás hozzárendelés finomítása (például FPGA áramkörön valósítom meg, milyen családú FPGA)

C-alapú nyelvek (hardver leíró nyelvek): Handel-C, Silicon-C,Hardware-C ,System-C

gondok:

- Hogyan fejezzük ki a párhuzamos vagy szekvenciális működést? Adatfolyam alapú / Szekvenciális processzálás / Eseményvezérelt

- Hogyan alkalmazzunk algoritmikus és RTL alapú leírást

- Mit specifikáljunk előre: Ciklusok, Interfészek?

- Hogyan vezessünk be kényszereket, tanácokat?