Real time digital image processing in a Cyclone IV FPGA, using the DE0 Nano development board and OV7670 camera module.

Filters are changed in real time with the board's buttons.

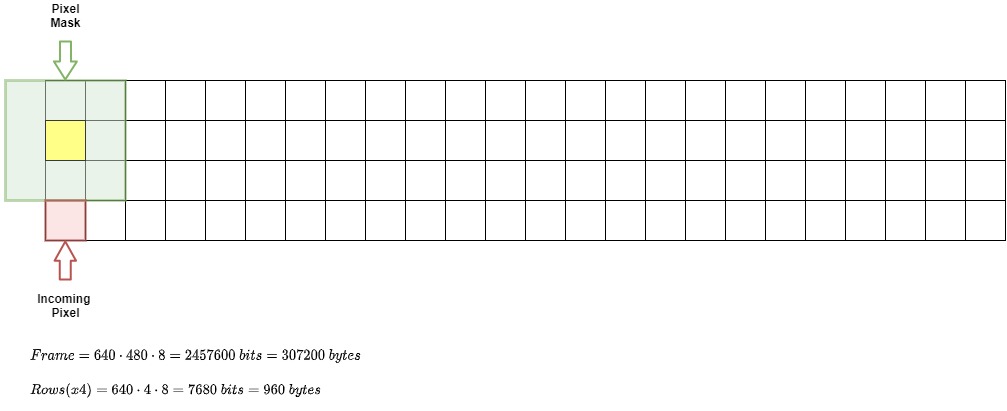

Since we are using the limited M9K blocks available in the FPGA, we can't buffer a whole frame from the camera data. The following scheme is implemented, where we store 4 rows of data, use the oldest 3 to apply the kernel (green) and write in the last one (red):

- design/: Contains design documents such as drawings, diagrams or schemes

- quartus/: Contains the Quartus project

- hdl/: VHDL files used for custom modules

- bdf/: Modules designed schematically

- symbols/: Symbols generated for created modules

- reference/: Contains reference documents such as component datasheets or application notes

- miscellaneous/: Contains some general files and documents

- support/: Contains