DRAM

La memoria dinámica de acceso aleatorio o DRAM (del inglés dynamic random-access memory) es un tipo de tecnología de memoria de acceso aleatorio (RAM) basada en condensadores, los cuales pierden su carga progresivamente, necesitando de un circuito dinámico de refresco que, cada cierto período, revisa dicha carga y la repone en un ciclo de refresco. En oposición a este concepto surge el de SRAM (RAM estática), con la que se denomina al tipo de tecnología RAM basada en semiconductores que, mientras siga alimentada, no necesita refresco.

Se usa principalmente como módulos de memoria principal de ordenadores y otros dispositivos. Su principal ventaja es la posibilidad de construir memorias con una gran densidad de posiciones y que todavía funcionen a una velocidad alta: en la actualidad se fabrican integrados con millones de posiciones y velocidades de acceso medidos en millones de bit por segundo.

Como el resto de tipos de RAM, es volátil por lo que si se interrumpe la alimentación eléctrica la información almacenada se pierde. Fue inventada a finales de los sesenta y es una de las memorias más usadas en la actualidad.[1] DRAM tuvo un aumento del 47 % en el precio por bit en 2017, el salto más grande en 30 años desde el salto del 45 % en 1988, mientras que en los últimos años el precio ha estado bajando.[2]

Historia

[editar]

La memoria dinámica fue desarrollada en los laboratorios de IBM pasando por un proceso evolutivo que la llevó de usar 6 transistores a sólo un condensador y un transistor, como la memoria DRAM que conocemos hoy. La invención de esta última la hizo Robert Dennard[3] quien obtuvo una patente norteamericana en 1968[4] por una memoria fabricada con un solo transistor de efecto de campo y un condensador.

IBM estaba encaminado a mejorar sus equipos de cómputo, como por ejemplo la línea System 360: el modelo 25 en 1968 ya incluía un ScratchPad (una especie de Caché controlada por software) en forma de integrados 5 veces más rápidos que la memoria principal basada en núcleos de ferrita.[5] Dado el modelo de negocios de IBM que consistía en vender o arrendar computadores,[6] un negocio rentable, para IBM el uso de DRAM se reducía a ser el complemento de la memoria principal basada en núcleos magnéticos. No hubo interés en comercializar ese tipo de memorias para otros fabricantes ni tampoco se pensó en usar las tecnologías de estado sólido tipo SRAM o DRAM para construir la memoria principal. La empresa Intel fue creada para aprovechar esa oportunidad de negocios: Gordon Moore, observaba que hace tiempo la industria de los semiconductores se había estancado, a pesar de existir potenciales usos de los integrados de silicio como la fabricación de SRAM y DRAM.[7]

Aunque Intel se inició con SRAM como la i1101 y la i3101, el primer producto rentable fue el integrado de DRAM i1103 de 1024 bits. El i1103 lanzado en 1970 estaba formado por celdas de memoria con 3 transistores tipo PMOS y un condensador,[8] estaba organizado en un arreglo de 32 filas y 32 columnas, empacado en un encapsulado de 18 pines y con un costo de 1 centavo por bit era un fuerte competidor para las memorias de núcleo. La producción y calidad del integrado era difícil de mantener, hecho que se demostró cuando Intel entregó parte de la producción a otra empresa llamada Microelectronics Integrated Limited (MIL) que en un principio pudo obtener mejores resultados que la misma Intel, pero después del cambio importante en el proceso de fabricación no fue capaz de producir.[7]

La memoria i1103 era muy primitiva en comparación a las DRAM de la actualidad, aun así se comportaba mejor que la memoria de núcleo y con un precio menor. A finales de 1971 se había convertido en el producto dominante para la fabricación de memoria principal y era usado por 14 entre 18 de los principales fabricantes de computadores,[9] ganando el mote "core killer".[10]

Reinvención de la DRAM

[editar]Para 1973 Intel y otros fabricantes construían y empacaban sus integrados de DRAM empleando un esquema en el que se aumentaba un pin por cada vez que se doblaba la capacidad. De acuerdo a este esquema, un integrado de 64 kilobits tendría 16 pines solo para las direcciones. Dentro de los costos más importantes para el fabricante y el ensamblador de circuitos impresos estaba la cantidad de pines del empaque y en un mercado tan competido era crucial tener los menores precios. Debido a eso, un integrado con una capacidad de 16 pines y 4Kb de capacidad fue un producto apreciado por los usuarios, que encontraban a los integrados de 22 pines, ofrecidos por Intel y Texas Instruments como insumos costosos.

El lanzamiento de la memoria MK4096 de 4K, con un solo transistor por celda y con direccionamiento multiplexado resultó del trabajo de Robert Proebsting quien observó que en las celdas con un solo transistor, era imposible acceder la información en una posición, enviando al mismo tiempo los datos de fila y columna a la matriz: había que enviar las señales una después de la otra. La solución a nivel de la celda conducía a un ahorro en el empaque, ya que la dirección podría recibirse en dos etapas, reduciendo la cantidad de pines usados.[11] Por ejemplo para un integrado de 64 Kb se pasaba de 16 pines dedicados a solo 8 y dos más para señales de control extra. La multiplexación en tiempo es un esquema de direccionamiento que trae muchas ventajas, a costa de unos pocos cambios en el circuito externo, de manera que se convirtió en un estándar de la industria que todavía se mantiene. Mucha de la terminología usada en la hoja de datos del MK4096 todavía se usa y muchos de los parámetros de temporización como el retardo RAS a CAS fueron instaurados con ese producto, entre otros aspectos.[12][13]

Funcionamiento

[editar]

La celda de memoria es la unidad básica de cualquier memoria, capaz de almacenar un Bit en los sistemas digitales. La construcción de la celda define el funcionamiento de la misma, en el caso de la DRAM moderna, consiste en un transistor de efecto de campo y un condensador. El principio de funcionamiento básico, es sencillo: una carga se almacena en el condensador significando un 1 y sin carga un 0. El transistor funciona como un interruptor que conecta y desconecta al condensador. Este mecanismo puede implementarse con dispositivos discretos y de hecho muchas memorias anteriores a la época de los semiconductores, se basaban en arreglos de celdas transistor-condensador.

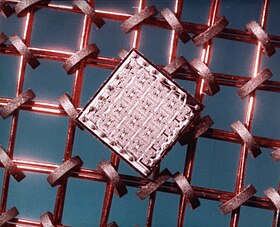

Las celdas en cualquier sistema de memoria, se organizan en la forma de matrices de dos dimensiones, a las cuales se accede por medio de las filas y las columnas. En la DRAM estas estructuras contienen millones de celdas y se fabrican sobre la superficie de la pastilla de silicio formando áreas que son visibles a simple vista. En el ejemplo tenemos un arreglo de 4x4 celdas, en el cual las líneas horizontales conectadas a las compuertas de los transistores son las llamadas filas y las líneas verticales conectadas a los canales de los FET son las columnas.

Para acceder a una posición de memoria se necesita una dirección de 4 bits, pero en las DRAM las direcciones están multiplexadas en tiempo, es decir se envían por mitades. Las entradas marcadas como a0 y a1 son el bus de direcciones y por el mismo entra la dirección de la fila y después la de la columna. Las direcciones se diferencian por medio de señales de sincronización llamadas RAS (del inglés row address strobe) y CAS (column address strobe) que indican la entrada de cada parte de la dirección.[14]

Los pasos principales para una lectura son:

- Las columnas son precargadas a un voltaje igual a la mitad del voltaje de 1 lógico. Esto es posible ya que las líneas se comportan como grandes condensadores, dada su longitud tienen un valor más alto que la de los condensadores en las celdas.

- Una fila es energizada por medio del decodificador de filas que recibe la dirección y la señal de RAS. Esto hace que los transistores conectados a una fila conduzcan y permitiendo la conexión eléctrica entre las líneas de columna y una fila de condensadores. El efecto es el mismo que se produce al conectar dos condensadores, uno cargado y otro de carga desconocida: se produce un balance de que deja a los dos con un voltaje muy similar, compartiendo las cargas. El resultado final depende del valor de carga en el condensador de la celda conectada a cada columna. El cambio es pequeño, ya que la línea de columna es un condensador más grande que el de la celda.

- El cambio es medido y amplificado por una sección que contiene circuitos de realimentación positiva: si el valor a medir es menor que el la mitad del voltaje de 1 lógico, la salida será un 0, si es mayor, la salida se regenera a un 1. Funciona como un redondeo.

- La lectura se realiza en todas las posiciones de una fila de manera que al llegar la segunda parte de la dirección, se decide cual es la celda deseada. Esto sucede con la señal CAS. El dato es entregado al bus de datos por medio de la lineo DO y las celdas involucradas en el proceso son reescritas, ya que la lectura de la DRAM es destructiva.

La escritura en una posición de memoria tiene un proceso similar al de arriba, pero en lugar de leer el valor, la línea de columna es llevada a un valor indicado por la línea DI y el condensador es cargado o descargado. El flujo del dato es mostrado con una línea gruesa en el gráfico.

Diseño de celdas de memoria

[editar]Cada bit de datos en una DRAM se almacena como una carga eléctrica positiva o negativa en una estructura capacitiva. La estructura que proporciona la capacitancia, así como los transistores que controlan el acceso a ella, se denominan colectivamente "celda DRAM". Son el bloque de construcción fundamental en las matrices DRAM. Existen múltiples variantes de celdas de memoria DRAM, pero la variante más utilizada en las DRAM modernas es la celda de un transistor, un capacitor (1T1C). El transistor se utiliza para admitir corriente en el condensador durante las escrituras y para descargar el condensador durante las lecturas. El transistor de acceso está diseñado para maximizar la potencia de la unidad y minimizar las fugas de transistor a transistor (Kenner, pág. 34).

El condensador tiene dos terminales, uno de los cuales está conectado a su transistor de acceso y el otro a tierra o VCC/2. En las DRAM modernas, este último caso es más común, ya que permite un funcionamiento más rápido. En las DRAM modernas, un voltaje de +VCC/2 a través del condensador se requiere almacenar uno lógico; y un voltaje de -VCC/2 a través del condensador se requiere para almacenar un cero lógico. La carga eléctrica almacenada en el condensador se mide en culombio. Para una lógica, el cargo es: , donde Q es la carga en culombios y C es la capacitancia en faradios. Un cero lógico tiene una carga de: .[15]

Leer o escribir una lógica requiere que la línea de palabras se conduzca a un voltaje mayor que la suma de VCC y el voltaje de umbral del transistor de acceso (VTH). Este voltaje se llama VCC bombeado (VCCP). El tiempo requerido para descargar un condensador depende de qué valor lógico se almacena en el condensador. Un condensador que contiene uno lógico comienza a descargarse cuando el voltaje en la terminal de puerta del transistor de acceso está por encima de VCCP. Si el condensador contiene un cero lógico, comienza a descargarse cuando el voltaje del terminal de la puerta está por encima VTH.[16]

Diseño del condensador

[editar]Hasta mediados de la década de 1980, los condensadores de las celdas DRAM eran coplanares con el transistor de acceso (se construían sobre la superficie del sustrato), por lo que se los denominaba condensadores "planares". El impulso para aumentar tanto la densidad como, en menor medida, el rendimiento, requería diseños más densos. Esto estuvo fuertemente motivado por la economía, una consideración importante para los dispositivos DRAM, especialmente las DRAM comerciales. La minimización del área de la celda DRAM puede producir un dispositivo más denso y reducir el costo por bit de almacenamiento. A partir de mediados de la década de 1980, el condensador se movió por encima o por debajo del sustrato de silicio para cumplir con estos objetivos. Las celdas DRAM con condensadores sobre el sustrato se denominan condensadores "apilados" o "de placa plegada". Los que tienen condensadores enterrados debajo de la superficie del sustrato se denominan condensadores de "zanja". En la década de 2000, los fabricantes estaban muy divididos por el tipo de condensador utilizado en sus DRAM y el costo relativo y la escalabilidad a largo plazo de ambos diseños han sido objeto de un extenso debate. La mayoría de las DRAM, de los principales fabricantes como Hynix, Micron Technology, Samsung Electronics utilizan la estructura de condensadores apilados, mientras que los fabricantes más pequeños, como Nanya Technology, utilizan la estructura de condensadores de trinchera o zanja (Jacob, pp. 355–357).

Véase también

[editar]Referencias

[editar]- ↑ «What is DRAM (dynamic random access memory)? - Definition from WhatIs.com». SearchStorage (en inglés).

- ↑ «Are the Major DRAM Suppliers Stunting DRAM Demand?». www.icinsights.com. Archivado desde el original el 16 de abril de 2018. Consultado el 16 de abril de 2018.

- ↑ https://www.research.ibm.com/journal/rd/391/adler.html Archivado el 2 de mayo de 2008 en Wayback Machine. Historia de investigaciones de IBM (en inglés)

- ↑ https://www.freepatentsonline.com/3387286.pdf Patente # 3'387.286 para la memoria DRAM

- ↑ https://www-03.ibm.com/ibm/history/exhibits/mainframe/mainframe_PP2025.html Descripción del equipo System 360 modelo 25 de IBM

- ↑ «IBM Archives: System/370 Model 195». Consultado el 2009.

- ↑ a b The Power of Boldness: "Ten Master Builders of American Industry Tell Their Success Stories" página 82

- ↑ «DRAM - A Personal View». Consultado el 2009.

- ↑ «Museum». Consultado el 2009.

- ↑ «EETimes.com». Consultado el 2009.

- ↑ https://archive.computerhistory.org/resources/text/Oral_History/Proebsting_Robert/102658285.05.01.pdf

- ↑ «Datasheet Archive - MK4096-16 datasheet - MK4096-16 application note - MK4096-16 pdf». Consultado el 2009.

- ↑ «Dynamic RAM Tutorial | DRAM Memory Technology | Radio-Electronics.Com» (en inglés). Consultado el 23 de enero de 2017.

- ↑ «What is the difference between static RAM and dynamic RAM?». HowStuffWorks (en inglés). 24 de agosto de 2000.

- ↑ Keeth et al., 2007, p. 22

- ↑ Keeth et al., 2007, p. 24

Para más información

[editar]- Keeth, Brent; Baker, R. Jacob; Johnson, Brian; Lin, Feng (2007). DRAM Circuit Design: Fundamental and High-Speed Topics. Wiley. ISBN 978-0470184752.

- Jacob, Bruce; Wang, David; Ng, Spencer (2010). Memory Systems: Cache, DRAM, Disk. Morgan Kaufmann. ISBN 978-0-08-055384-9.

Enlaces externos

[editar]- Video de R. Dennard inventor de la DRAM.

- Blout, Elkan (1996). The Power of Boldness: Ten Master Builders of American Industry Tell Their Success Stories. Joseph Henry Press. ISBN 0309054451.

- «Museo de las memorias DRAM». Consultado el 7 de febrero de 2009.

- «Historia de los integrados Intel i1102 y del i1103». Archivado desde el original el 14 de marzo de 2020. Consultado el 7 de febrero de 2009.