# Automated PCB Component Placement using Reinforcement Learning

Luke Vassallo

Supervisor: Dr Josef Bajada

September, 2023

Submitted in partial fulfilment of the requirements for the degree of M.Sc. Artificial Intelligence.

Copyright in text of this thesis rests with the Author. Copies (by any process) either in full, or of extracts may be made only in accordance with regulations held by the Library of the University of Malta. Details may be obtained from the Librarian. This page must form part of any such copies made. Further copies (by any process) made in accordance with such instructions may not be made without the permission (in writing) of the Author.

Ownership of the right over any original intellectual property which may be contained in or derived from this thesis is vested in the University of Malta and may not be made available for use by third parties without the written permission of the University, which will prescribe the terms and conditions of any such agreement.

Copyright ©2023 University of Malta

www.um.edu.mt

Second edition, Thursday 7<sup>th</sup> September, 2023

All the wonders of our universe can in effect be captured by simple rules, yet there can be no way to know all the consequences of these rules, except in effect just to watch and see how they unfold.

(Stephen Wolfram)

## Acknowledgements

I wish to convey my heartfelt appreciation to everyone who contributed to the realisation of this thesis and played a substantial role in shaping this remarkable phase of my journey.

First and foremost, I am immensely grateful to Dr Josef Bajada, my M.Sc. advisor, whose guidance and mentorship have been invaluable to me. He introduced me to reinforcement learning and the world of research, which have profoundly influenced my professional development. His extensive expertise in planning and reinforcement learning, coupled with his exceptional leadership, played a crucial role in delivering the contributions of this work. I could not have asked for a better mentor to assist me.

I would like to thank Dr Vincent Vella, Dr Jean Paul Ebejer and Prof. Luca locchi for examining my thesis and Prof. Matthew Montebello for chairing the process. Their insightful questions and detailed comments have significantly improved the quality of this thesis.

Next, I would like to thank Marja for her boundless patience, unwavering encouragement and dedication. I would also like to extend my thanks to my parents, Emanuel and Ruth, my brother Darren and uncle Geoffrey, for encouraging me to follow my passions and supporting me in pursuit of my goals with their unconditional love.

Lastly, I want to thank everyone else who shared an ear or provided an opinion, whether directly or indirectly related to this thesis. These conversations have been a source of inspiration, and some of their ideas live through this work.

I am grateful to the Malta Digital Innovation Authority (MDIA) for their support through the Pathfinder scholarship.

## Abstract

Component placement is the first step of Printed Circuit Board (PCB) physical design and demands considerable time and domain expertise. Placement quality impacts the performance of subsequent tasks, and the generation of an optimal placement is known to be, at the very least, NP-Complete. While stochastic optimisation and analytic techniques have had some success, they often lack the intuitive understanding of human engineers. Consequently, automation tools have not gained acceptance among hardware engineers, resulting in predominantly manual PCB physical design. Moreover, limited literature on this topic is available, with a particular focus on placement co-optimisation for niche applications. We aim to challenge this prevailing approach and propose a general placement methodology that integrates an AI-assisted workflow, shifting the designer's focus towards higher-level problem-oriented tasks.

This thesis investigates state-of-the-art AI constructive placement methodology and, based on its shortcomings, proposes a novel Markov Decision Process (MDP) formulation for iterative placement. We study the fundamental mechanisms in a constrained single-component setup using advanced policy optimisation and actor-critic Reinforcement Learning (RL) algorithms. Furthermore, we evaluate the feasibility of encouraging the agent to learn by emulating the design style of experts or by acting as an expert itself in an iterative self-improvement scenario. Based on the key findings, we adapt it to a multi-component setup and learn general policies for optimising the placement of components on unseen PCBs. Our research suggests that an adaptive reward signal removes the need for expert knowledge, and the multi-component environment yields diverse training datasets sufficient for learning general policies from a handful of circuits. Our methodology is evaluated on unseen circuits alongside simulated annealing, an effective methodology for optimising the placement of circuit components on a PCB. TD3 and SAC, on average yield 17% and 21% lower post-routing wirelength. Qualitative analysis shows that the policies learn fundamental placement techniques. Collectively, they demonstrate emergent collaborative and competitive behaviours between components and faster placement convergence over an order of magnitude. The methodologies have been open sourced and are available on GitHub https://github.com/lukevassallo/rl\_pcb.git

# Contents

| Lis | st of F | Figures                           | xi   |

|-----|---------|-----------------------------------|------|

| Lis | st of 1 | <b>Fables</b>                     | xiv  |

| Lis | stings  | ;                                 | xvi  |

| Lis | st of A | Abbreviations                     | xvii |

| 1   | Intro   | oduction                          | 1    |

|     | 1.1     | Motivation                        | 1    |

|     | 1.2     | Aims and Objectives               | 3    |

|     | 1.3     | Proposed Solution                 | 3    |

|     | 1.4     | Document Structure                | 4    |

| 2   | Bac     | kground                           | 5    |

|     | 2.1     | Electronic Design Automation      | 5    |

|     | 2.2     | IC Design Process                 | 6    |

|     |         | 2.2.1 Design Flow                 | 7    |

|     | 2.3     | PCB Design Process                | 9    |

|     |         | 2.3.1 Components                  | 9    |

|     |         | 2.3.2 PCB Structure               | 10   |

|     |         | 2.3.3 Design Flow                 | 11   |

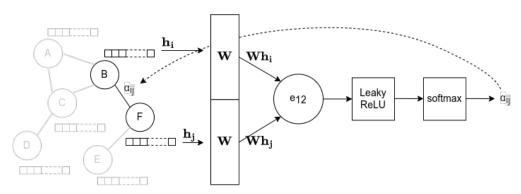

|     | 2.4     | Graph Neural Networks             | 13   |

|     |         | 2.4.1 Graph Neural Networks       | 13   |

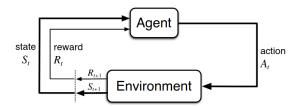

|     | 2.5     | Reinforcement Learning            | 16   |

|     |         | 2.5.1 Basics                      | 16   |

|     |         | 2.5.2 The Bellman Equation        | 18   |

|     |         | 2.5.3 Fundamentals RL Algorithms  |      |

|     |         | 2.5.4 Deep Reinforcement Learning |      |

|   |       | 2.5.5    | Actor-Critic                                         |

|---|-------|----------|------------------------------------------------------|

| 3 | Liter | ature R  | zeview 23                                            |

|   | 3.1   | PCB P    | lacement                                             |

|   |       | 3.1.1    | General Placement                                    |

|   |       | 3.1.2    | Thermal-Aware PCB Placement                          |

|   |       | 3.1.3    | PCB Placement for Power Modules                      |

|   | 3.2   | Layout   | Techniques in IC Physical Design                     |

|   |       | 3.2.1    | Black Box Optimisation                               |

|   |       | 3.2.2    | Analytic Placers                                     |

|   | 3.3   | Machi    | ne Learning                                          |

|   |       | 3.3.1    | Performance Prediction                               |

|   |       | 3.3.2    | Learning Based Placers                               |

|   | 3.4   | Key Fi   | ndings from Prior Work                               |

| 4 | Mat   | erials & | Methods 39                                           |

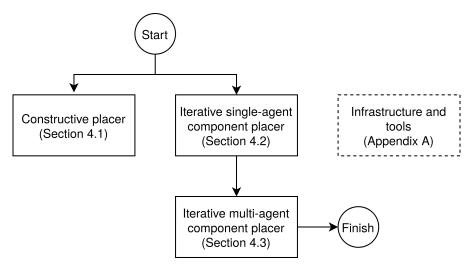

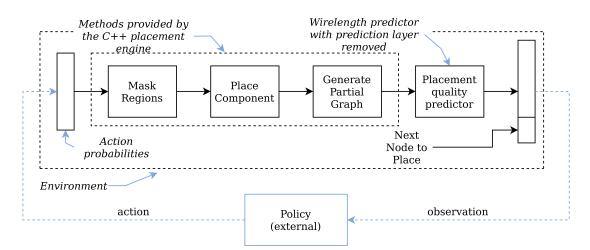

|   | 4.1   | Constr   | ructive Placer                                       |

|   |       | 4.1.1    | Gym Environment                                      |

|   |       | 4.1.2    | Placement Engine                                     |

|   |       | 4.1.3    | Dataset                                              |

|   |       | 4.1.4    | Wirelength Prediction                                |

|   |       | 4.1.5    | Training and Experimental Setup                      |

|   |       | 4.1.6    | Evaluation                                           |

|   | 4.2   | Single   | Component Iterative Placer                           |

|   |       | 4.2.1    | Iterative PCB Component Placement as an MDP 53       |

|   |       | 4.2.2    | Gym Environment                                      |

|   |       | 4.2.3    | Observation Space                                    |

|   |       | 4.2.4    | Action Space                                         |

|   |       | 4.2.5    | Reward Signal                                        |

|   |       | 4.2.6    | Dataset                                              |

|   |       | 4.2.7    | Training                                             |

|   |       | 4.2.8    | Experimental Setup                                   |

|   |       | 4.2.9    | Evaluation                                           |

|   | 4.3   | Multi-   | Component Iterative Placer                           |

|   |       | 4.3.1    | Environment                                          |

|   |       | 4.3.2    | Computing Observations in a Multi-Component Setup 73 |

|   |       | 4.3.3    | Episodic Flow                                        |

|   |      | 4.3.4    | Dataset                                                               | . 76  |

|---|------|----------|-----------------------------------------------------------------------|-------|

|   |      | 4.3.5    | Training                                                              | . 76  |

|   |      | 4.3.6    | Experimental Setup                                                    | . 77  |

|   |      | 4.3.7    | Evaluation                                                            | . 78  |

| 5 | Resu | ults & D | Discussion                                                            | 79    |

|   | 5.1  | Const    | ructive Placer                                                        | . 79  |

|   |      | 5.1.1    | Wirelength Prediction                                                 | . 80  |

|   |      | 5.1.2    | Constructive Placement                                                | . 82  |

|   |      | 5.1.3    | Key Conclusions for Constructive Placement                            | . 85  |

|   | 5.2  | Single   | -Component Iterative Placement                                        | . 86  |

|   |      | 5.2.1    | Experiments with a Discrete Action Space and $R_1$                    | . 87  |

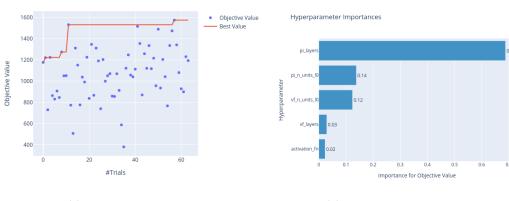

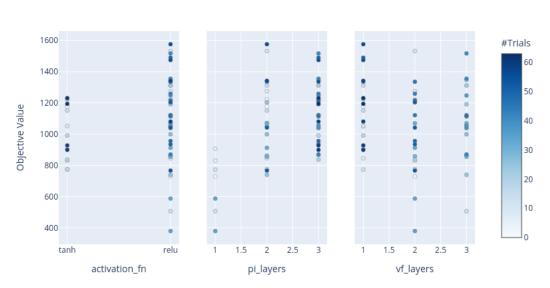

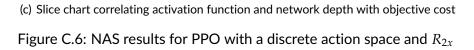

|   |      | 5.2.2    | Experiments with a Discrete Action Space and $R_{2x}$ $\ .$           | . 90  |

|   |      | 5.2.3    | Experiments with a Continuous Action Space and $R_{2x} \ \ . \ . \ .$ | . 95  |

|   |      | 5.2.4    | Action Space Comparison on $R_{2x}$                                   | . 100 |

|   |      | 5.2.5    | Experiments with a Continuous Action Space and $R_3\ .\ .\ .\ .$      | . 100 |

|   |      | 5.2.6    | Key Conclusions for Single-Component Iterative Placement              | . 105 |

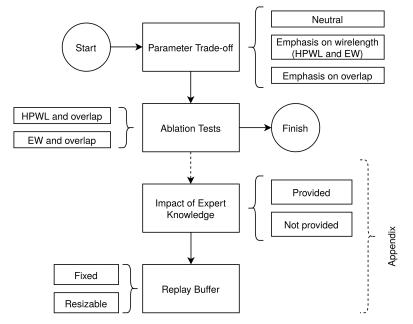

|   | 5.3  | Multi-   | Component Iterative Placement                                         | . 107 |

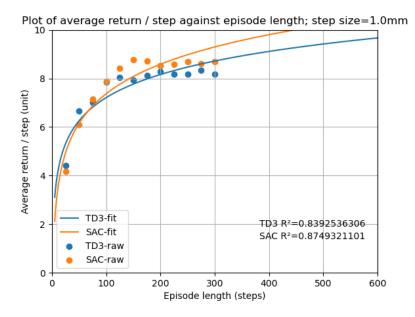

|   |      | 5.3.1    | Reward Function Parameter Trade-off Experiments                       | . 108 |

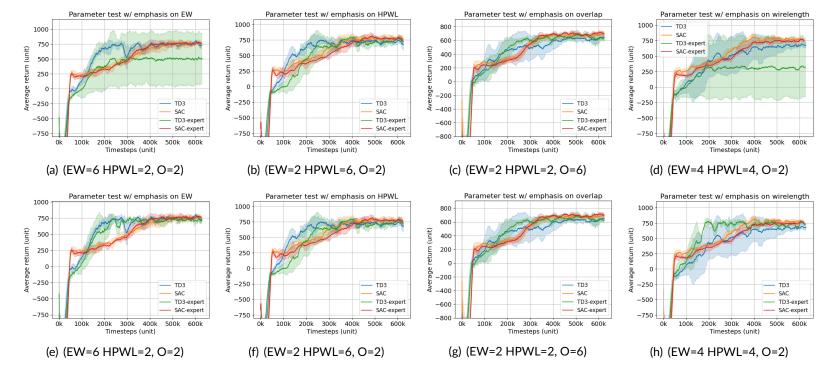

|   |      | 5.3.2    | Ablation Experiments                                                  | . 110 |

|   |      | 5.3.3    | Qualitative Policy Analysis                                           | . 112 |

|   |      | 5.3.4    | Key Conclusions for Multi-Component Iterative Placement               | . 117 |

|   | 5.4  | Summ     | ary                                                                   | . 118 |

| 6 | Con  | clusion  | S                                                                     | 119   |

|   | 6.1  | Revisi   | ting the Aims and Objectives                                          | . 119 |

|   |      | 6.1.1    | Constructive Placer                                                   | . 119 |

|   |      | 6.1.2    | Formulating the PCB Component Problem as an RL task $\ldots$ .        | . 120 |

|   |      | 6.1.3    | Design and Testing of a Single-Component PCB Placer                   | . 120 |

|   |      | 6.1.4    | Multi-Component RL Capable of Generalised PCB Placement               | . 121 |

|   | 6.2  | Limita   | tions                                                                 | . 121 |

|   |      | 6.2.1    | Limitations of Constructive Placement                                 | . 122 |

|   |      | 6.2.2    | Evaluation in terms of Post-Routing Wirelength                        | . 122 |

|   |      | 6.2.3    | Sub-Optimal Weighting of Adaptive Reward Parameters                   | . 122 |

|   | 6.3  | Future   | e Work                                                                | . 123 |

|   |      | 6.3.1    | Expand the Multi-Component Setup                                      | . 123 |

|   |      | 6.3.2    | Investigate the Offline Reinforcement Learning                        | . 124 |

|         | 6.3.3 Improve Feature Extraction and Move Beyond Wirelength |     |

|---------|-------------------------------------------------------------|-----|

|         | 6.3.4 Improve Policy Performance                            | 125 |

| Referer | nces                                                        | 126 |

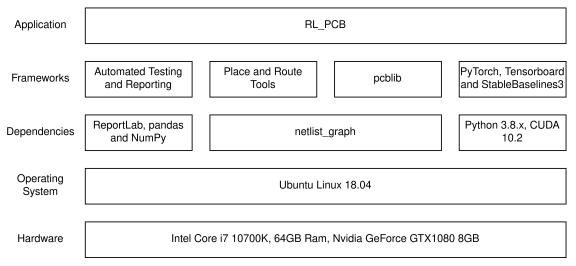

| Append  | lix A Infrastructure and tools                              | 136 |

| A.1     | KiCAD PCB Design Software Suite                             | 137 |

| A.2     | PCB Place and Route Tools                                   | 137 |

| A.3     | Netlist Graph                                               | 139 |

| A.4     | Internal Representation                                     | 139 |

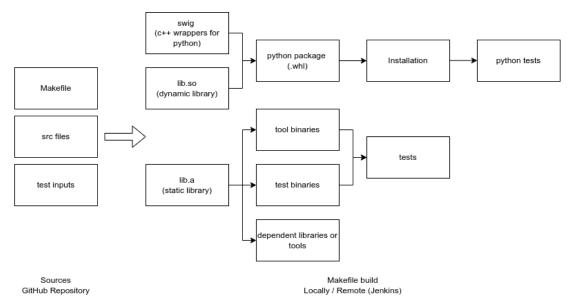

| A.5     | Automated Builds                                            | 142 |

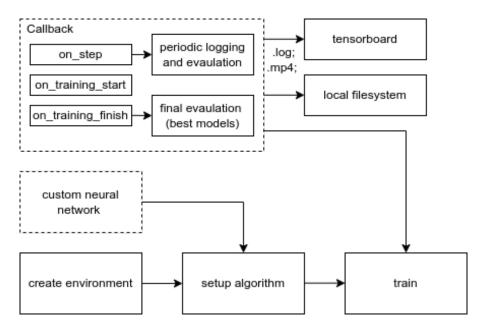

| A.6     | RL Framework                                                | 143 |

| A.7     | Reproducibility of Results                                  | 144 |

| Append  | lix B Datasets                                              | 145 |

| B.1     | Constructive Placement Dataset                              | 146 |

| B.2     | Single-Component Iterative Placement Dataset                | 147 |

| B.3     | Multi-Component Iterative Placement Dataset                 | 149 |

| Append  | lix C Supplementary Experiments                             | 150 |

| C.1     | Expectations from Single-Component Iterative Placement      | 151 |

| C.2     | Single-Component Placement with Discrete Actions            | 151 |

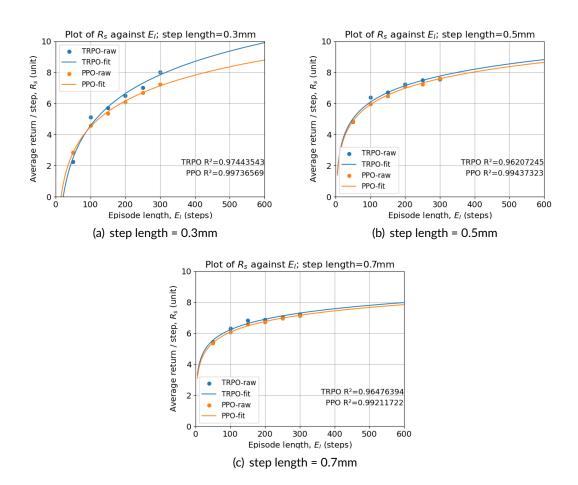

|         | C.2.1 Quantitative Analysis of Episode and Step Length      | 151 |

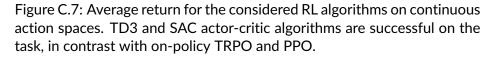

| C.3     | Single-Component Placement with Continuous Actions          | 158 |

|         | C.3.1 Preliminary Experiments                               | 158 |

|         | C.3.2 Quantitative Analysis of Episode Length               | 159 |

| C.4     | Multi-Component Iterative Placement                         | 160 |

|         | C.4.1 Impact of Expert Knowledge on Learning Performance    | 160 |

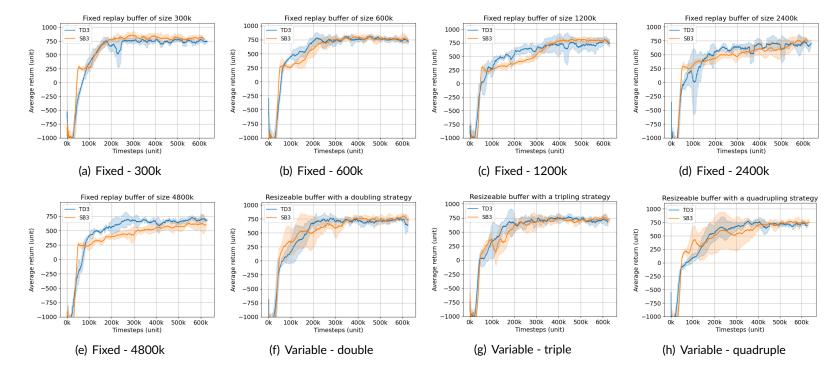

|         | C.4.2 Impact of Replay Buffer on Adaptive Reward Learning   | 163 |

| Append  | lix D Additional Background                                 | 167 |

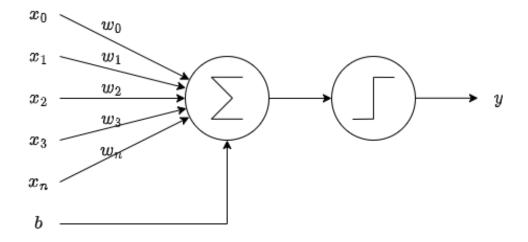

| D.1     | Artificial Neural Networks                                  | 167 |

|         | D.1.1 Perceptron Model                                      | 167 |

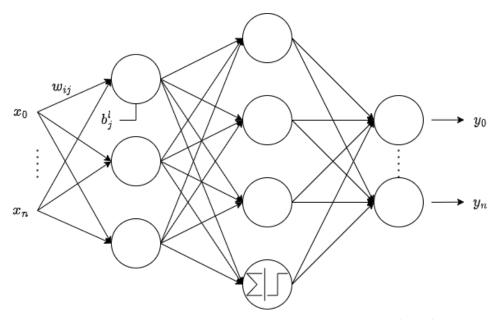

|         | D.1.2 Multi-Layer Perceptrons                               | 168 |

|         | D.1.3 Neural Network Training                               | 169 |

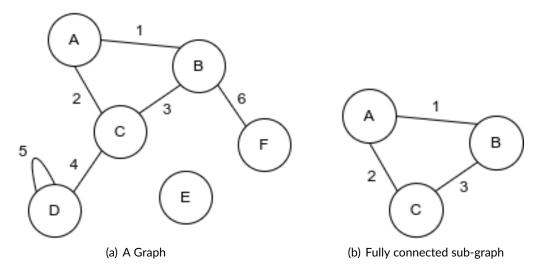

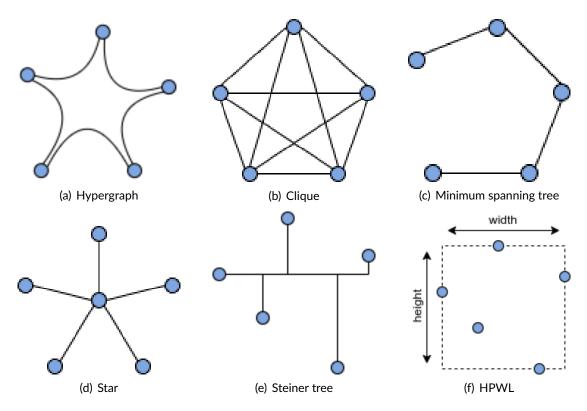

| D.2     | Graph Theory                                                | 170 |

|         | D.2.1 Mathematical Representation                           | 171 |

| D.3     | Net Models                                                  | 172 |

|        | D.3.1 Differentiable Net Models          | . 172 |

|--------|------------------------------------------|-------|

| Append | lix E Machine Information and Statistics | 175   |

| E.1    | Machine Information                      | . 175 |

| E.2    | Experiment Runtimes                      | . 175 |

# **List of Figures**

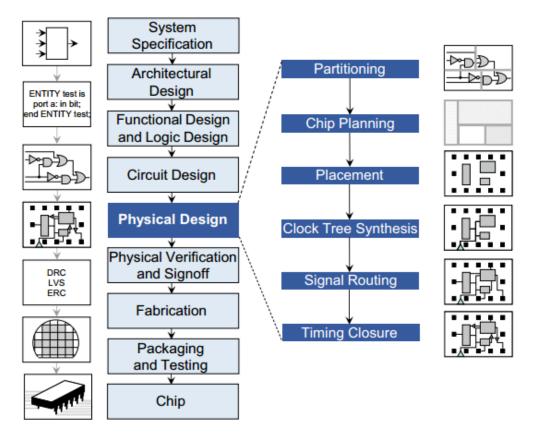

| 2.1  | Key steps in VLSI circuit design flow with an emphasis on physical design    | 6  |

|------|------------------------------------------------------------------------------|----|

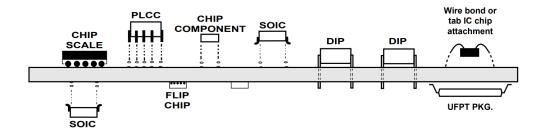

| 2.2  | Comparison of through-hole and surface mount package technologies            | 10 |

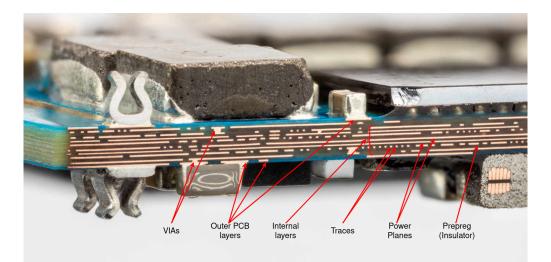

| 2.3  | Cross-section of a Printed Circuit Board (PCB)                               | 11 |

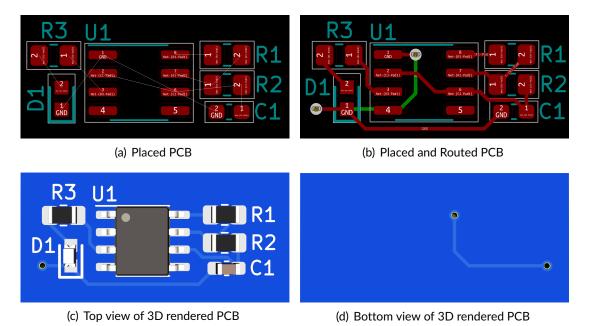

| 2.4  | Illustration of placed and routed PCBs in KiCad                              | 12 |

| 2.5  | Layer architecture of a GAT neural network                                   | 15 |

| 2.6  | Agent-environment interaction in Reinforcement Learning (RL)                 | 17 |

| 3.1  | Evolution of IC placement tools                                              | 27 |

| 4.1  | Methodology chapter flow                                                     | 39 |

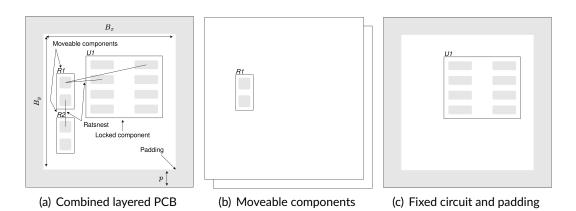

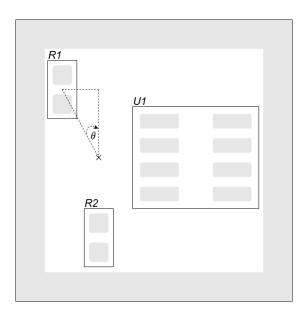

| 4.2  | Constructive PCB placement environment                                       | 41 |

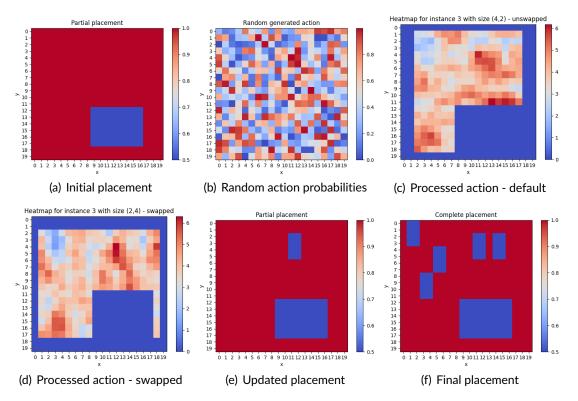

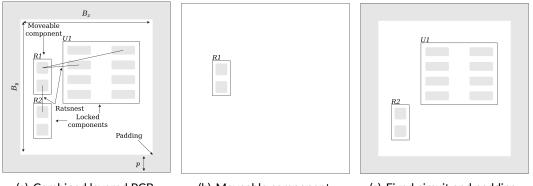

| 4.3  | Key depictions of the constructive placement process                         | 44 |

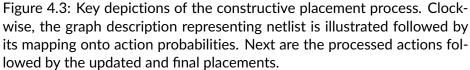

| 4.4  | Dataset generation strategy for wirelength prediction                        | 47 |

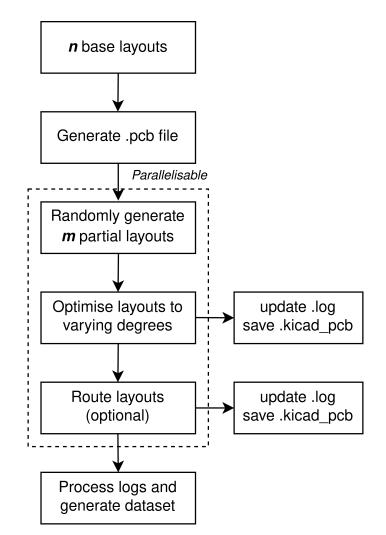

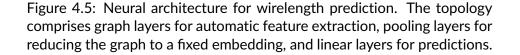

| 4.5  | Neural architecture for wirelength prediction                                | 48 |

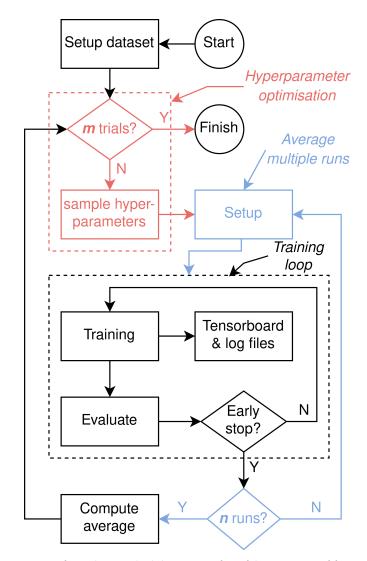

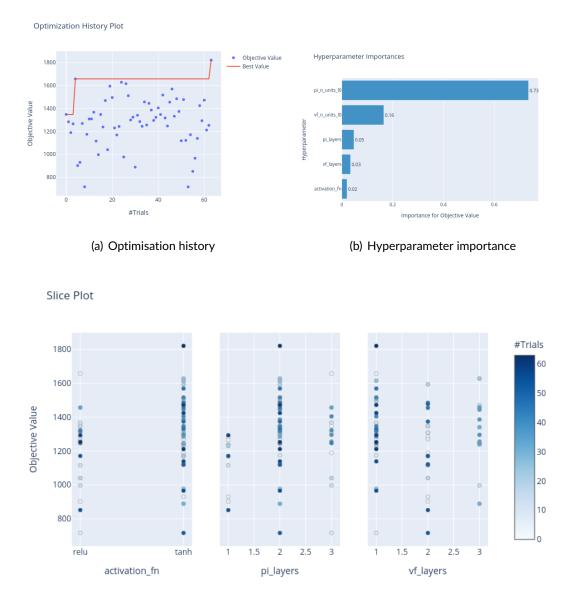

| 4.6  | Procedure for optimising neural architecture and hyperparameters             | 50 |

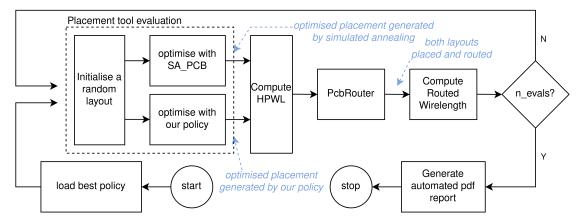

| 4.7  | Procedure for evaluating RL policies against SA                              | 52 |

| 4.8  | PCB representation as a stack of images for single-component placement       | 56 |

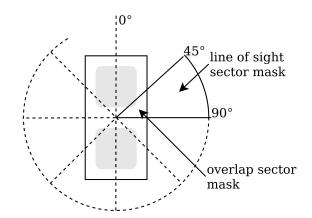

| 4.9  | Overlap and line-of-sight masks derived from circle segments                 | 57 |

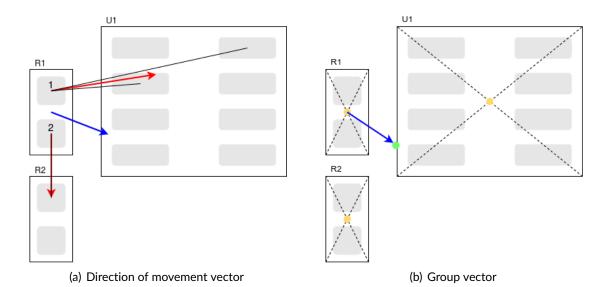

| 4.10 | Extraction of directional information from the circuit netlist               | 58 |

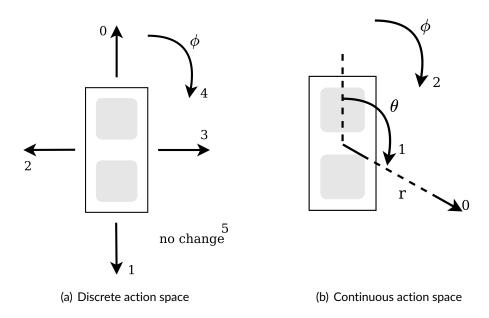

|      | Discrete and continuous action spaces                                        |    |

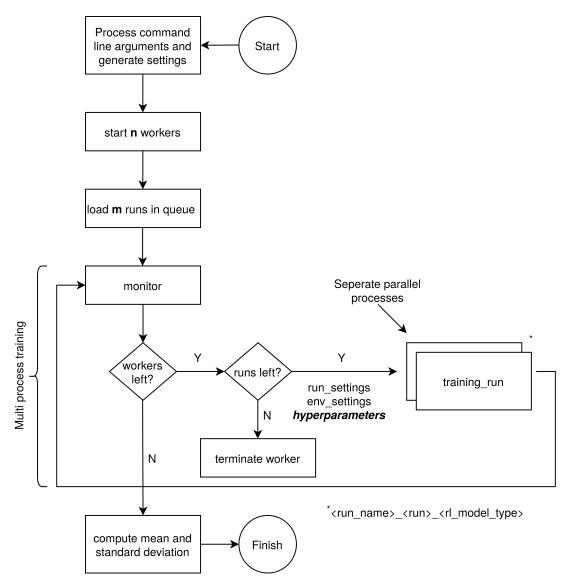

|      | Flowchart illustrating parallelised training procedure                       |    |

| 4.13 | PCB representation as a stack of images for multi-component placement        | 74 |

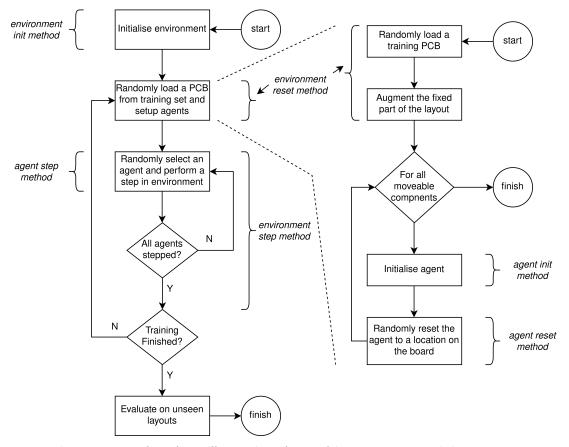

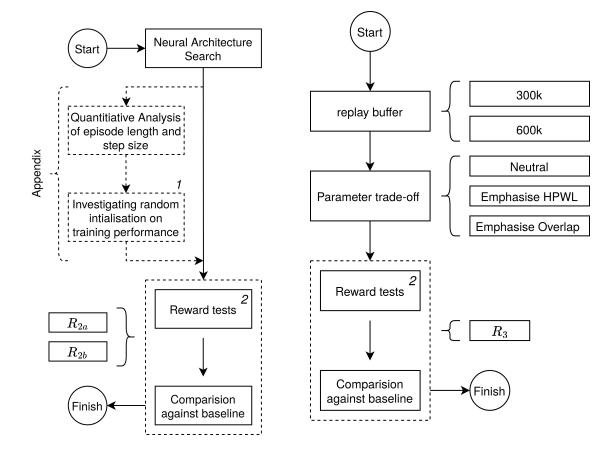

| 4.14 | Flowchart illustrating the multi-component training procedure                | 75 |

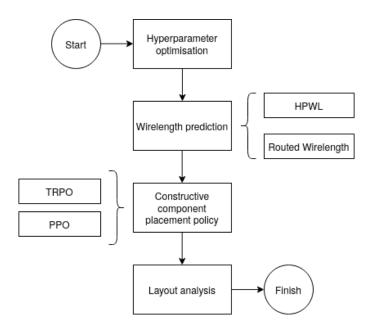

| 5.1  | Experimental flow for constructive placement methodology                     | 79 |

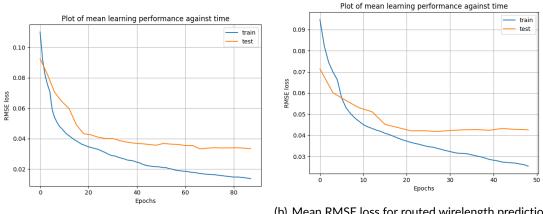

| 5.2  | Training performance for the wirelength predication task                     | 81 |

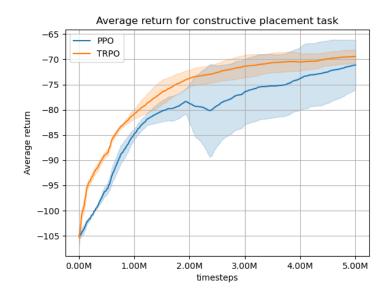

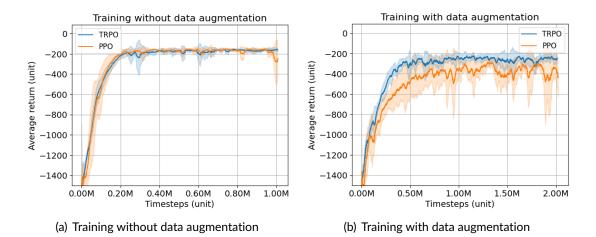

| 5.3  | Plot of average return for constructive placement training                   | 83 |

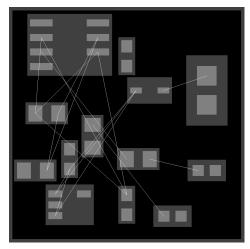

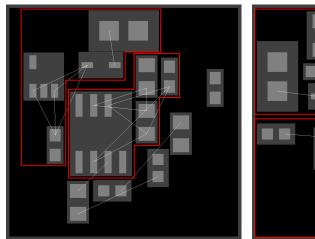

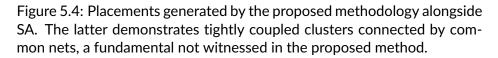

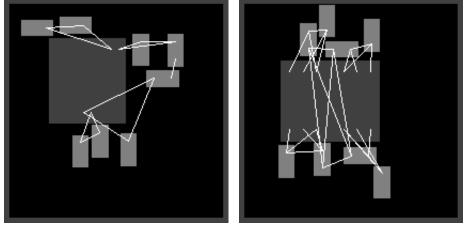

| 5.4  | Placements generated by the proposed constructive methodology alongside $SA$ | 84 |

| 5.5  | Experimental flow for iterative single-component methodology                 | 87 |

| 5.6  | Average return for training on layout $D_{1a}$ guided by reward $R_1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

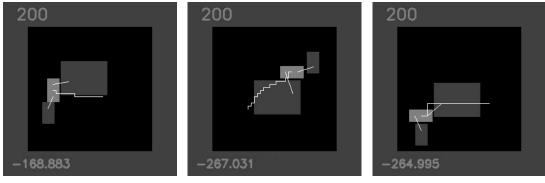

| 5.7  | Distinct terminal states demonstrating learned behaviours under reward $R_1$ 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

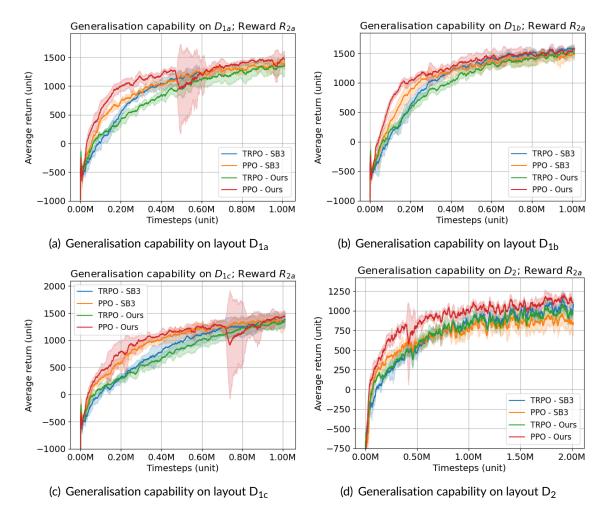

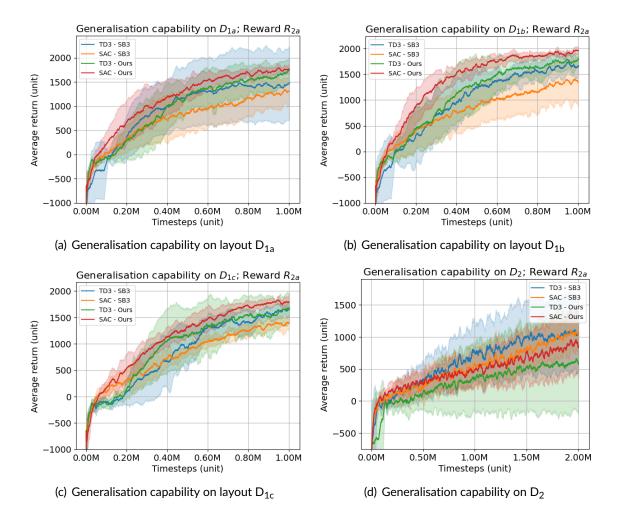

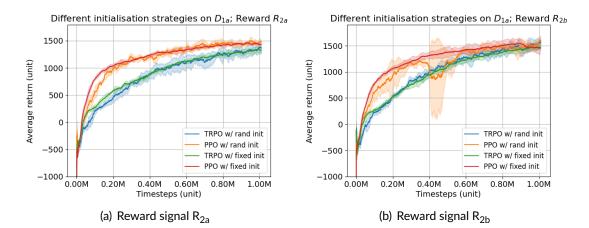

| 5.8  | Generalisation capability with $R_{2a}$ and a discrete action space $\ \ldots \ \ldots \ 91$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

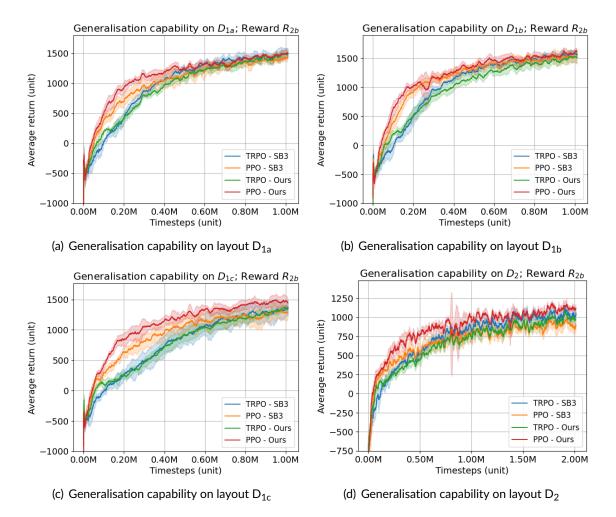

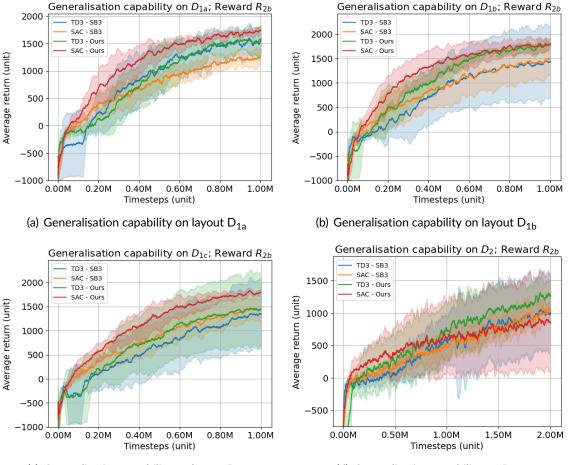

| 5.9  | Generalisation capability with $R_{2b}$ and a discrete action space $\hdots \ldots \hdots \hdots\$ |

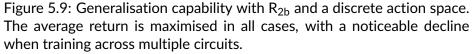

| 5.10 | Distinct terminal states demonstrating policies with discrete action spaces 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.11 | Generalisation capability with $R_{2a}$ and a continuous action space $\ldots \ldots$ 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.12 | Generalisation capability with $R_{2b}$ and a continuous action space $\ldots \ldots $ 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.13 | Distinct terminal states illustrating policies with continuous action spaces 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

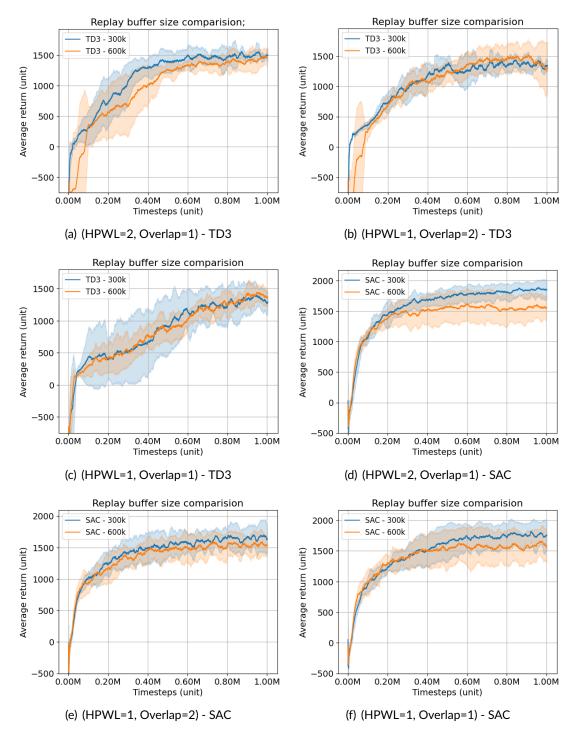

| 5.14 | Average return for variations of $R_3$ and replay buffer sizes $\ldots \ldots \ldots \ldots \ldots 102$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

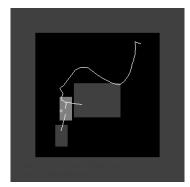

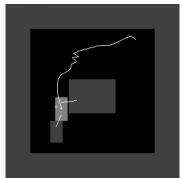

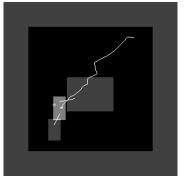

| 5.15 | Illustration of policy behaviour on different configurations of reward signal $R_3$ . 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

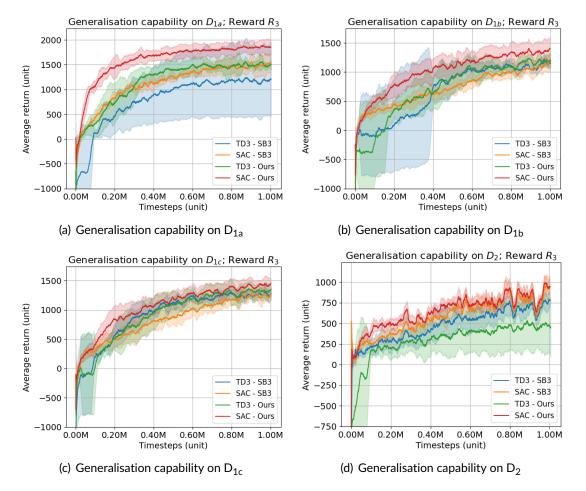

| 5.16 | Generalisation capability with $R_3$ and a small replay buffer $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.17 | Experimental flow for iterative multi-component methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

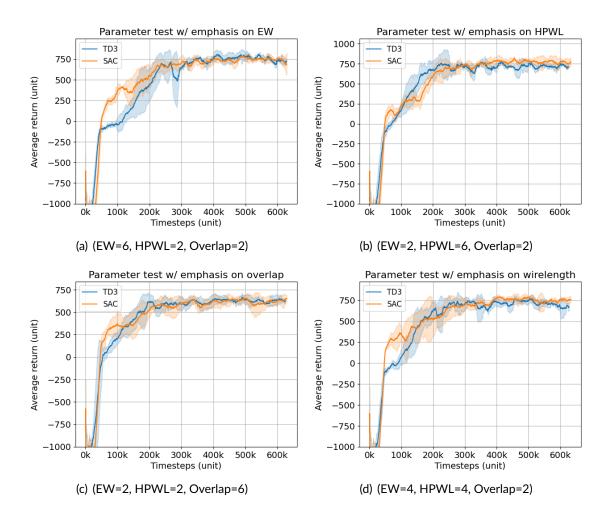

| 5.18 | Average return for multi-component parameter trade-off experiments 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

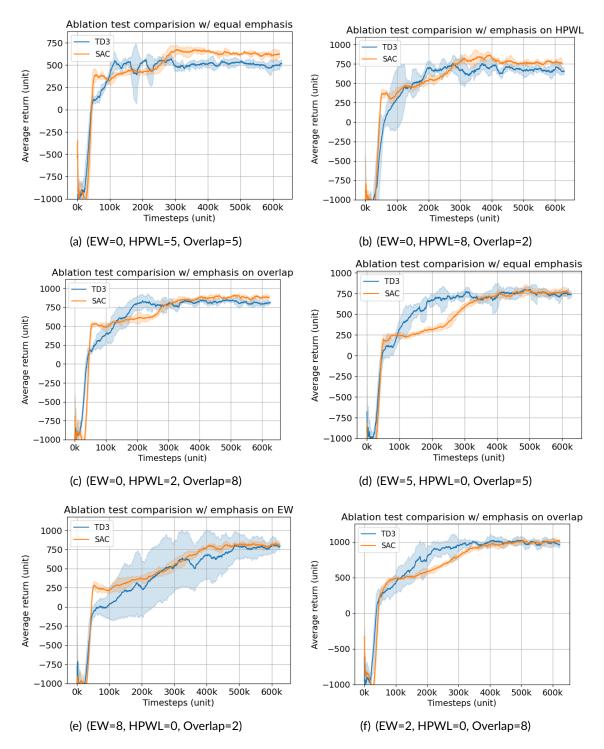

| 5.19 | Average return for multi-component ablation experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

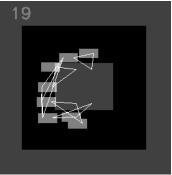

| 5.20 | Circuit placements optimised with SA-PCB for 600 steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

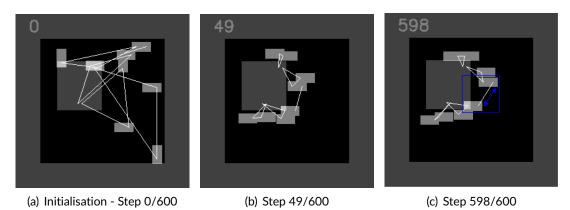

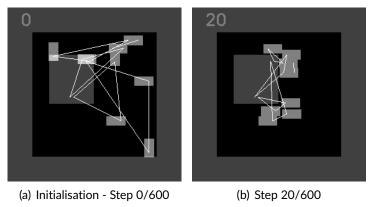

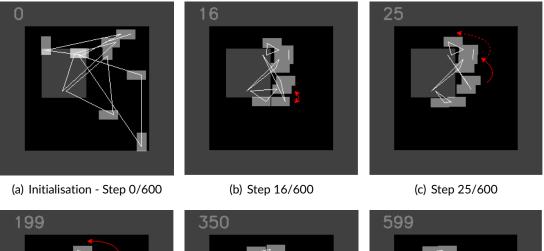

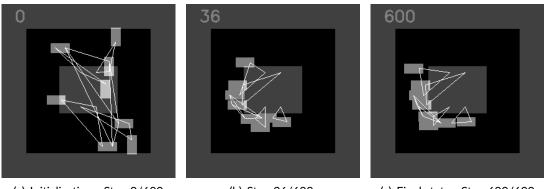

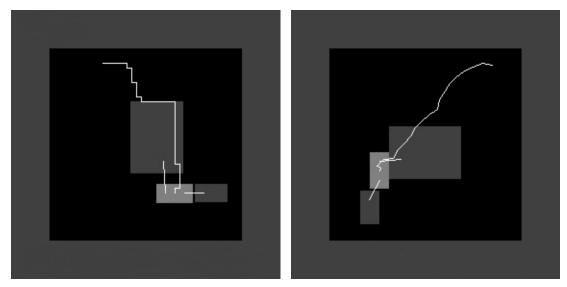

| 5.21 | . Key states in optimising $M_{U0}$ with policy (EW=8, Overlap=2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

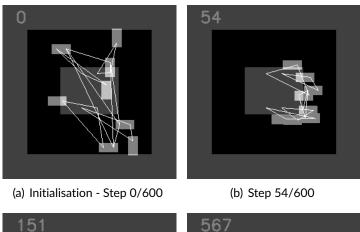

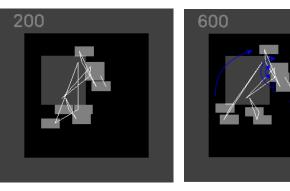

| 5.22 | Key states in optimising $M_{U2}$ with policy (EW=8, Overlap=2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

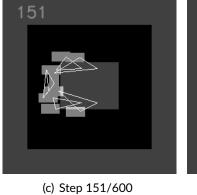

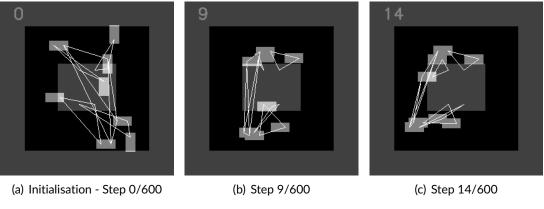

| 5.23 | Key states in placing $M_{U0}$ with policy (HPWL=5, Overlap=5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.24 | Key states in placing $M_{U2}$ with policy (HPWL=5, Overlap=5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.25 | Key states in placing $M_{U0}$ with policy (HPWL=8, Overlap=2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.26 | Key states in placing $M_{U2}$ with policy (HPWL=8, Overlap=2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ۸ 1  | Technology Stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A.1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A.2  | Illustration of the automated build and test processes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A.3  | Depiction of the RL training framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

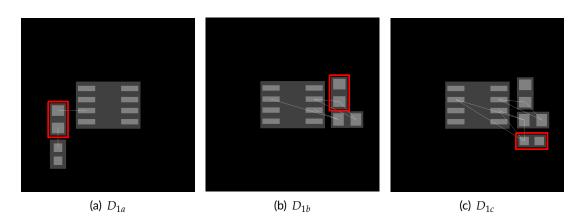

| B.1  | Constituents of the single-component dataset, $D_1 \ldots \ldots \ldots \ldots \ldots \ldots 148$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

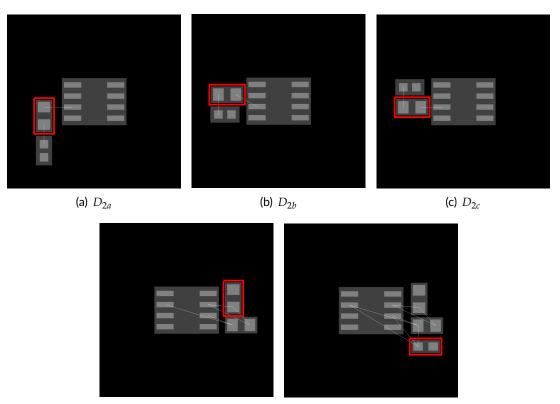

| B.2  | Constituents of the multi-component dataset, $D_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ~ .  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |