# Radiation-Tolerant 10x SpaceWire Router Radiation Tolerant 6x SpaceWire Router with PCI RT-SPW-ROUTER

**Data Sheet and User's Manual**

#### **Features**

- SpaceWire Router compliant with ECSS-E-ST-50-12C

- Non-blocking switch-matrix connecting any input to any output

- Packet Distribution

- Group Adaptive Routing

- Path, Logical and Regional Logical addressing

- Two priority levels for output port arbitration

- Configuration port using RMAP, compliant with ECSS-E-ST-50-52C

- 8x SpaceWire ports, full duplex, on-chip or offchip LVDS transceivers

- 2x external FIFO ports, 9-bit wide data paths

- Possible to cascade two routers without glue logic via the FIFO ports

- 2x internal AMBA ports with DMA and RMAP

- PCI Initiator/Target interface, 32-bit, 33 MHz

- System-time distribution via all ports

- Timers on all ports to prevent deadlock

- Fault-tolerant design

# **Description**

The Radiation-Tolerant SpaceWire Router family is available as standard components using the Actel RTAX and RT ProASIC3 FPGAs. The fault tolerant design of the router in combination with the radiation tolerant FPGA makes it ideally suited for space and other high-rel applications.

# **Specification**

- CCGA484, CQFP352, CCGA624

- Total Ionizing Dose (TID) to 300 krad (Si, functional)

- Single-Event Latch-Up Immunity (SEL) to LET<sub>TH</sub> > 117 MeV-cm<sup>2</sup>/mg

- Immune to Single-Event Upsets (SEU) to LET<sub>TH</sub> > 37 MeV-cm<sup>2</sup>/mg

- 1.2-1.5V, 2.5V & 3.3V supply, 500 mW consumption (TBD)

- Up to 200 MBPS on SpaceWire links

# **Applications**

The router implements a routing switch as defined in the ECSS-E-ST-50-12C SpaceWire links, nodes, routers and networks standard, supporting all mandatory and optional features.

The router implements up to ten external routing ports and the mandatory configuration port.

The configuration port provides access to configuration and status registers, and the routing table using the Remote Memory Access Protocol (RMAP) as defined in the ECSS-E-ST-50-52C protocol standard.

The router also fully supports the ECSS-E-ST-50-51C SpaceWire protocol identification standard.

An optional PCI Initiator/Target interface is available.

# **Table of contents**

| 1 | Intro | Introduction5  |                               |    |  |  |  |  |

|---|-------|----------------|-------------------------------|----|--|--|--|--|

|   | 1.1   | Overvie        | ew                            | 5  |  |  |  |  |

|   | 1.2   | Standar        | d configurations              | 5  |  |  |  |  |

|   | 1.3   | Signal o       | overview                      | 6  |  |  |  |  |

| 2 | Arch  | itecture       |                               | 7  |  |  |  |  |

|   | 2.1   | Cores          |                               | 7  |  |  |  |  |

|   | 2.2   | Interrur       | ots                           |    |  |  |  |  |

|   | 2.3   |                | y map                         |    |  |  |  |  |

|   | 2.4   | •              | play information              |    |  |  |  |  |

|   | 2.5   | Ü              | cations                       |    |  |  |  |  |

|   | 2.6   | •              |                               |    |  |  |  |  |

| 3 | Spac  | Č              | uter                          |    |  |  |  |  |

| 3 | 3.1   |                |                               |    |  |  |  |  |

|   |       |                | Overview                      |    |  |  |  |  |

|   | 3.2   | 3.2.1          | Port numbering                |    |  |  |  |  |

|   |       | 3.2.1          | Routing table                 |    |  |  |  |  |

|   |       | 3.2.3          | Output port arbitration       |    |  |  |  |  |

|   |       | 3.2.4          | Group adaptive routing        |    |  |  |  |  |

|   |       | 3.2.5          | Packet distribution           |    |  |  |  |  |

|   |       | 3.2.6          | Port disable                  | 14 |  |  |  |  |

|   |       | 3.2.7          | Timers                        | 14 |  |  |  |  |

|   |       | 3.2.8          | On-chip memories              |    |  |  |  |  |

|   |       | 3.2.9          | System time-distribution      |    |  |  |  |  |

|   |       | 3.2.10         | Invalid address error         |    |  |  |  |  |

|   | 2.2   | 3.2.11         | Global configuration features |    |  |  |  |  |

|   | 3.3   | _              | Vire ports                    |    |  |  |  |  |

|   | 3.4   | FIFO ports     |                               |    |  |  |  |  |

|   |       | 3.4.1          | Transmitter                   |    |  |  |  |  |

|   |       | 3.4.2          | Receiver                      |    |  |  |  |  |

|   |       | 3.4.3<br>3.4.4 | Time-code transmit            |    |  |  |  |  |

|   |       | 3.4.4          | Time-code receive             |    |  |  |  |  |

|   | 3.5   |                | ports                         |    |  |  |  |  |

|   | 3.3   |                | Overview                      | 21 |  |  |  |  |

|   |       | 3.5.2          | Operation                     |    |  |  |  |  |

|   |       | 3.5.3          | Receiver DMA channels         |    |  |  |  |  |

|   |       | 3.5.4          | Transmitter DMA channels      |    |  |  |  |  |

|   |       | 3.5.5          | RMAP target                   | 32 |  |  |  |  |

|   |       | 3.5.6          | AMBA interface                |    |  |  |  |  |

|   |       | 3.5.7          | Registers                     | 37 |  |  |  |  |

|   | 3.6   | Configu        | ıration port                  |    |  |  |  |  |

|   |       | 3.6.1          | AMBA AHB slave interface      |    |  |  |  |  |

|   |       | 3.6.2          | Write commands                |    |  |  |  |  |

|   |       | 3.6.3          | Read commands                 |    |  |  |  |  |

|   |       | 3.6.4          | RMW commands                  |    |  |  |  |  |

|   | 3.7   | _              | rs                            |    |  |  |  |  |

|   |       | 3.7.1          | Reset value definitions       |    |  |  |  |  |

|   |       | 3.7.2          | Register type definitions     | 48 |  |  |  |  |

|   | 3.8   | Signal definitions and reset values                      |    |  |  |  |  |

|---|-------|----------------------------------------------------------|----|--|--|--|--|

|   | 3.9   |                                                          |    |  |  |  |  |

| 4 | -     | eWire encoder-decoder                                    |    |  |  |  |  |

|   | 4.1   | Overview                                                 |    |  |  |  |  |

|   | 4.2   | Operation                                                |    |  |  |  |  |

|   |       | 4.2.1 Overview                                           |    |  |  |  |  |

|   |       | 4.2.3 Transmitter                                        |    |  |  |  |  |

|   |       | 4.2.4 Receiver                                           |    |  |  |  |  |

|   |       | 4.2.5 Time interface                                     | 62 |  |  |  |  |

|   | 4.3   | Receiver interface                                       | 63 |  |  |  |  |

|   |       | 4.3.1 Link errors                                        |    |  |  |  |  |

|   | 4.4   | Transmitter interface                                    |    |  |  |  |  |

|   |       | 4.4.1 Link errors                                        |    |  |  |  |  |

|   | 4.5   | Registers                                                |    |  |  |  |  |

| 5 | PCI : | Initiator/Target                                         | 65 |  |  |  |  |

|   | 5.1   | Overview                                                 |    |  |  |  |  |

|   | 5.2   | Operation                                                |    |  |  |  |  |

|   |       | 5.2.1 PCI Initiator                                      |    |  |  |  |  |

|   |       | 5.2.2 PCI Target                                         |    |  |  |  |  |

|   |       | 5.2.3 Configuration                                      |    |  |  |  |  |

|   |       | 5.2.5 Error response                                     |    |  |  |  |  |

|   |       | 5.2.6 Interrupt controller (generation of PCI interrupt) |    |  |  |  |  |

|   | 5.3   | Registers                                                |    |  |  |  |  |

|   | 5.4   | Signal definitions and reset values                      |    |  |  |  |  |

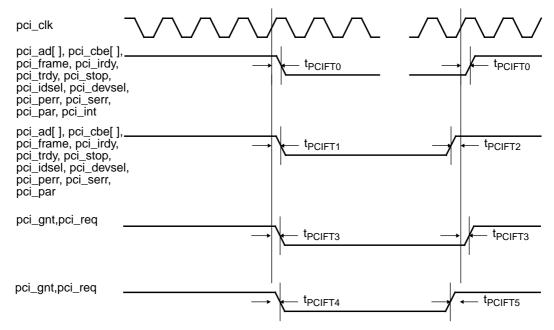

|   | 5.5   | Timing                                                   | 72 |  |  |  |  |

| 6 | Statu | ıs Registers                                             | 73 |  |  |  |  |

|   | 6.1   | Overview                                                 | 73 |  |  |  |  |

|   | 6.2   | Operation                                                | 73 |  |  |  |  |

|   |       | 6.2.1 Errors                                             |    |  |  |  |  |

|   |       | 6.2.2 Correctable errors                                 |    |  |  |  |  |

|   |       | 6.2.3 Interrupts                                         |    |  |  |  |  |

|   | 6.3   | Registers                                                | 73 |  |  |  |  |

| 7 | Seria | al Debug Interface                                       | 75 |  |  |  |  |

|   | 7.1   | Overview                                                 | 75 |  |  |  |  |

|   | 7.2   | Operation                                                | 75 |  |  |  |  |

|   |       | 7.2.1 Transmission protocol                              |    |  |  |  |  |

|   |       | 7.2.2 Baud rate generation                               |    |  |  |  |  |

|   | 7.3   | Registers                                                |    |  |  |  |  |

|   | 7.4   | Signal definitions and reset values                      |    |  |  |  |  |

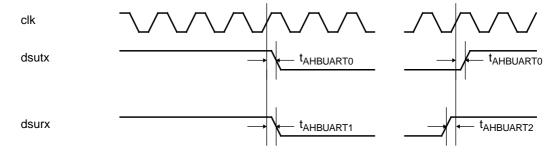

|   | 7.5   | Timing                                                   | 77 |  |  |  |  |

| 8 | JTA(  | G Debug Interface                                        | 78 |  |  |  |  |

|   | 8.1   | Overview                                                 |    |  |  |  |  |

|   | 8.2   | 2 Operation                                              |    |  |  |  |  |

|   |       | 8.2.1 Transmission protocol                              |    |  |  |  |  |

|   | 8.3   | Registers                                                | 79 |  |  |  |  |

|     | 8.4                                        | Signal definitions and reset values                     | 79 |  |  |  |  |

|-----|--------------------------------------------|---------------------------------------------------------|----|--|--|--|--|

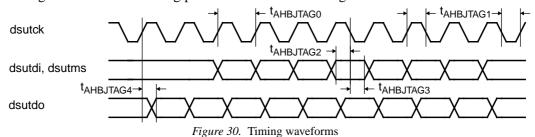

|     | 8.5                                        | Timing                                                  | 79 |  |  |  |  |

| 9   | Clock generation                           |                                                         |    |  |  |  |  |

|     | 9.1                                        | _                                                       |    |  |  |  |  |

|     | 9.2                                        | Signal definitions and reset values                     | 80 |  |  |  |  |

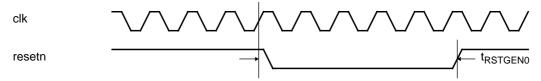

|     | 9.3                                        | Timing                                                  | 80 |  |  |  |  |

| 10  | Reset                                      | t generation                                            | 81 |  |  |  |  |

|     | 10.1                                       | Overview                                                | 81 |  |  |  |  |

|     | 10.2                                       | Signal definitions and reset values                     | 81 |  |  |  |  |

|     | 10.3                                       | Timing                                                  | 81 |  |  |  |  |

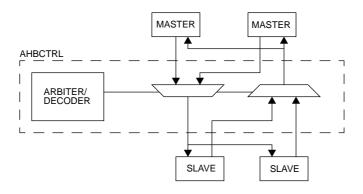

| 11  | AME                                        | BA AHB controller with plug&play support                | 82 |  |  |  |  |

|     | 11.1                                       | Overview                                                |    |  |  |  |  |

|     | 11.2                                       | Operation                                               | 82 |  |  |  |  |

|     |                                            | 11.2.1 Arbitration                                      |    |  |  |  |  |

|     |                                            | 11.2.2 Decoding                                         |    |  |  |  |  |

|     | 11.0                                       | 11.2.3 Plug&play information                            |    |  |  |  |  |

|     | 11.3                                       | Registers                                               | 83 |  |  |  |  |

| 12  | AMBA AHB/APB bridge with plug&play support |                                                         |    |  |  |  |  |

|     | 12.1                                       | Overview                                                |    |  |  |  |  |

|     | 12.2                                       | Operation                                               |    |  |  |  |  |

|     |                                            | 12.2.1 Decoding                                         |    |  |  |  |  |

|     |                                            |                                                         |    |  |  |  |  |

| 13  |                                            | rical description                                       |    |  |  |  |  |

|     | 13.1                                       | Absolute maximum ratings                                |    |  |  |  |  |

|     | 13.2                                       | Operating conditions                                    |    |  |  |  |  |

|     | 13.3                                       | Input voltages, leakage currents and capacitances       |    |  |  |  |  |

|     | 13.4                                       | Output voltages, leakage currents and capacitances      |    |  |  |  |  |

|     | 13.5                                       | Clock Input voltages, leakage currents and capacitances |    |  |  |  |  |

|     | 13.6                                       | Power supplies                                          |    |  |  |  |  |

| 14  | Mechanical description                     |                                                         |    |  |  |  |  |

|     | 14.1                                       | Component and package                                   |    |  |  |  |  |

|     | 14.2                                       | Pin assignment.                                         |    |  |  |  |  |

|     | 14.3                                       | RTAX2000S/SL specific pins - CQ352 package              |    |  |  |  |  |

|     | 14.4                                       | RTAX2000S/SL specific pins - CG624 package              |    |  |  |  |  |

| 1.5 | 14.5                                       | RT3PE3000L specific pins - CG484 package                |    |  |  |  |  |

| 15  |                                            | rence documents                                         |    |  |  |  |  |

| 16  | Orde                                       | ring information                                        | 98 |  |  |  |  |

| 17  | Chan                                       | Change record9                                          |    |  |  |  |  |

#### 1 Introduction

#### 1.1 Overview

The SpaceWire Router family is based on a common architecture from which standard configurations are derived. The architecture is centered around the a non-blocking switch matrix which can connect any input port to any output port.

All the addressing modes such as path, logical and regional logical are supported. Group adaptive routing is fully supported, meaning that both path and logical addresses can be individually configured to use from one up to all ports. A unique feature is the support for packet distribution, which can be used to implement multicast and broadcast addresses. Output ports are arbitrated using two priority levels with a round-robin scheme within each level.

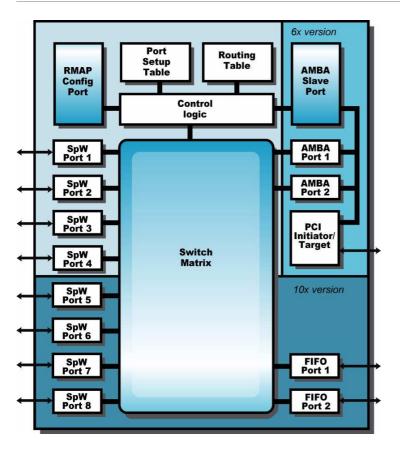

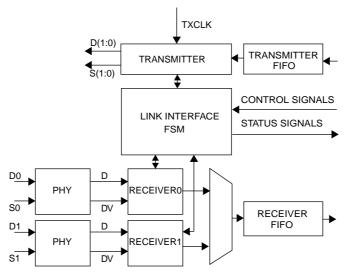

The 10x SpaceWire router implements 8 external SpaceWire ports and 2 external FIFO ports. The SpaceWire and FIFO interfaces are directly connected to the switch matrix.

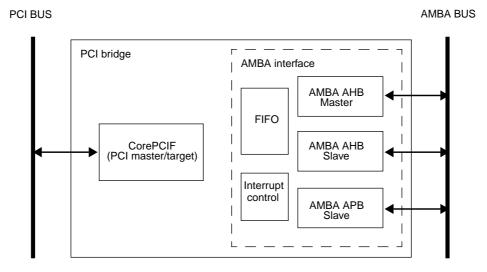

The 6x SpaceWire router implements 4 external SpaceWire ports and a PCI initiator and target interface (32-bit, 33 MHz) accessed via two internal AMBA ports with DMA and RMAP. In this configuration, the AMBA Advanced High-speed Bus (AHB), to which the AMBA ports and the PCI interface are connected, is used for high-speed communication between the switch matrix and the external PCI interface. Supporting low-bandwidth items, such as configuration registers, are connected to the AMBA Advanced Peripheral Bus (APB) which is accessed through an AHB to APB bridge.

The full SpaceWire router architecture includes the following modules: SpaceWire Router, PCI Initiator/Target Interface, AMBA AHB Debug UART and AMBA AHB Status Register.

# 1.2 Standard configurations

Due to resource limitations, it is not possible to fit the full SpaceWire router architecture on a single device. Therefore, sub-set configurations have been defined to suit applications with different interfacing needs. Table 1 below shows which functions are available in each of the configurations.

Table 1. Standard configurations

| Configuration name                            | 10x SpaceWire Router     | 6x SpaceWire Router with PCI |

|-----------------------------------------------|--------------------------|------------------------------|

| Configuration ID (CID)                        | 1                        | 2                            |

| SpaceWire Ports                               | 8                        | 4                            |

| FIFO Ports                                    | 2                        |                              |

| AMBA Ports with RMAP                          |                          | 2                            |

| Configuration port with RMAP                  | Yes                      | Yes                          |

| Configuration port with AMBA                  |                          | Yes                          |

| PCI Initiator/Target and Interrupt Controller |                          | Yes                          |

| AMBA Status Register                          |                          | Yes                          |

| UART Debug Link                               |                          | Yes                          |

| JTAG Debug Link                               |                          |                              |

| FPGA and Package                              | Actel RTAX2000S CCGA624  | Actel RTAX2000S CCGA624      |

|                                               | Actel RTAX2000S CQFP352  | Actel RTAX2000S CQFP352      |

|                                               | Actel RT3PE3000L CCGA484 |                              |

| SpaceWire Physical Layer                      | LVTTL / LVDS (on-chip)   | LVTTL / LVDS (on-chip)       |

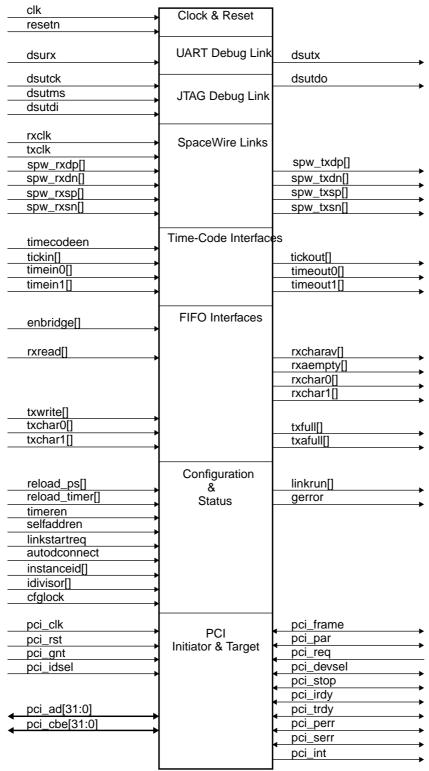

# 1.3 Signal overview

Figure 1. Signal overview

# 2 Architecture

# 2.1 Cores

The common architecture of the SpaceWire router family is based on cores from the GRLIB IP library. The vendor and device identifiers for each core can be extracted from the plug & play information. The used IP cores are listed in table 2.

Table 2. Used IP cores

| Core        | Function                     | Vendor | Device | CID |

|-------------|------------------------------|--------|--------|-----|

| AHBCTRL     | AHB Arbiter & Decoder        | 0x01   | -      | 2   |

| APBCTRL     | AHB/APB Bridge               | 0x01   | 0x006  | 2   |

| GRSPWROUTER | SpaceWire Router             | 0x01   | -      | All |

|             | AMBA port                    | 0x01   | 0x8A   | 2   |

|             | AMBA configuration port      | 0x01   | 0x8B   | 2   |

| PCIF        | PCI Initiator/Target         | 0x01   | 0x075  | 2   |

| AHBUART     | Serial/AHB debug interface   | 0x01   | 0x007  | 2   |

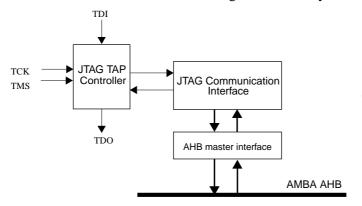

| AHBJTAG     | JTAG/AHB debug interface     | 0x01   | 0x01C  | -   |

| AHBSTAT     | AHB failing address register | 0x01   | 0x052  | 2   |

# 2.2 Interrupts

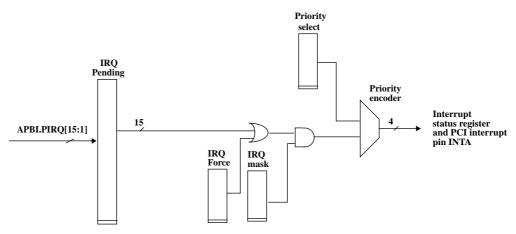

The SpaceWire router family uses the same interrupt assignment for all configurations. See the description of the individual cores for how and when the interrupts are raised. All interrupts are handled by the interrupt controller and forwarded to the PCI bus. Note that this only applies to CID 2.

Table 3. Interrupt assignment

| Core        | Interrupt | Comment                          | CID |

|-------------|-----------|----------------------------------|-----|

| GRSPWROUTER | 1, 2      | AMBA ports 0 and 1, respectively | 2   |

| PCIF        | 3         | (spare for future use)           | 2   |

| AHBSTAT     | 4         | (spare for future use)           | 2   |

-(()

# 2.3 Memory map

I

The SpaceWire router family uses the same memory map for all standard configurations. The memory map shown in table 4 is based on the AMBA AHB address space. Access to addresses outside the ranges will return an AHB error response. The detailed register layout is defined in the description of each individual core. Note that this only applies to CID 2.

Table 4. AMBA AHB address range

| Core          | Address range           | Area                     | CID |

|---------------|-------------------------|--------------------------|-----|

| PCIF          | 0x00000000 - 0x3FFFFFFF | PCI memory area, 1 GByte | 2   |

| APBCTRL       | 0xffE00000 - 0xffEfffff | APB bridge               | 2   |

| PCIF          | 0xFFF00000 - 0xFFF1FFFF | PCI I/O area             | 2   |

| GRSPWROUTER   | 0xFFFC0000 - 0xFFFC0FFF | Configuration area       | 2   |

| AHB plug&play | 0xfffff000 - 0xffffffff |                          | 2   |

The control registers of most on-chip peripherals are accessible via the AHB/APB bridge, which is mapped at address 0x80000000. The memory map shown in table 5 is based on the AMBA AHB address space. Note that this only applies to CID 2.

Table 5. APB address range

| Core          | Address range           | Comment     | CID |

|---------------|-------------------------|-------------|-----|

| GRSPWROUTER   | 0xffE00100 - 0xffE001ff | AMBA port 0 | 2   |

| GRSPWROUTER   | 0xfFE00200 - 0xfFE002FF | AMBA port 1 | 2   |

| PCIF          | 0xfFE00300 - 0xfFE003FF |             | 2   |

| AHBUART       | 0xffE00400 - 0xffE004ff |             | 2   |

| AHBJTAG       | 0xFFE00500 - 0xFFE005FF |             | -   |

| AHBSTAT       | 0xfFE00600 - 0xfFE006FF |             | 2   |

| APB plug&play | 0xffEff000 - 0xffEfffff |             | 2   |

# 2.4 Plug & play information

The LEON3FT RTAX family uses the same plug & play map for all standard configurations. The plug & play memory map and bus indexes for AMBA AHB masters are shown in table 6 and is based on the AMBA AHB address space. Note that this only applies to CID 2.

Table 6. Plug & play information for AHB masters

| Core        | Index | Function                   | Address range           | CID |

|-------------|-------|----------------------------|-------------------------|-----|

| GRSPWROUTER | 0     | AMBA port 0                | 0xFFFFF000 - 0xFFFFF01F | 2   |

| GRSPWROUTER | 1     | AMBA port 1                | 0xFFFFF020 - 0xFFFFF03F | 2   |

| PCIF        | 2     | PCI Initiator/Target       | 0xFFFFF040 - 0xFFFFF05F | 2   |

| AHBUART     | 3     | Serial/AHB debug interface | 0xFFFFF060 - 0xFFFFF07F | 2   |

| AHBJTAG     | 4     | JTAG/AHB debug interface   | 0xFFFFF080 - 0xFFFFF09F | -   |

The plug & play memory map and bus indexes for AMBA AHB slaves are shown in table 7 and is based on the AMBA AHB address space.

Table 7. Plug & play information for AHB slaves

| Core        | Index | Function             | Address range           | CID |

|-------------|-------|----------------------|-------------------------|-----|

| APBCTRL     | 0     | AHB/APB Bridge       | 0xFFFFF800 - 0xFFFFF81F | 2   |

| GRSPWROUTER | 1     | Configuration area   | 0xFFFFF820 - 0xFFFFF83F | 2   |

| PCIF        | 2     | PCI Initiator/Target | 0xFFFFF840 - 0xFFFFF85F | 2   |

The plug & play memory map and bus indexes for AMBA APB slaves are shown in table 8 and is based on the AMBA AHB address space.

Table 8. Plug & play information for APB slaves

| Core        | Index | Function                     | Address range           | CID |

|-------------|-------|------------------------------|-------------------------|-----|

| GRSPWROUTER | 0     | AMBA port 0                  | 0xFFEFF000 - 0xFFEFF017 | 2   |

| GRSPWROUTER | 1     | AMBA port 1                  | 0xFFEFF018 - 0xFFEFF01F | 2   |

| PCIF        | 2     | PCI Initiator/Target         | 0xFFEFF020 - 0xFFEFF027 | 2   |

| AHBUART     | 3     | Serial/AHB debug interface   | 0xFFEFF028 - 0xFFEFF02F | 2   |

| AHBJTAG     | 4     | JTAG/AHB debug interface     | 0xFFEFF030 - 0xFFEFF037 | -   |

| AHBSTAT     | 5     | AHB failing address register | 0xFFEFF038 - 0xFFEFF03F | 2   |

# 2.5 Specifications

Table 9. Specifications

| Technology                                         | Actel RT Axcelerator                            | Actel RT ProASIC3                                          |

|----------------------------------------------------|-------------------------------------------------|------------------------------------------------------------|

| Device                                             | RTAX2000S/SL                                    | RT3PE3000L                                                 |

| Link speed                                         | 200 MBPS                                        | 100 MBPS                                                   |

| Receiver clock                                     | 200 MHz                                         | 100 MHz                                                    |

| Transmitter clock                                  | 100 MHz (DDR)                                   | 50 MHz (DDR)                                               |

| System clock                                       | 25 MHz (CID 1) / 33 MHz (CID 2)                 | 25 MHz (CID 1)                                             |

| PCI clock                                          | 33 MHz                                          | N/A                                                        |

| Power consumption                                  | 500 mW (TBD)                                    | 500 mW (TBD)                                               |

| Package                                            | CQFP352, CCGA624                                | CCGA484                                                    |

| Total Ionizing Dose 1)                             | 300 krad (Si)                                   | 15 krad (Si)                                               |

| Single-Event Latch-Up Immunity (SEL) <sup>1)</sup> | LET <sub>TH</sub> > 117 MeV-cm <sup>2</sup> /mg | LET <sub>TH</sub> > 68 MeV-cm <sup>2</sup> /mg             |

| Single-Event Upsets (SEU) 1)                       | LET <sub>TH</sub> > 37 MeV-cm <sup>2</sup> /mg  | LET <sub>TH</sub> > 6 MeV-cm <sup>2</sup> /mg (before TMR) |

| Supply voltage                                     | 1.5 V, 2.5 V & 3.3 V                            | 1.2 V -1.5 V, 2.5 V & 3.3 V                                |

| Screening level <sup>2)</sup>                      | B, E, EV and PROTO                              | В                                                          |

Note 1: Refer to Actel RTAX and RT ProASIC3 data sheets [RTAX] and [RT3PE] for details.

Note 2: The pre-programmed Actel RTAX and RT ProASIC3 devices are shipped in all quality levels supported by Actel, as defined in [RTAX] and [RT3PE], respectively.

# 2.6 Signals

The common architecture has the external signals shown in table 10.

Table 10. External signals

| Name          | Usage                                              | Direction | Polarity | CID                  |

|---------------|----------------------------------------------------|-----------|----------|----------------------|

| clk           | Main system clock                                  | In        | -        | All                  |

| resetn        | System reset                                       | In        | Low      | All                  |

| dsutx         | Debug UART transmit data                           | Out       | Low      | 2                    |

| dsurx         | Debug UART receive data                            | In        | Low      | 2                    |

| dsutck        | Debug JTAG Clock                                   | In        | -        | -                    |

| dsutms        | Debug JTAG Mode                                    | In        | High     | -                    |

| dsutdi        | Debug JTAG Input                                   | In        | High     | -                    |

| dsutdo        | Debug JTAG Output                                  | Out       | High     | -                    |

| rxclk         | SpaceWire link receive clock                       | In        | -        | All                  |

| txclk         | SpaceWire link transmit clock                      | In        | -        | All                  |

| spw_rxdp[7:0] | Data input, positive                               | In, LVDS  | High     | All 1) 3)            |

| spw_rxdn[7:0] | Data input, negative                               | In, LVDS  | Low      | All 1) 3)            |

| spw_rxsp[7:0] | Strobe input, positive                             | In, LVDS  | High     | All 1) 3)            |

| spw_rxsn[7:0] | Strobe input, negative                             | In, LVDS  | Low      | All 1) 3)            |

| spw_txdp[7:0] | Data output, positive                              | Out, LVDS | High     | All <sup>1) 3)</sup> |

| spw_txdn[7:0] | Data output, negative                              | Out, LVDS | Low      | All 1) 3)            |

| spw_txsp[7:0] | Strobe output, positive                            | Out, LVDS | High     | All 1) 3)            |

| spw_txsn[7:0] | Strobe output, negative                            | Out, LVDS | Low      | All 1) 3)            |

| spw_rxd[7:0]  | Data input                                         | In,       | High     | All <sup>2) 3)</sup> |

| spw_rxs[7:0]  | Strobe input                                       | In        | High     | All <sup>2) 3)</sup> |

| spw_txd[7:0]  | Data output                                        | Out       | High     | All <sup>2) 3)</sup> |

| spw_txs[7:0]  | Strobe output                                      | Out       | High     | All <sup>2) 3)</sup> |

| timecodeen    | Enable time-code functionality                     | In        | High     | 1                    |

| tickin[1:0]   | Tick input signals for FIFO interfaces             | In        | High     | 1                    |

| timein0[7:0]  | Time input signals for FIFO 0 interface            | In        | -        | 1                    |

| timein1[7:0]  | Time input signals for FIFO 1 interface            | In        | -        | 1                    |

| tickout[1:0]  | Tick output signals for FIFO interfaces            | Out       | High     | 1                    |

| timeout0[7:0] | Time output signals for FIFO 0 interface           | Out       | -        | 1                    |

| timeout1[7:0] | Time output signals for FIFO 1 interface           | Out       | -        | 1                    |

| rxread[1:0]   | Receiver FIFO read signals for FIFO interfaces     | In        | High     | 1                    |

| rxchar0[8:0]  | Receiver character signals for FIFO 0 interface    | Out       | -        | 1                    |

| rxchar1[8:0]  | Receiver character signals for FIFO 1 interface    | Out       | -        | 1                    |

| txwrite[1:0]  | Transmitter FIFO write signals for FIFO interfaces | In        | High     | 1                    |

| txchar0[8:0]  | Transmitter character signals for FIFO 0 interface | In        | -        | 1                    |

| txchar1[8:0]  | Transmitter character signals for FIFO 1 interface | In        | -        | 1                    |

| txfull[1:0]   | Transmitter full signal for FIFO interfaces        | Out       | High     | 1                    |

Table 10. External signals

I

| Name              | Usage                                                                                                                              | Direction | Polarity | CID    |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|--------|--|

| txafull[1:0]      | Transmitter almost full signal for FIFO interfaces                                                                                 | Out       | High     | 1      |  |

| rxcharav[1:0]     | Receiver data available signal for FIFO interfaces                                                                                 | Out       | High     | 1      |  |

| rxaempty[1:0]     | Receiver empty signal for FIFO interfaces                                                                                          | Out       | High     | 1      |  |

| enbridge[1:0]     | Enables bridge mode for the FIFO interfaces                                                                                        | In        | High     | 1      |  |

| linkrun[7:0]      | SpaceWire link in run state when asserted                                                                                          | Out       | High     | All 3) |  |

| gerror            | Global error                                                                                                                       | Out       | High     | All    |  |

| reload_ps[5:0]    | Reset value for the timer prescaler. Mapped to bits 13, 11, 9, 7, 5 and 3 of the prescaler register, other bits to 0 at reset.     | In        | -        | All    |  |

| reload_timer[3:0] | In                                                                                                                                 | -         | All      |        |  |

| timeren           | Reset value for the timer enable bit in the port control registers                                                                 | In        | High     | All    |  |

| selfaddren        | Reset value for selfaddren register bit                                                                                            | In        | High     | All    |  |

| linkstartreq      | Reset value for the <i>linkstartreq</i> register bit                                                                               | In        | High     | All    |  |

| autodconnect      | Reset value for the <i>autodconnect</i> register bit                                                                               | In        | High     | All    |  |

| instanceid[3:0]   | Reset value for the instance <i>id</i> field of the version/instance id register. Sets bits 3:0, other bits cleared to 0 at reset. |           |          |        |  |

| idivisor[3:0]     | In                                                                                                                                 | -         | All      |        |  |

| cfglock           | Lock configuration port accesses from all ports except port 1 when asserted                                                        | In        | High     | All    |  |

| pci_clk           | PCI clock                                                                                                                          | In        | -        | 2      |  |

| pci_rst           | PCI reset                                                                                                                          | In        | Low      | 2      |  |

| pci_frame         | Cycle frame                                                                                                                        | BiDir     | Low      | 2      |  |

| pci_irdy          | Initiator ready                                                                                                                    | BiDir     | Low      | 2      |  |

| pci_trdy          | Target ready                                                                                                                       | BiDir     | Low      | 2      |  |

| pci_stop          | Stop                                                                                                                               | BiDir     | Low      | 2      |  |

| pci_idsel         | Device select during configuration                                                                                                 | In        | High     | 2      |  |

| pci_devsel        | Device select                                                                                                                      | BiDir     | Low      | 2      |  |

| pci_par           | Parity signal                                                                                                                      | BiDir     | High     | 2      |  |

| pci_perr          | Parity error                                                                                                                       | BiDir     | Low      | 2      |  |

| pci_serr          | System error                                                                                                                       | BiDir     | Low      | 2      |  |

| pci_req           | Request signal                                                                                                                     | BiDir     | Low      | 2      |  |

| pci_gnt           | Grant signal                                                                                                                       | In        | Low      | 2      |  |

| pci_cbe[3:0]      | Bus command and byte enable                                                                                                        | BiDir     | Low      | 2      |  |

| pci_ad[31:0]      | Address and Data bus                                                                                                               | BiDir     | High     | 2      |  |

| pci_int           | Interrupt signal                                                                                                                   | Out       | Low      | 2      |  |

Note 1: These signals are only used in configuration with on-chip LVDS drivers.

Note 2: These signals are only used in configuration with off-chip LVDS drivers.

Note 3: All bus signal elements are not used in all listed configurations. See pin assignment at end of document for details.

# 3 SpaceWire router

#### 3.1 Overview

The SpaceWire router core implements a SpaceWire routing switch as defined in the ECSS-E-ST-50-12C standard. It provides an RMAP target for configuration at port 0 used for accessing internal configuration and status registers. In addition to this there are three different external port types: SpaceWire links, FIFO interfaces and AMBA interfaces. An AHB slave interface is also provided for accessing the port 0 registers from the AHB bus. Group adaptive routing and packet distribution are fully supported (two ports up to all ports can be assigned to an address). System time-distribution is also supported. Timers are available for each port to prevent deadlock situations.

# 3.2 Operation

The router ports are interconnected using a non-blocking switch matrix which can connect any input port to any output port. Access to each output port is arbitrated using a round-robin arbitration scheme. A single routing-table is used for the whole router. Access to the table is also arbitrated using a round-robin scheme.

The ports consist of configuration port 0 and three different types of external ports: SpaceWire links, FIFO interfaces and AMBA interfaces.

All the ports regardless of their type have the same interface to the switch matrix and behave in the same manner. The difference in behavior is on the external side of the port. The SpaceWire ports provide standard SpaceWire link interfaces using either on- or off-chip LVDS. The FIFO interfaces store characters in two FIFOs which are accessed using 9-bit wide data paths with read/write signals. Lastly the AMBA ports transfer characters from and to an AHB bus using DMA. The four different port types are described in further detail in sections 3.3, 3.4, 3.5 and 3.6.

#### 3.2.1 Port numbering

The ports are numbered in the following order: configuration port, SpW ports, AMBA ports, FIFO ports. The configuration port is always present and has number 0. If SpW ports are present in the router they are numbered starting from number 1. If AMBA ports are present they are numbered starting from the last SpW ports. If no SpW ports are present the AMBA ports start at number 1. Lastly, the FIFO ports are numbered starting after the last AMBA port, SpW port or at number 1 depending on if AMBA ports and SpW ports are present respectively.

For example if 7 SpW ports and 4 FIFO ports are included in the router they will have port numbers 1-7 and 8-11. If 16 SpW ports, 2 AMBA ports and 7 FIFO ports are included they have port numbers 1-16, 17-18 and 19-25 respectively.

# 3.2.2 Routing table

A single routing table is provided. The access to this routing table is arbitrated using a round-robin arbiter with each port being of equal priority. The operation is pipelined and one lookup can be done each cycle. This way the maximum latency is equal to the number of ports in the router minus one. The impact on throughput should be negligible provided that packets are not incoming at the same time. The probability for this is higher when the traffic only consist of very small packets sent continuously (the average size being about the same as the number of ports). This should be a very uncommon case. Latency is still bounded and probably negligible in comparison to other latencies in most systems. The benefit is a reduced area enabling the router to be implemented with a higher number of ports on many FPGA technologies.

Since the latency for the lookup is very small and deterministic there is not much to gain by having configurable priorities for this. Priorities are instead used for arbitrating packets contending for an output port as described in the next section.

The routing table and all the configuration registers are configured through an RMAP target or an AHB slave interface which use the same routing table as the logic handling packet traffic. They do not introduce any extra latency because they have lower priority than the packet traffic and thus are only allowed access on cycles when no lookup is needed for packets. This can slow down configuration accesses but they are probably mostly done before packet traffic starts and very seldom afterwards.

Logical addresses have a routing table entry containing a priority bit, header deletion enable bit and a entry enable bit. The routing table entry is enabled by writing a 1 to the enable bit. It can be disabled again by writing a 0. The contents of the routing table is undetermined after reset and should not be read. When a routing table entry is disabled, packets with a destination address corresponding to that entry will be discarded and the invalid address error bit asserted.

Before the routing table entry is enabled the corresponding port setup register must be initialized. The port setup register should be written with ones to one or more bits to enable packets to be transmitted on the ports corresponding to the bit numbers. See sections 3.2.4 and 3.2.5 for more details on how to use the port setup register. If the port setup register is not initialized but the routing table entry is enabled packets with that logical address will be discarded and the invalid address error bit asserted.

The mechanism is the same for path addresses except that they do not have a routing table entry and header deletion is always enabled. Packets will be routed to the output corresponding to the path address in the packet even if the port setup register has not been initialized. For group adaptive routing and packet distribution to be used the port setup register must be initialized also for path addresses.

The routing table entries are also marked as invalid before they have been written the first time. When the entries are invalid, packets with the corresponding logical address will be discarded and an invalid address error bit asserted.

# 3.2.3 Output port arbitration

Each output port is arbitrated individually using two priority levels with round-robin at each level. Each path or logical address can be configured to be high or low priority. In this case the delays can be very long (compared to when arbiting for access to the routing table) before the next arbitration because packets can be very large and the speed of the data consumer and the link itself cannot be known. In this case priority assignments can have a large impact on the amount of bandwidth a source port can use on a destination port.

The priority for path addresses is set in the port's control register with the port number corresponding to the path address. For logical addresses the priority is set in the routing table entry.

#### 3.2.4 Group adaptive routing

Group adaptive routing is used to enable a packet to be transmitted on several different paths. For example a packet with address 45 can be enabled to be transmitted on port 1 and 2. If port 1 is busy when a packet with address 45 arrives it is transmitted on port 2 instead if not busy.

Group adaptive routing is used if bit 0 in the port setup register for the corresponding path or logical address is 0. Each bit in the register corresponds to the port with the same number as the bit index. So if bit 5 is set to 1 at address offset 0x80 it means that incoming packets with logical address 32 can be transmitted on port 5. If only one bit is set for an address all packets with that address will be transmitted on that port. If one or more bits are set the group adaptive function is used and the packet is transmitted on the first available port with a bit set to 1 starting from the lowest number. A port being

available means that no other packet transmission is active at the moment and also for SpaceWire links that the link is in run-state. For path addresses the bit corresponding to the path address will always be set. This is done as specified in the standard which requires a packet with a path address to be transmitted on the port with the same number as the address. The standard does not mention what should happen when group adaptive routing is used for path addresses but in this router the bit corresponding to the port number of the path address is always set so that the packet *can* be transmitted on that port also when group adaptive routing is used.

For logical addresses the corresponding routing table entry and port setup register must be valid for the packet to be routed (otherwise it is discarded). There is no default port as with path addresses so at least one bit in the port setup register must be 1 for the packet to be routed otherwise it is discarded.

#### 3.2.5 Packet distribution

Packet distribution can be used to implement multicast and broadcast addresses. Packets with logical address 50 can for example be configured to be transmitted on ports 1, 2 and 3 while address 51 can be configured to be transmitted on all ports (broadcast).

When packet distribution is enabled the group adaptive routing register is used to determine the ports that a packet should be transmitted on. Packet distribution is enabled for a path or logical address by setting bit 0 in the corresponding port setup register to 1. The packet will be transmitted on all the ports with a bit set to 1 in the register. This means that if one of the ports enabled for packet distribution is busy the router will wait for it to become free before transmitting on any of the ports. Due to the wormhole routing implementation the slowest link will determine the speed at which a packet is transmitted on all the ports.

When packet distribution is used with path addresses the port with the same number as the address will always be enabled (as for group adaptive routing).

#### 3.2.6 Port disable

The disable port bit in the port's control register can be used to disable a port for data traffic. It will behave just like if the physical port was not existing. Packets transmitted to it will be spilt and the invalid address bit on the source port is set. Packets received to the port will be silently discarded, no status bits are set.

All ports except the configuration port (0) and port 1 can be disabled to prevent the situation of all ports being locked out from happening.

## **3.2.7** Timers

Timers are individually enabled for each port by writing the timer enable bit in the port control register. When timers are enabled during packet transmission on a port the timer is reset each time a character is transmitted. If the timer expires the packet will be discarded and an EEP is inserted on all the ports to which the packet was transmitted (can be more than one if packet distribution was used). It does not matter if it is the output port or source port which is stalling. The blocking situation is always detected at the source port which handles the spilling. It also does not matter if the stall is caused by the link being stopped or lack of credits, the discard mechanism is always the same. When the timers are not implemented or disabled the source and destination ports will always block until the blocking situation is resolved.

The timers use a global prescaler and an individual timer per port. Both the prescaler and the individual timer tick rate can be configured through the configuration port.

In group adaptive routing mode the packet will be spilt if no characters have been transmitted for the timeout period after being assigned to a port. For packet distribution a packet will be spilt if no character has been transmitted for the timeout period after being assigned to all the ports. This means that it is enough for one port to stall for the packet to timeout and be spilt.

The behavior described above also means that the timeout is handled in the same way regardless of the port type (SpW, FIFO or AMBA).

If a destination port is disabled it behaves as if it is not existing and will not be used thus being spilt immediately. Timers are not applicable in that case. For group adaptive routing and packet distribution disabled ports are also masked before transmission starts and will not affect timers.

Details for the different scenarios will be listed in the remaining sub-sections.

#### 3.2.7.1 Timers disabled

If timers are disabled packets will always wait indefinitely regardless of stall reason. In the case that timers are present but are enabled on some ports and disabled on others it is always the source port that determines whether the timer will be active or not. This means that if a packet arrives at port 2 which has its timer enabled and it is routed to port 4 which has timers disabled a timer will be active for that packet routing and transmission. The same applies for group adaptive routing and packet distribution.

#### 3.2.7.2 Timer enabled and output port not in run state

The timer is started when the packet arrives and if the link has not entered run-state until the timer expires the packet will be spilt. No EEP will be written to the destination port in this case. If the link start on request feature has been enabled the router will try to start the link but still only waits for the timeout period for the link to start.

#### 3.2.7.3 Timer enabled and output port in run state but busy with other transmission

The packet will wait indefinitely until the destination port becomes free. In the case that the destination port is stalled the port currently sourcing the packet for it has to have its timer enabled and spill the packet before the new port can be allocated for it. If the port stalls again the new port will also spill its packet after the timeout period. In this case and EEP will be written to the destination port since the transmission of the packet had started.

## 3.2.7.4 Timer enabled and group adaptive routing is enabled, ports not running

The timer is started when the packet arrives and if no port has been allocated until the timer expires the packet will be spilt. If link start on request is enabled the router will try to start all the links.

## 3.2.7.5 Timer enabled and group adaptive routing enabled, ports running but busy

The packet will wait until one port becomes free and then start transmitting. The timer is not started while waiting for busy ports.

# 3.2.7.6 Timer enabled and packet distribution enabled, ports not running

If at least one of the destination ports is not running the timer is started and the packet will be discarded if all the ports are not running when the timer expires.

June 2012, Version 1.2

# 3.2.7.7 Timer enabled and packet distribution enabled, ports running but busy

If at least one port is busy but all are running when packet distribution is enabled the packet will wait indefinitely. When the transmission has started the timer is restarted each time a character is transmitted and if the timer expires the remaining part of the packet is spilt and an EEP written to all the destination ports.

#### 3.2.7.8 Timer functionality when accessing the configuration port

Timers work in the same way when accessing the configuration port as for the other ports. When the command is being received by the RMAP target the timer on the source port will trigger if the source of the command is too slow, spill the remaining part of the packet and insert an EEP to the configuration port. The RMAP target will always be able to receive the characters quick enough. If the source is too slow when the reply is sent the configuration port's timer will trigger and the remaining part of the packet is spilled and an EEP is inserted. This is to prevent the configuration port from being locked up by a malfunctioning source port.

# 3.2.8 On-chip memories

There are two memory blocks in the routing table, one for the port setup registers and one for the routing table. The port setup memory bit width is equal to the number of ports including the configuration port with depth 256. The routing table is 256 locations deep and 2 bits wide.

Each port excluding the configuration port also have FIFO memories. The SpaceWire ports have one FIFO per direction (rx, tx) which are 9-wide. The FIFO ports have the exact same FIFO configuration as the SpaceWire ports.

The AMBA ports have one 9-bit wide receiver FIFO and two 32-bit wide AHB FIFOs.

Parity is used to protect the memories and up to four bits per word can be corrected and there is a signal indicating an uncorrectable error.

If a memory error occurs in the port setup table or the routing table the memory error (ME) bit in the router configuration/status register is set and remains set until cleared by the user. If a memory error is detected in any of the ports FIFO memories the memory error (ME) bit in the respective port status register is set and remains set until cleared by the user. The ME bits are only set for uncorrectable errors.

When an uncorrectable error is detected in the port setup or routing table when a packet is being routed it will be discarded. Uncorrectable errors in the FIFO memories are not handled since they only affect the contents of the routed packet not the operation of the router itself. These type of errors should be caught by CRC checks if used in the packet.

The ME bit for the ports is only usable for detecting errors and statistics since there is no need to correct the error manually since the packet has already been routed when it is detected. The ME indication for the routing table and port setup registers can be used for starting a scrubbing operation if detected. There is also an option of having automatic scrubbing (see section 3.2.8.1)

#### 3.2.8.1 Autoscrub

With autoscrubbing the routing table and port setup registers will be periodically read and rewritten. This is done to prevent buildup of SEUs to cause an uncorrectable error in the memories. It will run in the background and has no impact on routing table lookup for traffic but can delay configuration accesses with two cycles.

The scrubber starts at address 0 and simultaneously writes one location in the port setup memory and the routing table memory. It then waits for a timeout period until it writes the next word. Eventually the last location is reached and the process starts over from address 0.

The period between each word refresh is approximately  $2^{26}$  core clock cycles. The scrubber uses a free slot when data traffic does not need to perform a table lookup to read and write the memories which causes a small indeterminism in the period.

#### 3.2.9 System time-distribution

The router contains a global time-counter register which handles system time-distribution. All the different port types support time-code transmission. Incoming time-codes on the ports are checked against the time-counter which is then updated. If time-code was determined to have a count value one more modulo 64 than the previous value then a tick is generated and the time-code is forwarded to all the other ports. The time-codes are also forwarded to the FIFO and AMBA ports where they appear on their respective external interfaces. Time-codes can also be transmitted from the FIFO and AMBA ports. In that case they are also compared to the time-counter and propagated to the other ports if valid.

The current router master time-counter and control flag values can be read through the configuration port (see the time-code register in section 3.7).

In default mode the router does not check the control flags so time-codes will be accepted regardless of their value. If the TF bit in the router configuration/status register is set to 1 time-code control flag filtering is enabled and the time-codes are required to have the control flags set to "00" to be accepted, otherwise they are dropped when received.

After reset all the ports are enabled to receive and transmit time-codes. The TE bit in a port's control register can be set to 0 to disable time-code transmission and reception on that port.

Time-code transfers can also be disabled globally using a signal.

#### 3.2.10 Invalid address error

An invalid address error occurs when a port receives a packet with an destination address that belongs to one or more of the three following groups:

- 1. Destination address is a path address corresponding to a non-existing port number. For example if the router only has 8 ports and a packet has destination address 15 this error will occur. If a router has 31 ports (32 including the configuration port) this error cannot occur.

- 2. Destination address is a logical address corresponding to a routing table entry which has not been configured. The routing table entries start at address 0x480.

- 3. Destination address is a logical address corresponding to a port setup register which has not been configured. The port setup registers start at address 0x80 for logical addresses.

- 4. The destination port determined either through physical or logical address has the disable (DI) bit set in the port control register.

#### 3.2.11 Global configuration features

#### 3.2.11.1 Self addressing

Normally the ports are allowed to address themselves i.e. a packet is received on a port with a destination address configured to be transmitted on the same port (which the packet was received on). This

June 2012, Version 1.2

can be disabled by setting the self addressing enable (SA) bit in the router configuration/status register to 0. The reset value of this bit is set using a signal.

This also applies to group adaptive routing and packet distribution. When group adaptive routing is enabled for an address a packet with that destination address will be spilt due to self-addressing only if the packet is actually routed to the source port. That is if ports 1 and 2 are enabled for address 1 and a packet with address 1 arrives and it is routed to port 2 the transfer will be performed normally. If it is routed to port 1 and self-addressing is disabled it will be discarded.

For packet distribution the packet will always be discarded if the source port is included in the list of destination ports since the packet will be sent to all destinations.

#### 3.2.11.2 Link start on request

Ports can be configured to start automatically when a packet is waiting to be transmitted on it. This is done by setting the LS bit in the router configuration/status register to 1. If the port link is disabled it will override the start feature and the link will not start. The reset value of this bit is set using a signal. This feature is only applicable for SpaceWire ports.

If the linkstart bit for the port is set the setting for the link start on request bit will have no effect. The link will continue to be started until a '0' is written to the linkstart bit of the port or if the auto disconnect feature is enabled (see next section).

#### 3.2.11.3 Auto disconnect

If the link was started by the link start feature the auto disconnect feature can be enabled to automatically stop the link if inactive during a timeout period. The auto disconnect feature is enabled by setting the AD bit in the router configuration/status register. The reset value is set using a signal. This feature is only applicable to SpaceWire ports.

The link will be disconnected under the following conditions. The link start on request feature is enabled and the link was not in run-state when the packet arrived at the output port. Then the link will be disconnected when the packet transmission has finished (output port free), the transmit FIFO is empty, no receive operation is active and the timeout period has expired since the last of the requirements for disconnect (the ones listed here) became true.

# 3.3 SpaceWire ports

When a port is configured as a SpaceWire link it consists of a SpaceWire codec with FIFO interfaces. All the configurable parameters for the link are accessible through the router configuration port (see the register section for the configurable parameters).

# 3.4 FIFO ports

A port configured as a FIFO port contains one FIFO in each direction to/from the switch matrix.

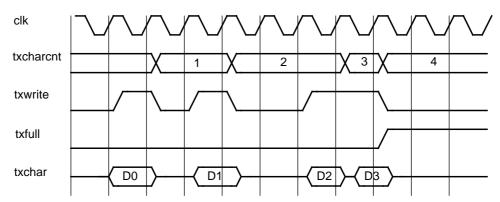

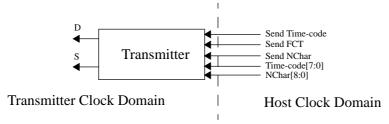

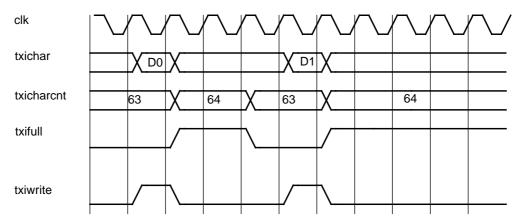

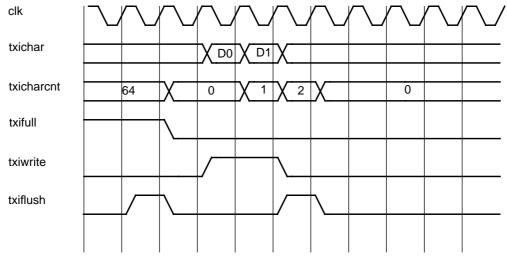

#### 3.4.1 Transmitter

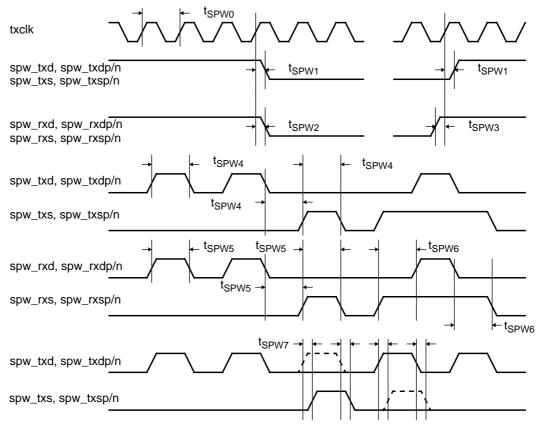

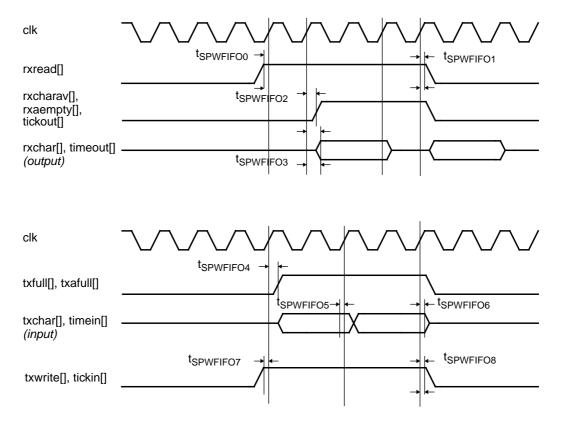

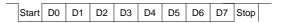

The transmitter FIFO interface consists of the following signals: txfull, txafull, txwrite, txchar, txcharcnt. Figure 2 illustrates the write operation. Note that txfull would only be asserted as illustrated in the figure when txcharcnt is 4 if the FIFO size is 4 (which is not the case typically).

June 2012, Version 1.2

Figure 2. Transmitter FIFO interface write cycle.

Txwrite is the write signal and each time when asserted on the rising edge of the clock the value on the txchar signal will be written into the transmitter FIFO if it is not full. If it is full the character will be dropped. Txcharcnt indicates the number of characters currently in the FIFO. Txfull is asserted when the FIFO is full and txafull is asserted when the FIFO is almost full.

The transmitter FIFO can be reset through the port's control register using the TF bit.

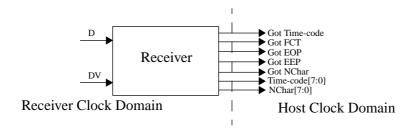

#### 3.4.2 Receiver

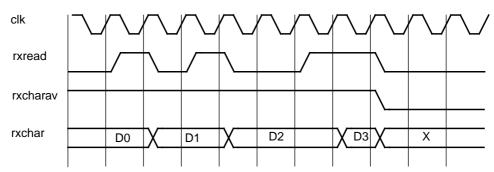

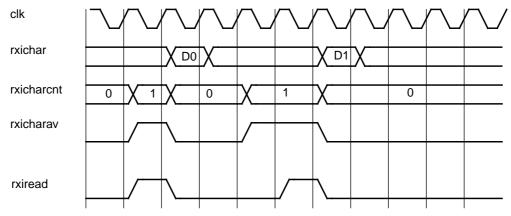

The receiver FIFO interface consists of the following signals: rxread, rxchar, rxcharav and rxaempty. Figure 3 illustrates the read operation. Note that rxcharav would only be deasserted as illustrated in the figure if the FIFO contained 4 characters.

Figure 3. Receiver FIFO interface read cycle.

Each time rxread is asserted on the rising edge of the clock a new character will be available on the rxchar output the next cycle if available. If the FIFO is empty the value is undefined. Rxcharav is asserted when the FIFO contains at least one character. Rxaempty is asserted when the FIFO is almost empty.

The receiver FIFO can be reset using the RF bit in the port's control register.

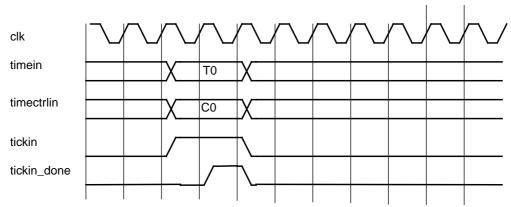

#### 3.4.3 Time-code transmit

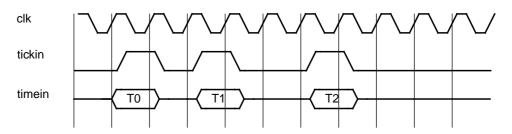

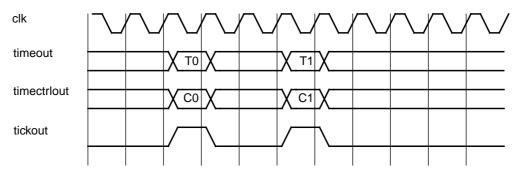

The time-code transmit interface consists of the following signals: tickin, timein. Figure 4 illustrates the tickin operation.

Figure 4. Time interface tickin operation.

#### 3.4.4 Time-code receive

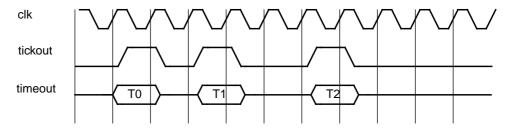

The time-code receive interface consists of the following signals: tickout, timeout. Figure 5 illustrates the tickout operation.

Figure 5. Time interface tickout operation.

The clock that all the interface signals are synchronized to is the same as the core clock (the clock that everything except the SpaceWire links' transmitters and receivers are running on). It can run on any frequency but to support the maximum throughput it has to be at least one eighth of the maximum link bitrate.

# 3.4.5 Bridge mode

The FIFO ports normally operate in standard mode which has been described so far in this section. But they can also be set in bridge mode through the bridge enable (BE) bit in the port's control register. The reset value of this signal is set through an input signal so this mode can be enabled per default after reset.

In bridge mode two FIFO ports can be connected together with automatic packet and time-code transfer without any glue logic. Table 11 shows how the signals should be mapped. Rxaempty and txafull are unused in this mode.

0

| Table 11. Signa | l mappings | of FIFO | port in | bridge | mode. |

|-----------------|------------|---------|---------|--------|-------|

|-----------------|------------|---------|---------|--------|-------|

| Port 0   | Port 1   |

|----------|----------|

| rxchar   | txchar   |

| rxread   | txfull   |

| txwrite  | rxcharav |

| txchar   | rxchar   |

| txfull   | rxread   |

| rxcharav | txwrite  |

| tickin   | tickout  |

| timein   | timeout  |

| tickout  | tickin   |

| timeout  | timein   |

# 3.5 AMBA ports

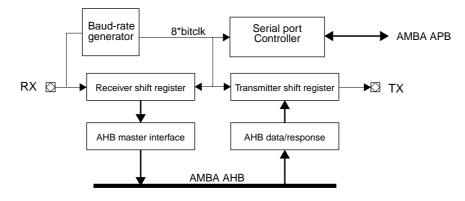

The AMBA ports consists of what is basically a GRSPW2 core with the SpaceWire codec removed. The same drivers that are provided for the GRSPW2 core can be used for each AMBA port on the router. Only an additional driver is needed which handles the setup of all the registers on the configuration port.

#### 3.5.1 Overview

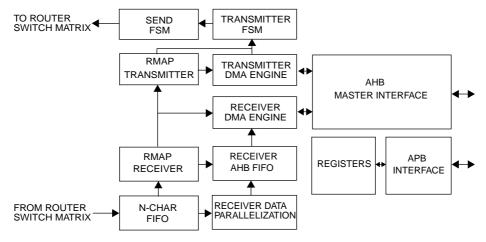

The Router AMBA port is configured through a set of registers accessed through an APB interface. Data is transferred through DMA channels using an AHB master interface.

Figure 6. Block diagram of the Router DMA port

## 3.5.2 Operation

The main sub-blocks of the router AHB interfaces are the DMA engines, the RMAP target and the AMBA interface. A block diagram of the internal structure can be found in figure 6.

The AMBA interface is divided into the AHB master interface and the APB interface. The DMA engines have FIFO interfaces to the router switch matrix. These FIFOs are used to transfer N-Chars between the AMBA bus and the other ports in the router.

The RMAP target handles incoming packets which are determined to be RMAP commands instead of the receiver DMA engine. The RMAP command is decoded and if it is valid, the operation is performed on the AHB bus. If a reply was requested it is automatically transmitted back to the source by the RMAP transmitter.

#### 3.5.2.1 Protocol support

The AMBA port only accepts packets with a valid destination address in the first received byte. Packets with address mismatch will be silently discarded (except in promiscuous mode which is covered in section 3.5.3.10).

The second byte is sometimes interpreted as a protocol ID a described hereafter. The RMAP protocol (ID=0x1) is the only protocol handled separately in hardware while other packets are stored to a DMA channel. If the RMAP target is present and enabled all RMAP commands will be processed, executed and replied automatically in hardware. Otherwise RMAP commands are stored to a DMA channel in the same way as other packets. RMAP replies are always stored to a DMA channel. More information on the RMAP protocol support is found in section 3.5.5 (note that this RMAP target is different from the one in the configuration port). When the RMAP target is not present or disabled, there is no need to include a protocol ID in the packets and the data can start immediately after the address.

All packets arriving with the extended protocol ID (0x00) are stored to a DMA channel. This means that the hardware RMAP target will not work if the incoming RMAP packets use the extended protocol ID. Note also that packets with the reserved extended protocol identifier (ID = 0x000000) are not ignored by the AMBA port. It is up to the client receiving the packets to ignore them.

When transmitting packets, the address and protocol-ID fields must be included in the buffers from where data is fetched. They are *not* automatically added by the AMBA port DMA engine.

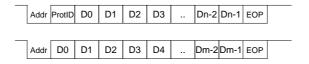

Figure 7 shows the packet types accepted by the port. The port also allows reception and transmission with extended protocol identifiers but without support for RMAP CRC calculations and the RMAP target.

Figure 7. The SpaceWire packet types supported by the port.

# 3.5.2.2 Time interface

The time interface is used for sending Time-codes over the SpaceWire network and consists of a time-counter register, time-ctrl register, tick-in signal, tick-out signal, tick-in register field and a tick-out register field. There are also two control register bits which enable the time receiver and transmitter respectively.

Each Time-code sent from the sent from the port is a concatenation of the time-ctrl and the time-counter register. There is a timetxen bit which is used to enable Time-code transmissions. It is not possible to send time-codes if this bit is zero.

Received Time-codes are stored to the same time-ctrl and time-counter registers which are used for transmission. The timerxen bit in the control register is used for enabling time-code reception. No time-codes will be received if this bit is zero.

The two enable bits are used for ensuring that a node will not (accidentally) both transmit and receive time-codes which violates the SpaceWire standard. It also ensures that a master sending time-codes on a network will not have its time-counter overwritten if another (faulty) node starts sending time-codes.

The time-counter register is set to 0 after reset and is incremented each time the tick-in signal is asserted for one clock-period and the timetxen bit is set. This also causes the new value to be sent to the router (which will propagate the time-code to the other ports if valid just as if it was transmitted on a normal SpW link). Tick-in can be generated either by writing a one to the register field or by asserting the tick-in signal. A Tick-in should not be generated too often since if the time-code after the previous Tick-in has not been sent the register will not be incremented and no new value will be sent. The tick-in field is automatically cleared when the value has been sent and thus no new ticks should be generated until this field is zero. If the tick-in signal is used there should be at least 4 system-clock plus 25 transmit-clock cycles between each assertion.

A tick-out is generated each time a valid time-code is received and the timerxen bit is set. When the tick-out is generated the tick-out signal will be asserted one clock-cycle and the tick-out register field is asserted until it is cleared by writing a one to it.

The current time counter value can be read from the time register. It is updated each time a Time-code is received and the timerxen bit is set. The same register is used for transmissions and can also be written directly from the APB interface.

The control bits of the Time-code are stored to the time-ctrl register when a Time-code is received whose time-count is one more than the nodes current time-counter register. The time-ctrl register can be read through the APB interface. The same register is used during time-code transmissions.

It is possible to have both the time-transmission and reception functions enabled at the same time.

#### 3.5.3 Receiver DMA channels

The receiver DMA engine handles reception of data from the SpaceWire network to different DMA channels.

#### 3.5.3.1 Address comparison and channel selection

Packets are received to different channels based on the address and whether a channel is enabled or not. When the receiver N-Char FIFO contains one or more characters, N-Chars are read by the receiver DMA engine. The first character is interpreted as the logical address and is compared with the addresses of each channel starting from 0. The packet will be stored to the first channel with an matching address. The complete packet including address and protocol ID but excluding EOP/EEP is stored to the memory address pointed to by the descriptors (explained later in this section) of the channel.

Each SpaceWire address register has a corresponding mask register. Only bits at an index containing a zero in the corresponding mask register are compared. This way a DMA channel can accept a range of addresses. There is a default address register which is used for address checking in all implemented DMA channels that do not have separate addressing enabled and for RMAP commands in the RMAP target. With separate addressing enabled the DMA channels' own address/mask register pair is used instead.

If an RMAP command is received it is only handled by the target if the default address register (including mask) matches the received address. Otherwise the packet will be stored to a DMA channel if one or more of them has a matching address. If the address does not match neither the default address nor one of the DMA channels' separate register, the packet is still handled by the RMAP target if enabled since it has to return the invalid address error code. The packet is only discarded (up to and including the next EOP/EEP) if an address match cannot be found and the RMAP target is disabled.

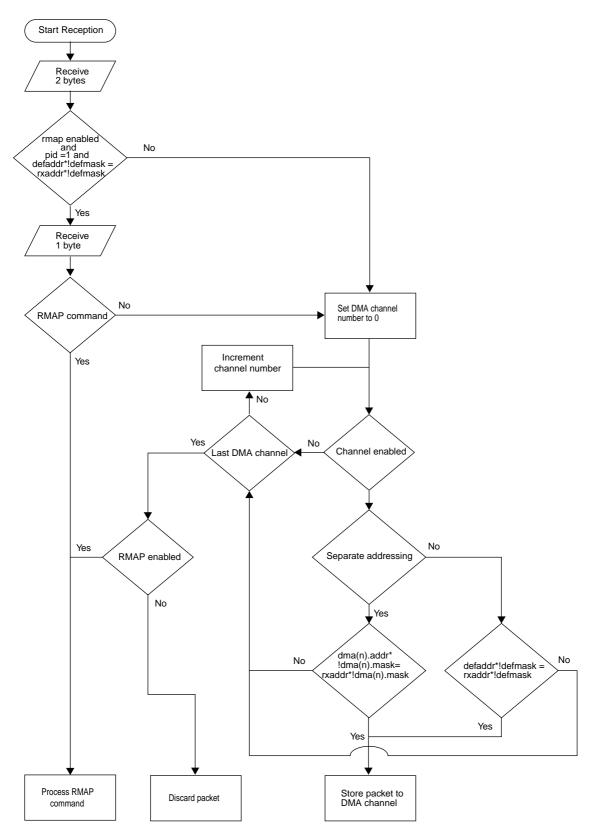

Packets, other than RMAP commands, that do not match neither the default address register nor the DMA channels' address register will be discarded. Figure 8 shows a flowchart of packet reception.

At least 2 non EOP/EEP N-Chars needs to be received for a packet to be stored to the DMA channel unless the promiscuous mode is enabled in which case 1 N-Char is enough. If it is an RMAP packet with hardware RMAP enabled 3 N-Chars are needed since the command byte determines where the packet is processed. Packets smaller than these sizes are discarded.

Figure 8. Flow chart of packet reception (promiscuous mode disabled).

# 3.5.3.2 Basic functionality of a channel

Reception is based on descriptors located in a consecutive area in memory that hold pointers to buffers where packets should be stored. When a packet arrives at the port the channel which should receive it is first determined as described in the previous section. A descriptor is then read from the channels' descriptor area and the packet is stored to the memory area pointed to by the descriptor. Lastly, status is stored to the same descriptor and increments the descriptor pointer to the next one. The following sections will describe DMA channel reception in more detail.

# 3.5.3.3 Setting up the port for reception

A few registers need to be initialized before reception to a channel can take place. The DMA channel has a maximum length register which sets the maximum packet size in bytes that can be received to this channel. Larger packets are truncated and the excessive part is spilled. If this happens an indication will be given in the status field of the descriptor. The minimum value for the receiver maximum length field is 4 and the value can only be incremented in steps of four bytes up to the maximum value 33554428. If the maximum length is set to zero the receiver will *not* function correctly.

Either the default address register or the channel specific address register (the accompanying mask register must also be set) needs to be set to hold the address used by the channel. A control bit in the DMA channel control register determines whether the channel should use default address and mask registers for address comparison or the channel's own registers. Using the default register the same address range is accepted as for other channels with default addressing and the RMAP target while the separate address provides the channel its own range. If all channels use the default registers they will accept the same address range and the enabled channel with the lowest number will receive the packet.

Finally, the descriptor table and control register must be initialized. This will be described in the two following sections.

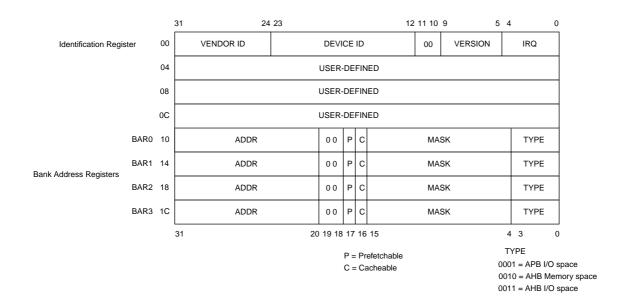

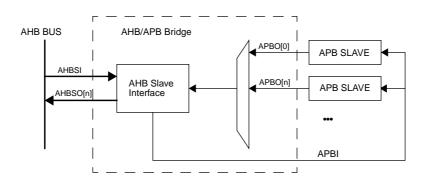

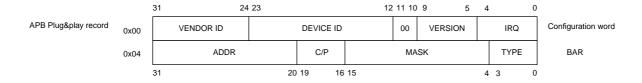

## 3.5.3.4 Setting up the descriptor table address