Kazuo Kondo • Morihiro Kada • Kenji Takahashi Editors

# Three-Dimensional Integration of Semiconductors

Processing, Materials, and Applications

@2015

Springer, Chem X/eialle berg

# **Contributors**

Taubasa Bandoh Okamoto Machine Tool Works, Ltd., Annaka, Gunma, Japan Raleigh Estrada Carl Zeiss X-ray Microscopy Inc., Pleasanton, CA, USA Michael Feser Carl Zeiss X-ray Microscopy Inc., Pleasanton, CA, USA Gilles Fresquet. FOGALE nanotech, NÎMES, France Hiroaki Fusano 3DI Dept. ATS BU, Tokyo Electron Ltd., Tokyo, Japan Allen Gu Carl Zeiss X-ray Microscopy Inc., Pleasanton, CA, USA Takashi Haimoto Dicer Grinder Marketing Team, Marketing Group, Sales Engineering Division, DISCO Corporation, Ota-ku, Tokyo, Japan Masaki Hashizume The University of Tokushima, Tokushima, Japan Yoshinobu Higami Ehime University, Ehime, Japan Yoshihito Inaba Hitachi Chemical Co., Ltd., Ibaraki, Japan Toshihiro Ito Okamoto Machine Tool Works, Ltd., Annaka, Gunma, Japan Bruce Johnson Carl Zeiss X-ray Microscopy Inc., Pleasanton, CA, USA Morihiro Kada Osaka Prefecture University, Osaka, Japan The National Institution of Advanced Industrial Science and Technology (AIST), Ibaraki, Japan

Tadashi Kamada DENSO Corp., Aichi, Japan

Shuichi Kameyama Fujitsu Limited, Kanagawa, Japan

Harufumi Kobayashi Lapis Semiconductor, Kanagawa, Japan Kazno Kondo Osaka Prefecture University, Osaka, Japan

Mitsuma Koyanagi NICHe, Tohoku University, Miyagi, Japan Yutaka Kusuda R&D Division, SAMCO Inc., Kyoto, Japan xviii Contributors

Kangwook Lee NICHe, Tohoku University, Miyagi, Japan

**Shyue-Kung Lu** National Taiwan University of Science and Technology, Taipei, Taiwan (R.O.C.)

Takahiko Mitsui Okamoto Machine Tool Works, Ltd., Annaka, Gunma, Japan

Fumihiko Nakazawa FUJITSU LABORATORIES LTD., Kanagawa, Japan

Tomoyuki Nonaka R&D Division, SAMCO Inc., Kyoto, Japan

Toshihisa Nonaka Toray Research Center, Inc. (TRC), Shiga, Japan

Kenichi Osada Hitachi Ltd., Tokyo, Japan

Sylvain Perrot FOGALE nanotech, NÎMES, France

Jean-Philippe Piel FOGALE nanotech, NÎMES, France

Zvi Roth Florida Atlantic University, Boca Raton, FL, USA

Kazuta Saito 53M Japan Limited, Sagamihara-shi, Kanagawa, Japan

Itsuko Sakai Graduate School of Engineering, Nagoya University, Nagoya, Japan

Osamu Sato Lasertec Corporation, Yokohama, Japan

Makoto Sekine Graduate School of Engineering, Nagoya University, Nagoya, Japan

Haruo Shimamoto Advanced Industrial Science and Technology (AIST), Ibaraki, Japan

Hiroshi Takahashi Computer Science, Graduate School of Science and Engineering, Ehime University, Ehime, Japan

Kenichi Takeda Hitachi Ltd., Tokyo, Japan

Hideo Takizawa Lasertec Corporation, Yokohama, Japan

Masahiko Tanaka SPP Technologies Co., Ltd., Amagasaki, Hyogo, Japan

Yoshitaka Tatsumoto Lasertec Corporation, Yokohama, Japan

Osamu Tsuji R&D Division, SAMCO Inc., Kyoto, Japan

Shiro Uchiyama Micron Memory Japan, Kanagawa, Japan

Senling Wang Ehime University, Ehime, Japan

Fumiaki Yamada IBM Research, Tokyo, Japan

Elichi Yamamoto Okamoto Machine Tool Works, Ltd., Annaka, Gunma, Japan

Masahiro Yamamoto 3DI Dept. ATS BU, Tokyo Electron Ltd., Minato-ku, Tokyo, Japan

Tsuyoshi Yoshida Okamoto Machine Tool Works, Ltd., Annaka, Gunma, Japan Hiroyuki Yotsuyanagi The University of Tokushima, Tokushima, Japan

# **About the Editors**

Dr. Kazuo Kondo is a professor in the Department of Chemical Engineering, Osaka Prefecture University. He received his Ph.D. in chemical engineering from the University of Illinois in 1981. He has worked for Sumitomo Metal Industries, Hokkaido University, and Okayama University. He has 200 research publications and 100 patents. His major research is Copper Electrodeposition for TSV. His research extends to various fields, not only in electrodeposition but also in battery science and CVD. He is a member of the Electrochemical Society, IEEE, the Society of Chemical Engineering, Japan, the Japanese Institute of Electrochemistry Japan and the Japanese Society of Applied Physics.

Morihiro Kada is an invited researcher of the National Institute of Advanced Industrial Science and Technology (AIST) and a part-time researcher at Osaka Prefecture University. Prior to joining AIST and the university, he headed the Japanese national research and development project on semiconductor 3D-Integration technology in the Association of Super-Advanced Electronics Technologies (ASET). He has also been the general manager of the Advanced Packaging Development Department in Sharp Corporation. He received his B.E. in applied physics from Fukui University, Japan in 1970. He has more than 40 years of experience in semiconductor packaging engineering, with major emphasis on developing chip scale, chip stack package, and three-dimensional-system-in-package (3D-SiP), and is the global pioneer of 3D-Integration technology in the world.

Dr. Kenji Takahashi is a chief specialist at Memory Packaging Development Department, Memory Division, Semiconductor and Storage Company, Toshiba Corporation. He received an M.E. in chemical engineering from the University of Tokyo in 1984 and a Ph.D. in information science and electrical engineering from Kyushu University in 2010. His major research and development focuses on semiconductor packaging and chip package interaction, especially through-silicon via technology. He was the research manager of the Electronic System Integration Technology Research Department at the Association of Super-Advanced Electronics Technologies (ASET). He is a senior member of IEEE, and a member of the Society for Chemical Engineers, Japan; the Institute of Electronics, Information and Communication Engineers; and the Japanese Institute of Electronics Packaging.

# Chapter 1 Research and Development History of Three-Dimensional Integration Technology

Moribiro Kada

## Introduction

Semiconductor integrated circuits have been developed according to Moore's law: the conjecture made in 1965 was that the number of transistors in a dense integrated circuit (IC) will double every 2 years, and the industry has developed according to this trend [1]. Two different concepts have been proposed for future advancements. One is "More Moore," which suggests that technological progress will continue to follow scaling theory, and the other is termed "More than Moore," which emphasizes the evolution and diversification of function [2].

# 1.1.1 The International Technology Roadmap for Semiconductors

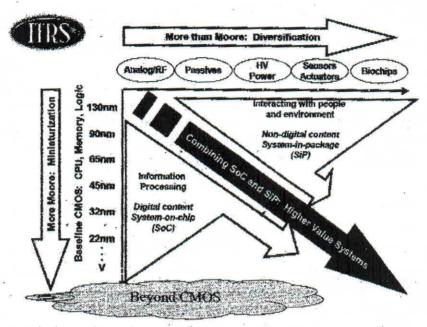

The international semiconductor research community gathered in 2005, at the abovementioned meeting (the International Technology Roadmap for Semiconductors, ITRS), which led to the concept of "More than Moore," Two years later, at ITRS 2007, a number of such ideas were formally defined. We elaborate on two of these: scaling and functional diversification with reference to Fig. 1.1.

- 1. Scaling: Fig. 1.1, vertical axis of "More Moore"

- a. Geometrical scaling: Also referred to as constant field scaling, this design methodology involves reducing the horizontal and vertical dimensions of physical features of the on-chip logic and memory storage components to

M. Kada (⊠)

Osaka Prefeorare University, Osaka, Japan

c-mail: cmk26222@osakafu-u.ac.jp

The National Institution of Advanced Industrial Science and Technology (AIST). Ibaraki, Japan

e-mail: m-kada@aist.go.jp

© Springer International Publishing Switzerland 2015 K. Kondo et al. (eds.), Three-Dimensional Integration of Semiconductors, DOI 10.1007/978-3-319-18675-7 1

Fig. 1.1 A diagrammatic representation of the concepts of "Moore's law" and "More than Moore". (Reproduced with permission from Ref. [3], Fig. 4). RF radio frequency, CPU central processing unit, CMOS complementary metal—oxide—semiconductor

improve density (cost per function reduction), performance (speed, power), and reliability (Fig. 1.1).

b. Equivalent scaling: This approach refers to (a) three-dimensional (3D) device structure ("design factor") improvements as well as other nongeometric processing techniques and the use of new materials that affect the performance of the chip; (b) novel design techniques and technologies, such as multi-core design. Equivalent scaling occurs in conjunction with geometric scaling and aims for the continuation of "Moore's law."

## 2. Functional Diversification: Fig. 1.1, horizontal axis of "More than Moore."

Moore's law is not the only way to provide additional value to the end user. A complementary approach is that of functional diversification, which refers to the incorporation of new functionalities into devices that are not necessarily scalings of existing hardware or software. Typical of this "More than Moore" approach is the migration of non-digital functionalities (e.g., radio frequency (RF) communication, power control, passive components, sensors, and actuators) from the system board level into a particular chip-level (system on a chip; SoC) or package-level (system in package; SiP) implementation. As the need increases for evermore complex software to be embedded into SoCs and SiPs, the role of the software itself in performance scaling may also need to be considered. The objective of the "More than Moore" design methodology is to incorporate digital and non-digital functionalities into compact systems.

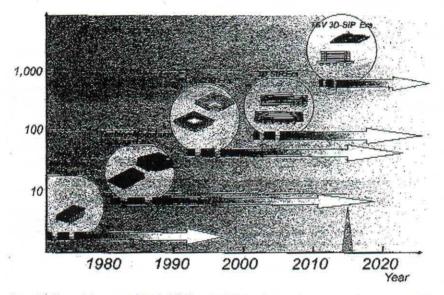

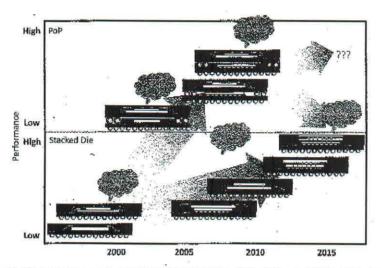

Fig. 1.2 Toward the new TSV 3D-SiP Era. 3D-SiP three-dimensional system in package, TSV through-Si via, BGA/CSP ball grid array/chip-scale package

## 1.1.2 3D Integration Technology

Although 3D integration technology is not explicit in the definition of "More than Moore," it is generally considered to be one of the most important technology development strategies. The transistor scaling that has continued for more than 40 years is approaching the atomic level of silicon, and this physical limit will likely be reached in 10–15 years.

Entirely new device structures, such as carbon nanotubes, spintronics, and molecular switches are being developed to replace transistor technology. However, they will not be ready for 10–15 years. In the interim, 3D integration technology offers a viable solution for continued performance and economic advancement [4].

"More than Moore" is not just a solution to the limitation of "More Moore," it also recognizes the evolution and potential for improvements of packaging technology. Figure 1.2 illustrates the history of IC packaging technology. Every 10 years since the 1970s, packaging technology has undergone a technological revolution. The first decade of this century is the era of the 3D system in package (3D-SiP), and work has begun to develop new 3D technology termed through-Si via (TSV) that will define the present decade [5]. In TSV, the electrode passes completely through the silicon wafer (or chip). It represents the fusion of silicon wafer process technology (front end of line, FEOL) and semiconductor packaging technology (assembly/packaging).

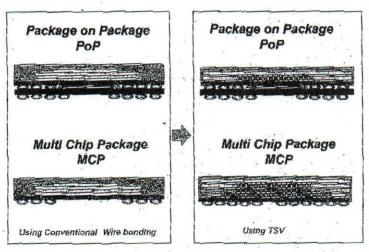

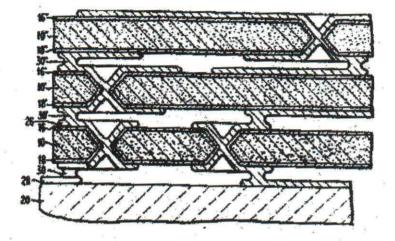

3D integration using conventional technologies, such as with the wire bonding (WB) as shown in Fig. 1.3 (left), is referred to as 3D integration packaging technologies. In this book, we focus our attention on systems in which semiconductor chips are stacked and connected by TSV, as shown in Fig. 1.3 (right), which

Fig. 1.3 3D integration packaging technology and 3D integration technology [6]

define 3D integration technology [6]. We do not discuss 3D integrated circuits (3D-IC) that use FEOL, such as 3D NAND in which transistors are stacked, nor the Intel tri-gate transistors that were introduced in the 22-nm generation ivy bridge CPU.

## 1.2 Motivation for 3D Integration Technology

The development impetus is accounted for in the following two points.

- If semiconductor integrated circuit chips are connected using TSV, the interconnected distance is approximately 1/1000 of that using conventional WB (micrometers compared with millimeters). This results in dramatic reductions in electric resistance and capacitance, making possible high-speed operation and low power consumption.

- 2. It is difficult to make (wire) connections between the conventional packages on the mounting board on the order of thousands, but this task is straightforward, and on even grander scales, between Si chips using TSV. Thus, TSV-based systems that have several 1000 input/output (I/O) circuits are realizable, which also benefit from being lower power consumption devices with higher data transmission speeds.

3D integration need not be confined to like technologies. By combining semiconductor integrated circuits with, for example, micro-electro-mechanical systems (MEMS) devices, unique functionalities can be developed in what is termed heterogeneous 3D integration technology.

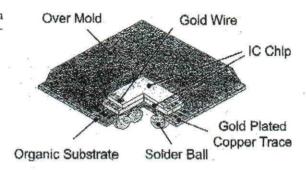

Fig. 1.4 Typical construction of S-CSP (MCP). IC integrated circuit

# 1.3 Research and Development History of 3D Integration Technology

# 1.3.1 3D Packaging Technology

Even as of 2015, the use of 3D-IC (TSV) is uncommon, with the exception of complementary metal-oxide-semiconductor imaging sensors (CIS). However, high-volume manufacturing of 3D integration packaging technology using WB continues.

In 1998, Sharp Corporation developed the world's first stacked two-chip chipscale package (CSP) using WB [7]. Before that time, there was no notion of chip stacking in CSP. This led to its development for use in mobile phones, mostly by Japanese chip makers, such as Sharp; Mitsubishi, Hitachi, NEC, Toshiba, and Fujitsu. This technology was called stacked chip-scale (size) package (S-CSP) or multichip package (MCP). Figure 1.4 shows the typical construction of S-CSP (MCP).

S-CSP/MCP was first used to make combinations of NOR flash memory and of static random-access memory (SRAM), which are at the heart of all mobile phones. Consumer demand fuelled the development of smaller sizes and higher performance [8]. When Sharp developed the world's first stacked CSP, the combination memory development race was called the "East versus West War" over standardization by the Joint Electron Device Engineering Council. It became a demonstration of the strength of Japanese packaging technology.

Although, in the beginning, the interconnect technology was only WB, CSP stacking has given rise to the package on package (PoP) model, which also uses flip chip (FC) technology. Today, this approach is integral to modern smart phones and tablets; dynamic random access memory (DRAM) and application and/or baseband processors are stacked together using this technology. Upon these foundations, newer technologies continue to drive advances in telecommunications, such as through mold via (TMV) [9, 10]; see Fig. 1.5.

In the present-day flash memory, there are more than eight chips stacked into a single package [11]; see, for example, Fig. 1.6. This technology will likely continue being a mainstay of 3D integration packaging technology for some time yet. On the horizon are wireless interconnect technologies, such as capacitive and inductive 3D coupling [12].

Fig. 1.5 3D integration packaging technology transition [10]. (With permission from Amkor Technology, Inc., Chandler AZ). WB wire bonding, PoP package on package, FC flip chip, TMV through-mold via, TSV through-Si via

Fig. 1.6 World's first ninechip stacked memory. (With permission from Toshiba Corporation)

# 1.3.2 Origin of the TSV Concept

The underlying concept of TSV technology is not new. International Business Machines Corporation filed the patent USP3,648,131 entitled, "Hourglass-shaped conductive connection through semiconductor structures" in November 1969, with the following abstract [13]:

Fig. 1.7 US Patent 3,648,131 A [13]

"An integrated semiconductor structure including the fabrication thereof, and more particularly, an improved means for interconnecting the two planar surfaces of a semiconductor wafer. To provide the electrically conductive interconnections through the wafer, a hole is etched, insulated, and metallized. Active or passive devices may be formed on either or both sides of the wafer and connected to a substrate by solder pads without the use of beam leads or flying lead bonding." The drawings are shown in Fig. 1.7.

# 3D Projects in Tohoku Univ. (Koyanagi Group)

Fig. 1.8 Extracts from presentations by Tohoku University researchers in 1989 [14] and 1991 [15]. (With permission from Tohoku University, Japan). TSV through-Si via, LSI wafer large-scale integration wafer

Later on, patents JP (S59)1984-22954 (June 1, 1983) and patent JP (S61)1986-88546 (October 5, 1984) were filed by Hitachi Ltd. and Fujitsu Ltd, respectively. The patent JP (S63)1988-156348 (December 19, 1986), by Fujitsu, describes a stacked chip structure. Figure 1.8 shows key schematics of chip stacking techniques sourced from 1989 and 1991 conference presentations by Tohoku University, Japan [14, 15].

# 1.3.3 Research and Development History of 3D Technology in Organizations

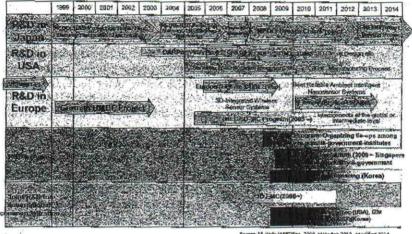

Research and development of 3D integration technologies has been carried out through global efforts [16]. Some of the major contributions by region are summarized in Fig. 1.9 [17].

# History of WW R&D on 3D Integration/Interconnect Technology

Source: Mr. Kida (456) (Map. July), Materiac July, Modified July

Fig. 1.9 History of global research and development on 3D integration technology. (Adapted from Ref. [16]). NEDO New Energy and Industrial Technology Development Organization, DARPA Defense Advanced Research Projects Agency, VISA vertically interconnected sensor arrays, AD-STAC Advanced Stacked-System Technology and Application Consortium, TSV through-silicon via, ASSM All Silicon System Module, EMC Equipment and Materials Consortium, SiC stacked integrated circuit, German BMFT German Ministry of Research, BMBF Federal Ministry of Education and Research, FP7 Seventh Framework Programme

#### 1.3.3.1 Japan

In Japan, research and development of the "Three-Dimensional Circuit Element R&D Project" by the Research and Development Association for Future (New) Electron Devices was conducted from 1981 to 1990, and the technology developed was termed "Cumulatively Bonded IC" (CUBIC): (in Japanese); TSV was not integral to the design. A thin film (approximately 2-µm thick) of electron channel metal-oxide-semiconductor field-effect transistor (nMOSFET) was laminated onto the bulk silicon device. The electrical interconnection of 1600 wiring contact arrays was checked, and the contact volume resistance of  $5\times10^{-6}\,\Omega\cdot\text{cm}^2$  did not adversely affect the operation [18].

In Japan, the Association of Super-Advanced Electronics Technologies (ASET) carried out a research and development project of 3D integration technology using TSV during the 5-year period 1999–2003. The project was entitled, "R&D on High Density Electronic System Integration Technology" (in Japanese). Its execution was entrusted to the New Energy and Industrial Technology Development Organization (NEDO) organization of the Japanese government's Ministry of Economy, Trade, and Industry (METI) [19]. Following on were the "Stacked Memory Chip

M. Kada

Technology Development Project" (in Japanese), 2004–2006 [20] and the "Development on Functionally Innovative 3D-Integrated Circuit (Dream Chip) Technology Project" (in Japanese), 2008–2012. In 2010, research was conducted with a focus on "Design Environmental Technology, Interposer Technology, Chip-Testing Technology, Three-dimensional Integration Basic Technology, Flex chip (FPGA) Technology, and RF MEMS."

The majority of the semiconductor-related businesses in Japan were involved in these projects. These included semiconductor companies Elpida, Toshiba, Renesas, and Rohm; electronic companies NEC, Sharp, Nac Image Tech., IBM, Panasonic, Hitachi, and Fujitsu; and material/equipment companies Advantest, DNP, Ibiden, Shinko, TEL, Toppan, Yamaichi, and Zycube, Furthermore, The University of Tokyo, Tohoku University, and the National Institute of Advanced Industrial Science and Technology represented the academic participation [21–23].

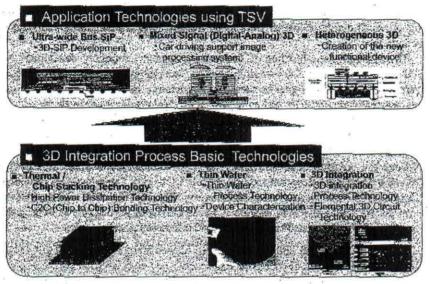

In 2010, an interim assessment led to a focus shift to thermal management/chip stacking technology, thin wafer technology, 3D integration technology, ultra-wide bus 3D-SiP, mixed signal (digital-analog) 3D integration technology, and heterogeneous 3D integration technology. The research outcomes are described in later sections of this book [24, 25].

However, despite the sizeable investment by the Japanese government over these long periods of time, the national semiconductor industry is presently in decline and future research and development remains uncertain.

The WOW alliance based at the Tokyo Institute of Technology (based at The University of Tokyo until 2014) was founded in 2008 [26], and the "Three-Dimensional Semiconductor Investigation Center" (translated from the Japanese) in Kyushu commenced operations in 2011 [27].

## 1.3.3.2 Japanese 3D Integration Technology Research and Development Project (Dream Chip)

The second full-scale national research and development (R&D) initiative of 3D integration technology using through-silicon via (TSV) was implemented over the 5-year period from 2008 to 2012. Super-Advanced Electronics Technologies (ASET) conducted the project "Development on Functionally Innovative 3D-Integrated Circuit (Dream Chip) Technology Project," and it was managed by the NEDO Organization that is based on "IT innovation Program" of Japanese government's Ministry of Economy, Trade and Industry (METI). After the 2010 interim assessment, the two focus areas became 3D integration process basic technologies and application technologies using TSV. The former consisted of thermal management/chip-stacking technology, thin wafer technology, and 3D integration technology, while the latter focus area comprised ultra-wide bus 3D-SiP, mixed signal (digital-analog) 3D, and heterogeneous 3D; see Fig. 1.10. For details beyond research and development subjects and results, the reader is referred to Chapter 9 [17, 28].

Fig. 1.10 Research and development subject of the Droam Chip Project, (With permission from the Electrochemical Society: ECS) [17]. TSV through-Si via

#### 1.3.3.3 The USA

The US Defense Advanced Research Projects Agency (DARPA)'s work in microsystems technology has a long history. 3D-related research and development projects are controlled by the "Microsystems Technology Office (MTO)." These projects are:

- 1. Enhanced Digital (3D-IC Program)

- Large amounts of bache memory

- High memory bandwidth

- Enhanced Analog (COSMOS Program)

- Heterogeneous integration

- Disparate process technologies (e.g., SiGe/Si, C.S./Si, SOI/Bulk)

- 3. Smart Focal Planes (Vertically Interconnected Sensor Arrays, VIŞA Program)

- Processing at each pixel

- High fill factors

- 4. Photonics (EPIC Program)

- Optical and electronic tiers

DARPA funding and the Microelectronics Center of North Carolina Research and Development Institute (MCNC-RDI) supported a project that was started in 2003. The research and development device comprised VISA that implemented highly 12 M. Kada

parallel and densely interconnected architectures with micron-sized vias penetrating stacks of detectors, which were made from analog, digital, and mixed signal circuits.

The Massachusetts Institute of Technology Lincoln Laboratory developed "A SOI-Based Wafer-scale 3-D Circuit Integration Technology." Integral to this project were precision wafer aligner-bonder, low temperature oxide—oxide bonding, and concentric 3D via, all 3D-enabling technologies. Major milestones were the delivery of the 3DL1, 3DM2, and 3DM3 chips in April 2006, and November 2007 and 2010, respectively. Participants of the 3DM3 chip project were from universities, commercial laboratories, and the business sector.

They are Arizona State University (ASU), North Carolina State University (NCSU), The Naval Research Laboratory (NRL), the US Department of Defense (DoD), Fermi National Accelerator Laboratory, IBM, The State University of New York (SUNY), MIT Lincoln Laboratory, and so on. As for third 3D-IC Multiproject Run (3DM3)3D Circuits, 39 designs were submitted as follows:

3D Circuits Anti-tamper authentication chip, stacked memory (SRAM & DRAM), stacked microprocessor, hi-speed transmit/receive, one-chip GPS, network-on-chip, reconfigurable neural network, SAR processor elements, RF-switching power converter, power management for 3D-IC's, Integrated RF MEMS, implantable biosensors, and bio lab on chip.

3D Imaging Applications International Linear Collider (ILC) pixel readout, low-power pattern recognition 3D vision chip, multi-core processor with image recognition, focal plane image processor, and sub-1-sized pixel imaging array

3D Technology Characterization 3D radiation test structures, jitter-clock skew-propagation delay, hi-speed I/O, RF building block, meta-material inductors, and stacked MOSFET.

3D design software were also developed by PTC, NTSU, R3Logic, and the University of Minnesota (UMN) [29-32].

Following are the overview of press releases by International SEMATEC from 2004 to 2006. "June 10, 2004 they released its several top technical challenges for 2005, one of several top technical challenges was 3-D interconnect on the list for the first time" [33]. "Then aiming to expand the range of potential solutions to the challenges of continued CMOS scaling, they launched a project to explore the feasibility of 3D interconnect technology for the semiconductor industry, in February 9, 2006" [34]. Also, "December 13, 2010, SEMATECH, the Semiconductor Industry Association (SIA), and Semiconductor Research Corporation (SRC) announced they had established a new 3D Enablement program to drive cohesive industry standardization efforts and technical specifications for heterogeneous 3D integration" [35].

In September 13, 2011, members of SEMATEC were Hynix, IBM, Intel, Samsung, ADI, and ON Semiconductor as the IDMS. As for foundries, Global Foundries, TSMC, and UMC. As for Fabless, HP, Altera, LSI, and Qualcomm. As for

OSATs, ASE. As for Suppliers Atotech, COSAR, NEXX, TEL, R&D Partners, CNSE/FRMC, NIST, and SRC [36].

## 1.3.3.4 Europe

In Europe, 3D integration technology research has a long history, which was reviewed in the welcome presentation at the IEEE 3D System Integration Conference 2010 (3D-IC) in Munich, November 16–18 [37].

Siemens, AEG, Philips, and Fraunhofer IFT formed the 1987-1989 consortium for developing 3D integration technology. From the 1980s through to the early 2000s, projects were supported by the German Ministry of Research (German BMFT) and the Federal Ministry of Education and Research (BMBF). Subsequent projects were supported by the European Committee. From 2006 to 2009, the European ICT Project "e-CUBES (6th European Framework ICT)—3D-Integrated Wireless Sensor Systems, Technology Platform for 3D Heterogeneous Integration" was conducted. They said four optimized 3D integration technologies were successfully used in the development of three e-CUBES application demonstrators: thin-chip-integration technology (TCI/UTCS) for Philips' Health & Fitness demonstrator, TSV technology ICV-SLID, HoViGo for Infineon's Automotive demonstrator (TPMS) and Package-in-Package technology HiPPiP for Thales' Aeronautic demonstrator [38, 39].

And the latest was the Seventh Framework Programme (FP7: 2007-2013) of the European Union for research, technological R&D, and demonstration activities. "e-BRAINS"—Best Reliable Ambient Intelligent Nanosensor Systems for developing 3D Heterogeneous System Integration.

The project members were Infineon, Fraunhoer, Siemens, SINTEF, sensonor, imec, SORIN Group, CEA, IQE, FPFL, 3D plus, Tyndall, DMCE, TU, Vermon, ITE, MaganaDiagnositics, TECHNICHE UNIVERSITAT CHEMNITZ, and eesyid. Applications are smart biosensor grain, Infrared imager, active medical implant, air quality system, and smart ultra-sound imaging probe [40, 41]. Following are the overview of press releases by IMEC from 2005 and CEA-Leti from 2011.

July 2005, "IMEC announced that IMEC launched advanced Packaging and Interconnect Center (APIC) and started to develop 3D Stacked IC "3D-SIC." APIC grouped more than 30 partners worldwide including integrated device manufacturers (IDMs), system houses, packaging, assembly and test houses and so on. The programs were based on interconnects at the global or intermediate level of the chip wiring hierarchy." [42].

Then "IMEC developed another R&D subject "3D-WLP," wafer level packaging, and "3D-SIP," traditional packaging interconnect technology. These were the part of IMEC's Industrial Affiliation Program (HAP) on advanced interconnect technology for future technology node" [43].

14 M. Kada

And, "Qualcomm announced to participate in IMEC's industrial affiliation program (IIAP) on 3D-integration 2008 and also extends 3D research agreement with Qualcomm focusing on advanced technologies and devices 2011 [44, 45].

Also, "IMEC and TSMC announced 2009 that they have forged an Innovation Incubation Alliance to create a platform enabling the R&D of innovative product solutions using emerging More-than-Moore technology options [46].

Partners of IMEC 3D System Integration Program in 2011, were for Logic IDM, Panasonic, Intel, Fujitsu, Sony, As for Memory IDM Micorn, As for foundries TSMC, GlobalFanundries. As for fabless Quacomm, Xilinx, Nvidea, Altera. As for OSAT Amkor UTAC. As for EDA Synopsys, Acdaxe, Atrenta. As for Material suppliers Hitachi Chemical, ThinMaterials, Henkel, BASF. As for Equipment Suppliers Applied Material, Lam, TEL, Suss Screen, Ultratec, CascadeMicortech, Disco, Nanda Tech PVA Tepla, Smart Equipment Technology (Set) [47].

Followings are the announcement of CEA-Leti. "January 2011, they significantly expand its technology offering this month when it ramps up one of Europe's first 300 mm lines dedicated to 3D-integration applications." [48].

And "CEA-Leti announced January 2012 that the launch of a major new platform that provides industrial and academic partners with a global offer of mature 3D innovative technologies for their advanced products and research projects" [49].

#### 1.3.3.5 Asia

The research and development project entitled, "Advanced Stacked-System Technology and Application Consortium" (Ad-STAC), centering on ITRI, has been supported by the Taiwanese government since 2008. The initial announcement was as follows:

"Formed on July 23, 2008, Ad-STAC provides a unique platform for both technical exchanges and information sharing among the partners distributed worldwide." "The purpose of Ad-STAC is to unify companies in different field but not limited academia, government industries, and institute, to co-operate and improve the 3D IC technology [50].

Members were 22 companies in October 2010. Applied Materials Inc of Taiwan, Atotech, Deutschland GmbH, Brewer Science Inc., Cadence Design Systems, Inc. Graduate School of Engineering, the University of Tokyo, Hernes Epitek Corp., SUSS MicroTec AG., Tazmo Co., Ltd, Unimicron Corporation, IV Technologies, Air Products, GPT, Disco, ASE, Leading Precision, Dupont, BASF, SPTS, UMC, SPIL, Cabot Microelectronics, and Cisco.

The full 300 mm line for 3D development was installed by the end of 2009 [51]. In South Korea, there has been speculation of a national project led by Hynix and Amkor but details presently remain confidential [52].

The Institute of Microelectronics (IME) Agency for Science, Technology, and Research (A\*STAR) has been active since 2011. They announced, "Dec 6, 2011, IME and Tezzaron Semiconductor announced a research collaboration agreement to develop and exploit advanced Through Silicon Interposer (TSI) technology" [53].

June 5, 2012-IME and United Microelectronics Corporation agreed to develop Through-Silicon Via (TSV) technology for backside illuminated CMOS image sensors (CIS). [54] Aug 17, 2012-IME and Huawei Technologies, signed MOU to develop and advance Through Silicon Interposer (TSI) technology. The two organizations will collaborate on advanced packaging with TSI, 2.5D/3D-IC research and development, and demonstrate heterogeneous 2.5D design and manufacturing flow. [55]

#### 1.3.3.6 International

Press releases of international 3D integration technology research and development consortia are as follows:

"Semiconductor 3D Equipment and Materials Consortium (EMC-3D) is a new consortium created to address the technical and cost issues of creating 3D interconnects using TSV technology for chip stacking and MEMS/sensors packaging. Equipment companies initiating the consortium are Alcatel, EV Group, Semitool and XSiL. Associate research members include Fraunhofer IZM, SAIT (Samsung Advanced Institute of Technology), KAIST (Korea Advanced Institute of Science and Technology) and TAMU (Texas A&M University). Material members include Rohm and Haas, Honeywell, Enthone, and AZ with wafer service support from Isonics [56].

Another international consortium's announcement was as follows; "The Microsystems Packaging Research Center (PRC) at Georgia Tech, in partnership with Fraunhofer IZM (Germany) and the Korea Advanced Institute of Science and Technology (KAIST) launched a global industry consortium titled "3D All Silicon System Module (3DASSM)" in October, 2008 [57].

# 1.4 Research and Development History of 3D Integration Technology for Applications

## 1.4.1 CMOS Image Sensor and MEMS

Toshiba, Aptina, STMicroelectronics, and several other companies commercialized the complementary metal-oxide-semiconductor (CMOS) image sensor during 2007-2008, which used TSV as the target electrode formation technology. The advantage of using TSV was its compactness, permitting the design of miniature devices.

Toshiba named the new application of penetration electrode technology "Through Chip Via" (TCV). This space-saving technology made it possible to mount an assembly of camera module components in a wafer state. For example, the conventional substrates and wire bonding spaces were reduced by forming a solder ball in the back side of the chip.

16 M; Kada

STMicroelectronics' multi-chip MEMS devices, such as smart sensors and multi-axis inertial modules, enable a higher level of functional integration and performance in a smaller form factor [58–60].

#### 1.4.2 DRAM

DRAM is anticipated to be the principle application driving volume manufacturing of full-scale 3D integration technology.

In June 2011, Elpida Memory shipped the world's first 8 GB DRAM sample. It consisted of four 2 GB (double data rate type 3; DDR3) modules stacked using TSV technology [61]. Then in August of the same year, Samsung Electronics announced that they had developed 30-nm-class 32 GB Green DDR3 DRAM using TSV package technology for next-generation servers [62].

Hynix became a member of SEMATECH's 3D Interconnect program at the College of Nanoscale Science and Engineering (CNSE) of the University at Albany [63].

Smart phone and tablet SoCs have reached impressive levels of performance in the past few years. However, limited memory bandwidth has become a bottleneck for further advancements, and the continued growth of the display resolution only exacerbates this problem. Despite their size difference, tablets have now overtaken laptop computers in display resolution.

JEDEC Solid State Technology Association, the global leader in the development of standards for the microelectronics industry, announced the availability of a new standard for wide I/O mobile DRAM: JESD229 Wide I/O Single Data Rate (SDR). They said "Widely anticipated by the industry, Wide I/O mobile DRAM is a breakthrough technology that will meet industry demands for increased levels of integration as well as improved bandwidth, latency, power, weight and form factor; providing the ultimate in performance, energy efficiency and small size for smartphones, tablets, handheld gaming consoles and other mobile devices." JESD229 using TSV was standardized in December 2011 in JEDEC [64, 65].

However, wide I/O memory, which has a bandwidth of 12.8 GB/s for mobile applications, has not been adopted because of the significant improvements of classical DDR memory. It is now possible to achieve the desired bandwidth using more traditional 2D-IC integration in both PC/server and mobile DRAM applications. JEDEC more recently moved to standardize Wide I/O2

One of the primary challenges facing DRAM engineers is the memory bandwidth required by high-performance computers and next-generation networking equipment. Conventional DDR is not suitable for these architectures. To address these needs, in October 2011, Samsung Electronics and Micron Technology announced a collaboration to implement as an open interface the Hybrid Memory Cube (HMC). They said "The Hybrid Memory Cube Consortium (HMCC) will work closely with fellow developers Altera, IBM (added by another announcement), Open-Silicon and Xilinx to collectively accelerate industry efforts in bringing to market a broad set of technologies. The consortium will initially define a specification to enable

applications ranging from large-scale networking to industrial products and high-performance computing."

Then, in May 2012, HMCC announced that Microsoft Corp. has joined the consortium and in June 2012, they also announced that new members ARM, HP, and SK hynix, Inc. have joined the global effort to accelerate widespread industry adoption of HMC technology.

In August 2012, they aunounced that its developer members have released the initial draft of the HMC interface specification to a rapidly growing number of industry adopters [66–70].

# 1.4.3 2.5D with Interposer

The technology of mounting IC chips side by side, using a Si Interposer, rather than 3D stacking with TSV, has gained popularity. Because the Si interposer is technically a silicon chip with the wiring layer only, the IC is also referred to as being 2.5 dimensional.

Xilinx announcement in October 2010 for 2.5D is as follows. "The industry's first stacked silicon interconnect technology for delivering breakthrough capacity, bandwidth and power savings using multiple FPGA die in a single package for applications that require high-transistor and logic density, as well as tremendous levels of computational and bandwidth performance" [71, 72].

Then, just 1 year later, in 2011, Xilinx announced the progression. "First shipments of its Virtex®-72000T Field Programmable Gate Array (FPGA), the world's highest-capacity programmable logic device built using 6.8 billion transistors, providing customers access to an unprecedented 2 million logic cells, equivalent to 20 million ASIC gates, for system integration, ASIC replacement, and ASIC prototyping and emulation." [73].

One and a half years later, the competition started. Taiwan Semiconductor Manufacturing Co. Ltd. (TSMC) and Altera Corp., on March 22, 2012, announced "The joint development of a heterogeneous 3-D IC test vehicle using TSMC's chip-on-wafer-on-substrate (CoWoS) integration process. TSMC said the technology is an integrated process technology that attaches device silicon chips to a wafer through a chip-on-wafer bonding process [74].

## 1.4.4 Others

Many other semiconductor companies, such as IBM [75] and Qualcomm [76], have also been developing 3D integration technology.

In September 2006, Intel announced at their developer forum, the promise of an 80-core chip within 5 years based on the innovation of connecting memory directly to processor cores. They also showcased TSV alongside the 80-core chip prototypes, which piggybacked 256 MB of SRAM directly to each chip's 80 cores [77].

But, in June 2010, they said as follows. "There are several problems with TSV technology: Lack of EDA design tools; complexity of designs; integration of

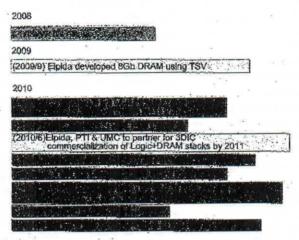

Fig. 1.11 Worldwide research and development activities in 2008–2010. DRAM dynamic random access memory, TSV through-silicone via, TSMC Taiwan Semiconductor Manufacturing Co. Ltd, AD-STAC Advanced Stacked-System Technology and Application Consortium, UMC United Microelectronics Corporation, MPW multi-project wafer, MOSIS metal—exide-silicon implementation service, CMP circuits multi-projects, SEMI semiconductor equipment and materials international, I/O input/output

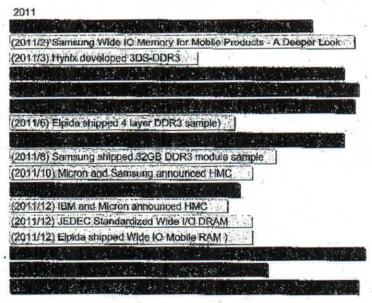

Fig. 1.12 Worldwide research and development activities in 2011. DDR3 double data rate type 3, CNSE College of Nanoscale Science and Engineering, 3D-IC three-dimensional integrated circuit, MOSIS metal-oxide-silicon implementation service, DRAM dynamic random access memory, TSV through-silicone via, HMC hybrid memory cube, FPGA field-programmable gate array, I/O input/output, RAM random access memory, SoC system on chip, TSMC Taiwan Semiconductor Manufacturing Co. Ltd, TSI through silicon interposer, A\*STAR Agency for Science, Technology, and Research

Fig. 1.13 Worldwide research and development activities in 2012, BIS back-illuminated sensor, CIS complementary metal—oxide—semiconductor imaging sensors, TSMC Taiwan Semiconductor Manufacturing Co. Ltd., JEITA Iapan Electronics and Information Technology Industries Association, TSV through-silicone via, FPGA field-programmable gate array, A\*STAR Agency for Science, Technology, and Research, UMC United Microelectronics Corporation, SIP system in package

assembly and test; cost; and lack of standards. As previously reported, Intel Corp. is still searching for an application for TSVs. It does not make sense for Intel to go to 3D with CPU cache memory" [78].

A summary of worldwide research and development activities from 2008 to 2012 are shown in Figs. 1.11, 1.12, and 1.13.

The 3D integration technology using TSV has not yet reached high-volume manufacturing despite the sizeable global investment in research and development. There are several reasons for this. Standardization is difficult because of the diversity of architectures, such as Via Size and TSV, process order, for example, Via First/Last/Front/Back, and issues with the supply chain for high-volume manufacturing and high component costs.

However, the 3D integration technology in which TSV is used and the arguments surrounding its application and forecasted use is actively being discussed.

## References

- 1. Moore GE (1965) Cramming more components onto integrated circuits. Electronics 38(8):19

- Dennard RH et al (1974) Design of ion-implanted MOSFETs with very small physical dimension. IEEE J Solid-State Circuits 9(5):256–268.

- International Technology Roadmap for Semiconductors 2007 Edition, Executive Summary Interconnect

- 4. Garrou P (2007) Perspectives from the leading edge. The SIA meeting in NYC, mid Sept

- 5. Kada M (2005) Presentation slide toward the 3D-SiP era. SEMICON Japan

- Kada M (2012) Presentation slide 3D-integrated circuits technologies—the history and future. ISSM Tokyo

- Kada M (1999) Stacked CSP/a solution for system LSI. Chip Scale International Technical Symposium Semicon West, B1-B7, Sept13

- Kada M, Smith L (2000) Advancements in Stacked Chip Scale Packaging (S-CSP), provides system-in-a-package functionality for wireless and handheld applications. Pan Pacific Microelectronics Symposium Conference, Jan. http://www.eet.bme.hu/~benedek/CAD\_Methodology/Courses/packaging/PanPacific\_StackedCSP\_RevG1.pdf, Accessed 9 July 2014

- Chen M et al (2011) Presentation slide TI OMAP4xxx POP SMT design guideline. http:// www.ti.com/pdfs/wibu/SWPA182C.pdf. Accessed 8 July 2014

- Yoshida A (2013) Presentation slide bump & ball interconnect technology update. ICSJ 2013 Nov

- Akejima S (2007) Hi-density flash memory packaging technology. J Jpn Inst Electron Packag 10(5):375-379 (in Japanese), https://www.jstage.jst.go.jp/article/jiep1998/10/5/10\_5\_375/ pdf. Accessed 8 July 2014

- Niitsu K, Kuroda T (2010) An inductive-coupling inter-chip link for high-performance and low-power 3D system integration. Solid-State Circuits Technologies, ISBN: 978-953-307-045-2, INTECH, pp 281-306, Jan

- International Business Machines Corporation (1969) US Patent US3648131 Hourglassshaped conductive connection through semiconductor structures. Filed: Nov 7 1969

- 14. Fukushima T et al (2007) Presentation slide thermal issues of 3D ICs (M. Koyanagi, Proceeding of 8th symposium on future electron devices, pp 50–60 Oct 1989). http://www.sematech.org/meetings/archives/3d/8334/pres/Pukushima.pdf. Accessed 12 July 2014

- Fukushima T et al (2007) Presentation slide thermal issues of 3D ICs (M. Koyanagi, Proc. 8th symposium on future electron devices, pp 50-60 Oct 1989). http://www.sematech.org/meetings/archives/3d/8334/pres/Fukushima.pdf. Accessed 12 July 2014

- 16. Kada M (2010) Prospect for development on 3D-integration technology and development of functionally innovative 3d-integrated circuit (dream chip) technology. 16th symposium on microjoining and assembly technology in electronics, P5-P12, Feb, (in Japanese)

- Kada M (2014) R&D overview of 3D integration technology using TSV worldwide and in Japan. 2014 ECS and SMEQ joint international meeting (Oct 5-10)

- Research & Development Association for Future Electron Devices (FED) Overview Report of R&D Result Spillover Effects and Prospect 3D Circuit Element R&D Project. 1981F-1990F (in Japanese)

- Electronics and Information Technology Development Department (2004) Super high density electronic system integration technology. NEDO report of project assessment, Sept. 30 (in Japanese)

- NEDO Assessment Committee (2008) Stacked memory chip technology development project report of after project. Assessment Feb (in Japanese). http://www.nedo.go.jp/content/100096542.pdf, Accessed 25 June 2014

- Kada M (2009) Development on functionally innovative 3D-integrated circuit (dream chip) technology. 3D system integration conference

- Kada M (2009) Highly performance TSV is pursued towards "dream chip", simulator, peripheral technology, such as proving technology, are also developed. The semiconductor technology yearbook, Nikkei BP (in Japanese).

- ASET (2009) R&D result of "dream chip project" ASET annual symposium 2010 (in Japanose)

- NEDO R&D Assessment Committee (2010) Dream chip development project, report of interim project assessment, Nov (in Japanese). http://www.nedo.go.jp/content/100140983.pdf. Accessed 25 June 2014

- NEDO R&D Assessment Committee (2013) Dream chip development project. Report of after project assessment Nov. (in Japanese). http://www.nedo.go.jp/content/100545199.pdf. Accessed 25 June 2014

- 26. Electronic Journal (2009) Sept, pp 28-29 (in Japanese)

- 27. Home Page Research Center for Three Dimensional Semiconductors (2014) (in Japanese), http://www.tl.fukuoka-u.ac.jp/~tomokage/3dcenter/toppage,html, Accessed 22 April 2014

- ASET (2013) Presentation slide dream-chip project by ASET (final result). March 8, http://aset.la.coocan.jp/english/e-keukyu/Dream\_Chip\_Pj\_Final-Results\_ASET.pdf. Accessed 12 July 2014

- Fritze M et al (2007) Presentation slide thermal challenges in DARPA's 3DIC Portfolio, Sematech workshop on "Thermal & Design Issues in 3D IC's" Albany, NY, Oct 11-12. http://www.sematech.org/meetings/archives/3d/8334/pres/Fritze-Steer.pdf. Accessed 19 July 2014

- DA3RPA (2002) Fiscal Year (FY) 2003 budget estimates Feb pp 184–185, p 193, http://www.darpa.mii/WorkArca/DownloadAsset.aspx?id=1636. Accessed 22 April 2014

- 31. Research and Development Services in Support of the DARPA VISA Program Solicitation Number; DON-SNOTE-050228-001Agency: Department of the Navy Office: Space and Naval Warfare Systems Command Location: SPAWAR Systems Center Pacific (2005) Federal Business Opportunities, Research and Development Services in Support of the DARPA VISA Program. https://www.fbo.gov/index?s=opportunity&mode=form&tab=core&id=d0e6ddf71 bfc03e9095d3b7b276d21b7. Accessed 3 March 2014

- Keast C et al (2009) Presentation slide A SOI-based wafer-scale 3-D circuit integration techuology. 3D architectures for semiconductor integration and packaging, Dec 11

- Sematech (2004) Press release international SEMATECH identifies top technical challenges for 2005. http://www.sematech.org/corporate/news/releases/20040610a.htm. Accessed 17 April 2014

- Sematech (2006) Press release SEMATECH launches 3D project to probe options for advanced interconnect. http://www.sematech.org/corporate/news/releases/20060209htm. Accessed 17 April 2014

- Somatech (2010) Press release new 3D enablement program launched by SEMATECH, SIA and SRC. http://www.azonano.com/news.aspx?newsID=20908. Accessed 17 April 2014

- Arkalgud S (2011) Presentation slide 3D interconnects 3D enablement center. Annual SE-MATECH symposium Hsinchu, Sept 13. http://www.scmatech.org/meetings/archives/symposia/10187/Session2/01Arkalgudl.pdf. Accessed 11 July 2014

- Ramm P et al (2010) Presentation slide, welcome to the IEEE international 3D system integration conference (3DIC). Munich, Nov 16–18

- Ramin P et al (2010) The European 3D technology platform (e-CUBES). IMAPS, http://www.sintef-norge.com/upload/IKT/9031/Ramm%20IMAPS%20Device%20Packaging%202010.

pdf. Accessed 13 July 2014

- Lietaer N et al (2009) Presentation slide 3D integration technologies for miniaturized tire pressure monitor system (TPMS). Lietaer09—IMAPS symposium Foredrage, http://sintef. org/upload/IKT/9031/Lietaer09%20-%20IMAPS%20Symposium%202009%20Foredrag pdf. Accessed 25 June 2014

- 40. Ramin P et al (2013) Presentation slide the e-BRAINS project, ESSDERC/ESSCIRC, Bucharest Romania workshop: In the quest for zero power: enabling smart autonomous system applications. http://www.e-brains.org/data/events/uploads/Peter\_Ramm\_The\_e-BRAINS\_Project\_ESSDERC\_2013\_WS\_in\_The\_Quest\_For\_Zero\_Power.pdf, Accessed 13\_July\_2014

- 41. http://www.e-brains.org/project/rtd/. Accessed 26 April 2014

- IMEC (2005) Press release IMEC packaging research center attracts 30 companies, www. embedded.com/print/4054184. Accessed 2 March 2014

- IMEC (2008) Brochure 3D @ IMEC, http://www2.imec.be/content/user/File/3D\_brochure.pdf. Accessed 13 July 2014

- Qualcomm (2008) Press release Qualcomm and IMEC collaborate on 3D integration research. http://www.on-c114.net/577/a330029.html. Accessed 2 March 2014

- 45. IMEC (2011) Press release IMEC extends 3D research agreement with Qualcomm focusing on advanced technologies and devices. http://www2.imec.be/be\_en/press/imec-news/imecqualcomminsite.html. Accessed 2 March 2014

- 46. TSMC and IMEC (2009) Press release TSMC and IMEC join forces to bring novel technology solutions to emerging markets. http://www.leuveninc.com/event/36/784/TSMC\_and\_IMEC\_join\_forces\_to\_bring\_novel\_technology\_solutions\_to\_emergin/. Accessed March 2, 2014

- Heyne E (2011) Presentation slide 3D system integration technology, convergence. Semicon Europe, Messe Dresden, Germany, Oct 10–13, http://semicurope.onnibooksonline.com/2011/ semicon\_europa/SEMI\_TechARENA\_presentations/3DICsession\_02\_Eric.Beyne\_IMEC. pdf. Accessed 14 July 2014

- CEA Leti (2011) Press release CEA-Leti Ramps up 300 mm line dedicated to 3D-integration applications. Accessed 18 Apr 2014

- CEA Leti (2012) Press release CEA-Leti launches open 3D™ initiative. Accessed 18 April 2014

- 50. Ad-stac HP, http://ad-stac.itri.org.tw/memb/index\_c.aspx, Accessed 26 April 2014.

- Tsai MJ (2011) Presentation slide overview of TTRI's TSV Technology, 2011-06-22, http://www.sematech.org/meetings/archives/symposia/9237/Session%205%203D%20interconnect/1%20MJ Tsai ITRI.pdf. Accessed 9 July 2014

- Kim G (2009) Presentation slide TSV based 3D technologies in Korea, TSV technology conference, NIKKEI MICRODEVICES, 2009-04-16

- A\*STAR (2011) Press release A \*STAR Institute of Microelectronics and Tezzaron Team Up to Develop 2.5D3D through-silicon interposer technology, http://www.bizwireexpress.com/ showstoryACN.php?storyid=26505538. Accessed 26 April 2014

- 54. A\*STAR (2012) Press release A-STAR institute of microelectronics and UMC to develop TSV technology for BSI image sensor used in mobile applications. http://www.advfn.com/ news\_A-STAR-Institute-of-Microelectronics-and-UMC-to-De\_52659319.html. Accessed 26 April 2014

- A\*STAR (2012) Press release A\*STAT of microelectronics and Huawei announced joint effort to develop 25D/3D through-silicon interposer technology, https://www.astar.edu.sg/Portals/30/news/IMEFuturewei%20Press%20Release%20Final.pdf. Accessed 26 April 2014

- Siblerud P, Kim B (2007) Presentation slide EMC-3D consortium overview and COC Model<sup>a</sup>.

Jan 22–26, http://atlas-old.lal.in/2p3.fr/elec/BMC3DEu/documents/Semitool-Consortium%20 Overview.pdf. Accessed 18 July 2014

- 3DASMM Consortium (2008) News release new consortium formed focusing on Si interposer technologies. http://www.i-micronews.com/news/3D-consortiumof-formed-focusing-Si-interposer-technologies, 1464.html. Accessed 26 April 2014

- Toshiba (2007) Press release strengthening of CMOS image sensor business by in-house production of COMS camera module for mobile phone. (in Japanese), http://www.toshiba.co.jp/about/press/2007\_10/pr\_j0102.htm. Accessed 26 April 2014

- Micron (2008) News release micron introduces wafer level camera technology with TSV interconnects. <a href="http://www.i-micronews.com/news/Micron-wafer-level-camera-TSV-interconnects,1025.html">http://www.i-micronews.com/news/Micron-wafer-level-camera-TSV-interconnects,1025.html</a>. Accessed 26 April 2014

- ST Micro (2011) Press release ST microelectronics first to use through-silicon vias for smaller and smarter MEMS chips, http://www.bizjournals.com/prnewswire/press\_releases/2011/10/11/NY84151. Accessed 26 April 2014

- Elpida (2011) Press release Elpida to start to ship sample of 8 Gbit DDR3 SDRAM of X32 using TSV. (in Japanese). http://techon.nikkeibp.co.jp/article/NEWS/20110627/192909/. Accessed 27 April 2014

- Samsung (2011) Press release Samsung develops 30 nm-class 32 GB green DDR3 for nextgeneration servers using TSV package technology, http://www.samsung.com/global/business/ semiconductor/news-events/press-releases/detail?newsId=4014. Accessed 27 April 2014

- Hynix (2011) Press release Hynix semiconductor joins SEMATECH 3D interconnect program at UAibany Nano College, http://electroiq.com/blog/2011/03/hynix-semiconductor/. Accessed 27 April 2014

- 64. JEDEC (2012) Press release JEDEC publishes breakthrough standard for wide I/O mobile DRAM. http://www.jedec.org/news/pressreleases/jedec-publishes-breakthrough-standardwide-io-mobile-dram. Accessed 27 April 2014

- 65. JEDEC (2011) STANDAD JESD229 wide I/O single data rate (Wide I/O SDR) wide I/O single data rate. December

- 66. Samsung and Micron (2011) Press release micron and samsung launch consortium to break down the memory wall. http://investors.micron.com/releasedetail.cfm?releaseid=611879. Oct 6, Accessed 3 July 2014

- 67. IBM and Micron (2011) Press release IBM to produce Micron's hybrid memory cube in debut of first commercial, 3D chip-making capability. IBM news room, https://www-03.ibm.com/ press/us/en/pressrelease/36125.wss. Accessed 15 Aug 2014

- HMCC (2012) Press release microsoft joins hybrid memory cube consortium. http://investors. micron.com/releasedetail.cfm?releaseid=671338. Accessed 3 July 2014 (May 8)

- FIMCC (2012) Press release consortium to accelerate dramatic advances in memory technology announces new members. http://investors.micron.com/releasedetail.cfm?ReleaseID=686974. Accessed 3 July 2014 (June 27)

- HMCC (2012) Press release first draft of hybrid memory cobe interface specification released, http://news.micron.com/releasedetail.cfm?ReleaseID=700331, Accessed 3 July 2014 (August 14)

- Xilipx (2010) Press release XIlinx stacked silicon interconnect extends FPGA technology to deliver 'More than Moore' density, bandwidth and power efficiency. http://press.xilinx.com/2010-10-26-Xilinx-Stacked-Silicon-Interconnect-Extends-FPGA-Technology-to-Deliver-More-than-Moore-Density-Bandwidth-and-Power-Efficiency. Accessed 27 April 2014

- Xilinx (2012) White paper: Virtex-7 FPGAs, Xilinx stacked silicon interconnect technology delivers breakthrough FPGA capacity, bandwidth, and power efficiency Virtex-7 FPGAs. http://www.xilinx.com/support/documentation/white\_papers/wp380\_Stacked\_Silicon\_Interconnect\_Technology.pdf. Accessed 11 July 2014 (December 11)

- Xilinx (2011) Press release XIlinx ships world's highest capacity FPGA and shatters industry record for number of transistors by 2X. http://press.xilinx.com/2011-10-25-Xilinx-Ships-Worlds-Highest-Capacity-FPGA-and-Shatters-Industry-Record-for-Number-of-Transistors-by-2X, Accessed 27 April 2014

- 74. TSMC and Altera (2010) Press release TSMC, Altera team on 3-D IC test vehicle. http://www.eetimes.com/document.asp?doc\_id=1261410. Accessed 12 June 2014

- Knickerbocker JU (2012) IBM presentation slide 3D integration & packaging challenges with through-silicon-vias (TSV). USA NSF Workshop—2/02/2012, http://weti.cs.obiou.edu/john\_ weti.pdf. Accessed 3 July 2014

- I-Micronews (2012) Qualcomm integrates Wide IO Memory onto 28 inm logic chip. http:// www.i-micronews.com/news/Qualcomm-integrates-Wide-IO-Memory-onto-28-nm-logicchip.9605.html. Accessed 27 April 2014 (Oct 3)

- TechFreep (2006) Hardware news Intel's TSV connects processors to memory. http://tech-freep.com/intels-isv-connects-processors-to-memory.htm. Accessed 27 April 2014 (Sept 28)

- EETimes (2010) India news 3D TSV chips still pre-mature. http://www.eetindia.co.in/ ART 8800610003 1800007\_NT\_192ccb4b.HTM. Accessed 6 Aug 2011 (18 Jun)