# Fully Depleted Ge CMOS Devices and Logic Circuits on Si

Heng Wu, Student Member, IEEE, and Peide D. Ye, Fellow, IEEE

Abstract—We systematically studied Ge CMOS devices and logic circuits fabricated on a GeOI substrate, with the novel recessed channel and source/drain structures. Various channel lengths  $(L_{\rm ch})$  from 500 to 30 nm and channel thicknesses  $(T_{\rm ch})$  from 90 to 10 nm are implemented into the Ge CMOS devices and comprehensive geometry dependence analysis is carried out in terms of both  $L_{\rm ch}$  and  $T_{\rm ch}$ . With shrinking  $T_{\rm ch}$ , the gate electrostatics are enhanced significantly but the on-state performance is found to be deteriorated simultaneously. It is also confirmed that Ge nMOSFETs are more sensitive to  $T_{\rm ch}$  than pMOSFETs due to the phosphorus diffusion inside Ge. CMOS circuits, such as inverters, NANDs, NORs, and ring oscillators, are further investigated.

*Index Terms*—CMOS, Ge, GeOI, logic circuits, MOSFET, recessed channel, recessed source/drain (S/D), scalability, SOI.

#### I. Introduction

HILE the semiconductor industry is struggling to extend the life of Moore's Law in nowadays, non-Si CMOS [1]–[3] is considered as one of the most important approaches to keep boosting the drive current and circuit speed with reduced supply voltage. High mobility channel materials, such as Ge [3] and III–V compounds [1], [4]–[6], are intensively studied for pMOSFETs and nMOSFETs, respectively. Whereas, the poor hole mobility greatly limits the applicability of III–V for manufacturable CMOS technology [1], [5]. Compared with III–V compounds, Ge is quite promising for post-Si CMOS technology [5], [7]–[11], due to its higher and near symmetrical carrier mobilities, large density of state, and relatively matured process. Meanwhile, Ge, as a material, has been widely employed in current Si CMOS manufacturing.

For the last decades, while great achievements have been realized in Ge pMOSFETs, the research of Ge nMOSFETs is significantly lagged behind due to the Fermi level pining [12], [13] in Ge interface. Recently, encouraging progresses have been obtained in Ge nMOSFETs research, in terms of electron mobility [14]–[16], contacts [13], [17]–[21], interface passivation [14], [22], [23], and device scaling [16], [17], [24], [25], making all Ge CMOS possible [17], [22], [26]–[29].

Manuscript received April 13, 2016; revised May 30, 2016; accepted June 10, 2016. Date of publication June 30, 2016; date of current version July 21, 2016. This work was supported by the Semiconductor Research Corporation through the Global Research Collaboration Program. The review of this paper was arranged by Editor W. Tsai.

The authors are with the Birck Nanotechnology Center, School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47907 USA (e-mail: yep@purdue.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2016.2581203

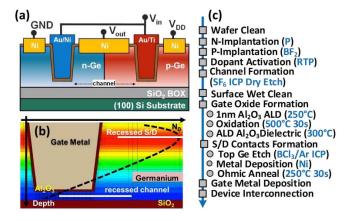

Fig. 1. (a) 2-D device schematic of a Ge CMOS inverter, showing the recessed channel and S/D. (b) Working principle of the MOSFETs in this paper. (c) Simplified fabrication process flow of the Ge CMOS.

As an extension of the previous conference reports [22], [27], [28], this paper thoroughly studies the Ge CMOS devices and circuits on Si by recessed channel and source/drain (S/D). Taking advantage of the dopant distribution profile inside Ge, the recess dry etching process can realize not only a heavily doped S/D for reduced contact resistance but also a lightly doped channel for enhanced gate electrostatics and better  $V_{\rm TH}$  tuning. Benefited from the balanced carrier mobilities of Ge and well-engineered gate-stacks, the Ge nMOSFETs and pMOSFETs show near-symmetrical performance. Ge fully depleted CMOS devices and circuits with various  $L_{\rm ch}$  from 500 to 30 nm and  $T_{\rm ch}$  from 90 to 10 nm are comprehensively studied in terms of device characteristics in ON- and OFF-states for MOSFETs and switching characteristics for logic gates.

This paper is organized as follows. Section II explains the device structures and fabrication processes. Section III talks about the electrical characteristics of Ge pMOSFETs and nMOSFETs, in terms of the device performance and their dependences on device geometry. Section IV presents the Ge CMOS circuit's results, including inverters, NANDs, NORs, and ring oscillators. The scaling metrics of CMOS inverters and ring oscillators are also detailedly explored. A summary is concluded in Section V.

#### II. EXPERIMENT

Fig. 1(a) shows the 2-D cross-sectional cartoon of a Ge CMOS inverter, with recessed channel and recessed S/D depicted. As detailedly described in our previous report [30], the working principle of recessed channel and S/D is shown in Fig. 1(b). Higher doping in recessed S/D enables better contacts and lower doping in recessed channel delivers

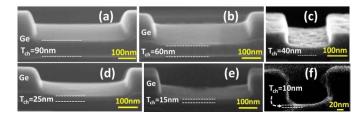

Fig. 2. Cross-sectional images of Ge recessed channels with channel thicknesses of (a) 90 nm, (b) 60 nm, (c) 40 nm, (d) 25 nm, (e) 15 nm, and (f) 10 nm.

enhanced gate control. Fig. 1(c) briefly shows the fabrication process flow.

The device fabrication was carried out on a GeOI substrate. The GeOI substrate is fabricated by Smartcut technology and is composed of 180-nm lightly Sb doped n-type (100) Ge layer, 400-nm SiO<sub>2</sub> buried oxide (BOX) and a (100) Si handling wafer. At first, native oxide stripping was conducted by soaking in diluted 2% HF solution, followed by an organic clean by sequentially soaking in acetone, methanol, and isopropanol for 5/5/5 min. After the mesa isolation based on an SF<sub>6</sub> dry etching, ion implantation was carried out by using P ions for nMOSFET (5  $\times$  10<sup>15</sup>/cm<sup>2</sup> at 30 keV) and BF<sub>2</sub> ions for pMOSFET ( $4 \times 10^{15}$ /cm<sup>2</sup> at 30 keV), respectively. Note that, both the S/D and gate region of MOSFETs were implanted. The P and BF<sub>2</sub> doping ions were then activated by a common ion activation in rapid thermal anneal at 500 °C for 1 min in N<sub>2</sub> ambient. Compared with our previous report, the simplified common ion activation here was carried out at lower temperature to reduce the thermal budget and the diffusion of P ions.

Next, in an inductive-coupled plasma dry etcher, SF<sub>6</sub> plasma was employed to partially etch away the Ge layer in the channel area, leaving a thin lightly doped recessed channel. The channel dry etching is calibrated to have a good aspect ratio and the etch rate is about 3 nm/s. By precisely controlling the dry etching time, different channel thicknesses of 90, 60, 40, 25, 15, and 10 nm were realized. The recessed channels with different  $T_{\rm ch}$  values are shown in Fig. 2. To remove the surface damages caused by dry etching, a surface wet clean was then conducted by three times cyclically soaking in 2% HF solution and DI water, ending at third soaking in HF to maintain a hydrophobic surface. The rough edges on the Ge surface could be smoothened by the cyclic oxidation in DI water and etching in HF solution. Then, 1-nm atomic layer deposition (ALD) Al<sub>2</sub>O<sub>3</sub> was deposited as the capping layer at 250 °C and the low temperature was adopted to reduce the formation of low-quality native oxide during the ALD process.  $GeO_x$  passivation layer was then formed by thermal annealing in pure O<sub>2</sub> ambient at 500 °C for 30 s. Next, the common ALD gate dielectric of 8- or 5-nm Al<sub>2</sub>O<sub>3</sub> was deposited at 300 °C. After finishing the gate-stack, common recessed S/D dry etching was conducted by first striping the oxide covering the S/D region and then removing the top less doped Ge layer. The BCl<sub>3</sub>/Ar-based recessed S/D dry etching is carefully calibrated to precisely control the etching rate to be around 15 nm/min. 100-nm Ni was then deposited as the contact metal, followed

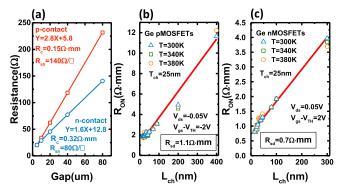

Fig. 3. (a) Typical TLM results of n and p contacts. ON-resistance dependence on  $L_{\rm ch}$  of Ge (b) pMOSFETs and (c) nMOSFETs with  $T_{\rm ch}$  of 25 nm at different temperatures of 300, 340, and 400 K.  $R_{\rm sd}$  is extracted.

by a common ohmic anneal at 250  $^{\circ}$ C for 30 s in N<sub>2</sub> ambient. The metal gate was formed by 40/60-nm Ti/Au for pMOSFETs and 40/60-nm Ni/Au for nMOSFETs. Finally, devices were connected for CMOS logic gates.

In total, seven steps of electron beam lithography were employed in the layer patterning. Note that the MOSFETs in this experiment are majority carrier devices working in accumulation mode and their threshold voltages  $(V_{TH})$  are relatively lower compared with the inversion mode devices, since extra gate bias is needed to deplete the channel. Resulted from this, high work-function metal of Ni/Au and low workfunction metal of Ti/Au were employed in nMOSFETs and pMOSFETs, respectively, to tune  $V_{TH}$  for CMOS circuits. The equivalent-oxide-thicknesses (EOTs) are calculated using the physical thickness and dielectric constant of the gate dielectric, considering both  $GeO_x$  and the  $Al_2O_3$  capping layer. The phyical thickness of  $GeO_x$  has been comfirmed to be 0.6 nm by TEM and that of Al<sub>2</sub>O<sub>3</sub> is 6 or 9 nm, resulting in an esitmated EOT of 4.5 or 3 nm. More detailed C-V characterization is needed for accurate EOT calculation.

# III. Ge CMOS TRANSISTORS

### A. Device Characteristics

Fig. 3(a) shows the typical TLM results on n- and p-Ge. Low  $R_c$  of 0.32 and 0.15  $\Omega \cdot$ mm and sheet resistance ( $R_{\rm sh}$ ) of 80 and 140  $\Omega/\square$  are achieved on n- and p-type Ge contacts, respectively. Fig. 3(b) and (c) shows the ON-resistance ( $R_{\rm ON}$ ) versus  $L_{\rm ch}$  of pMOSFETs and nMOSFETs with  $T_{\rm ch}$  of 25 nm at different temperatures. The S/D series resistance ( $R_{\rm sd}$ ) is extracted to be 0.7 and 1.1  $\Omega \cdot$  mm for nMOSFETs and pMOSFETs. Although  $R_c$  of p-type Ge contact is smaller than that of n-type Ge contact,  $R_{\rm sd}$  of pMOSFETs is larger than that of nMOSFETs because of a factor of two larger  $R_{\rm sh}$ .  $R_{\rm sd}$  shows negligible dependence on temperature, indicating the dominance of the tunneling current in the ohmic contacts.

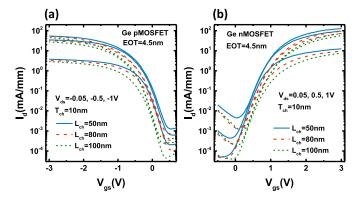

Fig. 4 shows the transfer characteristics of ultrathin body (UTB) Ge pMOSFETs and nMOSFETs, fabricated on the common substrate with 10-nm  $T_{\rm ch}$  [shown in Fig. 2(f)] and different channel lengths from 100 to 50 nm at  $V_{\rm ds}$  of  $\mp 0.05$ , 0.5 and 1 V. Both of the two sets of devices show good  $I_{\rm ON}/I_{\rm OFF}$  ratio of around 10<sup>5</sup>. For bulk Ge MOSFETs, high

Fig. 4. Transfer curves of 10-nm  $T_{\rm ch}$  Ge MOSFETs with 4.5-nm EOT and different  $L_{\rm ch}$  values of 100, 80, and 50 nm, at various  $|V_{\rm ds}|$  of 0.05, 0.5, and 1 V. (a) pMOSFETs. (b) nMOSFETs.

device  $I_{\rm ON}/I_{\rm OFF}$  ratio is very challenging due to the junction leakage current to body caused by the defects in nonoptimized S/D implantation and the punch through effect in short channel case, especially for Ge nMOSFETs, due to the high diffusivity of P ions [18], [20], [31], [32]. The good device  $I_{\rm ON}/I_{\rm OFF}$  ratio can be mainly attributed to the excellent gate control from the UTB channel and the BOX layer in the GeOI substrate, which blocks the leakage path from drain to body. Because of the UTB channel structure, the MOSFETs still maintain good OFF-state current of below 10 nA/ $\mu$ m at high  $V_{\rm ds}$  bias of 1 V for scaled channel lengths of 50 nm.

Meanwhile, with smaller channel length, the OFF-state current increases slightly and the transfer curves shifts positively and negatively for nMOSFETs and pMOSFETs, respectively, which is commonly known as the  $V_{\rm TH}$  roll off due to short channel effects (SCEs). With shrinking  $L_{\rm ch}$ , both subthreshold swing (SS) and drain induced barrier lowering (DIBL) also increase but the DIBL still remains below 100 mV/V, further confirming the excellent SCE immunity in the UTB channel. Note that the SS of these devices is acceptably large, due to thick gate oxide with an EOT of 4.5 nm used.

Comparing the two types of devices, nMOSFETs show about two times higher drain current than pMOSFETs, which can be attributed to mobility difference between electrons and holes inside Ge and the different series resistances in nMOSFETs and pMOSFETs. The carrier mobilities are extracted to be 35 and 10 cm<sup>2</sup>/Vs for electrons and holes at  $N_{\rm inv}$  of  $5 \times 10^{12}$  cm<sup>-2</sup>, respectively, through split-C-V measurement over long channel devices with 10- $\mu$ m  $L_{\rm ch}$ . Meanwhile, in our previous report [28], the  $R_{\rm SD}$  values of nMOSFETs and pMOSFETs are extracted to be 0.7 and 1.1  $\Omega \cdot$  mm.

## B. $L_{ch}$ Dependence of Device Characteristics

To further study MOSFET's behavior related to the device geometry, channel length scaling study is carried out first.

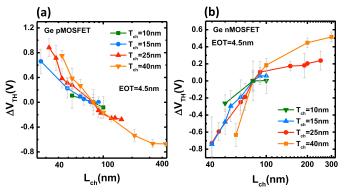

Fig. 5 shows the  $V_{\rm TH}$  dependence on  $L_{\rm ch}$  of Ge planar pMOSFETs and nMOSFETs with different  $T_{\rm ch}$  values of 40, 25, 15, and 10 nm. Since these devices were not fabricated in parallel, to exclude the influence from process variations and different gate metals used,  $\Delta V_{\rm TH}$  in relative to  $V_{\rm TH}$  of 80-nm  $L_{\rm ch}$  devices with the same  $T_{\rm ch}$  is used in the comparison.

Fig. 5.  $\Delta V_{\rm TH}$  [ $V_{\rm TH}-V_{\rm TH}(L_{\rm ch}=80~{\rm nm})$ ] relationships with  $L_{\rm ch}$  of Ge planar MOSFETs with  $T_{\rm ch}$  of 10, 15, 25, and 40 nm and same EOT of 4.5 nm. (a) pMOSFETs. (b) nMOSFETs.

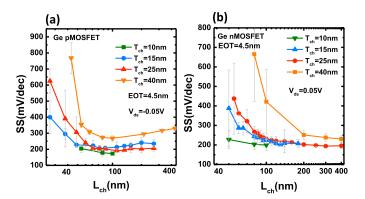

Fig. 6. SS relationships with  $L_{\rm ch}$  of Ge planar MOSFETs with  $T_{\rm ch}$  of 10, 15, 25, and 40 nm and the same EOT of 4.5 nm at low  $V_{\rm ds}$  of  $\mp 0.05$  V. (a) pMOSFETs. (b) nMOSFETs.

The scale bars reflect the standard deviations of results obtained in around 20 measured devices at each point. With decreasing  $L_{\rm ch}$ , both pMOSFET and nMOSFET show clear trend of  $V_{\rm TH}$  roll-off. It is found that shrinking  $T_{\rm ch}$  in planar devices could effectively reduce the  $V_{\rm TH}$  roll-off from 1 to 0.2 V, proving better gate electrostatics in thinner channel devices. For fully depleted MOSFETs, reducing channel thickness could physically decrease the thickness of depletion region [33], thus, relieving the requirement of minimum channel length for an acceptable  $V_{\rm TH}$  shift and providing better device scalability. By scaling gate dielectric and employing 3-D channel structure, smaller  $V_{\rm TH}$  shift would be expected [34].

SS scaling metrics of the same sets of devices in Fig. 5 are shown in Fig. 6. The SS first remains the same and then increases exponentially with reduced  $L_{\rm ch}$ . In shorter channel device at fixed  $V_{\rm ds}$  bias, the S/D transverse electrical field increases, resulting in loss of the controllability over the carriers of the vertical electrical field induced by gate bias. Thus, SS degrades with smaller channel lengths. Enhancing the vertical electrical field by using thinner channels could sufficiently improve the gate control, as proved by reduced SS in smaller  $T_{\rm ch}$  devices.

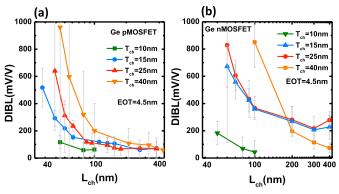

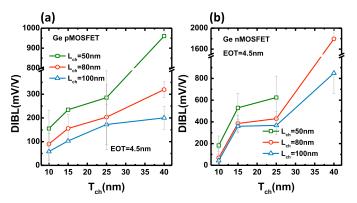

Fig. 7 shows the DIBL scaling metrics for pMOSFETs and nMOSFETs. Similar to that of SS, DIBL first keeps as a constant but then increases exponentially with decreasing  $L_{\rm ch}$ ,

Fig. 7. DIBL relationships with  $L_{\rm ch}$  of Ge planar MOSFETs with  $T_{\rm ch}$  of 10, 15, 25, and 40 nm and the same EOT of 4.5 nm. (a) pMOSFETs. (b) nMOSFETs.

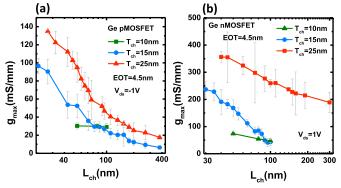

Fig. 8. Maximum transconductance relationships with  $L_{\rm ch}$  of Ge planar MOSFETs with  $T_{\rm ch}$  of 10, 15, and 25 nm and the same EOT of 4.5 nm at low  $V_{\rm ds}$  of  $\mp 1$  V. (a) pMOSFETs. (b) nMOSFETs.

which is also related with SCEs. By thinning down the channel, DIBL could be effectively suppressed. It is also worth noting that  $L_{\rm ch}$  at which DIBL starts to rise rapidly is reduced with smaller  $T_{\rm ch}$ , pointing out better channel length scalability in thinner channels.

For the ON-state performance of the devices, Fig. 8 shows the maximum trans-conductance  $(g_{\text{max}})$  scaling metrics of planar MOSFETs with 10-, 15-, and 25-nm  $T_{ch}$  at high  $V_{ds}$ of  $\mp 1$  V.  $g_{\text{max}}$  increases almost linearly with reduced  $L_{\text{ch}}$ , due to reduced channel resistance. Meanwhile, it is quite interesting that  $g_{\text{max}}$  degrades a lot with thinner channel. This can be mainly attributed to mobility degradation and reduced cross-sectional area for the accumulation channel. It is widely reported [35], [36] that the carrier mobility is deteriorated in thinner channel or smaller channel sizes due to severer surface roughness scattering and phonon scattering. What is more, especially for Silicon-on-Insulator (SOI)-based devices, stronger self-heating effect in thinner channel could also reduce the mobility [37], [38], since the heat dissipation from channel to substrate is more limited. Meanwhile, the  $g_{\text{max}}$ difference between pMOSFETs and nMOSFETs is mainly caused by the mobility difference, and different series resistances resulted from the nonoptimized common ion activation process during CMOS fabrication.

## C. $T_{ch}$ Dependence of Device Characteristics

Besides the channel length dependence study, the influences of channel thickness on device behaviors are also investigated.

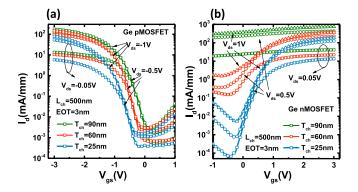

Fig. 9. Transfer curves of 500-nm  $L_{\rm ch}$  Ge MOSFETs with 3-nm EOT and different  $T_{\rm ch}$  values of 90, 60, and 25 nm, at various  $|V_{\rm ds}|$  of 0.05, 0.5, and 1 V. (a) pMOSFETs. (b) nMOSFETs.

Fig. 9 shows the transfer curves of 500-nm  $L_{ch}$  Ge MOS-FETs with an EOT of 3 nm and different  $T_{ch}$  values of 90, 60, and 25 nm at various  $V_{\rm ds}$  bias. Similar to the channel length dependence, in thinner channels, the curves shift negatively and positively for pMOSFETs and nMOSFETs, respectively. However, it is found that the nMOSFETs are much more sensitive to  $T_{\rm ch}$  than the pMOSFETs. The  $I_d$ – $V_{\rm gs}$  curves of pMOSFETs just shift with almost no  $I_{ON}/I_{OFF}$  ratio and SS degradation and the DIBL is also negligible due to the long channel length of 500 nm. While, with thicker channels, the curves of nMOSFETs show much larger  $V_{TH}$  shifts with rapid  $I_{\rm ON}/I_{\rm OFF}$  ratio, SS and DIBL degradations. Especially, the 90-nm  $T_{\rm ch}$  nMOSFET has almost no gate modulation to the drain current, indicating very weak gate control. This prominent distinction existing between pMOSFET and nMOSFET could be due to that the doping profile is different for n- and p-type ion implantation in Ge. As mentioned earlier, the n-type P ions inside Ge is much more diffusive than the p-type BF<sub>2</sub> ions [13], [31], which is one of the key challenges in realizing well behaved Ge nMOSFETs. As a result, large amount of p ions would diffuse deep into the channel area in the thermal process during device fabrication, leading to higher channel doping density in nMOSFETs than pMOSFETs. It will further reduce the maximum depletion width  $(W_{\rm dm})$ of the channel, making the gate harder to deplete the whole conducting Ge channel layer.

In other words,  $W_{\rm dm}$  would be much larger in pMOSFETs than nMOSFETs at the same  $T_{\rm ch}$ . For fully depleted MOSFETs with  $T_{\rm ch} < W_{\rm dm}$ , both p- and n-type devices' gate control should be similar, as proved by the 25-nm  $T_{\rm ch}$  ones. Whereas, with increasing  $T_{\rm ch}$  from 25 to 90 nm,  $W_{\rm dm}$  of pMOSFETs would increase slightly with almost no change to the gate control but  $W_{\rm dm}$  would decrease rapidly in nMOSFETs due to the fast rising P concentration, leading to  $W_{\rm dm}$  reaching down to  $T_{\rm ch}$  or even smaller and deteriorating gate electrostatics, as confirmed by the 60- and 90-nm  $T_{\rm ch}$  ones.

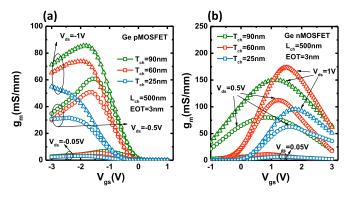

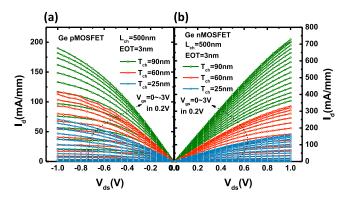

Figs. 10 and 11 show  $g_m - V_{\rm gs}$  and output curves of the same set of devices in Fig. 9. On the condition of same  $T_{\rm ch}$  and  $L_{\rm ch}$ , nMOSFETs show better ON-state performance because of the higher electron mobility. For pMOSFETs, the 90-nm  $T_{\rm ch}$  device has the largest  $g_{\rm max}$  due to higher majority carrier concentration induced by higher doping.

Fig. 10.  $g_m$  versus  $V_{\rm gs}$  curves of 500-nm  $L_{\rm ch}$  Ge MOSFETs with 3-nm EOT and different  $T_{\rm ch}$  values of 90, 60, and 25 nm, at various  $|V_{\rm ds}|$  of 0.05, 0.5, and 1 V. (a) pMOSFETs. (b) nMOSFETs.

Fig. 11. Output curves of 500-nm  $L_{\rm ch}$  Ge MOSFETs with 3-nm EOT and different  $T_{\rm ch}$  values of 90, 60, and 25 nm with  $|V_{\rm gs}|$  from 0 to 3 V in 0.2 V step. (a) pMOSFETs. (b) nMOSFETs.

Fig. 12. SS relationships with  $T_{\rm ch}$  of Ge planar MOSFETs with  $L_{\rm ch}$  of 50, 80, and 100 nm and the same EOT of 4.5 nm. (a) pMOSFETs. (b) nMOSFETs.

However, for nMOSFETs,  $g_{\rm max}$  of the 90-nm  $T_{\rm ch}$  is smaller than that of the 60-nm  $T_{\rm ch}$  device. This can be partly explained by: 1) larger OFF-state leakage and loss of gate control in thicker channels and 2) the fact that the P ion concentration in the 90-nm  $T_{\rm ch}$  channel is much higher than that of the 60-nm  $T_{\rm ch}$  channel, leading to lower electron mobility caused by impurity scattering.

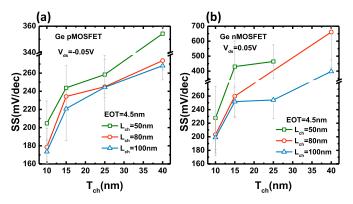

To further clarify the explanation above, channel thickness dependence is investigated. Fig. 12 shows the SS relationships with  $T_{\rm ch}$  of Ge MOSFETs with an EOT of 4.5 nm and different  $L_{\rm ch}$  values of 50, 80, and 100 nm at  $V_{\rm ds}$  of  $\mp 0.05$  V. The SS is reduced by shrinking  $T_{\rm ch}$ , in a near linear

Fig. 13. DIBL relationships with  $T_{\rm ch}$  of Ge planar MOSFETs with  $L_{\rm ch}$  of 50, 80, and 100 nm and the same EOT of 4.5 nm. (a) pMOSFETs. (b) nMOSFETs.

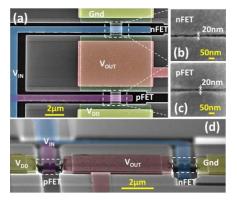

Fig. 14. (a) Top-down view of a fabricated Ge CMOS inverter with the smallest channel length under the SEM. (b) and (c) Zoom-in images of the gate areas in the CMOS inverter in (a), the channel length is 20 nm. (d) Bird's eye view of a CMOS inverter under SEM.

relationship, due to better gate control explained previously. For  $T_{\rm ch}$  below 25 nm, the SS of two types of devices keeps at a low range and pMOSFETs have slightly better SS, but not very significantly. Nevertheless, for  $T_{\rm ch}$  higher than 25 nm, nMOSFETs show much more prominent SS degradation, which is almost twice higher than that of pMOSFETs, in great consistence with the results shown in Fig. 9. Furthermore, in Fig. 13, the DIBL relationships with  $T_{\rm ch}$  for the same sets of devices also confirm the explanation on doping concentration difference. Similar to that of SS, DIBL remains at low ranges in both nMOSFETs and pMOSFETs for  $T_{\rm ch}$  < 25 nm but much more rapidly rises in nMOSFETs when  $T_{\rm ch}$  increases to 40 nm.

# IV. Ge CMOS CIRCUITS

Since both nMOSFETs and pMOSFETs have been realized on the same GeOI substrate, they are further interconnected for functional CMOS circuits.

## A. Ge CMOS Logic Gates

Fig. 14(a) shows the false-colored SEM image of a Ge CMOS inverter with the smallest 20-nm  $L_{\rm ch}$  in top-down view. For the circuit structure, the gates of the pMOSFET and nMOSFET setting on SiO<sub>2</sub> isolation region (the dark area)

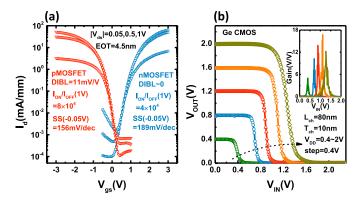

Fig. 15. (a)  $I_d$ – $V_{\rm gs}$  curves of the pMOSFET and nMOSFET in a CMOS inverter with  $T_{\rm ch}$  of 10 nm and  $L_{\rm ch}$  of 80 nm at  $|V_{\rm ds}|=0.05, 0.5,$  and 1 V. (b) Voltage transition curves of the same CMOS inverter in (a) at various  $V_{\rm DD}$  from 0.4 to 2 V. Inset: extracted voltage gain relationship with  $V_{\rm IN}$ .

are connected as the input electrode and drains of the two are connected as the output electrode with the sources of pMOSFET and nMOSFET are used as the supply and ground electrode, respectively. The enlarged gate areas with  $L_{\rm ch}$  of 20 nm are shown in Fig. 14(b) and (c). Fig. 14(d) shows the tilted SEM image of a Ge CMOS inverter, clearly showing the small notch on the gate metal caused by channel recessing.

Benefited from the most balanced carrier mobility in Ge and carefully engineered gate-stacks, Fig. 15(a) shows the transfer curves of the pMOSFET and nMOSFET in a typical 80-nm  $L_{\rm ch}$  and 10-nm  $T_{\rm ch}$  CMOS inverter, showing near-symmetrical performance. Thanks to the ultrathin channel, low DIBLs are obtained on both of the devices with 11 mV/V for the pMOSFET and a near-zero value for the nMOSFET and the SSs are 156 and 189 mV/decade at  $|V_{ds}|$  of 50 mV. It is further confirmed by the large  $I_{\rm ON}/I_{\rm OFF}$  ratio of around  $10^5$  at high  $V_{\rm ds}$  bias of 1 V. Fig. 15(b) shows the output voltage ( $V_{\rm OUT}$ ) versus input voltage  $(V_{\text{IN}})$  curves of the same CMOS inverter in Fig. 15(a), showing a steep voltage transition. The voltage gains  $[\Delta(V_{\text{OUT}})/\Delta(V_{\text{IN}})]$  are further extracted and given in Fig. 15(b) (inset). The maximum voltage gain is 17 V/V at  $V_{\rm DD}$  of 1.6 V, delivering a 70% increase over previously reported results [5] with the same  $L_{ch}$  but a larger  $T_{ch}$ of 25 nm.

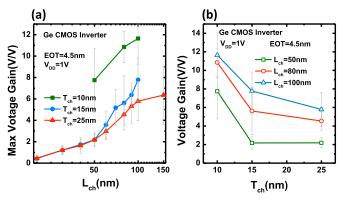

The device geometry dependences of Ge CMOS inverters are also investigated. Fig. 16(a) shows the maximum voltage gain scaling metrics of Ge CMOS inverters with  $T_{\rm ch}$  of 25, 15, and 10 nm at  $V_{\rm DD}=1$  V. With shrinking  $L_{\rm ch}$ , the maximum voltage gain is reduced, which is also related with the SCEs. As determined by inverter's working mechanism, the voltage gain strongly depends on the output conductance  $(g_d)$  of pMOSFET and nMOSFET as inverter's components. Smaller  $g_d$  gives higher voltage gains. Due to the DIBL induced by SCE, higher  $g_d$  would be expected in shorter channel MOSFETs, resulting in reduced voltage gains in CMOS inverters. By enhancing the gate electrostatics through employing thinner channels, the DIBL would be suppressed, thus reducing  $g_d$  and improving the voltage gains. Fig. 16(b) shows the maximum voltage gain relationships with channel thickness of inverters with various  $L_{ch}$  at  $V_{DD}$  of 1 V.

Fig. 16. (a)  $I_d$ – $V_{\rm gS}$  curves of the pMOSFET and nMOSFET in a CMOS inverter with  $T_{\rm ch}$  of 10 nm and  $L_{\rm ch}$  of 80 nm at  $|V_{\rm ds}|=0.05$ , 0.5, and 1 V. (b) Voltage transition curves of the same CMOS inverter in (a) at various  $V_{\rm DD}$  from 0.4 to 2 V. Inset: extracted voltage gain relationship with  $V_{\rm IN}$ .

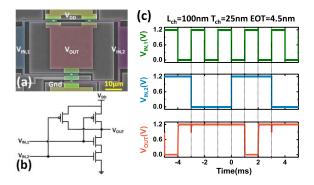

Fig. 17. (a) Top-down false-colored SEM image of a NAND logic gate. (b) Circuit diagram of the NAND logic gate. (c) Response signals of a 100-nm  $L_{\rm ch}$  NAND logic gate with 25-nm  $T_{\rm ch}$  and 4.5-nm EOT to two square-wave input signals in the time domain.

The 10-nm  $T_{\rm ch}$  channel delivers more than 200% improvement over the 25-nm  $T_{\rm ch}$  one and this improvement is even more prominent in the shortest channel devices with 50-nm  $L_{\rm ch}$ .

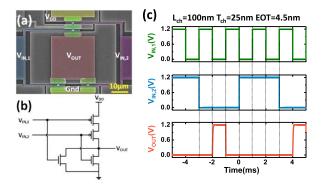

Other logic gates, such as NAND and NOR, are also realized and analyzed. Fig. 17(a) and (b) shows the top-down view of a fabricated NAND logic gate under SEM and its circuit diagram. The output signal of a 100-nm  $L_{\rm ch}$  NAND gate with 25-nm  $T_{\rm ch}$  and 4.5-nm EOT responding to two input signals at a supply voltage of 1.2 V is shown in Fig. 17(c). Four combinations of input states 1 1, 0 1, 1 0, and 0 0 are used and the output signal shows sharp transitions. Fig. 18(a) and (b) shows the top-down view of a fabricated NOR logic gate under SEM and its circuit diagram. The output signal of a 100-nm  $L_{\rm ch}$  NOR gate is provided in Fig. 18(c), with same testing conditions applied in the NAND gate.

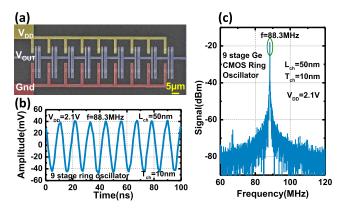

## B. Ge CMOS Ring Oscillators

Because of the well calibrated and stabilized fabrication processes, the MOSFETs in this paper have a decent performance and high yield, enabling the operation of CMOS ring oscillators, which requires good consistency of working CMOS inverters with high voltage gain. A fabricated nine-stage ring oscillator is shown in Fig. 19(a) and (b) shows the output signal of a Ge ring oscillator with  $L_{\rm ch}$  of 50 nm at  $V_{\rm DD}$

Fig. 18. (a) Top–down false-colored SEM image of a NOR logic gate. (b) Circuit diagram of the NOR logic gate. (c) Response signals of a 100-nm  $L_{\rm ch}$  NOR logic gate with 25-nm  $T_{\rm ch}$  and 4.5-nm EOT to two square-wave input signals in the time domain.

Fig. 19. (a) Top-down false-colored SEM image of a fabricated nine-stage ring oscillator. (b) Output signal of a nine-stage ring oscillator with 50-nm  $L_{\rm ch}$  at  $V_{\rm DD}$  of 2.1 V. (c) Oscillator power spectrum of the same ring oscillator in (b), indicating a oscillation frequency of 88.3 MHz.

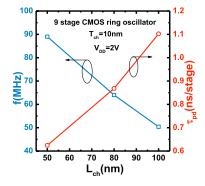

Fig. 20. Oscillation frequency and propagation delay per stage relationships with  $L_{\rm ch}$  of the nine-stage ring oscillators in this paper at  $V_{\rm DD}$  of 2 V.

of 2.1 V in the time domain. The power spectrum of the same device is shown in Fig. 19(c), showing an oscillation frequency of 88.3 MHz. The propagation delay  $(\tau_{pd})$  is calculated to be 629 ps by  $\tau_{pd} = 1/2$   $nf_0$ , where n is the number of stages and  $f_0$  is the oscillation frequency. The maximum oscillation frequency obtained is 102 MHz (not shown). Note that the demonstrated oscillation frequency is still far below the state-of-the-art Si CMOS technology, due to the large series resistance and fringing capacitance resulted from the

non-self-aligned process at the device level, and large parasitic capacitance from the test pads for measurement. Basically, it is a physical demonstration, which cannot reflect the potential performance of Ge ring oscillators. The oscillation frequency could be further improved by reducing the gate to S/D overlaps to decrease parasitic capacitance and reducing the S/D resistance to increase the drive current.

To further examine the scalability of the circuits, nine-stage ring oscillators with different channel lengths are shown in Fig. 20. The oscillation frequency increases and  $\tau_{\rm pd}$  decreases with smaller  $L_{\rm ch}$  at the same  $V_{\rm DD}$ . It could be easily understood: with shrinking  $L_{\rm ch}$ , the drive current of inverters increases but the gate capacitance decreases. Thus, the gate delay resulted from the charging and discharging of the fan-out capacitor is reduced. Hence, the speed of the circuit gets improved.

## V. Conclusion

We experimentally study the Ge CMOS devices and logic circuits with the recessed channel and S/D structures. Various channel lengths and channel thicknesses are implemented into the device fabrication. Detailed investigation on  $L_{\rm ch}$  and  $T_{\rm ch}$  dependences of device behaviors are conducted in terms of MOSFET OFF-state performance, such as  $V_{\rm TH}$  roll off, SS, and DIBL,  $g_{\rm max}$  as the ON-state performance, maximum voltage gain for CMOS inverters and oscillation frequency for CMOS ring oscillators. This paper provides valuable evidences of Ge as a promising candidate to replace Si in future's low-power and high-speed CMOS logic applications.

#### ACKNOWLEDGMENT

The authors would like to thank M. Lundstrom, A. Alam, S. Takagi, T. Ma, and K. K. Ng for the valuable discussions.

#### REFERENCES

- [1] J. A. del Alamo, "Nanometre-scale electronics with III–V compound semiconductors," *Nature*, vol. 479, no. 7373, pp. 317–323, Nov. 2011.

- [2] A. M. Ionescu and H. Riel, "Tunnel field-effect transistors as energy-efficient electronic switches," *Nature*, vol. 479, no. 7373, pp. 329–337, 2011.

- [3] R. Pillarisetty, "Academic and industry research progress in germanium nanodevices," *Nature*, vol. 479, no. 7373, pp. 324–328, Nov. 2011.

- [4] Y. Xuan, Y. Q. Wu, and P. D. Ye, "High-performance inversion-type enhancement-mode InGaAs MOSFET with maximum drain current exceeding 1 A/mm," *IEEE Electron Device Lett.*, vol. 29, no. 4, pp. 294–296, Apr. 2008.

- [5] S. Takagi et al., "III-V/Ge channel MOS device technologies in nano CMOS era," Jpn. J. Appl. Phys., vol. 54, no. 6S1, p. 06FA01, Jun. 2015.

- [6] J. J. Gu et al., "20–80 nm channel length InGaAs gate-all-around nanowire MOSFETs with EOT = 1.2 nm and lowest SS = 63 mV/dec," in *IEDM Tech. Dig.*, Dec. 2012, pp. 27.6.1–27.6.4.

- [7] A. Toriumi et al., "Material potential and scalability challenges of germanium CMOS," in IEDM Tech. Dig., Dec. 2011, pp. 28.4.1–28.4.4.

- [8] P. Hashemi et al., "Ultrathin strained-Ge channel p-MOSFETs with high-k/metal gate and sub-1-nm equivalent oxide thickness," IEEE Electron Device Lett., vol. 33, no. 7, pp. 943–945, Jul. 2012.

- [9] L. Gomez, P. Hashemi, and J. L. Hoyt, "Enhanced hole transport in short-channel strained-SiGe p-MOSFETs," *IEEE Trans. Electron Devices*, vol. 56, no. 11, pp. 2644–2651, Nov. 2009.

- [10] X. Yu, J. Kang, M. Takenaka, and S. Takagi, "Experimental study on carrier transport properties in extremely-thin body Ge-on-insulator (GOI) p-MOSFETs with GOI thickness down to 2 nm," in *IEDM Tech. Dig.*, Dec. 2015, pp. 2.2.1–2.2.4.

- [11] R. Kim, U. E. Avci, and I. A. Young, "Ge nanowire nMOSFET design with optimum band structure for high ballistic drive current," *IEEE Electron Device Lett.*, vol. 36, no. 8, pp. 751–753, Aug. 2015.

- [12] A. Dimoulas, P. Tsipas, A. Sotiropoulos, and E. K. Evangelou, "Fermi-level pinning and charge neutrality level in germanium," *Appl. Phys. Lett.*, vol. 89, no. 25, pp. 252110-1–252110-3, 2006.

- [13] D. P. Brunco et al., "Germanium MOSFET devices: Advances in materials understanding, process development, and electrical performance," J. Electrochem. Soc., vol. 155, no. 7, pp. H552–H561, 2008.

- [14] X. Gong et al., "InAIP-capped (100) Ge nFETs with 1.06 nm EOT: Achieving record high peak mobility and first integration on 300 mm Si substrate," in *IEDM Tech. Dig.*, Dec. 2014, pp. 9.4.1–9.4.4.

- [15] C. H. Lee, T. Nishimura, N. Saido, K. Nagashio, K. Kita, and A. Toriumi, "Record-high electron mobility in Ge n-MOSFETs exceeding Si universality," in *IEDM Tech. Dig.*, Dec. 2009, pp. 1–4.

- [16] R. Zhang, P.-C. Huang, J.-C. Lin, N. Taoka, M. Takenaka, and S. Takagi, "High-mobility Ge p- and n-MOSFETs with 0.7-nm EOT using HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge gate stacks fabricated by plasma postoxidation," *IEEE Trans. Electron Devices*, vol. 60, no. 3, pp. 927–934, Mar. 2013.

- [17] H. Wu, M. Si, L. Dong, J. Zhang, and P. D. Ye, "Ge CMOS: Break-throughs of nFETs (I<sub>max</sub> = 714 mA/mm, g<sub>max</sub> = 590 mS/mm) by recessed channel and S/D," in VLSI Symp. Tech. Dig., Jun. 2014, pp. 1–2.

- [18] R. R. Lieten, S. Degroote, M. Kuijk, and G. Borghs, "Ohmic contact formation on n-type Ge," Appl. Phys. Lett., vol. 92, no. 2, pp. 022106-1–022106-3, Jan. 2008.

- [19] M. J. H. van Dal et al., "Ge n-channel FinFET with optimized gate stack and contacts," in *IEDM Tech. Dig.*, Dec. 2014, pp. 9.5.1–9.5.4.

- [20] G. Thareja et al., "High performance germanium n-MOSFET with antimony dopant activation beyond 1 × 1020 cm<sup>-3</sup>," in *IEDM Tech. Dig.*, Dec. 2010, pp. 10.5.1–10.5.4.

[21] I.-H. Wong et al., "In-situ doped and tensily stained Ge junction-

- [21] I.-H. Wong *et al.*, "*In-situ* doped and tensily stained Ge junctionless gate-all-around nFETs on SOI featuring  $I_{on} = 828 \ \mu A/\mu m$ ,  $I_{on}/I_{off} \sim 1 \times 10^5$ , DIBL = 16–54 mV/V, and 1.4X external strain enhancement," in *IEDM Tech. Dig.*, Dec. 2014, pp. 9.6.1–9.6.4.

- [22] H. Wu, N. Conrad, W. Luo, and P. D. Ye, "First experimental demonstration of Ge CMOS circuits," in *IEDM Tech. Dig.*, Dec. 2014, pp. 9.3.1–9.3.4.

- [23] Y. Kamata, "High-k/Ge MOSFETs for future nanoelectronics," Mater. Today, vol. 11, nos. 1–2, pp. 30–38, Jan./Feb. 2008.

- [24] S.-H. Hsu et al., "Triangular-channel Ge NFETs on Si with (111) sidewall-enhanced Ion and nearly defect-free channels," in *IEDM Tech. Dig.*, Dec. 2012, pp. 23.6.1–23.6.4.

- [25] J. Mitard et al., "First demonstration of 15 nm-WFIN inversion-mode relaxed-germanium n-FinFETs with Si-cap free RMG and NiSiGe source/drain," in *IEDM Tech. Dig.*, Dec. 2014, pp. 16.5.1–16.5.4.

- [26] Y. Kamata et al., "Operations of CMOS inverter and ring oscillator composed of ultra-thin body poly-Ge p- and n-MISFETs for stacked channel 3D-IC," in SSDM Dig., Sep. 2014, pp. 668–669.

- [27] H. Wu, N. Conrad, M. Si, and P. D. Ye, "Demonstration of Ge CMOS inverter and ring oscillator with 10 nm ultra-thin channel," in *Proc. 73rd Annu. Device Res. Conf. (DRC)*, 2015, pp. 281–282.

- [28] H. Wu, W. Luo, M. Si, J. Zhang, H. Zhou, and P. D. Ye, "Deep sub-100 nm Ge CMOS devices on Si with the recessed S/D and channel," in *IEDM Tech. Dig.*, Dec. 2014, pp. 16.7.1–16.7.4.

- [29] C.-T. Chung, C.-W. Chen, J.-C. Lin, C.-C. Wu, C.-H. Chien, and G.-L. Luo, "First experimental Ge CMOS FinFETs directly on SOI substrate," in *IEDM Tech. Dig.*, Dec. 2012, pp. 16.4.1–16.4.4.

- [30] H. Wu, M. Si, L. Dong, J. Gu, J. Zhang, and P. D. Ye, "Germanium nMOSFETs with recessed channel and S/D: Contact, scalability, interface, and drain current exceeding 1 A/mm," *IEEE Trans. Electron Devices*, vol. 62, no. 5, pp. 1419–1426, May 2015.

- [31] R. Duffy, M. Shayesteh, I. Kazadojev, and R. Yu, "Germanium doping challenges," in *Proc. 13th Int. Workshop Junction Technol. (IWJT)*, 2013, pp. 16–21.

- [32] K. Suzuki *et al.*, "Ion-implanted impurity profiles in Ge substrates and amorphous layer thickness formed by Ion implantation," *IEEE Trans. Electron Devices*, vol. 56, no. 4, pp. 627–633, Apr. 2009.

- [33] Y. Taur and T. H. Ning, Fundamentals of Modern VLSI Devices. Cambridge, U.K.: Cambridge Univ. Press, 2009.

- [34] H. Wu, W. Wu, M. Si, and P. D. Ye, "First demonstration of Ge nanowire CMOS circuits: Lowest SS of 64 mV/dec, highest g<sub>max</sub> of 1057 μS/μm in Ge nFETs and highest maximum voltage gain of 54 V/V in Ge CMOS inverters," in *IEDM Tech. Dig.*, Dec. 2015, pp. 2.1.1–2.1.4.

- [35] S. H. Kim et al., "High performance sub-20-nm-channel-length extremely-thin body InAs-on-insulator tri-gate MOSFETs with high short channel effect immunity and V<sub>th</sub> tunability," in *IEDM Tech. Dig.*, Dec. 2013, pp. 16.4.1–16.4.4.

- [36] K. Uchida, H. Watanabe, A. Kinoshita, J. Koga, T. Numata, and S. Takagi, "Experimental study on carrier transport mechanism in ultrathin-body SOI nand p-MOSFETs with SOI thickness less than 5 nm," in *IEDM Tech. Dig.*, Dec. 2002, pp. 47–50.

- [37] L. T. Su, J. E. Chung, D. A. Antoniadis, K. E. Goodson, and M. I. Flik, "Measurement and modeling of self-heating in SOI nMOSFET's," *IEEE Trans. Electron Devices*, vol. 41, no. 1, pp. 69–75, Jan. 1994.

- [38] K. A. Jenkins and K. Rim, "Measurement of the effect of self-heating in strained-silicon MOSFETs," *IEEE Electron Device Lett.*, vol. 23, no. 6, pp. 360–362, Jun. 2002.

**Heng Wu** (S'13) received the B.E. degree in electronic science and engineering from Northwestern Polytechnical University, Xi'an, China in 2011, and the Ph.D. degree in electrical and computer engineering from Purdue University, West Lafayette, IN, USA in 2016.

His current research interests include high performance CMOS and alternative channel materials beyond Silicon.

**Peide D. Ye** (M'01–SM'03–F'13) received the B.S. degree from Fudan University, Shanghai, China, in 1988, and the Ph.D. degree from the Max-Planck-Institute for Solid State Research, Stuttgart, Germany, in 1996.

He is currently the Mary Jo Schwartz Chair Professor of Electrical and Computer Engineering with Purdue University, West Lafayette, IN, USA. His current research interests include high-k dielectric integration on novel channel materials include III-V, Ge, and grapheme.