# A Vision for 5G Channel Coding

Robert G. Maunder CTO AccelerComm September 2016

## **Abstract**

Channel coding is a vital but complex component of cellular communication systems, which is used for correcting the communication errors that are caused by noise, interference and poor signal strength. The turbo code was selected as the main channel code in 3G and 4G cellular systems, but the 3GPP standardization group is currently debating whether it should be replaced by the Low Density Parity Check (LDPC) code in 5G. This debate is being driven by the requirements for 5G, which include throughputs of up to 20 Gbps in the downlink to user devices, ultra-low latencies, as well as much greater flexibility to support diverse use-cases, including broadband data, Internet of Things (IoT), vehicular communications and cloud computing. In our previous white paper, we demonstrated that flexible turbo codes can achieve these requirements with superior hardware- and energy-efficiencies than flexible LDPC decoders. However, the proponents of LDPC codes have highlighted that inflexible LDPC decoders can achieve throughputs of 20 Gbps with particularly attractive hardware- and energyefficiencies. This white paper outlines a vision for 5G, in which channel coding is provided by a flexible turbo code for most use-cases, but which is supported by an inflexible LDPC code for 20 Gbps downlink use-cases, such as fixed wireless broadband. We demonstrate that this approach can meet all of the 5G requirements, while offering hardware- and energy-efficiencies that are significantly better than those of an LDPC-only solution. Furthermore, the proposed approach benefits from synergy with the 3G and 4G turbo code, as well as a significantly faster time-to-market for 5G. These benefits translate to a 5G that is significantly more capable, significantly easier to deploy and significantly lower cost.

## I. Introduction

In cellular communication systems, wireless transmission is used to convey bits of information between handsets and basestations, where the latter act as gatekeepers to the Internet and telephone networks. However, the received bits typically differ to the transmitted bits, owing to communication errors caused by noise, interference or poor signal strength. In order to correct these communication errors, cellular communication systems use channel codes. The turbo code [1] was selected as the main channel code in the 3G UMTS and 4G LTE cellular standards [2], [3], owing to its strong error correction capability and flexibility. However, the 3GPP standardization group is currently debating whether 5G should replace the turbo code with the Low Density Parity Check (LDPC) code [4], which is employed in WiFi, WiMAX, G.hn, Ethernet and DVB-S2 standards [5]–[9], or with the relatively new polar code [10].

This debate is being driven by the requirements for 5G, which aim to continue the trend of successive generations offering exponentially greater user experience and more diverse applications. In particular, a peak information throughput of 20 Gbps is targeted for the 5G downlink to user devices, which is much higher than the 1 Gbps achieved by 4G. During video streaming, this significantly improved throughput will enable opportunistic forward buffering when the channel conditions are favorable, for example. This will substantially increase the efficiency and reliability of streamed video, which currently suffers from drop outs when the channel conditions become unfavorable. Similar improvements to latency are targeted, in order to facilitate new applications in Internet of Things (IoT), vehicular communications and cloud computing. Owing to this significant widening of use cases beyond broadband data and telephony services, a much higher degree of flexibility is a key requirement for 5G, relative to previous generations.

In our previous white paper [11], we demonstrated that a *flexible* turbo-only solution to channel coding in 5G can achieve these requirements with superior hardware- and energy-efficiencies than a *flexible* LDPC-only solution. However, the proponents of LDPC codes have highlighted that *inflexible* LDPC decoders can achieve throughputs of 20 Gbps with particularly attractive hardware- and energy-efficiencies. This drives the discussion of this white paper, which outlines a hybrid turbo/LDPC solution for 5G, in which channel coding is provided by a flexible turbo code for most use-cases, but which is supported by an inflexible LDPC code for 20 Gbps downlink use-cases, such as fixed wireless broadband. We demonstrate that this approach can meet all of the 5G requirements, while offering hardware- and energy-efficiencies that are significantly better than those of an LDPC-only solution. Furthermore, the proposed approach benefits from synergy with the 3G and 4G turbo code, as well as a significantly faster time-to-market for 5G. These benefits translate to a 5G that is significantly more capable, significantly easier to deploy and significantly lower cost.

The remainder of this paper is organized as follows. Section II provides background information on turbo and LDPC codes. Section III provides the first comprehensive comparison of turbo and LDPC decoder Application Specific Integrated Circuits (ASICs). Motivated by this, our vision for a hybrid turbo/LDPC solution to 5G channel coding is described in Section IV. Finally, we offer our conclusions in Section V.

#### II. BACKGROUND ON CHANNEL CODING

As described in Section I, channel coding is a vital but complex component of cellular communication systems, which is used for correcting the communication errors that are caused by noise, interference and poor signal strength. This is achieved by using a channel encoder in the transmitter (be it the handset or the basestation) to process each so-called information block comprising K information bits and convert it into a longer encoded block comprising N > K encoded bits, which are transmitted. In the receiver, the additional (N - K) encoded bits provide the channel decoder with information that allows it to detect and correct communication errors within the original K information bits.

If the noise, interference or poor signal strength is particularly severe, then a low coding rate R=K/N will be required for the channel decoder to successfully detect and correct all transmission errors. However, a low coding rate implies the transmission of a high number N of encoded bits, which consume transmission energy, bandwidth and time. Therefore, good channel codes are ones which allow the successful detection and correction of transmission errors at coding rates R that are as close as possible to the theoretical limit that is imposed by the channel capacity [12]. In the past couple of decades, several near-capacity channel codes have emerged. These include turbo and LDPC codes, which use iterative decoding processes, where each successive decoding attempt informs the next, until the process converges.

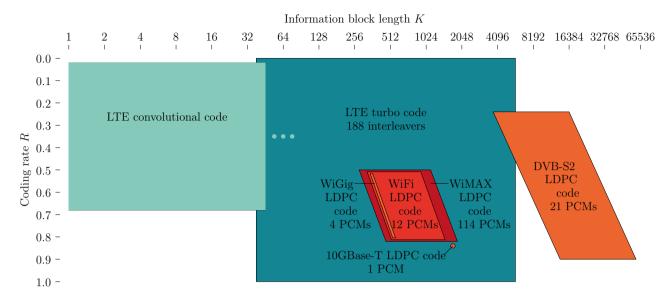

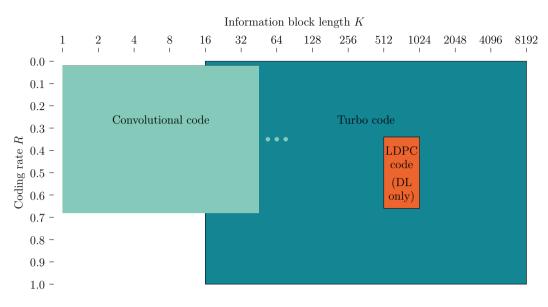

As discussed in our previous white paper [11], turbo codes employ a regular structure, which equally protects the K bits in each information block. The complexity of this structure scales with K, since the interconnections within the turbo code may be described by a  $1 \times K$  vector, which is referred to as the interleaver pattern. Owing to the regularity of this structure, turbo codes can be readily designed to flexibly support a wide range of information block lengths K and the full range of coding rates K. More specifically, support for a number of different information block lengths K is typically achieved by defining a different interleaver pattern for each. In particular, the 4G LTE turbo code employs 188 different interleaver patterns for information block lengths K in the range 40 to 6144 bits [3], as shown in Figure 1. Note however that shortening techniques can also be employed to provide further fine-grain information block length flexibility [13]. Meanwhile, turbo codes typically offer flexible support for the full range of coding rates K from 0 to 1 by using puncturing and repetition techniques, as shown for the 4G LTE turbo code in Figure 1. Note that since turbo codes protect all information bits equally, the

Fig. 1. The range of information block lengths K and coding rates R supported by a selection of standardized turbo and LDPC codes.

parametrization of the shortening, puncturing and repetition techniques does not require a high level of optimization.

By contrast, LDPC codes employ an irregular structure, which applies unequal protection to the K bits in each information block. The complexity of this structure scales with the encoded block length N, since the interconnections within the LDPC code may be described by a  $(N-K) \times N$  matrix, which is referred to as the Parity Check Matrix (PCM). Owing to the irregularity of this structure, it is a significant challenge to design flexible LDPC codes that support various block lengths and various coding rates. This flexibility is typically achieved by defining a different PCM for each supported combination of block length and coding rate.

However, there are no previously standardized LDPC (or polar) codes that flexibly support a wide range of block lengths and coding rates, as required for 5G [14]. In particular, the only standards that have adopted LDPC codes with low coding rates are those of DVB, although even this code does not support coding rates R below 1/4, as shown in Figure 1. More specifically, the DVB-S2 LDPC code [9] employs 21 PCMs to support the two encoded block lengths N of 16200 and 64800 bits, as well as 11 coding rates R in the range 1/4 to 9/10, as shown in Figure 1. Meanwhile, the WiMAX LDPC code [6] employs 114 PCMs to support 19 encoded block lengths N in the range 576 to 2304 bits, as well as four coding rates R in the range 1/2 to 5/6, as shown in Figure 1. Note that the WiMAX PCMs are grouped into families that share common structures, according to a quasi-cyclic technique [6]. A similar technique has been proposed by Qualcomm [15], in order to produce a set of 84 PCMs that support information block lengths K in the range 64 to 26880 bits and coding rates R in the range 10/122 to 24/27.

In addition to employing multiple PCMs, LDPC codes can achieve further fine-grain flexibility by using shortening, puncturing and repetition techniques. However, owing to the unequal protection that LDPC codes apply to the information bits, these techniques must be carefully parametrized in order to avoid degraded error correction capability, particularly if they are used to provide more than just fine-grain flexibility. Owing to this, the flexibility to support a wide range of block lengths and coding rates can only be achieved by employing a sufficient number of PCMs. In particular, in order meet the 5G requirement for a very high degree of flexibility [14], it may be expected that an LDPC-only solution would need to support combinations of around 10 different coding rates and around 10 different block lengths, for a

total of around 100 PCMs as in [6], [15]. This flexibility may be enhanced using quasi-cyclic, shortening, puncturing and/or repetition techniques.

Since the channel decoder must overcome the uncertainty introduced by noise, interference and poor signal strength, it typically has a much greater complexity than the channel encoder, particularly when flexible support for a wide range of information block lengths K and for the full range of coding rates  $R \in [0,1]$  is required, as in 5G [16]. Owing to this, dedicated ASIC implementations of channel decoders are typically required, so that the bits can be decoded in real-time, with comparable latencies (measured in ns) and throughputs (measured in Mbps or Gbps) to those that are achieved for their transmission. This is particularly important in 5G, where information throughputs of up to 20 Gbps are being targeted in the downlink [17]. Furthermore, it is this complexity that dictates the chip area (measured in mm²) and power consumption (measured in mW) of the ASIC. When characterizing an ASIC implementation of a channel decoder, we are typically interested in its *information* throughput, which is typically R times that of its *encoded* throughput. We are also interested in the ratio of this information throughput to the chip area and to the power consumption, in order to obtain the hardware efficiency (measured in Mbps/mm²) and the energy efficiency (measured in bit/nJ), respectively.

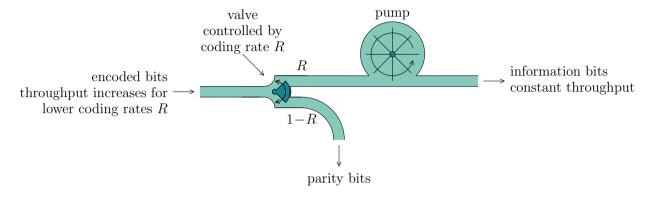

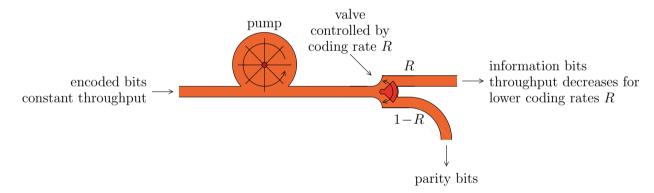

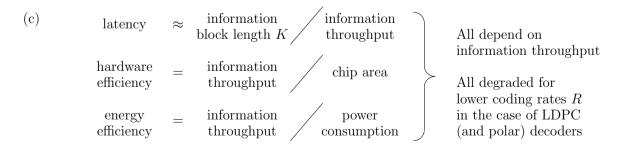

However, these hardware characteristics of LDPC decoders are particularly poor at medium and low coding rates, owing to two fundamental reasons. Firstly, the number of rows in an LDPC PCM grows as the coding rate R is reduced, which implies a greater decoding complexity. Secondly, the number of columns in the PCM is given by the encoded block length N, which dictates the input and output interface to the LDPC decoder. Therefore, LDPC decoders must operate by recovering the encoded bits and then extracting the information bits, as in polar decoders. Since LDPC (and polar) decoders must recover 1/R encoded bits in order to decode each information bit, their information throughputs, hardware efficiencies and energy efficiencies scale down proportionately with the coding rate R, as illustrated in Figure 2. Likewise, the latency associated with decoding a given information block length K scales up inversely proportionately with the coding rate R. By contrast, since the structure of turbo decoders scales with the information block length K, they can be said to decode the information bits directly. Owing to this, the information throughputs, latencies, hardware efficiencies and energy efficiencies of turbo decoders do not typically vary significantly with coding rate R, as illustrated in Figure 2.

Observation 1: There are no previously standardized LDPC (or polar) codes - and hence no mature LDPC (or polar) decoder ASICs - that support a sufficiently wide range of block lengths and coding rates.

Observation 2: In order to offer sufficient flexibility, an LDPC-only approach to 5G channel coding would need to support around 100 PCMs, together with quasi-cyclic, shortening, puncturing and repetition techniques.

Observation 3: In contrast to turbo decoders, the information throughput, hardware efficiency and energy efficiency of LDPC (and polar) decoder ASICs scale down proportionately with the coding rate, while the latency scales up inversely proportionately.

## III. SURVEY OF STATE-OF-THE-ART TURBO AND LDPC DECODER ASICS

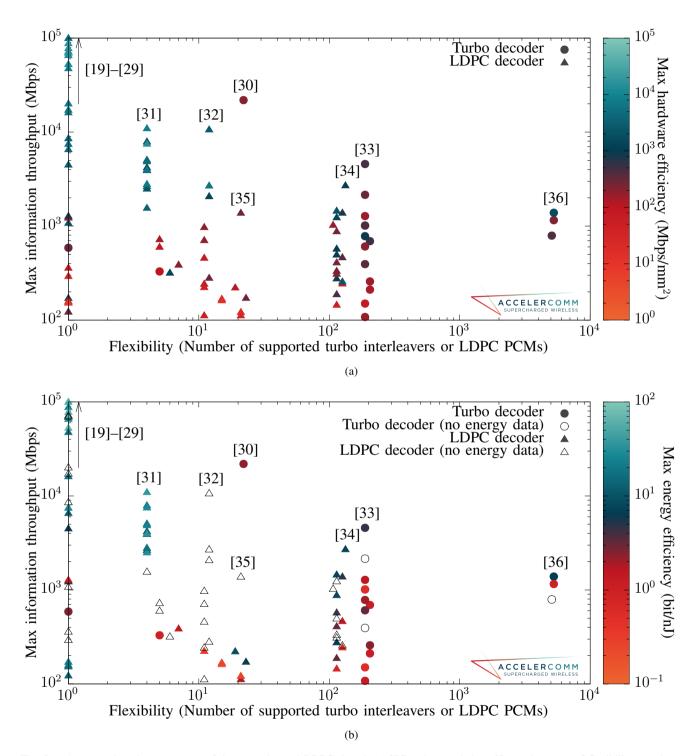

The first comprehensive survey of state-of-the-art ASIC implementations of turbo and LDPC decoders is provided in the dataset of [18], which tabulates and compares various hardware implementation characteristics. This comparison is summarized in Figure 3, which plots the flexibility, information throughput, hardware efficiency and energy efficiency of 22 recent turbo decoder ASICs and 89 recent LDPC decoder ASICs. Here, the flexibility is quantified by the number of interleaver designs that are supported by

(a) Turbo decoders recover the information bits directly

(b) LDPC (and polar) decoders recover the encoded bits, then extract the information bits

Fig. 2. An analogy using pumps, valves and pipes, to illustrate how the coding rate R of (a) turbo and (b) LDPC decoders affects their encoded and information throughputs, as well as (c) their latency, hardware efficiency and energy efficiency.

each turbo decoder ASIC and by the number of PCMs that are supported by each LDPC decoder ASIC. This is motivated since the range of information block lengths K and coding rates R that can be flexibly supported is dictated by the number of interleavers or PCMs that are employed, as discussed in Section II. The information throughputs, hardware efficiencies and energy efficiencies shown in Figure 3 have all been scaled to 65 nm technology, since this minimizes the degree of scaling that is required for the majority of the considered ASICs. As described in Section II, these characteristics of a channel decoder ASIC may vary with information block length K and coding rate R, particularly for LDPC decoders. In all cases, Figure 3 plots the *maximum* information throughput, hardware efficiency and energy efficiency that is achieved by each ASIC, across all information block lengths K and coding rates R. In the case of the LDPC decoders, these maximum information throughputs, hardware efficiencies and energy efficiencies are typically achieved for high coding rates of around R = 5/6. However, lower coding rates typically result in significantly lower information throughputs and therefore also significantly lower hardware- and energy-efficiencies, as will be detailed below.

As shown in Figure 3, the only LDPC decoder ASICs that achieve information throughputs in excess of 20 Gbps are those of [19]–[29]. All of these LDPC decoders adopt fully-parallel architectures that can only support a single PCM, having a high coding rate R. This is because these ASICs are laid out according to the factor graph [37] that is described by the PCM, using hard-wired connections between registers and dedicated computational hardware for each part of the factor graph. While this approach prevents the flexible support for more than one PCM, it allows the LDPC decoding process to be completed using a minimal number of clock cycles and without the use of additional memory, switchable interconnections or a complex controller. Owing to this, the LDPC decoders of [19]–[29] offer the best throughputs, latencies, hardware efficiencies and energy efficiencies among all of the channel decoder ASICs considered in Figure 3, although they offer the least flexibility.

By contrast, all flexible LDPC decoder ASICs employ partially-parallel architectures to support more than one PCM. More specifically, these ASICs employ a bank of computational hardware, which can be flexibly reused at different times to perform the processing associated with different parts of different PCMs. However, this approach requires the use of additional memory, switchable interconnections and a complex controller, which typically occupy around 75% of the chip area in the case of LDPC decoders that support around 100 PCMs [34]. Owing to this, these additional hardware components dominate the throughput, latency, hardware efficiency and energy efficiency of the resultant ASICs, particularly as the number of supported PCMs is increased, as shown in Figure 3. This is because LDPC codes have irregular structures with a high interconnection complexity, as described in Section II.

By contrast, turbo decoders have regular structures with significantly lower interconnection complexities, where the corresponding hardware typically occupies only 30% of the chip area. Owing to this, partially-parallel turbo decoders offer superior flexibilities, information throughputs, latencies, hardware efficiencies and energy efficiencies than partially-parallel LDPC decoders, as shown in Figure 3. This superiority is particularly apparent at medium and low coding rates R, as revealed by the comparison provided in Table I, which considers the partially-parallel turbo and LDPC decoder ASICs of [33] and [34]. This is a particularly fair comparison for several reasons. Firstly, both of these channel decoder ASICs support around 100 turbo interleavers or LDPC PCMs, meeting the 5G flexibility requirement discussed in Section II. Furthermore, both of these ASICs offer the best flexibilities, throughputs, latencies, hardware efficiencies and energy efficiencies among the sets of turbo and LDPC decoders having similar flexibility, as shown in Figure 3. Finally, both ASICs have been published within successive years, in the same prestigious journal and using post-layout analysis at the same technology scale, as shown in Table I.

As shown in Table I, the channel decoder ASICs of [33] and [34] both achieve different information throughputs and latencies at different coding rates R. In the case of the turbo decoder ASIC of [33], the

Fig. 3. A comparison between state-of-the-art turbo and LDPC decoder ASICs when scaled to 65 nm, in terms of flexibility, maximum information throughput and (a) maximum hardware efficiency or (b) maximum energy efficiency.

TABLE I COMPARISON OF THE STATE-OF-THE-ART PARTIALLY-PARALLEL TURBO AND LDPC DECODER ASICS OF [33], [34] AND [35].

| Paper                   | [33]                         |        |      | [34]                         |         |     | [35]                     |        |      |

|-------------------------|------------------------------|--------|------|------------------------------|---------|-----|--------------------------|--------|------|

| Year                    | 2014                         |        |      | 2013                         |         |     | 2009                     |        |      |

| Published in            | IEEE Trans. Circuits Syst. I |        |      | IEEE Trans. Circuits Syst. I |         |     | IEEE Veh. Technol. Conf. |        |      |

| Technology (nm)         | 90                           |        |      | 90                           |         |     | 90                       |        |      |

| Analysis                | Post-layout                  |        |      | Post-layout                  |         |     | Post-synthesis           |        |      |

| Code                    | Turbo                        |        |      | LDPC                         |         |     | LDPC                     |        |      |

| Supported standards     | LTE                          |        |      | WiMAX, WiFi and G.hn         |         |     | DVB-S2                   |        |      |

| Number of supported     | 188                          |        |      | 133                          |         |     | 21                       |        |      |

| interleavers/PCMs       |                              |        |      |                              |         |     |                          |        |      |

| Coding rate R           | High                         | Medium | Low  | High                         | Medium  | Low | High                     | Medium | Low  |

|                         | 0.95                         | 0.50   | 0.33 | 0.83                         | 0.50    | _   | 0.90                     | 0.50   | 0.25 |

| Information             | 2274                         | 3028*  | 3307 | 857-                         | 343-    | _   | 998                      | 380    | 181  |

| throughput (Mbps)       |                              |        |      | 1957                         | 762     |     |                          |        |      |

| Latency** for           | 440                          | 330*   | 302  | 511-                         | 1312-   | _   | 1002                     | 2632   | 5525 |

| K = 1000  (ns)          |                              |        |      | 1167                         | 2915    |     |                          |        |      |

| Hardware efficiency     | 115                          | 153*   | 167  | 154-                         | 62–138  | _   | 104                      | 40     | 19   |

| (Mbps/mm <sup>2</sup> ) |                              |        |      | 354                          |         |     |                          |        |      |

| Energy efficiency       | 1.57                         | 2.09*  | 2.28 | 2.30-                        | 0.92-   | _   | ?                        | ?      | ?    |

| (bit/nJ)                |                              |        |      | 5.25***                      | 2.04*** |     |                          |        |      |

<sup>\*</sup> These characteristics for the medium coding rate have been obtained using linear interpolation between those achieved at the high and low coding rates.

information throughput and latency are degraded slightly when higher coding rates R are employed, since these require more decoding iterations in order to maintain near-capacity error correction. By contrast, the LDPC decoder ASIC of [34] requires more decoding iterations for lower coding rates R. Furthermore, the information throughput and latency of an LDPC decoder naturally degrade with reduced coding rate R, as described in Section II. Owing to this, Table I shows that at different coding rates R, the LDPC decoder ASIC of [34] has dramatically different latencies and information throughputs, leading to dramatically different hardware- and energy-efficiencies. While the LDPC decoder ASIC of [34] has higher hardwareand energy-efficiencies than the turbo decoder ASIC of [33] at high coding rates, this relationship is reversed at medium coding rates R. Although the LDPC decoder ASIC of [34] does not support coding rates below R = 1/2, it may be expected that a version supporting lower coding rates would achieve inversely proportionately higher latencies and proportionately lower information throughputs, as described in Section II. This would lead to much lower hardware- and energy-efficiencies than the turbo decoder ASIC of [33] at these lower coding rates. Furthermore, increasing the flexibility of the LDPC decoder ASIC of [34] in this way would increase its interconnection complexity, as described above. This may be expected to result in worse information throughput, latency, hardware efficiency and energy efficiency than those of the turbo decoder ASIC of [33] for all coding rates R, not just medium and low coding rates.

The only standards that have adopted LDPC codes with low coding rates R are those of DVB, as discussed in Section II. Of the 14 DVB-S2 LDPC decoder ASICs considered in Figure 3, it is the design of [35] that offers the best throughputs, latencies and hardware-efficiencies. However, this 90 nm ASIC achieves worse information throughputs, latencies and hardware efficiencies than the 90 nm turbo decoder ASIC of [33] at all coding rates R, as shown in Table I. In particular, the hardware efficiency of [35] is

<sup>\*\*</sup> Latency is estimated by dividing the information block length K=1000 by the information throughput, since latency is not quantified in [33], [34] or [35]. Note that while none of these decoders support information block lengths of exactly K=1000, these estimates are provided for the sake of illustration.

<sup>\*\*\*</sup> The power consumption is stated as 228.36–517.70 mW in [34], but no discussion is provided about how this varies with coding rate. So, the average value of 373.03 mW has been used to calculate these energy efficiencies.

8.8 times worse than that of [33] at low coding rates R. Furthermore, this advantage of the turbo decoder ASIC could be expected to be even greater if post-layout analysis was applied to the LDPC decoder ASIC of [35], rather than only post-synthesis analysis. The advantage could be expected to become even greater still, if the flexibility of this LDPC decoder ASIC was increased to include more information block lengths K and lower coding rates R, in order to match the flexibility of the turbo decoder. Note that while the energy efficiency of this DVB-S2 LDPC decoder ASIC was not quantified in [35], we may expect this to scale linearly with the hardware efficiency, as is the case for the ASICs of [33] and [34]. Hence, we may conclude that the information throughput, latency, hardware efficiency and energy efficiency of flexible turbo decoder ASICs can be around an order-of-magnitude better than those of flexible LDPC decoder ASICs at low coding rates.

Observation 4: All LDPC decoders that have demonstrated information throughputs of 20 Gbps use fully-parallel architectures that support only a single PCM.

Observation 5: The information throughput, latency, hardware efficiency and energy efficiency of partially-parallel LDPC decoder ASICs are dominated by their flexibility, where support for more PCMs results in significantly reduced performance.

Observation 6: Partially-parallel turbo decoders offer significantly better flexibilities, information throughputs, latencies, hardware efficiencies and energy efficiencies than partially-parallel LDPC decoders, particularly at medium and low coding rates.

## IV. COMPLEMENTARY TURBO AND LDPC CODES FOR 5G

As described in Section III, partially-parallel LDPC decoder ASICs can achieve flexibility, while fully-parallel LDPC decoder ASICs can achieve high information throughputs. However, no LDPC decoder architectures have been demonstrated that can achieve both flexibility and throughputs of 20 Gbps. In particular, the throughput of the flexible partially-parallel LDPC decoder ASIC of [34] would need to be increased by around 40 times in order to reach the 5G downlink target of 20 Gbps across its range of supported coding rates R, which is not feasible using either state-of-the-art technology scales or by operating many replicas of the decoder in parallel. Therefore, in order to meet the 5G flexibility and downlink information throughput requirements, an LDPC-only approach would require the use of two independent LDPC decoders in the handsets, in order to avoid imposing an excessive chip area and power consumption. More specifically, a fully-parallel LDPC decoder would be used in applications where the channel is pushed to its capacity, allowing multi-Gbps information throughputs to be achieved by using medium coding rates R to maintain reliability. By contrast, a partially-parallel LDPC decoder would be used to flexibly support a wide variety of information block lengths K, as well as the full range of coding rates R.

However, Section III showed that partially-parallel turbo decoders offer superior flexibilities, information throughputs, latencies, hardware efficiencies and energy efficiencies than partially-parallel LDPC decoders, particularly at medium and low coding rates R. This suggests a hybrid turbo/LDPC approach to channel coding in the 5G downlink, which complements a fully-parallel LDPC decoder with a partially-parallel turbo decoder, rather than the partially-parallel LDPC decoder of the LDPC-only approach. Furthermore, this motivates a turbo-only approach to channel coding in the 5G uplink, where 20 Gbps information throughputs are not required. In addition to improved flexibility, information throughput, latency, hardware efficiency and energy efficiency, this approach would also offer the significant advantage of having synergy with the 3G and 4G turbo codes. More specifically, a hardware implementation of a 5G turbo code could be readily reused to also perform 3G and 4G turbo coding, reducing the chip area and power consumption

Fig. 4. A turbo code may be employed to flexibly support a wide range of information block lengths K and the full range of coding rates R. This may be supported by an LDPC code for medium information block lengths K and medium coding rates R. A convolutional code may also be used for short information block lengths K and low to medium coding rates R, as in 3G and 4G.

of a handset or basestation that supports multiple generations. This would offer significantly reduced time-to-market, as well as significant cost savings, as discussed in [11].

Figure 4 illustrates a particular vision for 5G channel coding, which adopts the hybrid turbo/LDPC approach described above. Here, an enhanced 4G LTE turbo code may be employed, which includes additional interleavers for shorter and longer information block lengths K, native support for lower coding rates, improved error correction using tailbiting, as well as traditional puncturing and repetition techniques [38]. At state-of-the-art technology scales, it may be expected that this turbo decoder could achieve information throughputs of several Gbps. For higher information throughputs in the downlink, this turbo decoder may be complemented by an LDPC code having a single PCM, which is suitable for fully-parallel decoding. This PCM may be carefully designed to allow some fine-grain flexibility to be achieved using puncturing, repetition and shortening techniques. Furthermore, the native information block length Kof this PCM must be carefully selected. If K is too large, then the fully-parallel decoder will have an excessive chip area. But if K is too small, then it will not be possible to achieve information throughputs of 20 Gbps, particularly when shortening is employed. In order to facilitate a reduced time-to-market for 5G, it may be prudent to adapt the PCM that is employed in 10GBase-T Ethernet [8] to use a coding rate of R = 1/2. Besides the proprietary PCMs of [28], this 10GBase-T Ethernet design is the only LDPC PCM for which information throughputs exceeding 20 Gbps have been demonstrated, as detailed in [19]–[27], [29]. This PCM would have an information block length of K = 1024 bits and it may be expected that shortening could be used to support information block lengths K of several hundreds of bits, without excessively degrading the performance of the decoder. Likewise, it may be expected that this PCM's coding rate of R=1/2 could be extended across the range of medium coding rates, using puncturing and repetition techniques. As shown in Figure 4, this hybrid turbo/LDPC approach could also be complemented by a convolutional code, for use at short information block lengths K and low to medium coding rates R, as in 3G and 4G.

The advantages of the hybrid turbo/LDPC approach described above can be appreciated by considering a hypothetical implementation example and comparing with LDPC-only benchmarkers, as shown in Table II.

TABLE II

COMPARISON OF HYBRID TURBO/LDPC APPROACH TO CHANNEL CODING IN THE 5G DOWNLINK WITH TWO LDPC-ONLY APPROACHES.

| Papers                        | [33] and [27]                 |          |      | [34] and [27]                  |          |       | [34]                          |        |       |

|-------------------------------|-------------------------------|----------|------|--------------------------------|----------|-------|-------------------------------|--------|-------|

| Technology (nm)               | Scaled to 40                  |          |      | Scaled to 40                   |          |       | Scaled to 40                  |        |       |

| Codes                         | 1 inflexible LDPC decoder and |          |      | 1 inflexible LDPC decoder and  |          |       | 12 parallel flexible LDPC de- |        |       |

|                               | 1 flexible turbo decoder      |          |      | 5 parallel flex. LDPC decoders |          |       | coders only                   |        |       |

| Coding rate R                 | High                          | Medium   | Low  | High                           | Medium   | Low   | High                          | Medium | Low   |

|                               | 0.95                          | 0.50     | 0.33 | 0.83                           | 0.50     | 0.33  | 0.83                          | 0.50   | 0.33  |

| Information                   | 6.24                          | 102.62** | 7.44 | 22.02*                         | 102.62** | 5.71* | 52.8*                         | 20.6*  | 13.7* |

| throughput (Gbps)             |                               |          |      |                                |          |       |                               |        |       |

| Latency*** for                | 160                           | 10       | 134  | 227                            | 10       | 876   | 227                           | 583    | 876   |

| K = 1000  (ns)                |                               |          |      |                                |          |       |                               |        |       |

| Total area (mm <sup>2</sup> ) | 3.90 + 0.55 = 4.45            |          |      | 5.46 + 0.55 = 6.01             |          |       | 13.11                         |        |       |

| Total power (mW)              | 645 + 284 = 929               |          |      | 829**** + 284 = 1113           |          |       | 1989****                      |        |       |

<sup>\*</sup> These information throughputs for the flexible LDPC decoder of [34] at high and medium coding rates are optimistically based on the highest values in the corresponding ranges of Table I. The results for the low coding rate of R=0.33 are obtained by scaling those of the medium coding rate R=0.50. It is optimistically assumed that the flexibility can be increased to include this low coding rate without degrading the hardware- or energy-efficiency.

Here, it is assumed that information throughputs of at least 20 Gbps are required for high throughput applications at medium coding rates R, while 5 Gbps is required for all other applications at all other coding rates R. In each case considered, these targets are achieved using either a combination of inflexible and flexible decoders, or using a flexible decoder alone, where technology scaling to 40 nm is assumed. The inflexible fully-parallel LDPC decoder of [27] is selected, since this offers the best hardware- and energy-efficiencies among all decoders considered in [18].

As shown in Table II, the combination of the inflexible LDPC decoder of [27] with the flexible partiallyparallel turbo decoder of [33] satisfies the throughput requirements described above, while imposing only modest latencies, chip area and power consumption. Furthermore, the turbo decoder of this combination fully satisfies the 5G flexibility requirement. By contrast, the 5G flexibility requirement is not met by the partially-parallel LDPC decoder of [34], since it only supports a narrow range of block lengths and only supports coding rates above R = 0.50, as described above. Increasing the flexibility of this design to meet the requirement could be expected to significantly degrade its hardware- and energy-efficiency. However, despite this, Table II optimistically assumes that the flexibility of this design could be enhanced to support a low coding rate of R=0.33 at a scaled information throughput, without degrading the hardware- or energyefficiency otherwise. As shown in Table II, the above-mentioned information throughput requirements are met in the case where a flexible LDPC decoder comprising 5 parallel replicas of the design of [34] is combined with the inflexible LDPC decoder of [27]. However, this approach can be seen to impose significantly greater latencies, chip area and power consumption than the hybrid turbo/LDPC approach described above. Much worse hardware characteristics result when attempting to meet the throughput requirements using only a flexible LDPC decoder comprising 12 parallel replicas of the design of [34], without the aid of the inflexible LDPC decoder of [27]. This highlights that an LDPC-only approach to

<sup>\*\*</sup> These information throughputs are achieved using the inflexible LDPC decoder of [27], when it is scaled to a coding rate of R = 0.50. It is assumed that this can be achieved without degrading the hardware- or energy-efficiency.

<sup>\*\*\*</sup> Latency is estimated by multiplying the number of parallel decoders by the information block length K=1000 and dividing by the information throughput. Note that while none of these decoders support information block lengths of exactly K=1000, these estimates are provided for the sake of illustration.

<sup>\*\*\*\*</sup> The power consumption is stated as 228.36–517.70 mW in [34], but no discussion is provided about how this varies with coding rate. So, the average value of 373.03 mW has been scaled and used as the basis of these power consumptions.

5G channel coding would require two independent LDPC decoders, namely one fully-parallel decoder to achieve information throughputs of 20 Gbps and one partially-parallel decoder to achieve flexibility. However, since flexible turbo decoders offer superior information throughput, latency, hardware efficiency and energy efficiency than flexible LDPC decoders, it is better to adopt the hybrid turbo/LDPC approach instead.

Observation 7: An LDPC-only approach to 5G channel coding would require two independent LDPC decoders, namely one fully-parallel decoder to achieve information throughputs of 20 Gbps and one partially-parallel decoder to achieve flexibility.

Recommendation 1: A hybrid turbo/LDPC approach to 5G channel coding should be adopted in the downlink, which employs a turbo code to flexibly support a wide range of information block lengths and the full range of coding rates, supported by an LDPC code based on a single PCM having a medium information block length and a medium coding rate.

Recommendation 2: A turbo-only approach to 5G channel coding should be adopted in the uplink, which employs a turbo code to flexibly support a wide range of information block lengths and the full range of coding rates.

## V. CONCLUSIONS

In this white paper, we have discussed the degrees to which turbo and LDPC codes can meet the requirements for 5G, which include much higher information throughputs and much greater flexibility than previous generations. We have shown that there are no previously standardized LDPC codes and hence no mature LDPC decoder ASICs that support a sufficiently wide range of information block lengths K and coding rates R. So in order to offer sufficient flexibility, an LDPC-only approach to 5G channel coding would need to adopt a new approach comprising around 100 PCMs, supported by quasi-cyclic, shortening, puncturing and repetition techniques. However, the 20 Gbps information throughput downlink requirement has only been met by fully-parallel LDPC decoders, which support only a single PCM. This highlights that an LDPC-only approach to 5G channel coding would require the use of two independent LDPC decoders in the handset, namely one fully-parallel decoder to achieve information throughputs of 20 Gbps and one partially-parallel decoder to achieve flexibility. However, we have shown that the information throughput, latency, hardware efficiency and energy efficiency of partially-parallel LDPC decoder ASICs are dominated by their flexibility, where support for more PCMs results in significantly reduced performance. Owing to this, partially-parallel turbo decoders offer superior flexibilities, information throughputs, latencies, hardware efficiencies and energy efficiencies than partially-parallel LDPC decoders, particularly at medium and low coding rates R. This is because the information throughputs, hardware efficiencies and energy efficiencies of LDPC (and polar) decoders scale down proportionately with coding rate R, while the latencies scale up inversely proportional with R, unlike in turbo decoders. This leads us to recommend a hybrid turbo/LDPC approach to 5G channel coding, which employs a turbo code to flexibly support a wide range of information block lengths K and the full range of coding rates R, but supported in the downlink by an LDPC code based on a single PCM having a medium information block length K and a medium coding rate R. This may also be supported by a convolutional code for short information block lengths K and low to medium coding rates R, as in 3G and 4G. We have demonstrated that the proposed hybrid turbo/LDPC approach can meet all of the 5G requirements, while offering hardwareand energy-efficiencies that are significantly better than those of an LDPC-only solution. Furthermore, the proposed approach benefits from synergy with the 3G and 4G turbo code, as well as a significantly faster time-to-market for 5G. These benefits translate to a 5G that is significantly more capable, significantly easier to deploy and significantly lower cost.

#### REFERENCES

- [1] C. Berrou, A. Glavieux, and P. Thitimajshima, "Near Shannon limit error-correcting coding and decoding: Turbo-codes (1)," in *Proc. IEEE Int. Conf. on Communications*, vol. 2, Geneva, Switzerland, may 1993, pp. 1064–1070.

- [2] ETSI TS 125 222; Universal Mobile Telecommunications System (UMTS); Multiplexing and Channel Coding (FDD), V9.3.0 ed., 2012.

- [3] ETSI TS 136 212 LTE; Evolved Universal Terrestrial Radio Access (E-UTRA); Multiplexing and Channel Coding, V13.1.0 ed., 2016.

- [4] D. J. C. MacKay and R. M. Neal, "Near Shannon limit performance of low density parity check codes," *Electron. Lett.*, vol. 32, no. 18, pp. 457–458, aug 1996.

- [5] IEEE 802.11-2012 Standard for Information Technology Telecommunications and Information Exchange between Systems Local and Metropolitan Area Networks - Specific Requirements - Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY), 2012.

- [6] IEEE 802.16-2012 Standard for Local and Metropolitan Area Networks Part 16: Air Interface for Broadband Wireless Access Systems, 2012.

- [7] ITU-T G.hn Standard for Wired Home Networking, 2009.

- [8] IEEE 802.3an-2006 Specific requirements Part 3: Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications Amendment 1: Physical Layer and Management Parameters for 10 Gb/s Operation, 2006.

- [9] ETSI EN 302 307-1 Digital Video Broadcasting (DVB); Second generation framing structure, channel coding and modulation systems for Broadcasting, Interactive Services, News Gathering and other broadband satellite applications; Part 1: DVB-S2, V1.4.1 ed., 2014.

- [10] E. Arikan, "Channel polarization: A method for constructing capacity-achieving codes for symmetric binary-input memoryless channels," IEEE Trans. Inform. Theory, vol. 55, no. 7, pp. 3051–3073, jul 2009.

- [11] R. G. Maunder, "The 5G channel code contenders," *AccelerComm White Paper*, Aug. 2016. [Online]. Available: http://www.accelercomm.com

- [12] C. E. Shannon, "The mathematical theory of communication," Bell System Technical Journal, vol. 27, pp. 379–423, jul 1948.

- [13] A. Nimbalker, Y. Blankenship, B. Classon, and T. K. Blankenship, "ARP and QPP interleavers for LTE turbo coding," in *Proc. IEEE Wireless Commun. Networking Conf.*, Las Vegas, NV, USA, mar 2008, pp. 1032–1037.

- [14] 3GPP, "Draft minutes report," in 3GPP TSG RAN WG1 #86, Aug. 2016.

- [15] Qualcomm, "R1-166388 LDPC rate compatible design," in 3GPP TSG RAN WG1 #86, Aug. 2016.

- [16] NTT DoCoMo, "R1-167373 Workplan for study on NR access technology," in 3GPP TSG RAN WG1 #86, Aug. 2016.

- [17] Samsung, "R1-162181 Channel coding for 5G new radio interface," in 3GPP TSG RAN WG1 #84bis, Apr. 2016.

- [18] R. G. Maunder, "Survey of ASIC implementations of turbo and LDPC decoders," *University of Southampton Dataset*, Aug. 2016. [Online]. Available: http://eprints.soton.ac.uk/399846/

- [19] D. Wu, Y. Chen, Q. Zhang, Y. l. Ueng, and X. Zeng, "Strategies for reducing decoding cycles in stochastic LDPC decoders," *IEEE Trans. Circuits Syst. II*, vol. 63, no. 9, pp. 873–877, Sept 2016.

- [20] Z. Zhang, V. Anantharam, M. J. Wainwright, and B. Nikolic, "An efficient 10GBASE-T Ethernet LDPC decoder design with low error floors," *IEEE J. Solid-State Circuits*, vol. 45, no. 4, pp. 843–855, April 2010.

- [21] K. Cushon, S. Hemati, S. Mannor, and W. J. Gross, "Energy-efficient gear-shift LDPC decoders," in *Proc. IEEE Int. Conf. Application-Specific Systems, Architectures Processors*, Zurich, Switzerland, June 2014, pp. 219–223.

- [22] C. C. Cheng, J. D. Yang, H. C. Lee, C. H. Yang, and Y. L. Ueng, "A fully parallel LDPC decoder architecture using probabilistic min-sum algorithm for high-throughput applications," *IEEE Trans. Circuits Syst. 1*, vol. 61, no. 9, pp. 2738–2746, Sept 2014.

- [23] D. Wu, Y. Chen, Q. Zhang, L. Zheng, X. Zeng, and Y. I. Ueng, "Latency-optimized stochastic LDPC decoder for high-throughput applications," in *Proc. IEEE Int. Symp. Circuits Systems*, Lisbon, Portugal, May 2015, pp. 3044–3047.

- [24] S. S. Tehrani, A. Naderi, G. A. Kamendje, S. Hemati, S. Mannor, and W. J. Gross, "Majority-based tracking forecast memories for stochastic LDPC decoding," *IEEE Trans. Signal Process.*, vol. 58, no. 9, pp. 4883–4896, Sept 2010.

- [25] T. Mohsenin, H. Shirani-mehr, and B. M. Baas, "LDPC decoder with an adaptive wordwidth datapath for energy and BER co-optimization," VLSI Design, 2013.

- [26] T. Mohsenin, D. N. Truong, and B. M. Baas, "A low-complexity message-passing algorithm for reduced routing congestion in LDPC decoders," *IEEE Trans. Circuits Syst. I*, vol. 57, no. 5, pp. 1048–1061, May 2010.

- [27] K. Cushon, S. Hemati, C. Leroux, S. Mannor, and W. J. Gross, "High-throughput energy-efficient LDPC decoders using differential binary message passing," *IEEE Trans. Signal Process.*, vol. 62, no. 3, pp. 619–631, Feb 2014.

- [28] K. Cushon, P. Larsson-Edefors, and P. Andrekson, "Energy-efficient soft-decision LDPC FEC for long-haul optical communication," in Proc. Euro. Conf. Optical Commun., Valencia, Spain, Sept 2015, pp. 1–3.

- [29] A. Naderi, S. Mannor, M. Sawan, and W. J. Gross, "Delayed stochastic decoding of LDPC codes," *IEEE Trans. Signal Process.*, vol. 59, no. 11, pp. 5617–5626, Nov 2011.

- [30] A. Li, L. Xiang, T. Chen, R. G. Maunder, B. M. Al-Hashimi, and L. Hanzo, "VLSI implementation of fully parallel LTE turbo decoders," *IEEE Access*, vol. 4, pp. 323–346, 2016.

- [31] X. R. Lee, C. L. Chen, H. C. Chang, and C. Y. Lee, "A 7.92 Gb/s 437.2 mW stochastic LDPC decoder chip for IEEE 802.15.3c applications," *IEEE Trans. Circuits Syst. I*, vol. 62, no. 2, pp. 507–516, Feb. 2015.

- [32] T. H. Tran, Y. Nagao, H. Ochi, and M. Kurosaki, "ASIC design of 7.7 Gbps multi-mode LDPC decoder for IEEE 802.11ac," in *Proc. IEEE Int. Symp. Commun. Information Tech.*, Incheon, Republic of Korea, Sept 2014, pp. 259–263.

- [33] R. Shrestha and R. P. Paily, "High-throughput turbo decoder with parallel architecture for LTE wireless communication standards," *IEEE Trans. Circuits Syst. I*, vol. 61, no. 9, pp. 2699–2710, Sept 2014.

## ACCELERCOMM WHITE PAPER: A VISION FOR 5G CHANNEL CODING

- [34] Y. L. Ueng, B. J. Yang, C. J. Yang, H. C. Lee, and J. D. Yang, "An efficient multi-standard LDPC decoder design using hardware-friendly shuffled decoding," *IEEE Trans. Circuits Syst. I*, vol. 60, no. 3, pp. 743–756, March 2013.

- [35] B. Zhang, H. Liu, X. Chen, D. Liu, and X. Yi, "Low complexity DVB-S2 LDPC decoder," in Proc. IEEE Veh. Technol. Conf., Barcelona, Spain, April 2009.

- [36] Q. Yang, X. Zhou, G. E. Sobelman, and X. Li, "Network-on-chip for turbo decoders," *IEEE Trans. VLSI Syst.*, vol. 24, no. 1, pp. 338–342, Jan 2016.

- [37] H.-A. Loeliger, "An introduction to factor graphs," IEEE Sig. Process. Mag., vol. 21, no. 1, pp. 28-41, jan 2004.

- [38] Orange, "R1-167413 Enhanced turbo codes for NR: Implementation details," in 3GPP TSG RAN WG1 #86, Aug. 2016.

**Robert G. Maunder** is an industry authority on channel coding, having gained his PhD in Wireless Communications in 2007 from the University of Southampton. As an Associate Professor, he published over 100 IEEE papers and resources on the holistic design of signal processing algorithms and hardware implementations for error correction decoders, including turbo, LDPC and polar decoders. This work led him to dispel the longstanding myth that the level of parallelism in turbo decoders is inherently limited. Rob has found a way to unlock unlimited levels of parallelism and with it, dramatically improve turbo decoder throughput and latency. This is what is being leveraged by his founding of AccelerComm Limited.