# IEEE Standard for a High Performance Serial Bus

Sponsor

Microprocessor and Microcomputer Standards Committee of the IEEE Computer Society

Approved 12 December 1995

**IEEE Standards Board**

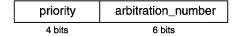

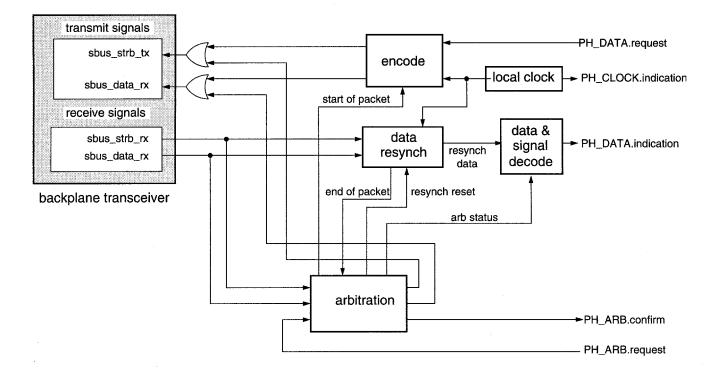

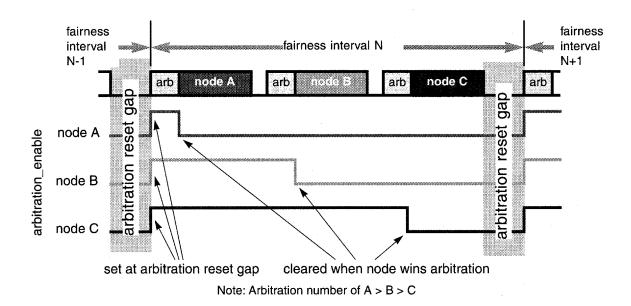

Approved 22 July 1996

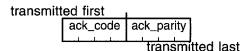

**American National Standards Institute**

**Abstract:** A high-speed serial bus that integrates well with most IEEE standard 32-bit and 64-bit parallel buses, as well as such nonbus interconnects as the IEEE Std 1596-1992, Scalable Coherent Interface, is specified. It is intended to provide a low-cost interconnect between cards on the same backplane, cards on other backplanes, and external peripherals. This standard follows the IEEE Std 1212-1991 Command and Status Register (CSR) architecture.

Keywords: backplane, bus, computers, high-speed serial bus, interconnect, parallel buses

The Institute of Electrical And Electronics Engineers, Inc.

345 East 47th Street, New York, NY 10017-2394, USA

Copyright © 1996 by the Institute of Electrical and Electronics Engineers, Inc.

All rights reserved. Published 1996. Printed in the United States of America.

ISBN 1-55937-583-3

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without the prior written permission of the publisher.

i

**IEEE Standards** documents are developed within the IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Board. Members of the committees serve voluntarily and without compensation. They are not necessarily members of the Institute. The standards developed within IEEE represent a consensus of the broad expertise on the subject within the Institute as well as those activities outside of IEEE that have expressed an interest in participating in the development of the standard.

Use of an IEEE Standard is wholly voluntary. The existence of an IEEE Standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of the IEEE Standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard. Every IEEE Standard is subjected to review at least every five years for revision or reaffirmation. When a document is more than five years old and has not been reaffirmed, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE Standard.

Comments for revision of IEEE Standards are welcome from any interested party, regardless of membership affiliation with IEEE. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments.

Interpretations: Occasionally questions may arise regarding the meaning of portions of standards as they relate to specific applications. When the need for interpretations is brought to the attention of IEEE, the Institute will initiate action to prepare appropriate responses. Since IEEE Standards represent a consensus of all concerned interests, it is important to ensure that any interpretation has also received the concurrence of a balance of interests. For this reason, IEEE and the members of its societies and Standards Coordinating Committees are not able to provide an instant response to interpretation requests except in those cases where the matter has previously received formal consideration.

Comments on standards and requests for interpretations should be addressed to:

Secretary, IEEE Standards Board 445 Hoes Lane P.O. Box 1331 Piscataway, NJ 08855-1331 USA

Note: Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. The IEEE shall not be responsible for identifying all patents for which a license may be required by an IEEE standard or for conducting inquiries into the legal validity or scope of those patents that are brought to its attention.

Authorization to photocopy portions of any individual standard for internal or personal use is granted by the Institute of Electrical and Electronics Engineers, Inc., provided that the appropriate fee is paid to Copyright Clearance Center. To arrange for payment of licensing fee, please contact Copyright Clearance Center, Customer Service, 222 Rosewood Drive, Danvers, MA 01923 USA; (508) 750-8400. Permission to photocopy portions of any individual standard for educational classroom use can also be obtained through the Copyright Clearance Center.

### Introduction

(This introduction is not a part of IEEE Std 1394-1995, IEEE Standard for a High Performance Serial Bus.)

This standard describes a serial bus that provides the same services as modern IEEE-standard parallel buses, but at a much lower cost. It has a 64-bit address space, control registers, and a read/write/lock operation set that conforms to the IEEE Std 1212-1991, Command and Status Register (CSR) standard. This simplifies bridging between the Serial Bus and the other interconnects using the IEEE 1212 architecture: IEEE Std 896-1991, FutureBus+ <sup>®</sup> and IEEE Std 1596-1992, Scalable Coherent Interface (SCI).

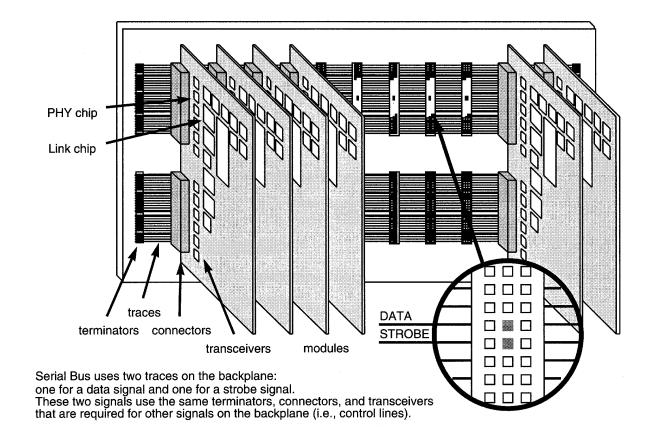

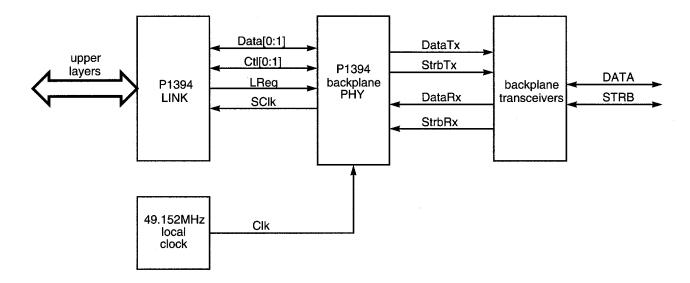

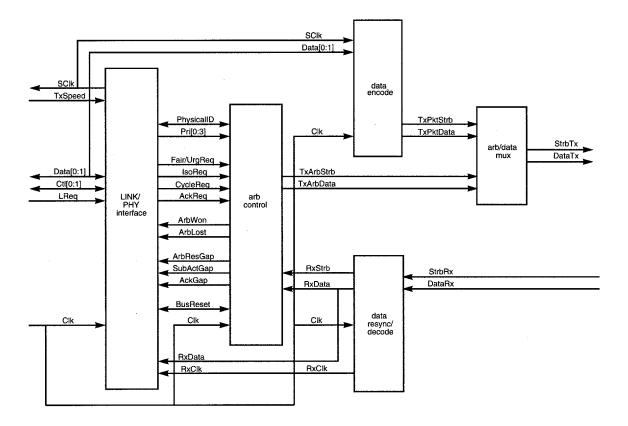

There are two physical environments for the Serial Bus: backplane and cable. The backplane environment uses two single-ended signals on a broadcast multitapped bus using backplane transceiver logic (BTL) or emitter coupled logic (ECL) transceiver technology at 49.152 Mbit/s or enhanced transistor-transistor logic (TTL) transceiver technology at 24.576 Mbit/s. In all cases, bus arbitration on the backplane is done using a dominant-mode-logic bit serial approach. The cable environment uses two low-voltage differential signals to connect devices in a noncyclic topology at 98.304 Mbit/s, 196.608 Mbit/s, and 393.216 Mbit/s data rates. The cable arbitration system uses a self-configuring hierachical request/grant protocol that supports hot plugging and widely varying physical topologies.

In addition to standard read/write/lock transactions, the Serial Bus provides extensive time-based services, including isochronous data transport (guaranteed latency and bandwidth) and an accurate submicrosecond global timebase for synchronizing events and data.

This standards effort started in 1986 at the request of the membership of the IEEE Microcomputer Standards Committee as an attempt to unify the different serial busses originally proposed as parts of the IEEE 1014 VME, IEEE 1296 Multibus II, and IEEE 896 FutureBus+<sup>®</sup> efforts. The original chair was Michael Teener, and much of the original architecture of this standard was invented by Mr. Teener, David James, and David Gustavson. In particular, the fairness and retry algorithms were originally proposed by David James during this early period.

As the proposed standard was developed, it attracted more interest from those that needed a much improved external I/O interconnect for multimedia information and for mass storage. This added the requirements for isochronous transport, much higher data rates, and a more rugged cable and connector system. To answer these needs

- a) David James and Michael Teener developed a isochronous access protocol that was compatible with the existing fairness scheme. This protocol was simplified and enhanced based on proposals by Ed Gardner.

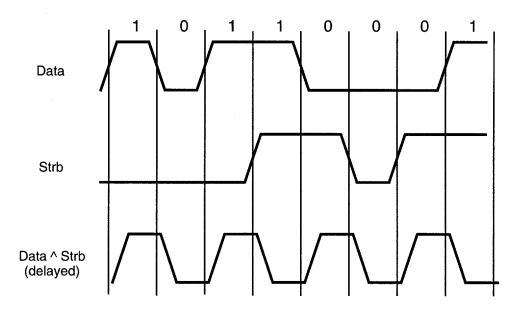

- b) Roger Van Brunt and Florin Oprescu developed a much improved physical layer for the cable environment, which was capable of 400 Mbit/s peak rates using low-cost digital complimentary-symmetry metal-oxide semiconductor (CMOS) technology. Forrest Crowell further reduced the complexity of the cable physical layer proposing the data-strobe encoding from INMOS. Florin Oprescu's self-configuring hierarchical arbitration protocol was also adopted at this time, with simplifications developed by Willam Duckwall.

- c) Andy Carter proposed the connector and cable system for the cable environment, based on original work done by Hosiden Corporation. The connector task group under the leadership of David Hatch refined that proposal to meet the requirements of all concerned.

- d) Greg Floryance, Bill Ham, and Max Bassler led the specification for the internal connection system for the cable environment. Bill Ham also worked to ensure that system level grounding and power issues were handled correctly.

- e) Thom Potyraj coordinated the development of the backplane environment and contributed much of its technical content.

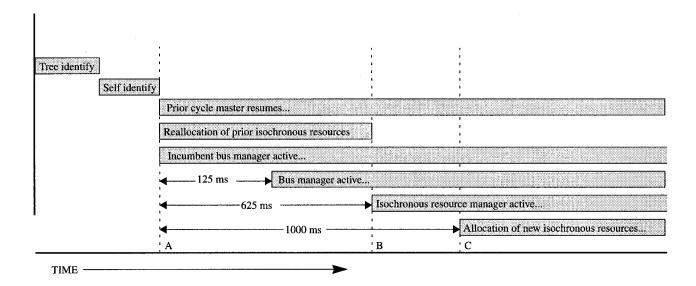

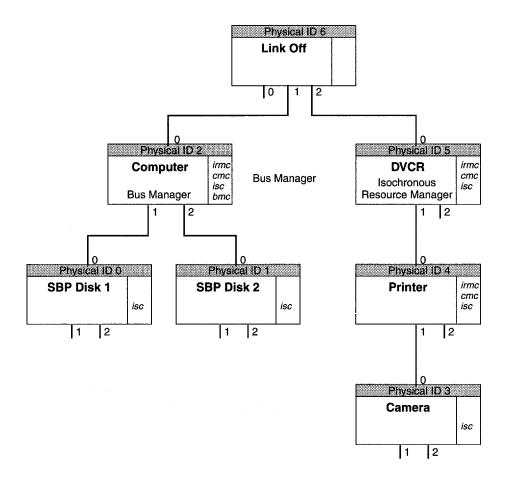

- f) Gerald Marazas defined the bus management protocols with extensive help from David James, Peter Johansson, Hisato Shima, Scott Smyers, and Michael Teener. Peter Johansson rewrote the bus management text during the ballot resolution process as the best way to respond to extensive ballot comments on this topic.

Gerald Marazas took over as chair of the working group in 1993, while Michael Teener continued as editor of the standard. Additional editing was done by Thom Potyraj for the backplane environment physical layer, Jeff Stai for the link and transaction layers, Gerald Marazas for the bus management layer, Bill Ham for the cable environment system

properties, Max Bassler and Greg Floryance for the internal device physical interface, Jim Baldwin for the PHY-Link interface definition, Florin Oprescu for the cable test procedures, and Steven Dunwoody for the shielding effectiveness test procedures.

#### Patent notice

Note: Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. The IEEE shall not be responsible for identifying all patents for which a license may be required by an IEEE standard or for conducting inquiries into the legal validity or scope of those patents that are brought to its attention.

The patent holder has, however, filed a statement of assurance that it will grant a license under these rights without compensation or under reasonable rates and nondiscriminatory, reasonable terms and conditions to all applicants desiring to obtain such a license. The IEEE makes no representation as to the reasonableness of rates and/or terms and conditions of the license agreement offered by the patent holder. Contact information may be obtained from the IEEE Standards Department.

# **Committee membership**

The following is a list of voting members of the IEEE P1394 working group at the time of publication.

Gerald Marazas, Chair Michael D. Teener (Editor) Ken Stewart, Secretary

| Max Bassler    | David V. James     | Scott Smyers      |

|----------------|--------------------|-------------------|

| Bob Bellino    | James Kuo          | Jeff Stai         |

| Charles Brill  | Lawrence J. Lamers | Roger Van Brunt   |

| Andy Carter    | Gene Milligan      | Hans H. Wang      |

| Greg Floryance | Jay Neer           | Harvey Watersdorf |

| Giles Frazier  | Florin Oprescu     | Alan Wetzel       |

| Bill Ham       | Thomas J. Potyraj  | Bob Whiteman      |

| Norm Harris    | Doug Riemer        | Michael Wingard   |

| David Hatch    | Ron Roberts        | _                 |

The following is a list of other major participants in the IEEE P1394 working group (those that attended at least three working group meetings in the last four years).

| Mark Andresen   | Dhiru Desai        | Mark Hassel       |

|-----------------|--------------------|-------------------|

| John Atwood     | Frank Duffy        | Rick Heidick      |

| James Baldwin   | Sam Duncan         | Dan Hillman       |

| Peter Bartlett  | W. P. Evertz       | Mark Jander       |

| Bryan Bell      | Stephen Finch      | Greg Kite         |

| Phil Bolton     | Mike Foster        | Lawence Kopp      |

| Paul L. Borrill | Richard Fryer      | Ralph Lachenmaier |

| David Brief     | Bob Gannon         | Michael Lazar     |

| Ed Cady         | Edward A. Gardner  | Wendell Lengefeld |

| Ramiro Calvo    | Charles Grant      | Fred Leung        |

| Mike Chastain   | Michael Griffin    | John Lohmeyer     |

| Kim Clohessy    | David B. Gustavson | John Lopata       |

| Forrest Crowell | Steffen Hagene     | Ivy Lui           |

| Wayne Davis     | Emil Hahn          | Don May           |

| Tom Debiec      | Ken Hallam         | Charles Monia     |

|                 |                    |                   |

Claude Mosley **Kevin Pokorney** Ray Muggli Jeffrey M. Rosa Gary Murdock Don Senzig Michael Nguyen Patricia Smith Dan O'Connor Robert N. Snively Erich Oetting Chris Stone Thomas A. Patrick Paul Sweazey Scott Petler Lars Thernsjö

Barry Thompson Joel Urban Mike Wenzel Lee Whetsel Dave Wickliff Yoshihiko Yano

#### The following persons served on the ballot response committee:

Max Bassler Larry Blackledge Andy Carter William Duckwall Bill Gamble Gary Hoffman

David V. James Peter Johansson Gerald Marazas Richard Mourn Dan O'Connor Amrish Patel

Scott Smyers

Jeff Stai

Michael D. Teener

Roger Van Brunt

Alan Wetzel

Thomas J. Potyraj

## The following persons were members of the balloting group:

M. Robert Aaron Ray S. Alderman Richard P. Ames Harry A. Andreas Keith D. Anthony Harrison A. Beasley Stephen E. Belvin Alan Beverly Christus Bezirtzoglou John Black Martin Blake Lim Boon Lum Paul L. Borrill Michael L. Bradley John C. Brightwell Charles Brill Hakon Ording Bugge Andrew L. Carter Stephen J. Cecil Andy B. Cheese C. H. Chen Joseph Chen Kim Clohessy Steven R. Corbesero Darrell Cox Patrick Crane Robert S. Crowder Dante Del Corso Roberto Divia Ian Dobson Samuel Duncan Sourav K. Dutta

Roger D. Edwards

Wayne P. Fischer

Gordon Force Giles Frazier Martin Freeman Richard E. Frver Paul J. Fulton Joseph D. George Stein Gjessing Patrick Gonia Julio Gonzalez Sanz Bruce Grieshaber William Groseclose Peter B. Gutgarts Mike Hasenfratz David Hawley Steven Hetzler Thomas G. Hillyer George Horansky **Edgar Jacques** David V. James Norman C. Joehlin David Kahn Richard H. Karpinski Stephen Kempainen James R. Koser Ernst H. Kristiansen Thomas M. Kurihara Ralph Lachenmaier Tuvia Lamdan Lawrence Lamers Conrad A. Laurvick Gerald E. Laws

Rollins Linser

Donald C. Loughry

Gerald A. Marazas

Roland Marbot Joseph R. Marshall William C. McDonald S. Fenton McDonald Thanos Mentzelopoulos Dhenna Moongilan Klaus-Dieter Mueller J. Michael Munroe J. D. Nicoud Gregory C. Novak Daniel C. O'Connor Katsuyuki Okada Peter Z. Onufryk Florin Oprescu Fred J. Orlando Michael Orlovsky Roman Orzol Granville Ott Elwood T. Parsons Mira Pauker Thomas Potyraj Suzanne L. Price Steve Quinton Gordon Robinson Fred U. Rosenberger John Rynearson Frederick E. Sauer Donald Senzig Gary K. Sloane Larry C. Sollman Robert K. Southard Richard C. Spratt Jeffrey Stai Larry Stein

Nobuaki Sugiura Eike G. Waltz Robert Widlicka Michael D. Teener Keith Weber Mark Williams Manu Thapar Thomas H. Wegmann Ronald T. Wolfe Michael G. Thompson H. Michael Wenzel David L. Wright Michael Timperman Alan Wetzel Forrest D. Wright Robert C. Tripi Colin Whitby-Strevens Yoshio Yamaguchi Roger Van Brunt Rob White Oren Yuen Yoshiaki Wakimura Dave Wickliff Janusz Zalewski

When the IEEE Standards Board approved this standard on December 12, 1995, it had the following membership:

Thomas Wicklund

E. G. "Al" Kiener, Chair Donald C. Loughry, Vice Chair Andrew G. Salem, Secretary

| Gilles A. Baril        | Jim Isaak              | Mary Lou Padgett  |

|------------------------|------------------------|-------------------|

| Clyde R. Camp          | Ben C. Johnson         | John W. Pope      |

| Joseph A. Cannatelli   | Sonny Kasturi          | Arthur K. Reilly  |

| Stephen L. Diamond     | Lorraine C. Kevra      | Gary S. Robinson  |

| Harold E. Epstein      | Ivor N. Knight         | Ingo Rüsch        |

| Donald C. Fleckenstein | Joseph L. Koepfinger*  | Chee Kiow Tan     |

| Jay Forster*           | D. N. "Jim" Logothetis | Leonard L. Tripp  |

| Donald N. Heirman      | L. Bruce McClung       | Howard L. Wolfman |

| Richard J. Holleman    | Marco W. Migliaro      |                   |

<sup>\*</sup>Member Emeritus

Paul Walker

Also included are the following nonvoting IEEE Standards Board liaisons:

Satish K. Aggarwal Steve Sharkey

Robert E. Hebner

Chester C. Taylor

Jonathan Zar

Mary Lynne Nielsen IEEE Standards Project Editor

Futurebus+ is a registered trademark of the Institute of Electrical and Electronics Engineers, Inc. SCSI is a registered trademark of SCSI Solutions.

NuBus is a registered trademark of Texas Instruments, Inc.

| CLA | AUSE                                            | PAGE |

|-----|-------------------------------------------------|------|

| 1.  | Overview                                        | 1    |

|     | 1.1 Scope                                       | 1    |

|     | 1.2 References                                  |      |

|     | 1.3 Document organization                       |      |

|     | 1.4 Serial Bus applications                     |      |

|     | 1.5 Service model                               |      |

|     | 1.6 Document notation                           |      |

|     | 1.7 Compliance                                  |      |

| 2.  | Definitions and abbreviations                   | 12   |

|     | 2.1 Conformance glossary                        | 12   |

|     | 2.2 Technical glossary                          | 12   |

| 3.  | Summary description                             | 16   |

|     | 3.1 Node and module architectures               |      |

|     | 3.2 Topology                                    |      |

|     | 3.3 Addressing                                  |      |

|     | 3.4 Protocol architecture                       |      |

|     | 3.5 Transaction layer                           | 21   |

|     | 3.6 Link layer                                  | 24   |

|     | 3.7 Physical layer                              |      |

|     | 3.8 Bus management                              | 45   |

| 4.  | Cable PHY specification                         | 46   |

|     | 4.1 Cable PHY services                          | 46   |

|     | 4.2 Cable physical connection specification     |      |

|     | 4.3 Cable PHY facilities                        |      |

|     | 4.4 Cable PHY operation                         |      |

| 5.  | Backplane PHY specification                     | 115  |

|     | 5.1 Backplane PHY services                      |      |

|     | 5.2 Backplane physical connection specification |      |

|     | 5.3 Backplane PHY facilities                    |      |

|     | 5.4 Backplane PHY operation                     |      |

|     | 5.5 Backplane initialization and reset          |      |

| 6.  | Link layer specification                        | 139  |

|     | 6.1 Link layer services                         |      |

|     | 6.2 Link layer facilities                       |      |

|     | 6.3 Link layer operation                        |      |

|     | 6.4 Link layer reference code                   |      |

| CLAU  | SE                                                                      | PAGE |

|-------|-------------------------------------------------------------------------|------|

| 7.    | Transaction layer specification                                         | 177  |

|       | 7.1 Transaction layer services                                          | 177  |

|       | 7.2 Transaction facilities                                              |      |

|       | 7.3 Transaction operation                                               | 181  |

|       | 7.4 CSR Architecture transactions mapped to Serial Bus                  | 203  |

| 8.    | Serial Bus management specification                                     | 203  |

|       | 8.1 Serial Bus management summary                                       | 203  |

|       | 8.2 Serial Bus management services                                      |      |

|       | 8.3 Serial Bus management facilities                                    | 207  |

|       | 8.4 Serial Bus management operations                                    |      |

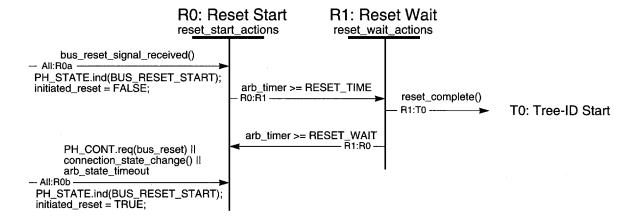

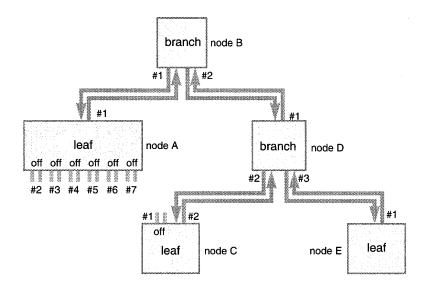

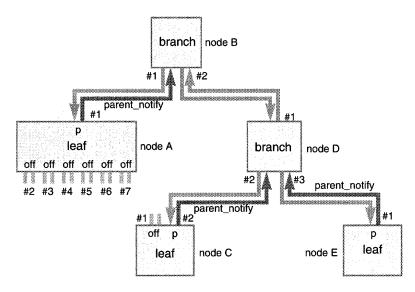

|       | 8.5 Bus configuration state machines (cable environment)                | 244  |

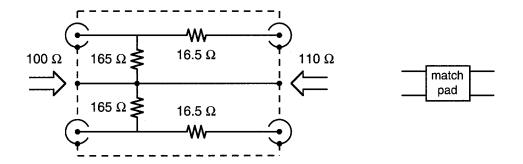

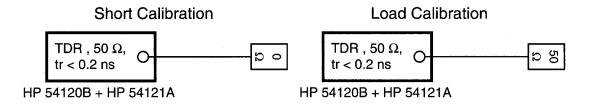

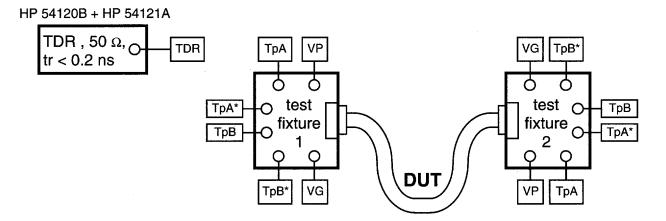

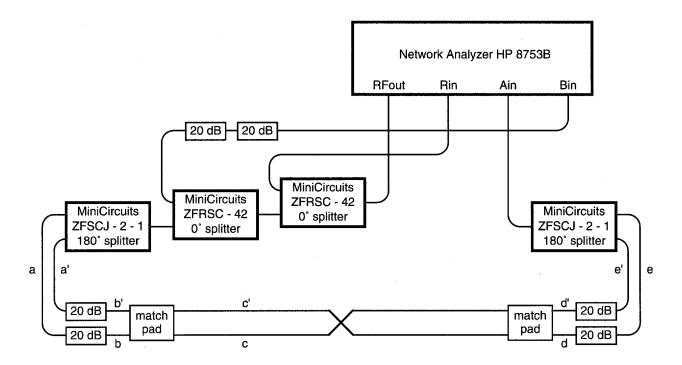

| Annex | A (Normative) Cable environment system properties                       | 250  |

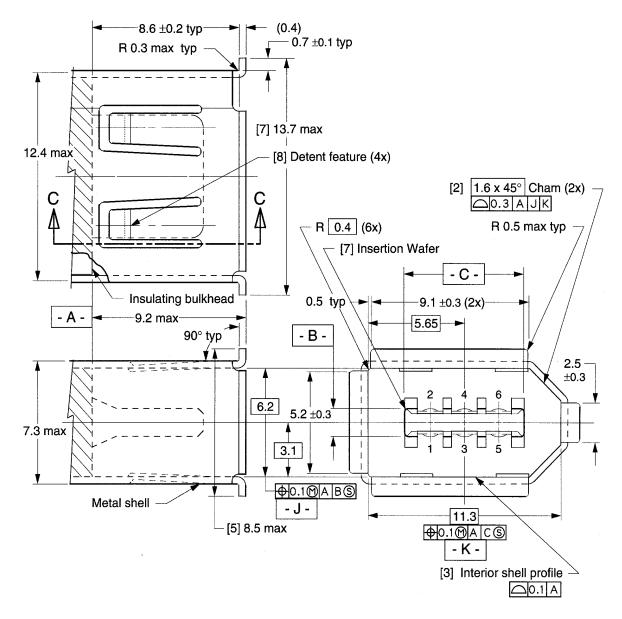

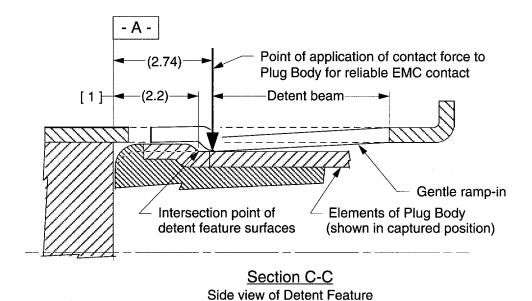

| Annex | B (Normative) External connector positive retention                     | 259  |

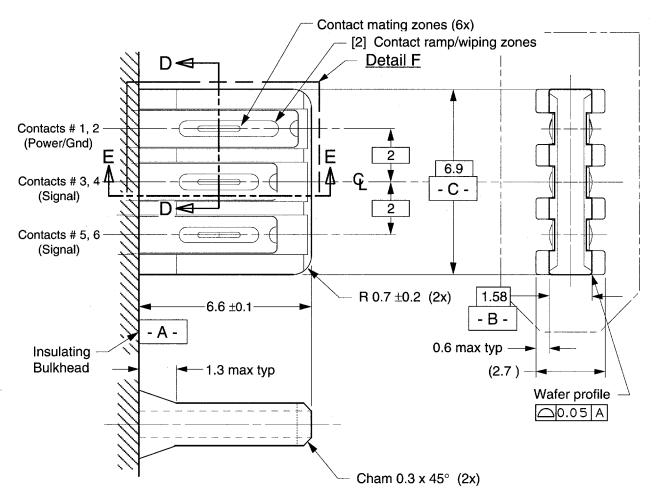

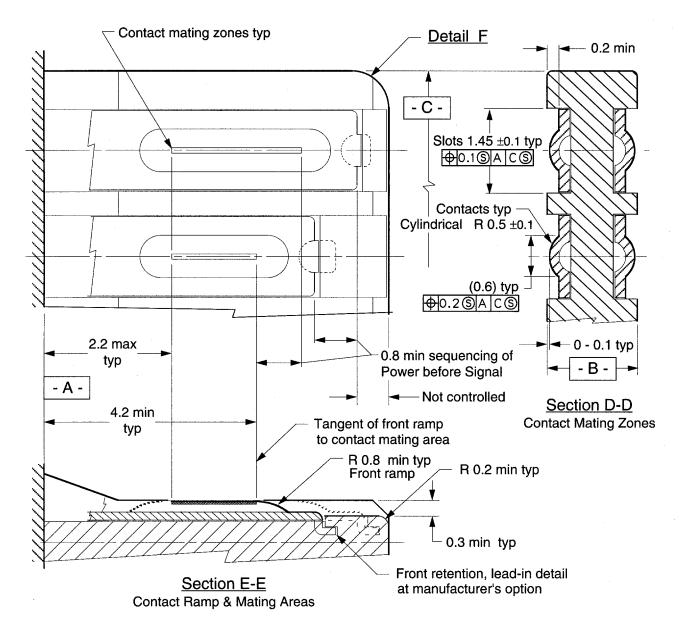

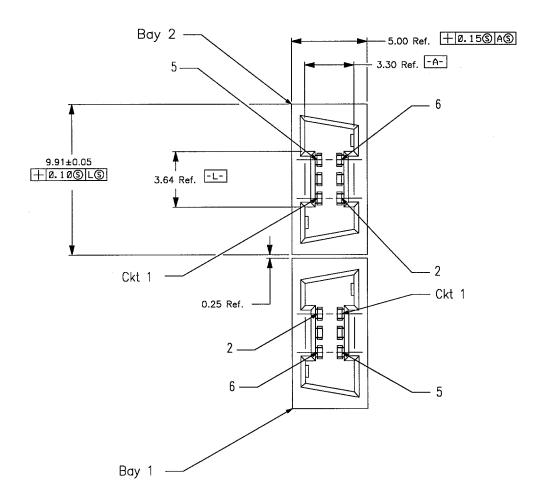

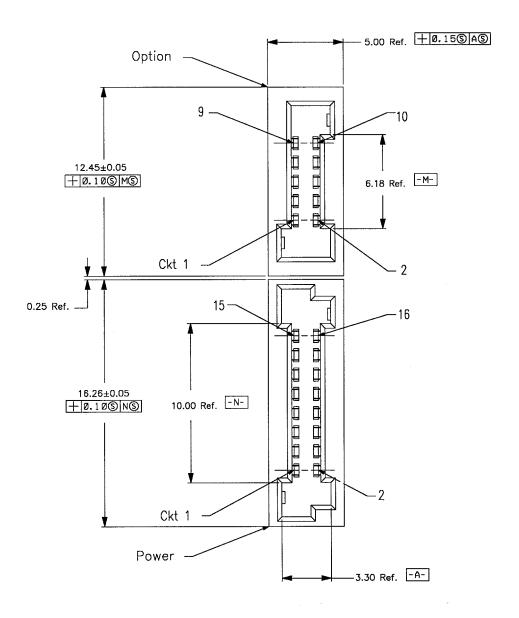

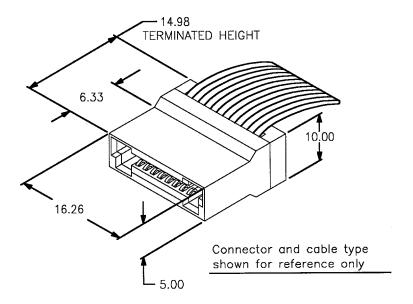

| Annex | C (Normative) Internal device physical interface                        | 261  |

| Annex | D (Informative) Backplane PHY timing formulas                           | 291  |

| Annex | E (Informative) Cable operation and implementation examples             | 301  |

| Annex | F (Informative) Backplane physical implementation example               | 320  |

| Annex | G (Informative) Backplane isochronous resource manager selection        | 326  |

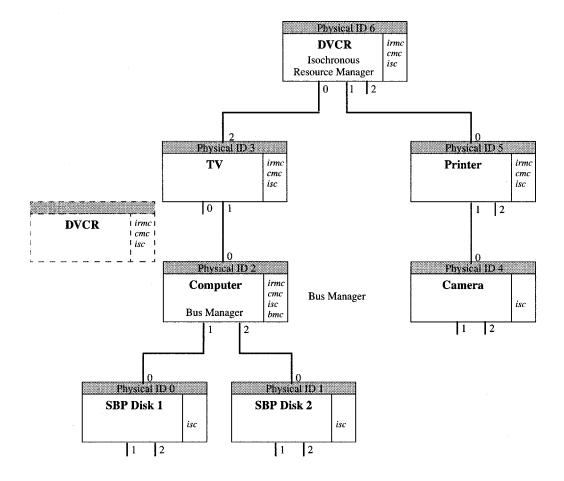

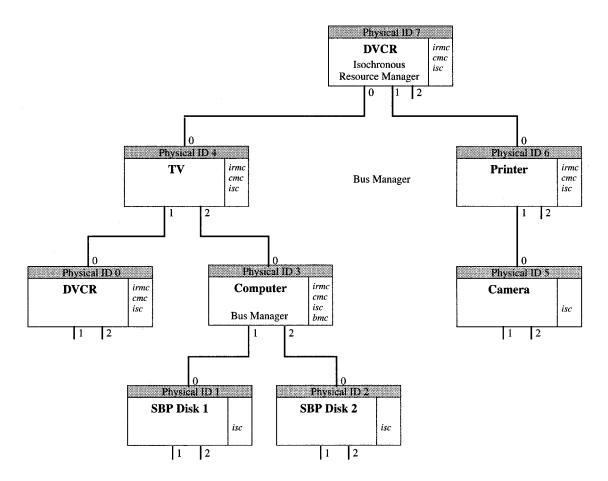

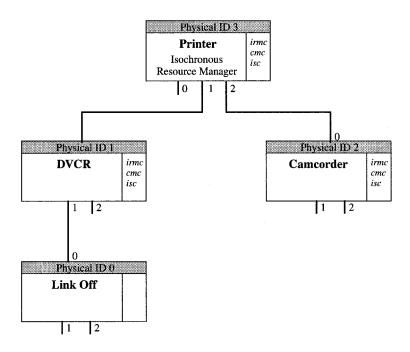

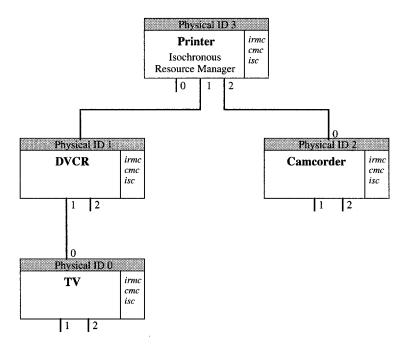

| Annex | H (Informative) Serial Bus configuration in the cable environment       | 328  |

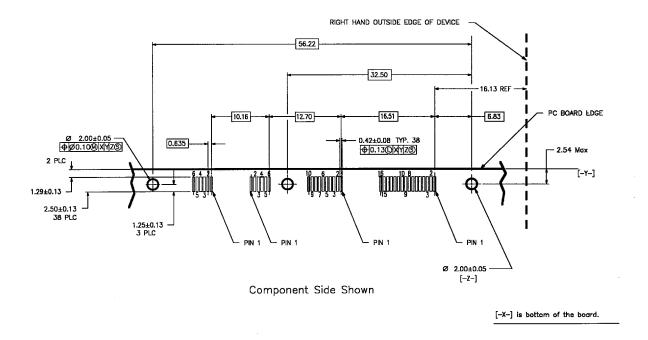

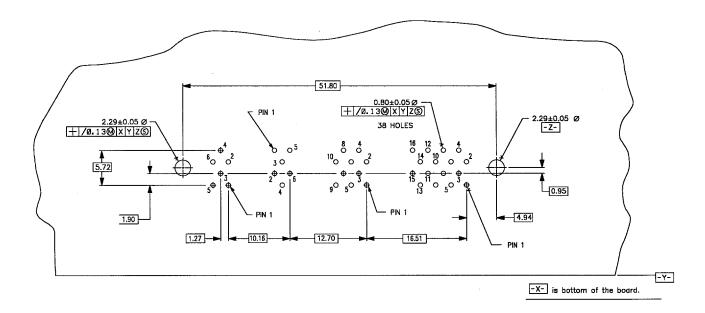

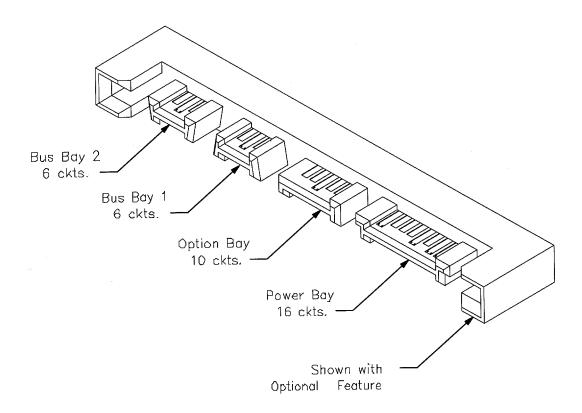

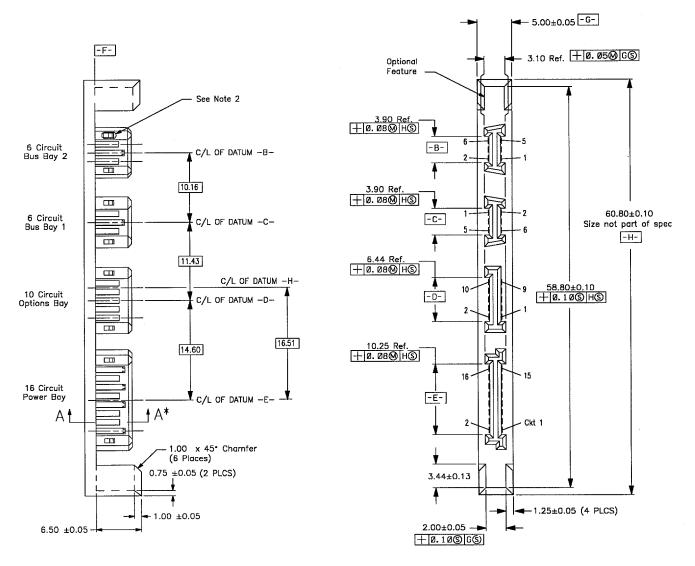

| Annex | I (Informative) Socket PCB terminal patterns and mounting               | 336  |

| Annex | J (Informative) PHY-link interface specification                        | 342  |

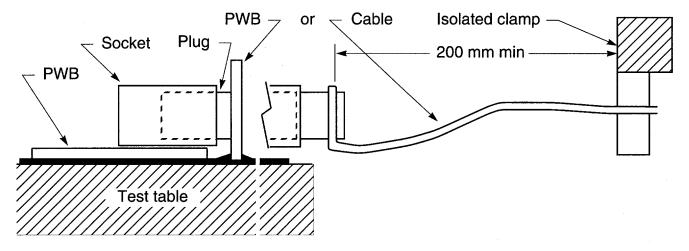

| Annex | K (Informative) Serial Bus cable test procedures                        | 360  |

| Annex | I. (Informative) Shielding effectiveness and transfer impedance testing | 379  |

# IEEE Standard for a High Performance Serial Bus

# 1. Overview

# 1.1 Scope

This standard describes a high-speed, low-cost Serial Bus suitable for use as a peripheral bus or a backup to parallel backplane buses. Highlights of the Serial Bus include

- a) Automatic assignment of node addresses—no need for address switches.

- b) Variable speed data transmission based on ISDN-compatible<sup>1</sup> bit rates from 24.576 Mbit/s for TTL backplanes to 49.152 Mbit/s for BTL backplanes to 98.304 Mbit/s, 196.608 Mbit/s, and 393.216 Mbit/s for the cable medium.

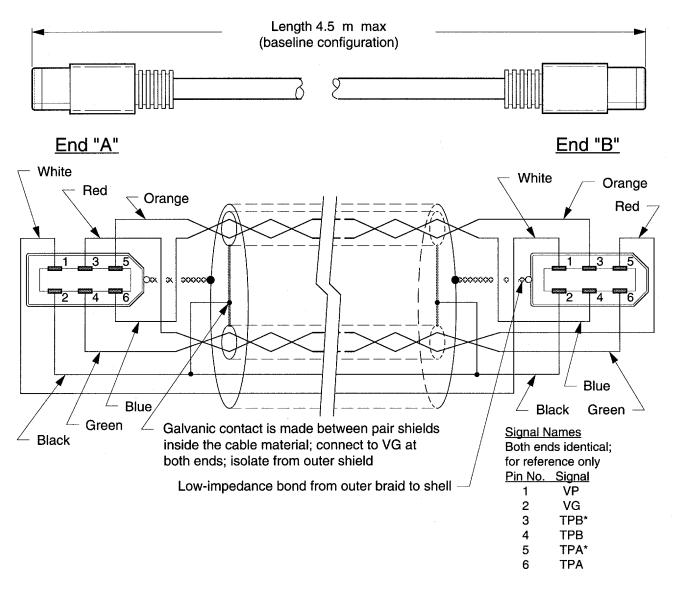

- c) The cable medium allows up to sixteen physical connections (cable hops), each up to 4.5 m, giving a total cable distance of 72 m between any two devices. Bus management recognizes smaller configurations to optimize performance.

- d) Bus transactions that include both block and single quadlet reads and writes, as well as an "isochronous" mode that provides a low-overhead guaranteed bandwidth service.

- e) A physical layer supporting both cable media and backplane buses.

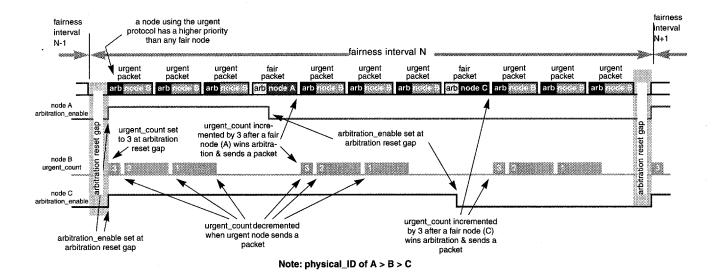

- f) A fair bus access mechanism that guarantees all nodes equal access. The backplane environment adds a priority mechanism, but one that ensures that nodes using the fair protocol are still guaranteed at least partial access.

- g) Consistent with ISO/IEC 13213:1994 (IEEE Std 1212-1991).

#### 1.2 References

This standard shall be used in conjunction with the following publications. When the following publications are superseded by an approved revision, the revision shall apply.

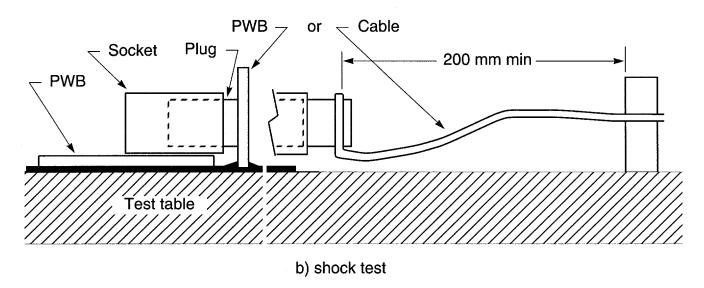

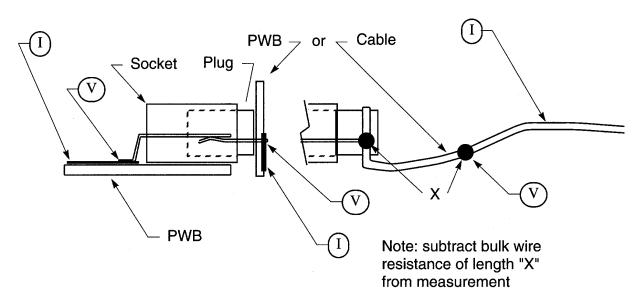

ANSI/EIA-364-B-90, Electrical Connector Test Procedures Including Environmental Classifications.<sup>2</sup>

<sup>&</sup>lt;sup>1</sup>The lowest data rate of 24.576 Mbit/s is exactly 18 times the 1.536 Mbit/s and 12 times the 2.048 Mbit/s ISDN primary rates. It is also an integer multiple of the ISDN basic rate and numerous other communication rates.

<sup>&</sup>lt;sup>2</sup>EIA publications are available from Global Engineering, 1990 M Street NW, Suite 400, Washington, DC, 20036, USA.

IEEE Std 896.2-1991, IEEE Standard for Futurebus+®—Physical Layer and Profile Specification (ANSI).<sup>3</sup>

IEEE Std 896.5-1993, IEEE Standard for Futurebus+<sup>®</sup>, Profile M (Military) (ANSI).

IEEE P896.6, IEEE Standard for Futurebus+ ® Telecommunications Systems, Profile T (Telecommunications).4

IEEE Std 1014-1987, IEEE Standard for a Versatile Backplane Bus: VMEbus (ANSI).

IEEE Std 1194.1-1991, IEEE Standard for Electrical Characteristics of Backplane Transceiver Logic (BTL) Interface Circuits (ANSI).

ISO/IEC 9899: 1990, Programming languages—C.<sup>5</sup>

ISO/IEC 10857: 1994 (ANSI/IEEE Std 896.1 1994 Edition) Information technology—Microprocessor systems—Futurebus+®—Logi cal Protocol Specification.

ISO/IEC 13213: 1994 [ANSI/IEEE Std 1212 1994 Edition], Information technology—Microprocessor systems—Control and Status Registers (CSR) Architecture for microcomputer buses.

## 1.3 Document organization

This standard contains this overview, a list of definitions, an informative summary description, chapters of technical specification, and application annexes. The new reader should read the document in order. The actual specification follows the summary and is organized from the bottom up; that is, the specification starts at the physical layer (cable and backplane), works up to the link layer, the transaction layer, and the bus management layer.

# 1.4 Serial Bus applications

Three primary applications have driven the design and architecture of the Serial Bus: an alternate for a parallel backplane bus, a low-cost peripheral bus, and a bus bridge between architecturally compatible 32-bit buses.

#### 1.4.1 Alternate bus

There are five main reasons for providing a serial bus on a system that already has a parallel bus:

- a) The many modules that make up a system might operate on different backplane bus standards, yet they need to work together.

- b) Although located within the same enclosure, the system is too large or physically disperse to use a single backplane, yet modules in the different backplanes have to communicate.

- c) One or more modules of a system are located neither on the same backplane nor within the same enclosure.

- d) A redundant data path increases fault tolerance. The system can use the Serial Bus to isolate and diagnose errors without depending on the failed parallel bus.

- e) Many system modules are price-sensitive and do not need the full bandwidth of a parallel bus.

<sup>&</sup>lt;sup>3</sup>IEEE publications are available from the Institute of Electrical and Electronics Engineers, 445 Hoes Lane, P.O. Box 1331, Piscataway, NJ 08855-1331, USA.

<sup>&</sup>lt;sup>4</sup>This IEEE standards project was not approved by the IEEE Standards Board at the time this publication went to press. For information about obtaining a draft, contact the IEEE.

<sup>&</sup>lt;sup>5</sup>ISO/IEC publications are available from the ISO Central Secretariat, Case Postale 56, 1 rue de Varembé, CH-1211, Genève 20, Switzerland/Suisse. ISO publications are also available in the United States from the Sales Department, American National Standards Institute, 11 West 42nd Street, 13th Floor, New York, NY 10036, USA.

#### 1.4.2 Low-cost peripheral bus

The Serial Bus can also be used as a powerful and low-cost peripheral interconnect. The compact Serial Bus cable and connector allow bandwidths comparable with existing I/O interconnect standards. The Serial Bus has the added advantage of architectural compatibility with parallel computer buses; this leads to lower communications overhead than limited function dedicated I/O interconnects.

# 1.4.3 Bus bridge

The Serial Bus architecture limits the number of nodes on any bus to 63, but supports multiple bus systems via bus bridges. The CSR Architecture defines the Serial Bus addressing structure, which allows almost 2<sup>16</sup> nodes.

A bus bridge normally eavesdrops on the bus, ignoring all transactions between local addresses but listening carefully for remote transactions. When the bridge receives a packet for a remote address, it forwards the packet to an adjacent bus. After initialization, the bus bridges are transparent to the system.

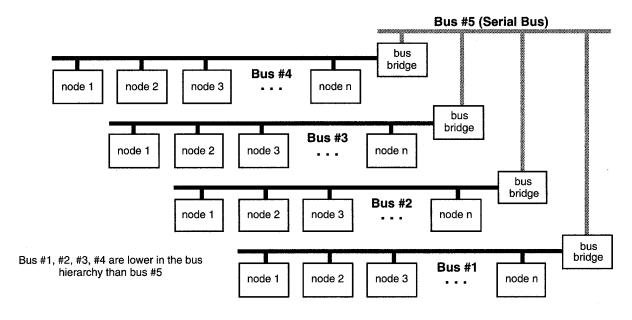

Although the Serial Bus may be used in many bus configurations, when used to bridge CSR-Architecture-compliant buses it is expected to be used mostly in a hierarchical bus fashion, as illustrated in figure 1.1 (where bus #5 is a Serial Bus and bridges together other CSR-Architecture-compliant buses 1 through 4; #1 could be IEEE 896 FutureBus+, 6 #2 could be IEEE 1596 Scalable Coherent Interface, and so on).

Figure 1.1—Example hierarchical bus topology

#### 1.5 Service model

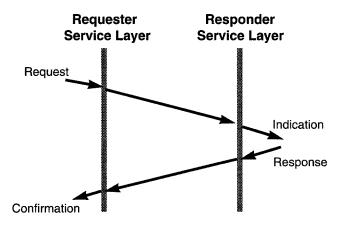

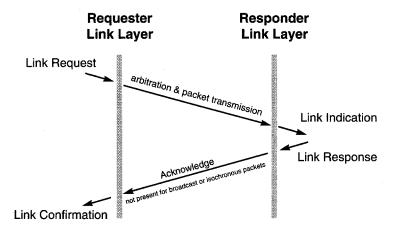

This standard uses a protocol model with multiple layers. Each layer provides services to communicate with the next higher layer and with the Serial Bus management layer. These services are abstractions of a possible implementation; an actual implementation may be significantly different and still meet all the requirements. The method by which these services are communicated between the layers is not defined by this standard. Four types of service are defined by this standard:

<sup>&</sup>lt;sup>6</sup>Information about references can be found in 1.2.

a) Request service. A request service is a communication from the higher layer to the lower layer to request the lower layer to perform some action. A request may also communicate parameters that may or may not be associated with an action. A request may or may not be confirmed by a confirmation. A data transfer request usually will trigger a corresponding indication on a peer node(s). (Since broadcast addressing is supported on the Serial Bus, it is possible for the request to trigger a corresponding indication on multiple nodes.)

- b) *Indication service*. An indication service is a communication from the lower layer to the upper layer to indicate a change of state or other event detected by the lower layer. An indication may also communicate parameters that are associated with the change of state or event. An indication may or may not be responded to by a response. A data transfer indication is originally caused by corresponding requests on a peer node.

- c) Response service. A response service is a communication from the higher layer to the lower layer to respond to an indication. A response may also communicate parameters that indicate the type of response to the indication. A response is always associated with an indication. A data transfer response usually will trigger a corresponding confirmation on a peer node.

- d) Confirmation service. A confirmation service is a communication from the lower layer to the upper layer to confirm a request service. A confirmation may also communicate parameters that indicate the completion status of the request, or any other status. A confirmation is always associated with a request. For data transfer requests, the confirmation may be caused by a corresponding response on a peer node.

If all four service types exist, they are related as shown by the following figure:

Figure 1.2—Service model

#### 1.6 Document notation

# 1.6.1 Mechanical notation

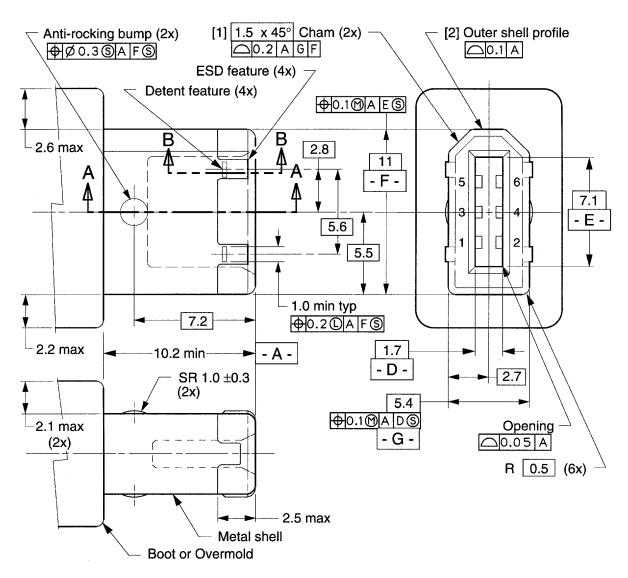

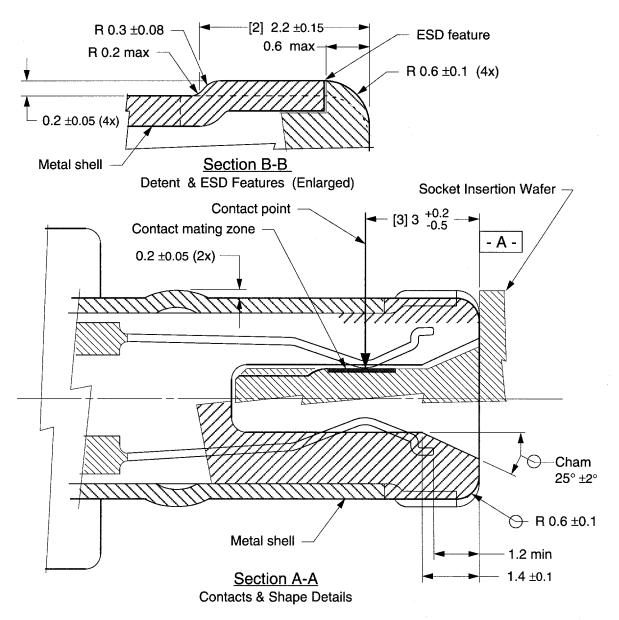

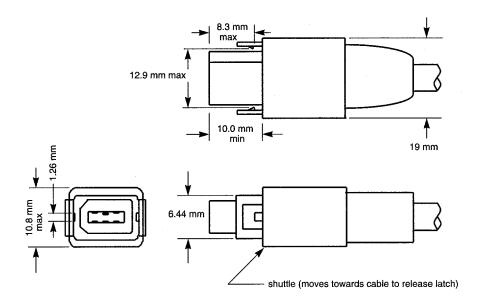

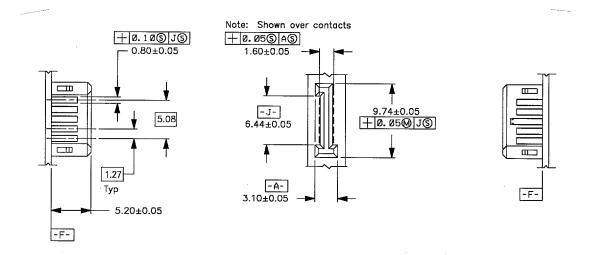

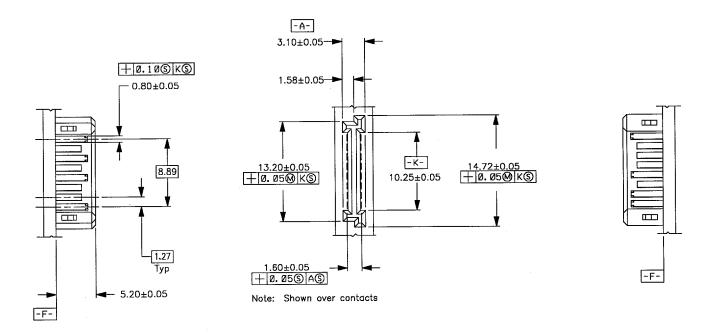

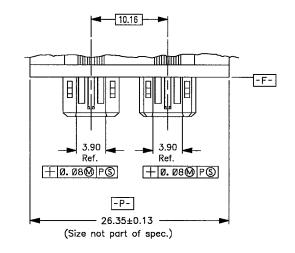

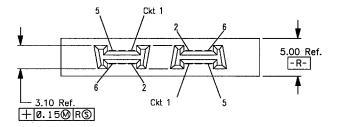

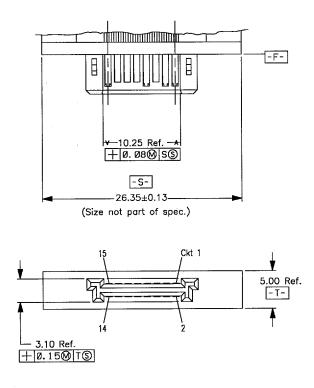

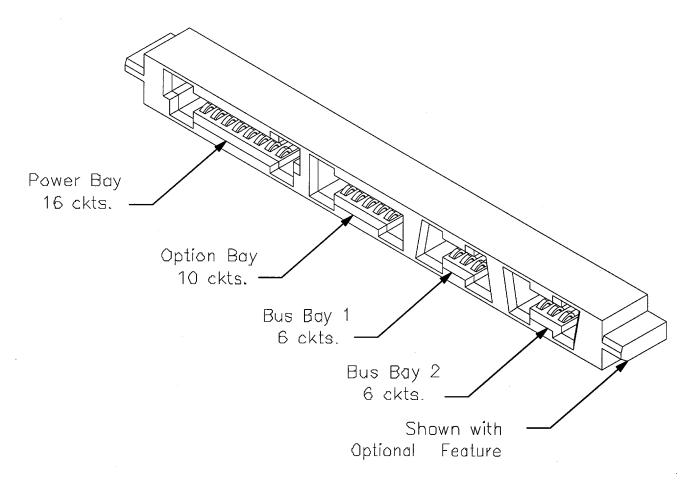

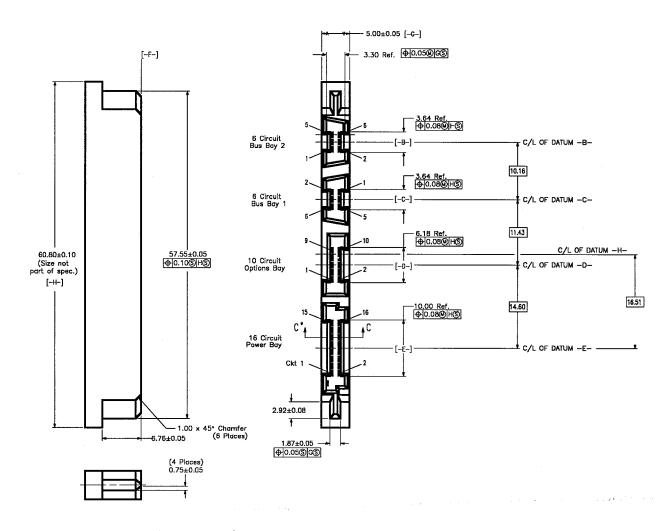

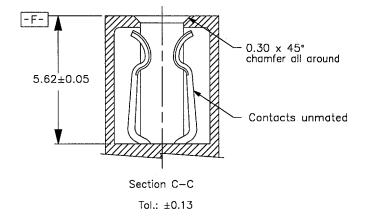

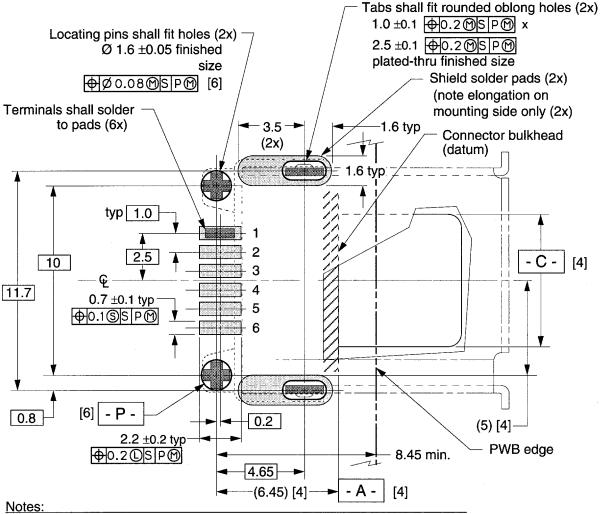

All mechanical drawings in this document use millimeters as the standard unit and follow ANSI Y14.2 and ANSI Y14.5 1982 formats.

# 1.6.2 Signal naming

All electrical signals are shown in all uppercase characters, and active-low signals have the suffix "\*". For example: TPA and TPA\* are the normal and inverted signals in a differential pair.

#### 1.6.3 Size notation

The Serial Bus description avoids the confusing terms half-word, word, and double-word, which have widely different definitions depending on the word size of the processor. In their place, the Serial Bus description uses terms established in previous IEEE bus standards, which are independent of the processor. These terms are illustrated in table 1.1.

| Table 1.1—Size notation examples |                      |                      |                                                |

|----------------------------------|----------------------|----------------------|------------------------------------------------|

| Size (in bits)                   | 16-bit word notation | 32-bit word notation | IEEE standard notation (used in this standard) |

| 8                                | byte                 | byte                 | byte                                           |

| 16                               | word                 | half-word            | doublet                                        |

| 32                               | long-word            | word                 | quadlet                                        |

| 64                               | quad-word            | double               | octlet                                         |

Table 1.1—Size notation examples

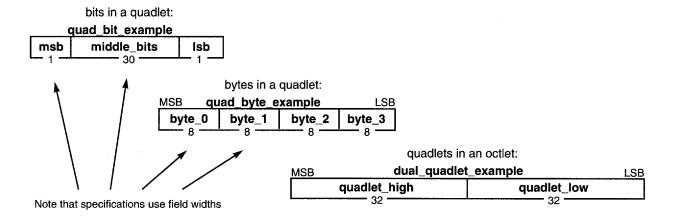

The Serial Bus uses big-endian ordering for byte addresses within a quadlet and quadlet addresses within an octlet. For 32-bit quadlet registers, byte 0 is always the most significant byte of the register. For a 64-bit quadlet-register pair, the first quadlet is always the most significant. The field on the left (most significant) is transmitted first, and within a field the most significant bit is also transmitted first. This ordering convention is illustrated in figure 1.3.

Figure 1.3—Bit and byte ordering

Although Serial Bus addresses are defined to be big-endian, their data values may also be processed by little-endian processors. To minimize the confusion between conflicting notations, the location and size of bit fields are usually specified by width, rather than their absolute positions, as is also illustrated in figure 1.3.

When specific bit fields must be used, the CSR Architecture convention of consistent big-endian numbering is used. Hence, the most significant bit of a quadlet ("msb" in figure 1.2) will be labeled "quad\_bit\_example[0]," the most significant byte of a quadlet ("byte\_0")will be labeled "quad\_byte\_example[0:7]," and the most significant quadlet in an octlet ("quadlet\_high")will be labeled "dual\_quadlet\_example[0:31];."

The most significant bit shall be transmitted first for all fields and values defined by this standard, including the data values read or written to the control and status registers (CSRs) defined in clause 8..

#### 1.6.4 Numerical values

Decimal, hexadecimal, and binary numbers are used within this document. For clarity, the decimal numbers are generally used to represent counts, hexadecimal numbers are used to represent addresses, and binary numbers are used to describe bit patterns within binary fields.

Decimal numbers are represented in their standard 0, 1, 2,... format. Hexadecimal numbers are represented by a string of one or more hexadecimal (0-9, A-F) digits followed by the subscript 16. Binary numbers are represented by a string of one or more binary (0,1) digits, followed by the subscript 2. Thus the decimal number "26" may also be represented as " $1A_{16}$ " or " $11010_2$ ". In C++ code examples, hexadecimal numbers have a "0x" prefix and binary numbers have a "0x" prefix, so the decimal number "26" would be represented by "0x1A" or "0b11010."

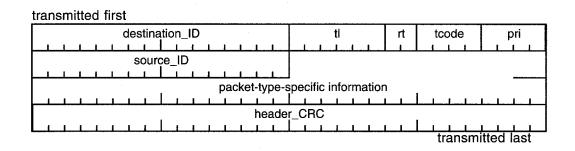

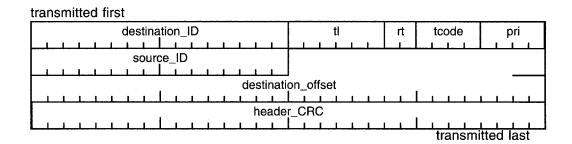

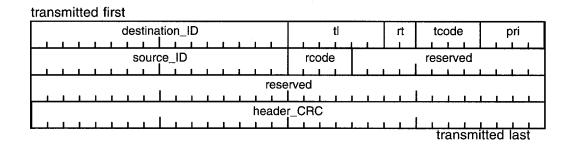

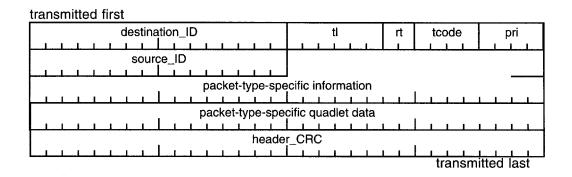

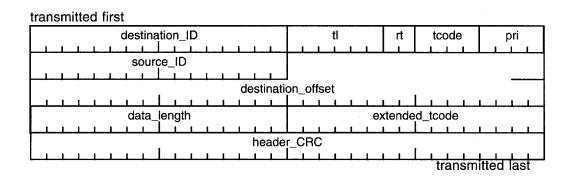

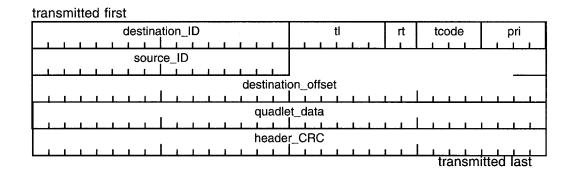

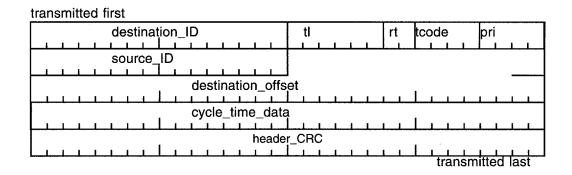

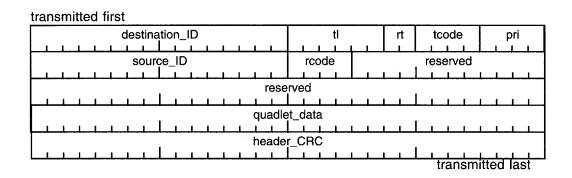

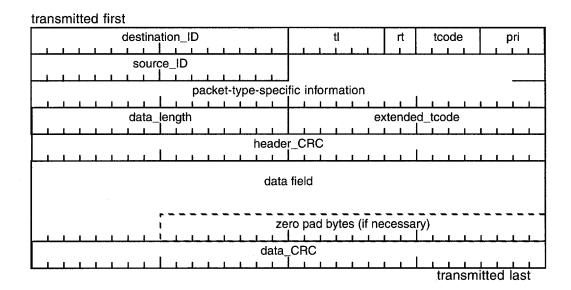

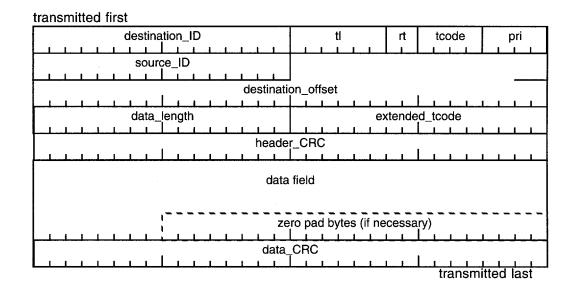

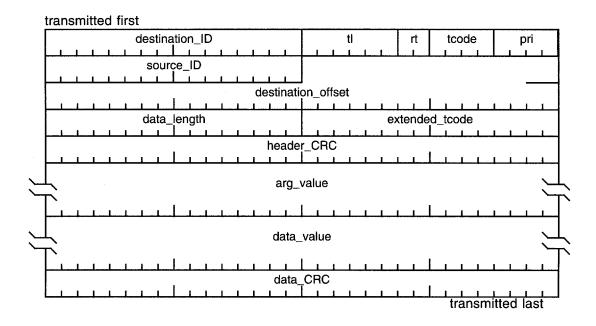

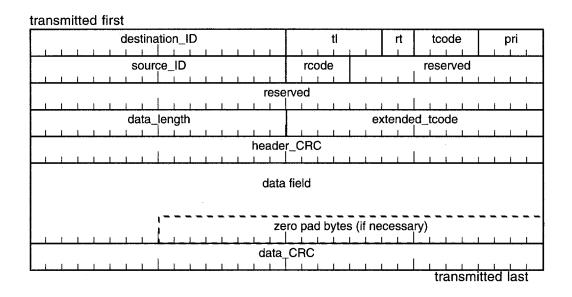

#### 1.6.5 Packet formats

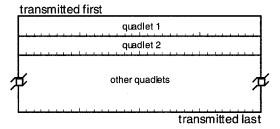

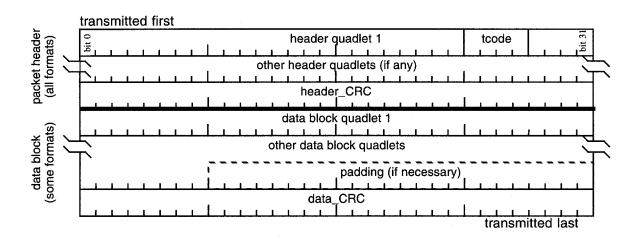

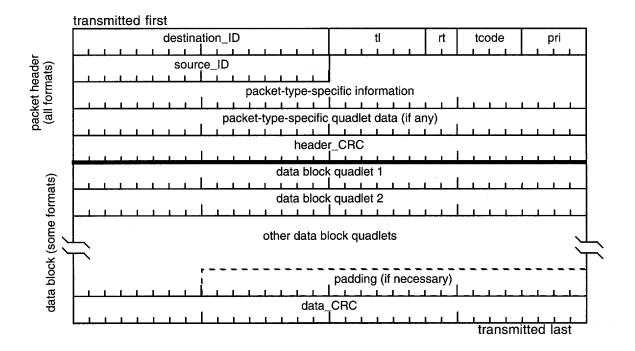

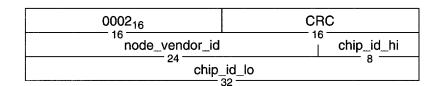

Serial Bus packets consist of a sequence of quadlets. Packet formats are shown using the style given in figure 1.4.

Figure 1.4—Example packet format

Fields appear in packet formats with their correct position and widths. Field widths are also stated explicitly in field descriptions. Bits in a packet are transmitted starting with the upper leftmost bit and finishing with the bottom rightmost bit. Given the rules in 1.6.3, this means that all fields defined in this standard are sent most significant bit first.

## 1.6.6 Register formats

All Serial Bus registers are documented in the style used by the CSR Architecture.

#### 1.6.7 C++ code notation

The conditions and actions of the state machines are formally defined by C++ code. Since many C++ code operators are not obvious to the casual reader, their meanings are summarized in table 1.2.

Table 1.2—Specific expression summary

| Expression | Description                                                                                              |  |

|------------|----------------------------------------------------------------------------------------------------------|--|

| ~I         | Bitwise complement of integer I                                                                          |  |

| ++I        | Pre-increment of integer I (I is incremented, then used in the expression)                               |  |

| I          | Pre-decrement of integer I (I is decremented, then used in the expression)                               |  |

| І^Ј        | Bitwise XOR of integers I and J                                                                          |  |

| I & J      | Bitwise AND of integer values I and J                                                                    |  |

| I   J      | Bitwise OR of integer values I and J                                                                     |  |

| I << J     | Value of I, shifted left by J bits, zero fill                                                            |  |

| I >> J     | Value of I, shifted right by J bits, zero fill if I is an unsigned number, sign extension if I is signed |  |

| I == J     | Equality test, true if I is equal to J                                                                   |  |

| I != J     | Inequality test, true if I is not equal to J                                                             |  |

| !B         | Logical negation of boolean variable B                                                                   |  |

| A && B     | Logical AND of boolean values A and B                                                                    |  |

| A    B     | Logical OR of boolean values A and B                                                                     |  |

In addition, the nonstandard data types (actually, object classes) listed in table 1.3 are supported.

Table 1.3—Serial Bus data types

| Data type | Data type Description                                                        |  |

|-----------|------------------------------------------------------------------------------|--|

| timer     | real value (units of seconds) that autonomously increments at a defined rate |  |

| boolean   | One bit value where 1 is true and 0 is false                                 |  |

Other, more specific data types are defined in the clauses where they are relevant.

All C++ code is executed as if it takes zero time. Time only elapses when the following function is called ("time" is in units of seconds):

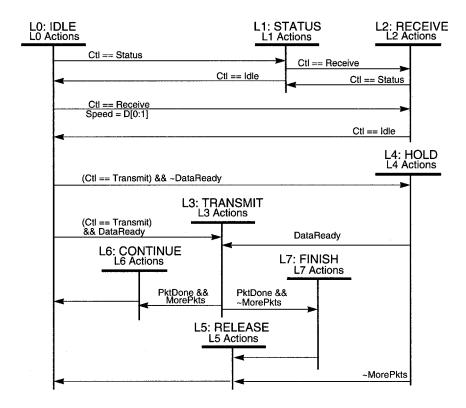

# 1.6.8 State machine notation

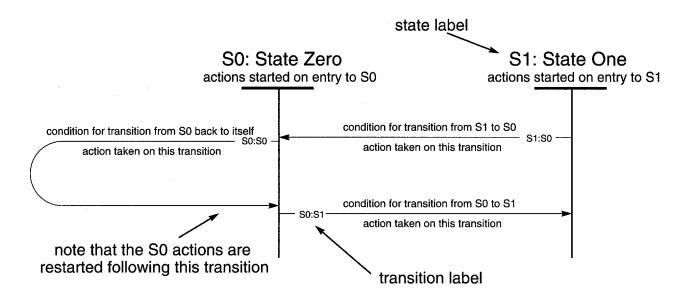

All state machines in this standard use the style shown in figure 1.5.

Figure 1.5—State machine example

These state machines make three assumptions:

- a) Time elapses only within discrete states.

- b) State transitions are logically instantaneous, so the only actions taken during a transition are setting flags and variables and sending signals.

- c) Every time a state is entered, the actions of that state are started. Note that this means that a transition that points back to the same state will restart the actions from the beginning.

#### 1.6.9 CSR, ROM, and field notation

This standard describes a number of CSRs and fields within these registers. To distinguish register and field names from node states or descriptive text, the register name is always capitalized. Thus, the notation STATE\_CLEAR. *lost* is used to describe the lost bit within the STATE\_CLEAR register. In this standard, a bold type font is used to emphasize a term, particularly on its first usage.

All CSRs are quadlets and are quadlet aligned. The address of a register (which is always a multiple of 4) is specified as the byte offset from the beginning of the initial register space. When a range of register addresses is described, the ending address is the address of the last register, which is also a multiple of 4. These addressing conventions are illustrated in table 1.4.

Table 1.4—Example CSR addressing conventions

| Offset | Register Name Description |                          |

|--------|---------------------------|--------------------------|

| 0      | STATE_CLEAR               | First CSR location       |

| 4–12   | OTHER_REGISTERS           | Next three CSR locations |

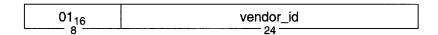

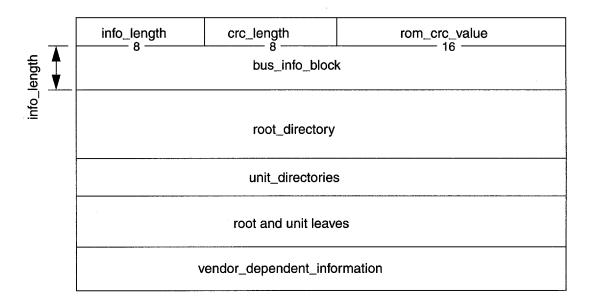

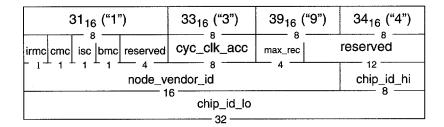

This document describes a number of configuration ROM entries and fields within these entries. To distinguish ROM entry and field names from node states or descriptive text, the first character of the entry name is always capitalized. Thus, the notation Bus\_Info\_Block.cmc is used to describe the cmc bit within the Bus\_Info\_Block entry.

Entries within temporary data structures, such as packets, timers, and counters, are lowercased (following normal Clanguage conventions) and are formatted in a fixed-space typeface. Examples are arb\_timer and connected[i].

NOTE — Within the C++ code, the character formatting is not used, but the capitalization rules are followed.

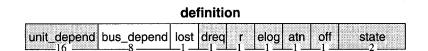

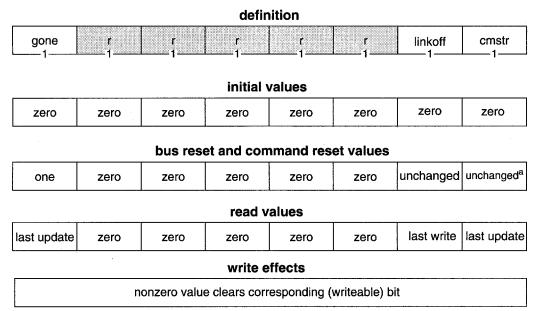

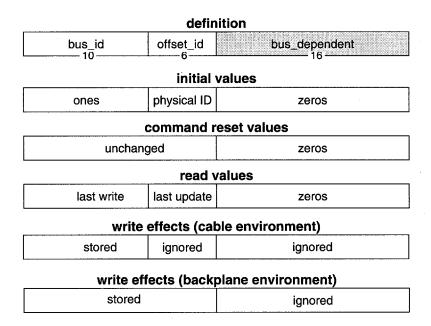

# 1.6.10 Register specification format

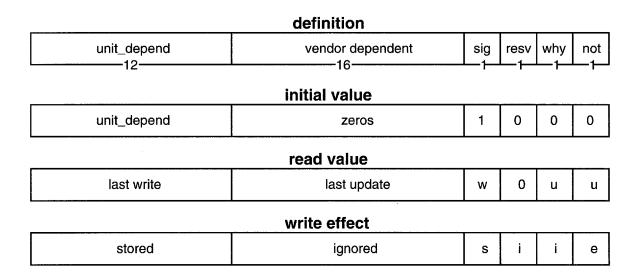

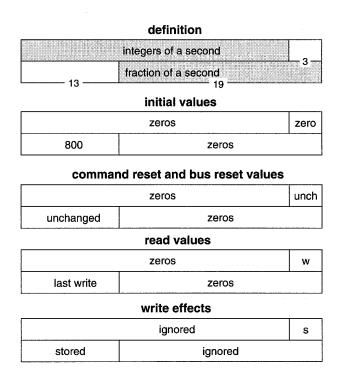

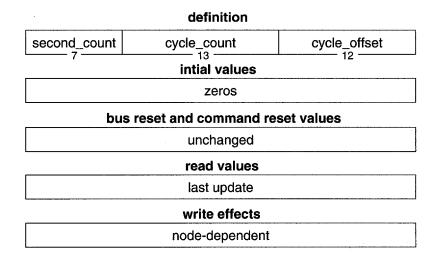

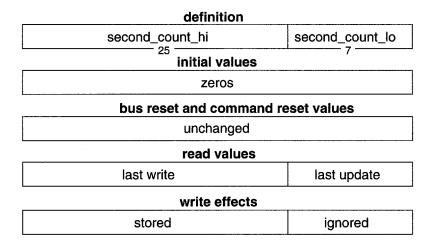

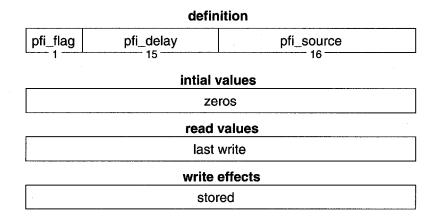

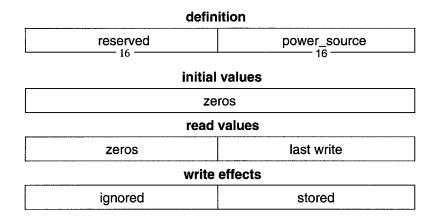

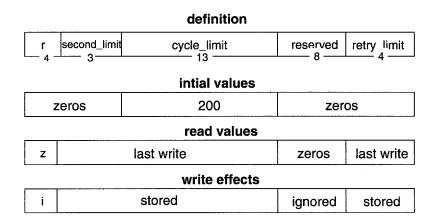

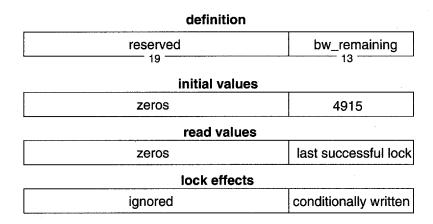

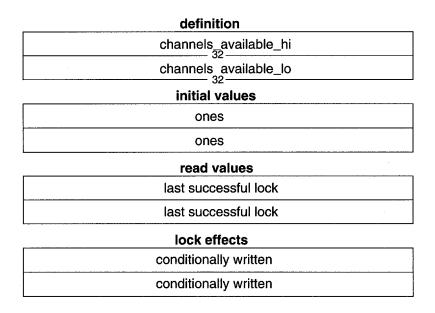

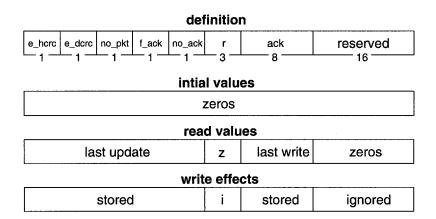

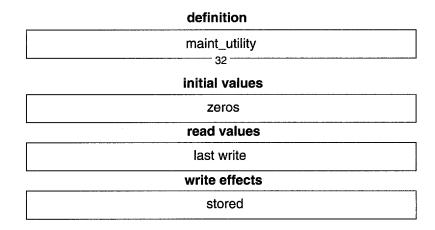

This document precisely defines the format and function of Serial Bus-specific CSRs. Some of these registers are read only, some are read-write, and some have special side-effects on writes. To define the content and function of these CSRs wholly, their specification includes the format (the sizes and names of bit field locations), the initial value of the register (if not zero), the value returned when the register is read, and the effect(s) when the register is written. An example register is illustrated in figure 1.6.

Figure 1.6—CSR format specification (example)

The register definition lists the names of register fields. These names are descriptive, but the fields are defined in the text; their function should not be inferred solely from their names. However, the register definition fields in table 1.5 have generic meanings.

Table 1.5—Register definition fields

| Name             | Abbreviation  | Definition                                                                                                                                                          |

|------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| unit dependent   | unit_depend   | The meaning of this field shall be defined by the unit architecture(s) of the node.                                                                                 |

| vendor dependent | vendor_depend | The meaning of this field shall be defined by the vendor of the node.  Within a unit architecture, the unit_dependent fields may be defined to be vendor dependent. |

The CSRs defined in this document shall be initialized when power is restored (a **power\_reset**) or when a quadlet is written to its RESET\_START register (a **command\_reset**). For most registers, the initial value after a power\_reset or command\_reset is the same. When the initial CSR values differ, the two initial values are explicitly illustrated.

The read value fields in table 1.6 have a generic meaning.

Table 1.6—Read value fields

| Name        | Abbreviation | Definition                                                                                               |

|-------------|--------------|----------------------------------------------------------------------------------------------------------|

| last write  | w            | The value of the data field shall be the value that was previously written to the same register address. |

| last update | u            | The value of the data field shall be the last value that was updated by node hardware.                   |

The write-effect fields in table 1.7 have a generic meaning.

Table 1.7—Write value fields

| Name    | Abbreviation | Definition                                                                                                                                       |

|---------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| stored  | s            | The value of the written data field shall be immediately visible to reads of the same register.                                                  |

| ignored | i            | The value of the written data field shall be ignored; it shall have no effect on the state of the node.                                          |

| effect  | e            | The value of the written data field shall have an effect on the state of the node, but is not immediately visible to reads of the same register. |

The register description specifies its bus transaction read/write characteristics, as well as whether it is a required register. A read-write register (**RW**) is expected to be read and written via bus transactions; a read-only register (**RO**) is expected to only be read; a write-only register (**WO**) is expected to only be written. Although reads of WO registers and writes of RO registers are not expected, the register definition still defines their results.

#### 1.6.11 Reserved registers and fields

Some CSR addresses correspond to unimplemented registers. This includes optional registers (when the option is not implemented) and reserved registers (which are required to be unimplemented). The capabilities of these unimplemented registers are exactly defined to minimize conflicts between current implementations and future definitions, as illustrated in figure 1.7.

definition

unimplemented

32

initial value

zeros

read value

zeros

write effect

ignored

Figure 1.7—Reserved fields

Within an implemented register, a field that is reserved for future revisions of this standard is labeled *reserved* (sometimes abbreviated as *r* or *resv*). For a reserved field within an implemented register, the field is ignored on a write and returns zero on a read, as formally specified below:

#### reserved:

Required. Reserved for future definitions.

Initial value: Zero.

Read4 value: Shall return zero.

Write4 effect: Shall be ignored.

# 1.6.12 Operation description priorities

The description of operations in this standard are done in three ways: state machines, C++ code segments, and English language. If more than one description is present, then priority shall be given first to the state machines, then the C++ code segments, and finally to the English text (including the state machine notes).

# 1.7 Compliance

## 1.7.1 CSR Architecture compliance

The Serial Bus follows ISO/IEC 13213: 1994. Specifically:

- a) Addressing: the Serial Bus uses 64-bit fixed addressing. See 3.3.

- b) Transactions:

- 1) The CSR-Architecture-defined transactions of read1-read64, write1-write64, lock4, and lock8 are equivalent to the Serial Bus transactions described in clause 7.3.5.2. The Serial Bus also specifies byte-aligned block read and write transactions from 1 byte to 2048 bytes, depending on the data rate as described in table 6.4.

- 2) The clock strobe signal is implemented by the Serial Bus cycle\_start packet described in clause 6.3.2.

- c) Error status codes: type\_error, address\_error, and conflict\_error are all possible values of the status returned in a transaction response. The Serial Bus calls these "response codes," and there are additional bus-specific values. See table 6.11 for more details.

- d) Resets: Power reset and command reset are described in clause 8.3.1.3.

- e) STATE\_CLEAR: the bus\_depend bits of the STATE\_CLEAR register are all optional and are described in clause 8.3.1.5.

- f) NODE\_IDs:

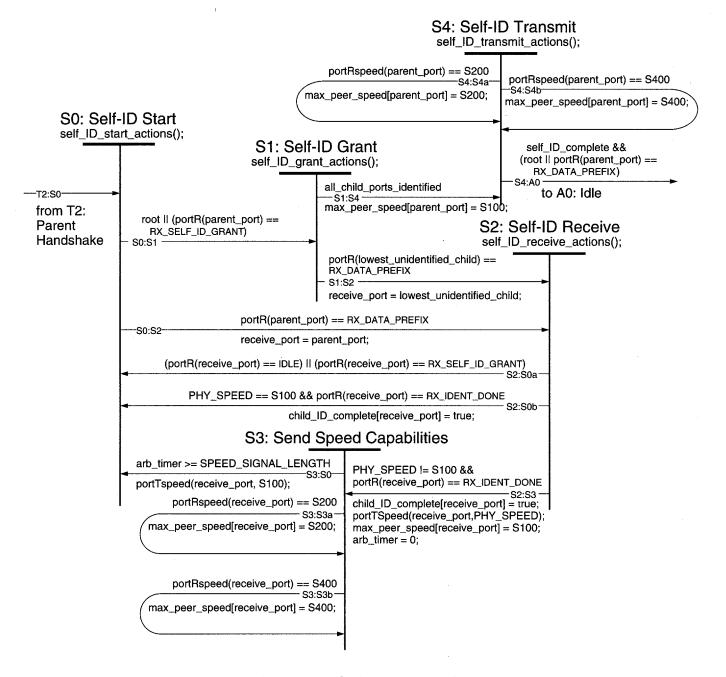

- offset\_id: The Serial Bus calls this the "physical\_ID." For cable environments, the values are chosen during the self-ID process described in clause 4.4.2.3. In such environments, this physical\_ID is a read-only value. For backplane environments, these values are dependent on the application environment (see clause 5.4.2.1).

- 2) bus depend: The bus-dependent field shall be all zeros and is a read-only value.

- g) SPLIT\_TIMEOUT\_HI and SPLIT\_TIMEOUT\_LO: Only the low-order 3 bits of SPLIT\_TIMEOUT\_HI (seconds) are to be implemented (8 s maximum timeout), and the higher order 13 bits of SPLIT\_TIMEOUT\_LO count at a granularity of 125 μs, not 1/8192 s.

- h) Bus-dependent registers: The Serial Bus has the following optional CSRs; see clause 8.3.2.2.7 for details:

- 1) CYCLE\_TIME

- 2) BUS\_TIME

- 3) POWER\_FAIL\_IMMINENT

- 4) POWER SOURCE

- 5) INCUMBENT ANSWER

- 6) BANDWIDTH ALLOCATE

- 7) CHANNELS AVAILABLE HI

- 8) CHANNELS\_AVAILABLE\_LO

- 9) MAINTENANCE CONTROL

- 10) MAINTENANCE UTILITY

- Bus\_dependent ROM entries: The Serial Bus has the following extra ROM entries; see clause 8.3.2.3.10 for details:

- 1) Node\_Capabilities root entry

- 2) NodeUniqueId leaf

- 3) Bus\_Dependent\_Info directory

- 4) Topological Map location

- 5) Speed\_Map location

# 1.7.2 Serial Bus physical layers

The following minimum performance is required:

- a) Cable Physical Layer:

- 1) 98.304 Mbit/s data bit transmit/receive

- b) Backplane Physical Layer:

- 1) Data bit transmit/receive at 49.152 Mbit/s for BTL and ECL.

- 2) Data bit transmit/receive at 24.576 Mbit/s for TTL.

# 2. Definitions and abbreviations

# 2.1 Conformance glossary

Several keywords are used to differentiate between different levels of requirements and optionality, as follows:

- **2.1.1 expected:** A keyword used to describe the behavior of the hardware or software in the design models assumed by this standard. Other hardware and software design models may also be implemented.

- **2.1.2 may:** A keyword that indicates flexibility of choice with no implied preference.

- **2.1.3 shall:** A keyword indicating a mandatory requirement. Designers are required to implement all such mandatory requirements to ensure interoperability with other products conforming to this standard.

- **2.1.4 should:** A keyword indicating flexibility of choice with a strongly preferred alternative. Equivalent to the phrase "is recommended."

# 2.2 Technical glossary

The following are terms that are used within this standard:

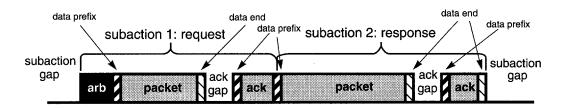

- 2.2.1 acknowledge: An acknowledge packet.

- 2.2.2 acknowledge gap: The period of idle bus between the end of a packet and the start of an acknowledge.

- **2.2.3 acknowledge packet:** A link-layer packet returned by a destination node back to a source node in response to most primary packets. An acknowledge packet is always exactly 8 bits long.

- **2.2.4 application environment:** The physical environment of a backplane serial bus. This includes the bus itself, the modules, and the system that contains them. This environment may be a standardized host backplane (e.g., a

- Futurebus+® profile) that describes signal requirements, transceivers, mechanical arrangement of the modules, and temperature range over which operation is guaranteed.

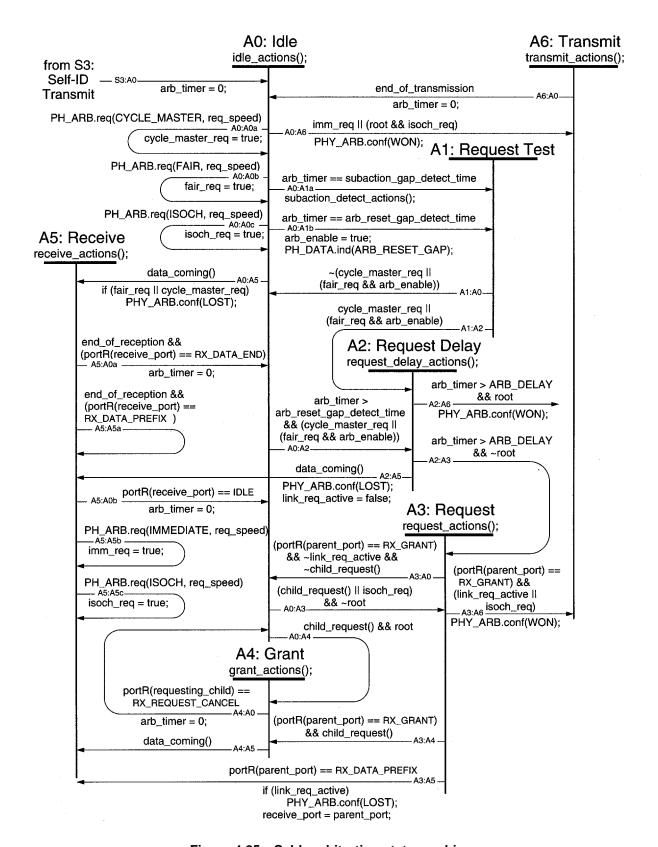

- **2.2.5 arbitration:** The process by which nodes compete for ownership of the bus. The cable environment uses a hierarchical point-to-point algorithm, while the backplane environment uses the bit-serial process of transmitting an arbitration sequence. At the completion of an arbitration contest, only one node will be able to transmit a data packet.

- **2.2.6 arbitration clock rate:** The rate used to define a number of timing requirements within the backplane physical layer. It is  $49.152 \text{ MHz} \pm 100 \text{ ppm}$ , regardless of the backplane interface technology.

- **2.2.7 arbitration reset gap:** The minimum period of idle bus that has to occur after a source using the fairness protocol has won an arbitration contest before it can once again compete for bus mastership. This is longer than a normal subaction gap.

- **2.2.8 arbitration sequence:** For the backplane environment, a set of bits transmitted by nodes that wish to transmit packets that is used to determine which node will be able to transmit next.

- **2.2.9 arbitration signal:** Bidirectional signal exchanged between nodes during arbitration. One of the PDUs for the physical layer (the other is the data bit).

- **2.2.10 asynchronous packet:** A primary packet that contains the bus\_ID of the destination in the first quadlet. It is sent as the request subaction and/or response subaction of a transaction.

- **2.2.11 attached peer PHY:** A peer cable PHY at the other end of a particular physical connection from the local PHY.

- **2.2.12 backplane physical layer:** The version of the physical layer applicable to the Serial Bus backplane environment.

- **2.2.13 backplane PHY:** Abbreviation for the backplane physical layer.

- **2.2.14 base rate:** The lowest data rate used by the Serial Bus in a particular cable environment. In multiple speed environments, all nodes have to be able to receive and transmit at the base rate. The base rate for the cable environment is  $98.304 \text{ MHz} \pm 100 \text{ ppm}$ .

- **2.2.15 broadcast\_physical\_ID:** A physical\_ID with a value of 1111111<sub>2</sub>.

- **2.2.16 bus\_ID:** A 10-bit number uniquely specifying a particular bus within a system of multiple interconnected buses.

- **2.2.17 bus manager:** The node that provides advanced power management, optimizes Serial Bus performance, describes the topology of the bus, and cross-references the maximum speed for data transmission between any two nodes on the bus. The bus manager node may also be the isochronous resource manager node.

- **2.2.18 byte:** Eight bits of data.

- **2.2.19 cable physical layer:** The version of the physical layer applicable to the Serial Bus cable environment.

- **2.2.20 cable PHY:** Abbreviation for the cable physical layer.

- **2.2.21 concatenated transaction:** A transaction where the request and response subactions are directly concatenated without a gap between the acknowledge of the request and the response packet.

- **2.2.22 connected PHY:** A peer cable PHY at the other end of a particular physical connection from the local PHY.

- **2.2.23 CSR Architecture:** ISO/IEC 13213 :1994 [ANSI/IEEE Std 1212, 1994 Edition], Information technology—Micro-processor systems—Control and Status Registers (CSR) Architecture for microcomputer buses.

- **2.2.24 cycle master:** The node that generates the periodic cycle start.

- **2.2.25 cycle start:** A primary packet sent by the cycle master that indicates the start of an isochronous cycle.

- **2.2.26 data bit:** The smallest signaling element used by the physical layer for transmission of packet data on the medium. One of the PDUs for the physical layer (the other is the arbitration signal).

**2.2.27 destination:** A node that is addressed by a packet. If the destination is individually addressed by a source, then it has to return an acknowledge packet.

- 2.2.28 doublet: Two bytes of data.

- **2.2.29 dribble bits:** Extra bits added to the end of a packet that allow extra synchronization in implementations.

- **2.2.30 fairness interval:** A group of back-to-back transfers during which each competing source using the fairness protocol gets a single transfer. The delimiters of the fairness interval are arbitration reset gaps.

- 2.2.31 gap: A period of idle bus.

- **2.2.32 initial register space:** The address space reserved for resources accessible immediately after a reset. This includes the registers defined by the CSR Architecture as well as those defined by this standard.

- **2.2.33 IRM:** Abbreviation for the isochronous resource manager.

- **2.2.34 isochronous:** The essential characteristic of a time-scale or a signal such that the time intervals between consecutive significant instances either have the same duration or durations that are integral multiples of the shortest duration.

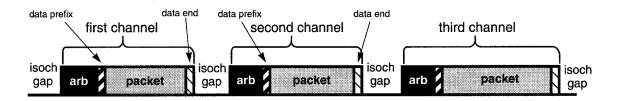

- **2.2.35** isochronous channel: A relationship between a talker and one or more listeners, identified by a channel number. One packet for each channel is sent during each isochronous cycle. Channel numbers are assigned using the isochronous resource management facilities.

- **2.2.36 isochronous cycle:** An operating mode of the bus that begins after a cycle start is sent, and ends when a subaction gap is detected. During an isochronous cycle, only isochronous subactions may occur. An isochronous cycle begins every 125 µs, on average.

- **2.2.37 isochronous gap:** The period of idle bus before the start of arbitration for an isochronous subaction.

- **2.2.38 isochronous resource manager (IRM):** The node that contains the facilities needed to manage isochronous resources. In particular, the isochronous resource manager includes the BUS\_MANAGER\_ID, BANDWIDTH\_AVAILABLE, and CHANNELS\_AVAILABLE registers. In addition, if there is no bus manager on the local bus, the isochronous resource manager may also perform limited power management and select a node to be the cycle master.

- **2.2.39 isochronous subaction:** A complete link layer operation (arbitration and isochronous packet) that is sent only during an isochronous cycle.

- **2.2.40 link layer (LINK):** The layer, in a stack of three protocol layers defined for the Serial Bus, that provides the service to the transaction layer of one-way data transfer with confirmation of reception. The link layer also provides addressing, data checking, and data framing. The link layer also provides an isochronous data transfer service directly to the application. See figure 3.4 for the relation of the link layer to the Serial Bus protocol stack.

- **2.2.41 LINK:** Abbreviation for the link layer.

- **2.2.42 listener:** A node that receives an isochronous subaction for an isochronous channel. There may be zero, one, or more than one listeners for any given isochronous channel.

- **2.2.43 local bus ID:** A bus ID with a value of 11111111111<sub>2</sub>.

- **2.2.44 lock-request packet:** The packet transmitted during the request subaction portion of a lock transaction.

- **2.2.45 lock-response packet:** The packet transmitted during the response subaction portion of a lock transaction.

- **2.2.46 lock transaction:** A transaction that passes an address, subcommand, and data parameter(s) from the requester to the responder and returns a data value from the responder to the requester. The subcommand specifies which indivisible update is performed at the responder; the returned data value is the previous value of the updated data.

- 2.2.47 module: The smallest component of physical management; i.e., a replaceable device.

- **2.2.48 natural priority:** The order of packet transmission of a node given that all nodes start arbitration at the same instant using the same priority level. For the cable environment, the closer a node is to the root, the higher its natural priority. For the backplane environment, the priority level and node\_offset are concatenated to give its natural priority.

- **2.2.49 node:** An addressable device attached to the Serial Bus with at least the minimum set of control registers. Changing the control registers on one node does not affect the state of control registers on another node.

- **2.2.50 node controller:** A component within a node that provides a coordination point for management functions exclusively local to a given node and involving the application, transaction, link, and physical elements located at that node.

- **2.2.51 node\_ID:** This is a unique 16-bit number, which distinguishes the node from other nodes in the system. The 10 most significant bits of node\_ID are the same for all nodes on the same bus; this is the bus\_ID. The six least-significant bits of node ID are unique for each node on the same bus; this is called the physical ID.

- **2.2.52 nonreturn to zero (NRZ):** A signaling technique in which a polarity level high represents a logical "1" (one) and a polarity level low represents a logical level "0" (zero).

- 2.2.53 octlet: Eight bytes of data.

- **2.2.54 packet:** A serial stream of clocked data bits. A packet is normally the PDU for the link layer, although the cable physical layer can also generate and receive special short packets for management purposes.

- **2.2.55 path:** The concatenation of all the physical links between the link layers of two nodes.

- 2.2.56 payload: The portion of a primary packet that contains data defined by an application layer.

- 2.2.57 PCB: Printed circuit board.

- **2.2.58 PDU:** Abbreviation for protocol data unit.

- **2.2.59 peer:** Service layer on a remote node at the same level. For instance a "peer link layer" is the link layer on a different node.

- **2.2.60 PHY:** Abbreviation for the physical layer.

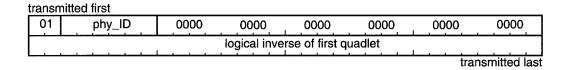

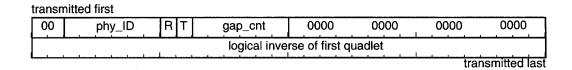

- **2.2.61 PHY packet:** A packet either generated or received by the cable physical layer. These packets are always exactly 64 bits long where the last 32 bits are the bit complement of the first 32 bits.

- **2.2.62 physical connection:** The full-duplex physical layer association between directly connected nodes. In the case of the cable physical layer, this is a pair of physical links running in opposite directions.

- **2.2.63 physical\_ID:** The least-significant 6 bits of the node\_ID. This number is unique on a particular bus and is chosen by the physical layer during initialization.

- **2.2.64 physical layer (PHY):** The layer, in a stack of three protocol layers defined for the Serial Bus, that translates the logical symbols used by the link layer into electrical signals on the different Serial Bus media. The physical layer guarantees that only one node at a time is sending data and defines the mechanical interfaces for the Serial Bus. There are different physical layers for the backplane and for the cable environment. See figure 3.4 for the relation of the physical layer to the Serial Bus protocol stack.

- **2.2.65 physical link:** In the cable physical layer, the simplex path from the transmit function of the port of one node to the receive function of a port of a directly connected node.

- **2.2.66 port:** A physical layer entity in a node that connects to either a cable or backplane and provides one end of a physical connection with another node.

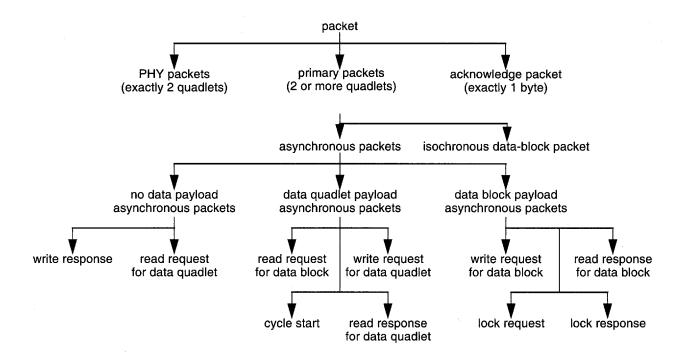

- **2.2.67 primary packet:** A packet made up of whole quadlets that contains a transaction code in the first quadlet. Any packet that is not an acknowledge or a PHY packet.

- **2.2.68 protocol data unit (PDU):** Information delivered as a unit between peer entities that may contain control information, address information, and data.

- **2.2.69 quadlet:** Four bytes of data.

- **2.2.70 quadlet aligned address:** An address with zeros in the east significant two bits.

- **2.2.71 request:** A subaction with a transaction code and optional data sent by a node (the requester) to another node (the responder).

- **2.2.72 response:** A subaction sent by a node (the responder) that sends a response code and optional data back to another node (the requester).

- **2.2.73 SBM:** Abbreviation for Serial Bus management.

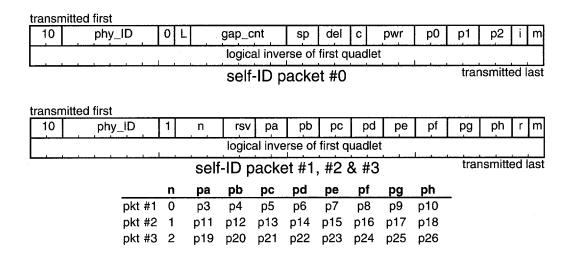

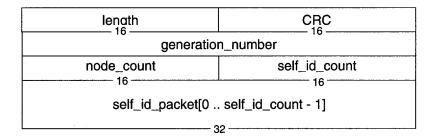

- **2.2.74 self-ID packet:** A special packet (see 4.3.4.1) sent by a cable PHY during the self-ID phase following a reset. One to four self-ID packets are sent by a given node depending on the maximum number of ports it has.

- **2.2.75 Serial Bus management (SBM):** The set of protocols, services, and operating procedures that monitors and controls the various Serial Bus layers: physical, link, and transaction. See figure 3.4 for the relation of Serial Bus management to the Serial Bus protocol stack.

- **2.2.76 services:** A set of capabilities provided by one protocol layer entity for use by a higher layer or by management entities.

- **2.2.77 service primitive:** A specific service provided by a particular protocol layer entity.

- **2.2.78 source:** A node that initiates a bus transfer.

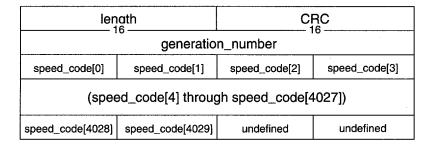

- **2.2.79 speed code:** The code used to indicate various bit rates for Serial Bus: S25 indicates 24.576 Mbit/s for TTL backplanes; S50 indicates 49.152 Mbit/s for BTL and ECL backplanes; S100 indicates the 98.304 Mbit/s base rate for cable; S200 and S400 indicate 196.608 Mbit/s and 393.216 Mbit/s for the cable.

- **2.2.80 split transaction:** A transaction where the responder releases control of the bus after sending the acknowledge and then some time later starts arbitrating for the bus so it can start the response subaction. Other subactions may take place on the bus between the request and response subactions for the transaction.

- **2.2.81 subaction gap:** The period of idle bus between subactions. There is no gap between the request and response subaction of a concatenated split transaction.

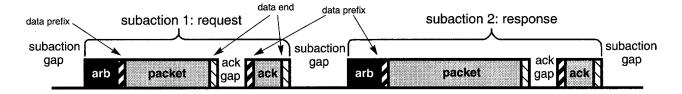

- **2.2.82 subaction:** A complete link layer operation: arbitration, packet transmission and acknowledgment. The arbitration may be missing when a node already controls the bus, and the acknowledge is not present for subactions with broadcast addresses or for isochronous subactions.

- **2.2.83 talker:** A node that sends an isochronous subaction for an isochronous channel.

- **2.2.84 transaction layer:** The layer, in a stack of three protocol layers defined for the Serial Bus, that defines a request response protocol to perform bus operations of type read, write, and lock. See figure 3.4 for the relation of the transaction layer to the Serial Bus protocol stack.

- **2.2.85 transaction:** A request and the corresponding response. The response may be null for transactions with broadcast destination addresses. This is the PDU for the transaction layer.

- **2.2.86 unified transaction:** A transaction that is completed in a single subaction.

- **2.2.87 unit architecture:** The specification document describing the format and function of the software-visible resources of the unit.

# 3. Summary description

This clause describes the form and function of the Serial Bus in a general way and is not intended to be a normative part of this standard. Instead, it provides useful background information to aid the understanding and implementation of the specification in clauses 4. through 7.3.5.2.1 and annexes A, B, and C.

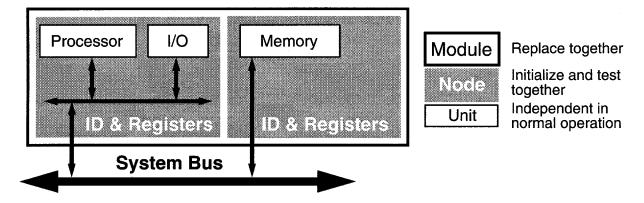

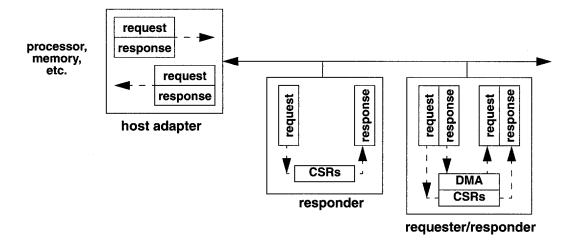

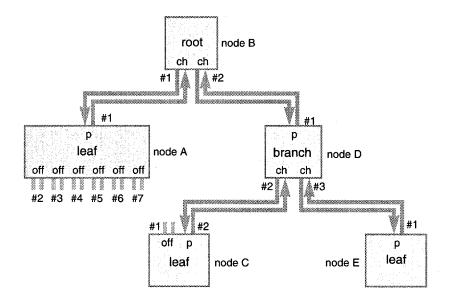

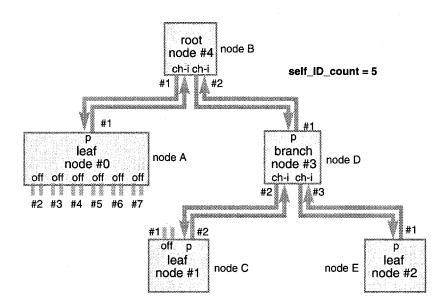

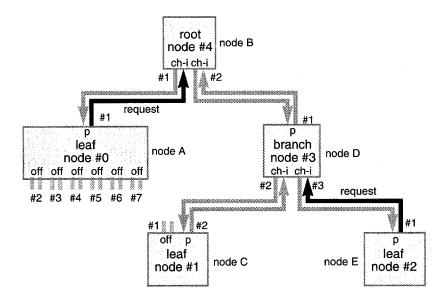

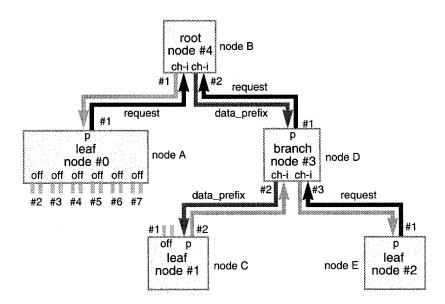

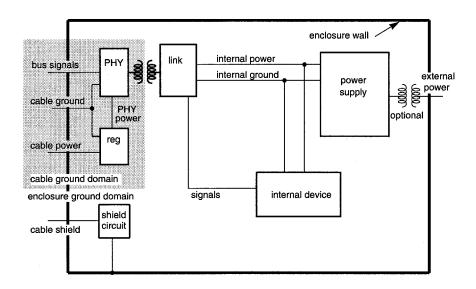

#### 3.1 Node and module architectures

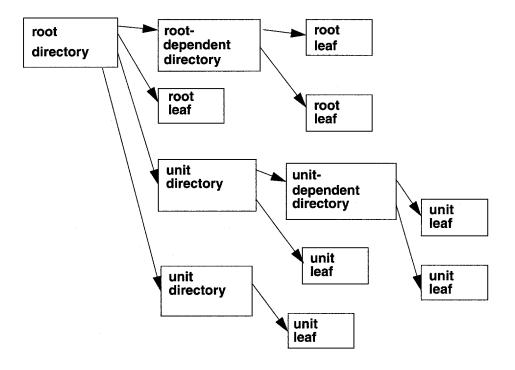

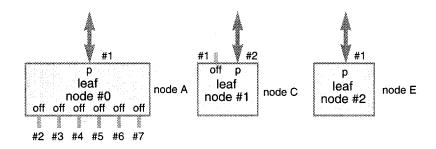

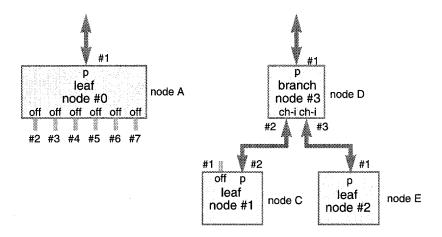

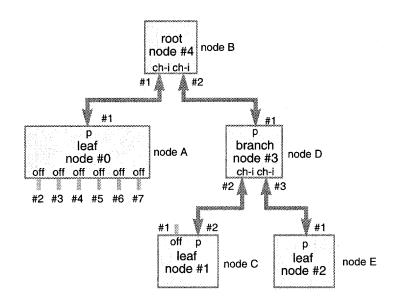

The Serial Bus architecture is defined in terms of nodes. A node is an addressable entity, which can be independently reset and identified. More than one node may reside on a single module, and more than one unit may reside in a single node, as illustrated in figure 3.1.

Figure 3.1—Module architecture

Each module consists of one or more nodes, which are independently initialized and configured. Note that modules are a physical packaging concept and nodes are a logical addressing concept. A module is a physical device, consisting of one or more nodes that share a physical interface. In normal operation, a module is not visible to software. Of course, this is not true when the module is replaced, when the shared bus interface fails, or when specialized module-specific diagnostic software is invoked.

A node is a logical entity with a unique address. It provides an identification ROM and a standardized set of control registers, and it can be reset independently.

The address space provided by a node can be directly mapped to one or more units. A unit is a logical entity, such as a disk controller, which corresponds to unique I/O driver software. On a multifunction node, for example, the processor and I/O interfaces could be different units on the same node. Unless the node is reset or reconfigured, the I/O driver software for each unit can operate independently. A unit may be defined by a unit architecture that describes the format and function of the software-visible registers of the unit. SCSI-3 Serial Bus Protocol (SBP) is a typical unit architecture.

Within a unit there may be multiple subunits, which can be accessed through independent control registers or uniquely addressed direct memory access (DMA)-command sequences. Although unit architectures should use the subunit concept to simplify I/O driver software, the definition of subunit architectures is beyond the scope of this standard.

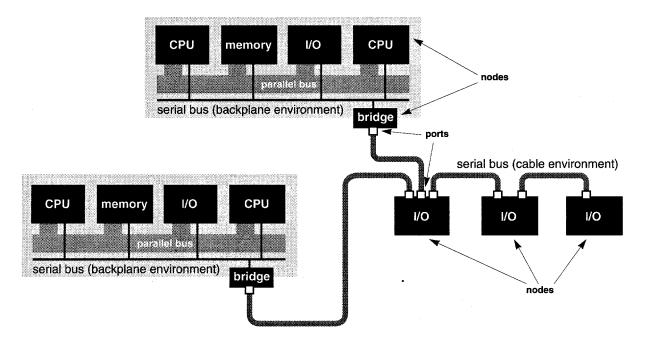

# 3.2 Topology

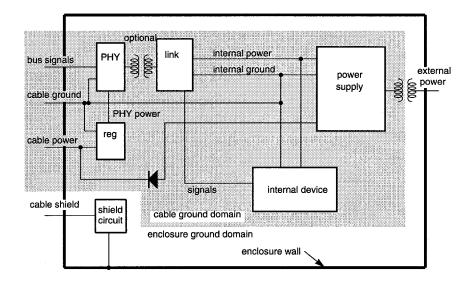

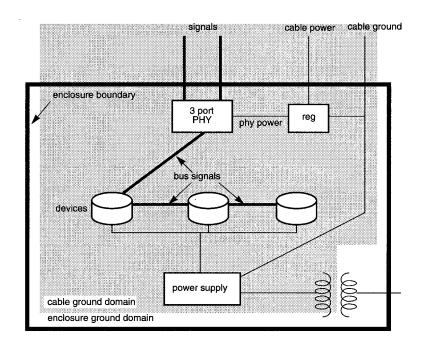

The physical topology of the Serial Bus is divided into two "environments," as shown in figure 3.2. One is called the "backplane environment" and is defined in this standard, although implementations may require additional physical-layer descriptions contained within other backplane bus standards. The other part is the "cable environment" and is completely specified in this standard. Interconnected nodes may reside in either environment without restriction.

Figure 3.2—Serial Bus physical topology

Note that figure 3.2 shows several logically separate buses. A bus bridge is required to connect buses with different environments. The full implementation of multiple bus systems using bus bridges is not defined in this standard: only the addressing and transactions are specified.

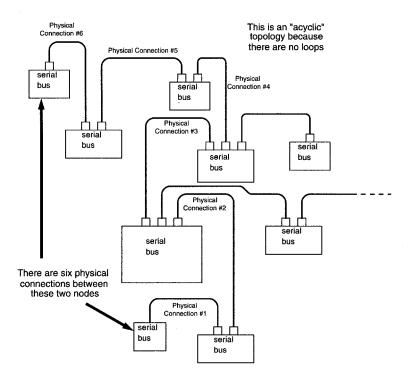

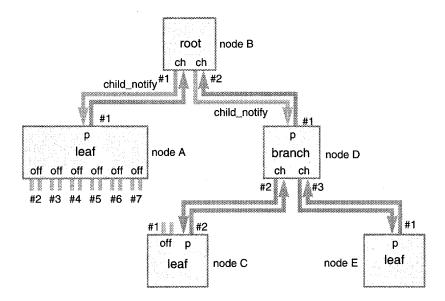

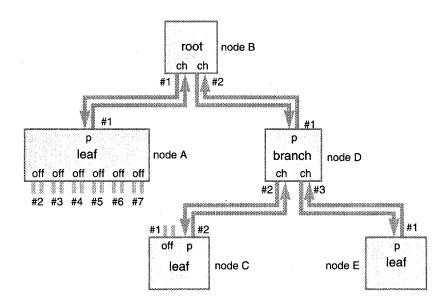

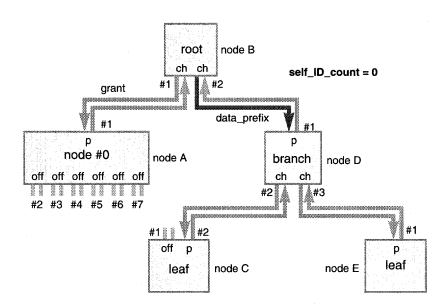

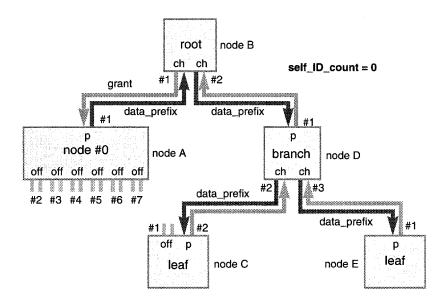

# 3.2.1 Cable environment

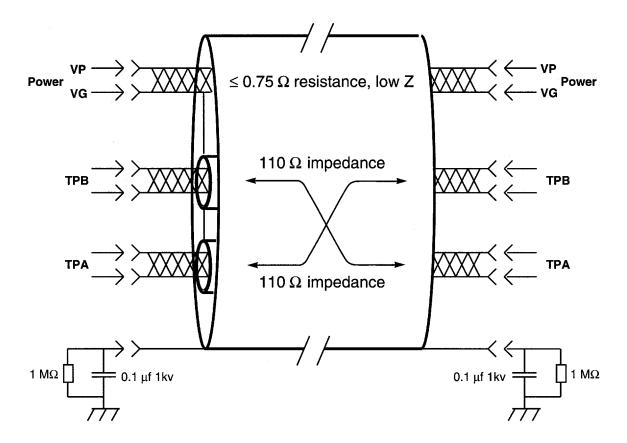

The physical topology for the cable environment is a noncyclic network with finite branches and extent. "Noncyclic" means that closed loops are unsupported. The medium consists of two conductor pairs for signals and one pair for power and ground that connect together ports on different nodes. Each port consists of terminators, transceivers, and simple logic. The cable and ports act as bus repeaters between the nodes to simulate a single logical bus.

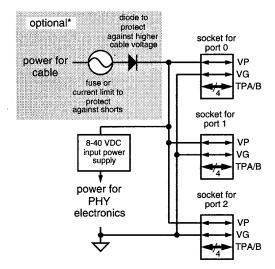

Since each node has to continuously repeat bus signals, the separate power and ground wires within the cable enable the physical layer of each node to remain operational even if node local power is off. The pair can even power an entire node if its requirements are modest. The Serial Bus cable provides 8–40 VDC at up to 1.5 A. The actual current available is system dependent.

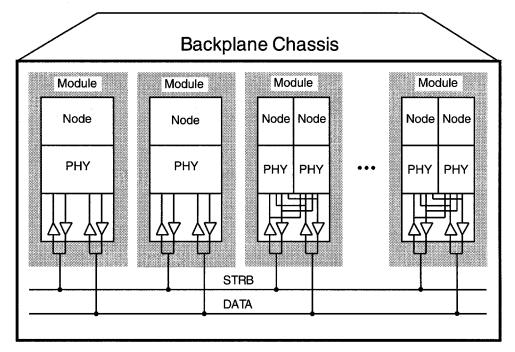

#### 3.2.2 Backplane environment

The physical topology of the backplane environment is a multidrop bus. The media consists of two single-ended conductors running the length of the backplane. Connectors distributed along the bus allow nodes to "plug into" the bus. Dominant mode (or "wired-OR") logic allows all nodes to assert the bus.

When in the backplane environment, the Serial Bus typically accompanies a standard parallel bus within an equipment chassis. In such an environment, the Serial Bus is extended from the backplane into each physical device using two pins reserved for a serial bus by the various IEEE bus standards. Drivers and receivers for Serial Bus signals follow the conventions established by the appropriate parallel bus standard: e.g., Futurebus+ using BTL, VME using TTL, and Fastbus and SCI using ECL. Power and ground are distributed as specified for the parallel bus. Examples of backplane implementations are given in annex F

## 3.3 Addressing

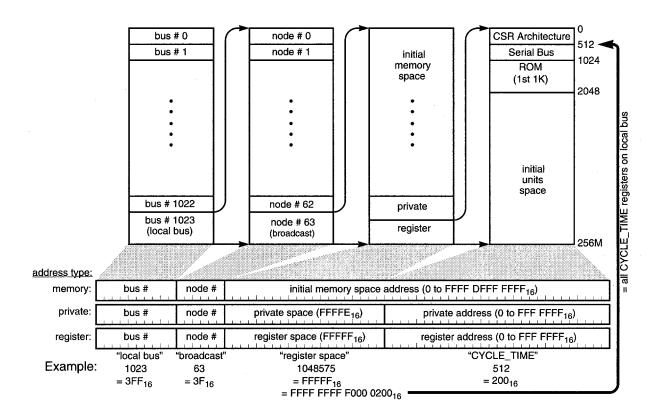

The Serial Bus follows the CSR Architecture for 64-bit fixed addressing, where the upper 16 bits of each address represent the node\_ID. This provides address space for up to 64 k nodes. The Serial Bus divides the node\_ID into two smaller fields: the higher order 10 bits specify a bus\_ID and lower order 6 bits specify a physical\_ID. Each of the fields reserves the value of all "1"s for special purposes, so this addressing scheme provides for 1023 buses, each with 63 independently addressable nodes. This standardization is continued within the node, with 2<sup>48</sup> bytes (256 terabytes) divided between **initial register space** (2048 bytes reserved for core CSR Architecture resources, registers specific to the Serial Bus, and the first 1024 bytes of a ROM ID area), **initial units space** (area reserved for node-specific resources), **private space** (area reserved for node-local uses), and **initial memory space**. Clause 4 of ISO/IEC 13213: 1994 defines these terms in more detail. Figure 3.3 illustrates the address structure of the Serial Bus.

Figure 3.3—Serial Bus addressing

When practical, the node should use only the first 2048 bytes of the initial units space. This simplifies the design of heterogeneous-bus systems, since the 2048 bytes of standard CSRs and ROM and first 2048 bytes of the initial units space use up the 4096 bytes allocated to CSR space on buses using the CSR-Architecture-defined 32-bit extended addressing (Futurebus+ has several profiles that use 32-bit extended addressing). Note, however, that nodes intended solely for Serial Bus systems (or mixed with other 64-bit fixed interconnects, such as SCI) may take full advantage of the 256 megabytes of CSR address space provided by this addressing architecture.

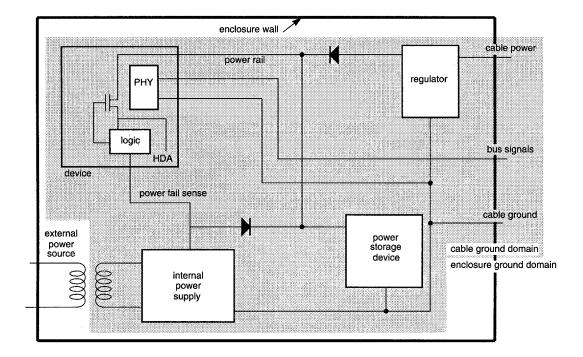

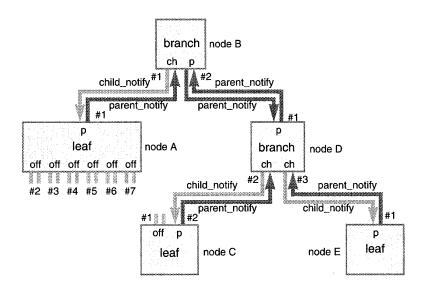

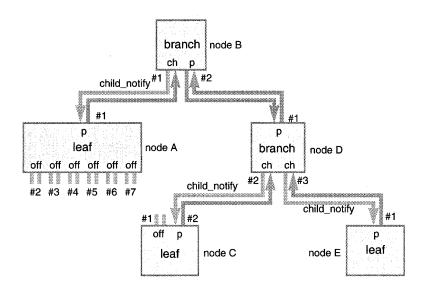

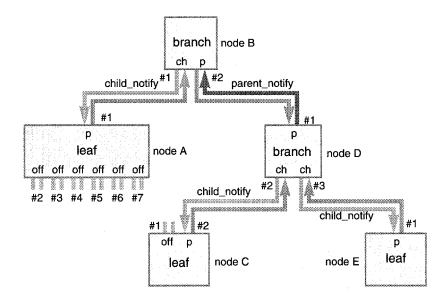

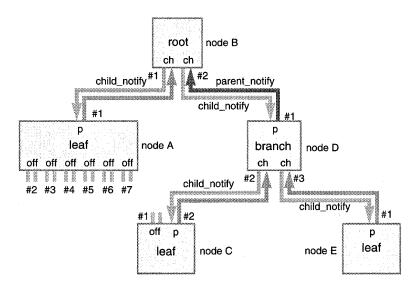

#### 3.4 Protocol architecture

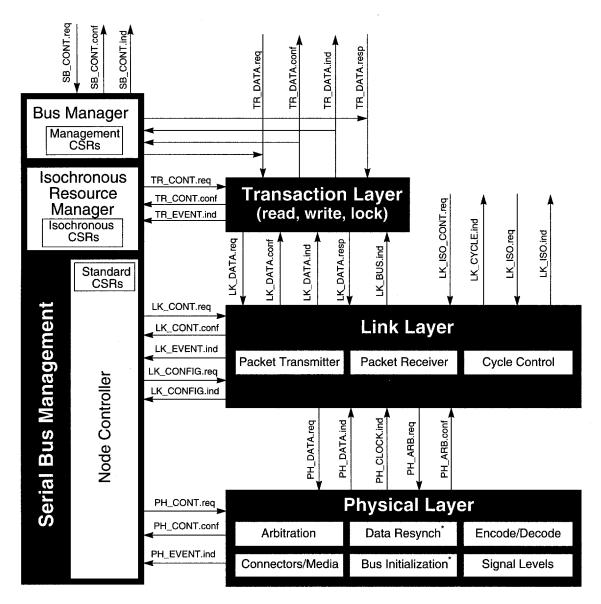

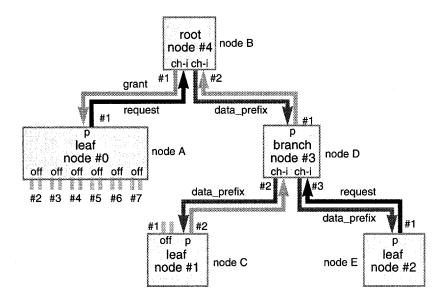

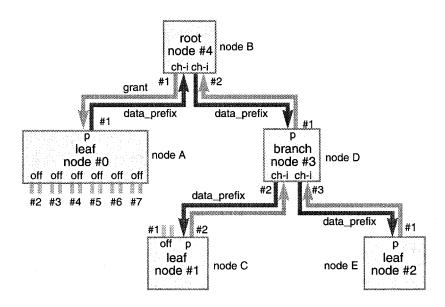

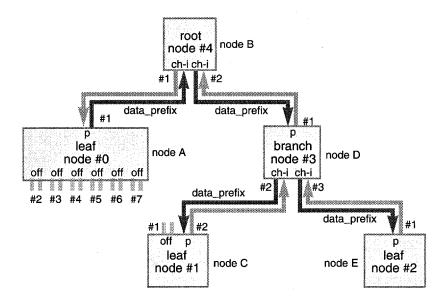

The serial bus protocols are described as a set of three stacked layers, as shown in figure 3.4.

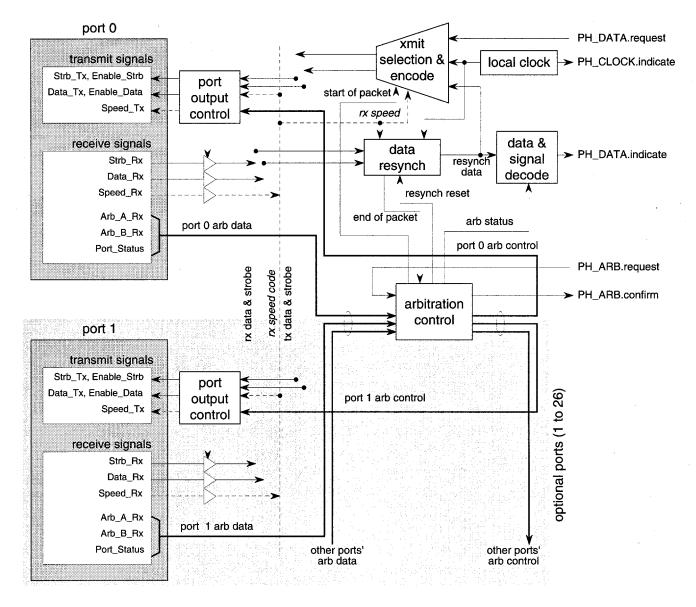

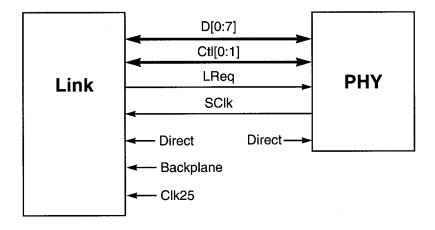

\*Only for the cable environment

Figure 3.4—Serial Bus protocol stack

- a) The transaction layer defines a complete request-response protocol to perform the bus transactions required to support the CSR Architecture (the operations of **read**, **write**, and **lock**). Note that the transaction layer does not add any services for isochronous data, although it does provide a path for isochronous management data to get to the Serial Bus management via reads from and compare-swaps with the isochronous control CSRs.

- b) The link layer provides an acknowledged datagram (a one-way data transfer with confirmation of request) service to the transaction layer. It provides addressing, data checking, and data framing for packet transmission and reception. The link layer also provides an isochronous data transfer service directly to the application, including the generation of a "cycle" signal used for timing and synchronization. One link layer transfer is called a "subaction."

- c) The physical layer has three major functions:

- It translates the logical symbols used by the link layer into electrical signals on the different Serial Bus media.

- 2) It guarantees that only one node at a time is sending data by providing an arbitration service.

- 3) It defines the mechanical interfaces for the Serial Bus.

There is a different physical layer for each environment: cable and backplane. The cable physical layer also provides a data resynch and repeat service and automatic bus initialization.

The Serial Bus protocols also include Serial Bus management, which provides the basic control functions and standard CSRs needed to control nodes or to manage bus resources. The bus manager component is only active at a single node that exercises management responsibilities over the entire bus. At the nodes being managed (all those that are not the bus manager), the Serial Bus management consists solely of the node controller component. An additional component, the isochronous resource manager, centralizes the services needed to allocate bandwidth and other isochronous resources.

#### 3.4.1 Data transfer services

This standard supports two basic data transfer services:

- a) Asynchronous data transfer

- b) Isochronous data transfer

The asynchronous (asyn = any, chronous = time) data transfer service provides a packet delivery protocol for variable-length packets to an explicit address and return of an acknowledgment. The isochronous (iso = same, chronous = time) data transfer service provides a broadcast packet delivery protocol for variable-length packets that are transferred at regular intervals. As shown in figure 3.4, the asynchronous data transfer service uses the transaction layer, whereas isochronous data transfer service is application driven.

# 3.5 Transaction layer

Data is transferred between nodes on the serial bus by three different transaction types:

- a) Read—data at a particular address within a responder is transferred back to a requester.

- b) Write—data is transferred from a requester to an address within one or more responders.

- c) Lock—data is transferred from a requester to a responder, processed with data at a particular address within the responder, and then transferred back to the requester.

Transactions are multithreaded, in that more than one transaction can be started by a requester before the corresponding response is returned. These are called a split-response transactions.

#### 3.5.1 Transaction layer services

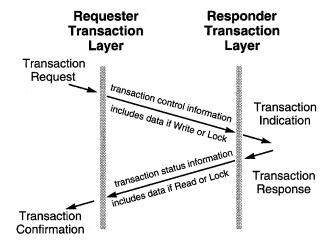

Transactions consist of four service primitives:

- a) Request—the primitive used by a requester to start the transaction.

- b) Indication—the primitive used to notify the responder of an incoming request.

- c) Response—the primitive used by the responder to return status and possibly data to the requestor.

- d) Confirmation—the primitive used to notify the requestor of the arrival of the corresponding response.

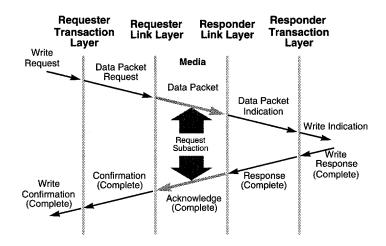

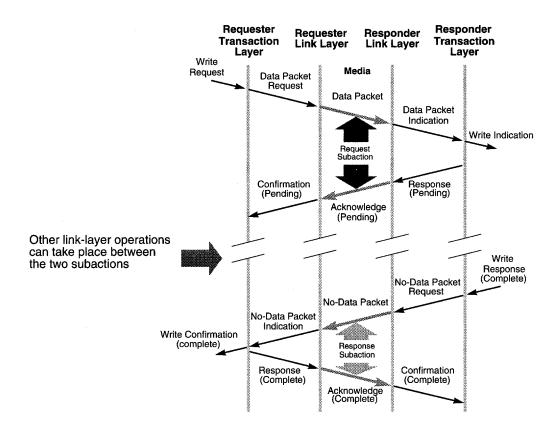

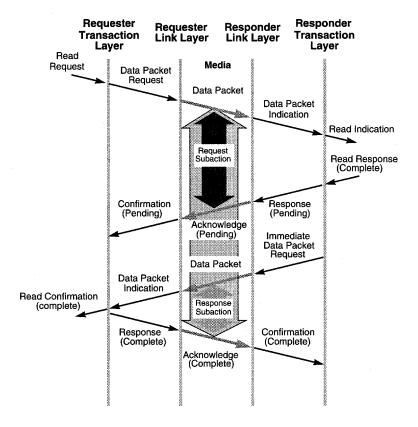

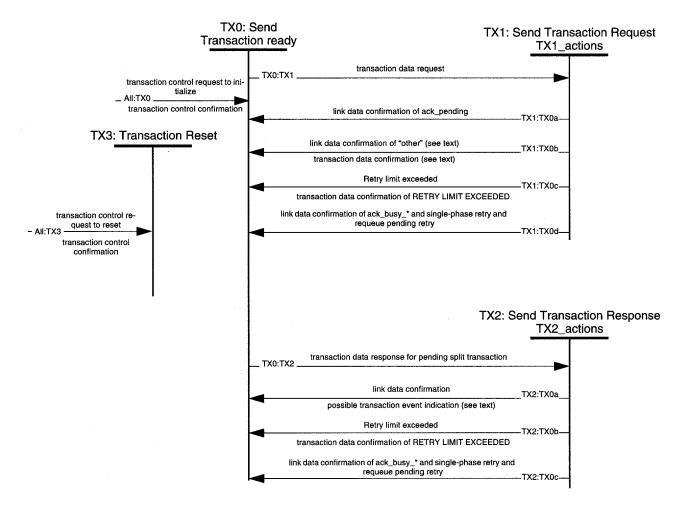

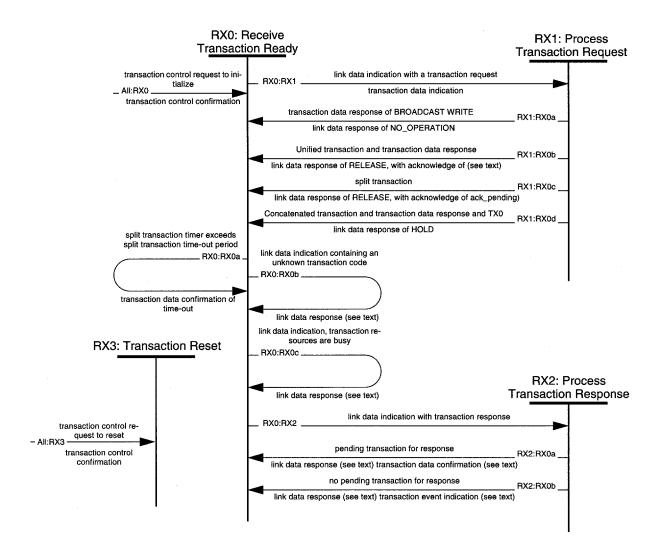

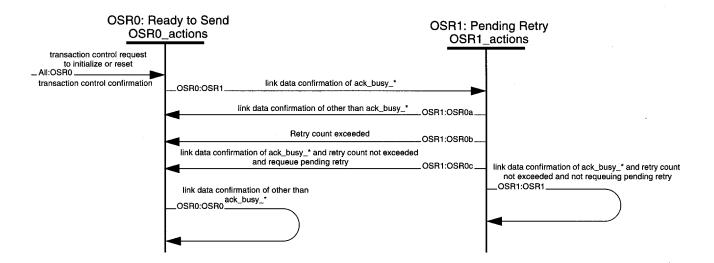

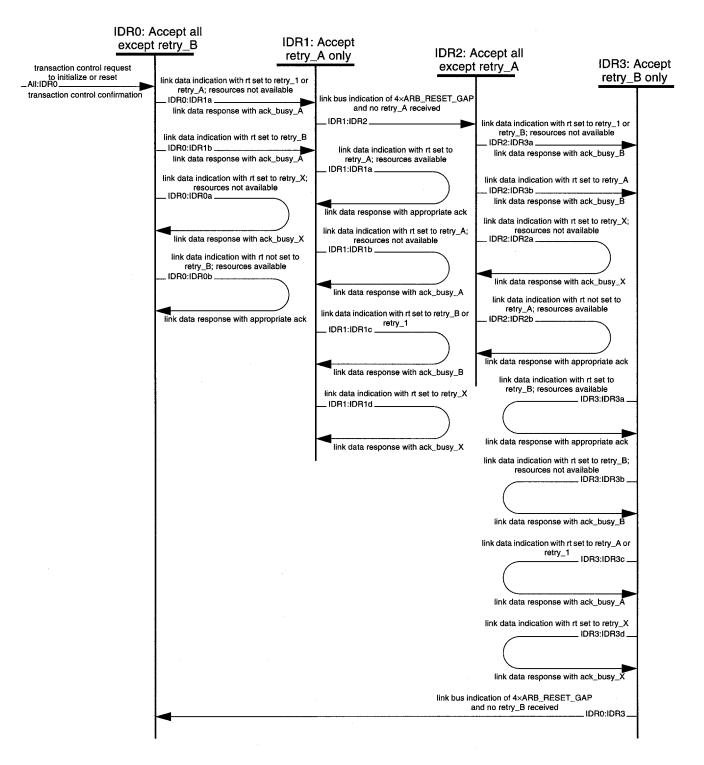

These primitives and their relation to data flow is shown in figure 3.5.

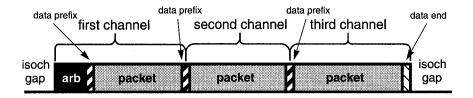

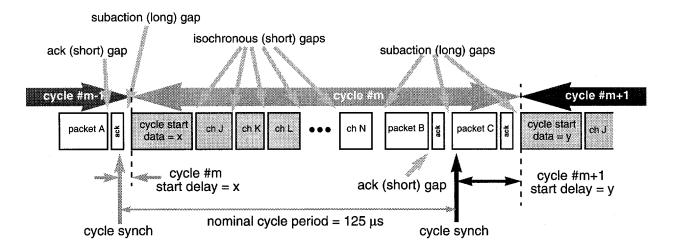

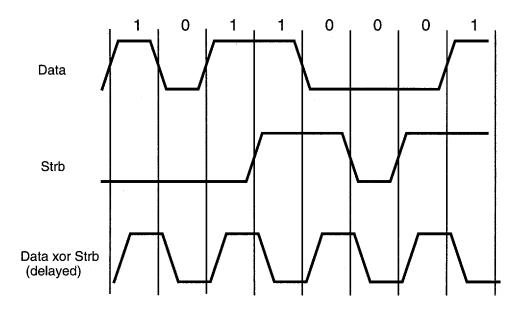

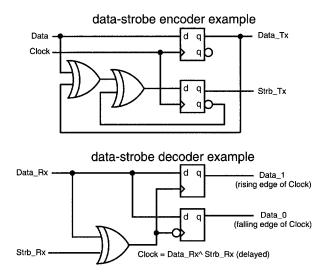

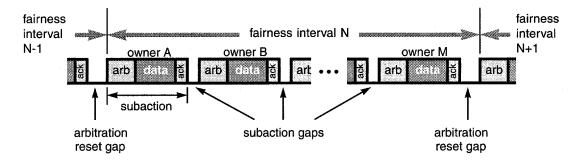

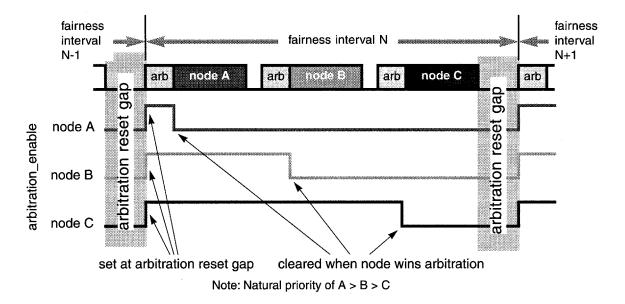

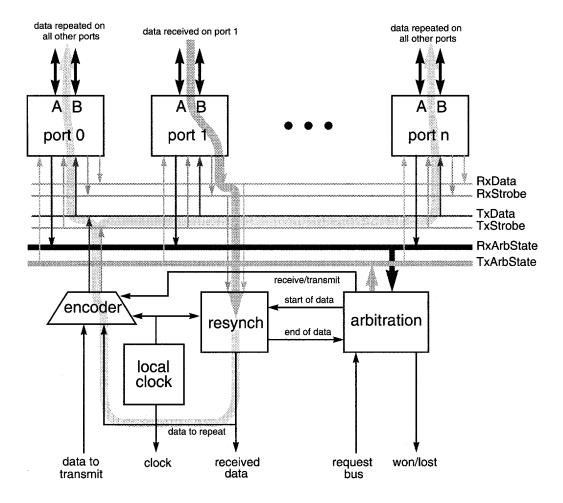

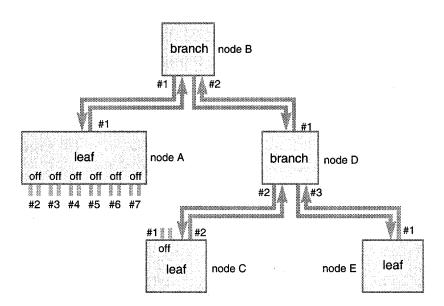

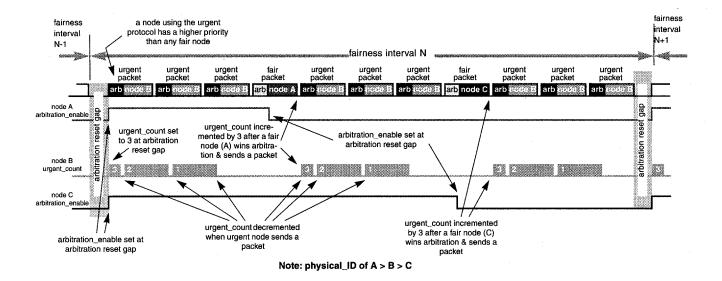

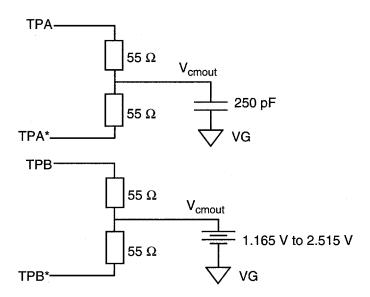

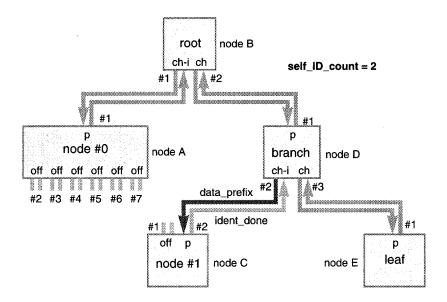

Figure 3.5—Transaction services