# 次世代の高速メモリアーキテクチャの検証

ラムバス株式会社 フィールド アプリケーション エンジニア 佐野 幸司

# アジェンダ

- ハイパフォーマンス・アプリケーションに要求される メモリインタフェイス

- XDR2 アーキテクチャ

- 次世代高速メモリアーキテクチャのデザインと検証

- ・チャレンジ

- システムの概要

- 基板とパッケージの設計とモデリング

- デバイス評価

- リンクのモデリング、シミュレーション及び評価

- ・まとめ

# マルチコア アプリケーションにおいての メモリへの要求

ゲーム

グラフィック マルチコア コンピューティング

- 非常に高いメモリバンド幅

- 様々なメモリ容量

- 様々なアクセス粒度 (Access granularity)

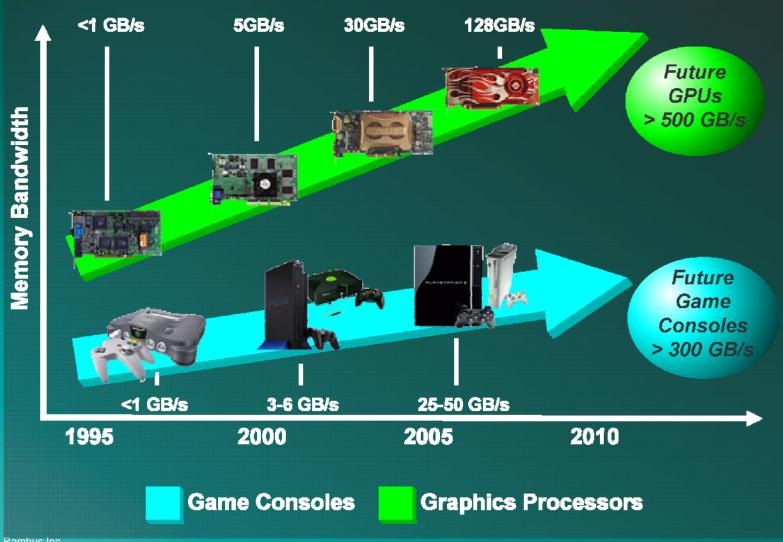

# 要求されるメモリバンド幅の進化

### メモリーパフォーマンスの課題

- 6Gbps以上のデータレートの達成

- メモリ効率/アクセス粒度

- 消費電力効率 / 温度管理

- 低コスト生産

- シグナルインテグリティーの確保

- 最小のピン数

- 最低のクロック周波数

- パッケージサイズ及びPCB面積の削減

# XDR™2 メモリ アーキテクチャの発表

- XDR2は最高速のDRAMテクノロジ

- 動作周波数は6.4から12.8Gbps

- デバイスあたりGDDR5の2倍のバンド幅

- 最も消費電力効率の良いハイパフォーマンスメモリ

- 同じバンド幅でGDDR5に比べ40%低いメモリシステム消費電力

- 同じ消費電力でGDDR5に比べ最大2倍以上のバンド幅

- GDDR5に比べ低いクロック周波数

- 受賞歴の有るXDRメモリアーキテクチャの次世代メモリ

- 500 GB/s以上のシステムバンド幅を実現可能

- コストリダクションやパフォーマンスアップに対応したメモリアーキテクチャ

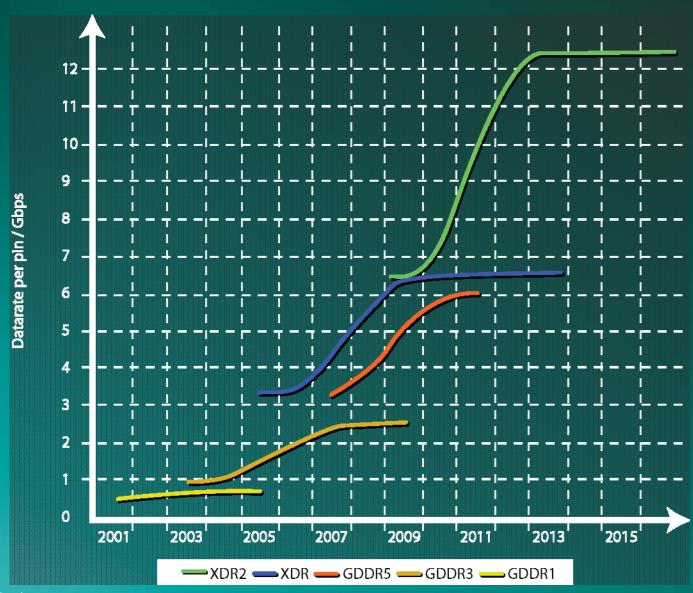

# XDR パフォーマンス ロードマップ

#### XDR2アーキテクチャに採用される革新的な技術

| 革新的な技術                                   | 効果                               |

|------------------------------------------|----------------------------------|

| FDMA *                                   | <ul><li>シグナルインテグリティの向上</li></ul> |

| (Fully Differential Memory Architecture) | ・低振幅の差動信号による低消費電力化               |

| FlexLink <sup>TM</sup> C/A *             | •ピン数と面積の縮小                       |

|                                          | • 拡張性のある容量とアクセス粒度                |

| Micro-threading                          | •アクセス粒度を小さくすることが可能               |

|                                          | • 高い処理能力が必要なアプリケーションの最適化         |

| 16X Data Rate                            | ・バンド幅の向上                         |

| Asymmetric Equalization *                | • DRAMの簡素化とコスト削減                 |

| Enhanced FlexPhase™ *                    | • レイアウトを簡素化し等長配線を不要にする           |

\* XDR2のテクノロジ ショウケースであるTerabyte Bandwidth Initiativeに使用された革新的な技術

#### **FDMA**

#### **Fully Differential Memory Architecture**

- 優れたシグナルインテグリティを提供

- 6Gbps以上のデータレートにて信頼性の高い高速動作

| Signals           | DDR3/ GDDR5  | XDR™         | XDR™2        |

|-------------------|--------------|--------------|--------------|

| Command / Address | Single Ended | Single Ended | Differential |

| DQ                | Single Ended | Differential | Differential |

| Clock / Strobes   | Differential | Differential | Differential |

#### FlexLink<sup>TM</sup> C/A

Full Speed C/A

C/A\*

DQ

Legacy

28 Wire C/A Interface (DDR2/GDDR3)

Memory Controller C/A

DRAM C/A FlexLink C/A

2 Wire, Point-to-Point

C/A Interface

Memory Controller C/A

DRAM C/A

- C/Aのピン数を最少化

- 設計の柔軟性を提供

- 低いパッケージコスト

\* Command / Address

# **Micro-threading**

- 4つの独立した物理 メモリスペース毎に RowとColumn アクセス可能

- •32バイトのアクセス 粒度

- より細かいアクセス粒度でより高いメモリバンド幅

- 高いメモリアクセス効率による低消費電力化

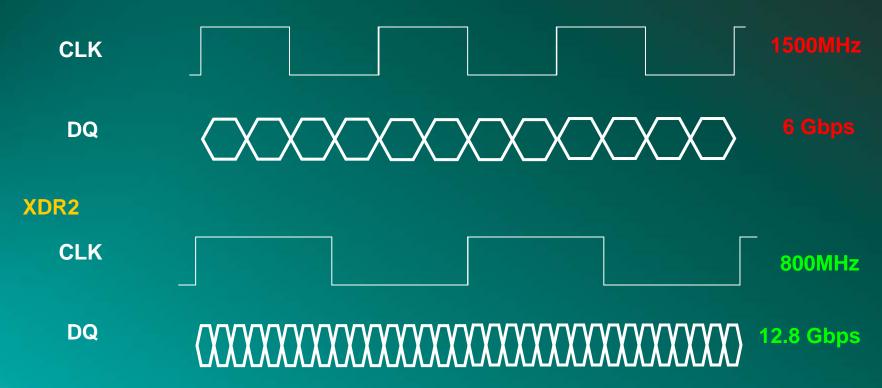

#### 16X Data Rate

#### **GDDR5**

- XDR2はGDDR5の約半分のクロック周波数で2倍のデータレートを提供

- 低いクロック周波数はデザインを簡素化することができ、歩留まりを向上させ コストを低減する

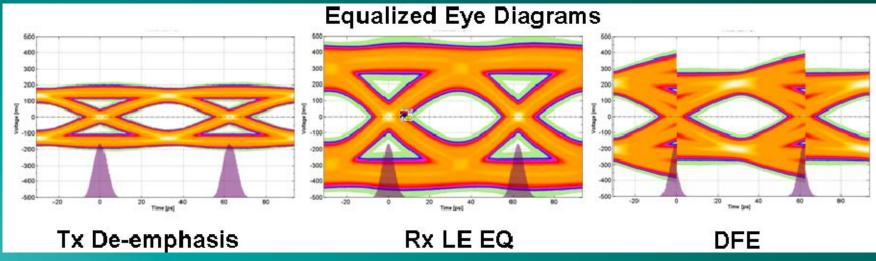

# **Asymmetric Equalization**

**Memory Controller Equalized TX Eye**

**Demonstrated DRAM Unequalized TX Eye**

コントローラのみにイコライゼーションを入れることによりDRAM を簡素化し製造コストを低くすることが可能

\*As measured in TBI Silicon Test Vehicle

# Enhanced FlexPhase™ Technology

・ 細かい位相調整分解能によって、マルチGHzの伝送速度の基 板配線と設計の簡素化が可能

# ピン数の比較

Source: Rambus x32 Package Description

Source: 512Mbit x32/x16 GDDR5 Datasheet

XDR2 DRAM Ballout: 124 pins

GDDR5 DRAM Ballout: 170 pins

•XDR2 DRAM は2倍のバンド幅で46ピン少ないピン数1 •XDR2 コントローラでは40%以上のバンド幅あたりのピン効率2

<sup>&</sup>lt;sup>2</sup> Power and ground pins not included

### XDR2 メモリのまとめ

#### 世界最速のDRAMテクノロジとクラス最高の消費電力効率

- デバイスあたりGDDR5の2倍のバンド幅

- 同じバンド幅にてGDDR5に比べ40%低いメモリシステム消費電力

- 同じ消費電力にてGDDR5に比べ最大2倍以上ののバンド幅

- グラフィック、ゲーム コンソール及びマルチコア コンピュー ティングにおいて最高のメモリパフォーマンスと効率

- ロードマップにて下位互換性を継続

# アジェンダ

- ハイパフォーマンス・アプリケーションに要求される メモリインタフェイス

- XDR2 アーキテクチャ

- 次世代高速メモリアーキテクチャのデザインと検証

- チャレンジ

- システムの概要

- 基板とパッケージの設計とモデリング

- デバイス評価

- ・リンクのモデリング、シミュレーション及び評価

- ・まとめ

# デザインの課題

- テラバイトのメモリバンド幅の実現

- リンクのバンド幅を最大化

- ・リンクの消費電力を最小化

- システム全体での低コスト化

- 一般的な基板やパッケージの使用

- 基板層数の最小化

- パッケージサイズの最小化

- 複雑な回路は可能な限りコントローラで実現

- DRAMプロセスは低速なトランジスタと少ないメタル層

# シグナル インティグリティの課題

- 伝送路のモデリング

- 高周波での減衰と反射

- トランスミッタとレシーバのモデリング

- ノイズとジッタ

- チャンネルと回路の相互作用

- 低いBERでの性能予測

- 受動素子と能動素子の評価

- システム検証

# アジェンダ

- ハイパフォーマンス・アプリケーションに要求される メモリインタフェイス

- XDR2 アーキテクチャ

- 次世代高速メモリアーキテクチャのデザインと検証

- チャレンジ

- システムの概要

- 基板とパッケージの設計とモデリング

- デバイス評価

- リンクのモデリング、シミュレーション及び評価

- ・まとめ

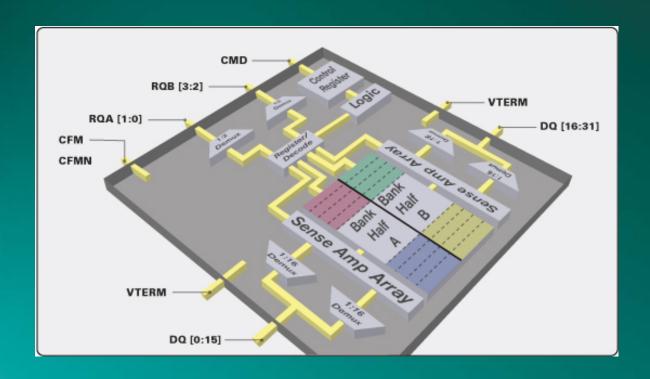

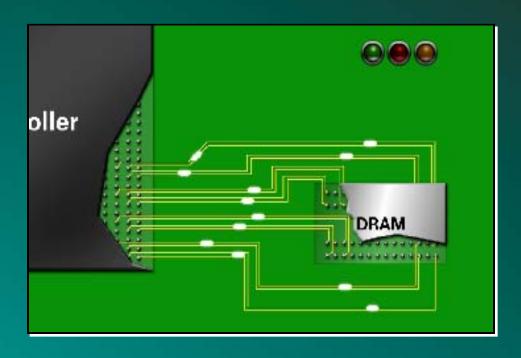

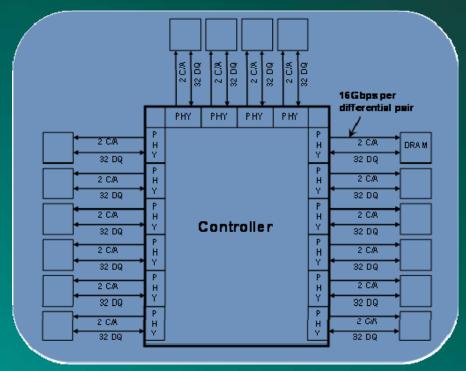

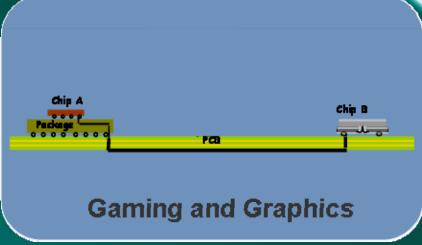

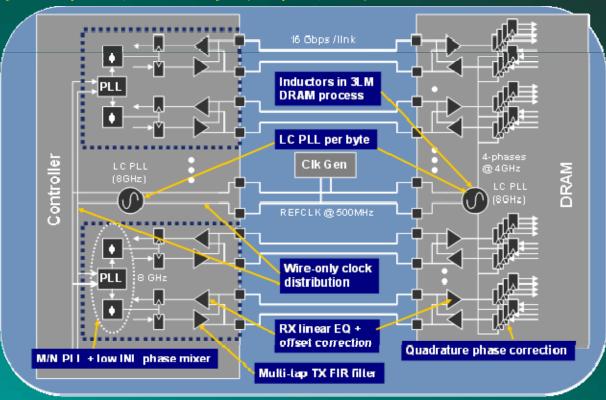

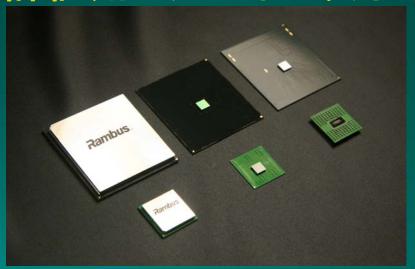

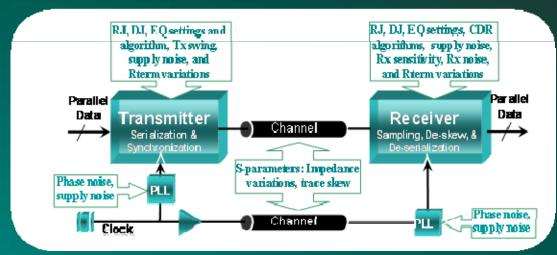

# テラバイト メモリシステム

- XDR2のベースとなったTBI(Terabyte Bandwidth Initiative)

- 全差動信号のメモリアーキテクチャ

- 16 DRAMを使用し、1つのDRAMで64GB/secをサポート

- ◆ それぞれのDRAMが32ペアのDQと2ペアのコマンド・アドレスを持つ

- データとコマンド・アドレスは16 Gbps

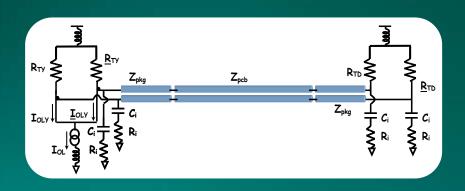

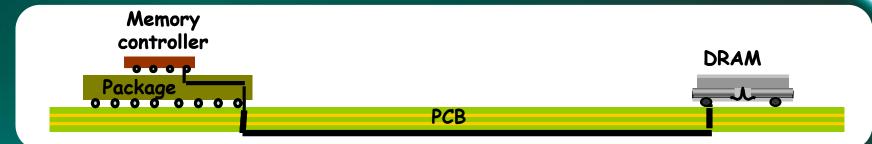

#### インターコネクト システム

- システム:100Ωの差動インピーダンス

- PCB: 3インチまでのマイクロストリップライン

- コントローラパッケージ:最大18mmの配線

- メモリパッケージ:最大6mmの配線

- デバイスの寄生性Ci及びRi、オンダイターミネーション(ODT)

- インターコネクトシステムの構成

- · 結合伝送線路

- ▼ Sパラメータブロック及び集中定数回路素子

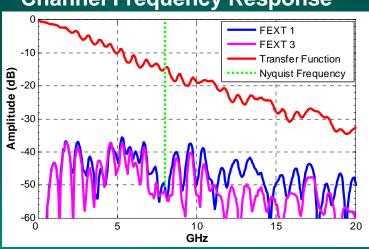

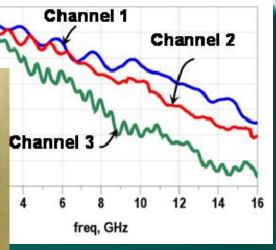

# チャンネル 評価

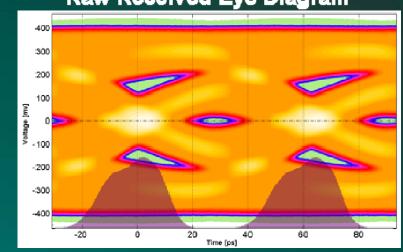

#### **Channel Frequency Response**

#### Raw Received Eye Diagram

・ チャンネルは高い減衰 (-15 dB) があるが低いクロストーク

# クロッキング アーキテクチャ

- 非対称クロッキング

- 低フェーズノイズのLC-VCOを使用したPLL

- コントローラに多段のPLLを実装

# アジェンダ

- ハイパフォーマンス・アプリケーションに要求される メモリインタフェイス

- XDR2 アーキテクチャ

- 次世代高速メモリアーキテクチャのデザインと検証

- チャレンジ

- システムの概要

- 基板とパッケージの設計とモデリング

- デバイス評価

- リンクのモデリング、シミュレーション及び評価

- ・まとめ

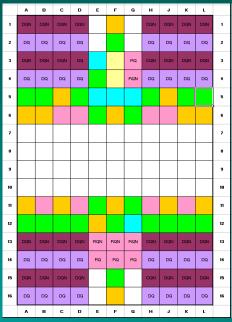

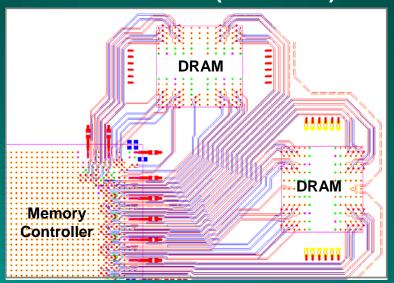

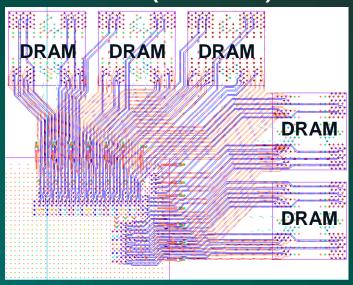

# 基板配線

512 GB/sec (Quadrant)

1 TB/sec (Quadrant)\*

- 512 GB/sec メモリ システム

- 1.0mmピッチの4層基板 (信号配線は2層)

- 薄板(Thin-core) パッケージ (信号配線は2層)

- 1 TB/secメモリシステム(信号配線は5層)

- さらに小さなバンプピッチ: 180μから150μへ

- さらに小さなBGAピッチ: 1.0mmから0.8mmへ

- より大きなパッケージ基板: 45 mm

\* Only microstrip layers shown

# 反射の原因

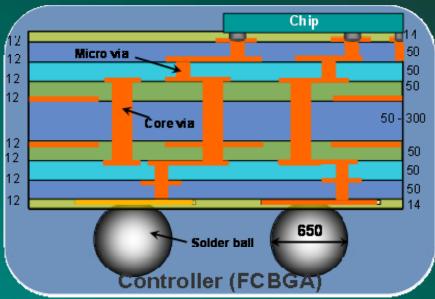

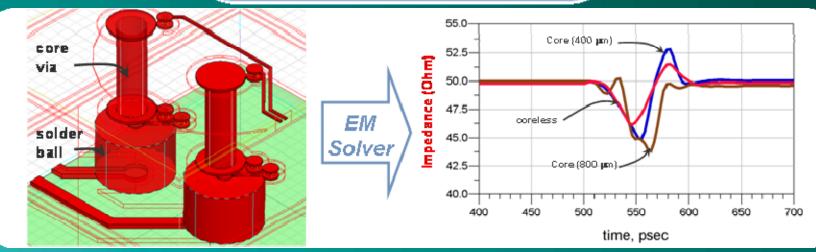

# コントローラ パッケージ

コントローラ: 薄板(Thin-core)パッケージ

# 評価用: デバイス及びデモ基板

- 65 nm CMOSプロセス

- 将来の コントローラとDRAM製品の実現可能性をデモ

- ターゲット: 16Gbps @ BER < 1E-21

- 消費電力及び面積の目標

- ▶ 回路構造上のトレードオフを評価検証

- 電圧とタイミングマージンを確認

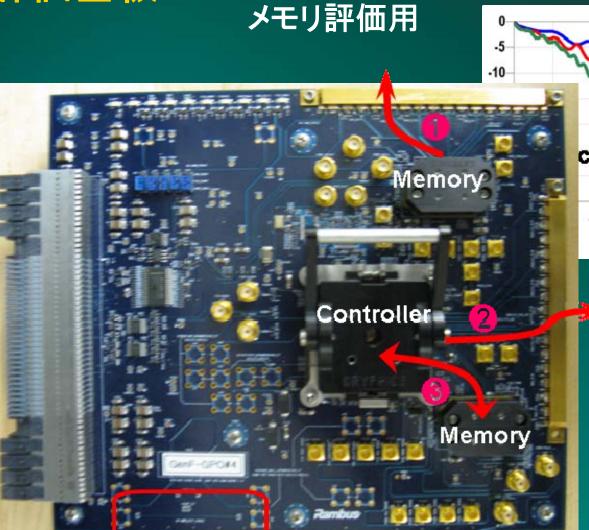

# 評価基板

コントローラ及び リンク評価用

高速信号は2層で 配線

テストクーポン: 40GHzまで評価したマイクロストリップ配線

© 2009 Rambus Inc.

For Presentation purposes only

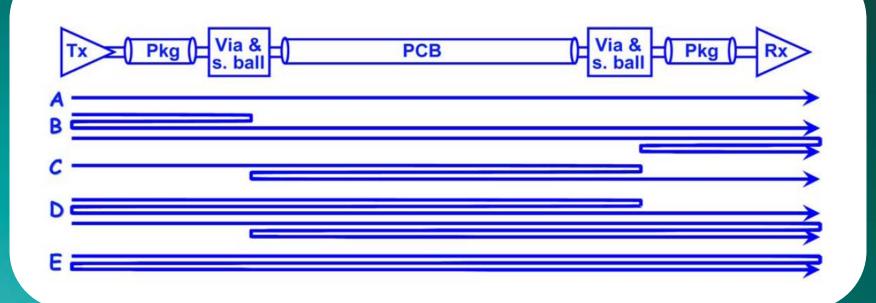

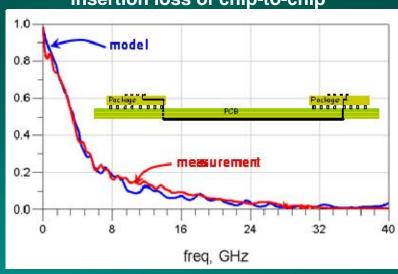

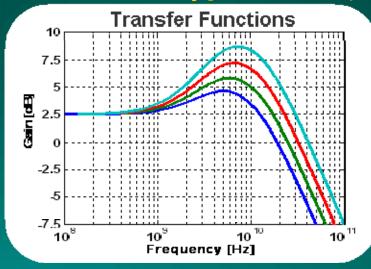

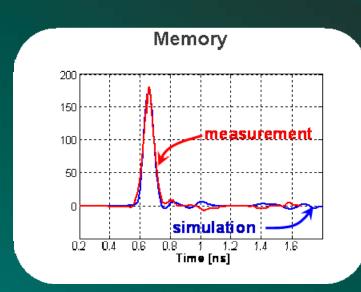

### 伝送路の評価

**Insertion loss of chip-to-chip**

#### Insertion loss of components/channels

- パッケージは送信端、受信端ともにフリップチップBGAを使用

- パッケージの配線は18 mmまでの長さ

- パッケージ及び基板の接合部での大きなインピーダンスの不連続性が発生

- そのため伝送路の受動素子部分を測定すると、小さなメモリパッケージを 使用したチャンネルより特性が悪い

- 広範囲の周波数帯で良い相関が得られる

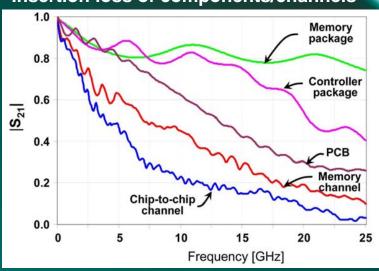

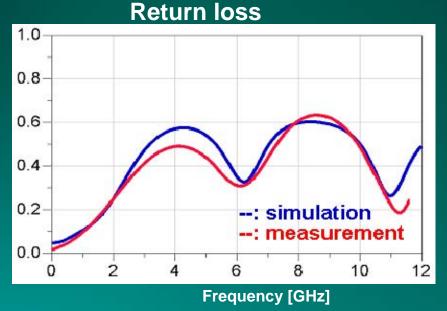

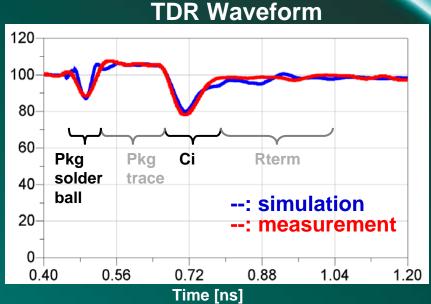

#### コントローラ デバイス 評価

- パッケージの半田ボールにて極めて大きな不連続性がある。

- パッケージの配線インピーダンスはターゲットより高い

- ODTターミネーションの値は周波数による

- Ci ≈ 0.9 pF から 1.1 pF

# アジェンダ

- ハイパフォーマンス・アプリケーションに要求される メモリインタフェイス

- XDR2 アーキテクチャ

- 次世代高速メモリアーキテクチャのデザインと検証

- チャレンジ

- システムの概要

- 基板とパッケージの設計とモデリング

- デバイス評価

- リンクのモデリング、シミュレーション及び評価

- まとめ

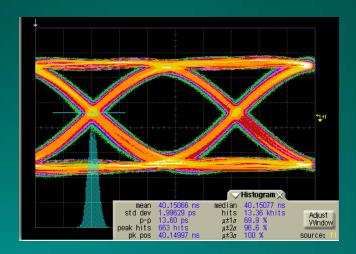

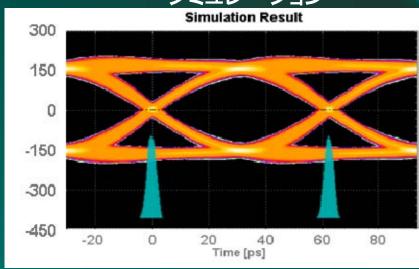

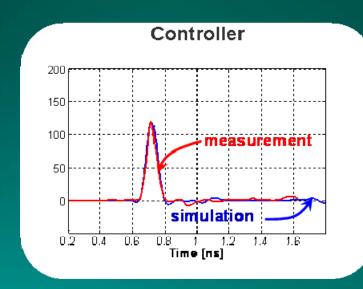

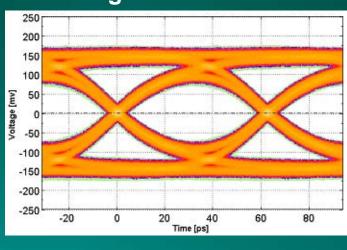

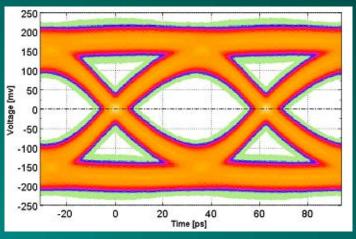

# TXイコライザを使用した16 Gbpsのアイダイアグラム

計測結果

Elle Control Setup Measure Calbrate Utilities Help 16 Nov 2007 12:19

Eye/Mask Mode

Ethnison

Ratio

American

Average

Percentage

Percen

シミュレーション

- コントローラの信号をオシロスコープへ

- チャンネルの測定

- パッケージ及び基板は約3インチ、SMPコネクタから18インチのケー ブルを接続

- TXイコライザは計測したチャンネルに最適化

- アイダイアグラムの計測とシミュレーション結果でよい相関 が取れている

# メモリ信号をオシロスコープへ

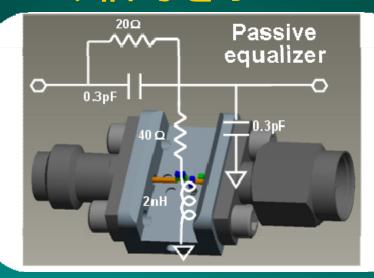

レシーバの線形イコライゼーション評価

$$H_{EQ}(s) = \frac{k_1(s+z_1)}{(s+p_1)(s+p_2)}$$

- 極と零点を使用してCTLE\*をモデリング

- CTLEパラメータは直接計測できない

- ◆ イコライザの相対的な周波数応答をBERTを使用し計測

- 正弦波を加えたPRBS信号

- 正弦波の振幅と周波数の関数をBERで計測

- CTLEの周波数応答は正弦波の振幅の逆数として得られる

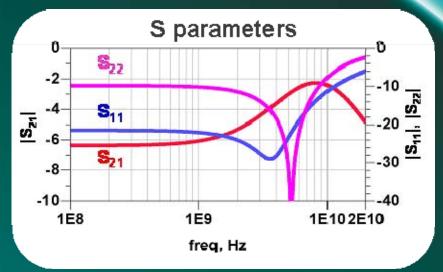

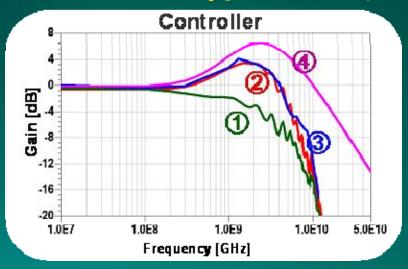

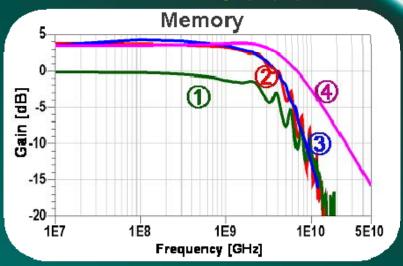

# レシーバの線形イコライゼーションの計測

#### • 周波数応答

- (1) チャンネルの計測結果

- (2) チャンネル及びレシーバCTLEの計測結果

- (3) チャンネルとレシーバの線形イコライゼーションのモデル

- (4) 抽出されたレシーバCTLEのモデル

# オンチップ計測

- オンチップ計測回路はタイミングと電圧のマージンを 計測可能

- 任意のパターンを使ったリンク全体の応答を計測

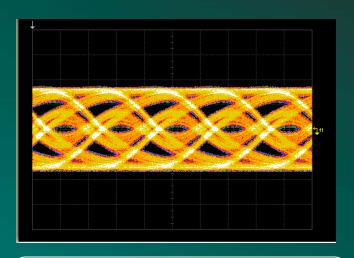

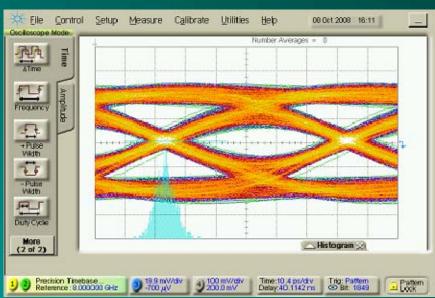

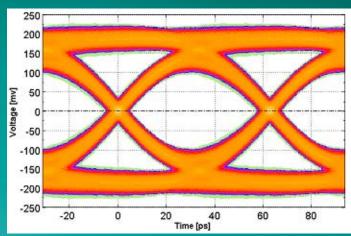

# オンチップ計測によるアイダイアグラム

**Using Measured SBR\***

**SI Simulation**

SBRを利用したオンチップ計測結果から生成したアイダイアグラムと シミュレーション結果でよい相関がとれた

39

Write Operation

Read Operation

# 完全なリンクモデル

- 完全なリンクシミュレーションを行うために以下のパラメータも必要となる

- ・トランスミッタ ジッタ

- RJ:標準偏差

- DJ:ピーク・トゥ・ピーク and/or 分布

- レシーバタイミングの不確実性

- RJ

- DJ:ピーク・トゥ・ピーク and/or 分布

- レシーバ 感度

- ランダムと確定的な電圧ノイズ

- •

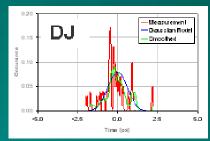

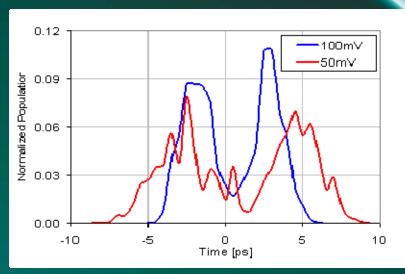

# トランスミッタのジッタ計測

コントローラデバイス

メモリデバイス

- <u>● 分解機能付きオシロスコー</u>プでの計測結果

- コントローラ

- RJ (rms) : 791 fs

- DCD: 540 fs

- ・メモリ

- RJ (rms): 378 fs

- DCD: 520 fs

**DCD = Duty Cycle Distortion**

\_.1.\_.1.\_

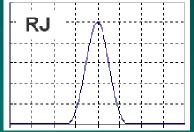

# レシーバのジッタ測定

- BERTを使用しレシーバのジッタを測定

- パターンジェネレータにてディレイを変化させる

- RJをバスタブカーブの傾斜から抽出

- DJとRJを分化する

- DJの分布を入力信号の振幅毎にプロット

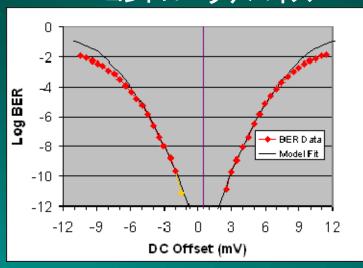

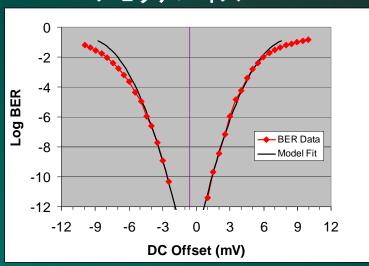

# レシーバの評価

#### コントローラデバイス

#### メモリデバイス

- DCオフセットの関数としてBERを計測

- 電圧バスタブカーブの傾斜から入力ノイズを抽出

- コントローラ

- RN : ≤ 1.3 mV rms

- DN : ≤ 5.0 mV

- ・メモリ

- RN:  $\leq$  0.8 mV rms

- DN : ≤ 2.0 mV

# アジェンダ

- ハイパフォーマンス・アプリケーションに要求される メモリインタフェイス

- XDR2 アーキテクチャ

- 次世代高速メモリアーキテクチャのデザインと検証

- チャレンジ

- システムの概要

- 基板とパッケージの設計とモデリング

- デバイス評価

- リンクのモデリング、シミュレーション及び評価

- まとめ

# テストシステムの評価結果

| Link parameters                 | WRITE                                | READ                          |

|---------------------------------|--------------------------------------|-------------------------------|

| Target BER                      | 10e <sup>-21</sup>                   |                               |

| Data rate                       | 16 Gbps                              |                               |

| Modulation (no coding)          | Binary NRZ                           |                               |

| Technology                      | TSMC 65-nm G+ CMOS                   | Emulates 40-nm DRAM process   |

| Supply Voltage (VDDA/VDD/VDDIO) | 1.1 V/1.1 V/1.2 V                    | 1.0 V/1.0 V/1.2 V             |

| Tx Swing                        | ±400 mV                              | ±300 mV                       |

| Equalization architecture       | Tx de-emphasis<br>(1-pre and 3-post) | CTLE with gain peaking > 4 dB |

| РСВ                             | 3-in microstrip or stripline         |                               |

| Package (of tx)                 | Thin-core FCBGA                      | Two-layer CSP                 |

| Device input Ci                 | 0.8 PF                               | 1.0 pF                        |

| DCD                             | 0.01 UI                              | 0.01 UI                       |

| Tx jitter RJ                    | 0.8 ps rms                           | 0.4 ps rms                    |

| Tx jitter DJ                    | 5 ps                                 | 5 ps                          |

| Rx timing uncertainties, RJ     | 0.9 ps                               | 1.0 ps                        |

| DJ                              | 10 ps                                | 10 ps                         |

| Rx sensitivity, random noise    | 1.3 mV (rms)                         | 1.4 mV (rms)                  |

| Deterministic noise*            | 3 mV                                 | 2 mV                          |

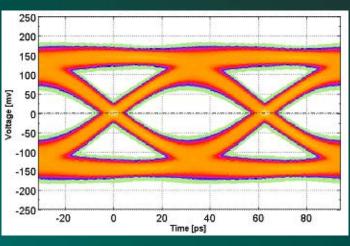

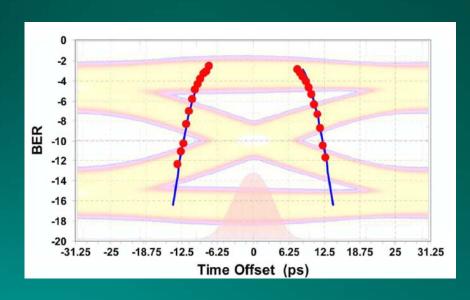

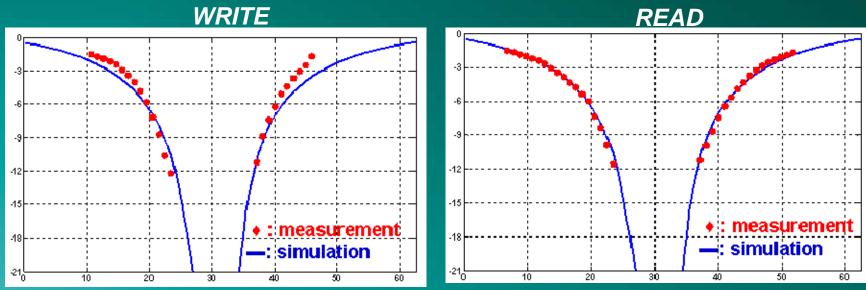

# リード及びライトのバスタブカーブ

実機とシミュレーションにて非常によい相関がとれた

#### まとめ

- 高速なデータレートでは、基板及びパッケージ間の整合が取れた接続が必要になる

- パッケージと基板上の配線は広範囲の周波数帯で評価された

- デバイスのリターンロス (Ci) は正確にモデル化された

- トランスミッタとレシーバ回路は正確にモデル化され評価された

- DJ、RJ及びレシーバノイズはモデル化され計測された

- システムシミュレーションによってシステムパフォーマンスを 予測し最適化及び検証を行った

- モデル化及び計測によって得られたパラメータによってリンクのBERは実機とシミュレーションでよい相関がとれた