## Development of Trigger and Control Systems for CMS

### J. A. Jones

High Energy Physics

Blackett Laboratory

Imperial College

London

A thesis submitted for the degree of Doctor of Philosophy of the University of London and the Diploma of Imperial College

December 2006

#### Abstract

During the year of 2007, the Large Hadron Collider (LHC) and its four main detectors will begin operation with a view to answering the most pressing questions in particle physics. However before one can analyse the data produced to find the rare phenomena being looked for, both the detector and readout electronics must be thoroughly tested to ensure that the system will operate in a consistent way.

The Compact Muon Solenoid (CMS) is one of the two general-purpose detectors at CERN. The tracking component of the design produces more data than any previous detector used in particle physics, with approximately ten million detector channels. The data from the detector is processed by the tracker Front End Driver (FED). The large data volume necessitated the development of a buffering and throttling system to prevent buffer overflow both on and off the detector. A critical component of this system is the APV emulator (APVe), which vetoes trigger decisions based on buffer status in the tracker. The commissioning of these components, along with a large part of the Timing, Trigger and Control (TTC) system is discussed, including the various modifications that were made to improve the robustness of the full system.

Another key piece of the CMS electronics is the calorimeter trigger system, responsible for identifying 'interesting' physical events in a background of well-understood phenomena using calorimetric information. Calorimeter information is processed to identify various trigger objects by the Global Calorimeter Trigger (GCT). The first component of this system is the Source card, which has been developed to transfer data from the Regional Calorimeter Trigger (RCT) to the Leaf card, the processing engine of the GCT. The use of modern programmable logic with high speed optical links is discussed, emphasising its use for data concentration and the benefit it confers to the processing algorithms.

Looking forward to Super-LHC, a possible addition to the CMS Level-1 trigger system is discussed, incorporating information from a new pixel detector with an alternative stacked geometry that allows the possibility of on-detector data rate reduction by means of a transverse momentum cut. A toy Monte Carlo was developed to study detector performance. Issues with high-speed reconstruction and the complications of on-detector data rate reduction are also discussed.

### Acknowledgements

To Geoff my supervisor, for letting me build things that other people wouldn't have entrusted to me. Costas Foudas for getting me interested in High Energy Physics and for being a mentor. Mark Raymond, for being a genuinely great (and far too modest) person. Matthew Noy, for pushing me further than I could have gone on my own working on the I-ImaS project, teaching me to drink Guinness and for being a good friend. My family, for looking out for me when I was too tired to notice. Renata Longo and Christian Venanzi, for going far beyond the call of duty working with us on the first I-ImaS beam test. Freya Blekman, for giving me an idea of the practical side of hadronic physics. Jose Carlos Rasteiro Da Silva, Mike Matveev and Paul Padley for their advice on optical link design. Jan Troska for his help testing the Source card optical links and measuring the QPLL locking range. Magnus Hansen and Matt Stettler for being great colleagues to work with - I learned a lot from you guys. Andrew Rose, for knowing far too much about most things for a 1st year PhD student and being modest about it. Gregory Iles, who provided advice on the IDAQ design and helped get me started with FPGAs when I was first learning and for the time spent working on the CMS GCT. James Leaver - how you work so religiously I'll never know. Davy Machin on the I-ImaS project - ni hao! Renato Turchetta, Jamie Crooks and Andrea Fant at Rutherford Appleton Laboratory for their insight and pub lunches working on the I-ImaS and HEPAPS sensors. Sarah Greenwood for doing a brilliant job on the IDAQ and GCT Source card PCB layouts, and for putting up with me when I changed my mind! Maria Khaleeq, Vera Kasey and Dave Price in the electronic workshop for their advice and help. Mark Pesaresi, for being quick with a joke when the mood got too serious. Everyone else in Imperial HEP for their help in whatever form it took. Kate Bishop for her incredible cooking! Seb Tallents for being around when things got too much, and for discussions about the finer points of the British political system (although you did all the talking!). Stephanie Wright for understanding that my PhD took up a lot of my time and not complaining (although you had every right to!). Paul Spicer at the Royal College of Music and Timothy Salter at the Ionian Singers for letting me sing - it took my mind off the thesis! Richard Hallam, Chris Rogers, William Panduro-Vazquez, Catherine Fry, Stuart Wakefield - it was fun being in your year.

## Contents

| Abs                  | stract  |                                                                                    | 1  |

|----------------------|---------|------------------------------------------------------------------------------------|----|

| $\mathbf{Ack}$       | nowle   | $\mathbf{d}\mathbf{g}\mathbf{e}\mathbf{m}\mathbf{e}\mathbf{n}\mathbf{t}\mathbf{s}$ | 2  |

| Cor                  | ntents  |                                                                                    | 3  |

| List                 | of Fig  | gures                                                                              | 8  |

| List                 | of Ta   | bles                                                                               | 16 |

| $\operatorname{Pre}$ | Preface |                                                                                    |    |

| Cha                  | apter 1 | 1. Introduction                                                                    | 17 |

| 1.1                  | Curre   | ent Searches in Particle Physics                                                   | 18 |

| 1.2                  | The I   | Large Hadron Collider (LHC)                                                        | 21 |

| 1.3                  | The C   | Compact Muon Solenoid                                                              | 26 |

|                      | 1.3.1   | The Silicon Tracker                                                                | 27 |

|                      | 1.3.2   | The Electromagnetic Calorimeter                                                    | 31 |

|                      | 1.3.3   | The Hadronic Calorimeter (HCAL)                                                    | 32 |

| Cor | ntents  |                                                  | $\frac{4}{}$ |

|-----|---------|--------------------------------------------------|--------------|

|     | 1.3.4   | The Muon Detectors                               | 33           |

|     | 1.3.5   | The CMS Trigger System                           | 33           |

|     | 1.3.6   | XDAQ                                             | 36           |

| 1.4 | Progra  | ammable Logic Devices                            | 37           |

|     | 1.4.1   | History                                          | 37           |

|     | 1.4.2   | The Complex Programmable Logic Device (CPLD)     | 38           |

|     | 1.4.3   | The Field Programmable Gate Array (FPGA)         | 38           |

|     | 1.4.4   | FPGA Clock Management                            | 39           |

|     | 1.4.5   | Input-Output Interfaces                          | 40           |

|     | 1.4.6   | Additional Features in Modern FPGAs              | 41           |

| Cha | apter 2 | 2. Integration of the CMS Tracker Readout System | 43           |

| 2.1 | The C   | CMS Tracker Readout System                       | 43           |

| 2.2 | The T   | racker Front End Driver                          | 47           |

| 2.3 | Buffer  | Overflow in the CMS Tracker                      | 48           |

|     | 2.3.1   | The APV25 Readout Buffer                         | 48           |

|     | 2.3.2   | The APVe                                         | 49           |

|     | 2.3.3   | Implementation of the APVe Firmware              | 50           |

|     | 2.3.4   | The APVe Software Interface                      | 51           |

| 2.4 | Integr  | ation of the APVe                                | 53           |

|     | 2.4.1   | Integration with the Global Trigger              | 53           |

|     | 2.4.2   | Online Recording of Trigger Statistics           | 54           |

| Coı | ntents  |                                             | 5  |

|-----|---------|---------------------------------------------|----|

|     | 2.4.3   | Feedback Loop Latency                       | 56 |

|     | 2.4.4   | Implementation of the FED Deglitcher Module | 57 |

| 2.5 | Comn    | nissioning of the Tracker FED               | 59 |

|     | 2.5.1   | Fake Event Generation                       | 59 |

|     | 2.5.2   | Test Setup                                  | 60 |

| Cha | apter 3 | 3. The Global Calorimeter Trigger           | 62 |

| 3.1 | The C   | Calorimeter Trigger Algorithms              | 62 |

|     | 3.1.1   | Electron/Photon (e/ $\gamma$ )              | 63 |

|     | 3.1.2   | Jets                                        | 63 |

|     | 3.1.3   | Other triggers                              | 65 |

| 3.2 | The C   | Global Calorimeter Trigger                  | 65 |

| 3.3 | The C   | GCT Source Card Design                      | 68 |

|     | 3.3.1   | Development Challenges                      | 72 |

|     | 3.3.2   | Firmware Architecture                       | 75 |

|     | 3.3.3   | Software Architecture                       | 82 |

| 3.4 | Evalu   | ation and Testing of the Source Card        | 84 |

|     | 3.4.1   | RCT Emulator Data Capture                   | 85 |

|     | 3.4.2   | Integration with the RCT                    | 89 |

|     | 3.4.3   | Optical Links                               | 91 |

|     | 3.4.4   | QPLL Locking Range                          | 94 |

|     | 3.4.5   | Source Card Production Testing              | 94 |

| Cha | apter 4 | a. Super-LHC and the CMS Trigger         | 97  |

|-----|---------|------------------------------------------|-----|

| 4.1 | Implie  | eations for the CMS L1 Trigger           | 97  |

| 4.2 | Tracke  | er Contributions to Triggering           | 99  |

|     | 4.2.1   | The Electron Algorithm                   | 99  |

|     | 4.2.2   | The $\tau$ -Jet Algorithm                | 100 |

| 4.3 | Issues  | with the Implementation of a new Tracker | 100 |

|     | 4.3.1   | Tracker Occupancies and Data Rate        | 100 |

|     | 4.3.2   | Limitations of the Current CMS Tracker   | 101 |

|     | 4.3.3   | Reconstruction Combinatorials            | 102 |

| 4.4 | Imple   | mentation of Stacked Tracking            | 106 |

|     | 4.4.1   | Reconstruction                           | 106 |

|     | 4.4.2   | Probability of Hit-Pair Finding          | 109 |

| 4.5 | Simula  | ation Studies                            | 110 |

|     | 4.5.1   | Simulated Reconstruction Performance     | 112 |

|     | 4.5.2   | Simulated Resolution                     | 115 |

| 4.6 | Doubl   | e Stack Reconstruction                   | 117 |

|     | 4.6.1   | Reconstruction Method                    | 118 |

|     | 4.6.2   | Transverse Momentum Resolution           | 121 |

|     | 4.6.3   | Projected Resolution                     | 122 |

| 4.7 | Recon   | struction Implementation                 | 124 |

|     | 4.7.1   | Correlation Logic Implementation         | 124 |

|     |         |                                          |     |

| Con                  | ntents                                           | 7   |

|----------------------|--------------------------------------------------|-----|

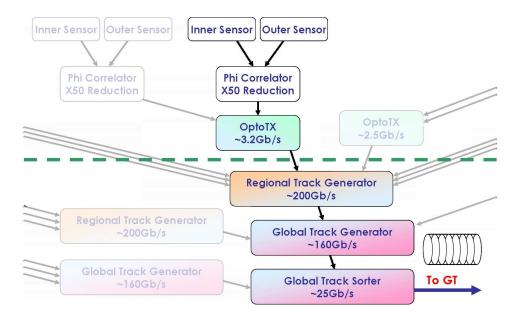

|                      | 4.7.2 Data Processing Flow                       | 125 |

|                      | 4.7.3 Further Improvements                       | 127 |

| 4.8                  | Summary                                          | 128 |

| Cha                  | apter 5. Conclusions                             | 129 |

| Арр                  | pendix A. Development and Evaluation of the IDAQ | 131 |

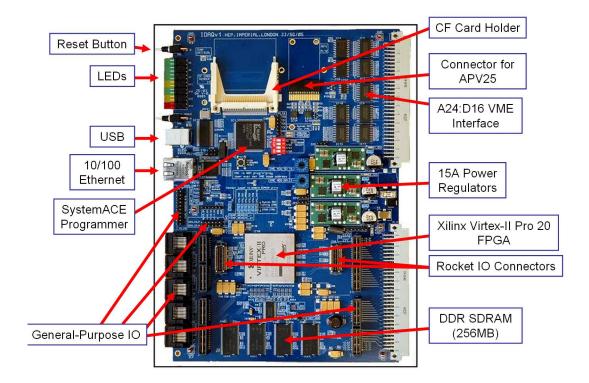

| A.1                  | Design of the Imperial DAQ (IDAQ)                | 131 |

|                      | A.1.1 Board Components                           | 133 |

|                      | A.1.2 PCB Stackup and FPGA Decoupling            | 136 |

|                      | A.1.3 Upgrade Possibilities                      | 138 |

| A.2                  | Evaluation and Testing                           | 138 |

| A.3                  | Summary                                          | 139 |

| App                  | pendix B. VHDL Code Examples                     | 140 |

| В.1                  | CRC-32 Generator                                 | 140 |

| B.2                  | The TTC SERIAL_B Decoder                         | 145 |

| В.3                  | The FED Status Deglitcher                        | 148 |

| B.4                  | 4-Phase Interlocked Strobe                       | 150 |

| B.5                  | Trigger Histogrammer                             | 152 |

| $\operatorname{Glo}$ | ssary                                            | 154 |

| $\operatorname{Ref}$ | erences                                          | 160 |

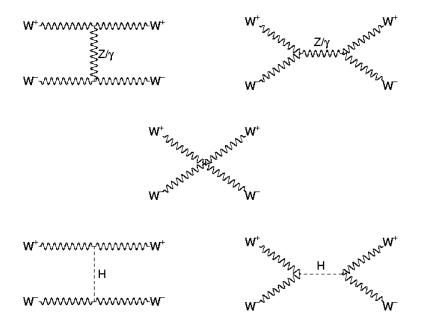

| 1.1 | The five second-order WW scattering diagrams in the Standard Model.                                        |    |

|-----|------------------------------------------------------------------------------------------------------------|----|

|     | Note that the two diagrams involving the Higgs boson act to cancel the                                     |    |

|     | divergences in the other three diagrams.                                                                   | 19 |

| 1.2 | Latest results of searches for the Higgs boson. Taken from [1].                                            | 20 |

| 1.3 | Total pp collision cross-sections for varying collision energies [2]. The                                  |    |

|     | highest-energy points in this plot are from cosmic ray data.                                               | 22 |

| 1.4 | Higgs production channels at the LHC.                                                                      | 24 |

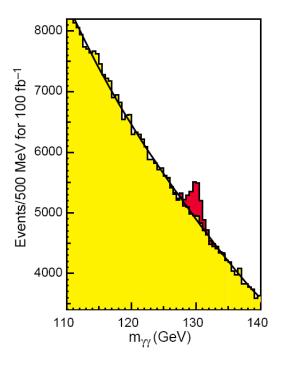

| 1.5 | Signal for $m_H=130 {\rm GeV~H} \rightarrow \gamma \gamma$ after $100 {\rm fb^{-1}}$ of data recorded. The |    |

|     | Higgs signal is shown in red, background in yellow. Adapted from [3].                                      | 25 |

| 1.6 | Higgs discovery channels at CMS. Depending on the Higgs mass, various                                      |    |

|     | decays become favourable due to a combination of production rates for                                      |    |

|     | the intermediate particles and the background rates.                                                       | 26 |

| 1.7 | Diagram of the CMS detector.                                                                               | 27 |

| 1.8 | Layout of a quarter of the CMS tracking detector. This image is mirrored                                   |    |

|     | along both axes to make the full detector layout. The interaction point                                    |    |

|     | is marked at $z=0$ .                                                                                       | 28 |

|     |                                                                                                            |    |

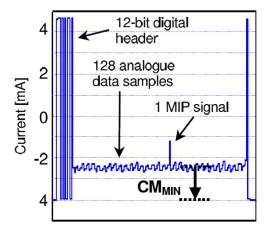

| 1.9  | A single APV data frame with the passage of time indicated by the horizontal axis. A frame begins with a digital header including pipeline address information, followed by analogue voltage levels for each of the 128 APV channels in that bunch crossing. The end of the frame is                                                                                 |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | indicated by another digital strobe. Taken from [4].                                                                                                                                                                                                                                                                                                                 | 30 |

| 1.10 | Diagram of the CMS trigger/Data AcQuisition (DAQ) system. Data from the detector are first sent to the Level-1 trigger for processing and then selected events have the front-end detector data sent to the Higher Level Trigger for further processing. Status reports from the different subsystems allow debugging and throttling of the trigger systems to allow |    |

|      | a sustainable trigger rate to be attained.                                                                                                                                                                                                                                                                                                                           | 34 |

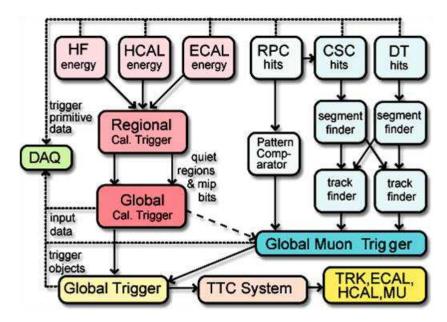

| 1.11 | Diagram of the CMS L1 trigger. Most of the system is located in the underground cavern next to the detector to minimise latency. The only exception to this is the first part of the muon track finder, which is attached to the outside of the detector.                                                                                                            | 35 |

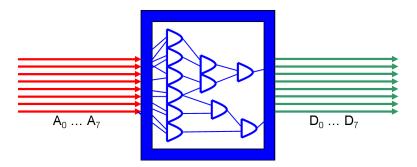

| 1.12 | Diagram of a ROM LUT. The device is programmed with the equivalent output for every permutation of input to a particular logic circuit.                                                                                                                                                                                                                              | 38 |

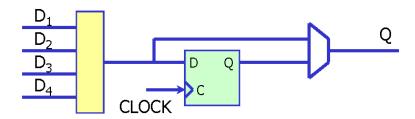

| 1.13 | Diagram of a four-input FPGA LUT. The multiplexer selects between registered and unregistered modes of operation, allowing large combinatorial circuits to be produced. Alternatively registers can be used to create more pipelined designs.                                                                                                                        | 39 |

| 2.1  | Diagram of a CMS tracker partition.                                                                                                                                                                                                                                                                                                                                  | 44 |

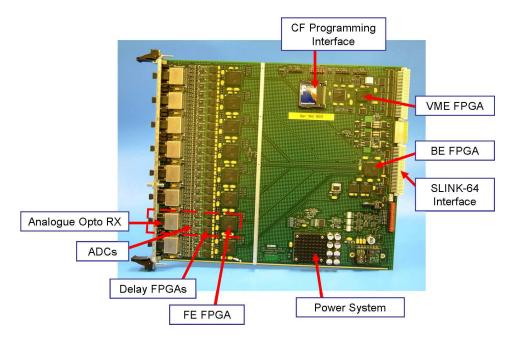

| 2.2  | Diagram of the CMS tracker FED.                                                                                                                                                                                                                                                                                                                                      | 48 |

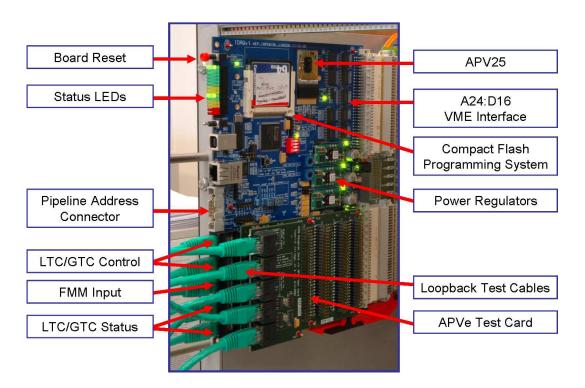

| 2.3  | Diagram of IDAQ connections for the APVe.                                                                                                                                                                                                                                                                                                                            | 50 |

|      |                                                                                                                                                                                                                                                                                                                                                                      |    |

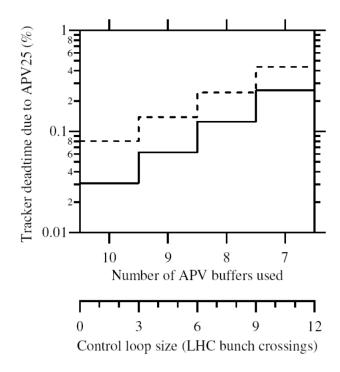

| 2.4  | Theorised readout 'dead-time' for the CMS tracker [5]. This directly depends on the control loop size, which is related to the number of APV buffers than can be used before the APVe asserts BUSY. The solid line indicates the performance when using the 'virtual' APV emulation in the FPGA, whilst the dashed line represents the performance achieved when using the 'real' APV. | 51 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

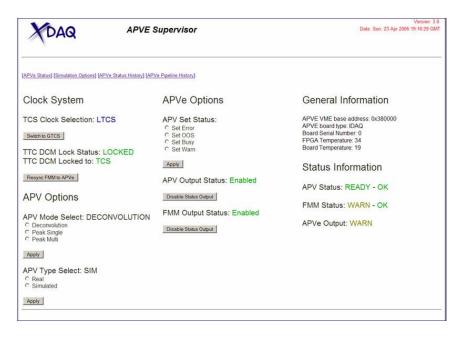

| 2.5  | The main page of the APVe HyperDAQ interface, showing the basic settings and status information for one of the boards.                                                                                                                                                                                                                                                                 | 52 |

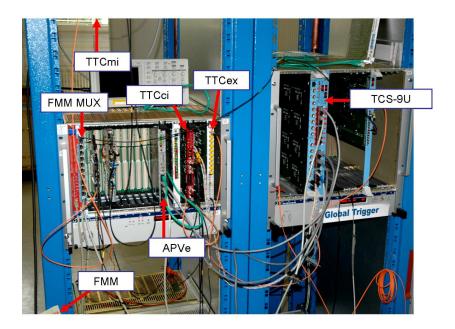

| 2.6  | Test setup for integration of the APVe with the global trigger system.                                                                                                                                                                                                                                                                                                                 | 53 |

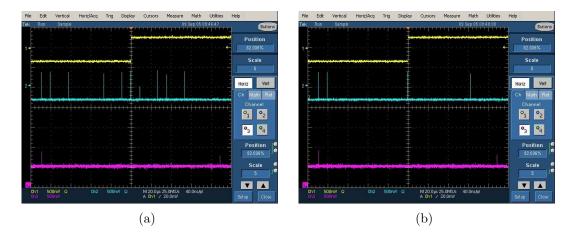

| 2.7  | Two examples of the APVe asserting ERROR when an orbit BC0 from the TCS-9U coincides with a L1 trigger. The magenta trace shows the BC0 strobe, the cyan trace represents L1As and the yellow trace represents a READY $\rightarrow$ ERROR transition. Note the missing BC0 when it coincides with a L1 trigger.                                                                       | 54 |

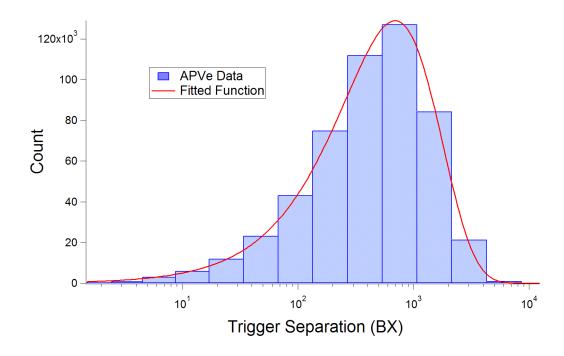

| 2.8  | Results from a real-time histogram of the trigger distribution as measured by the APVe during testing, as viewed using the HyperDAQ interface. In this case the LTC was being used to generate a fake Poisson trigger distribution with a mean of 100kHz.                                                                                                                              | 56 |

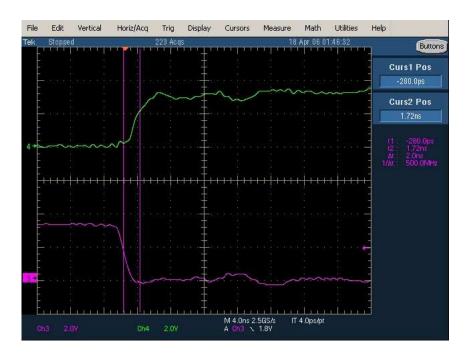

| 2.9  | Measurements of a READY-WARN transition at the APVe FMM input connector. The purple trace represents the de-assertion of a READY state, whilst the green trace represents the assertion of a WARN state.                                                                                                                                                                               | 58 |

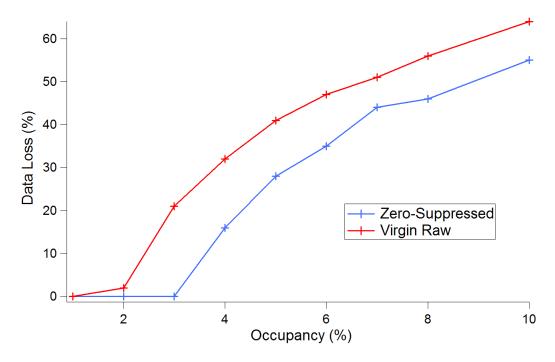

| 2.10 | Data loss when throttling during a full FED test using 100kHz Poisson triggers (adapted from [6]). These measurements are compatible with those in [7].                                                                                                                                                                                                                                | 61 |

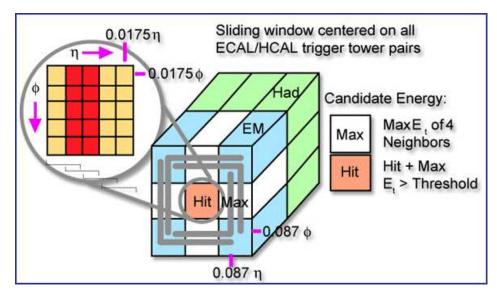

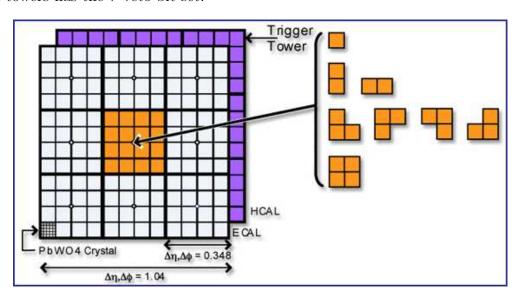

| 3.1  | The calorimeter trigger $e/\gamma$ algorithm [8].                                                                                                                                                                                                                                                                                                                                      | 63 |

| 3.2  | The calorimeter trigger jet algorithm [8].                                                                                                                                                                                                                                                                                                                                             | 64 |

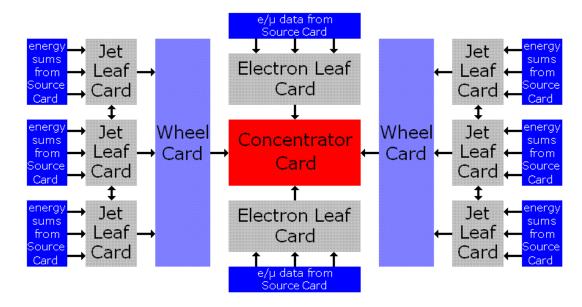

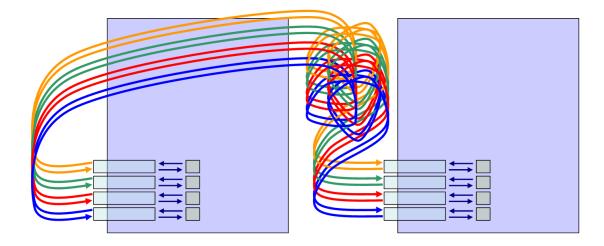

| 3.3  | The GCT architecture. The half-barrel geometry of the detector is mirrored by the hardware in its symmetry from left to right.                                                                                                                                                                                                                                                                                                         | 67 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

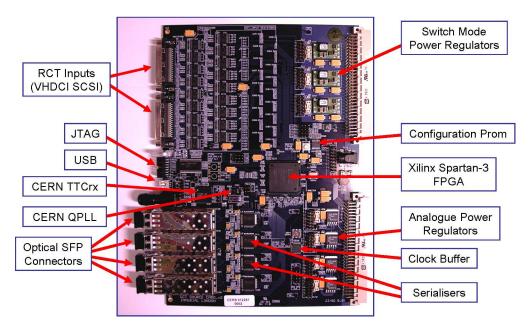

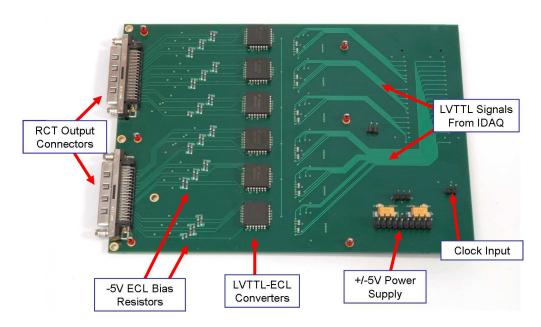

| 3.4  | Picture of a Source card.                                                                                                                                                                                                                                                                                                                                                                                                              | 69 |

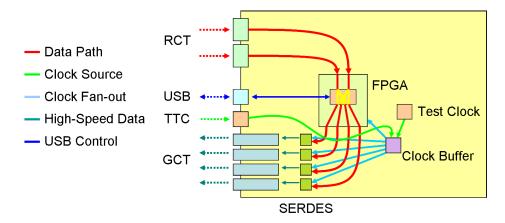

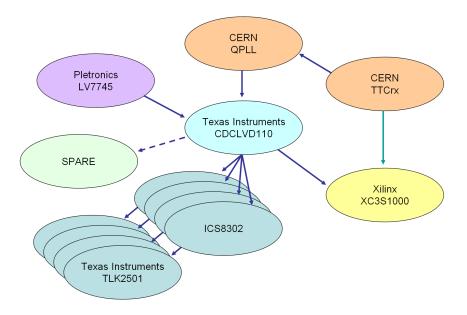

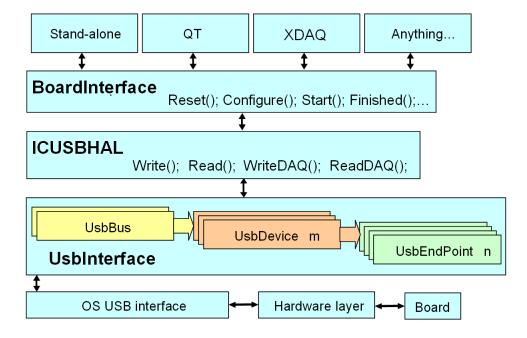

| 3.5  | Simplified schematic of data flow through a Source card during normal operation. RCT data are captured by the FPGA, multiplexed and fed into four serialisers. The entire board is driven by either a local test oscillator or LHC clock via the TTC input. A USB link provides a control interface for board settings.                                                                                                                | 71 |

| 3.6  | The Source card clock system.                                                                                                                                                                                                                                                                                                                                                                                                          | 74 |

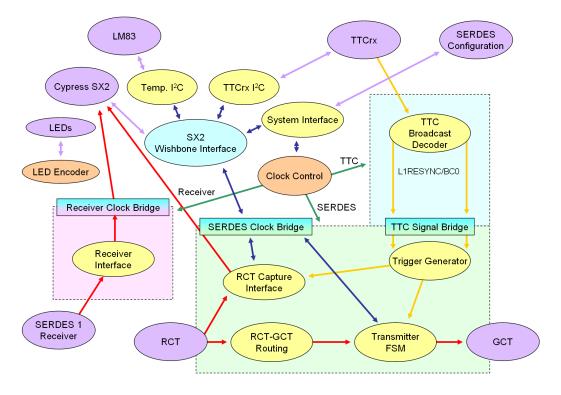

| 3.7  | Schematic diagram of the Source card firmware.                                                                                                                                                                                                                                                                                                                                                                                         | 75 |

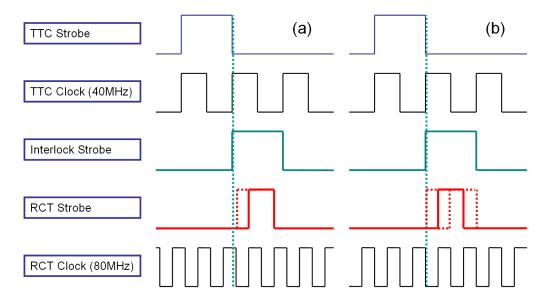

| 3.8  | Interlocking method for passing strobes between the TTC (40MHz) and RCT (80MHz) clock domains. When the rising edge of the TTC clock does not coincide with an edge of the RCT clock: (a), either edge can be used to transfer the strobe into the transmitter clock domain. However when coincidental with an edge either the rising or falling edge can be used (whichever is not coincidental with the TTC clock rising edge): (b). | 78 |

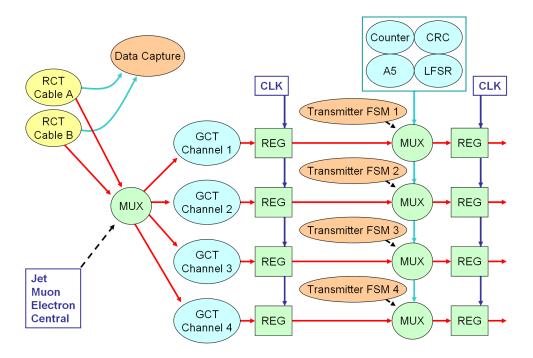

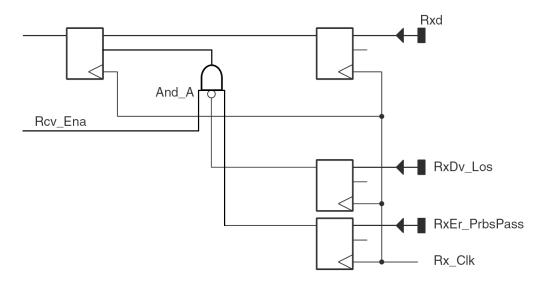

| 3.9  | Data pathway for the transmitter clock domain.                                                                                                                                                                                                                                                                                                                                                                                         | 79 |

| 3.10 | Data registering architecture for the receiver clock domain (adapted from [9]).                                                                                                                                                                                                                                                                                                                                                        | 81 |

| 3.11 | Software implementation for the Source card.                                                                                                                                                                                                                                                                                                                                                                                           | 83 |

| 3.12 | The RCT emulator card. It is designed to be mounted on an IDAQ. The ICs are TTL-ECL converters which take signals from the FPGA on the IDAQ. Next are the -5V bias resistors and two VHDCI (HD68) SCSI connectors.                                                                                                                                                                                                                     | 85 |

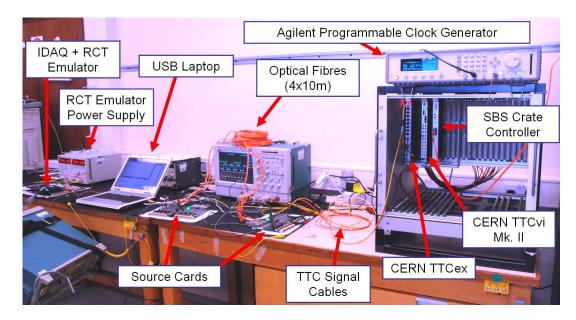

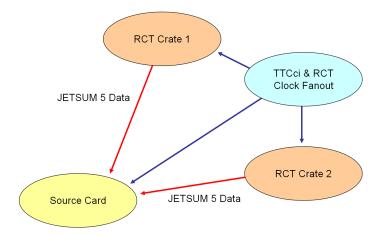

| 3.13 | Component interconnections for the RCT emulator-Source card test. A common clock from a TTCci is shared by the Source card and two RCT crates, making a synchronous test possible. Data from the JETSUM 5 output on each RCT crate is captured by the Source card.                                                                                                                                                                     | 86 |

|      | output on each ricer crate is captured by the source card.                                                                                                                                                                                                                                                                                                                                                                             | 30 |

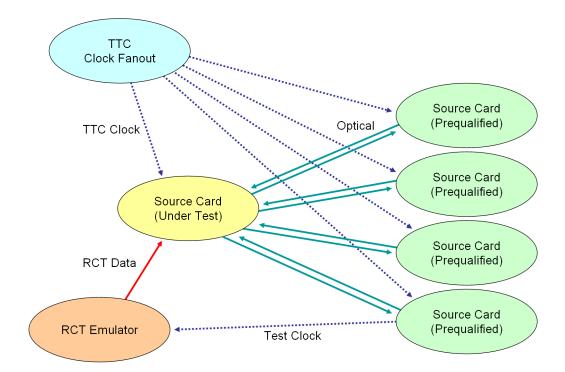

| 3.14 | Component interconnections for the RCT-Source card integration test.                                                                                                                                                                                                                                                                                                      | 89  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

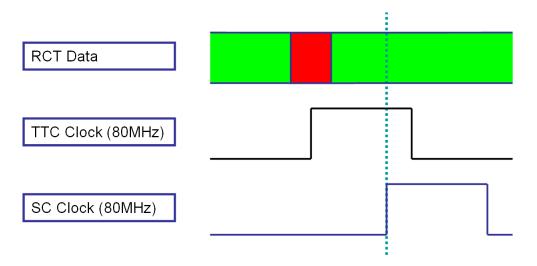

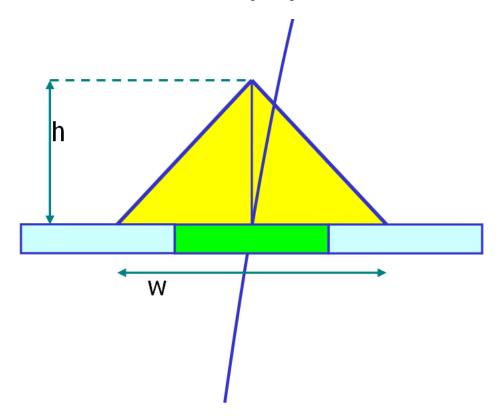

| 3.15 | Calibration of the RCT data capture window. The red region around the rising edge of the TTC/RCT clock represents the period of time during which the data lines are not stable. The green region represents stable data. In order to capture data efficiently, the rising edge of the Source card (SC) clock should be aligned with the middle of the valid data region. | 90  |

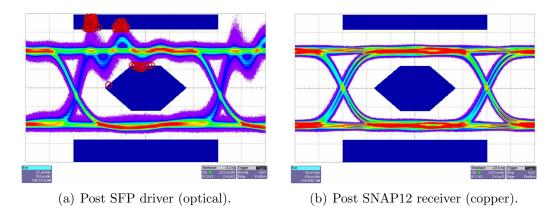

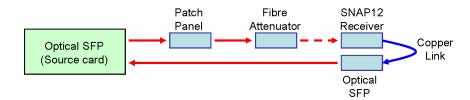

| 3.16 | Eye diagrams of high-speed signals from the Source card.                                                                                                                                                                                                                                                                                                                  | 92  |

| 3.17 | Test setup for measuring the effect of optical attenuation on the GCT links.                                                                                                                                                                                                                                                                                              | 92  |

| 3.18 | PRBS test interconnections between two Source cards. Each serial link on one board is connected to one of the serial links on the other board.                                                                                                                                                                                                                            | 93  |

| 3.19 | Final test setup for the GCT Source cards. Having qualified four Source cards for final use, the rest of the boards can be qualified using four routed receivers (one per card). This allows all of the tests to be carried out with little human intervention.                                                                                                           | 95  |

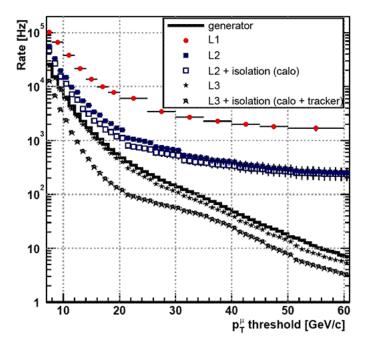

| 4.1  | L1 single muon trigger rates for CMS [10]. Note the flattening of the L1 and L2 trigger curves where tracking information is not used. Only the additional information provided in the HLT at L2.5 and L3 can provide sufficient momentum resolution to control the trigger rate.                                                                                         | 98  |

| 4.2  | The HLT electron algorithm - taken from [11, 12].                                                                                                                                                                                                                                                                                                                         | 100 |

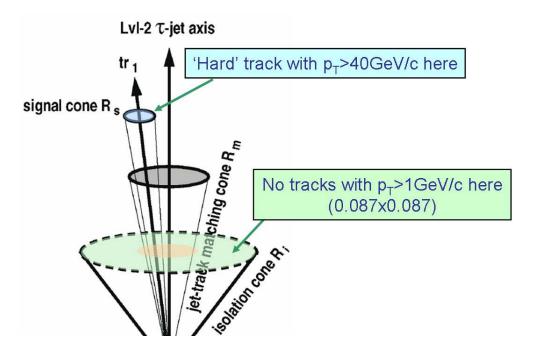

| 4.3  | The HLT $\tau$ -jet algorithm [10].                                                                                                                                                                                                                                                                                                                                       | 101 |

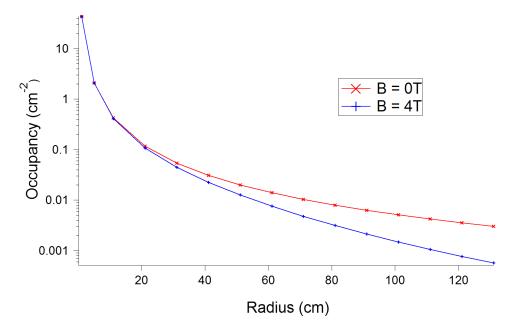

| 4.4  | Simulated occupancy in the CMS tracker in SLHC.                                                                                                                                                                                                                                                                                                                           | 102 |

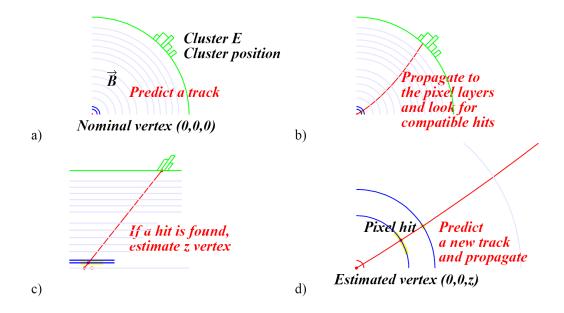

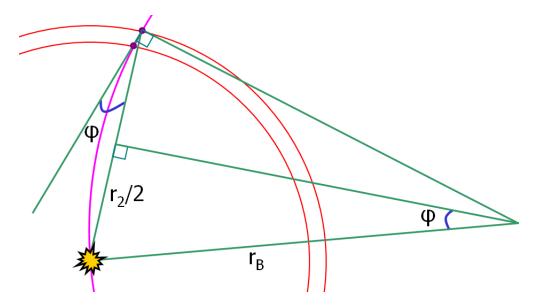

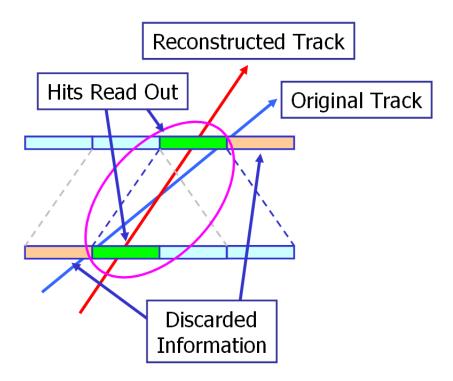

| 4.5  | Illustration of the principle of a search window for pixel seeding.                                                                                                                                                                                                                                                                                                       | 103 |

| 4.6  | Track overlap in y-z plane (detector co-ordinates). Note the significant overlap of tracks between these two layers in the case of 1cm layer separation, which will hinder track reconstruction.                                                                                                                                                                          | 105 |

|      | ration, which will hinder track reconstruction.                                                                                                                                                                                                                                                                                                                           | 105 |

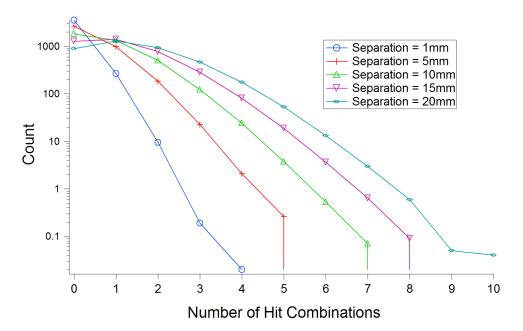

| 1.7  | Average number of hit combinations per bunch crossing versus count $r=10cm$ for varying pixel layer separations, with a $p_T$ cut of 1GeV. For this plot 100 minimum bias events were super-imposed for each bunch crossing.                                                                                                                                                              | 105 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

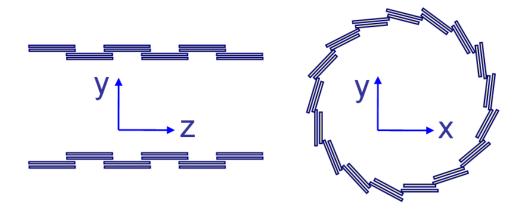

| 1.8  | Basic layout of a flat stacked tracker (not to scale). Left is a y-z view, right is an x-y view.                                                                                                                                                                                                                                                                                          | 106 |

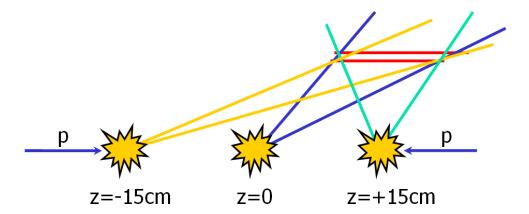

| 4.9  | Illustration of the effect of the size of the luminous region on the overlap of the segments of the detector.                                                                                                                                                                                                                                                                             | 107 |

| 4.10 | Mean cumulative count of the charged particles per collision versus their radius of curvature, counting from high to low $p_T$ . 100 super-imposed events per bunch crossing are used in this plot. The discontinuities seen at higher $p_T$ are the result of limited statistics.                                                                                                        | 108 |

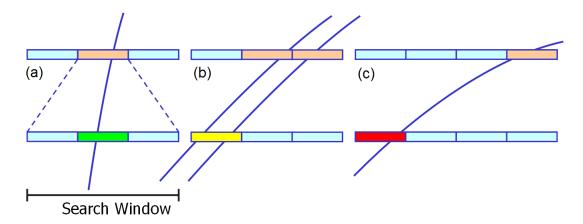

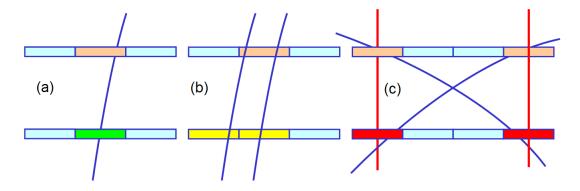

| 4.11 | Tangent-point reconstruction in detail. In a binary readout scheme, a pixel is simply active or inactive. There are things that can happen during correlation: (a) The track is always found in the search. (b) A lower- $p_T$ track may or may not be recorded depending on the impact point of the track on the sensor. (c) The $p_T$ is low and so the track will never pass a search. | 109 |

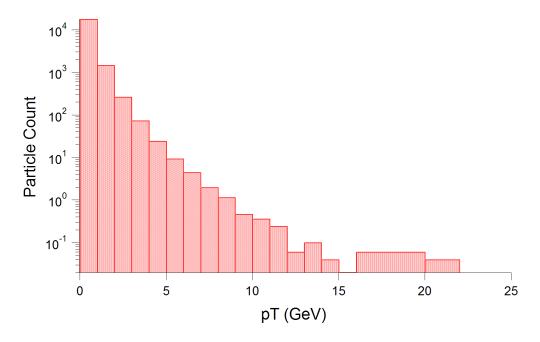

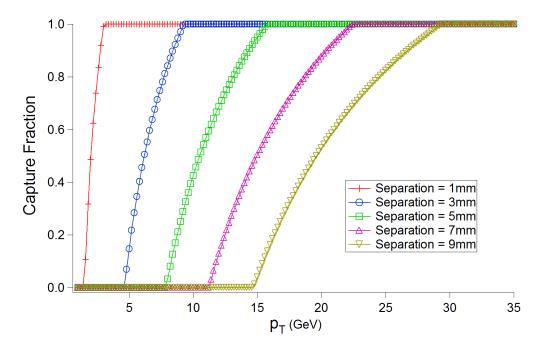

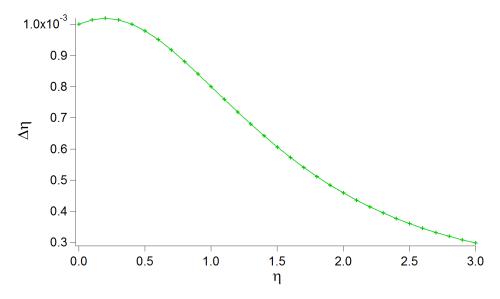

| 4.12 | Capture probabilities for particles with varying transverse momenta. The $r\phi$ pitch is $20\mu m$ . Inner sensor radius is 10cm.                                                                                                                                                                                                                                                        | 110 |

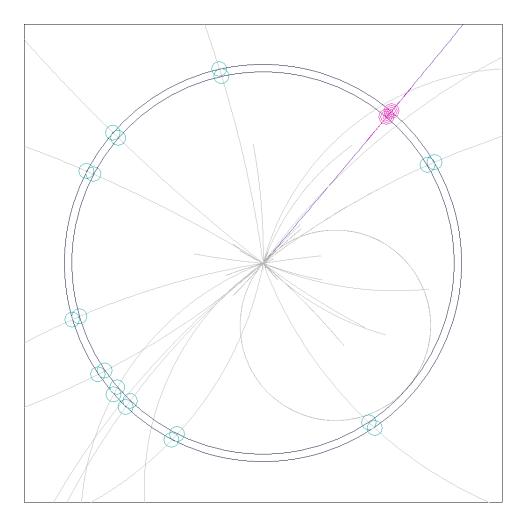

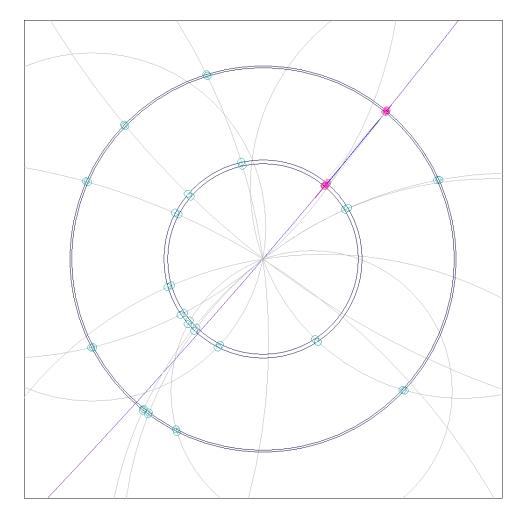

| 4.13 | Three stages of simulation: The tracks are constructed (light grey), hits are found (cyan) and those passing the geometrical $p_T$ cut are selected for readout (pink). The dark blue track is from a high- $p_T$ lepton.                                                                                                                                                                 | 111 |

| 4.14 | Charge sharing model.                                                                                                                                                                                                                                                                                                                                                                     | 112 |

| 4.15 | From left to right: Pure (a), impure (b) and incorrect (c) track reconstructions.                                                                                                                                                                                                                                                                                                         | 113 |

| 4.16 | Illustration of the effect of charge sharing. In this case, if a search window of only one pixel in $\pm r\phi$ is chosen, the track will be considered to have a higher $p_T$ than it does in reality, and some information about the cluster will be lost.                                    | 116 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

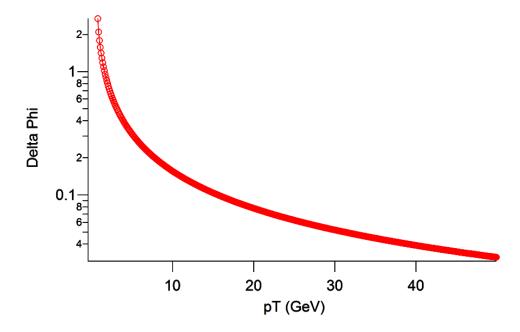

| 4.17 | Azimuthal angular separation in radians for a given particle $p_T$ between the projected tangent of a track at its point of intersection with the stacked tracker and the point on the calorimeter which it hit.                                                                                | 117 |

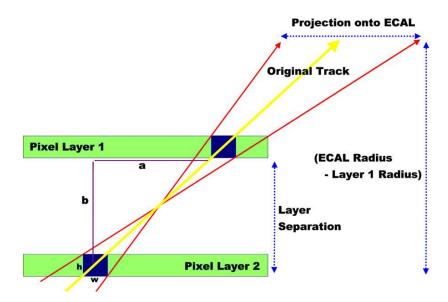

| 4.18 | Minimum and maximum pseudo-rapidities for a given pixel pair. This is referred to as the min-max range. A similar method is used to calculated the $\Delta\phi$ resolution.                                                                                                                     | 118 |

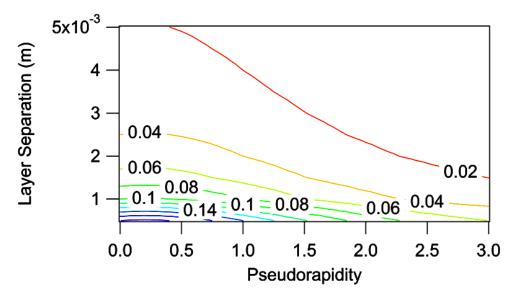

| 4.19 | The stub resolution for a track extrapolated to the calorimeter. The values depend on both the separation between the two sensor layers and the position of the calorimeter hit. The values shown on the plot represent $\Delta \eta$ .                                                         | 119 |

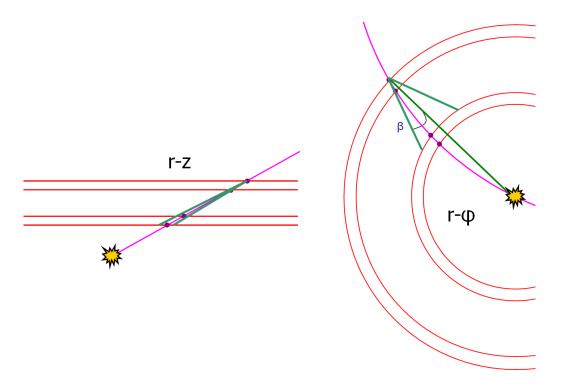

| 4.20 | Reconstruction using the double-stack method. The left diagram shows the straight-line projection of the track in the rz plane, while the other diagram shows the curved projection of the track in the $r\phi$ plane.                                                                          | 120 |

| 4.21 | The four stages of double-stack reconstruction. In addition to the three stages used in a single stack, once the data has been sent off-detector a correlation is made between stubs in the individual superlayers.                                                                             | 121 |

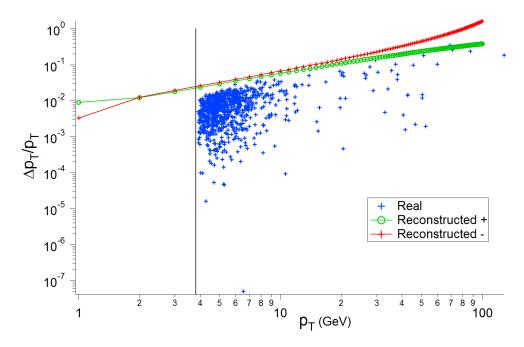

| 4.22 | Transverse momentum measurement using the double-stack method. The black line represents the reconstruction transverse momentum cut, the 'true' points are from simulation and the red and green lines represent the largest possible error in reconstructed $p_T$ and therefore the worst-case |     |

|      | momentum resolution.                                                                                                                                                                                                                                                                            | 123 |

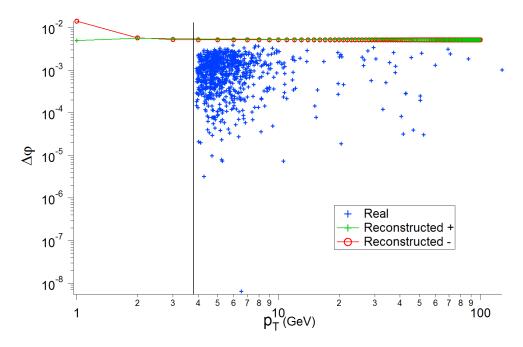

| 4.23 | Reconstructed angular resolution at the calorimeter-tracker interface plot-             |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | ted as a function of real transverse momentum. The black line represents                |     |

|      | the reconstruction transverse momentum cut, the 'real' points are from                  |     |

|      | simulation and the red and green lines represent the largest possible $\pm \Delta \phi$ |     |

|      | variation and therefore the worst-case momentum resolution. Note the                    |     |

|      | significantly improved resolution when compared to figure 4.17.                         | 124 |

| 4.24 | Projected ECAL resolution in $\eta$ using the double-stack method. Note                 |     |

|      | the significantly improved resolution when compared to figure 4.19. It                  |     |

|      | should be borne in mind that a full simulation would include material                   |     |

|      | effects, which would result in a 'band' for reconstruction resolution rather            |     |

|      | than a line.                                                                            | 125 |

| 4.25 | Illustration of different stages of data processing both on and off-detector.           |     |

|      | The top half of this diagram represents on-detector electronics whilst the              |     |

|      | bottom half is off-detector.                                                            | 126 |

|      |                                                                                         |     |

| A.1  | Block diagram of the IDAQ.                                                              | 132 |

## List of Tables

| 1.1 | Examples of Level-1 triggers and their relation to their underlying physics       |     |

|-----|-----------------------------------------------------------------------------------|-----|

|     | channels. Taken from [8].                                                         | 36  |

| 1.2 | Examples of various I/O standards and their supply voltages in Xilinx devices.    | 41  |

| 2.1 | Latencies between various test points for a READY $\rightarrow$ WARN transition.  |     |

|     | The values are rounded to the nearest bunch crossing as this reflects the         |     |

|     | registered nature of the transmitted signals.                                     | 57  |

| 2.2 | Skew measurements between the READY and WARN states on the FED                    |     |

|     | and FMM, measured to the nearest 100ps.                                           | 58  |

| 3.1 | Latency measurements between different test points in the Source card.            | 88  |

| 3.2 | Contributions to skew on the GCT Source card.                                     | 91  |

|     |                                                                                   |     |

| 4.1 | Performance of a detector stack for sensors of lateral pitch $20x50\mu\text{m}^2$ |     |

|     | $(r\phi xz)$ .                                                                    | 114 |

## Chapter 1

## Introduction

"Who has seen the wind?

Neither I nor you:

But when the leaves hang trembling,

The wind is passing through

Who has seen the wind?

Neither you nor I:

But when the trees bow down their heads,

The wind is passing by."

- Christina Rosetti

The search for the Higgs boson or other even more elusive signs of new physics is like searching for something as ethereal yet omni-present as the wind. It is not surprising that modern physics is looking for something so difficult to find; every generation of particle physics experiment naturally has to look with a keener eye than the previous one. This necessitates an improvement in the ability to identify the significant features in a background of less significant events and record them on a very short timescale ( $\mu$ s-ms). Hence this 'feature extraction' must occur 'online', in customised hardware rather than in software on a computer. This thesis considers the many demands placed on modern hardware for these purposes, in both current and future particle physics applications.

### 1.1 Current Searches in Particle Physics

The vast majority of particle physicists are focused on the search for the Higgs boson [13, 14, 15, 16, 17, 18]. This is motivated by the fact that particle masses are otherwise not present in the mathematics of Quantum Field Theory (QFT). Furthermore, the W and Z bosons would be massless if the fundamental symmetry of the electroweak sector was not broken. This must be achieved in a way that is locally gauge invariant. The scalar Higgs field was introduced as an additional term in the Standard Model Lagrangian as a solution to both of these problems. In the form taken in the Standard Model it comprises a doublet of complex scalar fields, resulting in four degrees of freedom. Three of these degrees of freedom are used to assign mass to the W and Z bosons; the fourth degree of freedom results in the Higgs boson itself. The Higgs boson couples to all massive particles in the Standard Model, with the coupling strength related to the mass of the particle. In the case of the W and Z bosons this coupling can be derived directly from the Higgs mechanism. The masses of the fermions are introduced explicitly using the Yukawa couplings.

The Higgs boson can also interact with the W and Z bosons directly, and in this way, (at least in the perturbative limit), it is responsible for cancelling the divergences found in WW scattering diagrams by providing a counterterm to the longitudinal component of the W boson (see figure 1.1), restoring gauge invariance while allowing the W to acquire mass. This is the key difference between using a Higgs model and introducing the W mass directly, which would not include these cancellation terms.

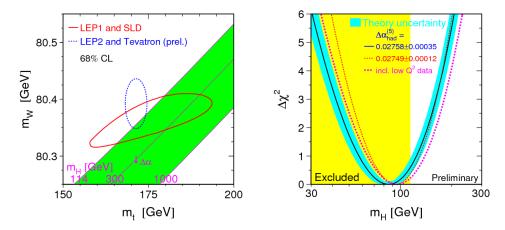

Figures 1.2(a) and 1.2(b) are the latest predictions for the most likely mass of the Higgs boson. While its mass is not currently well known (if indeed the particle exists at all), the most likely mass can be inferred using measurements from the electroweak sector [1]. Indirect experimental bounds for the Higgs mass can be calculated from electroweak observables, which are related to couplings between the Higgs boson and other fundamental particles. The reason for this derives from radiative corrections to the W<sup>±</sup> and Z propagators, for which the dominant effects are the  $W^+ \to \bar{b}t \to W^+$ ,  $W^- \to \bar{t}b \to W^-$ ,  $Z \to \bar{t}t \to Z$ ,  $Z \to HZ \to Z$  and

**Figure 1.1:** The five second-order WW scattering diagrams in the Standard Model. Note that the two diagrams involving the Higgs boson act to cancel the divergences in the other three diagrams.

$W^{\pm} \to HW^{\pm} \to W^{\pm}$  processes. Hence, by accurate measurement of the W<sup>±</sup>, Z, t and b masses, one can infer the most likely Higgs mass.

Initial estimates for the mass of the Higgs boson were calculated by the SLD experiment at SLAC [19] and the four LEP experiments [20]. As both experiments involved collisions between electrons and positrons they allowed both indirect measurements based on precision measurements of the Z and W boson mass and that of the b quark, and direct searches by looking for a resonance at the Higgs mass. Direct searches [21] were carried out at LEP by studying the Higgsstrahlung process  $e^+e^- \to HZ$  and the following decay modes:

- $H \rightarrow b\bar{b}, Z \rightarrow q\bar{q}$

- $H \rightarrow b\bar{b}, Z \rightarrow \nu\bar{\nu}$

- $H \rightarrow b\bar{b}, Z \rightarrow e^+e^-, \mu^+\mu^-$

- $H \to \tau^+ \tau^-, \ Z \to q\bar{q} \ {

m and} \ H \to q\bar{q}, \ Z \to \tau^+ \tau^-$

The results of these searches, marked by the yellow region in figure 1.2(b), exclude the possibility of a Standard Model Higgs mass less than 114.4GeV (95% confidence level).

(a) 68% confidence level region given the (b)  $\chi^2$  plot of  $m_H$  using the Tevatron and current best measurements of  $m_W$  and the results of direct LEP searches.  $m_t$ .

Figure 1.2: Latest results of searches for the Higgs boson. Taken from [1].

Proton colliders such as the  $p\bar{p}$  Tevatron accelerator [22] have improved statistical limits on estimates of a Higgs mass greater than 114.4GeV. In particular measurements of the mass of the top quark have been significantly improved upon (currently 170.9 $\pm$ 1.8GeV [23]), and therefore predictions of the most likely Higgs mass have also improved. However due to the high levels of background particles in proton colliders, it is very difficult to detect a Higgs boson directly.

While the Higgs is an elegant solution to the existence of symmetry breaking in the electroweak sector, as stated previously it (or something else) is also necessary to balance higher-order corrections to WW scattering (i.e.  $WW \to X \to WW$ ), which theoretical arguments otherwise predict will become divergent at an energy scale of approximately 1TeV (the so-called 'unitarity problem' [24]). If the Higgs boson does not exist, it will be necessary to study WW scattering in this energy range to understand what alternative mechanism is at work to prevent instabilities in the theory.

Even the Standard Model Higgs presents additional complications [25]; for example, the calculation of the Higgs mass directly from theory suffers higher-order quadratic and logarithmic divergences which occur as a result of radiative corrections to the Higgs mass. While the logarithmic divergences can be treated by using renormalisation, the quadratic divergences cannot. This is known as the naturalness problem as the only way to manage it within the limits of the Standard model is to fine-tune all the constants in the theory to an extremely precise degree. One possible solution to this problem is the introduction of SUperSYmmetry (SUSY) [26], in which every fermionic particle in the Standard Model would have a bosonic partner and vice versa. This cancels the quadratic radiative corrections to the Higgs mass through additional terms occurring due to couplings between the Higgs and several additional supersymmetric particles. While this stabilises the Higgs field, it leads to not only a plethora of new particle types (squarks, gluinos and neutralinos to name a few), none of which have yet been observed, but also to at least five different types of Higgs boson in the Minimal SuperSymmetric Model (MSSM). Furthermore it requires the measurement and tuning of 105 constants in addition to those already found in the Standard Model. A new higher-energy particle beam should give some indication of whether SUSY exists in the real world, providing coverage of at least part of the SUSY parameter space.

There are many other models and potentially interesting physics phenomena that can be studied using energy scales at the TeV level and beyond. These include precision measurements of Charge-Parity (CP) violation, related to the asymmetry between the amount of matter and anti-matter in the universe [27]. In any case the motivation for a high-energy collider is clear.

### 1.2 The Large Hadron Collider (LHC)

The LHC [28] is the planned proton-proton collider based at CERN, operating at a centre-of-mass energy of 14TeV, collision rate of 40MHz and a nominal luminosity of  $10^{34}$ cm<sup>-2</sup>s<sup>-1</sup>. As a proton collider, it is a 'statistics engine', designed to produce large numbers of Deep Inelastic Scattering (DIS) collisions during every bunch crossing

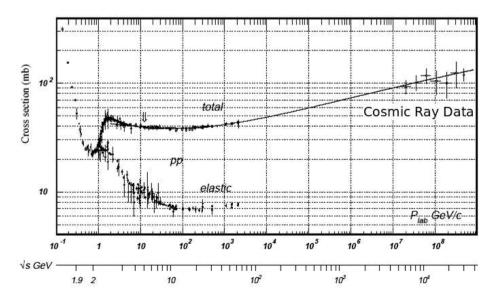

(BX). This is expected to permit the discovery of new physics up to an energy of 1TeV, physics above this energy being more difficult to study due to limited statistics (although sometimes the signatures can be unmissable [29]). The event rate at the LHC depends on the large cross-section for pp inelastic scattering as shown in figure 1.3.

**Figure 1.3:** Total pp collision cross-sections for varying collision energies [2]. The highest-energy points in this plot are from cosmic ray data.

At an energy scale of 14TeV the total cross-section is estimated from cosmic ray data to be 100mb, of which 30mb is expected to be elastic and therefore not as relevant to the experiments. The rate at which an event occurs is defined as the product of the cross-section and the luminosity of the accelerator:

$$N = L\sigma \tag{1.1}$$

where N is the event rate per second, L is the luminosity in cm<sup>-2</sup>s<sup>-1</sup> and  $\sigma$  is the event cross-section in cm<sup>2</sup>. Therefore a 70mb (70 \* 10<sup>-27</sup>cm<sup>2</sup>) inelastic scattering cross-section at a luminosity of  $10^{34}$ cm<sup>-2</sup>s<sup>-1</sup> results in an event rate of  $7x10^8$ s<sup>-1</sup>. As the bunch crossing rate is 40MHz and bearing in mind that during normal operation at the LHC not all bunches are filled (only 2808/3564), the number of events per bunch crossing can be calculated as:

$$Rate = 7 * 10^8 * 25 * 10^{-9} * 2808/3564 \approx 22$$

(1.2)

As the energy scale and raw data rate aimed for at the LHC are much higher than in previous experiments, there are a number of resulting detector implementation issues which can be summarised as follows:

- Intensity The intended design luminosity is  $10^{34}$ cm<sup>-2</sup>s<sup>-1</sup>. This leads to problems both in terms of radiation damage and pileup effects, in which the energy deposited by particles generated by the previous proton bunch crossing, and also the particles themselves, are still present in the detector. This problem is exacerbated by the fact that there are an average of 22 proton-proton collisions per bunch crossing.

- Crossing Rate In order to achieve the desired instantaneous luminosity the bunch crossings occur once every 25ns, which places strict requirements on the speed of the readout electronics and the charge collection time of the detectors.

- Radiation Damage Detectors in the LHC suffer a variety of types of damage from high energy protons, neutrons and pions and also ionisation effects from photons and charged particles. The dose is highest in the forward regions and the inner detector; for example it can reach 30MRad and 10<sup>15</sup>n<sub>eq</sub>/cm<sup>2\*</sup> in the CMS pixel detector [30].

The issues described above are also inter-related (for example a change in bunch crossing rate is directly related to a change in the luminosity). In any case these criteria require the design of detectors and readout electronics that are capable of operating for ten years in this harsh environment, which must withstand both long-term damage and Single Event Upsets (SEUs) [31], where a charged particle passing through the readout electronics changes the state of a single bit in a digital logic circuit or memory (typically triple-redundant logic circuits with a majority sum rule [32] are implemented to reduce the probability of this occurring). The detectors have to be everything at the same time - fast, radiation-hard and low-noise. This isn't

$<sup>{}^*</sup>n_{eq}/{\rm cm}^2$  is the neutron equivalent particle flux that pass through every square centimetre of the material. 100Rad=1Gy.

currently possible so trade-offs are made in the design of each detector to improve the quality of a particular measurement.

The two smaller detectors at the LHC are focused on particular physics areas: CP-violation in the B sector (LHCb) [33] and heavy ion physics (ALICE) [34]. The other two larger detectors (CMS [35] and ATLAS [36]) are designed with general-purpose studies in mind and the search for the Higgs boson in particular.

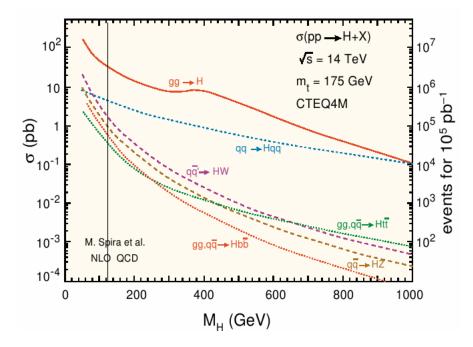

Figure 1.4: Higgs production channels at the LHC.

There are four major production channels for the Higgs at LHC (see figure 1.4), each of which is preferred at different energy scales and for different reasons: gg fusion,  $t\bar{t}$  fusion, W/Z fusion and W/Z bremsstrahlung. The reason that these reactions dominate is due to the Yukawa and Higgs couplings in the Standard Model - the strength of the coupling of the Higgs to a particle determines its mass, which also means that heavier particles have greater cross-sections for Higgs production. Although gg fusion is by far the dominant production channel, it suffers background from quark annihilation and gluon box diagrams; therefore it is most useful when combined with a distinct decay channel. A key decay channel for CMS at lower Higgs masses is  $H \rightarrow \gamma \gamma$ , which requires excellent calorimetry in order to identify the signal over the background (see figure 1.5). It is worth noting also that while these

are the dominant production channels for the Higgs, the production cross-sections are all at least nine orders of magnitude smaller than the total proton cross-section. Therefore only one in a billion events produced at the LHC are likely to be Higgs events.

**Figure 1.5:** Signal for  $m_H=130 \text{GeV H} \rightarrow \gamma \gamma$  after  $100 \text{fb}^{-1}$  of data recorded. The Higgs signal is shown in red, background in yellow. Adapted from [3].

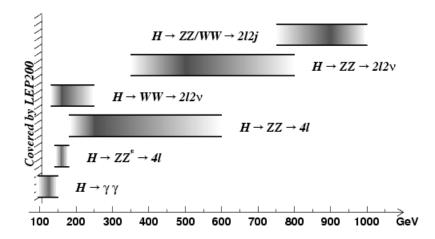

$H \rightarrow \tau \tau$  can also be used when searching for smaller Higgs masses. For greater  $m_H$ ,  $H \rightarrow ZZ \rightarrow l^+ l^- l^+ l^-$  can also be used, as well as  $H \rightarrow WW/ZZ \rightarrow jjl^+ l^-$ . If the alternative production channel W/Z fusion is considered, it provides the additional benefit of a di-jet signature with a rapidity gap between them (due to the lack of colour transfer between the two quarks emitting the W bosons); this acts as a useful filter for the event. A summary of typical decay modes under study versus the Higgs mass is shown in figure 1.6.

From these various signatures it is clear that in order to stand the best chance of finding the Higgs (and also studying other interesting channels involving heavy particles), we need very efficient tagging of particles such as b and t quarks as well as  $\mu$  and  $\tau$  leptons. We also require excellent calorimetry to detect electrons and photons.

**Figure 1.6:** Higgs discovery channels at CMS. Depending on the Higgs mass, various decays become favourable due to a combination of production rates for the intermediate particles and the background rates.

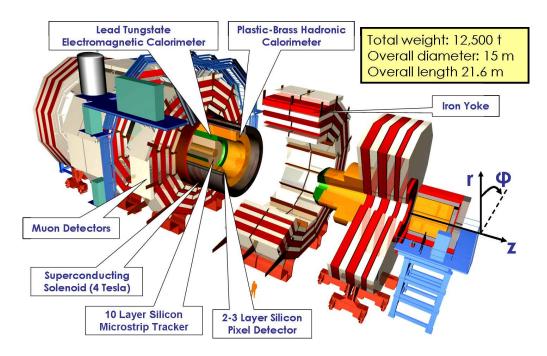

## 1.3 The Compact Muon Solenoid

CMS [37] is the smaller of the two general-purpose detectors being built at CERN. It comprises (from the beam pipe outward) a pixel detector, silicon microstrip tracker, lead tungstate crystal electromagnetic calorimeter, plastic-brass/quartz-iron hadronic calorimeter and muon detectors. Its main feature is the 4 Tesla solenoidal magnet [38], the largest superconducting solenoid ever constructed. This massive field is required both to produce the lever-arm necessary to calculate charged particle transverse momenta to high precision<sup>†</sup> [24] and also helps to trap low-momentum particles close to the beam pipe, reducing the occupancy in the outer detector.

As stated previously, one of the prominent decay channels for the Higgs is the di-photon channel  $H\to\gamma\gamma$ . Although the branching fraction for this reaction is extremely small relative to those from other events, the decay is very distinctive (two photons with an invariant mass close to that of the Higgs boson). CMS aims to detect these events using a high-resolution (both spatially and energetically) Electromagnetic CALorimeter (ECAL). Other significant decay channels, such as  $H\to ZZ\to l^+l^-l^+l^-$  and  $H\to WW/ZZ\to \overline{\nu}\nu l^+l^-$  rely on the tracking detectors. Muons

<sup>&</sup>lt;sup>†</sup>This measurement is made in a different way in ATLAS, using air-core toroidal magnets for muon spectrometry and a weaker magnetic field with no iron for flux return. Many of the other differences between the ATLAS and CMS detectors evolved from this choice.

Figure 1.7: Diagram of the CMS detector.

produced by these decays are relatively easy to identify because they travel practically unhindered through the detector.

#### 1.3.1 The Silicon Tracker

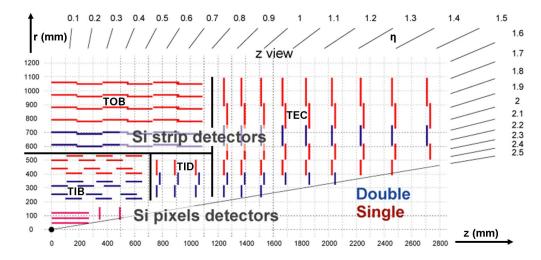

The CMS tracker [39, 40] (see figure 1.8) is an all-silicon detector comprising ten layers of microstrip sensors and three layers of pixellated sensor in the barrel. It is 5.4m long and has a diameter of 2.4m, and is subdivided into five main parts: The Tracker Outer Barrel (TOB), Tracker Inner Barrel (TIB), Tracker Inner Disks (TID), Tracker End Caps (TEC) and the pixels. The pixel detector has to cope with some of the highest fluences in CMS where the dose is  $3.2 \times 10^{15} n_{eq} \text{cm}^{-2}$  at 4cm radius from the beam pipe over the lifetime of the experiment. It must be situated as close to the interaction region as possible in order to tag relatively long-lived particles such as bottom and charmed hadrons and the  $\tau$ , and to identify light quark and gluon jets. The microstrip tracker provides the necessary lever arm for accurate momentum measurements and improves the precision of vertex measurements [41]. The entire detector is operated at low temperature (minus ten degrees Centigrade) to minimise the effects of radiation damage.

**Figure 1.8:** Layout of a quarter of the CMS tracking detector. This image is mirrored along both axes to make the full detector layout. The interaction point is marked at z=0.

The pixel detector is a hybrid design combining a silicon sensor with pixel pitch  $120\mathrm{x}150\mu\mathrm{m}^2$  (r $\phi$ xz) and a series of bump-bonded ReadOut Chips (ROCs) [42]. The sensors and readout Application-Specific Integrated Circuits (ASICs) of the design were kept separate in order to provide a large depletion region and fast charge collection that will have a usable signal after very heavy irradiation, which in turn requires a large external bias voltage to be applied (up to 600 volts). The sensing element contains a set of n-on-n diodes and a contact pad for each bump bond. The readout chip contains electronics for a high-speed token-ring readout system, analogue readout of the pixels and digitisation of the analogue values at the periphery of the ROC. In order to optimise the resolution of the pixel detector in both the  $r\phi$  and z directions, each module in the pixel end disks is rotated to take advantage of electron Lorentz drift in the sensor layer due to the 4T magnetic field. Analogue interpolation between the strips is also used to maximise resolution. The resolution of the pixel detector is anticipated to be approximately  $10\mu\mathrm{m}$  in  $r\phi$  and  $15\text{-}20\mu\mathrm{m}$  in z [43].

Unlike the binary tracker used in ATLAS, the CMS microstrip tracker is an almost exclusively analogue design with approximately 10 million detector channels. It uses  $p^+$ -in-n microstrip sensors of pitches from  $80\mu m$  upwards and either 512 or 768 strips per sensor, layered in an overlapping fashion to provide detector hermeticity. Some sensors are also placed back-to-back rotated relative to each other by approximately

100mrad, providing two-dimensional hit detection in the outer tracker. Signals from each set of 128 microstrips are sampled into an analogue pipeline using an APV (Analogue Pipeline Voltage) [44, 45, 46] readout chip that is capacitively-coupled to the sensor. Each APV25 ASIC has been manufactured using a  $0.25\mu m$  CMOS process [47], using enclosed gate technology in order to mitigate the effects of long term radiation damage in the detector environment. Each of the 128 readout channels in the APV25 has its own front-end preamplifier circuit followed by a CR-RC filter which shapes the charge pulse from the sensor to have a characteristic time constant of 50ns. The signal voltage is sampled at 25ns intervals into a 192-cell-deep analogue buffer of switched capacitors. The system has a response of 100mV/MIP (Minimum Ionising Particle<sup>‡</sup>) and a non-linearity of less than 2% over a 5 MIP range. The total power consumption is approximately 2.3mW/channel. The chip has two fundamental modes of operation. In peak mode (used at low luminosity), only the peak of the pulse shape is sampled into the APV25 pipeline and sent off-detector when a L1A (Level-1 Accept) is received from the trigger system. At higher luminosity, where pileup in a single channel is more likely, deconvolution mode is used [48, 49, 50, 51]; this involves sampling the pulse shape before the charge peak, at the peak and after, and using an Analogue Pulse Shape Processor (APSP) circuit to reconstruct the original charge peak at each bunch crossing. This does however contribute to a small increase in overall noise; more specifically, when operating in peak mode the series noise is reduced relative to deconvolution mode because only a single sample is used to create the resultant signal, however the signal is more prone to noise from pileup. Conversely in deconvolution mode the pileup noise is reduced by the use of three samples but the series noise is increased. After this the analogue signals are converted into the optical domain and time-division multiplexed in order to reduce the cabling requirements.

An example of a single APV25 readout frame is shown in figure 1.3.1. These data are carried out of the detector by approximately 45,000 optical fibres. In the case of the microstrip tracker, zero-suppression is not performed until data reaches the

<sup>&</sup>lt;sup>‡</sup>A MIP is defined as a particle possessing a kinetic energy that deposits the minimum amount of energy possible in the sensitive region of a detector, and therefore defines the signal-to-noise ratio requirement for the sensor.

**Figure 1.9:** A single APV data frame with the passage of time indicated by the horizontal axis. A frame begins with a digital header including pipeline address information, followed by analogue voltage levels for each of the 128 APV channels in that bunch crossing. The end of the frame is indicated by another digital strobe. Taken from [4].

front-end electronics of the tracker Front End Driver (FED). This is the major disadvantage of using an analogue system. It does however provide several benefits:

- Reduced power consumption Digitisation consumes power, and fast digitisation even more. This leads to requirements for greater power densities in the tracker and would also have resulted in the dissipation of additional heat.

- Greater effective information Interpolation of the charge distribution across several microstrips can improve the resolution beyond the pitch of the sensors themselves.

- Immunity to noise If pedestal subtraction is performed after readout, noise immunity can be improved upon. For example, one can isolate common mode noise and interference from external sources such as fluctuations in the detector ground level. Furthermore the use of an analogue system avoids the use of discriminator thresholds in the detector electronics, which can potentially cause a high 'fake hit' rate and would require constant monitoring and calibration.

- **Performance Monitoring** As the analogue pulse shape is monitored offdetector, any degradation of sensor or electronic performance can be monitored throughout the operation of the experiment.

As the signals from the tracker are not digitised until they reach the FED, data from the tracker is unavailable for a  $7\mu$ s readout period. Therefore it is unable to contribute to the first stage of triggering in CMS. This may be of critical importance for Super-LHC (SLHC), as discussed in chapter 4.

#### 1.3.2 The Electromagnetic Calorimeter

The ECAL [3] is a very compact homogeneous scintillating crystal calorimeter designed for precision measurements of electron and photon energies (0.5%@50GeV). For high-energy particles, electromagnetic calorimeters rely on the use of materials that promote two processes: electron (and positron) Bremsstrahlung emission of photons, and the conversion of photons into electron-positron pairs (called 'pair-production'). These processes are characterised by the radiation length,  $X_0$ , which is the distance over which and electron (or positron) loses, on average  $1 - \frac{1}{e}$  of its energy. The probability of a pair conversion over a single radiation length is  $e^{-\frac{7}{9}}$ . As one of these two processes naturally gives rise to the other, a cascade of particles is produced, ultimately resulting in a multitude of low-energy photons that can be detected and used to measure the energy of the initial particle. In order to achieve the required performance in the limited space available in CMS, lead tungstate was chosen as the active material for its short radiation length (approximately 0.9 cm) and high radiation tolerance. Each crystal has a front face 2.2x2.3cm<sup>2</sup> in the barrel section (approximately 0.0175 square in  $\Delta \eta x \Delta \phi$ ).

As the active material has a relatively low light yield, the signal from the light collected must be amplified. This is achieved using Avalanche PhotoDiodes (APDs) in the barrel (two per crystal) and Vacuum PhotoTriodes (VPTs) in the end caps where the radiation dose is greater. The signals from the ECAL are digitised on the detector, then stored for readout upon the reception of a readout trigger. In addition to this trigger primitives are generated on-detector using 5x5 crystal 'trigger towers' and forwarded to the calorimeter trigger off-detector (see chapter 3).

#### 1.3.3 The Hadronic Calorimeter (HCAL)

Surrounding the ECAL is the HCAL [52] that is responsible for energy measurements of hadrons and their products (i.e. jets) with an energy resolution (when combined with the ECAL) of  $\sigma_E/E = 120\%/\sqrt{E} \oplus 6.9\%$  [43], where E is measured in GeV. Hadronic calorimeters rely on nuclear interactions which result in both hadronic and electromagnetic showers. Interactions are defined in terms of the nuclear interaction length  $\lambda$ , which is greater for more dense materials. As the probability of a nuclear interaction is small but the energy deposited in the calorimeter is large, there are significant fluctuations in the measured energy in hadronic calorimeter showers, lowering the overall energy resolution of the detector.

Pions play a key role in shower development in a hadronic calorimeter, as they are the lowest-energy products of nuclear interactions. Neutral pions from the proton collisions convert close to the interaction point in CMS to produce two photons which are subsequently absorbed by the electromagnetic calorimeter. Therefore the photons from these particles do not reach the hadronic calorimeter. However the nuclear interactions in the HCAL itself produce neutral and charged pions. The charged pions can further interact with the detector to produce more neutral pions, which then decay to produce photons that are detected in the HCAL. This leads to multiple large depositions of energy throughout the HCAL, which are then combined to reconstruct the energy of the incoming particle(s).

The measurement of the energy by the detection of photons is achieved in the barrel and endcap regions using a sampling calorimeter, with brass absorbers and plastic scintillators, coupled to wavelength-shifting fibres and Hybrid PhotoDiode (HPD) sensors. In the very forward end cap region (HF), quartz fibres emitting Cerenkov light are used instead of plastic and embedded into iron due to their greater radiation tolerance. They are coupled to phototubes, which are faster than the HPDs used in the central region of the detector. Total HCAL detector coverage reaches  $|\eta| = 5$ .

#### 1.3.4 The Muon Detectors

CMS contains three different types of muon detector [53, 54]. The barrel contains Drift Tube (DT) chambers for precision track measurement, whilst the end caps use Cathode Strip Chambers (CSCs). In addition, Resistive Plate Chambers (RPCs) are used in both parts of the system for triggering detectors; the reason being that while they have poorer spatial resolution than the CSCs and DTs, they are capable of resolving individual bunch crossings in time and are therefore needed for Level-1 triggering.

The spatial resolution of the muon detectors is between 50 and  $200\mu\text{m}$ , while the standalone momentum resolution is at most 15% for a particle with 10GeV p<sub>T</sub>, and 40% at 1TeV.

#### 1.3.5 The CMS Trigger System

As the LHC is designed to operate at a very high event rate, there is neither the space nor detector readout bandwidth available to store all of the data produced. The readout rate is particularly limited by data storage space. Each event in CMS produces approximately 1MB of processed data and the total data volume produced by the CMS detector is several TB per second. The peak storage rate for CMS is approximately 1TB per day (100Hz), and therefore the data volume must be reduced by a factor of 400,000 before writing to disk. This necessitates the use of a 'trigger' system to pre-process a coarse-grained subset of the data.

It is a common misconception that a trigger identifies 'interesting' events in the background and select them for further processing. This would by definition imply that one already knew what to look for; in fact the purpose of a trigger is to discard data that are understood with our current physical understanding and retain data relating to events that cannot be immediately identified. Of course at the same time one must ensure that the trigger has the capability to distinguish signatures of possible new physics and store them for further study, such as the anticipated Higgs boson. Essentially in CMS this reduces to a 'cut' on the transverse energy,

missing transverse energy and types of particle detected. In doing this one is placing as few constraints as possible on the physics available to the end-user (ignoring low energy physics for which the LHC was clearly not designed). This is often described as 'inclusive triggering' and is particularly important for the first trigger stage. In addition to the requirement of efficient event selection, the trigger must also operate with minimal deadtime (a period after a trigger during which data cannot be taken), allowing one to maintain a high efficiency for the recording of useful events. This is achieved using buffers in the detector readout combined with a fast, efficient trigger processor.

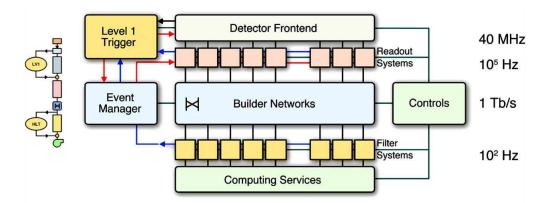

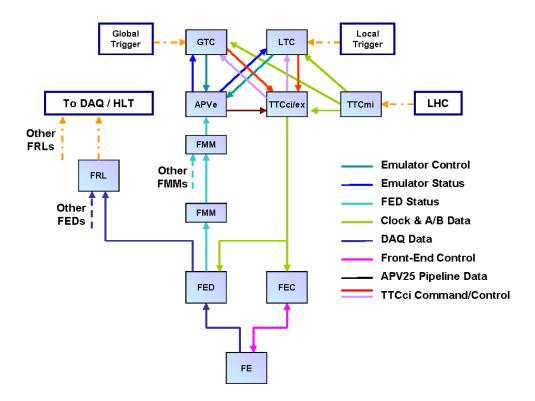

**Figure 1.10:** Diagram of the CMS trigger/Data AcQuisition (DAQ) system. Data from the detector are first sent to the Level-1 trigger for processing and then selected events have the frontend detector data sent to the Higher Level Trigger for further processing. Status reports from the different subsystems allow debugging and throttling of the trigger systems to allow a sustainable trigger rate to be attained.

As shown in figure 1.10, the CMS trigger comprises two stages of event selection [8, 55, 10]. The Level-1 (L1) trigger [56] is primarily a Field-Programmable Gate Array (FPGA) and ASIC-based processing system in order to handle the enormous data volume from the detector and provide a trigger decision in a very short (and guaranteed) time period of 128 BX or  $3.2\mu s^{\S}$ . The goal of the system is to reduce the data volume by an average factor of 400 (i.e. to 100kHz).

The Higher Level Trigger (HLT) reduces the rate by a further factor of 1,000 and is dominated by the use of PCs using a multi-stage iterative approach to reconstruction

<sup>§</sup>There is in fact some margin in this requirement; the limiting factor in the trigger latency is the size of the tracker APV25 pipeline, which was originally 128 BX but increased to an effective latency of 160 BX in the final revision of the ASIC.

with a limiting cut-off in allowed processing time. At this level basic tracker information is used, and initial selection based on possible underlying physics events is made. The data produced at this level of filtering is then recorded to disk at approximately 100Hz.