# **IBM @**server **p5 590** and **595 Technical Overview and Introduction**

# Redpaper

ibm.com/redbooks

International Technical Support Organization

# IBM @server p5 590 and 595 Technical Overview and Introduction

August 2005

**Note:** Before using this information and the product it supports, read the information in "Notices" on page vii.

#### First Edition (August 2005)

This edition applies to the IBM @server p5 590 and 595, and AIX 5L Version 5.3, product number 5765-G03.

#### © Copyright International Business Machines Corporation 2005. All rights reserved.

Note to U.S. Government Users Restricted Rights -- Use, duplication or disclosure restricted by GSA ADP Schedule Contract with IBM Corp.

## Contents

| Notices<br>Trademarks                                                    |     |

|--------------------------------------------------------------------------|-----|

| Preface                                                                  |     |

| Become a published author                                                |     |

|                                                                          | X   |

| Chapter 1. General description                                           |     |

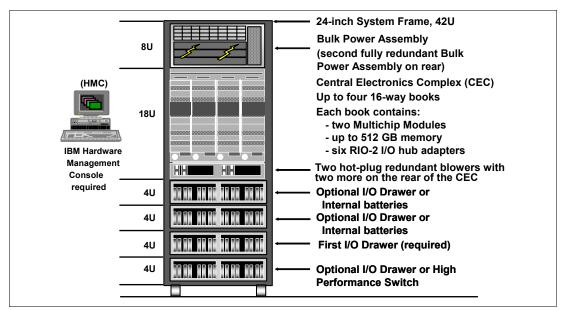

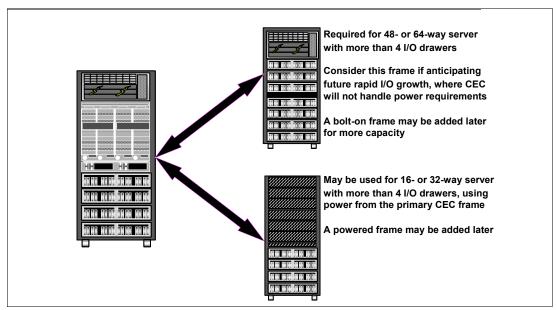

| 1.1 Model abstract for 9119-590 and 9119-595           1.2 System frames |     |

| 1.3 Installation planning                                                |     |

| 1.3.1 System specifications                                              |     |

| 1.3.2 Physical package                                                   |     |

| 1.3.3 Service clearances                                                 |     |

| 1.4 Power and cooling.                                                   |     |

| 1.5 Minimum and optional features                                        |     |

| 1.5.1 Processor features                                                 |     |

| 1.5.2 Memory features                                                    | . 9 |

| 1.5.3 USB diskette drive                                                 | . 9 |

| 1.5.4 Hardware Management Console models                                 | 10  |

| 1.6 External disk subsystem                                              | 10  |

| 1.6.1 IBM 2104 Expandable Storage Plus                                   |     |

| 1.6.2 IBM TotalStorage® Storage servers                                  |     |

| 1.6.3 IBM TotalStorage DS6000 and DS8000 series.                         |     |

| 1.7 Operating system support                                             |     |

| 1.7.1 AIX 5L                                                             |     |

| 1.7.2 Linux                                                              |     |

| 1.7.3 i5/OS V5R3                                                         | 13  |

| Chapter 2. Architecture and technical overview                           | 15  |

| 2.1 System design.                                                       |     |

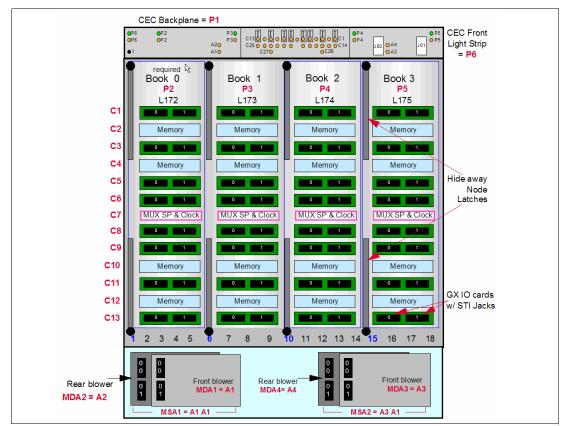

| 2.1.1 Central Electronics Complex                                        |     |

| 2.1.2 CEC backplane                                                      |     |

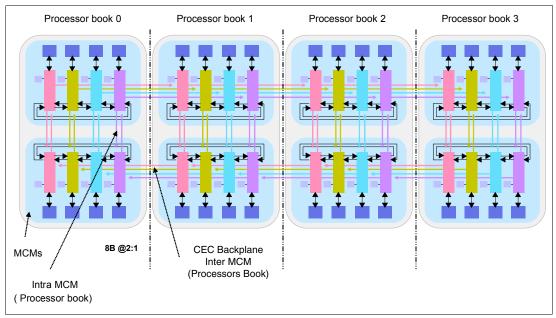

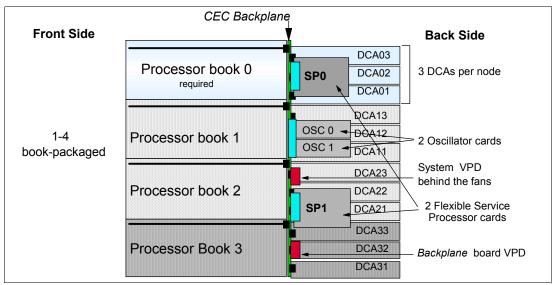

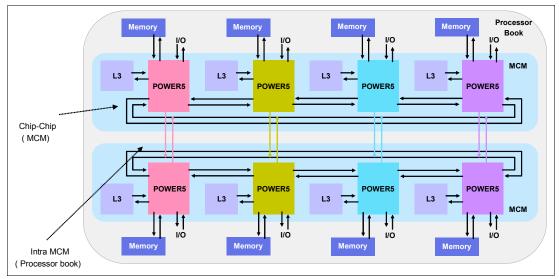

| 2.1.3 Processor books                                                    |     |

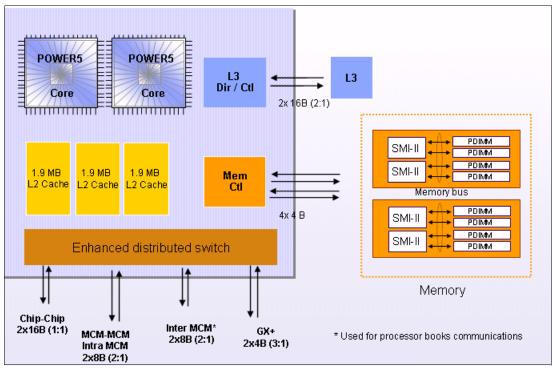

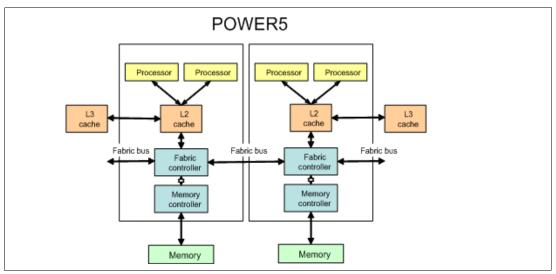

| 2.1.4 The POWER5 chip                                                    | 18  |

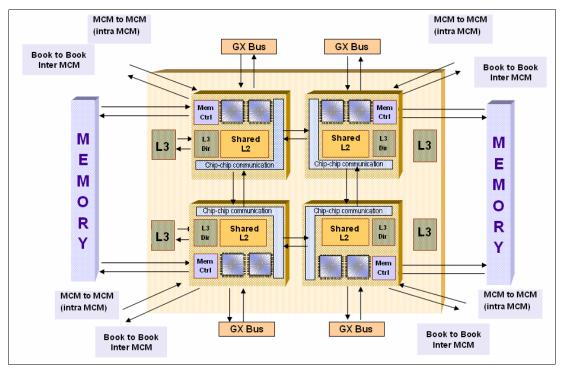

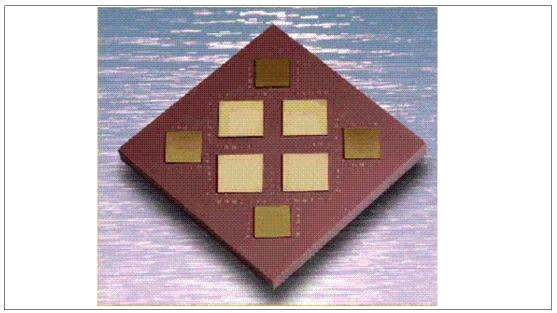

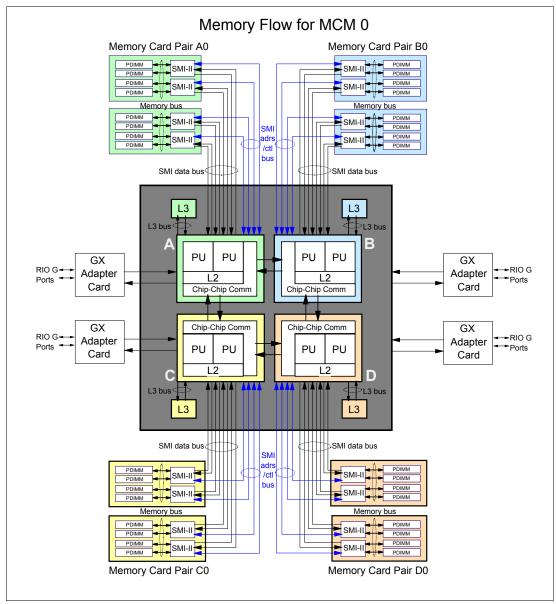

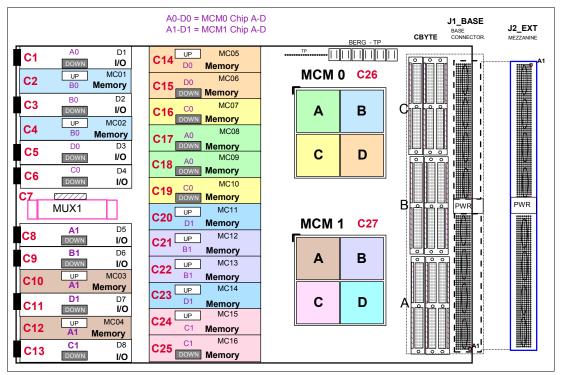

| 2.1.5 Multichip module and system interconnect                           | 21  |

| 2.1.6 Simultaneous multithreading                                        | 23  |

| 2.1.7 Dynamic power management                                           | 24  |

| 2.1.8 Available processor speeds                                         |     |

| 2.2 System flash memory configuration                                    |     |

| 2.2.1 Vital product data and system smart chips                          |     |

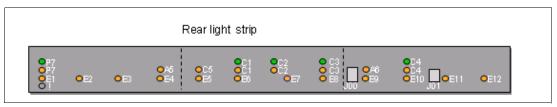

| 2.3 Light strip                                                          |     |

| 2.4 Memory subsystem                                                     |     |

| 2.4.1 Memory cards                                                       |     |

| 2.4.2 Memory configuration and placement.                                |     |

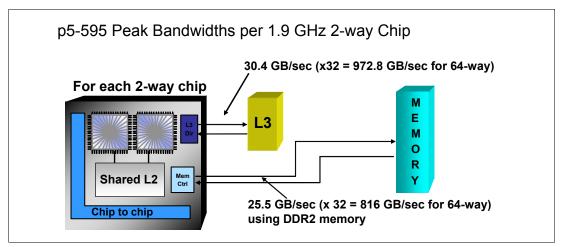

| 2.4.3 Memory throughput.                                                 |     |

| 2.5 System buses                                                         |     |

| 2.5.1 GX+ and RIO-2 buses                                                | 32  |

| 2.6 Internal I/O subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

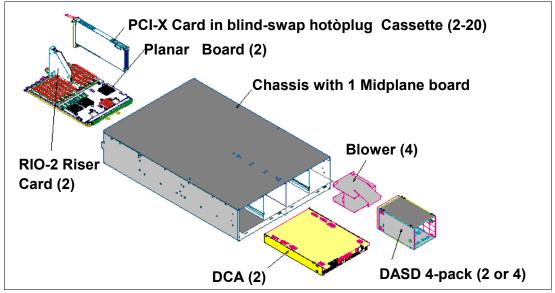

| 2.6.1 I/O drawer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33                                                                                                       |

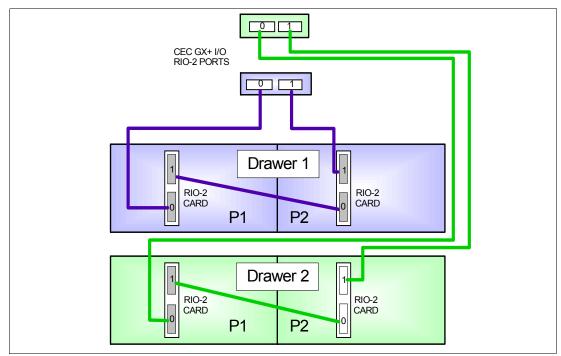

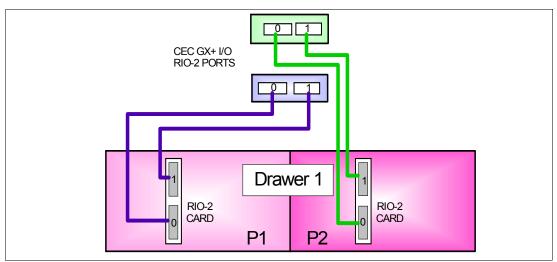

| 2.6.2 I/O drawer attachment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 35                                                                                                       |

| 2.6.3 Single loop (full-drawer cabling)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35                                                                                                       |

| 2.6.4 Dual looped (Half-drawer cabling)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36                                                                                                       |

| 2.6.5 Disks and boot devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                          |

| 2.6.6 Media options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                          |

| 2.6.7 PCI-X slots and adapters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                          |

| 2.6.8 LAN adapters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                          |

| 2.6.9 SCSI adapters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                          |

| 2.6.10 Internal storage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |

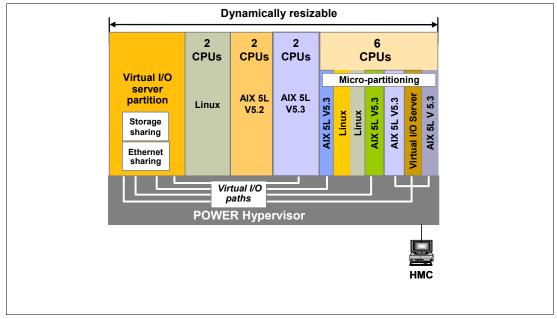

| 2.7 Logical partitioning and virtualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                          |

| 2.7.1 Dynamic logical partitioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                          |

| 2.7.2 Virtualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                          |

| 2.7.3 Advanced POWER Virtualization feature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                          |

| 2.7.4 Hardware and software guidelines for dynamic LPAR and virtualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                          |

| 2.7.5 LPAR validation tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                          |

| 2.7.6 Client-specific placement and eConfig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                          |

| 2.8 System management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                          |

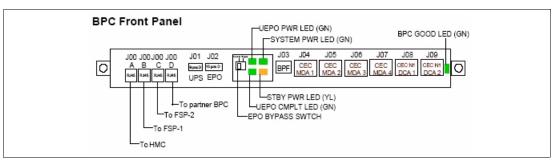

| 2.8.1 Power on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                          |

| 2.8.2 Service processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51                                                                                                       |

| 2.8.3 HMC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55                                                                                                       |

| 2.8.4 HMC connectivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 56                                                                                                       |

| 2.8.5 HMC code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 58                                                                                                       |

| 2.8.6 Hardware management user interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 58                                                                                                       |

| 2.8.7 Determining HMC serial number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                          |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                          |

| 2.8.8 Firmware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                          |

| 2.8.8 Firmware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 60                                                                                                       |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 60<br>67                                                                                                 |

| 2.8.8 Firmware       Chapter 3. Capacity on Demand         3.1 Types of Capacity on Demand                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 60<br>67<br>68                                                                                           |

| 2.8.8 Firmware       Chapter 3. Capacity on Demand         3.1 Types of Capacity on Demand                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 60<br>67<br>68<br>69                                                                                     |

| 2.8.8 Firmware         Chapter 3. Capacity on Demand         3.1 Types of Capacity on Demand         3.1.1 Capacity Upgrade on Demand (CUoD) for processors         3.1.2 Capacity Upgrade on Demand for memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60<br>67<br>68<br>69<br>70                                                                               |

| 2.8.8 Firmware         Chapter 3. Capacity on Demand         3.1 Types of Capacity on Demand         3.1.1 Capacity Upgrade on Demand (CUoD) for processors         3.1.2 Capacity Upgrade on Demand for memory         3.1.3 On/Off Capacity on Demand (On/Off CoD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 60<br>67<br>68<br>69<br>70<br>70                                                                         |

| 2.8.8 Firmware         Chapter 3. Capacity on Demand         3.1 Types of Capacity on Demand         3.1.1 Capacity Upgrade on Demand (CUoD) for processors         3.1.2 Capacity Upgrade on Demand for memory.         3.1.3 On/Off Capacity on Demand (On/Off CoD)         3.1.4 Reserve Capacity on Demand (Reserve CoD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60<br>67<br>68<br>69<br>70<br>70<br>71                                                                   |

| 2.8.8 Firmware         Chapter 3. Capacity on Demand         3.1 Types of Capacity on Demand         3.1.1 Capacity Upgrade on Demand (CUoD) for processors         3.1.2 Capacity Upgrade on Demand for memory.         3.1.3 On/Off Capacity on Demand (On/Off CoD).         3.1.4 Reserve Capacity on Demand (Reserve CoD).         3.1.5 Trial Capacity on Demand.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 60<br>67<br>68<br>69<br>70<br>70<br>71<br>71                                                             |

| 2.8.8 Firmware         Chapter 3. Capacity on Demand         3.1 Types of Capacity on Demand         3.1.1 Capacity Upgrade on Demand (CUoD) for processors.         3.1.2 Capacity Upgrade on Demand for memory.         3.1.3 On/Off Capacity on Demand (On/Off CoD).         3.1.4 Reserve Capacity on Demand (Reserve CoD)         3.1.5 Trial Capacity on Demand.         3.1.6 Capacity on Demand feature codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 60<br>67<br>68<br>69<br>70<br>70<br>71<br>71<br>72                                                       |

| 2.8.8 Firmware         Chapter 3. Capacity on Demand         3.1 Types of Capacity on Demand         3.1.1 Capacity Upgrade on Demand (CUoD) for processors         3.1.2 Capacity Upgrade on Demand for memory.         3.1.3 On/Off Capacity on Demand (On/Off CoD).         3.1.4 Reserve Capacity on Demand (Reserve CoD).         3.1.5 Trial Capacity on Demand.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 60<br>67<br>68<br>69<br>70<br>70<br>71<br>71<br>72                                                       |

| 2.8.8 Firmware         Chapter 3. Capacity on Demand         3.1 Types of Capacity on Demand         3.1.1 Capacity Upgrade on Demand (CUoD) for processors         3.1.2 Capacity Upgrade on Demand for memory.         3.1.3 On/Off Capacity on Demand (On/Off CoD).         3.1.4 Reserve Capacity on Demand (Reserve CoD)         3.1.5 Trial Capacity on Demand.         3.1.6 Capacity on Demand feature codes         3.1.7 Capacity BackUp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 60<br>67<br>68<br>69<br>70<br>70<br>71<br>71<br>72<br>72                                                 |

| 2.8.8 Firmware         Chapter 3. Capacity on Demand         3.1 Types of Capacity on Demand         3.1.1 Capacity Upgrade on Demand (CUoD) for processors.         3.1.2 Capacity Upgrade on Demand for memory.         3.1.3 On/Off Capacity on Demand (On/Off CoD).         3.1.4 Reserve Capacity on Demand (Reserve CoD).         3.1.5 Trial Capacity on Demand.         3.1.6 Capacity on Demand feature codes         3.1.7 Capacity BackUp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 60<br>67<br>68<br>69<br>70<br>70<br>71<br>71<br>72<br>72<br>75                                           |

| 2.8.8 Firmware         Chapter 3. Capacity on Demand         3.1 Types of Capacity on Demand         3.1.1 Capacity Upgrade on Demand (CUoD) for processors         3.1.2 Capacity Upgrade on Demand for memory.         3.1.3 On/Off Capacity on Demand (On/Off CoD).         3.1.4 Reserve Capacity on Demand (Reserve CoD).         3.1.5 Trial Capacity on Demand.         3.1.6 Capacity on Demand feature codes         3.1.7 Capacity BackUp         Chapter 4. Reliability, availability, and serviceability.         4.1 Reliability, fault tolerance, and data integrity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 60<br>67<br>68<br>69<br>70<br>70<br>71<br>71<br>72<br>72<br>75<br>76                                     |

| <ul> <li>2.8.8 Firmware.</li> <li>Chapter 3. Capacity on Demand</li> <li>3.1 Types of Capacity on Demand .</li> <li>3.1.1 Capacity Upgrade on Demand (CUoD) for processors.</li> <li>3.1.2 Capacity Upgrade on Demand for memory.</li> <li>3.1.3 On/Off Capacity on Demand (On/Off CoD).</li> <li>3.1.4 Reserve Capacity on Demand (Reserve CoD).</li> <li>3.1.5 Trial Capacity on Demand.</li> <li>3.1.6 Capacity on Demand feature codes.</li> <li>3.1.7 Capacity BackUp</li> <li>Chapter 4. Reliability, availability, and serviceability.</li> <li>4.1 Reliability, fault tolerance, and data integrity.</li> <li>4.1.1 PCI extended error handling.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 60<br>67<br>68<br>69<br>70<br>71<br>71<br>71<br>72<br>72<br>75<br>76<br>77                               |

| <ul> <li>2.8.8 Firmware.</li> <li>Chapter 3. Capacity on Demand</li> <li>3.1 Types of Capacity on Demand .</li> <li>3.1.1 Capacity Upgrade on Demand (CUoD) for processors.</li> <li>3.1.2 Capacity Upgrade on Demand for memory.</li> <li>3.1.3 On/Off Capacity on Demand (On/Off CoD).</li> <li>3.1.4 Reserve Capacity on Demand (Reserve CoD)</li> <li>3.1.5 Trial Capacity on Demand.</li> <li>3.1.6 Capacity on Demand feature codes</li> <li>3.1.7 Capacity BackUp</li> <li>Chapter 4. Reliability, availability, and serviceability.</li> <li>4.1 Reliability, fault tolerance, and data integrity.</li> <li>4.1.1 PCI extended error handling.</li> <li>4.1.2 Memory error correction extensions</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                            | 60<br>67<br>68<br>69<br>70<br>71<br>71<br>71<br>72<br>72<br>72<br>75<br>76<br>77<br>77                   |

| <ul> <li>2.8.8 Firmware.</li> <li>Chapter 3. Capacity on Demand</li> <li>3.1 Types of Capacity on Demand</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 60<br>67<br>68<br>69<br>70<br>70<br>71<br>71<br>72<br>72<br>75<br>75<br>76<br>77<br>78                   |

| <ul> <li>2.8.8 Firmware</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 60<br>67<br>68<br>69<br>70<br>70<br>71<br>71<br>72<br>72<br>72<br>75<br>75<br>76<br>77<br>78<br>78<br>78 |

| <ul> <li>2.8.8 Firmware.</li> <li>Chapter 3. Capacity on Demand .</li> <li>3.1 Types of Capacity on Demand .</li> <li>3.1.1 Capacity Upgrade on Demand (CUoD) for processors.</li> <li>3.1.2 Capacity Upgrade on Demand for memory.</li> <li>3.1.3 On/Off Capacity on Demand (On/Off CoD).</li> <li>3.1.4 Reserve Capacity on Demand (Reserve CoD).</li> <li>3.1.5 Trial Capacity on Demand.</li> <li>3.1.6 Capacity on Demand feature codes.</li> <li>3.1.7 Capacity BackUp .</li> <li>Chapter 4. Reliability, availability, and serviceability.</li> <li>4.1 Reliability, fault tolerance, and data integrity.</li> <li>4.1.1 PCI extended error handling.</li> <li>4.1.2 Memory error correction extensions</li> <li>4.1.3 Redundancy for array self-healing .</li> <li>4.1.4 First Failure Data Capture.</li> <li>4.1.5 Dynamic CPU Deallocation.</li> </ul>                                                                                                                                                                                                                                                                                               |                                                                                                          |

| 2.8.8 Firmware         Chapter 3. Capacity on Demand         3.1 Types of Capacity on Demand         3.1.1 Capacity Upgrade on Demand (CUoD) for processors.         3.1.2 Capacity Upgrade on Demand for memory.         3.1.3 On/Off Capacity on Demand (On/Off CoD).         3.1.4 Reserve Capacity on Demand (Reserve CoD).         3.1.5 Trial Capacity on Demand.         3.1.6 Capacity on Demand feature codes         3.1.7 Capacity BackUp         Chapter 4. Reliability, availability, and serviceability.         4.1 Reliability, fault tolerance, and data integrity.         4.1.1 PCl extended error handling.         4.1.2 Memory error correction extensions         4.1.3 Redundancy for array self-healing         4.1.4 First Failure Data Capture.         4.1.5 Dynamic CPU Deallocation.         4.1.6 Service processor                                                                                                                                                                                                                                                                                                             |                                                                                                          |

| <ul> <li>2.8.8 Firmware.</li> <li>Chapter 3. Capacity on Demand</li> <li>3.1 Types of Capacity on Demand .</li> <li>3.1.1 Capacity Upgrade on Demand (CUoD) for processors.</li> <li>3.1.2 Capacity Upgrade on Demand for memory.</li> <li>3.1.3 On/Off Capacity on Demand (On/Off CoD).</li> <li>3.1.4 Reserve Capacity on Demand (Reserve CoD).</li> <li>3.1.5 Trial Capacity on Demand.</li> <li>3.1.6 Capacity on Demand feature codes</li> <li>3.1.7 Capacity BackUp</li> <li>Chapter 4. Reliability, availability, and serviceability.</li> <li>4.1 Reliability, fault tolerance, and data integrity.</li> <li>4.1.1 PCI extended error handling.</li> <li>4.1.2 Memory error correction extensions</li> <li>4.1.3 Redundancy for array self-healing</li> <li>4.1.4 First Failure Data Capture.</li> <li>4.1.5 Dynamic CPU Deallocation.</li> <li>4.1.7 Fault monitoring functions.</li> </ul>                                                                                                                                                                                                                                                           |                                                                                                          |

| <ul> <li>2.8.8 Firmware.</li> <li>Chapter 3. Capacity on Demand</li> <li>3.1 Types of Capacity Upgrade on Demand (CUoD) for processors.</li> <li>3.1.2 Capacity Upgrade on Demand for memory.</li> <li>3.1.3 On/Off Capacity on Demand (On/Off CoD).</li> <li>3.1.4 Reserve Capacity on Demand (Reserve CoD).</li> <li>3.1.5 Trial Capacity on Demand.</li> <li>3.1.6 Capacity on Demand feature codes</li> <li>3.1.7 Capacity BackUp</li> <li>Chapter 4. Reliability, availability, and serviceability.</li> <li>4.1 PCI extended error handling.</li> <li>4.1.2 Memory error correction extensions</li> <li>4.1.3 Redundancy for array self-healing</li> <li>4.1.4 First Failure Data Capture.</li> <li>4.1.5 Dynamic CPU Deallocation.</li> <li>4.1.8 Mutual surveillance.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                          |

| 2.8.8 Firmware         Chapter 3. Capacity on Demand         3.1 Types of Capacity on Demand         3.1.1 Capacity Upgrade on Demand (CUoD) for processors.         3.1.2 Capacity Upgrade on Demand for memory.         3.1.3 On/Off Capacity on Demand (On/Off CoD).         3.1.4 Reserve Capacity on Demand (Reserve CoD).         3.1.5 Trial Capacity on Demand.         3.1.6 Capacity on Demand feature codes         3.1.7 Capacity BackUp         Chapter 4. Reliability, availability, and serviceability.         4.1 Reliability, fault tolerance, and data integrity.         4.1.1 PCI extended error handling.         4.1.2 Memory error correction extensions         4.1.3 Redundancy for array self-healing         4.1.4 First Failure Data Capture.         4.1.5 Dynamic CPU Deallocation.         4.1.6 Service processor         4.1.7 Fault monitoring functions.         4.1.8 Mutual surveillance         4.1.9 Environmental monitoring functions                                                                                                                                                                                |                                                                                                          |

| 2.8.8 Firmware         Chapter 3. Capacity on Demand         3.1 Types of Capacity on Demand         3.1.1 Capacity Upgrade on Demand (CUoD) for processors.         3.1.2 Capacity Upgrade on Demand for memory.         3.1.3 On/Off Capacity on Demand (On/Off CoD).         3.1.4 Reserve Capacity on Demand (Reserve CoD).         3.1.5 Trial Capacity on Demand (Reserve CoD).         3.1.6 Capacity on Demand feature codes         3.1.7 Capacity BackUp         Chapter 4. Reliability, availability, and serviceability.         4.1 Reliability, fault tolerance, and data integrity.         4.1.1 PCI extended error handling.         4.1.2 Memory error correction extensions.         4.1.3 Redundancy for array self-healing         4.1.4 First Failure Data Capture.         4.1.5 Dynamic CPU Deallocation.         4.1.6 Service processor         4.1.7 Fault monitoring functions.         4.1.8 Mutual surveillance         4.1.9 Environmental monitoring functions         4.1.10 Error handling and reporting.                                                                                                                    |                                                                                                          |

| <ul> <li>2.8.8 Firmware.</li> <li>Chapter 3. Capacity on Demand</li> <li>3.1 Types of Capacity on Demand .</li> <li>3.1.1 Capacity Upgrade on Demand (CUoD) for processors.</li> <li>3.1.2 Capacity Upgrade on Demand for memory.</li> <li>3.1.3 On/Off Capacity on Demand (On/Off CoD).</li> <li>3.1.4 Reserve Capacity on Demand (Reserve CoD).</li> <li>3.1.5 Trial Capacity on Demand (Reserve CoD).</li> <li>3.1.6 Capacity on Demand feature codes .</li> <li>3.1.7 Capacity BackUp .</li> <li>Chapter 4. Reliability, availability, and serviceability.</li> <li>4.1 Reliability, fault tolerance, and data integrity.</li> <li>4.1.1 PCI extended error handling .</li> <li>4.1.2 Memory error correction extensions .</li> <li>4.1.3 Redundancy for array self-healing .</li> <li>4.1.4 First Failure Data Capture .</li> <li>4.1.5 Dynamic CPU Deallocation .</li> <li>4.1.6 Service processor .</li> <li>4.1.7 Fault monitoring functions .</li> <li>4.1.8 Mutual surveillance .</li> <li>4.1.9 Environmental monitoring functions .</li> <li>4.1.10 Error handling and reporting .</li> <li>4.1.11 Availability enhancement functions .</li> </ul> |                                                                                                          |

| 2.8.8 Firmware         Chapter 3. Capacity on Demand         3.1 Types of Capacity on Demand         3.1.1 Capacity Upgrade on Demand (CUoD) for processors.         3.1.2 Capacity Upgrade on Demand for memory.         3.1.3 On/Off Capacity on Demand (On/Off CoD).         3.1.4 Reserve Capacity on Demand (Reserve CoD).         3.1.5 Trial Capacity on Demand (Reserve CoD).         3.1.6 Capacity on Demand feature codes         3.1.7 Capacity BackUp         Chapter 4. Reliability, availability, and serviceability.         4.1 Reliability, fault tolerance, and data integrity.         4.1.1 PCI extended error handling.         4.1.2 Memory error correction extensions.         4.1.3 Redundancy for array self-healing         4.1.4 First Failure Data Capture.         4.1.5 Dynamic CPU Deallocation.         4.1.6 Service processor         4.1.7 Fault monitoring functions.         4.1.8 Mutual surveillance         4.1.9 Environmental monitoring functions         4.1.10 Error handling and reporting.                                                                                                                    |                                                                                                          |

| 4.2.2 Online customer support.       4.3         4.3 IBM @server Cluster 1600       4.3 |          |

|-----------------------------------------------------------------------------------------|----------|

| Appendix A. Servicing an IBM @server p5 system                                          |          |

| IBM eServer Hardware Information Center                                                 | 86       |

| Related publications                                                                    | 89       |

| IBM Redbooks                                                                            |          |

| Other publications                                                                      | 89       |

| Online resources                                                                        | 90       |

| How to get IBM Redbooks                                                                 | 91<br>92 |

| •                                                                                       |          |

## Notices

This information was developed for products and services offered in the U.S.A.

IBM may not offer the products, services, or features discussed in this document in other countries. Consult your local IBM representative for information on the products and services currently available in your area. Any reference to an IBM product, program, or service is not intended to state or imply that only that IBM product, program, or service may be used. Any functionally equivalent product, program, or service that does not infringe any IBM intellectual property right may be used instead. However, it is the user's responsibility to evaluate and verify the operation of any non-IBM product, program, or service.

IBM may have patents or pending patent applications covering subject matter described in this document. The furnishing of this document does not give you any license to these patents. You can send license inquiries, in writing, to:

IBM Director of Licensing, IBM Corporation, North Castle Drive Armonk, NY 10504-1785 U.S.A.

The following paragraph does not apply to the United Kingdom or any other country where such provisions are inconsistent with local law: INTERNATIONAL BUSINESS MACHINES CORPORATION PROVIDES THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some states do not allow disclaimer of express or implied warranties in certain transactions, therefore, this statement may not apply to you.

This information could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication. IBM may make improvements and/or changes in the product(s) and/or the program(s) described in this publication at any time without notice.

Any references in this information to non-IBM Web sites are provided for convenience only and do not in any manner serve as an endorsement of those Web sites. The materials at those Web sites are not part of the materials for this IBM product and use of those Web sites is at your own risk.

IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation to you.

Information concerning non-IBM products was obtained from the suppliers of those products, their published announcements or other publicly available sources. IBM has not tested those products and cannot confirm the accuracy of performance, compatibility or any other claims related to non-IBM products. Questions on the capabilities of non-IBM products should be addressed to the suppliers of those products.

This information contains examples of data and reports used in daily business operations. To illustrate them as completely as possible, the examples include the names of individuals, companies, brands, and products. All of these names are fictitious and any similarity to the names and addresses used by an actual business enterprise is entirely coincidental.

#### COPYRIGHT LICENSE:

This information contains sample application programs in source language, which illustrates programming techniques on various operating platforms. You may copy, modify, and distribute these sample programs in any form without payment to IBM, for the purposes of developing, using, marketing or distributing application programs conforming to the application programming interface for the operating platform for which the sample programs are written. These examples have not been thoroughly tested under all conditions. IBM, therefore, cannot guarantee or imply reliability, serviceability, or function of these programs. You may copy, modify, and distribute these sample programs in any form without payment to IBM for the purposes of developing, using, marketing, or distributing application programs conforming to IBM's application programming interfaces.

#### Trademarks

The following terms are trademarks of the International Business Machines Corporation in the United States, other countries, or both:

| AIX 5L™                               |

|---------------------------------------|

| AIX®                                  |

| Chipkill™                             |

| Electronic Service Agent <sup>™</sup> |

| Enterprise Storage Server®            |

| @server®                              |

| @server®                              |

| Hypervisor™                           |

| HACMP™                                |

| i5/OS™                                |

| IBM®                                  |

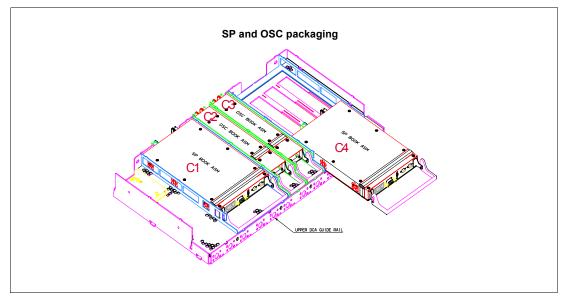

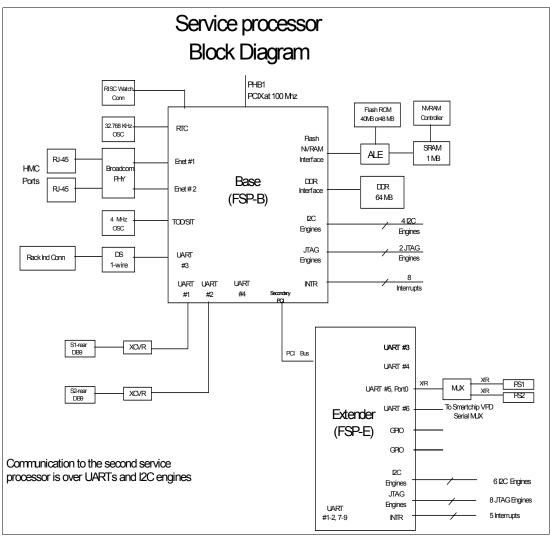

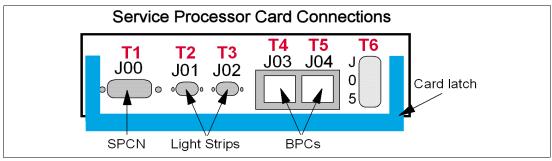

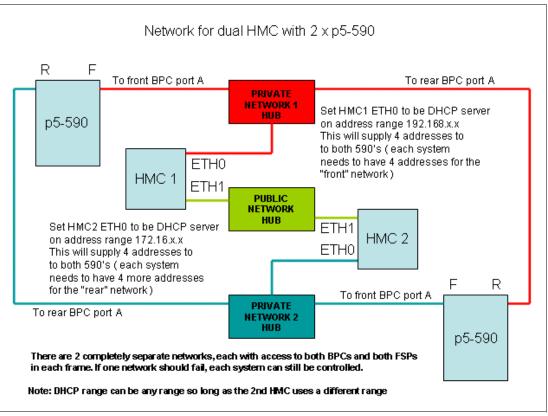

ibm.com® iSeries™ Micro-Partitioning™ Notes® OpenPower™ Perform™ PowerPC® POWER™ POWER4™ POWER4™ POWER4+™ POWER5™ pSeries® Redbooks™ Redbooks (logo)™ Resource Link™ RS/6000® TotalStorage® Virtualization Engine™ WebSphere® zSeries®