WO2010024240A1 - バイポーラ型炭化珪素半導体装置およびその製造方法 - Google Patents

バイポーラ型炭化珪素半導体装置およびその製造方法 Download PDFInfo

- Publication number

- WO2010024240A1 WO2010024240A1 PCT/JP2009/064770 JP2009064770W WO2010024240A1 WO 2010024240 A1 WO2010024240 A1 WO 2010024240A1 JP 2009064770 W JP2009064770 W JP 2009064770W WO 2010024240 A1 WO2010024240 A1 WO 2010024240A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- region

- base

- resistance layer

- emitter

- silicon carbide

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 91

- 229910010271 silicon carbide Inorganic materials 0.000 title claims abstract description 83

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 title claims abstract description 78

- 238000000034 method Methods 0.000 title claims description 52

- 238000004519 manufacturing process Methods 0.000 title claims description 26

- 230000006798 recombination Effects 0.000 claims abstract description 76

- 238000005215 recombination Methods 0.000 claims abstract description 76

- 230000001629 suppression Effects 0.000 claims abstract description 36

- 239000000758 substrate Substances 0.000 claims description 26

- 238000005530 etching Methods 0.000 claims description 24

- 239000013078 crystal Substances 0.000 claims description 16

- 230000003321 amplification Effects 0.000 abstract description 22

- 238000003199 nucleic acid amplification method Methods 0.000 abstract description 22

- 239000010410 layer Substances 0.000 description 104

- 230000008569 process Effects 0.000 description 34

- 239000012535 impurity Substances 0.000 description 20

- 238000005468 ion implantation Methods 0.000 description 18

- 230000015572 biosynthetic process Effects 0.000 description 13

- 230000002829 reductive effect Effects 0.000 description 8

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 7

- 238000010438 heat treatment Methods 0.000 description 7

- 230000001681 protective effect Effects 0.000 description 7

- 229910052814 silicon oxide Inorganic materials 0.000 description 7

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 6

- 150000002500 ions Chemical class 0.000 description 6

- 230000003647 oxidation Effects 0.000 description 6

- 238000007254 oxidation reaction Methods 0.000 description 6

- 229910052782 aluminium Inorganic materials 0.000 description 4

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 4

- 229910052757 nitrogen Inorganic materials 0.000 description 4

- 235000012431 wafers Nutrition 0.000 description 4

- MWUXSHHQAYIFBG-UHFFFAOYSA-N Nitric oxide Chemical compound O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 3

- 238000001994 activation Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 239000007789 gas Substances 0.000 description 3

- 238000002513 implantation Methods 0.000 description 3

- 239000000463 material Substances 0.000 description 3

- 238000000206 photolithography Methods 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- 230000000903 blocking effect Effects 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 230000006872 improvement Effects 0.000 description 2

- 230000006698 induction Effects 0.000 description 2

- 230000036961 partial effect Effects 0.000 description 2

- 238000005036 potential barrier Methods 0.000 description 2

- 230000003068 static effect Effects 0.000 description 2

- 239000010936 titanium Substances 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 239000012300 argon atmosphere Substances 0.000 description 1

- 239000012298 atmosphere Substances 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 125000004435 hydrogen atom Chemical class [H]* 0.000 description 1

- 230000002401 inhibitory effect Effects 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000002344 surface layer Substances 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/16—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only elements of Group IV of the Periodic Table

- H01L29/1608—Silicon carbide

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/1004—Base region of bipolar transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66053—Multistep manufacturing processes of devices having a semiconductor body comprising crystalline silicon carbide

- H01L29/66068—Multistep manufacturing processes of devices having a semiconductor body comprising crystalline silicon carbide the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/73—Bipolar junction transistors

- H01L29/732—Vertical transistors

Definitions

- the present invention relates to a bipolar silicon carbide semiconductor device and a method for manufacturing the same, and in particular, is a bipolar silicon carbide semiconductor device having a normal four-layer structure, in which a main current flowing between main electrodes and a control current flowing through a control electrode are

- the present invention relates to a bipolar silicon carbide semiconductor device suitable for suppressing recombination between the two and increasing the current amplification factor, and a method for manufacturing the same.

- SiC Silicon carbide

- junction SiC power devices include static induction transistors (Static Induction Transistor, “SIT”), junction field effect transistors (Junction Field Effect Transistor, “JFET”), or bipolar transistors (Bipolar Junction Transistor, “BJT”). and so on.

- SIT Static Induction Transistor

- JFET Junction Field Effect Transistor

- BJT Bipolar Junction Transistor

- BJT is stacked on the low resistance n + -type 4H-SiC (0001) plane 8 degree off substrate in the order of n ⁇ -type high resistance region, p-type base region, and n + -type emitter region from the bottom. It is formed.

- the emitter region is composed of a number of elongated regions. Electrodes for establishing electrical connection to the outside are formed in the emitter region, base region, and collector region.

- FIG. 13 shows a cross section of the BJT disclosed in Non-Patent Document 1.

- the BJT 500 surrounds the collector region 501, which is an n-type low resistance layer, the n-type high resistance region 502, the base region 503 of the p-type region, the emitter region 504 of n-type low resistance, and the emitter region.

- the base contact region 505 of the p-type low resistance region is formed.

- a collector electrode 506, a base electrode 507, and an emitter electrode 508 for electrical connection are joined to the outside of the collector region 501, the base region 503 (base contact region 505), and the emitter region. Further, the entire exposed surface other than the electrodes of the BJT 500 is covered with a surface protective film 509.

- Patent Document 1 As an example of a conventional BJT with improved device characteristics (current amplification factor), there is one having a structure described in Patent Document 1.

- the BJT disclosed in Patent Document 1 has a first n-type high resistance layer, a p-type base region, and a second n-type layer on the n + -type 4H—SiC (0001) surface substrate serving as a collector region from below.

- a type high resistance layer and an n + type emitter region are stacked in this order.

- the emitter region is separated and formed by etching in a predetermined planar pattern shape from the upper surface to the middle of the n + -type emitter region and the second n-type high resistance layer in the stacked structure. .

- the BJT has a plurality of emitter regions separated on the upper surface based on a predetermined pattern shape. In the region between the separated emitter regions, an Al ion implantation process is subsequently performed to form a p-type base contact region in contact with the base region. Each of the plurality of separated emitter regions is surrounded by a base contact region when viewed in a BJT planar shape.

- the BJT disclosed in Patent Document 1 has a structure in which the SiC surface of the BJT is covered with a surface recombination suppressing semiconductor layer between the emitter region and the base contact region.

- the surface recombination suppressing semiconductor layer has a function of suppressing recombination between electrons flowing out from the emitter region and holes flowing out from the base contact region. This suppresses recombination of electrons from the emitter region and holes from the base contact region, and achieves an improvement in the current amplification factor of the junction type semiconductor layer device.

- a control electrode portion called a base is formed by a pn junction.

- Ic main current

- control current Ib control current

- recombination of holes flowing from the control electrode (carrier of the control current Ib) and electrons flowing between the main electrodes (carrier of the main current Ic) can be mentioned.

- the value of the recombination current depends on the electron density, hole density, and recombination level density, and the higher the density, the larger the recombination current.

- the SiC surface is known as a site where recombination is likely to occur.

- various proposals have been made in the process of forming a protective film by oxidizing the SiC surface. This point is also described in Patent Document 1.

- a surface recombination suppressing semiconductor layer composed of a p-type region having a low concentration is provided on the SiC surface.

- a potential barrier against electrons is formed on the SiC surface, so that the electron density on the SiC surface can be lowered.

- the hole density can be kept low by forming a high resistance layer on the SiC surface in a p-type region having a low concentration.

- a surface recombination suppressing semiconductor layer By forming such a surface recombination suppressing semiconductor layer, even if a recombination level exists on the SiC surface of the junction transistor, the recombination probability can be reduced and the current amplification factor of the junction transistor is increased. be able to.

- the emitter region is etched until the surface of the base region is exposed. At this time, the base region layer needs to be slightly shaved. For this reason, since the base region becomes thin, the resistance increases, and the base resistance varies due to variations in the etching substrate surface. In order to improve the current amplification factor of the BJT, it is desirable to reduce the thickness of the base region. However, if the thickness of the base region is reduced, the increase or variation in the base resistance due to the above-described etching process of the emitter region becomes remarkable. Become. For a conventional BJT having a four-layer structure, a device that achieves both a high current gain and a small and stable base resistance has not been realized.

- an object of the present invention is a conventional BJT having a four-layer structure, which reduces the recombination probability of electrons and holes, and controls the main current flowing between the main electrodes and the control electrode.

- An object of the present invention is to provide a bipolar silicon carbide semiconductor device capable of suppressing recombination between currents, improving a current amplification factor, and realizing a small and stable base resistance, and a method for manufacturing the same.

- a first bipolar silicon carbide semiconductor device (corresponding to claim 1) includes a collector region which is a substrate made of a silicon carbide semiconductor crystal, a high resistance layer formed on the collector region, and a high resistance layer.

- a base region formed thereon, an emitter region formed of a low-resistance layer and bonded to the base region; a low-resistance base contact region formed around the emitter region and bonded to the base region; and a base contact region Near the surface between the emitter region, a recombination suppression region having the same conductivity type as the base region and higher than its resistivity, or a recombination suppression region having the same conductivity type as the emitter region and higher than its resistivity It is characterized by having.

- a second bipolar silicon carbide semiconductor device (corresponding to claim 2) includes a collector region which is a substrate made of a silicon carbide semiconductor crystal, a high resistance layer formed on the collector region, and a high resistance layer.

- the base region formed above, an emitter region composed of a low resistance layer, joined to the base region, a low resistance base contact region formed around the emitter region and joined to the base region, and the base region, It is characterized by having a buried region that is in contact with the base contact region and has the same conductivity type as the base region and has a resistivity equal to or lower than the resistivity.

- a third bipolar silicon carbide semiconductor device (corresponding to claim 3) includes a collector region which is a substrate made of a silicon carbide semiconductor crystal, a high resistance layer formed on the collector region, and a high resistance layer.

- a base region formed on the base region, an emitter region joined to the base region, a low resistance base contact region formed around the emitter region and joined to the base region, and a high resistance layer A buried region that is in contact with the base region and has the same conductivity type as that of the base region and has a resistivity higher than that of the base region, or a recombination suppression region that has the same conductivity type as that of the high resistance region and has a resistivity higher than that of the base region. It is characterized by having.

- the collector region is a low-resistance layer of the first conductivity type and the emitter region is a low-resistance layer of the first conductivity type in the above configuration.

- the high resistance layer is of the first conductivity type, and the base region is of the second conductivity type.

- a first bipolar silicon carbide semiconductor device manufacturing method includes a first step of forming a high resistance layer on a substrate made of silicon carbide semiconductor crystals and serving as a collector region; A second step of forming a base region on the high resistance layer; a third step of forming a low resistance layer on the base region; and forming an emitter region by partially etching the low resistance layer

- a recombination suppression region having the same conductivity type as the base region and higher in resistivity than the base region exposed by etching, or having the same conductivity type as the emitter region and its resistance

- a second bipolar silicon carbide semiconductor device manufacturing method includes a first step of forming a high resistance layer on a substrate made of silicon carbide semiconductor crystals and serving as a collector region; A second step of forming a base region on the high resistance layer; a third step of forming a low resistance layer on the base region; and forming an emitter region by partially etching the low resistance layer And a fifth step of forming a buried region in the base region in contact with the base contact region and having the same conductivity type as the base region and having a resistivity equal to or lower than the resistivity. And a sixth step of forming a base contact region bonded to the base region.

- a third bipolar silicon carbide semiconductor device manufacturing method includes a first step of forming a high resistance layer on a substrate made of silicon carbide semiconductor crystals and serving as a collector region; A second step of forming a base region on the high resistance layer; a third step of forming a low resistance layer on the base region; and forming an emitter region by partially etching the low resistance layer And a fourth step of contacting the base region with the high-resistance layer and having the same conductivity type as that of the base region and higher than its resistivity, or having the same conductivity type as that of the emitter region and the resistivity thereof. A fifth step of forming a higher buried region and a sixth step of forming a base contact region bonded to the base region.

- a collector electrode, an emitter electrode, and a base electrode are formed in each of the collector region, the emitter region, and the base contact region. And a step of forming an upper layer electrode above the emitter electrode and the base electrode.

- the bipolar silicon carbide semiconductor device has the following effects. First, since the recombination suppression region is formed on the base surface from the base region to the emitter region, it prevents the electron or hole from approaching the recombination level formed on the surface of the silicon carbide semiconductor, thereby increasing the current amplification factor. Can be increased.

- the base region or the buried region having a higher resistance than the high resistance layer is formed in the high resistance layer, electrons from the high resistance layer can be prevented from approaching the base region, and the current amplification factor can be increased. .

- the base resistance value can be reduced and variations can be suppressed, and the device characteristics of BJT can be made uniform. can do.

- the bipolar silicon carbide semiconductor device is provided with the layered recombination suppressing semiconductor region at a required location as described above, and therefore, electrons flowing from the emitter and Recombination of holes flowing from the base can be suppressed, and a bipolar silicon carbide semiconductor device having a high current gain can be easily and reliably manufactured.

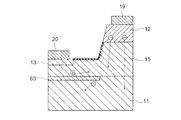

- FIG. 3 is a partial longitudinal sectional view of a bipolar semiconductor device (BJT) according to a first embodiment of the present invention, and is an enlarged sectional view taken along line AA of FIG. 1 is a plan view of a part of a bipolar semiconductor device according to a first embodiment. It is a fragmentary longitudinal cross-section explaining the problem of operation

- movement of the bipolar type semiconductor device by 1st Example. 3 is a flowchart illustrating a method for manufacturing a bipolar semiconductor device according to the first embodiment.

- FIG. 5 is a partial longitudinal sectional view of a bipolar semiconductor device according to a second embodiment of the present invention. It is a fragmentary longitudinal cross-sectional view explaining operation

- FIG. 6 is a longitudinal sectional view of a bipolar semiconductor device according to a fourth embodiment of the present invention.

- FIG. 6 is a longitudinal sectional view of a bipolar semiconductor device according to a fifth embodiment of the present invention. It is the longitudinal cross-sectional view which showed the structure of the conventional bipolar type semiconductor device.

- FIGS. 1 to 6B A first embodiment of a bipolar semiconductor device according to the present invention will be described with reference to FIGS. 1 to 6B.

- This bipolar semiconductor device shows an example of a conventional BJT having a general four-layer structure.

- the BJT 10 includes, for example, five emitter electrodes 19 arranged in parallel in a specific unit region on the upper surface of the device. These emitter electrodes 19 are surrounded by a base electrode 20.

- the BJT 10 has a collector region 11 formed of an n-type low resistance layer (n + layer) formed on a lower surface portion having a SiC (silicon carbide) crystal, and the SiC crystal.

- An emitter region 12 made of an n-type low resistance layer (n + layer) formed on the upper side surface portion is provided.

- a layer forming the collector region 11 is a substrate.

- a base electrode 20 is formed around each of the plurality of emitter electrodes 19 so as to surround the emitter electrode 19. This means that the periphery of the emitter region 12 located below the emitter electrode 19 is surrounded by the p-type base contact region 13 located below the base electrode 20.

- the base contact region 13 is formed up to a predetermined depth position.

- BJT 10 between the upper emitter region 12 and a lower collector region 11, n-type high-resistance layer from the lower side (n - layer) and 14 and p-type base region 15 is formed by stacking Yes.

- the base region 15 is formed so as to be in contact with and electrically connected to the base contact region 13. In other words, the base contact region 13 is formed so as to be embedded at a predetermined position on the base region 15.

- n-type is “first conductivity type” and the “p-type” is “second conductivity type”.

- the p + type base region 15 is further interposed between the p + type base contact region 13 formed on a part of the surface of the layered p type base region 15 and the emitter region 12.

- a layered recombination suppression region 16 is provided on the exposed surface portion so as to cover the surface portion.

- the depth of the recombination suppression region 16 is substantially equal to the depth of the base contact region 13.

- the recombination suppression region 16 is a high-resistance semiconductor and is “p ⁇ ” or “n ⁇ ”.

- the base contact region 13 is formed so as to come into contact with the surface of the base region 15 and further enter the inside of the base region 15 from the surface.

- the collector electrode 18 is bonded to the lower surface of the collector region 11

- the emitter electrode 19 is bonded to the upper surface of the emitter region 12

- the base contact region 13 A base electrode 20 is joined to the upper surface.

- the exposed surface between the emitter electrode 19 and the base electrode 20 is covered with a surface protective film 17 and is protected thereby.

- an upper layer electrode 21 is provided above each of the emitter electrode 19 and the base electrode 20. In FIG. 1, the upper layer electrode 21 is not shown.

- the main current is an electron flow that flows from the emitter region 12 (or the emitter electrode 19) to the collector region 11 (or the collector electrode 18).

- the emitter region 12 and the collector region 11 are main electrode regions for flowing a main current.

- Energization (ON) and non-energization (OFF) of the main current are based on a base voltage applied to the base electrode 20, that is, a control signal applied between the base contact region 13 and the base region 15 and the emitter region 12. Be controlled.

- the applied voltage between the base and the emitter is 0 V or less, the BJT 10 does not flow main current and is turned off.

- the BJT 10 When a voltage of a certain level or higher is applied between the base and the emitter, the BJT 10 is turned on due to the main current flowing. In the ON state, the pn junction formed between the base region 15 and the emitter region 12 is forward-biased, and a hole current that is a control current flows from the base region 15 to the emitter region 12.

- FIG. 3 shows a BJT 10A having a conventional structure.

- the same elements as those described in FIG. In the structure of the BJT 10A, in the base region 15, a large number of recombination levels 22 are formed in the vicinity of the SiC surface between the base contact region 13 and the emitter region 12. Therefore, some of the electrons 23 of the main current I1 flowing from the emitter region 12 toward the collector region 11 and the holes 24 flowing from the base contact region 13 are recombined at the recombination level 22. Such recombination of electrons 23 and holes 24 occurs frequently at the interface between the base region 15 and the high resistance layer 14. As a result, an invalid base current that does not contribute to the operation of the BJT 10A flows, and the current amplification factor of the BJT 10A is reduced.

- a layer-like layer is formed on the surface of the base region 15 exposed between the base contact region 13 and the emitter region 12 and its vicinity.

- a coupling suppression region 16 is formed.

- the recombination suppressing region 16 is formed of a “p ⁇ ” or “n ⁇ ” semiconductor region, and forms a high potential barrier against the electrons 23 or the holes 24 and also has a high resistance layer having a low hole or electron concentration. It has become. Due to the existence of the recombination suppression region 16, holes 24 flowing from the base contact region 13 to the base region 15 do not easily flow into the recombination suppression region 16 in FIG.

- Electrons flowing from the region 12 are also difficult to flow near the SiC surface. As a result, as shown in FIG. 4, the electrons 23 flowing out from the emitter region 12 flow toward the collector region 11 as the main current I2 without recombining with the holes, thereby improving the current amplification factor of the BJT 10. Can do.

- the implantation concentration is extremely low and the energy required for ion implantation is low compared to the ion implantation for forming the base contact region 13. Therefore, in the ion implantation for forming the recombination suppression region 16, the density of recombination levels can be suppressed low.

- the BJT 10 is designed with a target of a blocking voltage of 600V, for example.

- a low resistance n-type 4H—SiC substrate turned off by 8 degrees from the (0001) plane is used as the substrate portion.

- the substrate portion becomes the collector region 11.

- the n-type high resistance layer 14 on the substrate is a layer for blocking a high voltage applied between the emitter and the collector.

- the high resistance layer 14 is set to have a thickness of 10 ⁇ m and an impurity concentration of 1 ⁇ 10 16 cm ⁇ 3 , for example, so as to block a voltage of 600 V or higher.

- the p-type base region 15 on the high resistance layer 14 has a thickness and an impurity concentration so as not to be depleted when a high voltage is applied between the emitter and the collector.

- the p-type base region 15 has a thickness of 0.2 to 0.5 ⁇ m and an impurity concentration of about 4 ⁇ 10 17 to 2 ⁇ 10 18 cm ⁇ 3 .

- a low resistance n-type emitter region 12 having a thickness of 0.5 to 2.0 ⁇ m and an impurity concentration of 1 to 5 ⁇ 10 19 cm ⁇ 3 is provided.

- a low-resistance base contact region 13 is formed around the emitter region 12.

- the planar shape of the emitter region 12 is an elongated island shape.

- One BJT 10 includes a plurality of emitter regions 12.

- the dimensions of one emitter region 12 are about 3 to 10 ⁇ m in width and about 100 to 1000 ⁇ m in length.

- the period of the unit structure including the base contact region 13 and the emitter region 12 is about 10 to 30 ⁇ m.

- FIG. 5 is a flowchart showing each process of the manufacturing method.

- 6A and 6B are longitudinal sectional views showing structures manufactured by each process.

- the manufacturing method of the BJT 10 includes the following processes (1) to (10) (steps S11 to S20). As shown in FIG. 5, each process is executed in the order from step S11 to step S20.

- step S11 High resistance layer forming process

- step S12 Base region formation process

- step S13 Low resistance layer formation process

- step S14 Emitter etching process

- step S15 Recombination suppression region formation process

- step S17 Base contact region formation process

- step S18 Surface protective film formation process

- step S19 Electrode formation process

- step S20 Upper layer electrode formation process

- the structure shown in (a) of FIG. 6A is formed by performing the above steps S11 to S13.

- step S11 nitrogen having a thickness of 10 ⁇ m and a concentration of 1 ⁇ 10 16 cm ⁇ 3 is doped as an impurity on the n-type substrate 40 formed of SiC by an epitaxial growth method.

- a high resistance layer 41 is grown. “4H—SiC (0001) 8 ° off” is used for the substrate 40.

- the substrate 40 becomes the collector region 11 of the n-type low resistance layer described above.

- step S12 an epitaxial growth method is performed on the n-type high resistance layer 41 with aluminum (Al) as an impurity at a concentration of 4 ⁇ 10 17 to 2 ⁇ 10 18 cm ⁇ 3 to 0.2 to A 0.5 ⁇ m p-type base region 42 is grown.

- Al aluminum

- step S13 nitrogen having a thickness of 0.5 to 2.0 ⁇ m and a concentration of 1 to 5 ⁇ 10 19 cm ⁇ 3 is formed as an impurity on the n-type base region 42 by an epitaxial growth method.

- a doped n-type low resistance layer 43 is grown.

- the low resistance layer 43 is a portion for forming the emitter region 12 described above.

- step S14 in the structure shown in FIG. 6A (a), a silicon oxide film 51 is deposited on the upper surface by CVD, photolithography is performed, and then silicon oxide is formed by RIE. The film 51 is etched. Thus, a mask is formed. Then, using this silicon oxide film 51, SiC etching is performed on the low resistance layer 43 by RIE, and the emitter region 12 is formed using the low resistance layer 43. SF 6 gas or the like is used for RIE of SiC etching. The resulting structure is shown in FIG. 6A (b).

- the recombination suppression region 16 is formed using the mask 51 shown in FIG. 6A (b) as it is. .

- the recombination suppression region 16 is formed by performing ion implantation of nitrogen as an impurity (ion species). Ions are implanted into all regions etched by the emitter etching process (step S15).

- the ion implantation amount is set to a value approximately equal to or around the impurity concentration of the base region 42.

- the ion implantation amount is desirably about 3 to 5 ⁇ 10 17 cm ⁇ 3 .

- the recombination suppression region 16 since the recombination suppression region 16 only needs to include a recombination level in the vicinity of the surface, its depth may be about 0.1 to 0.2 ⁇ m. Therefore, the implantation energy can be suppressed to as low as about 100 keV, and the generation of crystal defects in the ion implantation process can be suppressed.

- step S16 In the base contact region forming process (step S16), first, as shown in FIG. 6A (d), a mask 52 is formed so that the surface portion for forming the base contact region 13 is exposed.

- the mask 52 is formed by depositing a silicon oxide film by a CVD method, performing photolithography, and then etching the silicon oxide film by RIE. Thereafter, ion implantation is performed to form the base contact region 13.

- the implanted ions are aluminum (Al), and the depth of implantation is, for example, 0.2 ⁇ m.

- the ion implantation amount is 1 ⁇ 10 18 to 10 20 cm ⁇ 3 , and the energy required for ion implantation is approximately 200 KeV.

- the recombination suppression region 16 is formed on the surface of the base region 15 between the base contact region 13 and the emitter region 12 by the above steps S15 and S16.

- the purpose of providing the recombination suppression region 16 is to keep electrons coming from the emitter region 12 away from the SiC surface of the recombination suppression region 16.

- step S17 in the process of activating the ion implantation layer (step S17), after the ion implantation, the implanted ions are electrically activated in the semiconductor, and a heat treatment is performed to eliminate crystal defects generated by the ion implantation ( FIG. 6B (e)).

- a heat treatment is performed to eliminate crystal defects generated by the ion implantation ( FIG. 6B (e)).

- both the implanted ions in the base contact region 13 and the implanted ions in the recombination suppression region 16 are activated at the same time.

- heat treatment is performed at a high temperature of about 1700 to 1800 ° C. for about 10 minutes.

- argon gas (Ar) is used as the atmospheric gas.

- step S18 In the process of forming the surface protective film (step S18), as shown in FIG. 6B (f), first, in order to remove the surface layer generated in the ion implantation process and the activation process, the oxide film is removed after the thermal oxidation. Perform sacrificial oxidation.

- the oxidation condition is, for example, 1100 ° C. for 20 hours in dry oxygen. Hydrofluoric acid is used to remove the oxide film.

- thermal oxidation is performed again to form an oxide film 53.

- the temperature is 1100 ° C.

- the time is 5 hours

- the atmosphere is wet.

- POA Post Oxidation Anneal

- heat treatment is performed to reduce the impurity level at the interface of the SiC oxide film.

- POA is performed in a hydrogen, nitrogen oxide (NO, N 2 O) or argon atmosphere at a high temperature of about 800 to 1300 ° C. for about 10 to 30 minutes.

- a CVD oxide film or a CVD nitride film is formed.

- the emitter electrode 19, the base electrode 20, and the collector electrode 18 are formed on the surfaces of the emitter region 12 (low resistance layer 43), the base contact region 13, and the collector region 11 (substrate 40), respectively. It forms (FIG. 6B (g)).

- the remaining oxide film 53 becomes the surface protective film 17 described above.

- the emitter electrode 19 and the collector electrode 18 are made of nickel or titanium, and the base electrode 20 is made of titanium or aluminum.

- Each electrode 18, 19, 20 is formed by vapor deposition or sputtering. For the formation of the electrode pattern, dry etching, wet etching, lift-off method or the like is used.

- heat treatment is performed to reduce the contact resistance between the metal portion and the semiconductor portion.

- the heat treatment conditions are a temperature condition of 800 to 1000 ° C. and a time condition of about 10 to 30 minutes.

- step S20 the upper layer electrode formation process (step S20) is executed.

- an upper layer electrode 54 for taking out a plurality of separated emitter electrodes 19 as one electrode is formed (FIG. 6B (h)).

- the silicon oxide film or the like in the emitter electrode 19 is removed by photolithography and etching.

- the upper layer electrode 54 is deposited.

- aluminum (Al) is used as the material of the upper electrode 54.

- the BJT 10 shown in FIGS. 1 and 2 is manufactured.

- the BJT 10 is a high-performance semiconductor device having normally-off characteristics.

- the combinations of the first and second conductivity types such as the collector region, the emitter region, the high resistance layer, the base region, the base contact region, and the recombination suppression region can be reversed. . This also applies to the other embodiments described below.

- FIG. 7 A second embodiment of a bipolar semiconductor device according to the present invention will be described with reference to FIGS.

- the bipolar semiconductor device of the second embodiment is also BJT.

- elements that are substantially the same as those described in FIG. 1 are given the same reference numerals.

- the emitter region 12 is etched until the surface of the base region 15 is exposed.

- the thickness of the base layer is reduced, and as a result, the resistance value of the base is increased.

- the base resistance value varies between wafers or between wafers due to variations in etching depth within a wafer or between wafers.

- a p-type semiconductor having a resistivity equal to or lower than that of the base region in a region corresponding to the region of the base surface exposed by etching in the base region 15 formed in a layer shape A low resistance buried region 61 made of p + or p ⁇ ) is provided.

- the surface recombination suppression region 16 is not formed as in the first embodiment.

- Other structures are the same as those of the first embodiment.

- the hole current flowing from the base contact region 13 to the base region 15 flows near the surface in the conventional example shown in FIG. 3, whereas the resistance value as shown in FIG. It flows to the lower low resistance buried region 61. Therefore, recombination near the surface of base region 15 is reduced, and the current amplification factor is improved.

- the resistance of the base region 15 is determined by the resistance value of the low-resistance buried region 61. As a result, it is possible to increase the resistance and variation of the base region 15 caused by the etching.

- the impurity concentration of the p-type base region 15 are as 4 ⁇ 10 17 ⁇ 2 ⁇ 10 18 cm -3 as described above, the concentration of more than the same level as the base region 15 the impurity concentration of the low-resistance buried region 61

- the impurity concentration of the p-type base region 15 is, for example, 4 ⁇ 10 17 cm ⁇ 3

- the impurity concentration of the low-resistance buried region 61 is set to 2 ⁇ 10 18 cm ⁇ 3 and the thickness thereof is set as the base. If the thickness of the region 61 is the same, the resistivity of the low-resistance buried region 61 can be reduced to 1/3 of the resistivity of the base region 15.

- the low resistance buried region 61 can be formed by applying a multi-stage ion implantation method in the manufacturing method of the BJT 10 of the first embodiment described above.

- a third embodiment of a bipolar semiconductor device according to the present invention will be described with reference to FIGS.

- the bipolar semiconductor device of the third embodiment is also a BJT. 9, elements that are substantially the same as those described in FIG. 1 are denoted by the same reference numerals.

- the BJT 10A having the conventional structure has a characteristic that the holes flowing through the base region 15 and the electrons flowing through the collector region 11 are recombined near the base-collector interface.

- the base region 15 is a region corresponding to the region of the base surface exposed by the etching described above on the lower side (on the high resistance layer 14 side) of the base region 15 formed in layers.

- a high resistance buried region made of a p-type semiconductor (p ⁇ ) having a higher resistance than the base region 15 or a high resistance buried region 63 made of an n-type semiconductor (n ⁇ ) having a higher resistance than the high resistance layer 14 in contact with the base region 15.

- the recombination suppression region 16 on the base surface is not formed as in the first embodiment. Other structures are the same as those of the first embodiment.

- the electron / hole concentration in the high resistance buried region / high resistance layer in the third embodiment is lower than that in the base region / high resistance layer vicinity in the BJT 10A having the conventional structure. Therefore, recombination can be reduced, thereby improving the current amplification factor. Even in the case of the n ⁇ layer, recombination can be suppressed by substantially the same principle, and the current amplification factor can be improved.

- the impurity concentration of the p-type base region 15 is 4 ⁇ 10 17 to 2 ⁇ 10 18 cm ⁇ 3 , whereas the impurity concentration of the high-resistance buried region 63 is less than or equal to that of the base region 15.

- the impurity concentration of the p-type base region 15 is, for example, 4 ⁇ 10 17 cm ⁇ 3

- the impurity concentration of the high-resistance buried region 63 is set to 1 ⁇ 10 17 cm ⁇ 3 or less.

- a bipolar semiconductor device according to a fourth embodiment of the present invention will be described with reference to FIG. 11, elements that are substantially the same as those described in FIGS. 7 and 9 are denoted by the same reference numerals.

- the BJT 300 of the fourth embodiment is configured by combining the characteristic structures of the second and third embodiments.

- the high resistance buried region 63 is formed so as to be in contact with the lower surface of the low resistance buried region 61.

- Other configurations are the same as those of the second or third embodiment. The same effect as described above is also exhibited by the BJT 300 of the present embodiment.

- FIG. 12 A fifth embodiment of a bipolar semiconductor device according to the present invention will be described with reference to FIG. 12, elements that are substantially the same as those described in FIGS. 1, 7, and 9 are denoted by the same reference numerals.

- the BJT 400 of the fifth embodiment is configured by combining the characteristic structures of the first, second and third embodiments.

- a recombination suppression region 16, a low-resistance buried region 61, and a high-resistance buried region 63 formed so as to be in contact with the lower surface of the low-resistance buried region 61 are provided.

- Other configurations are the same as those of the first, second, or third embodiment. The same effect as described above is also exhibited by the BJT 400 of the present embodiment.

- a reverse polarity type in which the polarities of p and n in the description of the process of the manufacturing method are reversed may be used.

- SiC has been described, but the present invention can also be applied to other semiconductors in which surface recombination is a problem.

- the present invention relates to a conventional general bipolar silicon carbide semiconductor device having a four-layer structure, which suppresses recombination of electrons of a main current with holes of a control current and improves a current amplification factor, and Even if the base layer is thinned, it is used for improving an increase or variation in the base resistance value, and further used for a method of manufacturing a bipolar silicon carbide semiconductor device having such characteristics.

- BJT Bipolar semiconductor devices

- SYMBOLS 11 Collector area

- region 12 Emitter area

- region 13 Base contact area

- region 14 High resistance layer 15

- region 17 Surface protective film 18

- Collector electrode 19 Emitter electrode 20

- Upper layer electrode 40 Substrate 41 High resistance layer 42

- Base area 43 Low resistance Layer 61 Low resistance buried region 63 High resistance buried region 100 BJT 200 BJT 300 BJT 400 BJT

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Manufacturing & Machinery (AREA)

- Bipolar Transistors (AREA)

Abstract

4層構造を有するBJTで、電子と正孔の再結合確率を低減し、主電流と制御電流との間の再結合を抑制し、電流増幅率を向上でき、小さく安定したベース抵抗を実現できるバイポーラ型炭化珪素半導体装置が開示される。該半導体装置は、ベースコンタクト領域(13)とエミッタ領域(12)との間の表面付近に形成され、ベース領域(15)と同じ導電型でありかつその抵抗率よりも高い再結合抑制領域(16)、またはエミッタ領域(12)と同じ導電型でありかつその抵抗率よりも高い再結合抑制領域(16)を有する。

Description

本発明はバイポーラ型炭化珪素半導体装置およびその製造方法に関し、特に、通常の4層構造を有するバイポーラ型炭化珪素半導体装置であって、主電極間に流れる主電流と制御電極に流れる制御電流との間の再結合を抑制し、電流増幅率を高めるのに適したバイポーラ型炭化珪素半導体装置、およびその製造方法に関する。

炭化珪素(シリコン・カーバイド(Silicon Carbide)、以下では単に「SiC」と記す。)は、広く半導体装置に応用されているシリコンと比べて、バンドギャップエネルギが大きいという特性を有する。そのためSiCを利用した半導体装置は、高電圧、大電力、高温動作の条件に適しており、パワーデバイスなどへの適用が期待されている。現在、研究開発されているSiCパワーデバイスの構造は、主に、「MOS型」と「接合型」の2つの型に分類されている。

ここでは接合型SiCパワーデバイスの性能向上という観点で説明する。接合型SiCパワーデバイスには、静電誘導トランジスタ(Static Induction Transistor、「SIT」)や接合型電界効果トランジスタ(Junction Field Effect Transistor、「JFET」)、あるいはバイポーラトランジスタ(Bipolar Junction Transistor、「BJT」)などがある。

従来のBJTの例として例えば非特許文献1に記載された構造を有するものがある。BJTは、低抵抗のn+型4H-SiC(0001)面8度オフ基板上に、下側から、n-型高抵抗領域、p型ベース領域、n+型エミッタ領域の順序に積層されて形成される。エミッタ領域は、多数の細長い形状の領域からなっている。エミッタ領域、ベース領域、コレクタ領域には外部に電気的接続を取るための電極が形成されている。

図13に非特許文献1に開示されたBJTの断面を示している。図13に示すように、BJT500は、n型低抵抗層であるコレクタ領域501、n型高抵抗領域502、p型領域のベース領域503、n型低抵抗のエミッタ領域504、エミッタ領域を囲むように形成されたp型低抵抗領域のベースコンタクト領域505を備えている。コレクタ領域501とベース領域503(ベースコンタクト領域505)とエミッタ領域のそれぞれの外部には、電気的接続をとるためのコレクタ電極506、ベース電極507、エミッタ電極508が接合されている。さらにBJT500の電極以外の露出表面の全体は表面保護膜509で覆われている。

さらにデバイス特性(電流増幅率)が改善された従来のBJTの例として特許文献1に記載された構造を有するものがある。特許文献1に開示されたBJTは、コレクタ領域となるn+型4H-SiC(0001)面基板上に、下側から、第1のn型高抵抗層、p型ベース領域、第2のn型高抵抗層、n+型エミッタ領域の順序で積層された構造を備えている。当該BJTで、そのエミッタ領域は、当該積層構造において上面からn+型エミッタ領域、および第2のn型高抵抗層の途中まで所定の平面パターン形状でエッチングすることにより、分離されて形成される。BJTは、その上面に、所定のパターン形状に基づいて分離された複数のエミッタ領域を有している。分離された複数のエミッタ領域の間の領域には、その後にAlイオン注入の工程が実行され、ベース領域に接触するp型ベースコンタクト領域が形成される。分離された複数のエミッタ領域の各々は、BJTの平面形状で見てみると、その周囲をベースコンタクト領域で囲まれている。

特許文献1に開示されているBJTは、エミッタ領域とベースコンタクト領域との間において、当該BJTにおけるSiC表面を表面再結合抑制半導体層で覆うようにした構造を有している。この表面再結合抑制半導体層は、エミッタ領域から流れ出る電子とベースコンタクト領域から流れ出る正孔との再結合を抑制する機能を有している。これにより、エミッタ領域からの電子とベースコンタクト領域からの正孔の再結合を抑え、接合型半導体層装置の電流増幅率の向上を達成している。

J. Zhang他著「High Power(500V-70A) and High Gain(44-47) 4H-SiC Bipolar Junction Transistors」Materials Science Forum Vols. 457-460 (2004) pp. 1149-1152.

BJTのごとき接合型トランジスタでは、ベースと呼ばれる制御電極部分がpn接合で形成されている。エミッタとコレクタの間の主電極の間に電流を流すためには、当該制御電極に電流を流す必要がある。主電極の間に流れる電流を「主電流Ic」、制御電極に流れる電流を「制御電流Ib」とするとき、両電流の比(Ic/Ib)は「電流増幅率」と呼ばれる。BJTの開発では、電流増幅率の値を大きくすることが重要な課題となっている。

上記電流増幅率を低下させる要因としては、制御電極から流れ込む正孔(制御電流Ibのキャリア)と主電極間を流れる電子(主電流Icのキャリア)との再結合を挙げることができる。再結合電流の値は、電子密度、正孔密度、再結合準位密度に依存し、それぞれの密度が高いほど再結合電流も大きくなる。

再結合が発生しやすい部位としてはSiC表面が知られている。SiC表面の再結合準位の密度を低減するために、SiC表面を酸化して保護膜を形成するプロセスで各種の工夫をなすことが提案されている。この点は特許文献1にも記載されている。さらに特許文献1のBJTでは、再結合確率を下げるために、SiC表面に、濃度の低いp型領域からなる表面再結合抑制半導体層を設けるようにしている。このような表面再結合抑制半導体層を形成すると、SiC表面に電子に対する電位障壁が形成されるので、SiC表面での電子密度を下げることができる。さらに、濃度の低いp型領域でSiC表面に高抵抗層を形成することにより、正孔の密度も低く抑えることができる。かかる表面再結合抑制半導体層を形成することにより、接合型トランジスタのSiC表面に再結合準位が存在したとしても、再結合確率を低減することができ、接合型トランジスタの電流増幅率を大きくすることができる。

以上のようにBJTにおいて、SiC表面での再結合を抑制して電流増幅率を大きくする試みが多くなされている。

他方、上面側からエミッタ領域、ベース領域、高抵抗層、および基板(コレクタ領域)の順序で構成される4層構造を有した従来の一般的なBJTでは、今まで、上記のような再結合を抑制して高い電流増幅率を実現する試みが十分になされていなかった。かかる一般的なBJTでも、制御電極から流れ込む正孔と主電極間を流れる電子とが、SiC表面に多数存在する再結合中心を介して再結合することが電流増幅率を下げる要因となる。またベース領域とコレクタ領域等との界面でも電子と正孔の濃度が共に高いため、再結合が盛んに発生するという問題もある。またBJTの製造方法では、エミッタ領域をベース領域の表面が露出するまでエッチングするが、その際にベース領域の層をわずかに削る必要がある。このため、ベース領域が薄くなるので抵抗が増大し、エッチングの基板面内のばらつきによりベース抵抗がばらつくことになる。BJTの電流増幅率を向上させるためにはベース領域の厚みを薄くすることが望ましいが、ベース領域の厚みを薄くすると、前述したエミッタ領域のエッチングプロセスに起因するベース抵抗の増大やばらつきが顕著になる。4層構造を有する従来のBJTについて、高い電流増幅率と、小さく安定したベース抵抗とを両立するデバイスは実現されていない。

本発明の目的は、上記の問題を鑑み、4層構造を有する従来の一般的なBJTで、電子と正孔の再結合確率を低減し、主電極間に流れる主電流と制御電極に流れる制御電流との間の再結合を抑制し、電流増幅率を向上することができ、小さく安定したベース抵抗を実現することができるバイポーラ型炭化珪素半導体装置およびその製造方法を提供することにある。

第1のバイポーラ型炭化珪素半導体装置(請求項1に対応)は、炭化珪素半導体結晶で作られた基板であるコレクタ領域と、コレクタ領域の上に形成された高抵抗層と、高抵抗層の上に形成されたベース領域と、低抵抗層からなり、ベース領域と接合されるエミッタ領域と、エミッタ領域の周囲に形成され、ベース領域に接合する低抵抗のベースコンタクト領域と、ベースコンタクト領域とエミッタ領域との間の表面付近に、ベース領域と同じ導電型でありかつその抵抗率よりも高い再結合抑制領域、またはエミッタ領域と同じ導電型でありかつその抵抗率よりも高い再結合抑制領域と、を有することで特徴づけられる。

第2のバイポーラ型炭化珪素半導体装置(請求項2に対応)は、炭化珪素半導体結晶で作られた基板であるコレクタ領域と、コレクタ領域の上に形成された高抵抗層と、高抵抗層の上に形成されたベース領域と、低抵抗層からなり、ベース領域と接合されるエミッタ領域と、エミッタ領域の周囲に形成され、ベース領域に接合する低抵抗のベースコンタクト領域と、ベース領域に、ベースコンタクト領域に接すると共に、ベース領域と同じ導電型でありかつその抵抗率と同等かまたは当該抵抗率よりも低い埋め込み領域と、を有することで特徴づけられる。

第3のバイポーラ型炭化珪素半導体装置(請求項3に対応)は、炭化珪素半導体結晶で作られた基板であるコレクタ領域と、コレクタ領域の上に形成された高抵抗層と、高抵抗層の上に形成されたベース領域と、低抵抗層からなり、ベース領域と接合されるエミッタ領域と、エミッタ領域の周囲に形成され、ベース領域に接合する低抵抗のベースコンタクト領域と、高抵抗層に、ベース領域に接すると共に、ベース領域と同じ導電型でありかつその抵抗率よりも高い埋め込み領域、または前記高抵抗領域と同じ導電型でありかつその抵抗率よりも高い再結合抑制領域と、を有することで特徴づけられる。

第4のバイポーラ型炭化珪素半導体装置(請求項4に対応)は、上記の構成において、コレクタ領域は第1の導電型の低抵抗層であり、エミッタ領域は第1の導電型の低抵抗層であり、高抵抗層は第1の導電型であり、ベース領域は第2の導電型であることを特徴とする。

第1のバイポーラ型炭化珪素半導体装置の製造方法(請求項5に対応)は、炭化珪素の半導体結晶で作られかつコレクタ領域となる基板の上に高抵抗層を形成する第1の工程と、高抵抗層の上にベース領域を形成する第2の工程と、ベース領域の上に低抵抗層を形成するための第3の工程と、低抵抗層を部分的にエッチングしてエミッタ領域を形成する第4の工程と、エッチングにより露出したベース領域の表面付近に、ベース領域と同じ導電型でありかつその抵抗率よりも高い再結合抑制領域、またはエミッタ領域と同じ導電型でありかつその抵抗率よりも高い再結合抑制領域を形成する第5の工程と、ベース領域に接合するベースコンタクト領域を形成する第6の工程と、を含む方法である。

第2のバイポーラ型炭化珪素半導体装置の製造方法(請求項6に対応)は、炭化珪素の半導体結晶で作られかつコレクタ領域となる基板の上に高抵抗層を形成する第1の工程と、高抵抗層の上にベース領域を形成する第2の工程と、ベース領域の上に低抵抗層を形成するための第3の工程と、低抵抗層を部分的にエッチングしてエミッタ領域を形成する第4の工程と、ベース領域に、ベースコンタクト領域に接すると共に、ベース領域と同じ導電型でありかつその抵抗率と同等かまたは当該抵抗率よりも低い埋め込み領域を形成する第5の工程と、ベース領域に接合するベースコンタクト領域を形成する第6の工程と、を含む方法である。

第3のバイポーラ型炭化珪素半導体装置の製造方法(請求項7に対応)は、炭化珪素の半導体結晶で作られかつコレクタ領域となる基板の上に高抵抗層を形成する第1の工程と、高抵抗層の上にベース領域を形成する第2の工程と、ベース領域の上に低抵抗層を形成するための第3の工程と、低抵抗層を部分的にエッチングしてエミッタ領域を形成する第4の工程と、高抵抗層に、ベース領域に接すると共に、ベース領域と同じ導電型でありかつその抵抗率よりも高い埋め込み領域、またはエミッタ領域と同じ導電型でありかつその抵抗率よりも高い埋め込み領域を形成する第5の工程と、ベース領域に接合するベースコンタクト領域を形成する第6の工程と、を含む方法である。

第4のバイポーラ型炭化珪素半導体装置の製造方法(請求項8に対応)は、上記の方法において、コレクタ領域、エミッタ領域、およびベースコンタクト領域のそれぞれに、コレクタ電極、エミッタ電極、ベース電極を形成する工程と、エミッタ電極とベース電極の上側に上層電極を形成する工程と、を有することを特徴とする。

本発明に係るバイポーラ型炭化珪素半導体装置によれば、次の効果を奏する。

第1に、ベース領域からエミッタ領域にかけてベース表面で再結合抑制領域を形成したため、炭化珪素半導体の表面に形成された再結合準位に電子または正孔を近づけることを防止して電流増幅率を高めることができる。

第1に、ベース領域からエミッタ領域にかけてベース表面で再結合抑制領域を形成したため、炭化珪素半導体の表面に形成された再結合準位に電子または正孔を近づけることを防止して電流増幅率を高めることができる。

第2に、またベース領域内に当該ベース領域よりも低抵抗の埋め込み領域を形成したため、ベースコンタクト領域からの正孔が埋め込み領域に流れ込むことによって炭化珪素半導体の表面での再結合を防止し、電流増幅率を高めることができる。

第3に、高抵抗層に、ベース領域あるいは高抵抗層よりも高い抵抗の埋め込み領域を形成したため、高抵抗層からの電子がベース領域に近づくことを防止し、電流増幅率を高めることができる。

第4に、上記のごとく所要の箇所に再結合抑制領域あるいは低抵抗または高抵抗の埋め込み領域を設けることにより、ベース抵抗値を低減できると共にばらつきを抑えることができ、BJTのデバイス特性を均一化することができる。

また本発明に係るバイポーラ型炭化珪素半導体装置の製造方法によれば、バイポーラ型炭化珪素半導体装置において上記のごとく所要の箇所に層状の再結合抑制半導体領域を設けるようにしたため、エミッタから流れ込む電子とベースから流れ込む正孔の再結合を抑制することができ、高い電流増幅率を有するバイポーラ型炭化珪素半導体装置を容易にかつ確実に製作することができる。

以下に、本発明の好適な幾つかの実施例について、添付図面に基づいて詳細に説明する。

<第1実施例>

図1~図6Bを参照して本発明によるバイポーラ型半導体装置の第1の実施例を説明する。このバイポーラ型半導体装置は従来の一般的な4層構造のBJTの例を示している。

図1~図6Bを参照して本発明によるバイポーラ型半導体装置の第1の実施例を説明する。このバイポーラ型半導体装置は従来の一般的な4層構造のBJTの例を示している。

図2に示すように、BJT10は、そのデバイス上面の特定な単位領域に、並列に配列された例えば5本のエミッタ電極19を備えている。これらのエミッタ電極19はベース電極20によって囲まれている。

図1に示す縦断面構造において、BJT10は、SiC(炭化珪素)結晶を有する下側面部分に形成されたn型の低抵抗層(n+層)からなるコレクタ領域11と、当該SiC結晶を有する上側面部分に形成されたn型の低抵抗層(n+層)からなるエミッタ領域12を備えている。コレクタ領域11を形成する層が基板となっている。

図2の平面図の位置関係において、複数のエミッタ電極19の各々の周囲には、当該エミッタ電極19を囲むようにベース電極20が形成されている。この意味は、エミッタ電極19の下側に位置するエミッタ領域12の周囲は、ベース電極20の下側に位置するp型のベースコンタクト領域13によって囲まれているということである。ベースコンタクト領域13は所定の深さ位置まで形成されている。さらにBJT10において、上側のエミッタ領域12と下側のコレクタ領域11の間には、下側からn型高抵抗層(n-層)14とp型のベース領域15とが積層されて形成されている。ベース領域15は、ベースコンタクト領域13と接触して電気的に接続されるように形成されている。換言すれば、ベースコンタクト領域13は、ベース領域15上の所定の位置に埋め込むように形成されている。

本実施例において、上記の「n型」は「第1の導電型」であり、上記の「p型」は「第2の導電型」であるとする。

本実施例のBJT10では、さらに、層状のp型ベース領域15の表面の一部に形成されたp+型のベースコンタクト領域13と、エミッタ領域12との間において、当該p型ベース領域15の露出表面部分に当該表面部分を覆うようにした層状の再結合抑制領域16とを設けている。再結合抑制領域16の深さはベースコンタクト領域13の深さとほぼ等しい。上記の再結合抑制領域16は、高抵抗の半導体であり「p-」または「n-」である。ベースコンタクト領域13はベース領域15の表面からに接触し、さらに表面より当該ベース領域15の内部に侵入するように形成されている。

上記のBJT10の構造において、図1に示すように、コレクタ領域11の下側表面にはコレクタ電極18が接合され、エミッタ領域12の上側表面にはエミッタ電極19が接合され、ベースコンタクト領域13の上側表面にはベース電極20が接合されている。BJT10の上面において、エミッタ電極19とベース電極20の間における露出表面は、表面保護膜17によって覆われており、これにより保護されている。

図2に示すように、エミッタ電極19およびベース電極20の各々の上側には上層電極21が設けられている。図1において、上層電極21の図示は省略されている。

上記BJT10において、主電流は、エミッタ領域12(またはエミッタ電極19)からコレクタ領域11(またはコレクタ電極18)に流れる電子流である。エミッタ領域12とコレクタ領域11は主電流を流すための主電極用領域である。主電流の通電(オン)と非通電(オフ)は、ベース電極20に印加されるベース電圧、すなわち、ベースコンタクト領域13およびベース領域15とエミッタ領域12との間に加えられる制御信号に基づいて制御される。ベース・エミッタ間の印加電圧が0V以下であるときにはBJT10は主電流が流れず、オフ状態になる。ベース・エミッタ間に一定以上の電圧が印加されると、BJT10は主電流が流れてオン状態に移行する。また、オン状態では、ベース領域15とエミッタ領域12の間に形成されているpn接合が順バイアスされて、ベース領域15からエミッタ領域12に制御電流である正孔電流が流れる。

図3と図4を参照し、従来のBJT構造と本実施例のBJT構造とを対比しながら、BJT10の特徴的構造を説明する。

図3は従来の構造を有するBJT10Aを示す。図3において、上記の図1で説明した要素と同一の要素には同一の符号を付している。BJT10Aの構造では、ベース領域15において、ベースコンタクト領域13とエミッタ領域12との間のSiC表面の近傍領域には多数の再結合準位22が形成されている。このため、エミッタ領域12からコレクタ領域11に向かって流れる主電流I1の一部の電子23と、ベースコンタクト領域13から流れ込む正孔24とが再結合準位22の箇所で再結合する。このような電子23と正孔24との再結合は、ベース領域15と高抵抗層14等との界面でも盛んに発生する。以上の結果、BJT10Aの動作に寄与しない無効なベース電流が流れ、BJT10Aの電流増幅率を低下させる。

従来構造を有するBJT10Aに対して、本実施例のBJT10では、図4に示すように、ベースコンタクト領域13とエミッタ領域12との間で露出するベース領域15の表面およびその近傍部分に層状の再結合抑制領域16が形成される。再結合抑制領域16は「p-」または「n-」の半導体領域で形成されており、電子23または正孔24に対して高い電位障壁を形成するとともに正孔または電子濃度の低い高抵抗層となっているとなっている。この再結合抑制領域16が存在することによって、ベースコンタクト領域13からベース領域15に流れる正孔24は図4中再結合抑制領域16には流れにくく主に表面以外のベース領域15を流れ、エミッタ領域12から流れ込む電子もSiC表面付近は流れにくくなる。その結果、図4に示すように、エミッタ領域12から流れ出す電子23は、正孔と再結合することなく主電流I2としてコレクタ領域11の方向に向かって流れ、BJT10の電流増幅率を向上させることができる。

再結合抑制領域16を形成する際、ベースコンタクト領域13を作る場合と同様に、イオン注入法を用いる。この場合、ベースコンタクト領域13を作るときのイオン注入に比較して注入濃度が極めて低く、イオン注入に要するエネルギも低い。そのため再結合抑制領域16を形成するためのイオン注入では再結合準位の密度を低く抑えることができる。

ここで、第1実施例のBJT10の各高抵抗層等の不純物濃度および寸法について具体的な一例を説明する。

BJT10は、例えば阻止電圧600Vを目標に設計されている。基板の部分には、(0001)面から8度オフさせた低抵抗のn型4H-SiC基板を使用している。BJT10において、当該基板部分がコレクタ領域11となる。基板上のn型高抵抗層14は、エミッタ・コレクタ間に加わる高電圧を阻止するための層である。本実施例では、高抵抗層14は、600V以上の電圧を阻止するように、例えば、厚み10μm、不純物濃度1×1016cm-3に設定されている。高抵抗層14上のp型のベース領域15は、エミッタ・コレクタ間に高電圧が印加されたときに、空乏化しないようにその厚みと不純物濃度が設定されている。本実施形態では、p型ベース領域15は、厚み0.2~0.5μm、不純物濃度4×1017~2×1018cm-3程度が用いられる。ベース領域15上には、厚さ0.5~2.0μm、不純物濃度1~5×1019cm-3の低抵抗のn型エミッタ領域12が設けられている。エミッタ領域12の周囲には、低抵抗のベースコンタクト領域13が形成されている。図2に示すように、エミッタ領域12の平面形状は、細長い島状の形状である。1つのBJT10に複数のエミッタ領域12を備えている。1つのエミッタ領域12の寸法は、幅3~10μm、長さ100~1000μm程度である。ベースコンタクト領域13とエミッタ領域12を含めた単位構造の周期は約10~30μmである。

次に、図5,6A,6Bを参照してBJT10の製造方法を説明する。図5は製造方法の各プロセスを示すフローチャートである。図6Aと図6Bは各プロセスで製作される構造を示す縦断面図である。

BJT10の製造方法は、次のプロセス(1)~(10)(ステップS11~S20)から成っている。図5に示されるようにステップS11からステップS20に到る順序で各プロセスが実行される。

(1)高抵抗層形成プロセス(ステップS11)

(2)ベース領域形成プロセス(ステップS12)

(3)低抵抗層形成プロセス(ステップS13)

(4)エミッタエッチングプロセス(ステップS14)

(5)再結合抑制領域形成プロセス(ステップS15)

(6)ベースコンタクト領域形成プロセス(ステップ16)

(7)イオン注入層活性化プロセス(ステップS17)

(8)表面保護膜形成プロセス(ステップS18)

(9)電極形成プロセス(ステップS19)

(10)上層電極形成プロセス(ステップS20)

(2)ベース領域形成プロセス(ステップS12)

(3)低抵抗層形成プロセス(ステップS13)

(4)エミッタエッチングプロセス(ステップS14)

(5)再結合抑制領域形成プロセス(ステップS15)

(6)ベースコンタクト領域形成プロセス(ステップ16)

(7)イオン注入層活性化プロセス(ステップS17)

(8)表面保護膜形成プロセス(ステップS18)

(9)電極形成プロセス(ステップS19)

(10)上層電極形成プロセス(ステップS20)

上記のステップS11~S13を実施することによって図6Aの(a)に示される構造が形成される。

n型高抵抗層形成プロセス(ステップS11)では、SiCで形成されたn型基板40の上に、エピタキシャル成長法により、厚さ10μmで、濃度1×1016cm-3の窒素を不純物としてドープした高抵抗層41を成長させる。基板40には「4H-SiC(0001)8°off」が用いられている。また基板40は、前述したn型低抵抗層のコレクタ領域11となる。

ベース領域形成プロセス(ステップS12)では、n型高抵抗層41の上に、エピタキシャル成長法により、アルミニウム(Al)を不純物として4×1017~2×1018cm-3の濃度で0.2~0.5μmのp型のベース領域42を成長させる。

低抵抗層形成プロセス(ステップS13)では、n型のベース領域42の上に、エピタキシャル成長法により、厚さ0.5~2.0μmで濃度1~5×1019cm-3の窒素を不純物としてドープしたn型の低抵抗層43を成長させる。この低抵抗層43は、前述したエミッタ領域12を形成する部分である。

次のエミッタエッチングプロセス(ステップS14)では、図6Aの(a)に示された構造において、その上面に、CVD法によりシリコン酸化膜51を堆積させ、フォトリソグラフィーを行い、その後にRIEによりシリコン酸化膜51をエッチングする。こうしてマスクが形成される。このシリコン酸化膜51を用いて、その後、RIEにより低抵抗層43についてSiCエッチングを行い、低抵抗層43を利用して前述したエミッタ領域12を形成する。SiCエッチングのRIEにはSF6ガスなどが用いられる。その結果得られた構造を図6Aの(b)に示す。

再結合抑制領域を形成するプロセス(ステップS15)では、さらに図6Aの(c)に示されるように、図6A(b)に示したマスク51をそのまま利用して再結合抑制領域16を形成する。再結合抑制領域16の形成は、不純物(イオン種)として窒素のイオン注入を行うことにより行われる。エミッタエッチングプロセス(ステップS15)によりエッチングされたすべての領域にイオン注入がなされる。再結合抑制領域の特性を抵抗率の高い「p-」または[n-]にするために、イオン注入量はベース領域42の不純物濃度と同程度かその前後の値に設定される。例えばベース領域42の不純物濃度が4×1017cm-3であればイオン注入量は3~5×1017cm-3程度が望ましい。また再結合抑制領域16は表面の極近傍の再結合準位を含めば良いので、その深さは0.1~0.2μm程度で良い。そのため注入エネルギーを100keV程度に低く抑えることができ、イオン注入プロセスでの結晶欠陥の生成を抑制することができる。

ベースコンタクト領域形成プロセス(ステップS16)では、最初に、図6A(d)に示すように、ベースコンタクト領域13を形成するための表面部分が露出するようにマスク52が形成される。マスク52は、CVD法によりシリコン酸化膜を堆積し、フォトリソグラフィーを行い、その後にRIEによりシリコン酸化膜をエッチングすることにより形成される。その後、イオン注入を行ってベースコンタクト領域13を形成する。注入されるイオンはアルミニウム(Al)であり、注入の深さは例えば0.2μmである。イオン注入量は1×1018~1020cm-3であり、イオン注入に必要なエネルギはほぼ200KeVである。

上記のステップS15,S16によってベースコンタクト領域13とエミッタ領域12の間におけるベース領域15の表面には再結合抑制領域16が形成される。再結合抑制領域16を設けることはエミッタ領域12から到来する電子を再結合抑制領域16のSiC表面から遠ざけることが目的である。

次に、イオン注入層を活性化するプロセス(ステップS17)では、イオン注入後に、注入イオンを半導体中で電気的に活性化すると共に、イオン注入で発生した結晶欠陥を消すための熱処理を行う(図6B(e))。この活性化の熱処理では、ベースコンタクト領域13の注入イオンと再結合抑制領域16の注入イオンの両方の活性化を同時に行っている。高周波熱処理炉などを用い、1700~1800℃程度の高温下で約10分程度の熱処理を行う。雰囲気ガスには例えばアルゴンガス(Ar)が用いられる。

表面保護膜を形成するプロセス(ステップS18)では、図6B(f)で示すように、初めに、イオン注入工程と活性化工程で生じた表面層を取り除くために、熱酸化後に酸化膜を取り除く犠牲酸化を行う。酸化条件は、例えばドライ酸素中で1100℃、20時間などである。酸化膜の除去にはフッ化水素酸を用いる。犠牲酸化後に再び熱酸化を行い酸化膜53を形成する。熱酸化膜形成では、例えば、温度が1100℃、時間が5時間、雰囲気はウェットである。その後に、SiC酸化膜界面の不純物準位を低減するための熱処理(POA:Post Oxidation Anneal)を行う。POAは、水素や酸化窒素(NO、N2O)またはアルゴン雰囲気中で、800~1300℃程度の高温下で、10~30分程度、行う。POA後、CVD酸化膜やCVD窒化膜を形成する。

電極を形成するプロセス(ステップS19)では、エミッタ領域12(低抵抗層43)、ベースコンタクト領域13、コレクタ領域11(基板40)の各々の表面にエミッタ電極19、ベース電極20、コレクタ電極18を形成する(図6B(g))。残った上記の酸化膜53が前述した表面保護膜17になる。エミッタ電極19、コレクタ電極18にはニッケルやチタンを用い、ベース電極20にはチタンやアルミニウムなどを用いる。各電極18,19,20は、蒸着やスパッタリングなどで形成する。電極パターンの形成には、ドライエッチング、ウェットエッチング、リフトオフ法などが利用される。

電極18~20を形成した後には、金属部分と半導体部分との間の接触抵抗を低減するために熱処理を行う。当該熱処理の条件は、温度条件が800~1000℃、時間条件が10~30分程度である。

最後に上層電極形成プロセス(ステップS20)が実行される。この上層電極形成工程(ステップS20)では、分離されている複数のエミッタ電極19を1つの電極に取り出すための上層電極54を形成する(図6B(h))。CVD法によりシリコン酸化膜などを層間膜55として形成した後、フォトリソグラフィーとエッチングによりエミッタ電極19の部分のシリコン酸化膜などを取り除く。こうしてエミッタ電極19を露出させた後に、上層電極54を堆積させる。上層電極54の材料には例えばアルミニウム(Al)を用いる。

このようにして、図1と図2で示したBJT10が作製される。当該BJT10は、ノーマリオフ特性を有する高性能の半導体装置である。

上記第1実施例において、コレクタ領域、エミッタ領域、高抵抗層、ベース領域、ベースコンタクト領域、再結合抑制領域等の第1および第2の導電型の組合せをすべて逆にして構成することもできる。この点については、以下に説明する他の実施例においても同様である。

<第2実施例>

図7と図8を参照して本発明によるバイポーラ型半導体装置の第2実施例を説明する。第2実施例のバイポーラ型半導体装置も同様にBJTである。図7において、図1で説明した要素と実質的に同一の要素には同一の符号を付している。

図7と図8を参照して本発明によるバイポーラ型半導体装置の第2実施例を説明する。第2実施例のバイポーラ型半導体装置も同様にBJTである。図7において、図1で説明した要素と実質的に同一の要素には同一の符号を付している。

図3に示すように、従来構造のBJT10Aではエミッタ領域12をベース領域15の表面が露出するまでエッチングする。このようにエッチングプロセスの精度の限界からベース領域15の一部をエッチングせざるを得ないため、ベース層の厚さが薄くなり、その結果ベースの抵抗値が大きくなる。またエッチング深さのウエハ内またはウエハ間のばらつきにより、ベース抵抗値もウエハ内またはウエハ間でばらつくことになる。さらに、BJTの電流増幅率を向上させるためにはベース層を薄くすることが望ましいが、ベース層を薄くするとエッチングプロセスに起因するベース抵抗の増大や値のばらつきがより顕著になる。

そこで、第2実施例によるBJT100では、層状に形成されたベース領域15において、エッチングにより露出したベース表面の領域に対応する領域に、ベース領域と同等またはそれ以下の抵抗率を有するp型半導体(p+またはp-)からなる低抵抗埋め込み領域61を設けるようにしている。本実施例では、第1実施例のように表面の再結合抑制領域16は形成されない。その他の構造は第1実施例の構造と同じである。

上記の構造によれば、ベースコンタクト領域13からベース領域15に流れ込む正孔電流は、図3で示した従来例では表面付近に流れていたのに対して、図8に示すように抵抗値のより低い低抵抗埋め込み領域61に流れることになる。そのため、ベース領域15の表面付近での再結合が低減され、電流増幅率が向上する。

低抵抗埋め込み領域61はベース領域15に対してより低い抵抗値であるため、ベース領域15の抵抗は低抵抗埋め込み領域61の抵抗値によって決まることになる。これにより上記のエッチングによって生じたベース領域15の高抵抗化とばらつきを低減することができる。

p型のベース領域15の不純物濃度は前述した通り4×1017~2×1018cm-3であるのに対して、低抵抗埋め込み領域61の不純物濃度はベース領域15と同程度以上の濃度とする。例えば、p型のベース領域15の不純物濃度が例えば4×1017cm-3であった場合には、低抵抗埋め込み領域61の不純物濃度を2×1018cm-3とし、かつその厚みをベース領域61の厚みと同じにすると、低抵抗埋め込み領域61の抵抗率はベース領域15の抵抗率に対して1/3に低減できる。

第2実施例のBJT100の製造方法について、特に上記の低抵抗埋め込み領域61は、前述した第1実施例のBJT10の製造方法において、多段のイオン注入法を適用することによって形成することができる。

<第3実施例>

図9と図10を参照して本発明によるバイポーラ型半導体装置の第3実施例を説明する。第3実施例のバイポーラ型半導体装置もBJTである。図9において、図1で説明した要素と実質的に同一の要素には同一の符号を付している。

図9と図10を参照して本発明によるバイポーラ型半導体装置の第3実施例を説明する。第3実施例のバイポーラ型半導体装置もBJTである。図9において、図1で説明した要素と実質的に同一の要素には同一の符号を付している。

図3で説明したように、従来構造のBJT10Aでは、ベース領域15を流れる正孔とコレクタ領域11を流れる電子とが、ベース・コレクタ界面付近で再結合するという特性を有している。

そこで、第3実施例のBJT200では、層状に形成されたベース領域15の下側(高抵抗層14側)において、前述したエッチングにより露出したベース表面の領域に対応する領域で、当該ベース領域15に接した状態でベース領域15よりも高抵抗のp型半導体(p-)からなる高抵抗埋め込み領域または高抵抗層14よりも高抵抗のn型半導体(n-)からなる高抵抗埋め込み領域63を設ける。本実施例では、第1実施例のようにベース表面の再結合抑制領域16は形成されない。その他の構造は第1実施例の構造と同じである。

第3実施例のBJT200の構造では、高抵抗埋め込み領域63を設けることにより、p-層である場合には、その存在で高抵抗埋め込み領域63と高抵抗層14の間に部分的にポテンシャル(電位差)が形成され、当該高抵抗層14の電子がベース領域15から遠ざけられる。また高抵抗埋め込み領域63内の正孔の濃度はベース領域15の正孔濃度よりも低い。このため、従来構造のBJT10Aにおけるベース領域・高抵抗層付近の電子・正孔の濃度と比較して、第3実施例での高抵抗埋め込み領域・高抵抗層付近の電子・正孔濃度が低いために再結合を低減することができ、これにより電流増幅率を向上することができる。またn-層である場合にも、ほぼ同様の原理で再結合を抑制でき電流増幅率を向上することができる。

p型のベース領域15の不純物濃度は前述した通り4×1017~2×1018cm-3であるのに対して、高抵抗埋め込み領域63の不純物濃度はベース領域15と同程度以下の濃度とする。例えば、p型のベース領域15の不純物濃度が例えば4×1017cm-3であった場合には、高抵抗埋め込み領域63の不純物濃度を1×1017cm-3以下とする。

<第4実施例>

図11を参照して本発明によるバイポーラ型半導体装置の第4実施例を説明する。図11において図7や図9で説明した要素と実質的に同一の要素には同一の符号を付している。

図11を参照して本発明によるバイポーラ型半導体装置の第4実施例を説明する。図11において図7や図9で説明した要素と実質的に同一の要素には同一の符号を付している。

第4実施例のBJT300は、第2および第3実施例の特徴的構造を組み合わせて構成される。第4実施例では、低抵抗埋め込み領域61の下面に接するように高抵抗埋め込み領域63が形成されている。その他の構成については、第2または第3実施例の構成と同じである。本実施例のBJT300によっても、前述した同様な効果が発揮される。

<第5実施例>

図12を参照して本発明によるバイポーラ型半導体装置の第5実施例を説明する。図12において図1、図7、図9で説明した要素と実質的に同一の要素には同一の符号を付している。

図12を参照して本発明によるバイポーラ型半導体装置の第5実施例を説明する。図12において図1、図7、図9で説明した要素と実質的に同一の要素には同一の符号を付している。

第5実施例のBJT400は、第1、第2および第3実施例の特徴的構造を組み合わせて構成される。第5実施例では、再結合抑制領域16、低抵抗埋め込み領域61、当該低抵抗埋め込み領域61の下面に接するように形成された高抵抗埋め込み領域63が設けられている。その他の構成については、第1、第2、または第3実施例の構成と同じである。本実施例のBJT400によっても、前述した同様な効果が発揮される。

本実施例においては、製造方法の工程の説明中のpとnの極性を逆にした逆極性タイプのものでも良い。さらに本実施例では、SiCの例について説明したが、本発明は表面再結合が問題となる他の半導体にも適用できる。

以上の各実施例で説明された構成、形状、大きさおよび配置関係については本発明が理解・実施できる程度に概略的に示したものにすぎず、また数値および各構成の組成(材質)等については例示にすぎない。従って本発明は、説明された実施例に限定されるものではなく、請求の範囲に示される技術的思想の範囲を逸脱しない限り様々な形態に変更することができる。

本発明は、4層構造を有する従来の一般的なバイポーラ型炭化珪素半導体装置で、主電流の電子が制御電流の正孔と再結合することを抑制して電流増幅率を向上すること、およびベース層を薄くしてもベース抵抗値の増大やばらつきを改善することに利用され、さらにかかる特性を有するバイポーラ型炭化珪素半導体装置を作製する方法に利用する。

10 バイポーラ型半導体装置(BJT)

11 コレクタ領域

12 エミッタ領域

13 ベースコンタクト領域

14 高抵抗層

15 ベース領域

16 再結合抑制領域

17 表面保護膜

18 コレクタ電極

19 エミッタ電極

20 ベース電極

21 上層電極

40 基板

41 高抵抗層

42 ベース領域

43 低抵抗層

61 低抵抗埋め込み領域

63 高抵抗埋め込み領域

100 BJT

200 BJT

300 BJT

400 BJT

11 コレクタ領域

12 エミッタ領域

13 ベースコンタクト領域

14 高抵抗層

15 ベース領域

16 再結合抑制領域

17 表面保護膜

18 コレクタ電極

19 エミッタ電極

20 ベース電極

21 上層電極

40 基板

41 高抵抗層

42 ベース領域

43 低抵抗層

61 低抵抗埋め込み領域

63 高抵抗埋め込み領域

100 BJT

200 BJT

300 BJT

400 BJT

Claims (12)

- 炭化珪素半導体結晶で作られた基板であるコレクタ領域と、

前記コレクタ領域の上に形成された高抵抗層と、

前記高抵抗層の上に形成されたベース領域と、

低抵抗層からなり、前記ベース領域と接合されるエミッタ領域と、

前記エミッタ領域の周囲に形成され、前記ベース領域に接合する低抵抗のベースコンタクト領域と、

前記ベースコンタクト領域と前記エミッタ領域との間の表面付近に形成され、前記ベース領域と同じ導電型でありかつその抵抗率よりも高い再結合抑制領域、または前記エミッタ領域と同じ導電型でありかつその抵抗率よりも高い再結合抑制領域と、

を備えているバイポーラ型炭化珪素半導体装置。 - 前記コレクタ領域は第1の導電型の低抵抗層であり、前記エミッタ領域は第1の導電型の低抵抗層であり、前記高抵抗層は第1の導電型であり、前記ベース領域は第2の導電型である請求項1に記載のバイポーラ型炭化珪素半導体装置。

- 炭化珪素半導体結晶で作られた基板であるコレクタ領域と、

前記コレクタ領域の上に形成された高抵抗層と、

前記高抵抗層の上に形成されたベース領域と、

低抵抗層からなり、前記ベース領域と接合されるエミッタ領域と、

前記エミッタ領域の周囲に形成され、前記ベース領域に接合する低抵抗のベースコンタクト領域と、

前記ベース領域に形成され、前記ベースコンタクト領域に接すると共に、前記ベース領域と同じ導電型でありかつその抵抗率と同等かまたは当該抵抗率よりも低い埋め込み領域と、

を備えているバイポーラ型炭化珪素半導体装置。 - 前記コレクタ領域は第1の導電型の低抵抗層であり、前記エミッタ領域は第1の導電型の低抵抗層であり、前記高抵抗層は第1の導電型であり、前記ベース領域は第2の導電型である請求項3に記載のバイポーラ型炭化珪素半導体装置。

- 炭化珪素半導体結晶で作られた基板であるコレクタ領域と、

前記コレクタ領域の上に形成された高抵抗層と、

前記高抵抗層の上に形成されたベース領域と、

低抵抗層からなり、前記ベース領域と接合されるエミッタ領域と、

前記エミッタ領域の周囲に形成され、前記ベース領域に接合する低抵抗のベースコンタクト領域と、

前記高抵抗層に形成され、前記ベース領域に接すると共に、前記ベース領域と同じ導電型でありかつその抵抗率よりも高い埋め込み領域、または前記高抵抗領域と同じ導電型でありかつその抵抗率よりも高い埋め込み領域と、

を備えているバイポーラ型炭化珪素半導体装置。 - 前記コレクタ領域は第1の導電型の低抵抗層であり、前記エミッタ領域は第1の導電型の低抵抗層であり、前記高抵抗層は第1の導電型であり、前記ベース領域は第2の導電型である請求項5に記載のバイポーラ型炭化珪素半導体装置。

- 炭化珪素の半導体結晶で作られかつコレクタ領域となる基板の上に高抵抗層を形成する第1の工程と、

前記高抵抗層の上にベース領域を形成する第2の工程と、

前記ベース領域の上に低抵抗層を形成するための第3の工程と、

前記低抵抗層を部分的にエッチングしてエミッタ領域を形成する第4の工程と、

エッチングにより露出した前記ベース領域の表面付近に、前記ベース領域と同じ導電型でありかつその抵抗率よりも高い再結合抑制領域、または前記エミッタ領域と同じ導電型でありかつその抵抗率よりも高い再結合抑制領域を形成する第5の工程と、

前記ベース領域に接合するベースコンタクト領域を形成する第6の工程と、

を含むバイポーラ型炭化珪素半導体装置の製造方法。 - 前記コレクタ領域、前記エミッタ領域、および前記ベースコンタクト領域のそれぞれに、コレクタ電極、エミッタ電極、ベース電極を形成する工程と、

前記エミッタ電極と前記ベース電極の上側に上層電極を形成する工程と、

をさらに含む請求項7に記載のバイポーラ型炭化珪素半導体装置の製造方法。 - 炭化珪素の半導体結晶で作られかつコレクタ領域となる基板の上に高抵抗層を形成する第1の工程と、

前記高抵抗層の上にベース領域を形成する第2の工程と、

前記ベース領域の上に低抵抗層を形成するための第3の工程と、

前記低抵抗層を部分的にエッチングしてエミッタ領域を形成する第4の工程と、

前記ベース領域に、前記ベースコンタクト領域に接すると共に、前記ベース領域と同じ導電型でありかつその抵抗率と同等かまたは当該抵抗率よりも低い埋め込み領域を形成する第5の工程と、

前記ベース領域に接合するベースコンタクト領域を形成する第6の工程と、

を含むバイポーラ型炭化珪素半導体装置の製造方法。 - 前記コレクタ領域、前記エミッタ領域、および前記ベースコンタクト領域のそれぞれに、コレクタ電極、エミッタ電極、ベース電極を形成する工程と、

前記エミッタ電極と前記ベース電極の上側に上層電極を形成する工程と、

をさらに含む請求項9に記載のバイポーラ型炭化珪素半導体装置の製造方法。 - 炭化珪素の半導体結晶で作られかつコレクタ領域となる基板の上に高抵抗層を形成する第1の工程と、

前記高抵抗層の上にベース領域を形成する第2の工程と、

前記ベース領域の上に低抵抗層を形成するための第3の工程と、

前記低抵抗層を部分的にエッチングしてエミッタ領域を形成する第4の工程と、

前記高抵抗層に、前記ベース領域に接すると共に、前記ベース領域と同じ導電型でありかつその抵抗率よりも高い埋め込み領域、または前記期エミッタ領域と同じ導電型でありかつその抵抗率よりも高い埋め込み領域を形成する第5の工程と、

前記ベース領域に接合するベースコンタクト領域を形成する第6の工程と、

を含むことを特徴とするバイポーラ型炭化珪素半導体装置の製造方法。 - 前記コレクタ領域、前記エミッタ領域、および前記ベースコンタクト領域のそれぞれに、コレクタ電極、エミッタ電極、ベース電極を形成する工程と、

前記エミッタ電極と前記ベース電極の上側に上層電極を形成する工程と、

をさらに含む請求項11に記載のバイポーラ型炭化珪素半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010526712A JP5469068B2 (ja) | 2008-08-26 | 2009-08-25 | バイポーラ型炭化珪素半導体装置およびその製造方法 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008217386 | 2008-08-26 | ||

| JP2008-217386 | 2008-08-26 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| WO2010024240A1 true WO2010024240A1 (ja) | 2010-03-04 |

Family

ID=41721408

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| PCT/JP2009/064770 WO2010024240A1 (ja) | 2008-08-26 | 2009-08-25 | バイポーラ型炭化珪素半導体装置およびその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP5469068B2 (ja) |

| WO (1) | WO2010024240A1 (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2012105899A1 (en) * | 2011-01-31 | 2012-08-09 | Fairchild Semiconductor Corporation | Sic bipolar junction transistor with overgrown emitter |

| JP2013041985A (ja) * | 2011-08-16 | 2013-02-28 | Shindengen Electric Mfg Co Ltd | 炭化珪素半導体装置 |

| JP2015018859A (ja) * | 2013-07-09 | 2015-01-29 | 国立大学法人京都大学 | 半導体装置、半導体装置の製造方法および熱処理装置 |

| US9478629B2 (en) | 2010-07-14 | 2016-10-25 | Fairchild Semiconductor Corporation | Conductivity modulation in a silicon carbide bipolar junction transistor |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS645063A (en) * | 1987-06-29 | 1989-01-10 | Toshiba Corp | Hetero-junction bipolar transistor |

| JPH06244195A (ja) * | 1993-02-17 | 1994-09-02 | Sharp Corp | 半導体装置 |

| JP2002359378A (ja) * | 2001-03-28 | 2002-12-13 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP2006351621A (ja) * | 2005-06-13 | 2006-12-28 | Honda Motor Co Ltd | バイポーラ型半導体装置およびその製造方法 |

| JP2007173841A (ja) * | 2005-12-22 | 2007-07-05 | Cree Inc | ベース領域上に炭化ケイ素保護層を有する炭化ケイ素バイポーラ接合トランジスタとその製造方法 |

| JP2007287782A (ja) * | 2006-04-13 | 2007-11-01 | Hitachi Ltd | メサ型バイポーラトランジスタ |

| JP2009054931A (ja) * | 2007-08-29 | 2009-03-12 | Hitachi Ltd | バイポーラ素子及びその製造方法 |

-

2009

- 2009-08-25 JP JP2010526712A patent/JP5469068B2/ja not_active Expired - Fee Related

- 2009-08-25 WO PCT/JP2009/064770 patent/WO2010024240A1/ja active Application Filing

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS645063A (en) * | 1987-06-29 | 1989-01-10 | Toshiba Corp | Hetero-junction bipolar transistor |

| JPH06244195A (ja) * | 1993-02-17 | 1994-09-02 | Sharp Corp | 半導体装置 |

| JP2002359378A (ja) * | 2001-03-28 | 2002-12-13 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP2006351621A (ja) * | 2005-06-13 | 2006-12-28 | Honda Motor Co Ltd | バイポーラ型半導体装置およびその製造方法 |

| JP2007173841A (ja) * | 2005-12-22 | 2007-07-05 | Cree Inc | ベース領域上に炭化ケイ素保護層を有する炭化ケイ素バイポーラ接合トランジスタとその製造方法 |

| JP2007287782A (ja) * | 2006-04-13 | 2007-11-01 | Hitachi Ltd | メサ型バイポーラトランジスタ |

| JP2009054931A (ja) * | 2007-08-29 | 2009-03-12 | Hitachi Ltd | バイポーラ素子及びその製造方法 |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9478629B2 (en) | 2010-07-14 | 2016-10-25 | Fairchild Semiconductor Corporation | Conductivity modulation in a silicon carbide bipolar junction transistor |

| WO2012105899A1 (en) * | 2011-01-31 | 2012-08-09 | Fairchild Semiconductor Corporation | Sic bipolar junction transistor with overgrown emitter |

| WO2012104322A1 (en) * | 2011-01-31 | 2012-08-09 | Fairchild Semiconductor Corporation | Silicon carbide bipolar junction transistor comprising shielding regions and method of manufacturing the same |

| US8785945B2 (en) | 2011-01-31 | 2014-07-22 | Fairchild Semiconductor Corporation | SiC bipolar junction transistor with overgrown emitter |

| US9515176B2 (en) | 2011-01-31 | 2016-12-06 | Fairchild Semiconductor Corporation | Silicon carbide bipolar junction transistor including shielding regions |

| JP2013041985A (ja) * | 2011-08-16 | 2013-02-28 | Shindengen Electric Mfg Co Ltd | 炭化珪素半導体装置 |

| JP2015018859A (ja) * | 2013-07-09 | 2015-01-29 | 国立大学法人京都大学 | 半導体装置、半導体装置の製造方法および熱処理装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JPWO2010024240A1 (ja) | 2012-01-26 |

| JP5469068B2 (ja) | 2014-04-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4777699B2 (ja) | バイポーラ型半導体装置およびその製造方法 | |

| JP5961865B2 (ja) | 半導体素子 | |

| JP4751308B2 (ja) | 横型接合型電界効果トランジスタ | |

| US8846531B2 (en) | Method of manufacturing an ohmic electrode containing titanium, aluminum and silicon on a silicon carbide surface | |

| JP2011044688A (ja) | 半導体装置および半導体装置の製造方法 | |

| JP2018206873A (ja) | 炭化珪素半導体装置および炭化珪素半導体装置の製造方法 | |

| JP2015115373A (ja) | 半導体装置および半導体装置の製造方法 | |

| JP2017092355A (ja) | 半導体装置および半導体装置の製造方法 | |

| WO2010024243A1 (ja) | バイポーラ型半導体装置およびその製造方法 | |

| JP2012160485A (ja) | 半導体装置とその製造方法 | |

| JP5469068B2 (ja) | バイポーラ型炭化珪素半導体装置およびその製造方法 | |

| JP2009043880A (ja) | 炭化珪素半導体装置の製造方法および炭化珪素半導体装置 | |

| JP2013058668A (ja) | 半導体素子及びその製造方法 | |

| JP5470254B2 (ja) | 接合型半導体装置およびその製造方法 | |

| US20110095398A1 (en) | Bipolar semiconductor device and method of producing same | |

| WO2015111177A1 (ja) | 半導体装置,パワーモジュール,電力変換装置,および鉄道車両 | |

| JP2006269679A (ja) | 接合型半導体装置の製造方法 | |

| JP3856729B2 (ja) | 半導体装置およびその製造方法 | |

| JP2017199926A (ja) | 半導体装置および半導体装置の製造方法 | |

| JP2016058660A (ja) | 半導体装置 | |

| JP5514726B2 (ja) | 接合型半導体装置およびその製造方法 | |

| JP2005033030A (ja) | 半導体装置及びその製造方法 | |

| JP6233537B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| JP2019165245A (ja) | 半導体装置 | |

| JP6183234B2 (ja) | 半導体装置および半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| 121 | Ep: the epo has been informed by wipo that ep was designated in this application |

Ref document number: 09809891 Country of ref document: EP Kind code of ref document: A1 |

|

| WWE | Wipo information: entry into national phase |

Ref document number: 2010526712 Country of ref document: JP |

|

| NENP | Non-entry into the national phase |

Ref country code: DE |

|

| 122 | Ep: pct application non-entry in european phase |

Ref document number: 09809891 Country of ref document: EP Kind code of ref document: A1 |