TWI739252B - Trench mosfet and manufacturing method of the same - Google Patents

Trench mosfet and manufacturing method of the same Download PDFInfo

- Publication number

- TWI739252B TWI739252B TW108147542A TW108147542A TWI739252B TW I739252 B TWI739252 B TW I739252B TW 108147542 A TW108147542 A TW 108147542A TW 108147542 A TW108147542 A TW 108147542A TW I739252 B TWI739252 B TW I739252B

- Authority

- TW

- Taiwan

- Prior art keywords

- region

- doping concentration

- epitaxial layer

- trench

- conductivity type

- Prior art date

Links

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 18

- 210000000746 body region Anatomy 0.000 claims abstract description 33

- 239000000758 substrate Substances 0.000 claims abstract description 19

- 239000002019 doping agent Substances 0.000 claims description 25

- 238000002513 implantation Methods 0.000 claims description 10

- 238000000034 method Methods 0.000 claims description 8

- 230000015556 catabolic process Effects 0.000 claims description 6

- 239000004020 conductor Substances 0.000 claims description 4

- 239000012535 impurity Substances 0.000 claims description 4

- 238000000151 deposition Methods 0.000 claims description 3

- 238000012545 processing Methods 0.000 claims description 3

- 238000009826 distribution Methods 0.000 description 13

- 238000010586 diagram Methods 0.000 description 7

- 239000004065 semiconductor Substances 0.000 description 4

- 230000003071 parasitic effect Effects 0.000 description 3

- 239000007943 implant Substances 0.000 description 2

- 230000007423 decrease Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000000407 epitaxy Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 230000001939 inductive effect Effects 0.000 description 1

- 230000007774 longterm Effects 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/1095—Body region, i.e. base region, of DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/107—Substrate region of field-effect devices

- H01L29/1075—Substrate region of field-effect devices of field-effect transistors

- H01L29/1079—Substrate region of field-effect devices of field-effect transistors with insulated gate

- H01L29/1083—Substrate region of field-effect devices of field-effect transistors with insulated gate with an inactive supplementary region, e.g. for preventing punch-through, improving capacity effect or leakage current

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7827—Vertical transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/22—Diffusion of impurity materials, e.g. doping materials, electrode materials, into or out of a semiconductor body, or between semiconductor regions; Interactions between two or more impurities; Redistribution of impurities

- H01L21/225—Diffusion of impurity materials, e.g. doping materials, electrode materials, into or out of a semiconductor body, or between semiconductor regions; Interactions between two or more impurities; Redistribution of impurities using diffusion into or out of a solid from or into a solid phase, e.g. a doped oxide layer

- H01L21/2251—Diffusion into or out of group IV semiconductors

- H01L21/2252—Diffusion into or out of group IV semiconductors using predeposition of impurities into the semiconductor surface, e.g. from a gaseous phase

- H01L21/2253—Diffusion into or out of group IV semiconductors using predeposition of impurities into the semiconductor surface, e.g. from a gaseous phase by ion implantation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/26506—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors

- H01L21/26513—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors of electrically active species

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/324—Thermal treatment for modifying the properties of semiconductor bodies, e.g. annealing, sintering

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0607—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration

- H01L29/0611—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices

- H01L29/0615—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0607—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration

- H01L29/0611—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices

- H01L29/0615—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE]

- H01L29/0619—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE] with a supplementary region doped oppositely to or in rectifying contact with the semiconductor containing or contacting region, e.g. guard rings with PN or Schottky junction

- H01L29/0623—Buried supplementary region, e.g. buried guard ring

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0684—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape, relative sizes or dispositions of the semiconductor regions or junctions between the regions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66537—Unipolar field-effect transistors with an insulated gate, i.e. MISFET using a self aligned punch through stopper or threshold implant under the gate region

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66666—Vertical transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66674—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/66712—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/66734—Vertical DMOS transistors, i.e. VDMOS transistors with a step of recessing the gate electrode, e.g. to form a trench gate electrode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7813—Vertical DMOS transistors, i.e. VDMOS transistors with trench gate electrode, e.g. UMOS transistors

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Ceramic Engineering (AREA)

- Manufacturing & Machinery (AREA)

- High Energy & Nuclear Physics (AREA)

- Health & Medical Sciences (AREA)

- Toxicology (AREA)

- Electrodes Of Semiconductors (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Abstract

Description

本發明是有關於一種功率半導體元件,且特別是有關於一種溝槽式金氧半導體場效電晶體(MOSFET)元件及其製造方法。 The present invention relates to a power semiconductor device, and more particularly to a trench metal oxide semiconductor field effect transistor (MOSFET) device and a manufacturing method thereof.

在功率半導體元件中,垂直設置於溝槽的功率半導體元件因為能大幅增加單元密度,所以已成為各界發展的重點之一。 Among the power semiconductor components, the power semiconductor components vertically arranged in the trenches have become one of the focuses of development in all walks of life because they can greatly increase the cell density.

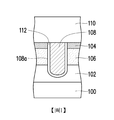

圖1是習知的一種溝槽式MOSFET元件的示意圖。在圖1中,基板100上的磊晶層102內有源極區104和本體(body)區106,而溝槽式閘極108則是設置於磊晶層102中,內層介電層(ILD)110覆蓋磊晶層102與溝槽式閘極108。另外,溝槽式閘極108表面會有閘氧化層112。

FIG. 1 is a schematic diagram of a conventional trench MOSFET device. In FIG. 1, the

圖2是沿著圖1的溝槽式閘極結構108的側壁108a的摻雜濃度曲線圖,其中顯示源極區104和本體區106之間的摻雜濃度分佈平緩,而使本體電阻(body resistance)變高。一旦本體電阻變高,將容易造成寄生N(源極104)-P(本體106)-N(磊晶層102)雙極性電晶體導通,MOSFET發生二次崩潰(Secondary

breakdown),使得元件溫度上升,造成元件永久損傷,即非箝制電感切換(Unclamped Inductive Switching,UIS)的性能變差。

2 is a graph showing the doping concentration along the

本發明提供一種溝槽式MOSFET元件,其本體與源極之間設有特定摻雜濃度範圍的抗擊穿摻雜區(anti-punch through region),能降低本體電阻率,藉此改善溝槽式MOSFET元件的UIS能力。 The present invention provides a trench-type MOSFET device, which is provided with an anti-punch through region with a specific doping concentration range between the body and the source, which can reduce the body resistivity, thereby improving the trench-type UIS capability of MOSFET components.

本發明另提供一種溝槽式MOSFET元件的製造方法,可使本體與源極之間產生高摻雜濃度區域,以降低本體電阻率(RS_Body),以抑制寄生雙極性電晶體開啟。 The present invention also provides a method for manufacturing a trench MOSFET device, which can generate a high doping concentration region between the body and the source, so as to reduce the body resistivity (R S_Body ) to prevent the parasitic bipolar transistor from turning on.

本發明的溝槽式MOSFET元件,包括基板、具有第一導電型的磊晶層、閘極、閘氧化層、具有第一導電型的源極區、具有第二導電型的本體區與具有第二導電型的抗擊穿摻雜區。磊晶層係形成於基板上。磊晶層則具有溝槽,閘極位於所述溝槽內,閘氧化層位於閘極與溝槽之間。源極區是位於溝槽兩側的磊晶層的表面,本體區是位於源極區下方的部分磊晶層內,且抗擊穿摻雜區是位於本體區與源極區的界面,其中所述抗擊穿摻雜區的摻雜濃度高於本體區的摻雜濃度。所述磊晶層具有接近源極區的一個第一pn接面(pn junction)及接近基板的一個第二pn接面,且以第一pn接面與第二pn接面之間劃分為N等分的N個區域,N是大於1的整數。所述N個區域內的摻雜濃度愈接近第一pn接面愈 大。所述N個區域分別具有一摻雜濃度對於磊晶層深度之積分面積,且所述N個區域中愈接近第一pn接面的區域的摻雜濃度對於磊晶層深度之積分面積愈大。 The trench MOSFET device of the present invention includes a substrate, an epitaxial layer having a first conductivity type, a gate electrode, a gate oxide layer, a source region having a first conductivity type, a body region having a second conductivity type, and a body region having a first conductivity type. Two conductivity type anti-breakdown doped regions. The epitaxial layer is formed on the substrate. The epitaxial layer has a trench, the gate is located in the trench, and the gate oxide layer is located between the gate and the trench. The source region is the surface of the epitaxial layer located on both sides of the trench, the body region is located in the part of the epitaxial layer below the source region, and the anti-breakdown doped region is located at the interface between the body region and the source region. The doping concentration of the anti-breakdown doped region is higher than the doping concentration of the body region. The epitaxial layer has a first pn junction (pn junction) close to the source region and a second pn junction close to the substrate, and the first pn junction and the second pn junction are divided into N N equally divided regions, where N is an integer greater than 1. The doping concentration in the N regions is closer to the first pn junction, the more Big. Each of the N regions has an integrated area of doping concentration for the depth of the epitaxial layer, and the region closer to the first pn junction among the N regions has a larger integrated area for the depth of the epitaxial layer. .

在本發明的一實施例中,上述N為2,且所述N個區域包括接近第一pn接面的第一區域與接近第二pn接面的第二區域,所述第一區域內的摻雜濃度均大於所述第二區域內的摻雜濃度,所述第一區域的所述摻雜濃度對於磊晶層深度之積分面積大於所述第二區域的所述摻雜濃度對於磊晶層深度之積分面積。 In an embodiment of the present invention, the above N is 2, and the N regions include a first region close to the first pn junction and a second region close to the second pn junction. The doping concentration is greater than the doping concentration in the second region, and the integrated area of the doping concentration in the first region with respect to the depth of the epitaxial layer is greater than the doping concentration in the second region with respect to the epitaxial layer. The integral area of the layer depth.

在本發明的一實施例中,上述N為3,且所述N個區域包括接近第一pn接面的第一區域、接近第二pn接面的第三區域與介於第一區域與第三區域之間的第二區域,所述第一區域內的摻雜濃度均大於所述第二區域內的摻雜濃度、所述第二區域內的摻雜濃度均大於所述第三區域內的摻雜濃度,且所述第一區域的所述摻雜濃度對於磊晶層深度之積分面積大於所述第二區域的所述摻雜濃度對於磊晶層深度之積分面積,所述第二區域的所述摻雜濃度對於磊晶層深度之積分面積大於所述第三區域的所述摻雜濃度對於磊晶層深度之積分面積。 In an embodiment of the present invention, the above N is 3, and the N regions include a first region close to the first pn junction, a third region close to the second pn junction, and between the first region and the first region. In the second region between the three regions, the doping concentration in the first region is all greater than the doping concentration in the second region, and the doping concentration in the second region is all greater than that in the third region And the integrated area of the doping concentration of the first region with respect to the depth of the epitaxial layer is greater than the integrated area of the doping concentration of the second region with respect to the depth of the epitaxial layer, the second The integrated area of the doping concentration of the region with respect to the depth of the epitaxial layer is greater than the integrated area of the doping concentration of the third region with respect to the depth of the epitaxial layer.

本發明的溝槽式MOSFET元件的製造方法,包括在一基板上的具有第一導電型的磊晶層內形成溝槽式閘極;以植入劑量往所述基板的方向逐漸減少的方式,對所述磊晶層進行多道植入具有第二導電型的摻雜物的步驟;進行第一驅入(drive-in)步驟,使具有所述第二導電型的所述摻雜物在所述磊晶層的上半部擴 散,形成具有所述第二導電型的本體區;在所述磊晶層的表面植入具有所述第一導電型的摻雜物;進行第二驅入步驟,使具有所述第一導電型的所述摻雜物擴散形成源極區;以及在形成所述源極區之後,在本體區與源極區的界面全面地植入具有第二導電型的摻雜物,以形成一抗擊穿摻雜區,其中所述抗擊穿摻雜區的摻雜濃度高於所述本體區的摻雜濃度。 The manufacturing method of the trench MOSFET device of the present invention includes forming a trench gate in an epitaxial layer with a first conductivity type on a substrate; and the implant dose is gradually reduced toward the substrate. A step of implanting a dopant having the second conductivity type in multiple passes is performed on the epitaxial layer; a first drive-in step is performed to make the dopant having the second conductivity type in The upper half of the epitaxial layer is expanded Dispersing, forming a body region with the second conductivity type; implanting dopants with the first conductivity type on the surface of the epitaxial layer; Type the dopant diffuses to form a source region; and after forming the source region, a dopant with the second conductivity type is implanted in the interface between the body region and the source region to form a resist The penetration doping region, wherein the doping concentration of the anti-breakdown doping region is higher than the doping concentration of the body region.

在本發明的另一實施例中,上述進行多道植入具有第二導電型的摻雜物的步驟包括兩道或三道植入步驟。 In another embodiment of the present invention, the above-mentioned step of multiple implantation of the dopant having the second conductivity type includes two or three implantation steps.

在本發明的另一實施例中,上述植入具有第一導電型的摻雜物的能量例如在20KeV~45KeV之間。 In another embodiment of the present invention, the energy for implanting the dopant having the first conductivity type is, for example, between 20 KeV and 45 KeV.

在本發明的另一實施例中,上述第二驅入步驟包括快速熱處理(RTP)。 In another embodiment of the present invention, the above-mentioned second drive-in step includes rapid thermal processing (RTP).

在本發明的另一實施例中,形成上述溝槽式閘極的步驟包括:在上述磊晶層先形成溝槽,在所述溝槽的表面形成閘氧化層,再在上述溝槽內沉積導體作為閘極。 In another embodiment of the present invention, the step of forming the trench gate includes: first forming a trench in the epitaxial layer, forming a gate oxide layer on the surface of the trench, and then depositing the trench in the trench The conductor acts as a gate.

在本發明的各個實施例中,上述抗擊穿摻雜區的摻雜濃度介於5E+16原子/cm3~5E+17原子/cm3。 In various embodiments of the present invention, the doping concentration of the anti-breakdown doped region ranges from 5E+16 atoms/cm 3 to 5E+17 atoms/cm 3 .

在本發明的各個實施例中,上述第一導電型為N型,上述第二導電型為P型。 In various embodiments of the present invention, the first conductivity type is N-type, and the second conductivity type is P-type.

在本發明的各個實施例中,上述第一導電型為P型,上述第二導電型為N型。 In each embodiment of the present invention, the first conductivity type is P type, and the second conductivity type is N type.

基於上述,本發明藉由本體與源極之間形成的抗擊穿摻 雜區,使該處具有陡峭的濃度分佈並因而降低本體電阻率,以抑制寄生雙極性電晶體開啟,改善溝槽式MOSFET元件的UIS能力。 Based on the above, the present invention uses the anti-breakdown doping formed between the body and the source. The impurity area has a steep concentration distribution there and thus reduces the body resistivity, so as to prevent the parasitic bipolar transistor from turning on and improve the UIS capability of the trench MOSFET device.

為讓本發明的上述特徵和優點能更明顯易懂,下文特舉實施例,並配合所附圖式作詳細說明如下。 In order to make the above-mentioned features and advantages of the present invention more comprehensible, the following specific embodiments are described in detail in conjunction with the accompanying drawings.

100、300:基板 100, 300: substrate

102、302:磊晶層 102, 302: epitaxial layer

104、304:源極區 104, 304: source region

106、306:本體區 106, 306: body area

108:溝槽式閘極 108: grooved gate

108a:側壁 108a: sidewall

110、316:內層介電層 110, 316: inner dielectric layer

112、310:閘氧化層 112, 310: gate oxide layer

302a:表面 302a: Surface

308:閘極 308: Gate

312:抗擊穿摻雜區 312: Anti-breakdown doped region

314:溝槽 314: Groove

400a:第一pn接面 400a: first pn junction

400b:第二pn接面 400b: second pn junction

404a、500a:第一區域 404a, 500a: the first area

404b、500b:第二區域 404b, 500b: second area

500c:第三區域 500c: third area

S600、S602、S604、S606、S608、S610:步驟 S600, S602, S604, S606, S608, S610: steps

圖1是習知的一種溝槽式MOSFET元件的示意圖。 FIG. 1 is a schematic diagram of a conventional trench MOSFET device.

圖2是沿著圖1的溝槽式閘極結構的側壁的摻雜濃度曲線圖 FIG. 2 is a graph of doping concentration along the sidewall of the trench gate structure of FIG. 1

圖3是依照本發明的第一實施例的一種溝槽式MOSFET元件的示意圖。 FIG. 3 is a schematic diagram of a trench MOSFET device according to the first embodiment of the present invention.

圖4是沿著圖3的溝槽式閘極結構的側壁的一種摻雜濃度曲線圖。 FIG. 4 is a graph of a doping concentration along the sidewall of the trench gate structure of FIG. 3.

圖5是沿著圖3的溝槽式閘極結構的側壁的另一種摻雜濃度曲線圖。 FIG. 5 is another graph of doping concentration along the sidewall of the trench gate structure of FIG. 3.

圖6是依照本發明的第二實施例的一種溝槽式MOSFET元件的製造流程步驟圖。 6 is a step diagram of a manufacturing process of a trench MOSFET device according to a second embodiment of the present invention.

以下揭示內容提供許多不同的實施方式或範例,用於實施本發明的不同特徵。當然這些實施例僅為範例,並非用於限制本發明的範圍與應用。再者,為了清楚起見,各個構件、膜層或 區域的相對厚度及位置可能縮小或放大。另外,在各圖式中使用相似或相同的元件符號來標示相似或相同元件或特徵,且圖式中如有與前一圖相同的元件符號,則將省略其贅述。 The following disclosure provides many different implementations or examples for implementing different features of the present invention. Of course, these embodiments are only examples, and are not intended to limit the scope and application of the present invention. Furthermore, for the sake of clarity, each member, layer or The relative thickness and location of the area may be reduced or enlarged. In addition, similar or identical element symbols are used in the various drawings to indicate similar or identical elements or features, and if there are elements in the drawings that are the same as the previous figure, their description will be omitted.

圖3是依照本發明的第一實施例的一種溝槽式MOSFET元件的示意圖。 FIG. 3 is a schematic diagram of a trench MOSFET device according to the first embodiment of the present invention.

請參照圖3,第一實施例的溝槽式MOSFET元件包括基板300、具有第一導電型的磊晶層302、具有第一導電型的源極區304、具有第二導電型的本體區306、閘極308、閘氧化層310與具有第二導電型的抗擊穿摻雜區312。在本實施例中,第一導電型為N型,第二導電型為P型。但是本發明並不限於此,於另一實施例中,第一導電型可為P型,第二導電型可為N型。磊晶層302係形成於基板300上,且磊晶層302具有溝槽314。雖然圖3只顯示一個溝槽314,但是應知用於功率裝置的溝槽式MOSFET元件實際上具有多個溝槽314。

3, the trench MOSFET device of the first embodiment includes a

請繼續參照圖3,閘極308位於溝槽314內,且閘氧化層310位於閘極308與溝槽314之間。源極區304是位於溝槽314兩側的磊晶層302的表面302a,本體區306則是位於源極區304下方的部分磊晶層302內。一般來說,磊晶層302若是N型磊晶,則源極區304是N+區。抗擊穿摻雜區312則是位於本體區306與源極區304的界面,其中抗擊穿摻雜區312的摻雜濃度需高於本體區306的摻雜濃度。也就是說,相對於本體區306若是P型井區,則抗擊穿摻雜區312是P+區。在一實施例中,抗擊穿摻雜區312的摻雜濃度例如介於5E+16

原子/cm3~5E+17原子/cm3。此外,可形成一內層介電層316覆蓋磊晶層302與閘極308。

Please continue to refer to FIG. 3, the

圖4是沿著圖3的溝槽式閘極結構的側壁的一種摻雜濃度曲線圖。 FIG. 4 is a graph of a doping concentration along the sidewall of the trench gate structure of FIG. 3.

在圖4中,磊晶層具有接近源極區304的一個第一pn接面(pn junction)400a以及接近基板300的一個第二pn接面400b,且以第一pn接面400a與第二pn接面400b之間劃分為2個等分,接近第一pn接面400a的設為第一區域404a、接近第二pn接面400b的設為第二區域404b。然而本發明並不限於此,第一pn接面400a與第二pn接面400b之間可劃分為N等份,N除了2以外也可以是大於1的其他整數。在圖4中,所述第一區域404a內的摻雜濃度均大於第二區域404b內的摻雜濃度,且第一區域404a具有一第一摻雜濃度對於磊晶層深度之積分面積、第二區域404b具有一第二摻雜濃度對於磊晶層深度之積分面積,所述第一摻雜濃度對於磊晶層深度之積分面積大於所述第二摻雜濃度對於磊晶層深度之積分面積。而且位於本體區306與源極區304的界面的抗擊穿摻雜區312具有陡峭的濃度分佈,使得此處的本體電阻率變低,進而改善溝槽式MOSFET元件的UIS能力。也就是說,本發明中的上述區域內的摻雜濃度愈接近第一pn接面400a愈大,愈接近第一pn接面400a的區域的摻雜濃度對於磊晶層深度之積分面積也愈大。關於這樣特別的摻雜濃度分佈的製作方式,將於下文描述。

4, the epitaxial layer has a first pn junction (pn junction) 400a close to the

圖5是圖3的元件的溝槽側壁的另一種摻雜濃度曲線圖,其中使用與圖4相同的元件符號來表示相同或近似的區域,且相同或近似的區域內容也可參照上述,不再贅述。 FIG. 5 is another doping concentration curve diagram of the trench sidewall of the device of FIG. 3, in which the same component symbols as in FIG. 4 are used to denote the same or similar regions, and the content of the same or similar regions can also be referred to above. Go into details again.

在圖5中與圖4不同的地方在於,第一pn接面400a與第二pn接面400b之間劃分為3等分,即包含接近第一pn接面400a的第一區域500a、接近第二pn接面400b的第三區域500c與介於第一區域500a與第三區域500c之間的第二區域500b。第一區域500a內的摻雜濃度均大於第二區域500b內的摻雜濃度、第二區域500b內的摻雜濃度均大於第三區域500c內的摻雜濃度,且第一區域500a的摻雜濃度對於磊晶層深度之積分面積大於第二區域500b的摻雜濃度對於磊晶層深度之積分面積,第二區域500b的摻雜濃度對於磊晶層深度之積分面積大於第三區域500c的摻雜濃度對於磊晶層深度之積分面積。所述摻雜濃度分佈的製作方式,也會於下文描述。

The difference between FIG. 5 and FIG. 4 is that the

圖6是依照本發明的第二實施例的一種溝槽式MOSFET元件的製造流程步驟圖。而且,根據第二實施例的步驟,可製作出如圖4或圖5的的摻雜濃度分佈。 6 is a step diagram of a manufacturing process of a trench MOSFET device according to a second embodiment of the present invention. Moreover, according to the steps of the second embodiment, the doping concentration distribution as shown in FIG. 4 or FIG. 5 can be produced.

請參照圖6,先進行步驟S600,在一基板上的具有第一導電型的磊晶層內形成溝槽式閘極。在本實施例中,上述第一導電型為N型,第二導電型為P型;反之亦然。形成溝槽式閘極的步驟可列舉但不限於:在N型磊晶層先形成溝槽,在溝槽的表面形成閘氧化層,再在溝槽內沉積導體作為閘極,其中所述導體例如多晶矽。 Please refer to FIG. 6, step S600 is first performed to form a trench gate in the epitaxial layer with the first conductivity type on a substrate. In this embodiment, the above-mentioned first conductivity type is N-type, and the second conductivity type is P-type; and vice versa. The steps of forming the trench gate include but are not limited to: first forming a trench in the N-type epitaxial layer, forming a gate oxide layer on the surface of the trench, and then depositing a conductor in the trench as the gate, wherein the conductor For example, polysilicon.

接著,在步驟S602中,以植入劑量往基板的方向逐漸減少的方式,對磊晶層進行多道植入具有第二導電型的摻雜物的步驟;在本實施例中,上述植入步驟可為兩道或三道植入P型的摻雜物的步驟。 Next, in step S602, the epitaxial layer is implanted with the dopant having the second conductivity type in a manner that the implant dose gradually decreases toward the substrate; in this embodiment, the above-mentioned implantation The steps can be two or three steps of implanting P-type dopants.

然後,在步驟S604中,進行第一驅入(drive-in)步驟,使上述P型摻雜物在N型磊晶層的上半部擴散,形成P型本體區。而且,為避免源極區底部趨近平緩的N型濃度與本體區平緩的P型濃度,在第一pn接面處相互抵消彼此的濃度,導致本體區的電阻率增加,本發明的製程藉由降低熱裕度(thermal budget),使本體區的摻雜濃度分佈接近步驟S602的植入步驟後的濃度分佈。舉例來說,若是習知的驅入步驟是高溫長時間的製程(如高於1000℃一小時),則步驟S604則是採取高溫短時間(如高於1000℃ 30分鐘以下)或者採取同時降低溫度與縮短時間(如1000℃以下且短於一小時)的驅入。也就是說,當步驟S602的植入步驟是兩道,則所形成的本體區的雜濃度分佈如圖4所示;另一方面,若是步驟S602的植入步驟是三道,則所形成的本體區的摻雜濃度分佈會如圖5所示。 Then, in step S604, a first drive-in step is performed to diffuse the above-mentioned P-type dopant in the upper half of the N-type epitaxial layer to form a P-type body region. Moreover, in order to avoid the near-flat N-type concentration at the bottom of the source region and the flat P-type concentration in the body region, the concentrations at the first pn junction cancel each other out, resulting in an increase in the resistivity of the body region. The process of the present invention uses By reducing the thermal budget, the doping concentration distribution of the body region is close to the concentration distribution after the implantation step of step S602. For example, if the conventional drive-in step is a high-temperature and long-term process (such as one hour higher than 1000°C), step S604 is to adopt a high-temperature short time (such as higher than 1000°C and less than 30 minutes) or adopt simultaneous reduction Drive in with temperature and shortened time (such as below 1000°C and less than one hour). That is to say, when the implantation steps of step S602 are two, the impurity concentration distribution of the formed body region is shown in FIG. 4; on the other hand, if the implantation steps of step S602 are three, the formed The doping concentration distribution of the body region will be as shown in FIG. 5.

隨後,在步驟S606中,在磊晶層的表面植入具有第一導電型(如N型)的摻雜物。而且,為了後續所形成的源極區具有較陡峭的摻雜濃度分佈,上述植入步驟的能量要比習知形成源極區所進行的植入要低,例如在20KeV~45KeV之間。然而,本發並不限於此。依據溝槽式MOSFET元件的設計準則,上述植入步驟的能量可進行變更。 Subsequently, in step S606, dopants having the first conductivity type (such as N-type) are implanted on the surface of the epitaxial layer. Moreover, in order to have a steeper doping concentration distribution in the source region to be formed later, the energy of the above-mentioned implantation step is lower than that of the conventional implantation for forming the source region, for example, between 20KeV and 45KeV. However, the present invention is not limited to this. According to the design criteria of the trench MOSFET device, the energy of the above-mentioned implantation step can be changed.

之後,在步驟S608中,進行第二驅入步驟,使具有第一導電型(如N型)的摻雜物擴散形成源極區。同樣地,為了使源極區具有較陡峭的摻雜濃度分佈,本發明的製程需進一步降低熱裕度,因此第二驅入步驟的時間要比習知的驅入步驟短,例如在5分鐘以下。舉例來說,第二驅入步驟可採用快速熱處理(RTP)。 After that, in step S608, a second drive-in step is performed to diffuse dopants having the first conductivity type (such as N-type) to form a source region. Similarly, in order to make the source region have a steeper doping concentration distribution, the process of the present invention needs to further reduce the thermal margin. Therefore, the time of the second drive-in step is shorter than that of the conventional drive-in step, for example, in 5 minutes. the following. For example, the second drive-in step may use rapid thermal processing (RTP).

然後,在步驟S608之後再進行步驟S610,在不需要任何光阻遮罩的情況下,在本體區與源極區的界面全面地植入具有第二導電型(如P型)的摻雜物,以形成抗擊穿摻雜區,其中所述抗擊穿摻雜區的摻雜濃度高於本體區的摻雜濃度,且後續將不再進行高溫的驅入步驟,使得本體區與源極區的界面形成陡峭的濃度分佈,如圖4與圖5中第一pn接面400a左側(往源極區304)的直線。在本實施例中,抗擊穿摻雜區的摻雜濃度例如介於5E+16原子/cm3~5E+17原子/cm3。然而,本發並不限於此。根據本體區的摻雜濃度大小,抗擊穿摻雜區的摻雜濃度也可作變更。後續的製程可按照既有技術進行,故不贅述。

Then, step S610 is performed after step S608. Without any photoresist mask, the interface between the body region and the source region is fully implanted with dopants with the second conductivity type (such as P-type) , To form an anti-breakdown doped region, wherein the dopant concentration of the anti-breakdown doped region is higher than that of the body region, and subsequent high-temperature driving steps will not be performed, so that the body region and the source region are The interface forms a steep concentration distribution, such as a straight line on the left side (toward the source region 304) of the

綜上所述,本發明藉由製程的控制在本體與源極之間形成特別的摻雜濃度分佈,而降低本體電阻率,並藉此改善溝槽式MOSFET元件的UIS能力。 In summary, the present invention forms a special doping concentration distribution between the body and the source through the control of the process, thereby reducing the body resistivity and thereby improving the UIS capability of the trench MOSFET device.

雖然本發明已以實施例揭露如上,然其並非用以限定本發明,任何所屬技術領域中具有通常知識者,在不脫離本發明的精神和範圍內,當可作些許的更動與潤飾,故本發明的保護範圍當視後附的申請專利範圍所界定者為準。 Although the present invention has been disclosed in the above embodiments, it is not intended to limit the present invention. Anyone with ordinary knowledge in the relevant technical field can make some changes and modifications without departing from the spirit and scope of the present invention. The protection scope of the present invention shall be subject to those defined by the attached patent application scope.

300:基板 300: substrate

304:源極區 304: source region

306:本體區 306: body area

312:抗擊穿摻雜區 312: Anti-breakdown doped region

400a:第一pn接面 400a: first pn junction

400b:第二pn接面 400b: second pn junction

404a:第一區域 404a: The first area

404b:第二區域 404b: second area

Claims (14)

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| TW108147542A TWI739252B (en) | 2019-12-25 | 2019-12-25 | Trench mosfet and manufacturing method of the same |

| CN202010113782.5A CN113035931B (en) | 2019-12-25 | 2020-02-24 | Trench MOSFET device and method of manufacturing the same |

| US16/830,225 US11588021B2 (en) | 2019-12-25 | 2020-03-25 | Trench MOSFET and manufacturing method of the same |

| US17/377,408 US20210343840A1 (en) | 2019-12-25 | 2021-07-16 | Manufacturing method of trench mosfet |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| TW108147542A TWI739252B (en) | 2019-12-25 | 2019-12-25 | Trench mosfet and manufacturing method of the same |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| TW202125822A TW202125822A (en) | 2021-07-01 |

| TWI739252B true TWI739252B (en) | 2021-09-11 |

Family

ID=76458896

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| TW108147542A TWI739252B (en) | 2019-12-25 | 2019-12-25 | Trench mosfet and manufacturing method of the same |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US11588021B2 (en) |

| CN (1) | CN113035931B (en) |

| TW (1) | TWI739252B (en) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI739252B (en) * | 2019-12-25 | 2021-09-11 | 杰力科技股份有限公司 | Trench mosfet and manufacturing method of the same |

| CN113990928B (en) * | 2021-10-28 | 2023-05-26 | 电子科技大学 | Trench MOSFET device with low breakdown voltage temperature coefficient and preparation method thereof |

| CN115911087A (en) * | 2022-09-08 | 2023-04-04 | 弘大芯源(深圳)半导体有限公司 | SGT-MOSFET (Metal-oxide-semiconductor field Effect transistor) for improving UIS (ultra thin silicon) performance and manufacturing method thereof |

Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20130280870A1 (en) * | 2005-02-11 | 2013-10-24 | Alpha & Omega Semiconductor Limited | Fabrication of mos device with integrated schottky diode in active region contact trench |

| US20140077290A1 (en) * | 2012-09-14 | 2014-03-20 | Fu-Yuan Hsieh | Trench metal oxide semiconductor field effect transistor with embedded schottky rectifier using reduced masks process |

| TW201535719A (en) * | 2014-03-05 | 2015-09-16 | Alpha & Omega Semiconductor | High density trench gate MOSFET array with self-aligned contacts enhancement plug and method |

| TW201611183A (en) * | 2014-09-02 | 2016-03-16 | 萬國半導體股份有限公司 | Power trench MOSFET with mproved UIS performance and preparation method thereof |

| TW201622015A (en) * | 2014-12-10 | 2016-06-16 | 萬國半導體股份有限公司 | Integrating enhancement mode depleted accumulation/inversion channel devices with mosfets and preparing method thereof |

| US20160190309A1 (en) * | 2012-02-02 | 2016-06-30 | Alpha And Omega Semiconductor Incorporated | Nano mosfet with trench bottom oxide shielded and third dimensional p-body contact |

| TW201631739A (en) * | 2015-02-27 | 2016-09-01 | 萬國半導體股份有限公司 | Semiconductor component and method of manufacture |

| TW201843833A (en) * | 2017-01-23 | 2018-12-16 | 大陸商矽力杰半導體技術(杭州)有限公司 | Semiconductor device and method for manufacturing the same |

| TW201909419A (en) * | 2017-04-26 | 2019-03-01 | 澳門商萬民半導體 (澳門) 有限公司 | Scalable SGT structure with improved FOM |

Family Cites Families (44)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5567634A (en) * | 1995-05-01 | 1996-10-22 | National Semiconductor Corporation | Method of fabricating self-aligned contact trench DMOS transistors |

| JPH10214888A (en) * | 1997-01-30 | 1998-08-11 | Nec Yamagata Ltd | Manufacture of semiconductor device |

| KR100275756B1 (en) * | 1998-08-27 | 2000-12-15 | 김덕중 | Trench insulated gate bipolar transistor |

| ATE457084T1 (en) * | 1998-12-18 | 2010-02-15 | Infineon Technologies Ag | FIELD EFFECT TRANSISTOR ARRANGEMENT WITH A TRENCH-SHAPED GATE ELECTRODE AND AN ADDITIONAL HIGHLY DOPED LAYER IN THE BODY AREA |

| US20010001494A1 (en) * | 1999-04-01 | 2001-05-24 | Christopher B. Kocon | Power trench mos-gated device and process for forming same |

| US6348712B1 (en) * | 1999-10-27 | 2002-02-19 | Siliconix Incorporated | High density trench-gated power MOSFET |

| JP4696335B2 (en) * | 2000-05-30 | 2011-06-08 | 株式会社デンソー | Semiconductor device and manufacturing method thereof |

| JP4823435B2 (en) * | 2001-05-29 | 2011-11-24 | 三菱電機株式会社 | Semiconductor device and manufacturing method thereof |

| US6569738B2 (en) * | 2001-07-03 | 2003-05-27 | Siliconix, Inc. | Process for manufacturing trench gated MOSFET having drain/drift region |

| JP4945055B2 (en) * | 2003-08-04 | 2012-06-06 | ルネサスエレクトロニクス株式会社 | Semiconductor device and manufacturing method thereof |

| GB0407363D0 (en) * | 2004-03-31 | 2004-05-05 | Koninkl Philips Electronics Nv | Trench semiconductor device and method of manufacturing it |

| US7952139B2 (en) * | 2005-02-11 | 2011-05-31 | Alpha & Omega Semiconductor Ltd. | Enhancing Schottky breakdown voltage (BV) without affecting an integrated MOSFET-Schottky device layout |

| US7453119B2 (en) * | 2005-02-11 | 2008-11-18 | Alphs & Omega Semiconductor, Ltd. | Shielded gate trench (SGT) MOSFET cells implemented with a schottky source contact |

| US8110869B2 (en) * | 2005-02-11 | 2012-02-07 | Alpha & Omega Semiconductor, Ltd | Planar SRFET using no additional masks and layout method |

| US7436022B2 (en) * | 2005-02-11 | 2008-10-14 | Alpha & Omega Semiconductors, Ltd. | Enhancing Schottky breakdown voltage (BV) without affecting an integrated MOSFET-Schottky device layout |

| US7948029B2 (en) * | 2005-02-11 | 2011-05-24 | Alpha And Omega Semiconductor Incorporated | MOS device with varying trench depth |

| DE102006053145B4 (en) * | 2005-11-14 | 2014-07-10 | Denso Corporation | Semiconductor device with separation region |

| US7807536B2 (en) * | 2006-02-10 | 2010-10-05 | Fairchild Semiconductor Corporation | Low resistance gate for power MOSFET applications and method of manufacture |

| JP2007221024A (en) * | 2006-02-20 | 2007-08-30 | Toshiba Corp | Semiconductor device |

| US7812409B2 (en) * | 2006-12-04 | 2010-10-12 | Force-Mos Technology Corp. | Trench MOSFET with cell layout, ruggedness, truncated corners |

| CN101689562B (en) * | 2007-01-09 | 2013-05-15 | 威力半导体有限公司 | Semiconductor device |

| US7807576B2 (en) * | 2008-06-20 | 2010-10-05 | Fairchild Semiconductor Corporation | Structure and method for forming a thick bottom dielectric (TBD) for trench-gate devices |

| JP2011134910A (en) * | 2009-12-24 | 2011-07-07 | Rohm Co Ltd | Sic field effect transistor |

| US8546893B2 (en) * | 2010-01-12 | 2013-10-01 | Mohamed N. Darwish | Devices, components and methods combining trench field plates with immobile electrostatic charge |

| US8742451B2 (en) | 2010-05-24 | 2014-06-03 | Ixys Corporation | Power transistor with increased avalanche current and energy rating |

| US20120080748A1 (en) * | 2010-09-30 | 2012-04-05 | Force Mos Technology Co., Ltd. | Trench mosfet with super pinch-off regions |

| US20120175699A1 (en) * | 2011-01-06 | 2012-07-12 | Force Mos Technology Co., Ltd. | Trench mosfet with super pinch-off regions and self-aligned trenched contact |

| CN102184945A (en) | 2011-05-03 | 2011-09-14 | 成都芯源系统有限公司 | Groove gate type MOSFET device |

| US8907415B2 (en) * | 2011-05-16 | 2014-12-09 | Force Mos Technology Co., Ltd. | High switching trench MOSFET |

| US9018701B2 (en) | 2012-08-14 | 2015-04-28 | Force Mos Technology Co., Ltd. | Avalanche capability improvement in power semiconductor devices using three masks process |

| US9704948B2 (en) | 2014-08-09 | 2017-07-11 | Alpha & Omega Semiconductor (Cayman), Ltd. | Power trench MOSFET with improved unclamped inductive switching (UIS) performance and preparation method thereof |

| US20160104702A1 (en) * | 2014-10-08 | 2016-04-14 | Force Mos Technology Co., Ltd. | Super-junction trench mosfet integrated with embedded trench schottky rectifier |

| US9929260B2 (en) * | 2015-05-15 | 2018-03-27 | Fuji Electric Co., Ltd. | IGBT semiconductor device |

| JP6514035B2 (en) * | 2015-05-27 | 2019-05-15 | 株式会社豊田中央研究所 | Semiconductor device |

| DE112016004086T5 (en) * | 2015-09-09 | 2018-06-14 | Sumitomo Electric Industries, Ltd. | Semiconductor device |

| JP6115678B1 (en) * | 2016-02-01 | 2017-04-19 | 富士電機株式会社 | Silicon carbide semiconductor device and method for manufacturing silicon carbide semiconductor device |

| CN108172622A (en) * | 2018-01-30 | 2018-06-15 | 电子科技大学 | Power semiconductor |

| JP7139683B2 (en) * | 2018-05-17 | 2022-09-21 | 富士電機株式会社 | Semiconductor integrated circuit and its manufacturing method |

| US11189702B2 (en) * | 2019-01-30 | 2021-11-30 | Vishay SIliconix, LLC | Split gate semiconductor with non-uniform trench oxide |

| US20210028305A1 (en) * | 2019-07-22 | 2021-01-28 | Nami MOS CO., LTD. | Trench mosfets with oxide charge balance region in active area and junction charge balance region in termination area |

| US20210126124A1 (en) * | 2019-10-29 | 2021-04-29 | Nami MOS CO., LTD. | Termination of multiple stepped oxide shielded gate trench mosfet |

| TWI739252B (en) * | 2019-12-25 | 2021-09-11 | 杰力科技股份有限公司 | Trench mosfet and manufacturing method of the same |

| US11444164B2 (en) * | 2020-11-09 | 2022-09-13 | Nami MOS CO., LTD. | Shielded gate trench MOSFET having improved specific on-resistance structures |

| CN115911087A (en) * | 2022-09-08 | 2023-04-04 | 弘大芯源(深圳)半导体有限公司 | SGT-MOSFET (Metal-oxide-semiconductor field Effect transistor) for improving UIS (ultra thin silicon) performance and manufacturing method thereof |

-

2019

- 2019-12-25 TW TW108147542A patent/TWI739252B/en active

-

2020

- 2020-02-24 CN CN202010113782.5A patent/CN113035931B/en active Active

- 2020-03-25 US US16/830,225 patent/US11588021B2/en active Active

-

2021

- 2021-07-16 US US17/377,408 patent/US20210343840A1/en active Pending

Patent Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20130280870A1 (en) * | 2005-02-11 | 2013-10-24 | Alpha & Omega Semiconductor Limited | Fabrication of mos device with integrated schottky diode in active region contact trench |

| US20160190309A1 (en) * | 2012-02-02 | 2016-06-30 | Alpha And Omega Semiconductor Incorporated | Nano mosfet with trench bottom oxide shielded and third dimensional p-body contact |

| US20170373185A1 (en) * | 2012-02-02 | 2017-12-28 | Alpha And Omega Semiconductor Incorporated | Nano mosfet with trench bottom oxide shielded and third dimensional p-body contact |

| US20140077290A1 (en) * | 2012-09-14 | 2014-03-20 | Fu-Yuan Hsieh | Trench metal oxide semiconductor field effect transistor with embedded schottky rectifier using reduced masks process |

| TW201535719A (en) * | 2014-03-05 | 2015-09-16 | Alpha & Omega Semiconductor | High density trench gate MOSFET array with self-aligned contacts enhancement plug and method |

| TW201611183A (en) * | 2014-09-02 | 2016-03-16 | 萬國半導體股份有限公司 | Power trench MOSFET with mproved UIS performance and preparation method thereof |

| TW201622015A (en) * | 2014-12-10 | 2016-06-16 | 萬國半導體股份有限公司 | Integrating enhancement mode depleted accumulation/inversion channel devices with mosfets and preparing method thereof |

| TW201631739A (en) * | 2015-02-27 | 2016-09-01 | 萬國半導體股份有限公司 | Semiconductor component and method of manufacture |

| TW201843833A (en) * | 2017-01-23 | 2018-12-16 | 大陸商矽力杰半導體技術(杭州)有限公司 | Semiconductor device and method for manufacturing the same |

| TW201909419A (en) * | 2017-04-26 | 2019-03-01 | 澳門商萬民半導體 (澳門) 有限公司 | Scalable SGT structure with improved FOM |

Also Published As

| Publication number | Publication date |

|---|---|

| CN113035931A (en) | 2021-06-25 |

| TW202125822A (en) | 2021-07-01 |

| CN113035931B (en) | 2022-11-04 |

| US20210202701A1 (en) | 2021-07-01 |

| US20210343840A1 (en) | 2021-11-04 |

| US11588021B2 (en) | 2023-02-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9466700B2 (en) | Semiconductor device and method of fabricating same | |

| JP3425967B2 (en) | Lateral MOS field effect transistor having lightly doped drain and method of manufacturing the same | |

| US11923450B2 (en) | MOSFET in SiC with self-aligned lateral MOS channel | |

| JP5096739B2 (en) | Manufacturing method of semiconductor device | |

| TWI388011B (en) | Semiconductor device and method of forming a semiconductor device | |

| US7161208B2 (en) | Trench mosfet with field relief feature | |

| TWI739252B (en) | Trench mosfet and manufacturing method of the same | |

| US9461117B2 (en) | High voltage semiconductor device and method of manufacturing the same | |

| JP5048214B2 (en) | Short channel trench power MOSFET with low threshold voltage | |

| US9608057B2 (en) | Semiconductor device and method for manufacturing semiconductor device | |

| US20130049113A1 (en) | U-shape resurf mosfet devices and associated methods of manufacturing | |

| CN105448916A (en) | Transistor and method of forming same | |

| KR101393962B1 (en) | Power transistor with high voltage counter implant | |

| US11552183B2 (en) | Transistors with oxide liner in drift region | |

| JP2012191053A (en) | Semiconductor device and method of manufacturing the same | |

| US8796100B2 (en) | Methods of manufacturing lateral diffused MOS devices with layout controlled body curvature and related devices | |

| US8841723B2 (en) | LDMOS device having increased punch-through voltage and method for making same | |

| CN112466950B (en) | Anti-edge leakage SOI MOS structure and forming method thereof | |

| CN115911087A (en) | SGT-MOSFET (Metal-oxide-semiconductor field Effect transistor) for improving UIS (ultra thin silicon) performance and manufacturing method thereof | |

| KR20220030587A (en) | Power semiconductor device and method of fabricating the same | |

| WO2023095363A1 (en) | Semiconductor device and method for manufacturing same | |

| CN112466949B (en) | BTS type MOSFET structure and preparation method thereof | |

| TWI798825B (en) | Manufacturing method of semiconductor device | |

| KR101928253B1 (en) | Method of Manufacturing Power Semiconductor Device | |

| CN113611598A (en) | Preparation method of split-gate type trench semiconductor power device |