KR20240143558A - Integrated circuit device and method of manufacturing the same - Google Patents

Integrated circuit device and method of manufacturing the same Download PDFInfo

- Publication number

- KR20240143558A KR20240143558A KR1020230047583A KR20230047583A KR20240143558A KR 20240143558 A KR20240143558 A KR 20240143558A KR 1020230047583 A KR1020230047583 A KR 1020230047583A KR 20230047583 A KR20230047583 A KR 20230047583A KR 20240143558 A KR20240143558 A KR 20240143558A

- Authority

- KR

- South Korea

- Prior art keywords

- horizontal direction

- film

- direct contact

- integrated circuit

- along

- Prior art date

Links

- 238000004519 manufacturing process Methods 0.000 title description 12

- 229910052751 metal Inorganic materials 0.000 claims abstract description 58

- 239000002184 metal Substances 0.000 claims abstract description 58

- 229910021332 silicide Inorganic materials 0.000 claims abstract description 52

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 claims abstract description 52

- 239000000758 substrate Substances 0.000 claims abstract description 40

- 239000011229 interlayer Substances 0.000 claims description 39

- 230000004888 barrier function Effects 0.000 claims description 25

- 229910044991 metal oxide Inorganic materials 0.000 claims description 3

- 150000004706 metal oxides Chemical class 0.000 claims description 3

- 125000006850 spacer group Chemical group 0.000 description 58

- 239000010410 layer Substances 0.000 description 23

- 238000002955 isolation Methods 0.000 description 20

- 238000000034 method Methods 0.000 description 20

- 238000000926 separation method Methods 0.000 description 11

- 229910052581 Si3N4 Inorganic materials 0.000 description 9

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 9

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 9

- 229910052814 silicon oxide Inorganic materials 0.000 description 9

- 229910052710 silicon Inorganic materials 0.000 description 7

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 6

- 239000010703 silicon Substances 0.000 description 6

- 238000005530 etching Methods 0.000 description 4

- 229910000449 hafnium oxide Inorganic materials 0.000 description 4

- MRELNEQAGSRDBK-UHFFFAOYSA-N lanthanum(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[La+3].[La+3] MRELNEQAGSRDBK-UHFFFAOYSA-N 0.000 description 4

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 4

- 239000003990 capacitor Substances 0.000 description 3

- 239000000463 material Substances 0.000 description 3

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 3

- 229910052718 tin Inorganic materials 0.000 description 3

- 239000010936 titanium Substances 0.000 description 3

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- 229910000673 Indium arsenide Inorganic materials 0.000 description 2

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 2

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 2

- 238000000137 annealing Methods 0.000 description 2

- 238000004380 ashing Methods 0.000 description 2

- 238000000231 atomic layer deposition Methods 0.000 description 2

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 2

- VKJLWXGJGDEGSO-UHFFFAOYSA-N barium(2+);oxygen(2-);titanium(4+) Chemical compound [O-2].[O-2].[O-2].[Ti+4].[Ba+2] VKJLWXGJGDEGSO-UHFFFAOYSA-N 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 2

- RPQDHPTXJYYUPQ-UHFFFAOYSA-N indium arsenide Chemical compound [In]#[As] RPQDHPTXJYYUPQ-UHFFFAOYSA-N 0.000 description 2

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- KJXBRHIPHIVJCS-UHFFFAOYSA-N oxo(oxoalumanyloxy)lanthanum Chemical compound O=[Al]O[La]=O KJXBRHIPHIVJCS-UHFFFAOYSA-N 0.000 description 2

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 2

- 229910052760 oxygen Inorganic materials 0.000 description 2

- 239000001301 oxygen Substances 0.000 description 2

- JMOHEPRYPIIZQU-UHFFFAOYSA-N oxygen(2-);tantalum(2+) Chemical compound [O-2].[Ta+2] JMOHEPRYPIIZQU-UHFFFAOYSA-N 0.000 description 2

- 238000005240 physical vapour deposition Methods 0.000 description 2

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- VEALVRVVWBQVSL-UHFFFAOYSA-N strontium titanate Chemical compound [Sr+2].[O-][Ti]([O-])=O VEALVRVVWBQVSL-UHFFFAOYSA-N 0.000 description 2

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium(II) oxide Chemical compound [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 239000011800 void material Substances 0.000 description 2

- GFQYVLUOOAAOGM-UHFFFAOYSA-N zirconium(iv) silicate Chemical compound [Zr+4].[O-][Si]([O-])([O-])[O-] GFQYVLUOOAAOGM-UHFFFAOYSA-N 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- GEIAQOFPUVMAGM-UHFFFAOYSA-N Oxozirconium Chemical compound [Zr]=O GEIAQOFPUVMAGM-UHFFFAOYSA-N 0.000 description 1

- 229910020654 PbScTaO Inorganic materials 0.000 description 1

- 229910008484 TiSi Inorganic materials 0.000 description 1

- 229910008482 TiSiN Inorganic materials 0.000 description 1

- 229910008807 WSiN Inorganic materials 0.000 description 1

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 1

- XWCMFHPRATWWFO-UHFFFAOYSA-N [O-2].[Ta+5].[Sc+3].[O-2].[O-2].[O-2] Chemical compound [O-2].[Ta+5].[Sc+3].[O-2].[O-2].[O-2] XWCMFHPRATWWFO-UHFFFAOYSA-N 0.000 description 1

- CEPICIBPGDWCRU-UHFFFAOYSA-N [Si].[Hf] Chemical compound [Si].[Hf] CEPICIBPGDWCRU-UHFFFAOYSA-N 0.000 description 1

- ILCYGSITMBHYNK-UHFFFAOYSA-N [Si]=O.[Hf] Chemical compound [Si]=O.[Hf] ILCYGSITMBHYNK-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- MIQVEZFSDIJTMW-UHFFFAOYSA-N aluminum hafnium(4+) oxygen(2-) Chemical compound [O-2].[Al+3].[Hf+4] MIQVEZFSDIJTMW-UHFFFAOYSA-N 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- FHTCLMVMBMJAEE-UHFFFAOYSA-N bis($l^{2}-silanylidene)manganese Chemical compound [Si]=[Mn]=[Si] FHTCLMVMBMJAEE-UHFFFAOYSA-N 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- -1 for example Inorganic materials 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- 229910052735 hafnium Inorganic materials 0.000 description 1

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- QRXWMOHMRWLFEY-UHFFFAOYSA-N isoniazide Chemical compound NNC(=O)C1=CC=NC=C1 QRXWMOHMRWLFEY-UHFFFAOYSA-N 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910003465 moissanite Inorganic materials 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- PXHVJJICTQNCMI-UHFFFAOYSA-N nickel Substances [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 1

- 229910021334 nickel silicide Inorganic materials 0.000 description 1

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- UVGLBOPDEUYYCS-UHFFFAOYSA-N silicon zirconium Chemical compound [Si].[Zr] UVGLBOPDEUYYCS-UHFFFAOYSA-N 0.000 description 1

- CZXRMHUWVGPWRM-UHFFFAOYSA-N strontium;barium(2+);oxygen(2-);titanium(4+) Chemical compound [O-2].[O-2].[O-2].[O-2].[Ti+4].[Sr+2].[Ba+2] CZXRMHUWVGPWRM-UHFFFAOYSA-N 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- 229910052726 zirconium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/48—Data lines or contacts therefor

- H10B12/485—Bit line contacts

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/31—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor

- H10B12/315—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor with the capacitor higher than a bit line

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/48—Data lines or contacts therefor

- H10B12/482—Bit lines

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/48—Data lines or contacts therefor

- H10B12/488—Word lines

Landscapes

- Semiconductor Memories (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

일부 실시예들에 따른 집적회로 소자는, 복수의 활성 영역을 갖는 기판; 상기 복수의 활성 영역 중에서 선택된 제1 활성 영역에 연결된 다이렉트 콘택; 상기 기판에 형성되며 제1 수평 방향으로 연장되는 복수의 워드 라인 트렌치 내에 배치되는 복수의 워드 라인; 상기 기판 상에서 상기 제1 수평 방향에 직교하는 제2 수평 방향을 따라 연장되고 상기 다이렉트 콘택에 연결되는 비트 라인; 및 상기 다이렉트 콘택과 상기 제1 활성 영역 사이의 금속 실리사이드막;을 포함하고, 상기 다이렉트 콘택은 상기 금속 실리사이드막의 상기 제2 수평 방향에 따른 양 측벽을 덮는다.An integrated circuit device according to some embodiments includes a substrate having a plurality of active regions; a direct contact connected to a first active region selected from the plurality of active regions; a plurality of word lines disposed within a plurality of word line trenches formed in the substrate and extending in a first horizontal direction; a bit line extending along a second horizontal direction orthogonal to the first horizontal direction on the substrate and connected to the direct contact; and a metal silicide film between the direct contact and the first active region, wherein the direct contact covers both sidewalls of the metal silicide film along the second horizontal direction.

Description

본 발명의 기술적 사상은 집적회로 소자 및 이의 제조 방법에 관한 것으로, 특히 매립된 워드 라인을 가지는 집적회로 소자 및 이의 제조 방법에 관한 것이다.The technical idea of the present invention relates to an integrated circuit device and a method for manufacturing the same, and more particularly, to an integrated circuit device having a buried word line and a method for manufacturing the same.

집적회로 소자의 집적도가 증가함에 따라 도전 라인들의 피치가 감소된다. 인접한 도전 영역들 사이의 신뢰성 있는 전기적 접속을 확보하기 위한 기술이 필요하다.As the integration density of integrated circuit devices increases, the pitch of conductive lines decreases. Technologies are needed to ensure reliable electrical connections between adjacent conductive areas.

본 발명의 기술적 사상이 이루고자 하는 기술적 과제는 다운-스케일링에 따라 축소된 면적의 소자 영역을 가지는 집적회로 소자에서 인접한 도전 영역들 사이의 신뢰성 있는 전기적 접속을 확보할 수 있는 구조를 가지는 집적회로 소자를 제공하는 것이다.The technical problem to be achieved by the technical idea of the present invention is to provide an integrated circuit device having a structure capable of securing reliable electrical connection between adjacent conductive regions in an integrated circuit device having a device area with a reduced area due to downscaling.

본 발명의 기술적 사상이 이루고자 하는 기술적 과제는 다운-스케일링에 따라 축소된 면적의 소자 영역을 가지는 집적회로 소자에서 인접한 도전 영역들 사이의 신뢰성 있는 전기적 접속을 확보할 수 있는 구조를 가지는 집적회로 소자의 제조 방법을 제공하는 것이다.The technical problem to be achieved by the technical idea of the present invention is to provide a method for manufacturing an integrated circuit device having a structure capable of securing reliable electrical connection between adjacent conductive regions in an integrated circuit device having a device area with a reduced area due to downscaling.

상술한 기술적 과제를 해결하기 위한 일부 실시예들에 따르면, 집적회로 소자가 제공된다. 상기 집적회로 소자는, 복수의 활성 영역을 갖는 기판; 상기 복수의 활성 영역 중에서 선택된 제1 활성 영역에 연결된 다이렉트 콘택; 상기 기판에 형성되며 제1 수평 방향으로 연장되는 복수의 워드 라인 트렌치 내에 배치되는 복수의 워드 라인; 상기 기판 상에서 상기 제1 수평 방향에 직교하는 제2 수평 방향을 따라 연장되고 상기 다이렉트 콘택에 연결되는 비트 라인; 및 상기 다이렉트 콘택과 상기 제1 활성 영역 사이의 금속 실리사이드막;을 포함하고, 상기 다이렉트 콘택은 상기 금속 실리사이드막의 상기 제2 수평 방향에 따른 양 측벽을 덮는다. According to some embodiments for solving the above-described technical problem, an integrated circuit device is provided. The integrated circuit device includes: a substrate having a plurality of active regions; a direct contact connected to a first active region selected from the plurality of active regions; a plurality of word lines disposed in a plurality of word line trenches formed in the substrate and extending in a first horizontal direction; a bit line extending along a second horizontal direction orthogonal to the first horizontal direction on the substrate and connected to the direct contact; and a metal silicide film between the direct contact and the first active region; wherein the direct contact covers both sidewalls of the metal silicide film along the second horizontal direction.

상술한 기술적 과제를 해결하기 위한 일부 실시예들에 따르면, 집적회로 소자가 제공된다. 상기 집적회로 소자는, 복수의 활성 영역을 갖는 기판; 상기 복수의 활성 영역 중에서 선택된 제1 활성 영역에 연결된 다이렉트 콘택; 상기 기판에 형성되며 제1 수평 방향으로 연장되는 복수의 워드 라인 트렌치 내에 배치되는 복수의 워드 라인; 상기 기판 상에서 상기 제1 수평 방향에 직교하는 제2 수평 방향을 따라 연장되고 상기 다이렉트 콘택에 연결되는 비트 라인; 및 상기 다이렉트 콘택과 상기 제1 활성 영역 사이의 금속 실리사이드막;을 포함하고, 상기 다이렉트 콘택은, 상기 비트 라인의 저면에 접하며 상기 제2 수평 방향을 따라 제1 폭을 갖는 상측 부분; 및 상기 상측 부분보다 낮은 수직 레벨에서 상기 금속 실리사이드막의 상면을 덮으며, 상기 제2 수평 방향을 따라 상기 제1 폭보다 작은 제2 폭을 갖는 하측 부분;을 포함한다.According to some embodiments for solving the above-described technical problem, an integrated circuit device is provided. The integrated circuit device includes a substrate having a plurality of active regions; a direct contact connected to a first active region selected from the plurality of active regions; a plurality of word lines formed in the substrate and arranged in a plurality of word line trenches extending in a first horizontal direction; a bit line extending along a second horizontal direction orthogonal to the first horizontal direction on the substrate and connected to the direct contact; and a metal silicide film between the direct contact and the first active region; wherein the direct contact includes an upper portion contacting a bottom surface of the bit line and having a first width along the second horizontal direction; and a lower portion covering an upper surface of the metal silicide film at a vertical level lower than the upper portion and having a second width smaller than the first width along the second horizontal direction.

본 발명의 기술적 사상에 의한 집적회로 소자는 복수의 비트 라인 사이의 공간이 확보되어, 다운-스케일링에 따라 축소된 면적의 소자 영역을 가지는 집적회로 소자에서 전기적 접속의 신뢰성이 향상될 수 있다.An integrated circuit device according to the technical idea of the present invention can secure a space between a plurality of bit lines, thereby improving the reliability of electrical connection in an integrated circuit device having a device area with a reduced area due to downscaling.

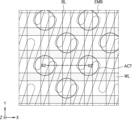

도 1은 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자의 메모리 셀 어레이 영역의 일부 구성들을 설명하기 위한 개략적인 평면 레이아웃이다.

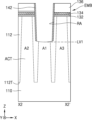

도 2a는 도 1의 X1-X1'선에 따른 단면도이다.

도 2b는 도 2a의 "EX1"로 표시된 부분의 확대도이다.

도 3a는 도 1의 Y-Y1'선에 따른 단면도이다.

도 3b는 도 3a의 "EX2"로 표시된 부분의 확대도이다.

도 4a는 일부 실시예들에 따른 집적회로 소자의 단면도로서, 도 3a에 대응되는 부분을 나타낸 것이다.

도 4b는 도 4a의 "EX3"으로 표시된 부분의 확대도이다.

도 5는 예시적인 실시예들에 따른 집적회로 소자의 제조 방법을 설명하기 위한 평편도이다.

도 6a 내지 도 6d는 예시적인 실시예들에 따른 집적회로 소자의 제조 방법을 설명하기 위하여 공정 순서에 따라 도시한 단면도들로서, 도 5의 X2-X2'선에 따른 단면을 나타낸 것이다.

도 7a 내지 도 7e는 일부 실시예들에 따른 집적회로 소자의 제조 방법을 설명하기 위하여 공정 순서에 따라 도시한 단면도들로서, 도 5의 X2-X2'선에 따른 단면에 대응되는 부분을 나타낸 것이다.FIG. 1 is a schematic planar layout for explaining some configurations of a memory cell array area of an integrated circuit device according to embodiments of the technical idea of the present invention.

Fig. 2a is a cross-sectional view taken along line X1-X1' of Fig. 1.

Figure 2b is an enlarged view of the portion indicated as “EX1” in Figure 2a.

Fig. 3a is a cross-sectional view along line Y-Y1' of Fig. 1.

Figure 3b is an enlarged view of the portion indicated as “EX2” in Figure 3a.

FIG. 4a is a cross-sectional view of an integrated circuit device according to some embodiments, showing a portion corresponding to FIG. 3a.

Figure 4b is an enlarged view of the portion indicated as “EX3” in Figure 4a.

FIG. 5 is a schematic diagram illustrating a method for manufacturing an integrated circuit device according to exemplary embodiments.

FIGS. 6A to 6D are cross-sectional views illustrating a process sequence for explaining a method of manufacturing an integrated circuit device according to exemplary embodiments, and illustrate cross-sections taken along line X2-X2' of FIG. 5.

FIGS. 7A to 7E are cross-sectional views illustrating a process sequence for explaining a method of manufacturing an integrated circuit device according to some embodiments, and illustrate a portion corresponding to a cross-section taken along line X2-X2' of FIG. 5.

이하, 첨부 도면을 참조하여 본 발명의 실시예들을 상세히 설명한다. 도면상의 동일한 구성요소에 대해서는 동일한 참조부호를 사용하고, 이들에 대한 중복된 설명은 생략한다. Hereinafter, embodiments of the present invention will be described in detail with reference to the attached drawings. The same reference numerals are used for the same components in the drawings, and redundant descriptions thereof are omitted.

도 1은 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자(100)의 메모리 셀 어레이 영역의 일부 구성들을 설명하기 위한 개략적인 평면 레이아웃이다. FIG. 1 is a schematic planar layout for explaining some configurations of a memory cell array area of an integrated circuit device (100) according to embodiments of the technical idea of the present invention.

도 1을 참조하면, 집적회로 소자(100)는 평면 상에서 상호 직교하는 제1 수평 방향(X 방향) 및 제2 수평 방향(Y 방향)에 대하여 사선 방향으로 수평으로 연장되도록 배치된 복수의 활성 영역(ACT)을 포함할 수 있다. 예를 들면, 복수의 활성 영역(ACT)은 수평 방향(X 방향 및/또는 Y 방향)에서 서로 이격되어 배치될 수 있다. Referring to FIG. 1, the integrated circuit device (100) may include a plurality of active regions (ACTs) arranged to extend horizontally in a diagonal direction with respect to a first horizontal direction (X direction) and a second horizontal direction (Y direction) that are orthogonal to each other on a plane. For example, the plurality of active regions (ACTs) may be arranged to be spaced apart from each other in the horizontal direction (X direction and/or Y direction).

예시적인 실시예들에 따르면, 복수의 워드 라인(WL)이 복수의 활성 영역(ACT)을 가로질러 제1 수평 방향(X 방향)을 따라 상호 평행하게 연장될 수 있다. 예시적인 실시예들에 따르면, 복수의 워드 라인(WL) 상에 복수의 비트 라인(BL)이 제2 수평 방향(Y 방향)을 따라 상호 평행하게 연장될 수 있다. 예시적인 실시예들에 따르면, 복수의 활성 영역(ACT)은 각각 다이렉트 콘택(DC)을 통해 복수의 비트 라인(BL)에 전기적으로 연결될 수 있다.According to exemplary embodiments, a plurality of word lines (WL) may extend in parallel to each other along a first horizontal direction (X direction) across a plurality of active regions (ACT). According to exemplary embodiments, a plurality of bit lines (BL) may extend in parallel to each other along a second horizontal direction (Y direction) on the plurality of word lines (WL). According to exemplary embodiments, the plurality of active regions (ACT) may be electrically connected to the plurality of bit lines (BL) respectively through direct contacts (DC).

예시적인 실시예들에 따르면, 복수의 비트 라인(BL) 중 상호 인접한 두 개의 비트 라인(BL) 사이에 복수의 베리드 콘택(BC)이 배치될 수 있다. 예시적인 실시예들에 따르면, 복수의 베리드 콘택(BC)은 제1 수평 방향(X 방향) 및 제2 수평 방향(Y 방향)을 따라 일렬로 배열될 수 있다. 복수의 베리드 콘택(BC) 위에는 복수의 랜딩 패드(미도시)가 형성될 수 있다. 복수의 베리드 콘택(BC) 및 복수의 랜딩 패드(미도시)는 복수의 비트 라인(BL)의 상부에 형성되는 커패시터의 하부 전극(미도시)을 복수의 활성 영역(ACT)에 연결시키는 역할을 할 수 있다. 예를 들면, 복수의 랜딩 패드(미도시)는 각각 베리드 콘택(BC)과 일부 오버랩되도록 배치될 수 있다.According to exemplary embodiments, a plurality of buried contacts (BC) may be arranged between two adjacent bit lines (BL) among a plurality of bit lines (BL). According to exemplary embodiments, the plurality of buried contacts (BC) may be arranged in a row along a first horizontal direction (X direction) and a second horizontal direction (Y direction). A plurality of landing pads (not shown) may be formed on the plurality of buried contacts (BC). The plurality of buried contacts (BC) and the plurality of landing pads (not shown) may serve to connect a lower electrode (not shown) of a capacitor formed on an upper portion of the plurality of bit lines (BL) to a plurality of active regions (ACT). For example, the plurality of landing pads (not shown) may be arranged to partially overlap with the buried contacts (BC), respectively.

도 2a는 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자(100)를 설명하기 위한 단면도로서 도 1의 X1-X1'선에 따른 단면도이고, 2b는 도 2a의 "EX1"로 표시된 부분의 확대도이다. 도 3a는 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자(100)를 설명하기 위한 단면도로서 도 1의 Y-Y1'선에 따른 단면도이며, 도 3b는 도 3a의 "EX2"로 표시된 부분의 확대도이다.FIG. 2a is a cross-sectional view illustrating an integrated circuit device (100) according to embodiments of the technical idea of the present invention, which is a cross-sectional view taken along line X1-X1' of FIG. 1, and FIG. 2b is an enlarged view of a portion indicated as "EX1" of FIG. 2a. FIG. 3a is a cross-sectional view illustrating an integrated circuit device (100) according to embodiments of the technical idea of the present invention, which is a cross-sectional view taken along line Y-Y1' of FIG. 1, and FIG. 3b is an enlarged view of a portion indicated as "EX2" of FIG. 3a.

도 1 및 도 2a 내지 도 3b를 함께 참조하면, 집적회로 소자(100)는 소자 분리 트렌치(112T)에 의해 복수의 활성 영역(ACT)이 정의된 기판(110)을 포함할 수 있다. 예시적인 실시예들에 따르면, 소자 분리 트렌치(112T)는 소자 분리막(112)으로 채워질 수 있다. 소자 분리막(112)은 기판(110) 상에서 복수의 활성 영역(ACT)을 포위할 수 있다. Referring to FIGS. 1 and 2A to 3B together, an integrated circuit device (100) may include a substrate (110) having a plurality of active regions (ACTs) defined by a device isolation trench (112T). According to exemplary embodiments, the device isolation trench (112T) may be filled with a device isolation film (112). The device isolation film (112) may surround the plurality of active regions (ACTs) on the substrate (110).

일부 실시예들에 있어서, 기판(110)은 실리콘, 예를 들면 단결정 실리콘, 다결정 실리콘, 또는 비정질 실리콘을 포함할 수 있다. 다른 일부 실시예들에 있어서, 기판(110)은 Ge, SiGe, SiC, GaAs, InAs, 및 InP 중에서 선택되는 적어도 하나를 포함할 수 있다. 본 명세서에서 사용되는 용어 "SiGe", "SiC", "GaAs", "InAs", "InP"등의 용어는 각각의 용어에 포함된 원소들로 이루어진 재료를 의미하는 것으로서, 화학양론적 관계를 나타내는 화학식이 아니며, 이하에서 서술되는 용어들에 대해서도 마찬가지로 이해될 수 있다.In some embodiments, the substrate (110) may include silicon, for example, single crystal silicon, polycrystalline silicon, or amorphous silicon. In some other embodiments, the substrate (110) may include at least one selected from Ge, SiGe, SiC, GaAs, InAs, and InP. The terms "SiGe", "SiC", "GaAs", "InAs", "InP", etc., used herein, mean a material composed of elements included in each term, and are not chemical formulas indicating a stoichiometric relationship, and can be understood in the same manner for terms described below.

일부 실시예들에 있어서, 기판(110)은 도전 영역, 예를 들면 도펀트가 도핑된 웰(well), 또는 도펀트가 도핑된 구조물을 포함할 수 있다. 일부 실시예들에 있어서, 소자 분리막(112)은 실리콘 산화막, 실리콘 질화막, 또는 이들의 조합으로 이루어질 수 있다.In some embodiments, the substrate (110) may include a conductive region, such as a dopant-doped well, or a dopant-doped structure. In some embodiments, the device isolation layer (112) may be formed of a silicon oxide film, a silicon nitride film, or a combination thereof.

예시적인 실시예들에 따르면, 기판(110)에 제1 수평 방향(X 방향)으로 길게 연장되는 복수의 워드 라인 트렌치(120T)가 형성될 수 있고, 복수의 워드 라인 트렌치(120T) 내에 각각 게이트 유전막(122), 워드 라인(124), 및 매몰 절연막(126)이 배치될 수 있다. 예시적인 실시예들에 따르면, 복수의 워드 라인(124)은 복수의 워드 라인 트렌치(120T) 내에서 제1 수평 방향(X 방향)을 따라 길게 연장될 수 있으며, 복수의 매몰 절연막(126)은 복수의 워드 라인 트렌치(120T) 내에서 복수의 워드 라인(124)의 상면을 덮을 수 있다. 예시적인 실시예들에 따르면, 복수의 게이트 유전막(122)은 각각 워드 라인 트렌치(120T)의 내부 표면을 컨포멀하게 덮으며 워드 라인(124) 및 매몰 절연막(126)을 감쌀 수 있다.According to exemplary embodiments, a plurality of word line trenches (120T) extending in a first horizontal direction (X direction) may be formed in a substrate (110), and a gate dielectric film (122), a word line (124), and a buried insulating film (126) may be disposed within each of the plurality of word line trenches (120T). According to exemplary embodiments, the plurality of word lines (124) may extend in a first horizontal direction (X direction) within the plurality of word line trenches (120T), and the plurality of buried insulating films (126) may cover upper surfaces of the plurality of word lines (124) within the plurality of word line trenches (120T). According to exemplary embodiments, the plurality of gate dielectric films (122) may conformally cover an inner surface of each of the word line trenches (120T) and surround the word line (124) and the buried insulating film (126).

일부 실시예들에 있어서, 게이트 유전막(122)은 실리콘 산화막, 실리콘 질화막, 실리콘 산화질화막, ONO(oxide/nitride/oxide) 막, 또는 실리콘 산화막보다 높은 유전 상수를 가지는 고유전막 중에서 선택되는 적어도 하나로 이루어질 수 있다. 상기 고유전막은 하프늄 산화물(HfO), 알루미늄 산화물(AlO), 하프늄 알루미늄 산화물(HfAlO), 탄탈륨 산화물(TaO), 티타늄 산화물(TiO), 또는 이들의 조합으로 이루어질 수 있다. 복수의 워드 라인(124)은 Ti, TiN, Ta, TaN, W, WN, TiSiN, WSiN, 또는 이들의 조합으로 이루어질 수 있다. 복수의 매몰 절연막(126)은 실리콘 산화막, 실리콘 질화막, 실리콘 산화질화막, 또는 이들의 조합으로 이루어질 수 있다.In some embodiments, the gate dielectric film (122) may be formed of at least one selected from a silicon oxide film, a silicon nitride film, a silicon oxynitride film, an oxide/nitride/oxide (ONO) film, or a high-k dielectric film having a higher dielectric constant than the silicon oxide film. The high-k dielectric film may be formed of hafnium oxide (HfO), aluminum oxide (AlO), hafnium aluminum oxide (HfAlO), tantalum oxide (TaO), titanium oxide (TiO), or a combination thereof. The plurality of word lines (124) may be formed of Ti, TiN, Ta, TaN, W, WN, TiSiN, WSiN, or a combination thereof. The plurality of buried insulating films (126) may be formed of a silicon oxide film, a silicon nitride film, a silicon oxynitride film, or a combination thereof.

예시적인 실시예들에 따르면, 기판(110) 상에는 버퍼층(132), 층간 배리어막(134), 및 층간 절연막(136)이 순차적으로 적층될 수 있다. 버퍼층(132)은 복수의 활성 영역(ACT)의 상면, 소자 분리막(112)의 상면, 및 복수의 매몰 절연막(126)의 상면을 덮을 수 있다. 층간 배리어막(134)은 버퍼층(132)의 상면을 덮을 수 있고, 층간 절연막(136)은 층간 배리어막(134)의 상면을 덮을 수 있다. 예를 들면, 층간 배리어막(134)은 다이렉트 콘택(DC)을 형성하는 공정에서 복수의 활성 영역(ACT)이 식각 또는 손상되지 않도록 보호하는 역할을 수행할 수 있다.According to exemplary embodiments, a buffer layer (132), an interlayer barrier film (134), and an interlayer insulating film (136) may be sequentially laminated on a substrate (110). The buffer layer (132) may cover upper surfaces of a plurality of active regions (ACTs), an upper surface of the device isolation film (112), and an upper surface of a plurality of buried insulating films (126). The interlayer barrier film (134) may cover an upper surface of the buffer layer (132), and the interlayer insulating film (136) may cover an upper surface of the interlayer barrier film (134). For example, the interlayer barrier film (134) may play a role in protecting the plurality of active regions (ACTs) from being etched or damaged during a process of forming a direct contact (DC).

일부 실시예들에 있어서, 버퍼층(132)은 기판(110) 상에 차례로 형성된 제1 실리콘 산화막, 실리콘 질화막, 및 제2 실리콘 산화막으로 이루어질 수 있으나, 이에 한정되는 것은 아니다. 일부 실시예들에 있어서, 금속 층간 배리어막(134)은 금속 산화물을 포함할 수 있다. 예를 들면, 상기 금속 산화물은 알루미늄 산화물(AlO), 하프늄 산화물(HfO), 하프늄 실리콘 산화물(HfSiO), 하프늄 산화 질화물(HfON), 하프늄 실리콘 산화 질화물(HfSiON), 란타늄 산화물(LaO), 란탄늄 알루미늄 산화물(LaAlO), 지르코늄 산화물(ZrO), 지르코늄 실리콘 산화물(ZrSiO), 지르코늄 산화 질화물(ZrON), 지르코늄 실리콘 산화 질화물(ZrSiON), 탄탈륨 산화물(TaO), 티타늄 산화물(TiO), 바륨 스트론튬 티타늄 산화물(BaSrTiO), 바륨 티타늄 산화물(BaTiO), 스트론튬 티타늄 산화물(SrTiO), 이트륨 산화물(YO), 또는 납 스칸듐 탄탈륨 산화물(PbScTaO)을 포함할 수 있으나, 이에 한정되는 것은 아니다. 일부 실시예들에 있어서, 층간 절연막(136)은 실리콘 산화막, 실리콘 질화막 또는 이들의 조합을 포함할 수 있으나, 이에 한정되는 것은 아니다.In some embodiments, the buffer layer (132) may be formed of, but is not limited to, a first silicon oxide film, a silicon nitride film, and a second silicon oxide film sequentially formed on the substrate (110). In some embodiments, the metal interlayer barrier film (134) may include a metal oxide. For example, the metal oxide may include, but is not limited to, aluminum oxide (AlO), hafnium oxide (HfO), hafnium silicon oxide (HfSiO), hafnium oxynitride (HfON), hafnium silicon oxynitride (HfSiON), lanthanum oxide (LaO), lanthanum aluminum oxide (LaAlO), zirconium oxide (ZrO), zirconium silicon oxide (ZrSiO), zirconium oxynitride (ZrON), zirconium silicon oxynitride (ZrSiON), tantalum oxide (TaO), titanium oxide (TiO), barium strontium titanium oxide (BaSrTiO), barium titanium oxide (BaTiO), strontium titanium oxide (SrTiO), yttrium oxide (YO), or lead scandium tantalum oxide (PbScTaO). In some embodiments, the interlayer insulating film (136) may include, but is not limited to, a silicon oxide film, a silicon nitride film, or a combination thereof.

예시적인 실시예들에 따르면, 층간 절연막(136) 상에 복수의 비트 라인(152)이 제2 수평 방향(Y 방향)을 따라 상호 평행하게 연장될 수 있다. 예를 들면, 복수의 비트 라인(152)은 층간 배리어막(134) 및 버퍼층(132)상에서 제2 수평 방향(Y 방향)을 따라 길게 연장될 수 있다. 예시적인 실시예들에 따르면, 복수의 비트 라인(152)은 제1 수평 방향(X 방향)을 따라 서로 이격될 수 있다.According to exemplary embodiments, a plurality of bit lines (152) may extend in parallel to each other along a second horizontal direction (Y direction) on the interlayer insulating film (136). For example, the plurality of bit lines (152) may extend long along the second horizontal direction (Y direction) on the interlayer barrier film (134) and the buffer layer (132). According to exemplary embodiments, the plurality of bit lines (152) may be spaced apart from each other along the first horizontal direction (X direction).

예시적인 실시예들에 따르면, 기판(110)의 일부 영역에서, 하부 리세스(RA)가 형성될 수 있다. 하부 리세스(RA)의 저면을 통해 노출된 복수의 활성 영역(ACT) 각각의 일부 영역 상에 다이렉트 콘택(DC)이 배치될 수 있다. 예시적인 실시예들에 따르면, 복수의 비트 라인(152)은 복수의 다이렉트 콘택(DC) 상에서 제2 수평 방향(Y 방향)을 따라 연장되며, 복수의 다이렉트 콘택(DC)의 상면에 접할 수 있다. 예를 들면, 하부 리세스(RA)의 저면은 제1 수직 레벨(LV1)에 배치될 수 있다. 본 명세서에서 사용되는 용어 "수직 레벨"은 수직 방향(Z 방향 또는 -Z 방향)을 따르는 높이를 의미한다. According to exemplary embodiments, a lower recess (RA) may be formed in a portion of a substrate (110). A direct contact (DC) may be arranged on a portion of each of a plurality of active regions (ACTs) exposed through a bottom surface of the lower recess (RA). According to exemplary embodiments, a plurality of bit lines (152) may extend along a second horizontal direction (Y direction) on the plurality of direct contacts (DC) and may contact upper surfaces of the plurality of direct contacts (DC). For example, a bottom surface of the lower recess (RA) may be arranged at a first vertical level (LV1). The term "vertical level" as used herein means a height along a vertical direction (Z direction or -Z direction).

예시적인 실시예들에 따르면, 하부 리세스(RA)의 저면 상에 복수의 활성 영역(ACT)의 노출된 부분을 덮는 복수의 금속 실리사이드막(144)이 배치될 수 있다. 예를 들면, 복수의 금속 실리사이드막(144)은 하부 리세스(RA)의 저면을 통해 노출된 복수의 활성 영역(ACT)과 복수의 다이렉트 콘택(DC) 사이에 개재될 수 있다. 예시적인 실시예들에 따르면, 복수의 활성 영역(ACT)은 각각 금속 실리사이드막(144) 및 다이렉트 콘택(DC)을 통해 비트 라인(152)에 전기적으로 연결될 수 있다.According to exemplary embodiments, a plurality of metal silicide films (144) may be disposed on a bottom surface of a lower recess (RA) to cover exposed portions of a plurality of active regions (ACT). For example, the plurality of metal silicide films (144) may be interposed between the plurality of active regions (ACT) exposed through the bottom surface of the lower recess (RA) and the plurality of direct contacts (DC). According to exemplary embodiments, the plurality of active regions (ACT) may be electrically connected to the bit line (152) through the metal silicide films (144) and the direct contacts (DC), respectively.

일부 실시예들에 있어서, 다이렉트 콘택(DC)은 Si, Ge, W, WN, Co, Ni, Al, Mo, Ru, Ti, TiN, Ta, TaN, Cu, 또는 이들의 조합으로 이루어질 수 있다. 일부 실시예들에 있어서, 금속 실리사이드막(144)은 TiSi일 수 있다. 다른 일부 실시예들에 있어서, 다이렉트 콘택(DC)은 도핑된 폴리실리콘막으로 이루어질 수 있다. 다른 일부 실시예들에 있어서, 다이렉트 콘택(DC)과 비트 라인(152) 사이에 금속 층간 배리어막(미도시) 개재될 수 있으나, 이에 한정되는 것은 아니다. 예를 들면, 도 2a의 비트 라인(152)은 도 1의 비트 라인(BL)에 대응될 수 있다.In some embodiments, the direct contact (DC) may be formed of Si, Ge, W, WN, Co, Ni, Al, Mo, Ru, Ti, TiN, Ta, TaN, Cu, or a combination thereof. In some embodiments, the metal silicide film (144) may be TiSi. In some other embodiments, the direct contact (DC) may be formed of a doped polysilicon film. In some other embodiments, a metal interlayer barrier film (not shown) may be interposed between the direct contact (DC) and the bit line (152), but is not limited thereto. For example, the bit line (152) of FIG. 2A may correspond to the bit line (BL) of FIG. 1.

도 2a 내지 도 3b에서, 복수의 비트 라인(152)이 단일의 도전층 구조를 갖는 것으로 예시하였으나, 이에 제한되지 않는다. 예를 들면, 복수의 비트 라인(152)은 각각 2중 이상의 복수의 도적층의 적층 구조를 가질 수 있다. In FIGS. 2A to 3B, the plurality of bit lines (152) are exemplified as having a single conductive layer structure, but are not limited thereto. For example, the plurality of bit lines (152) may each have a stacked structure of two or more conductive layers.

예시적인 실시예들에 따르면, 복수의 비트 라인(152) 상에 캡핑 절연 패턴(154)이 배치될 수 있다. 일부 실시예들에 있어서, 캡핑 절연 패턴(154)은 실리콘 질화막을 포함할 수 있으나, 이에 한정되는 것은 아니다.According to exemplary embodiments, a capping insulating pattern (154) may be disposed on a plurality of bit lines (152). In some embodiments, the capping insulating pattern (154) may include, but is not limited to, a silicon nitride film.

도 2a 및 도 2b에서 예시한 바와 같이, 하부 리세스(RA)는 다이렉트 콘택(DC), 내측 절연 스페이서(162), 및 갭필 절연 패턴(164)으로 채워질 수 있다. 예시적인 실시예들에 따르면, 내측 절연 스페이서(162)는 하부 리세스(RA)의 저면 일부 및 내벽 일부를 컨포멀하게 덮을 수 있고, 복수의 금속 실리사이드막(144)의 제1 수평 방향(X 방향)에 따른 양 측벽, 복수의 다이렉트 콘택(DC)의 제1 수평 방향(X 방향)에 따른 양 측벽, 비트 라인(152)의 제1 수평 방향(X 방향)에 따른 양 측벽, 캡핑 절연 패턴(154)의 제1 수평 방향(X 방향)에 따른 양 측벽을 컨포멀하게 덮을 수 있다. 예시적인 실시예들에 따르면, 갭필 절연 패턴(164)은 내측 절연 스페이서(162) 상에서 복수의 금속 실리사이드막(144)의 제1 수평 방향(X 방향)에 따른 양 측벽, 및 복수의 다이렉트 콘택(DC)의 제1 수평 방향(X 방향)에 따른 양 측벽을 덮을 수 있다. 일부 실시예들에 있어서, 내측 절연 스페이서(162)는 실리콘 질화막으로 이루어질 수 있고, 갭필 절연 패턴(164)은 실리콘 산화막으로 이루어질 수 있다.As illustrated in FIGS. 2A and 2B , the lower recess (RA) can be filled with a direct contact (DC), an inner insulating spacer (162), and a gapfill insulating pattern (164). According to exemplary embodiments, the inner insulating spacer (162) can conformally cover a portion of a bottom surface and a portion of an inner wall of the lower recess (RA), and can conformally cover both sidewalls along the first horizontal direction (X direction) of the plurality of metal silicide films (144), both sidewalls along the first horizontal direction (X direction) of the plurality of direct contacts (DC), both sidewalls along the first horizontal direction (X direction) of the bit line (152), and both sidewalls along the first horizontal direction (X direction) of the capping insulating pattern (154). According to exemplary embodiments, the gapfill insulating pattern (164) may cover both sidewalls along the first horizontal direction (X direction) of the plurality of metal silicide films (144) on the inner insulating spacer (162), and both sidewalls along the first horizontal direction (X direction) of the plurality of direct contacts (DC). In some embodiments, the inner insulating spacer (162) may be formed of a silicon nitride film, and the gapfill insulating pattern (164) may be formed of a silicon oxide film.

도 1, 도 3a 및 도 3b에 예시한 바와 같이, 복수의 다이렉트 콘택(DC)은 각각 복수의 워드 라인(WL)의 일부와 수직 방향(Z 방향)에서 중첩될 수 있다. 예를 들면, 복수의 활성 영역(ACT) 중에서 선택된 제1 활성 영역(ACT)에 연결되는 다이렉트 콘택(DC)은, 복수의 워드 라인(WL) 중에서 선택되며 상기 제1 활성 영역(ACT)을 가로지르는 제1 워드 라인(WL) 및 제2 워드 라인(WL)과 부분적으로 오버랩될 수 있다.As illustrated in FIG. 1, FIG. 3A, and FIG. 3B, a plurality of direct contacts (DC) may overlap a portion of a plurality of word lines (WL) in the vertical direction (Z direction), respectively. For example, a direct contact (DC) connected to a first active region (ACT) selected from among a plurality of active regions (ACTs) may partially overlap a first word line (WL) and a second word line (WL) selected from among a plurality of word lines (WL) and crossing the first active region (ACT).

예시적인 실시예들에 따르면, 복수의 다이렉트 콘택(DC)의 제2 수평 방향(Y 방향)에 따른 양 측벽은 버퍼층(132)에 접하는 부분, 층간 배리어막(134)에 접하는 부분, 층간 절연막(136) 접하는 부분, 및 매몰 절연막(126)에 접하는 부분을 포함할 수 있다.According to exemplary embodiments, the second horizontal direction (Y direction) side walls of the plurality of direct contacts (DC) may include a portion in contact with the buffer layer (132), a portion in contact with the interlayer barrier film (134), a portion in contact with the interlayer insulating film (136), and a portion in contact with the buried insulating film (126).

예시적인 실시예들에 따르면, 복수의 다이렉트 콘택(DC)은 각각 금속 실리사이드막(144)의 상면을 덮는 제1 부분(148a), 및 금속 실리사이드막(144)의 제2 수평 방향(Y 방향)에 따른 양 측면을 덮는 제2 부분(148b)을 포함할 수 있다. 예시적인 실시예들에 따르면, 금속 실리사이드막(144) 제2 수평 방향(Y 방향)에 따른 양 측면은 각각 제1 이격 공간(GV)을 사이에 두고 매몰 절연막(126)으로부터 이격될 수 있고, 제1 이격 공간(GV)은 금속 실리사이드막(144)의 제2 부분(148b)으로 채워질 수 있다. 예시적인 실시예들에 따르면, 금속 실리사이드막(144)의 제2 부분(148b)은 하부 리세스(RA)의 저면의 일부와 하부 내벽의 일부를 덮으며, 금속 실리사이드막(144)과 매몰 절연막(126) 사이에 개재될 수 있다.According to exemplary embodiments, the plurality of direct contacts (DC) may each include a first portion (148a) covering a top surface of the metal silicide film (144), and a second portion (148b) covering both side surfaces of the metal silicide film (144) along a second horizontal direction (Y direction). According to exemplary embodiments, both side surfaces of the metal silicide film (144) along the second horizontal direction (Y direction) may be spaced apart from the buried insulating film (126) with a first separation space (GV) therebetween, and the first separation space (GV) may be filled with the second portion (148b) of the metal silicide film (144). According to exemplary embodiments, the second portion (148b) of the metal silicide film (144) covers a portion of the bottom surface and a portion of the lower inner wall of the lower recess (RA), and may be interposed between the metal silicide film (144) and the buried insulating film (126).

일부 실시예들에 있어서, 집적회로 소자(100)는 제1 이격 공간(GV) 내에 형성된 보이드(void)를 포함할 수 있다. 일부 실시예들에 있어서, 상기 보이드는 금속 실리사이드막(144)에 의해 둘러싸일 수 있다. In some embodiments, the integrated circuit device (100) may include a void formed within the first separation space (GV). In some embodiments, the void may be surrounded by a metal silicide film (144).

다른 일부 실시예들에 있어서, 집적회로 소자(100)는 제1 이격 공간(GV)에 배치된 희생 절연 스페이서(142)(도 6c 참조)를 더 포함할 수 있다. 예를 들면, 희생 절연 스페이서(142)는 하부 리세스(RA)의 저면, 하부 리세스(RA) 내벽, 및 금속 실리사이드막(144)의 측면을 부분적으로 덮을 수 있다. 예를 들면, 희생 절연 스페이서(142)는 탄소 함유 물질로 이루어질 수 있다. 예를 들면, 희생 절연 스페이서(142)는 SiOC 또는 SiOCN을 포함할 수 있다. 예를 들면, 6a 내지 6d를 참조하여 후술하는 집적회로 소자(100)의 제조 과정에서, 희생 절연 스페이서(142)의 일부가 제1 이격 공간(GV)에 남을 수 있다.In some other embodiments, the integrated circuit device (100) may further include a sacrificial insulating spacer (142) (see FIG. 6c) disposed in the first separation space (GV). For example, the sacrificial insulating spacer (142) may partially cover the bottom surface of the lower recess (RA), the inner wall of the lower recess (RA), and the side surface of the metal silicide film (144). For example, the sacrificial insulating spacer (142) may be made of a carbon-containing material. For example, the sacrificial insulating spacer (142) may include SiOC or SiOCN. For example, during the manufacturing process of the integrated circuit device (100) described below with reference to FIGS. 6a to 6d, a portion of the sacrificial insulating spacer (142) may remain in the first separation space (GV).

다시 도 2a 및 도 2b를 참조하면, 기판(110)의 일부 영역에서, 복수의 상부 리세스(RB)가 형성될 수 있다. 예시적인 실시예들에 따르면, 복수의 상부 리세스(RB)의 저면을 통해 복수의 활성 영역(ACT) 각각의 일부가 노출될 수 있다. 예를 들면, 복수의 상부 리세스(RB)의 저면은 하부 리세스(RA)의 저면인 제1 수직 레벨(LV1)보다 높은 수직 레벨에 배치될 수 있다.Referring again to FIGS. 2A and 2B, a plurality of upper recesses (RB) may be formed in some areas of the substrate (110). According to exemplary embodiments, a portion of each of the plurality of active regions (ACT) may be exposed through bottom surfaces of the plurality of upper recesses (RB). For example, the bottom surfaces of the plurality of upper recesses (RB) may be arranged at a vertical level higher than the first vertical level (LV1), which is the bottom surface of the lower recesses (RA).

예시적인 실시예들에 따르면, 복수의 상부 리세스(RB) 내에 각각 복수의 베리드 콘택(BC)이 하나씩 배치될 수 있다. 예시적인 실시예들에 따르면, 복수의 베리드 콘택(BC)은 각각 기판(110) 내로 일부 연장되어 활성 영역(ACT)에 접할 수 있다. 예시적인 실시예들에 따르면, 복수의 베리드 콘택(BC)은 각각 내측 절연 스페이서(162) 및 갭필 절연 패턴(164)을 사이에 두고 다이렉트 콘택(DC) 및 금속 실리사이드막(144)로부터 이격될 수 있다.According to exemplary embodiments, a plurality of buried contacts (BC) may be arranged, one in each of the plurality of upper recesses (RB). According to exemplary embodiments, the plurality of buried contacts (BC) may each extend partly into the substrate (110) to contact the active region (ACT). According to exemplary embodiments, the plurality of buried contacts (BC) may each be spaced apart from the direct contact (DC) and the metal silicide film (144) with an inner insulating spacer (162) and a gapfill insulating pattern (164) therebetween.

일부 실시예들에 있어서, 복수의 베리드 콘택(BC)은 불순물이 도핑된 반도체 물질, 금속, 도전성 금속 질화물, 또는 이들의 조합으로 이루어질 수 있다. 예를 들면, 복수의 베리드 콘택(BC)은 각각 도핑된 폴리실리콘막, 에피택셜 성장된 실리콘막, 또는 이들의 조합으로 이루어질 수 있다.In some embodiments, the plurality of buried contacts (BC) can be formed of a doped semiconductor material, a metal, a conductive metal nitride, or a combination thereof. For example, the plurality of buried contacts (BC) can each be formed of a doped polysilicon film, an epitaxially grown silicon film, or a combination thereof.

일부 실시예들에 있어서, 하나의 다이렉트 콘택(DC)과, 상기 하나의 다이렉트 콘택(DC)을 사이에 두고 서로 대면하는 한 쌍의 베리드 콘택(BC)은 각각 복수의 활성 영역(ACT) 중 서로 다른 활성 영역(ACT)에 연결될 수 있다. 예를 들면, 복수의 활성 영역(ACT) 중에서 선택된 제1 활성 영역(ACT)이 다이렉트 콘택(DC)을 통해 하나의 비트 라인(BL)에 연결될 수 있다. 복수의 활성 영역(ACT) 중에서 선택되고, 상기 제1 활성 영역(ACT)과 인접하게 배치되며 상기 제1 활성 영역(ACT)을 사이에 두고 제1 수평 방향(X 방향)에서 이격된 제2 활성 영역(ACT)과 제3 활성 영역(ACT)은 각각 베리드 콘택(BC)에 연결될 수 있다. 상기 제2 활성 영역(ACT)에 연결된 베리드 콘택(BC)은 다이렉트 콘택(DC)을 사이에 두고 제3 활성 영역(ACT)에 연결된 베리드 콘택(BC)으로부터 제1 수평 방향(X 방향)에서 이격될 수 있다.In some embodiments, a direct contact (DC) and a pair of buried contacts (BC) facing each other with the direct contact (DC) interposed therebetween may be respectively connected to different active regions (ACTs) among the plurality of active regions (ACTs). For example, a first active region (ACT) selected from the plurality of active regions (ACTs) may be connected to a bit line (BL) through the direct contact (DC). A second active region (ACT) and a third active region (ACT) selected from the plurality of active regions (ACTs), arranged adjacent to the first active region (ACT), and spaced apart in a first horizontal direction (X direction) with the first active region (ACT) interposed therebetween, may each be connected to the buried contact (BC). The buried contact (BC) connected to the second active region (ACT) can be spaced apart in the first horizontal direction (X direction) from the buried contact (BC) connected to the third active region (ACT) with a direct contact (DC) therebetween.

예시적인 실시예들에 따르면, 복수의 베리드 콘택(BC) 상에 복수의 도전성 랜딩 패드(LP)가 배치될 수 있다. 복수의 도전성 랜딩 패드(LP)는 각각 베리드 콘택(BC) 상에서 수직 방향(Z 방향)으로 연장될 수 있다. 예를 들면, 복수의 도전성 랜딩 패드(LP)는 복수의 비트 라인(BL) 각각의 사이의 공간과 복수의 캡핑 절연 패턴(154) 각각의 사이의 공간을 지나도록 수직 방향(Z 방향)으로 길게 연장되고, 복수의 비트 라인(BL)의 일부와 수직으로 오버랩되도록 복수의 캡핑 절연 패턴(154) 각각의 상부까지 연장될 수 있다. 예시적인 실시예들에 따르면, 복수의 도전성 랜딩 패드(LP)와 복수의 베리드 콘택(BC) 사이에는 각각 도전성 배리어막(182)이 배치될 수 있다. According to exemplary embodiments, a plurality of conductive landing pads (LP) may be arranged on a plurality of buried contacts (BC). The plurality of conductive landing pads (LP) may each extend in a vertical direction (Z direction) on the buried contacts (BC). For example, the plurality of conductive landing pads (LP) may extend in a vertical direction (Z direction) so as to pass through a space between each of the plurality of bit lines (BL) and a space between each of the plurality of capping insulating patterns (154), and may extend to an upper portion of each of the plurality of capping insulating patterns (154) so as to vertically overlap a portion of the plurality of bit lines (BL). According to exemplary embodiments, a conductive barrier film (182) may be arranged between each of the plurality of conductive landing pads (LP) and the plurality of buried contacts (BC).

예시적인 실시예들에 따르면, 복수의 도전성 랜딩 패드(LP)는 각각 도전성 배리어막(182)과 도전층(184)을 포함할 수 있다. 일부 실시예들에 있어서, 도전성 배리어막(182)은 Ti/TiN 적층 구조로 이루어질 수 있다. 도전층(184)은 금속으로 이루어질 수 있다. 예를 들면, 도전층(184)은 텅스텐(W)으로 이루어질 수 있다.According to exemplary embodiments, the plurality of conductive landing pads (LP) may each include a conductive barrier film (182) and a conductive layer (184). In some embodiments, the conductive barrier film (182) may be formed of a Ti/TiN laminated structure. The conductive layer (184) may be formed of a metal. For example, the conductive layer (184) may be formed of tungsten (W).

도시되지는 않았으나, 복수의 도전성 배리어막(182)과 복수의 베리드 콘택(BC) 사이에 각각 금속 실리사이드막(미도시)이 배치될 수 있다. 예를 들면, 상기 금속 실리사이드막(미도시)은 코발트 실리사이드, 니켈 실리사이드, 또는 망간 실리사이드로 이루어질 수 있으나, 이들에 한정되는 것은 아니다.Although not shown, a metal silicide film (not shown) may be disposed between each of the plurality of conductive barrier films (182) and the plurality of buried contacts (BC). For example, the metal silicide film (not shown) may be made of, but is not limited to, cobalt silicide, nickel silicide, or manganese silicide.

예시적인 실시예들에 따르면, 복수의 도전성 랜딩 패드(LP)는 절연 구조물(192)에 의해 상호 전기적으로 절연될 수 있다. 예를 들면, 복수의 도전성 랜딩 패드(LP)는 평면적 관점에서, 복수의 아일랜드형 패턴 형상을 가질 수 있다.According to exemplary embodiments, the plurality of conductive landing pads (LP) may be electrically insulated from each other by an insulating structure (192). For example, the plurality of conductive landing pads (LP) may have a plurality of island-like pattern shapes in a planar view.

예시적인 실시예들에 따르면, 복수의 비트 라인(BL) 중 제1 수평 방향(X 방향)에서 서로 인접한 한 쌍의 비트 라인(BL) 사이에서 복수의 베리드 콘택(BC)이 제2 수평 방향(Y 방향)을 따라 일렬로 배열될 수 있다. 제2 수평 방향(Y 방향)을 따라 일렬로 배열된 복수의 베리드 콘택(BC) 각각의 사이에는 절연 펜스(미도시)가 배치될 수 있다. 예를 들면, 복수의 베리드 콘택(BC)은 복수의 절연 펜스(미도시)에 의해 상호 절연될 수 있다. 상기 복수의 절연 펜스(미도시)는 각각 기판(110) 상에서 수직 방향(Z 방향)으로 연장되는 기둥 형상을 가질 수 있다. According to exemplary embodiments, a plurality of buried contacts (BC) may be arranged in a row along a second horizontal direction (Y direction) between a pair of bit lines (BL) that are adjacent to each other in a first horizontal direction (X direction) among a plurality of bit lines (BL). An insulating fence (not shown) may be arranged between each of the plurality of buried contacts (BC) arranged in a row along the second horizontal direction (Y direction). For example, the plurality of buried contacts (BC) may be insulated from each other by the plurality of insulating fences (not shown). Each of the plurality of insulating fences (not shown) may have a pillar shape extending in a vertical direction (Z direction) on the substrate (110).

예시적인 실시예들에 따르면, 복수의 비트 라인(BL)과 복수의 도전성 랜딩 패드(LP)와의 사이에 각각 내측 절연 스페이서(162), 중간 절연 스페이서(166), 및 외측 절연 스페이서(168)가 개재될 수 있다. 예시적인 실시예들에 따르면, 내측 절연 스페이서(162), 중간 절연 스페이서(166), 및 외측 절연 스페이서(168)는 각각 제2 수평 방향(Y 방향)을 따라 비트 라인(BL)과 평행하게 연장될 수 있다. According to exemplary embodiments, an inner insulating spacer (162), a middle insulating spacer (166), and an outer insulating spacer (168) may be interposed between a plurality of bit lines (BL) and a plurality of conductive landing pads (LP), respectively. According to exemplary embodiments, the inner insulating spacer (162), the middle insulating spacer (166), and the outer insulating spacer (168) may each extend parallel to the bit lines (BL) along the second horizontal direction (Y direction).

예시적인 실시예들에 따르면, 중간 절연 스페이서(166)는 내측 절연 스페이서(162) 상에서 복수의 비트 라인(BL)의 양 측벽 및 캡핑 절연 패턴(154)의 양 측벽을 덮을 수 있다. 외측 절연 스페이서(168)는 중간 절연 스페이서(166) 상에서 복수의 비트 라인(BL)의 양 측벽 및 캡핑 절연 패턴(154)의 양 측벽을 덮을 수 있다. 예시적인 실시예들에 따르면, 외측 절연 스페이서(168)는 베리드 콘택(BC)에 접하는 부분 및 랜딩 패드(LP)에 접하는 부분을 포함할 수 있다. 예를 들면, 외측 절연 스페이서(168)는 베리드 콘택(BC) 및 랜딩 패드(LP)에 대면하는 측벽과, 중간 절연 스페이서(166)에 대면하는 측벽을 가질 수 있다.According to exemplary embodiments, the middle insulating spacer (166) may cover both sidewalls of the plurality of bit lines (BL) and both sidewalls of the capping insulating pattern (154) on the inner insulating spacer (162). The outer insulating spacer (168) may cover both sidewalls of the plurality of bit lines (BL) and both sidewalls of the capping insulating pattern (154) on the middle insulating spacer (166). According to exemplary embodiments, the outer insulating spacer (168) may include a portion contacting the buried contact (BC) and a portion contacting the landing pad (LP). For example, the outer insulating spacer (168) may have a sidewall facing the buried contact (BC) and the landing pad (LP), and a sidewall facing the middle insulating spacer (166).

예시적인 실시예들에 따르면, 복수의 비트 라인(152)은 각각 내측 절연 스페이서(162), 중간 절연 스페이서(166), 및 외측 절연 스페이서(168)를 사이에 두고 베리드 콘택(BC) 및 랜딩 패드(LP)로부터 이격될 수 있다. According to exemplary embodiments, a plurality of bit lines (152) may be spaced from the buried contact (BC) and the landing pad (LP) by an inner insulating spacer (162), a middle insulating spacer (166), and an outer insulating spacer (168), respectively.

일부 실시예들에 있어서, 내측 절연 스페이서(162)는 실리콘 질화막으로 이루어질 수 있다. 일부 시릿예들에 있어서, 중간 절연 스페이서(166)는 실리콘 산화막, 에어 스페이서(air spacer), 또는 이들의 조합으로 이루어질 수 있다. 본 명세서에서 용어 "에어"는 대기 또는 제조 공정 중에 존재할 수 있는 다른 가스들을 의미할 수 있다. 일부 실시예들에 있어서, 외측 절연 스페이서(168)는 실리콘 질화막으로 이루어질 수 있다.In some embodiments, the inner insulating spacer (162) may be formed of a silicon nitride film. In some embodiments, the middle insulating spacer (166) may be formed of a silicon oxide film, an air spacer, or a combination thereof. The term “air” herein may refer to the atmosphere or other gases that may be present during the manufacturing process. In some embodiments, the outer insulating spacer (168) may be formed of a silicon nitride film.

예시적인 실시예들에 따른 집적회로 소자(100)의 금속 실리사이드막(144)은 제1 이격 공간(GV)의 수평 폭만큼 다이렉트 콘택(DC) 및 비트 라인(152)을 형성하기 위한 식각 마진이 확보될 수 있다. 이에 따라, 다이렉트 콘택(DC) 및 비트 라인(152)이 끊김 등의 불량 없이 안정적으로 형성될 수 있고, 인접한 베리드 콘택(BC)과의 충분한 이격 거리가 확보되어 집적회로 소자의 전기적 신뢰성이 향상될 수 있다. According to exemplary embodiments, the metal silicide film (144) of the integrated circuit device (100) can secure an etching margin for forming a direct contact (DC) and a bit line (152) as wide as the horizontal width of the first separation space (GV). Accordingly, the direct contact (DC) and the bit line (152) can be stably formed without defects such as disconnection, and a sufficient separation distance from the adjacent buried contact (BC) is secured, so that the electrical reliability of the integrated circuit device can be improved.

도 4a는 일부 실시예들에 따른 집적회로 소자(100a)를 설명하기 위한 단면도로서, 도 1의 Y1-Y1'선에 따른 단면에 대응되는 부분을 나타낸 것이다. 도 4b는 도 4a의 "EX3"으로 표시된 부분의 확대도이다. 도 4a 및 도 4b에서, 도 3a 및 도 3b와 동일한 참조 부호는 동일 부재를 나타내며, 이하에서는 이들에 대한 중복 설명을 생략한다. 다만, 동일 부재라도 구조 및 배치관계 등에 있어서 차이가 있는 내용에 대해서는 새롭게 설명한다.FIG. 4A is a cross-sectional view for explaining an integrated circuit element (100a) according to some embodiments, and shows a part corresponding to a cross-section along line Y1-Y1' of FIG. 1. FIG. 4B is an enlarged view of a part indicated as "EX3" of FIG. 4A. In FIGS. 4A and 4B, the same reference numerals as in FIGS. 3A and 3B indicate the same parts, and their redundant descriptions are omitted below. However, even for the same parts, differences in structure and arrangement relationships, etc. are newly described.

도 3a 및 도 3b를 참조하면, 다이렉트 콘택(DC)은 비트 라인(152)에 접하는 상측 부분(149a)과, 상측 부분(149a)보다 낮은 수직 레벨에 배치되며 금속 실리사이드막(144)에 접하는 하측 부분(149b)을 포함할 수 있다. 예시적인 실시예들에 따르면, 다이렉트 콘택(DC)의 상측 부분(149a)은 기판(110)의 일부 영역에 형성된 제1 하부 리세스(RA1)의 일부를 채울 수 있다. 예시적인 실시예들에 따르면, 다이렉트 콘택(DC)의 상측 부분(149a)의 제2 수평 방향(Y 방향)에 따른 양 측벽은 제1 하부 리세스(RA1)의 내벽에 접할 수 있다. 예시적인 실시예들에 따르면, 제1 하부 리세스(RA1)보다 낮은 수직 레벨에, 제1 하부 리세스(RA1)로부터 연장되며 제1 하부 리세스(RA1)보다 수평 방향(X 방향 및/또는 Y 방향)에 따른 폭이 더 좁은 제2 하부 리세스(RA2)가 형성될 수 있다. 예시적인 실시예들에 따르면, 제2 하부 리세스(RA2)의 저면을 통해 노출된 활성 영역(ACT)은 금속 실리사이드막(144)에 의해 덮일 수 있고, 다이렉트 콘택(DC)의 하측 부분(149b) 금속 실리사이드막(144) 상에서 금속 실리사이드막(144)에 접하며 제2 하부 리세스(RA2)의 일부를 채울 수 있다. 예시적인 실시예들에 따른 다이렉트 콘택(DC)의 제2 수평 방향(Y 방향)에 따른 양 측벽은 제2 하부 리세스(RA2)의 내벽에 접할 수 있다.Referring to FIGS. 3A and 3B , the direct contact (DC) may include an upper portion (149a) in contact with the bit line (152) and a lower portion (149b) disposed at a lower vertical level than the upper portion (149a) and in contact with the metal silicide film (144). According to exemplary embodiments, the upper portion (149a) of the direct contact (DC) may fill a portion of a first lower recess (RA1) formed in a portion of the substrate (110). According to exemplary embodiments, both sidewalls of the upper portion (149a) of the direct contact (DC) along the second horizontal direction (Y direction) may be in contact with an inner wall of the first lower recess (RA1). According to exemplary embodiments, a second lower recess (RA2) may be formed at a vertical level lower than the first lower recess (RA1), extending from the first lower recess (RA1) and having a narrower width in the horizontal direction (X direction and/or Y direction) than the first lower recess (RA1). According to exemplary embodiments, an active region (ACT) exposed through a bottom surface of the second lower recess (RA2) may be covered by a metal silicide film (144), and a lower portion (149b) of the direct contact (DC) may be in contact with the metal silicide film (144) on the metal silicide film (144) and may fill a portion of the second lower recess (RA2). According to exemplary embodiments, both sidewalls of the direct contact (DC) in the second horizontal direction (Y direction) may be in contact with an inner wall of the second lower recess (RA2).

예시적인 실시예들에 따르면, 다이렉트 콘택(DC)의 상측 부분(149a)은 제2 수평 방향(Y 방향)에 따른 폭인 제1 폭(w1)을 가질 수 있고, 다이렉트 콘택(DC)의 하측 부분(149b)은 제2 수평 방향(Y 방향)에 따른 폭인 제2 폭(w2)을 가질 수 있다. 예시적인 실시예들에 따르면, 하측 부분(149b)의 제2 폭(w2)은 상측 부분(149a)의 제1 폭(w1)보다 좁을 수 있다. 예시적인 실시예들에 따르면, 상측 부분(149a)의 제2 수평 방향(Y 방향)에 따른 양 측벽은, 하측 부분(149b)의 제2 수평 방향(Y 방향)에 따른 양 측벽에 대하여 외측으로 확장될 수 있다.According to exemplary embodiments, the upper portion (149a) of the direct contact (DC) may have a first width (w1) which is a width along the second horizontal direction (Y direction), and the lower portion (149b) of the direct contact (DC) may have a second width (w2) which is a width along the second horizontal direction (Y direction). According to exemplary embodiments, the second width (w2) of the lower portion (149b) may be narrower than the first width (w1) of the upper portion (149a). According to exemplary embodiments, both sidewalls of the upper portion (149a) along the second horizontal direction (Y direction) may extend outwardly with respect to both sidewalls of the lower portion (149b) along the second horizontal direction (Y direction).

예시적인 실시예들에 따르면, 다이렉트 콘택(DC)의 상측 부분(149a) 및 다이렉트 콘택(DC)의 하측 부분(149b)은 각각 비트 라인(152)의 저면으로부터 멀어질수록 제2 수평 방향(Y 방향)에 따른 폭이 좁아지도록 테이퍼진 형상을 가질 수 있다. 예를 들면, 상측 부분(149a)의 제2 수평 방향(Y 방향)에 따른 양 측벽 및 하측 부분(149b)의 제2 수평 방향(Y 방향)에 따른 양 측벽은 각각 비트 라인(152)의 저면에 대한 경사를 가질 수 있다.According to exemplary embodiments, the upper portion (149a) of the direct contact (DC) and the lower portion (149b) of the direct contact (DC) may have a tapered shape such that the width along the second horizontal direction (Y direction) becomes narrower as they move away from the bottom surface of the bit line (152), respectively. For example, both sidewalls along the second horizontal direction (Y direction) of the upper portion (149a) and both sidewalls along the second horizontal direction (Y direction) of the lower portion (149b) may each have an incline with respect to the bottom surface of the bit line (152).

예시적인 실시예들에 따르면, 하측 부분(149b)의 제2 수평 방향(Y 방향)에 따른 양 측벽의 경사는, 상측 부분(149a)의 제2 수평 방향(Y 방향)에 따른 양 측벽의 경사보다 가파를 수 있다. 예를 들면, 상측 부분(149a)의 제2 수평 방향(Y 방향)에 따른 양 측벽은 비트 라인(152)의 저면에 대하여 제1 경사각을 가질 수 있고, 하측 부분(149b)의 제2 수평 방향(Y 방향)에 따른 양 측벽은 비트 라인(152)은 저면에 대하여 제2 경사각을 가질 수 있다. 예를 들면, 상기 제2 경사각은 상기 제1 경사각보다 클 수 있다.According to exemplary embodiments, the inclination of both side walls along the second horizontal direction (Y direction) of the lower portion (149b) may be steeper than the inclination of both side walls along the second horizontal direction (Y direction) of the upper portion (149a). For example, both side walls along the second horizontal direction (Y direction) of the upper portion (149a) may have a first inclination angle with respect to a bottom surface of the bit line (152), and both side walls along the second horizontal direction (Y direction) of the lower portion (149b) may have a second inclination angle with respect to a bottom surface of the bit line (152). For example, the second inclination angle may be greater than the first inclination angle.

일부 실시예들에 있어서, 상기 제1 경사각은 70°이상 및 90°이하의 범위를 가질 수 있다. 일부 실시예들에 있어서, 상기 제2 경사각은 80°이상 및 90°이하의 범위를 가질 수 있다.In some embodiments, the first inclination angle can have a range of 70° or more and 90° or less. In some embodiments, the second inclination angle can have a range of 80° or more and 90° or less.

예시적인 실시예들에 따르면, 다이렉트 콘택(DC)의 제2 수평 방향(Y 방향)에 따른 양 측벽은 기울기 변화를 갖는 변곡부를 포함할 수 있다. 예를 들면, 상기 변곡부는 상측 부분(149a)과 하측 부분(149b)의 사이에서 정의될 수 있다. 예시적인 실시예들에 따르면, 상기 변곡부는 비트 라인(152)의 저면보다 낮은 제2 수직 레벨(LV2)에 배치될 수 있다. 예시적인 실시예들에 따르면, 제2 하부 리세스(RA2)의 저면은 제2 수직 레벨(LV2)보다 낮은 제3 수직 레벨(LV3)에 배치될 수 있다.According to exemplary embodiments, both side walls along the second horizontal direction (Y direction) of the direct contact (DC) may include an inflection portion having a change in slope. For example, the inflection portion may be defined between the upper portion (149a) and the lower portion (149b). According to exemplary embodiments, the inflection portion may be arranged at a second vertical level (LV2) lower than a bottom surface of the bit line (152). According to exemplary embodiments, a bottom surface of the second lower recess (RA2) may be arranged at a third vertical level (LV3) lower than the second vertical level (LV2).

예시적인 실시예들에 따르면, 복수의 다이렉트 콘택(DC)의 상측 부분(149a)의 제2 수평 방향(Y 방향)에 따른 양 측벽은 버퍼층(132)에 접하는 부분, 층간 배리어막(134)에 접하는 부분, 층간 절연막(136) 접하는 부분을 포함할 수 있다. 복수의 다이렉트 콘택(DC)의 하측 부분(149b)의 제2 수평 방향(Y 방향)에 따른 양 측벽은 및 매몰 절연막(126)에 접하는 부분을 포함할 수 있다.According to exemplary embodiments, both side walls along the second horizontal direction (Y direction) of the upper portion (149a) of the plurality of direct contacts (DC) may include a portion in contact with the buffer layer (132), a portion in contact with the interlayer barrier film (134), and a portion in contact with the interlayer insulating film (136). Both side walls along the second horizontal direction (Y direction) of the lower portion (149b) of the plurality of direct contacts (DC) may include a portion in contact with the buried insulating film (126).

예시적인 실시예들에 따르면, 복수의 다이렉트 콘택(DC)은 복수의 금속 실리사이드막(144)의 상면을 전체적으로 덮을 수 있다. 도 2a 내지 도 3b를 참조하여 설명한 집적회로 소자(100)에서, 금속 실리사이드막(144)의 제2 수평 방향(Y 방향)에 따른 양 측벽이 다이렉트 콘택(DC)에 접했던 것과 달리, 집적회로 소자(100a)의 금속 실리사이드막(144)의 제2 수평 방향(Y 방향)에 따른 양 측벽은 매몰 절연막(126)에 접할 수 있다. 예를 들면, 집적회로 소자(100a)는 도 2a 내지 도 3b를 참조하여 설명한 제1 이격 공간(GV)을 포함하지 않을 수 있다. According to exemplary embodiments, the plurality of direct contacts (DC) may entirely cover the upper surfaces of the plurality of metal silicide films (144). Unlike the integrated circuit device (100) described with reference to FIGS. 2A to 3B in which both sidewalls of the metal silicide film (144) along the second horizontal direction (Y direction) are in contact with the direct contacts (DC), in the integrated circuit device (100a), both sidewalls of the metal silicide film (144) along the second horizontal direction (Y direction) may be in contact with the buried insulating film (126). For example, the integrated circuit device (100a) may not include the first separation space (GV) described with reference to FIGS. 2A to 3B.

예시적인 실시예들에 따른 집적회로 소자(100a)의 다이렉트 콘택(DC)은 상측 부분(149a) 및 하측 부분(149b)을 포함하여, 다이렉트 콘택(DC) 및 비트 라인(152)을 형성하기 위한 식각 마진이 확보될 수 있고, 이에 따라 인접한 도전 영역들 사이의 신뢰성 있는 전기적 접속을 확보할 수 있다.The direct contact (DC) of the integrated circuit device (100a) according to exemplary embodiments includes an upper portion (149a) and a lower portion (149b), so that an etching margin for forming the direct contact (DC) and the bit line (152) can be secured, thereby ensuring reliable electrical connection between adjacent conductive regions.

도 5는 예시적인 실시예들에 따른 집적회로 소자(100, 100a)의 제조 방법을 설명하기 위한 평편도이다.FIG. 5 is a schematic diagram illustrating a method for manufacturing an integrated circuit device (100, 100a) according to exemplary embodiments.

도 6a 내지 도 6d는 예시적인 실시예들에 따른 집적회로 소자(100)의 제조 방법을 설명하기 위하여 공정 순서에 따라 도시한 단면도들로서, 도 5의 X2-X2'선에 따른 단면을 나타낸 것이다. 구체적으로, 도 6a 내지 도 6d는 도 2a에 대응되는 부분을 나타낸다. FIGS. 6A to 6D are cross-sectional views illustrating a process sequence for explaining a method of manufacturing an integrated circuit device (100) according to exemplary embodiments, and illustrate cross-sections taken along line X2-X2' of FIG. 5. Specifically, FIGS. 6A to 6D illustrate portions corresponding to FIG. 2A.

도 5 및 6a를 함께 참조하면, 기판(110)에 소자 분리 트렌치(112T)를 형성하고, 소자 분리 트렌치(112T) 내에 소자 분리막(112)을 형성할 수 있다. 소자 분리막(112)에 의해 기판(110)에 복수의 활성 영역(ACT)이 정의될 수 있다. Referring to FIGS. 5 and 6A together, a device isolation trench (112T) may be formed in a substrate (110), and a device isolation film (112) may be formed within the device isolation trench (112T). A plurality of active regions (ACTs) may be defined in the substrate (110) by the device isolation film (112).

그 후, 기판(110)에 복수의 워드 라인 트렌치(120T)(도 3a 참조)를 형성할 수 있다. 상기 복수의 워드 라인 트렌치(120T)는 제1 수평 방향(X 방향)으로 상호 평행하게 연장되며, 활성 영역(ACT)을 가로지르는 라인 형상을 가질 수 있다. 상기 복수의 워드 라인 트렌치(120T)가 형성된 결과물을 세정한 후, 상기 복수의 워드 라인 트렌치(120T) 각각의 내부에 게이트 유전막(122), 워드 라인(124), 및 매몰 절연막(126)을 차례로 형성할 수 있다(도 3a 참조). 복수의 워드 라인(124)을 형성하기 전 또는 후에, 복수의 활성 영역(ACT)의 상부에 복수의 소스/드레인 영역을 형성하기 위한 이온 주입 공정이 수행될 수 있다.Thereafter, a plurality of word line trenches (120T) (see FIG. 3a) may be formed in the substrate (110). The plurality of word line trenches (120T) may extend in parallel to each other in the first horizontal direction (X direction) and may have a line shape crossing the active region (ACT). After the resultant product in which the plurality of word line trenches (120T) are formed is cleaned, a gate dielectric film (122), a word line (124), and a buried insulating film (126) may be sequentially formed inside each of the plurality of word line trenches (120T) (see FIG. 3a). Before or after forming the plurality of word lines (124), an ion implantation process may be performed to form a plurality of source/drain regions on the upper portions of the plurality of active regions (ACT).

그 후, 기판(110) 상에 버퍼층(132), 층간 배리어막(134), 및 층간 절연막(136)을 순차적으로 형성할 수 있다. 예를 들면, 버퍼층(132), 층간 배리어막(134), 및 층간 절연막(136)은 원자층 적층(ALD) 공정, 화학 기상 증착(CVD) 공정, 물리 기상 증착(PVD) 공정, 플라즈마 강화 CVD (PECVD) 공정, 저압 CVD (LPCVD) 공정 등을 통해 형성될 수 있다.Thereafter, a buffer layer (132), an interlayer barrier film (134), and an interlayer insulating film (136) can be sequentially formed on the substrate (110). For example, the buffer layer (132), the interlayer barrier film (134), and the interlayer insulating film (136) can be formed through an atomic layer deposition (ALD) process, a chemical vapor deposition (CVD) process, a physical vapor deposition (PVD) process, a plasma enhanced CVD (PECVD) process, a low-pressure CVD (LPCVD) process, etc.

그 후, 기판(110)의 일부 영역에서, 복수의 활성 영역(ACT)의 일부, 소자 분리막(112)의 일부, 버퍼층(132)의 일부, 층간 배리어막(134)의 일부, 및 층간 절연막(136)의 일부를 제거하여, 하부 리세스(RA)를 형성할 수 있다. 하부 리세스(RA)에 의해 복수의 돌출 구조물(EMB)이 정의될 수 있다. 예를 들면, 돌출 구조물(EMB)은 하부 리세스(RA)의 저면으로부터 수직 방향(Z 방향)으로 돌출될 수 있다.Thereafter, in some areas of the substrate (110), a portion of a plurality of active regions (ACTs), a portion of the device isolation film (112), a portion of the buffer layer (132), a portion of the interlayer barrier film (134), and a portion of the interlayer insulating film (136) may be removed to form a lower recess (RA). A plurality of protruding structures (EMB) may be defined by the lower recess (RA). For example, the protruding structures (EMB) may protrude in a vertical direction (Z direction) from a bottom surface of the lower recess (RA).

하부 리세스(RA)의 저면에서, 복수의 활성 영역(ACT) 중에서 선택된 제1 활성 영역(A1)이 노출될 수 있다. 예를 들면, 하부 리세스(RA)의 저면은 제1 수직 레벨(LV1)에 배치될 수 있다. 복수의 활성 영역(ACT) 중에서 선택되고, 제1 활성 영역(A1)과 인접하게 배치되며, 제1 활성 영역(A1)로부터 제1 수평 방향(X 방향)에서 이격된 제2 활성 영역(A2)과 제3 활성 영역(A3) 각각의 측벽은, 하부 리세스(RA)를 통해 일부 노출될 수 있다. At a bottom surface of the lower recess (RA), a first active region (A1) selected from among a plurality of active regions (ACT) can be exposed. For example, the bottom surface of the lower recess (RA) can be arranged at a first vertical level (LV1). Sidewalls of each of a second active region (A2) and a third active region (A3) selected from among the plurality of active regions (ACT), arranged adjacent to the first active region (A1), and spaced apart from the first active region (A1) in a first horizontal direction (X direction) can be partially exposed through the lower recess (RA).

도 6b를 참조하면, 도 6a의 결과물에서, 하부 리세스(RA)의 내벽을 덮는 희생 절연 스페이서(142)를 형성할 수 있다. 예를 들면, 희생 절연 스페이서(142)는 기판(110) 상에 하부 리세스(RA)의 저면, 내벽, 및 층간 절연막(136)의 상면을 컨포멀하게 덮는 절연막을 형성한 후, 식각을 통해 상기 절연막의 일부를 제거하여 형성할 수 있다. Referring to FIG. 6b, in the result of FIG. 6a, a sacrificial insulating spacer (142) covering the inner wall of the lower recess (RA) can be formed. For example, the sacrificial insulating spacer (142) can be formed by forming an insulating film conformally covering the bottom surface, inner wall, and upper surface of the interlayer insulating film (136) of the lower recess (RA) on the substrate (110), and then removing a portion of the insulating film through etching.

희생 절연 스페이서(142)는 하부 리세스(RA)의 내벽을 전체적으로 덮을 수 있다. 예를 들면, 희생 절연 스페이서(142)는 하부 리세스(RA)를 통해 노출된 제2 활성 영역(A2)의 측벽 및 제3 활성 영역(A3)의 측벽을 덮을 수 있다. 희생 절연 스페이서(142)는 하부 리세스(RA)를 통해 노출된 버퍼층(132)의 측벽, 층간 배리어막(134)의 측벽, 및 층간 절연막(136)의 측벽을 덮을 수 있다.The sacrificial insulating spacer (142) can cover the entire inner wall of the lower recess (RA). For example, the sacrificial insulating spacer (142) can cover the sidewall of the second active region (A2) and the sidewall of the third active region (A3) exposed through the lower recess (RA). The sacrificial insulating spacer (142) can cover the sidewall of the buffer layer (132), the sidewall of the interlayer barrier film (134), and the sidewall of the interlayer insulating film (136) exposed through the lower recess (RA).

도 6c를 참조하면, 도 6b의 결과물에서, 하부 리세스(RA)의 저면을 덮는 금속 실리사이드막(144)을 형성할 수 있다. 예를 들면, 금속 실리사이드막(144)은 하부 리세스(RA)의 저면을 통해 노출된 제1 활성 영역(A1)의 실리콘을 에피택셜 성장 시킨 후, 에피택셜 막 상에 금속막을 증착하고 어닐링하여 형성할 수 있다. Referring to FIG. 6c, in the result of FIG. 6b, a metal silicide film (144) covering the bottom surface of the lower recess (RA) can be formed. For example, the metal silicide film (144) can be formed by epitaxially growing silicon of the first active region (A1) exposed through the bottom surface of the lower recess (RA), and then depositing and annealing a metal film on the epitaxial film.

금속 실리사이드막(144)은 하부 리세스(RA)의 저면을 통해 노출된 제1 활성 영역(A1)의 상면과 소자 분리막(112)의 상면을 덮을 수 있다. 금속 실리사이드막(144)의 양 측벽은 희생 절연 스페이서(142)에 접하며, 희생 절연 스페이서(142)를 사이에 두고 인접한 복수의 활성 영역(ACT)의 측벽(예를 들면, 제2 활성 영역(A2)의 측벽 및 제3 활성 영역(A3)의 측벽)과 대면할 수 있다. The metal silicide film (144) can cover the upper surface of the first active region (A1) exposed through the bottom surface of the lower recess (RA) and the upper surface of the device isolation film (112). Both sidewalls of the metal silicide film (144) are in contact with the sacrificial insulating spacer (142) and can face the sidewalls of a plurality of adjacent active regions (ACTs) with the sacrificial insulating spacer (142) interposed therebetween (for example, the sidewall of the second active region (A2) and the sidewall of the third active region (A3)).

도 6d를 참조하면, 도 6c의 결과물에서, 희생 절연 스페이서(142)를 제거할 수 있다. 예를 들면, 희생 절연 스페이서(142)는 산소 함유 분위기 하에서 수행되는 애싱(ashing) 공정을 통해 제거될 수 있다. 이에 따라, 하부 리세스(RA)의 내벽이 노출될 수 있고, 금속 실리사이드막(144)의 양 측벽이 노출될 수 있다. 예를 들면, 금속 실리사이드막(144)의 양 측벽과 제2 및 제3 활성 영역(A2, A3) 사이에 있던 희생 절연 스페이서(142)가 제거되어, 제1 이격 공간(GV)이 형성될 수 있다. 다른 일부 실시예들에 있어서, 제1 이격 공간(GV)에 제거되지 않고 남은 희생 절연 스페이서(142)의 일부가 배치될 수 있다.Referring to FIG. 6d, in the result of FIG. 6c, the sacrificial insulating spacer (142) can be removed. For example, the sacrificial insulating spacer (142) can be removed through an ashing process performed under an oxygen-containing atmosphere. Accordingly, the inner wall of the lower recess (RA) can be exposed, and both sidewalls of the metal silicide film (144) can be exposed. For example, the sacrificial insulating spacer (142) between the both sidewalls of the metal silicide film (144) and the second and third active regions (A2, A3) can be removed, thereby forming a first separation space (GV). In some other embodiments, a portion of the sacrificial insulating spacer (142) that is not removed and remains in the first separation space (GV) can be placed.

그 후, 하부 리세스(RA)의 남은 공간을 채우는 제1 도전막(146)을 형성할 수 있다. 예를 들면, 제1 도전막(146)은 제1 이격 공간(GV)을 채울 수 있고, 하부 리세스(RA)의 내벽 및 층간 절연막(136)의 상면을 덮을 수 있다.Thereafter, a first conductive film (146) can be formed to fill the remaining space of the lower recess (RA). For example, the first conductive film (146) can fill the first separation space (GV) and cover the inner wall of the lower recess (RA) and the upper surface of the interlayer insulating film (136).

도 6d 및 도 2a를 함께 참조하면, 제1 도전막(146) 상에 제2 도전막(미도시), 및 캡핑 절연막(미도시)을 형성한 후, 제1 도전막(146) 상에 제2 도전막(미도시), 및 캡핑 절연막(미도시)의 일부를 제거하여 복수의 다이렉트 콘택(DC), 복수의 비트 라인(152), 및 복수의 캡핑 절연 패턴(154)을 형성할 수 있다. 이 과정에서, 층간 절연막(136)의 일부가 제거될 수 있다. 예시적인 실시예들에 따르면, 층간 배리어막(134)은 버퍼층(132) 및 버퍼층(132) 아래에 배치된 복수의 활성 영역(ACT)을 보호하는 역할을 수행할 수 있다.Referring to FIG. 6d and FIG. 2a together, after forming a second conductive film (not shown) and a capping insulating film (not shown) on a first conductive film (146), a portion of the second conductive film (not shown) and the capping insulating film (not shown) may be removed on the first conductive film (146) to form a plurality of direct contacts (DC), a plurality of bit lines (152), and a plurality of capping insulating patterns (154). In this process, a portion of the interlayer insulating film (136) may be removed. According to exemplary embodiments, the interlayer barrier film (134) may serve to protect the buffer layer (132) and a plurality of active regions (ACTs) disposed below the buffer layer (132).

그 후, 하부 리세스(RA) 내에 내측 절연 스페이서(162) 및 갭필 절연 패턴(164)을 형성한 후, 중간 절연 스페이서(166)와 외측 절연 스페이서(168)를 형성할 수 있다.After that, an inner insulating spacer (162) and a gapfill insulating pattern (164) are formed within the lower recess (RA), and then an intermediate insulating spacer (166) and an outer insulating spacer (168) can be formed.

그 후, 복수의 상부 리세스(RB)를 형성하고, 복수의 상부 리세스(RB) 내에 복수의 절연 펜스(미도시) 및 복수의 베리드 콘택(BC)을 형성할 수 있다. 그 후, 복수의 베리드 콘택(BC) 상에 복수의 랜딩 패드(LP)와 절연 구조물(192)을 형성하고, 복수의 랜딩 패드(LP) 상에 커패시터 구조물(미도시)을 형성할 수 있다.Thereafter, a plurality of upper recesses (RB) can be formed, and a plurality of insulating fences (not shown) and a plurality of buried contacts (BC) can be formed within the plurality of upper recesses (RB). Thereafter, a plurality of landing pads (LP) and an insulating structure (192) can be formed on the plurality of buried contacts (BC), and a capacitor structure (not shown) can be formed on the plurality of landing pads (LP).

도 7a 내지 도 7e는 일부 실시예들에 따른 집적회로 소자(100a)의 제조 방법을 설명하기 위하여 공정 순서에 따라 도시한 단면도들로서, 도 5의 X2-X2'선에 따른 단면에 대응되는 부분을 나타낸 것이다. 구체적으로, 도 7a 내지 도 7e는 도 2a에 대응되는 부분을 나타낸다. 도 7a 및 도 7e에서, 도 6a 내지 도 6d와 동일한 참조 부호는 동일 부재를 나타내며, 이하에서는 이들에 대한 중복 설명을 생략한다. 다만, 동일 부재라도 구조 및 형성 과정 등에 있어서 차이가 있는 내용에 대해서는 새롭게 설명한다.FIGS. 7A to 7E are cross-sectional views illustrating a manufacturing method of an integrated circuit device (100a) according to some embodiments in accordance with a process sequence, and illustrate portions corresponding to cross-sections taken along line X2-X2' of FIG. 5. Specifically, FIGS. 7A to 7E illustrate portions corresponding to FIG. 2A. In FIGS. 7A and 7E, the same reference numerals as in FIGS. 6A to 6D indicate the same elements, and their redundant descriptions will be omitted below. However, even for the same elements, differences in structure and formation process, etc. will be newly described.

도 5 및 도 7a를 참조하면, 복수의 활성 영역(ACT)이 정의된 기판(110)에 복수의 워드 라인 트렌치(120T)(도 3a 참조)를 형성한 후 복수의 워드 라인 트렌치(120T) 내에 각각 게이트 유전막(122), 워드 라인(124) 매몰 절연막(126)을 차례로 형성한 후, 기판(110) 상에 버퍼층(132), 층간 배리어막(134), 및 층간 절연막(136)을 순차적으로 형성할 수 있다. Referring to FIG. 5 and FIG. 7A, after forming a plurality of word line trenches (120T) (see FIG. 3A) in a substrate (110) in which a plurality of active regions (ACTs) are defined, a gate dielectric film (122) and a word line (124) buried insulating film (126) are sequentially formed in each of the plurality of word line trenches (120T), and then a buffer layer (132), an interlayer barrier film (134), and an interlayer insulating film (136) can be sequentially formed on the substrate (110).

그 후, 기판(110)의 일부 영역에서, 복수의 활성 영역(ACT)의 일부, 소자 분리막(112)의 일부, 버퍼층(132)의 일부, 층간 배리어막(134)의 일부, 및 층간 절연막(136)의 일부를 제거하여, 제1 하부 리세스(RA1)를 형성할 수 있다. 제1 하부 리세스(RA1)에 의해 복수의 돌출 구조물(EMB)이 정의될 수 있다. 예를 들면, 돌출 구조물(EMB)은 제1 하부 리세스(RA1)의 저면으로부터 수직 방향(Z 방향)으로 돌출될 수 있다.Thereafter, in some areas of the substrate (110), a portion of a plurality of active regions (ACTs), a portion of the device isolation film (112), a portion of the buffer layer (132), a portion of the interlayer barrier film (134), and a portion of the interlayer insulating film (136) may be removed to form a first lower recess (RA1). A plurality of protruding structures (EMB) may be defined by the first lower recess (RA1). For example, the protruding structures (EMB) may protrude in a vertical direction (Z direction) from a bottom surface of the first lower recess (RA1).

예시적인 실시예들에 따르면, 제1 하부 리세스(RA1)의 저면은 제2 수직 레벨(LV2)에 배치될 수 있다. 예를 들면, 제2 수직 레벨(LV2)은 도 6a 내지 도 6d를 참조하여 설명한 하부 리세스(RA) 저면의 수직 레벨인 제1 수직 레벨(LV1)보다 높을 수 있다. According to exemplary embodiments, the bottom surface of the first lower recess (RA1) may be arranged at a second vertical level (LV2). For example, the second vertical level (LV2) may be higher than the first vertical level (LV1), which is a vertical level of the bottom surface of the lower recess (RA) described with reference to FIGS. 6A to 6D.

제1 하부 리세스(RA1)의 저면에서, 복수의 활성 영역(ACT) 중에서 선택된 제1 활성 영역(A1)이 노출될 수 있다. 복수의 활성 영역(ACT) 중에서 선택되고, 제1 활성 영역(A1)과 인접하게 배치되며, 제1 활성 영역(A1)로부터 제1 수평 방향(X 방향)에서 이격된 제2 활성 영역(A2)과 제3 활성 영역(A3) 각각의 측벽은, 제1 하부 리세스(RA)를 통해 일부 노출될 수 있다. At the bottom surface of the first lower recess (RA1), a first active region (A1) selected from among a plurality of active regions (ACT) can be exposed. A sidewall of each of a second active region (A2) and a third active region (A3) selected from among the plurality of active regions (ACT), arranged adjacent to the first active region (A1), and spaced apart from the first active region (A1) in a first horizontal direction (X direction) can be partially exposed through the first lower recess (RA).

도 7b를 참조하면, 도 7a의 결과물에서, 제1 하부 리세스(RA1)의 내벽을 덮는 희생 절연 스페이서(142)를 형성할 수 있다. 희생 절연 스페이서(142)는 제1 하부 리세스(RA)의 내벽을 전체적으로 덮을 수 있다. 예를 들면, 희생 절연 스페이서(142)는 제1 하부 리세스(RA)를 통해 노출된 제2 활성 영역(A2)의 측벽 및 제3 활성 영역(A3)의 측벽을 덮을 수 있다. 희생 절연 스페이서(142)는 제1 하부 리세스(RA)를 통해 노출된 버퍼층(132)의 측벽, 층간 배리어막(134)의 측벽, 및 층간 절연막(136)의 측벽을 덮을 수 있다.Referring to FIG. 7b, in the result of FIG. 7a, a sacrificial insulating spacer (142) covering the inner wall of the first lower recess (RA1) can be formed. The sacrificial insulating spacer (142) can cover the entire inner wall of the first lower recess (RA). For example, the sacrificial insulating spacer (142) can cover the sidewall of the second active region (A2) exposed through the first lower recess (RA) and the sidewall of the third active region (A3). The sacrificial insulating spacer (142) can cover the sidewall of the buffer layer (132), the sidewall of the interlayer barrier film (134), and the sidewall of the interlayer insulating film (136) exposed through the first lower recess (RA).

도 7c를 참조하면, 도 7b의 결과물에서, 희생 절연 스페이서(142) 및 층간 절연막(136)을 식각 마스크로 제1 활성 영역(A1)의 일부 및 소자 분리막(112)의 일부를 제거하여 제2 하부 리세스(RA2)를 형성할 수 있다. 제2 하부 리세스(RA2)의 저면은 제2 수직 레벨(LV2) 보다 낮은 제3 수직 레벨(LV3)에 배치될 수 있다.Referring to FIG. 7c, in the result of FIG. 7b, a part of the first active region (A1) and a part of the device isolation film (112) may be removed using the sacrificial insulating spacer (142) and the interlayer insulating film (136) as an etching mask to form a second lower recess (RA2). The bottom surface of the second lower recess (RA2) may be arranged at a third vertical level (LV3) lower than the second vertical level (LV2).