KR20160092866A - 반도체 소자 및 그 제조 방법 - Google Patents

반도체 소자 및 그 제조 방법 Download PDFInfo

- Publication number

- KR20160092866A KR20160092866A KR1020150013801A KR20150013801A KR20160092866A KR 20160092866 A KR20160092866 A KR 20160092866A KR 1020150013801 A KR1020150013801 A KR 1020150013801A KR 20150013801 A KR20150013801 A KR 20150013801A KR 20160092866 A KR20160092866 A KR 20160092866A

- Authority

- KR

- South Korea

- Prior art keywords

- type region

- forming

- trench

- type

- disposed

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 33

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 15

- 239000000758 substrate Substances 0.000 claims abstract description 22

- 238000000034 method Methods 0.000 claims description 22

- 238000005468 ion implantation Methods 0.000 claims description 19

- 238000005530 etching Methods 0.000 claims description 12

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 claims description 4

- 230000000149 penetrating effect Effects 0.000 claims description 2

- 238000009413 insulation Methods 0.000 abstract 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 6

- 230000000694 effects Effects 0.000 description 6

- 235000012239 silicon dioxide Nutrition 0.000 description 3

- 239000000377 silicon dioxide Substances 0.000 description 3

- 230000015556 catabolic process Effects 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7812—Vertical DMOS transistors, i.e. VDMOS transistors with a substrate comprising an insulating layer, e.g. SOI-VDMOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7813—Vertical DMOS transistors, i.e. VDMOS transistors with trench gate electrode, e.g. UMOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7842—Field effect transistors with field effect produced by an insulated gate means for exerting mechanical stress on the crystal lattice of the channel region, e.g. using a flexible substrate

- H01L29/7848—Field effect transistors with field effect produced by an insulated gate means for exerting mechanical stress on the crystal lattice of the channel region, e.g. using a flexible substrate the means being located in the source/drain region, e.g. SiGe source and drain

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Electrodes Of Semiconductors (AREA)

Abstract

반도체 소자 및 그 제조 방법이 개시된다. 본 발명의 하나 또는 다수의 실시 예에 따른 반도체 소자는 기판; 상기 기판의 제1면에 배치되는 n-형 에피층; 상기 n-형 에피층 위에 차례로 배치되는 p형 영역 및 p+형 영역; 상기 p+형 영역 및 p형 영역의 일부에 배치되는 n+형 영역; 상기 n+형 영역, p형 영역 및 p+형 영역을 관통하고, 상기 n-형 에피층에 배치되는 트렌치; 상기 트렌치 내에 배치되는 게이트 절연막; 상기 게이트 절연막 위에 배치되는 게이트 전극; 상기 게이트 전극 위에 배치되는 산화막; 상기 p+형 영역, n+형 영역 및 산화막 위에 배치되는 소스 전극; 및 상기 기판의 제2면에 배치되는 드레인 전극을 포함하고, 상기 게이트 전극은 중앙부가 개구된 형상으로 이루어진다.

본 발명의 하나 또는 다수의 실시 예에 따른 반도체 소자의 제조 방법은 기판의 제1면에 에피택셜 성장으로 n-형 에피층을 형성하는 단계; 상기 n-형 에피층 위에 제1 이온주입으로 p형 영역을 형성하고, 상기 p형 영역 위에 제2 이온주입으로 p+형 영역을 형성하는 단계; 상기 p+형 영역 및 p형 영역의 일부에 제3 이온주입으로 n+형 영역을 형성하는 단계; 상기 n+형 영역, p형 영역 및 p+형 영역을 관통하고, 상기 n-형 에피층 위에 배치되도록 상기 n-형 에피층의 일부를 식각하여 트렌치를 형성하는 단계; 상기 p+형 영역의 상부, n+형 영역의 상부 및 트렌치 내에 제1 절연층을 형성하는 단계; 상기 제1 절연층 위에 게이트 도전층을 형성하는 단계; 및 상기 제1 절연층 및 게이트 도전층을 식각하여 게이트 절연막 및 게이트 전극을 형성하는 단계로 이루어지며, 상기 게이트 전극은 상기 트렌치 내부에 위치한다.

본 발명의 하나 또는 다수의 실시 예에 따른 반도체 소자의 제조 방법은 기판의 제1면에 에피택셜 성장으로 n-형 에피층을 형성하는 단계; 상기 n-형 에피층 위에 제1 이온주입으로 p형 영역을 형성하고, 상기 p형 영역 위에 제2 이온주입으로 p+형 영역을 형성하는 단계; 상기 p+형 영역 및 p형 영역의 일부에 제3 이온주입으로 n+형 영역을 형성하는 단계; 상기 n+형 영역, p형 영역 및 p+형 영역을 관통하고, 상기 n-형 에피층 위에 배치되도록 상기 n-형 에피층의 일부를 식각하여 트렌치를 형성하는 단계; 상기 p+형 영역의 상부, n+형 영역의 상부 및 트렌치 내에 제1 절연층을 형성하는 단계; 상기 제1 절연층 위에 게이트 도전층을 형성하는 단계; 및 상기 제1 절연층 및 게이트 도전층을 식각하여 게이트 절연막 및 게이트 전극을 형성하는 단계로 이루어지며, 상기 게이트 전극은 상기 트렌치 내부에 위치한다.

Description

본 발명은 반도체 소자 및 그 제조 방법에 관한 것으로서, 보다 상세하게는 전력용 반도체 소자의 전류밀도를 높일 수 있는 반도체 소자 및 그 제조 방법에 관한 것이다.

최근 응용 기기의 대형화 대용량화 추세에 따라 높은 항복전압과 높은 전류 및 고속 스위칭 특성을 갖는 전력용 반도체 소자의 필요성이 대두되고 있다.

이와 같은 전력용 반도체 소자는 매우 큰 전류를 흐르게 하면서도 도통 상태에서의 전력 손실을 적게하기 위하여 낮은 온 저항 또는 낮은 포화전압이 요구된다.

또한, 전력용 반도체 소자는 오프 상태 또는 스위치가 오프되는 순간에 전력 반도체 소자의 양단에 인가되는 PN 접합의 역방향 고전압에 견딜 수 있는 특성, 즉, 높은 항복 전압 특성이 기본적으로 요구된다.

이에 따라 트렌치 게이트 구조를 사용하는 전력용 반도체 소자의 개발이 활발하게 이루어지고 있는 추세이다.

상기 트렌치 게이트 구조는 기존의 플래너 구조의 JEET(Junction Field Effect Transistor) 효과가 제거되며, 셀폭(cell pitch)을 줄여 소자의 집적도를 향상시킴으로써, 온 저항을 감소시킬 수 있다는 이점이 있다.

그러나 상기한 바와 같은 종래의 전력용 반도체 소자는 이를 제조함에 있어서 공정의 특성상 이온 주입과 식각 공정이 존재하게 되는데, 이를 수행하기 위해서는 마스크(mask)를 사용하며, 이후, 마스크 얼라인(mask align) 작업이 선행되게 된다.

이러한 마스크 얼라인 작업은 공정장비의 얼라인 능력에 따라 얼라인을 보장할 수 있는 한계가 존재하며, 이는 소자 설계 시, 미스얼라인(misalign) 현상을 야기시킬 수 있다.

따라서, 마스크 얼라인 작업은 소자 설계 시, 이러한 미스얼라인을 고려하여, 선폭을 크게 설계해야 하고, 이에 따라, 단위면적당 소자 셀의 크기가 커지게 되는 문제점이 있다.

이 배경기술 부분에 기재된 사항은 발명의 배경에 대한 이해를 증진하기 위하여 작성된 것으로서, 이 기술이 속하는 분야에서 통상의 지식을 가진 자에게 이미 알려진 종래 기술이 아닌 사항을 포함할 수 있다.

본 발명의 실시 예는 전력용 반도체 소자를 제조함에 있어서, 마스크 수를 감소하여, 제조 공정의 단순화가 가능한 반도체 소자 및 그 제조 방법을 제공하고자 한다.

본 발명의 하나 또는 다수의 실시 예에서는 기판; 상기 기판의 제1면에 배치되는 n-형 에피층; 상기 n-형 에피층 위에 차례로 배치되는 p형 영역 및 p+형 영역; 상기 p+형 영역 및 p형 영역의 일부에 배치되는 n+형 영역; 상기 n+형 영역, p형 영역 및 p+형 영역을 관통하고, 상기 n-형 에피층에 배치되는 트렌치; 상기 트렌치 내에 배치되는 게이트 절연막; 상기 게이트 절연막 위에 배치되는 게이트 전극; 상기 게이트 전극 위에 배치되는 산화막; 상기 p+형 영역, n+형 영역 및 산화막 위에 배치되는 소스 전극; 및 상기 기판의 제2면에 배치되는 드레인 전극을 포함하고, 상기 게이트 전극은 중앙부가 개구된 형상으로 이루어지는 반도체 소자를 제공할 수 있다.

또한, 상기 게이트 전극은 상기 트랜치 내에서 "U" 자 형상으로 이루어질 수 있다.

또한, 상기 산화막은 상기 게이트 전극을 덮고 있으며, 상기 트랜치 내에 형성될 수 있다.

또한, 상기 소스 전극은 일측은 p+형 영역과 접촉하고, 타측은 평평하게 형성될 수 있다.

또한, 상기 기판은 탄화 규소(SiC) 기판일 수 있다.

본 발명의 하나 또는 다수의 실시 예에서는 기판의 제1면에 에피택셜 성장으로 n-형 에피층을 형성하는 단계; 상기 n-형 에피층 위에 제1 이온주입으로 p형 영역을 형성하고, 상기 p형 영역 위에 제2 이온주입으로 p+형 영역을 형성하는 단계; 상기 p+형 영역 및 p형 영역의 일부에 제3 이온주입으로 n+형 영역을 형성하는 단계; 상기 n+형 영역, p형 영역 및 p+형 영역을 관통하고, 상기 n-형 에피층 위에 배치되도록 상기 n-형 에피층의 일부를 식각하여 트렌치를 형성하는 단계; 상기 p+형 영역의 상부, n+형 영역의 상부 및 트렌치 내에 제1 절연층을 형성하는 단계; 상기 제1 절연층 위에 게이트 도전층을 형성하는 단계; 및 상기 제1 절연층 및 게이트 도전층을 식각하여 게이트 절연막 및 게이트 전극을 형성하는 단계로 이루어지며, 상기 게이트 전극은 상기 트렌치 내부에 위치하는 반도체 소자의 제조 방법을 제공할 수 있다.

또한, 상기 게이트 전극을 형성하는 단계는 상기 트렌치 내부에 위치하며, 중앙부가 개구된 게이트 전극을 형성할 수 있다.

또한, 상기 게이트 전극을 형성하는 단계 이후에 상기 게이트 전극, n+형 영역 및 p+형 영역을 덮도록 제2 절연층을 형성하는 단계; 상기 제2 절연층을 식각하여 상기 트렌치 내에서 상기 게이트 전극 위에 산화막을 형성하는 단계; 상기 p+형 영역, n+형 영역 및 산화막 위에 소스 전극을 형성하는 단계; 및 상기 기판의 제 2면에 드레인 전극을 형성하는 단계를 더 포함할 수 있다.

또한, 상기 소스 전극을 형성하는 단계는 상기 p+형 영역, n+형 영역 및 산화막 위에 상부 표면이 평평한 소스 전극을 형성하는 단계일 수 있다.

또한, 상기 제1 내지 제2 이온주입은 제1 마스크를 이용하여 이루어질 수 있다.

또한, 상기 제3 이온주입은 제2 마스크를 이용하여 이루어질 수 있다.

또한, 상기 트렌치를 형성하는 단계는 상기 n+형 영역, p형 영역 및 p+형 영역 위에 제3 마스크를 배치하는 단계; 및 상기 제3 마스크를 이용하여 상기 n+형 영역, p형 영역 및 p+형 영역을 관통하고, 상기 n-형 에피층의 일부를 식각하여 트렌치를 형성하는 단계를 포함할 수 있다.

또한, 상기 드레인 전극은 제4 마스크를 이용하여 형성될 수 있다.

본 발명의 실시 예는 전력용 반도체 소자를 제조함에 있어서, 마스크 수를 감소하여, 제조 공정의 단순화가 가능한 효과가 있다.

또한, 본 발명의 실시 예는 전력용 반도체 소자를 제조과정에서 발생하는 미스얼라인의 차이를 줄여 단위소자의 크기를 감소시키며, 제한된 웨이퍼 면적에서 보다 많은 소자를 형성할 수 있는 효과도 있다.

이 외에 본 발명의 실시 예로 인해 얻을 수 있거나 예측되는 효과에 대해서는 본 발명의 실시 예에 대한 상세한 설명에서 직접적 또는 암시적으로 개시하도록 한다. 즉, 본 발명의 실시 예에 따라 예측되는 다양한 효과에 대해서는 후술될 상세한 설명 내에서 개시될 것이다.

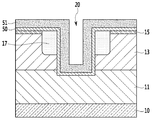

도 1은 본 발명의 실시 예에 따른 반도체 소자를 나타낸 단면도이다.

도 2 내지 도 9는 본 발 명의 실시 예에 따른 반도체 소자를 제조하는 방법을 순서대로 나타낸 단면도이다.

도 2 내지 도 9는 본 발 명의 실시 예에 따른 반도체 소자를 제조하는 방법을 순서대로 나타낸 단면도이다.

이하, 첨부한 도면을 참고로 하여 본 발명의 실시 예를 설명한다. 다만, 하기에 도시되는 도면과 후술되는 상세한 설명은 본 발명의 특징을 효과적으로 설명하기 위한 여러 가지 실시 예들 중에서 바람직한 하나의 실시 예에 관한 것이다. 따라서, 본 발명이 하기의 도면과 설명에만 한정되어서는 아니 될 것이다.

또한, 하기에서 본 발명을 설명함에 있어, 관련된 공지 기능 또는 구성에 대한 구체적인 설명이 본 발명의 요지를 불필요하게 흐릴 수 있다고 판단되는 경우에는 그 상세한 설명을 생략할 것이다. 그리고 후술되는 용어들은 본 발명에서의 기능을 고려하여 정의된 용어들로서, 이는 사용자, 운영자의 의도 또는 관례 등에 따라 달라질 수 있다. 그르므로 그 정의는 본 발명에서 전반에 걸친 내용을 토대로 내려져야 할 것이다.

또한, 이하 실시 예는 본 발명의 핵심적인 기술적 특징을 효율적으로 설명하기 위해 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자가 명백하게 이해할 수 있도록 용어를 적절하게 변형, 또는 통합, 또는 분리하여 사용할 것이나, 이에 의해 본 발명이 한정되는 것은 결코 아니다.

이하, 본 발명의 실시 예를 첨부한 도면을 참조하여 구체적으로 설명하면 다음과 같다.

도 1은 본 발명의 실시 예에 따른 반도체 소자를 나타낸 단면도이다.

도 1을 참조하면, 본 발명의 실시 예에 따른 반도체 소자는 기판(10)의 제1 면에 n-형 에피층(11), p형 영역(13), p+형 영역(15) 및 n+형 영역(17)이 위치한다.

이때, 상기 기판(10)은 탄화 규소(SiC)로 이루어질 수 있다.

또한, 상기 n+형 영역(17)은 p+형 영역(15) 및 p형 영역(13)의 일부를 포함하도록 형성된다.

또한, 상기 n-형 에피층(11), p형 영역(13) 및 p+형 영역(15)은 순차적으로 형성된다.

그리고 상기 n-형 에피층(11), p형 영역(13), p+형 영역(15) 및 n+형 영역(17)에는 트렌치(20)가 형성된다.

상기 트렌치(20)는 p형 영역(13), p+형 영역(15) 및 n+형 영역(17)을 관통하며, 상기 n-형 에피층(11)의 일부를 식각하여 이루어진다.

또한, 상기 트렌치(20) 내에는 게이트 절연막(21)이 형성되고, 상기 게이트 절연막(21) 위에는 게이트 전극(23)이 형성되며, 상기 게이트 전극(23) 위에는 산화막(25)이 형성된다.

이때, 상기 게이트 절연막(21)과 산화막(25)은 이산화규소(SiO2)로 이루어질 수 있다.

그리고 상기 게이트 전극(23)은 중앙부가 개구된 형상으로 "U"자 일 수 있다.

또한, 상기 산화막(25)은 상기 게이트 전극(23)을 덮고 있으며, 트렌치(20) 내부에 형성된다.

즉, 상기 게이트 절연막(21), 게이트 전극(23) 및 산화막(25)은 트렌치(20) 내부에서 순차적으로 형성되며, 이는 상기 트렌치(20) 내부에 위치하는 상기 산화막(25)이 상기 n+형 영역(17)의 상부와 비접촉되기 때문에, 전체적인 셀 너비에 영향을 주지 않아 결과적으로 셀 너비가 감소될 수 있다. 이로 인해 반도체 소자의 크기를 감소시킬 수 있다.

한편, 상기 p+형 영역(15), n+형 영역(17) 및 산화막(25)의 상부에는 소스 전극(30)이 형성된다.

그리고 기판(10)의 제2 면에는 드레인 전극(31)이 형성되어 반도체 소자를 이룬다.

이때, 상기 소스 전극(30)의 일측은 p+형 영역과(15) 접촉하고, 타측은 평평하게 형성된다. 즉, 상기 소스 전극(30)은 상부의 표면이 평평하게 형성될 수 있다.

상기와 같이, 본 발명의 실시 예에 따른 반도체 소자는 트렌치(20) 내부에 상기 게이트 전극(23)과 상기 게이트 전극(23)을 보호하는 산화막(25)이 형성되어, 상기 게이트 전극(23)과 산화막(25)이 셀 너비 형성에 영향을 주지 않아, 기존 대비 작은 치수의 셀 너비를 가지는 반도체 소자를 제조할 수 있으며, 이는 동일한 면적에 더 많은 단위 소자를 집적 시킬 수 있는 효과가 있다.

이하, 도 2 내지 도 9 및 도 1을 참조하여, 본 발명의 실시 예에 따른 반도체 소자의 제조 방법에 대해 상세하게 설명하고자 한다.

도 2 내지 도 9는 본 발 명의 실시 예에 따른 반도체 소자를 제조하는 방법을 순서대로 나타낸 단면도이다.

도 2에 도시한 바와 같이, 탄화 규소(SiC)로 이루어진 기판(10)을 준비하고, 상기 기판(10)의 제1 면에 에피택셜 성장으로 n-형 에피층(11)을 형성하는 단계를 진행한다.

이어서, 상기 n-형 에피층(11) 위에 제1 마스크를 배치하고, 상기 제1 마스크를 이용하여, 제1 이온주입으로 p형 영역(13)을 형성하고, 이후, 상기 p형 영역(13) 위에 제2 이온주입으로 p+형 영역(15)을 형성하는 단계를 진행한다.

도 3에 도시한 바와 같이, 상기 p+형 영역(15) 위에 제2 마스크를 배치하고, 상기 제2 마스크를 이용하여 제3 이온주입으로 n+형 영역(17)을 형성하는 단계를 진행한다.

이때, 상기 n+형 영역(17)을 형성하는 단계는 상기 p+형 영역(15) 및 p형 영역(13)의 일부를 포함하도록 제3 이온주입을 하여 n+형 영역(17)을 형성한다.

이어서, 도 4에 도시한 바와 같이, 상기 p+형 영역(15) 및 n+형 영역(17) 위에 제3 마스크를 배치하여 트렌치(20)를 형성하는 단계를 진행한다.

이때, 상기 트렌치(20)는 상기 n+형 영역(17), p+형 영역(15) 및 p형 영역(13)을 관통하며, n-형 에피층(11)의 일부를 식각하여 상기 n-형 에피층(11)에 위치하도록 형성된다.

도 5에 도시한 바와 같이, 제1 절연층(50)을 형성하는 단계를 진행하는데, 이때, 상기 제1 절연층(50)은 상기 p+형 영역(15)의 상부, n+형 영역(17)의 상부 및 트렌치(20)의 내부에 형성된다.

그리고 도 6에 도시한 바와 같이, 상기 제1 절연층(50) 위에 게이트 도전층(51)을 형성하는 단계를 진행한다.

이어서, 도 7에 도시한 바와 같이, 상기 제1 절연층(50) 및 게이트 도전층(51)을 한번에 식각하여 게이트 절연막(21) 및 게이트 전극(23)을 형성한다.

이때, 상기 게이트 절연막(21) 및 게이트 전극(23)은 상기 트렌치(20) 내부에 위치하도록 형성된다.

도 8에 도시한 바와 같이, 상기 p+형 영역(15), n+형 영역(17) 및 트렌치(20)의 내부에 제2 절연층(53)을 형성한다.

이때, 상기 트렌치(20)는 상기 제2 절연층(53)으로 인해 채워지게 된다.

그리고 상기 제1 및 제2 절연층(51, 53)은 이산화규소(SiO2)로 이루어질 수 있다.

도 9에 도시한 바와 같이, 상기 제2 절연층(53)을 식각하여 산화막(25)을 형성하는 단계를 진행한다.

이때, 상기 산화막(25)은 상기 트렌치(20) 내부에서 상기 게이트 전극(23)의 상부에만 위치하도록 형성되며, 나머지는 모두 식각공정으로 제거된다.

마지막으로 도 1에 도시한 바와 같이, 상기 p+형 영역(15), n+형 영역(17) 및 산화막(25) 위에 소스 전극(30)을 형성하고, 상기 기판(10)의 제2 면에 제4 마스크를 이용하여 드레인 전극(31)을 형성하는 단계를 진행한다.

이와 같이, 본 발명의 실시 예에 따른 반도체 소자의 제조 방법은 제1 및 제2 이온주입, 제3 이온주입, 트렌치 식각 및 드레인 전극(31)을 형성하는 단계에서 각각 마스크를 이용한다.

즉, 본 발명의 실시 예에 따른 반도체 소자의 제조 방법은 총 4개의 마스크와 4번의 얼라인공정으로 이루어진다. 특히, 제1 이온주입 및 제2 이온주입은 하나의 마스크로 이용하여 이루어지는 것이 특징이다.

이는 종래의 기술 대비 마스크의 수를 줄여 공정의 단순화를 이루며, 공정비용을 절감할 수 있다.

또한, 상기와 같은 방법으로 형성되는 반도체 소자는 기존 대비 약 50%의 셀 너비의 감소가 가능하여, 동일한 면적에 더 많은 단위 소자를 집적 시킬 수 있다.

상기에서는 본 발명의 바람직한 실시 예를 참조하여 설명하였지만, 해당 기술 분야에서 통상의 지식을 가진 자라면 하기의 특허 청구의 범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다.

10 ... 기판

11 ... n-형 에피층

13 ... p형 영역 15 ... p+형 영역

17 ... n+형 영역 20 ... 트렌치

21 ... 게이트 절연막 23 ... 게이트 전극

25 ... 산화막 30 ... 소스 전극

31 ... 드레인 전극 50 ... 제1 절연층

51 ... 게이트 도전층 53 ... 제2 절연층

13 ... p형 영역 15 ... p+형 영역

17 ... n+형 영역 20 ... 트렌치

21 ... 게이트 절연막 23 ... 게이트 전극

25 ... 산화막 30 ... 소스 전극

31 ... 드레인 전극 50 ... 제1 절연층

51 ... 게이트 도전층 53 ... 제2 절연층

Claims (13)

- 기판;

상기 기판의 제1면에 배치되는 n-형 에피층;

상기 n-형 에피층 위에 차례로 배치되는 p형 영역 및 p+형 영역;

상기 p+형 영역 및 p형 영역의 일부에 배치되는 n+형 영역;

상기 n+형 영역, p형 영역 및 p+형 영역을 관통하고, 상기 n-형 에피층에 배치되는 트렌치;

상기 트렌치 내에 배치되는 게이트 절연막;

상기 게이트 절연막 위에 배치되는 게이트 전극;

상기 게이트 전극 위에 배치되는 산화막;

상기 p+형 영역, n+형 영역 및 산화막 위에 배치되는 소스 전극; 및

상기 기판의 제2면에 배치되는 드레인 전극;

을 포함하고,

상기 게이트 전극은 중앙부가 개구된 형상으로 이루어지는 반도체 소자. - 제1항에 있어서,

상기 게이트 전극은

상기 트랜치 내에서 "U" 자 형상으로 이루어지는 반도체 소자. - 제1항에 있어서,

상기 산화막은

상기 게이트 전극을 덮고 있으며, 상기 트랜치 내에 형성되는 반도체 소자. - 제1항에 있어서,

상기 소스 전극은

일측은 p+형 영역과 접촉하고, 타측은 평평하게 형성되는 반도체 소자. - 제1항에 있어서,

상기 기판은

탄화 규소(SiC) 기판인 반도체 소자. - 기판의 제1면에 에피택셜 성장으로 n-형 에피층을 형성하는 단계;

상기 n-형 에피층 위에 제1 이온주입으로 p형 영역을 형성하고, 상기 p형 영역 위에 제2 이온주입으로 p+형 영역을 형성하는 단계;

상기 p+형 영역 및 p형 영역의 일부에 제3 이온주입으로 n+형 영역을 형성하는 단계;

상기 n+형 영역, p형 영역 및 p+형 영역을 관통하고, 상기 n-형 에피층 위에 배치되도록 상기 n-형 에피층의 일부를 식각하여 트렌치를 형성하는 단계;

상기 p+형 영역의 상부, n+형 영역의 상부 및 트렌치 내에 제1 절연층을 형성하는 단계;

상기 제1 절연층 위에 게이트 도전층을 형성하는 단계; 및

상기 제1 절연층 및 게이트 도전층을 식각하여 게이트 절연막 및 게이트 전극을 형성하는 단계;

로 이루어지며,

상기 게이트 전극은

상기 트렌치 내부에 위치하는 반도체 소자의 제조 방법. - 제5항에 있어서,

상기 게이트 전극을 형성하는 단계는

상기 트렌치 내부에 위치하며, 중앙부가 개구된 게이트 전극을 형성하는 반도체 소자의 제조 방법. - 제5항에 있어서,

상기 게이트 전극을 형성하는 단계 이후에

상기 게이트 전극, n+형 영역 및 p+형 영역을 덮도록 제2 절연층을 형성하는 단계;

상기 제2 절연층을 식각하여 상기 트렌치 내에서 상기 게이트 전극 위에 산화막을 형성하는 단계;

상기 p+형 영역, n+형 영역 및 산화막 위에 소스 전극을 형성하는 단계; 및

상기 기판의 제 2면에 드레인 전극을 형성하는 단계;

를 더 포함하는 반도체 소자의 제조 방법. - 제8항에 있어서,

상기 소스 전극을 형성하는 단계는

상기 p+형 영역, n+형 영역 및 산화막 위에 상부 표면이 평평한 소스 전극을 형성하는 단계인 반도체 소자의 제조 방법. - 제5항에 있어서,

상기 제1 및 제2 이온주입은

제1 마스크를 이용하여 이루어지는 반도체 소자의 제조 방법. - 제5항에 있어서,

상기 제3 이온주입은

제2 마스크를 이용하여 이루어지는 반도체 소자의 제조 방법. - 제5항에 있어서,

상기 트렌치를 형성하는 단계는

상기 n+형 영역, p형 영역 및 p+형 영역 위에 제3 마스크를 배치하는 단계; 및

상기 제3 마스크를 이용하여 상기 n+형 영역, p형 영역 및 p+형 영역을 관통하고, 상기 n-형 에피층의 일부를 식각하여 트렌치를 형성하는 단계;

를 포함하는 반도체 소자의 제조 방법. - 제5항에 있어서,

상기 드레인 전극은

제4 마스크를 이용하여 형성되는 반도체 소자의 제조 방법.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020150013801A KR20160092866A (ko) | 2015-01-28 | 2015-01-28 | 반도체 소자 및 그 제조 방법 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020150013801A KR20160092866A (ko) | 2015-01-28 | 2015-01-28 | 반도체 소자 및 그 제조 방법 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20160092866A true KR20160092866A (ko) | 2016-08-05 |

Family

ID=56711287

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020150013801A KR20160092866A (ko) | 2015-01-28 | 2015-01-28 | 반도체 소자 및 그 제조 방법 |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR20160092866A (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20190092667A (ko) * | 2018-01-30 | 2019-08-08 | 매그나칩 반도체 유한회사 | 전력 반도체 소자 및 이의 제조방법 |

-

2015

- 2015-01-28 KR KR1020150013801A patent/KR20160092866A/ko not_active Application Discontinuation

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20190092667A (ko) * | 2018-01-30 | 2019-08-08 | 매그나칩 반도체 유한회사 | 전력 반도체 소자 및 이의 제조방법 |

| US10593758B2 (en) | 2018-01-30 | 2020-03-17 | Magnachip Semiconductor, Ltd. | Power semiconductor device and method for manufacturing the same |

| US11038019B2 (en) | 2018-01-30 | 2021-06-15 | Magnachip Semiconductor, Ltd. | Power semiconductor device and method for manufacturing the same |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US20170373154A1 (en) | Semiconductor device and method of manufacturing the same | |

| US9698248B2 (en) | Power MOS transistor and manufacturing method therefor | |

| JP2014135494A (ja) | 二重並列チャネル構造を持つ半導体素子及びその半導体素子の製造方法 | |

| JP2017005140A (ja) | 絶縁ゲート型スイッチング装置とその製造方法 | |

| WO2017145594A1 (ja) | 化合物半導体装置の製造方法および化合物半導体装置 | |

| KR20150076840A (ko) | 반도체 소자 및 그 제조 방법 | |

| TWI566410B (zh) | 半導體元件、終端結構及其製造方法 | |

| US9324835B2 (en) | Method for manufacturing MOSFET | |

| KR101964153B1 (ko) | 절연 또는 반절연 SiC 기판에 구현된 SiC 반도체 소자 및 그 제조 방법 | |

| KR101360070B1 (ko) | 반도체 소자 및 그 제조 방법 | |

| US10615079B2 (en) | Semiconductor device and method for manufacturing the same | |

| US9059268B2 (en) | Tunneling field effect transistor and method for fabricating the same | |

| CN114068721B (zh) | 双梯形槽保护梯形槽碳化硅mosfet器件及制造方法 | |

| KR101427925B1 (ko) | 반도체 소자 및 그 제조 방법 | |

| KR101628105B1 (ko) | 반도체 소자 및 그 제조 방법 | |

| KR20160092866A (ko) | 반도체 소자 및 그 제조 방법 | |

| KR101339277B1 (ko) | 반도체 소자 및 그 제조 방법 | |

| US8803225B2 (en) | Tunneling field effect transistor having a lightly doped buried layer | |

| US20230155021A1 (en) | Silicon carbide semiconductor device | |

| KR102335328B1 (ko) | 반도체 소자의 제조 방법 | |

| CN109979801B (zh) | 一种半导体器件的制造方法和半导体器件 | |

| CN102420253A (zh) | 一种背面嵌入应变介质区的vdmos器件及其制备方法 | |

| JP2019165166A (ja) | 炭化珪素半導体装置およびその製造方法 | |

| TWI817719B (zh) | 半導體結構及其形成方法 | |

| KR20110078978A (ko) | 반도체 소자 및 그 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E601 | Decision to refuse application |