KR102400098B1 - 비휘발성 메모리 장치 및 상기 비휘발성 메모리 장치의 프로그램 방법 - Google Patents

비휘발성 메모리 장치 및 상기 비휘발성 메모리 장치의 프로그램 방법 Download PDFInfo

- Publication number

- KR102400098B1 KR102400098B1 KR1020170051073A KR20170051073A KR102400098B1 KR 102400098 B1 KR102400098 B1 KR 102400098B1 KR 1020170051073 A KR1020170051073 A KR 1020170051073A KR 20170051073 A KR20170051073 A KR 20170051073A KR 102400098 B1 KR102400098 B1 KR 102400098B1

- Authority

- KR

- South Korea

- Prior art keywords

- address

- bit

- lines

- memory cells

- line

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5671—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge trapping in an insulator

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3418—Disturbance prevention or evaluation; Refreshing of disturbed memory data

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/409—Read-write [R-W] circuits

- G11C11/4094—Bit-line management or control circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5628—Programming or writing circuits; Data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/08—Address circuits; Decoders; Word-line control circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/24—Bit-line control circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/30—Power supply circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3418—Disturbance prevention or evaluation; Refreshing of disturbed memory data

- G11C16/3427—Circuits or methods to prevent or reduce disturbance of the state of a memory cell when neighbouring cells are read or written

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0483—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells having several storage transistors connected in series

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2211/00—Indexing scheme relating to digital stores characterized by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C2211/56—Indexing scheme relating to G11C11/56 and sub-groups for features not covered by these groups

- G11C2211/562—Multilevel memory programming aspects

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2211/00—Indexing scheme relating to digital stores characterized by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C2211/56—Indexing scheme relating to G11C11/56 and sub-groups for features not covered by these groups

- G11C2211/564—Miscellaneous aspects

- G11C2211/5648—Multilevel memory programming, reading or erasing operations wherein the order or sequence of the operations is relevant

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Read Only Memory (AREA)

- Theoretical Computer Science (AREA)

- Non-Volatile Memory (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

Abstract

비휘발성 메모리 장치 및 비휘발성 메모리 장치의 프로그램 방법이 개시된다. 본 개시의 기술적 사상에 비휘발성 메모리 장치의 프로그램 방법은 워드 라인을 공유하는 제1 내지 제N 스트링 선택 라인들, 그리고 제1 및 제2 비트 라인 그룹들을 포함하는 비휘발성 메모리 장치의 프로그램 방법으로서, 순차적으로 인가되는 제1 내지 제N 어드레스들을 기초로, 워드 라인 및 제1 비트 라인 그룹에 포함된 적어도 하나의 비트 라인에 연결된 제1 메모리 셀들을 제1 내지 제N 스트링 선택 라인들의 순서에 따라 순차적으로 프로그램하고, 이어서, 순차적으로 인가되는 제N+1 내지 제2·N 어드레스들을 기초로, 워드 라인 및 제2 비트 라인 그룹에 포함된 적어도 하나의 비트 라인에 연결된 제2 메모리 셀들을 제1 내지 제N 스트링 선택 라인들의 순서에 따라 순차적으로 프로그램하며, N은 2 이상의 자연수이다.

Description

본 개시의 기술적 사상은 메모리 장치에 관한 것이며, 더욱 상세하게는, 복수의 스트링 선택 라인들 및 복수의 비트 라인 그룹들을 포함하는 비휘발성 메모리 장치 및 상기 비휘발성 메모리 장치의 프로그램 방법에 관한 것이다.

메모리 장치는 데이터를 저장하는데 사용되며, 휘발성 메모리 장치와 비휘발성 메모리 장치로 구분된다. 비휘발성 메모리 장치의 일 예로서, 플래쉬 메모리 장치는 휴대폰, 디지털 카메라, 휴대용 정보 단말기(PDA), 이동식 컴퓨터 장치, 고정식 컴퓨터 장치 및 기타 장치에서 사용될 수 있다.

본 개시의 기술적 사상이 해결하려는 과제는 복수의 스트링 선택 라인들 및 복수의 비트 라인 그룹들을 가지는 비휘발성 메모리 장치에서 프로그램 디스터브를 감소시키는 데에 있다.

본 개시의 기술적 사상에 따른 비휘발성 메모리 장치의 프로그램 방법은, 워드 라인을 공유하는 제1 내지 제N 스트링 선택 라인들, 및 제1 및 제2 비트 라인 그룹들을 포함하는 비휘발성 메모리 장치의 프로그램 방법으로서, 순차적으로 인가되는 제1 내지 제N 어드레스들을 기초로, 상기 워드 라인, 및 상기 제1 비트 라인 그룹에 포함된 적어도 하나의 비트 라인에 연결된 제1 메모리 셀들을 상기 제1 내지 제N 스트링 선택 라인들의 순서에 따라 순차적으로 프로그램하는 단계, 및 이어서, 순차적으로 인가되는 제N+1 내지 제2·N 어드레스들을 기초로, 상기 워드 라인, 및 상기 제2 비트 라인 그룹에 포함된 적어도 하나의 비트 라인에 연결된 제2 메모리 셀들을 상기 제1 내지 제N 스트링 선택 라인들의 순서에 따라 순차적으로 프로그램하는 단계를 포함하고, N은 2 이상의 자연수이다.

또한, 본 개시의 기술적 사상에 따른 비휘발성 메모리 장치의 프로그램 방법은, 워드 라인을 공유하는 제1 및 제2 스트링 선택 라인들, 및 제1 및 제2 비트 라인 그룹들을 포함하는 비휘발성 메모리 장치의 프로그램 방법으로서, 제1 어드레스 및 제1 프로그램 커맨드에 응답하여, 상기 워드 라인, 상기 제1 스트링 선택 라인, 및 제1 비트 라인 그룹에 포함된 비트 라인들에 연결된 메모리 셀들을 프로그램하는 단계, 이어서, 제2 어드레스 및 제2 프로그램 커맨드에 응답하여, 상기 워드 라인, 제2 스트링 선택 라인, 및 상기 제1 비트 라인 그룹에 포함된 상기 비트 라인들에 연결된 제2 메모리 셀들을 프로그램하는 단계, 이어서, 제3 어드레스 및 제3 프로그램 커맨드에 응답하여, 상기 워드 라인, 상기 제1 스트링 선택 라인 및 상기 제2 비트 라인 그룹에 포함된 비트 라인들에 연결된 제3 메모리 셀들을 프로그램하는 단계, 및 이어서, 제4 어드레스 및 제4 프로그램 커맨드에 응답하여, 상기 워드 라인, 상기 제2 스트링 선택 라인 및 상기 제2 비트 라인 그룹에 포함된 상기 비트 라인들에 연결된 제4 메모리 셀들을 프로그램하는 단계를 포함한다.

또한, 본 개시의 기술적 사상에 따른 비휘발성 메모리 장치의 프로그램 방법은, 워드 라인을 공유하는 스트링 선택 라인들, 및 비트 라인 그룹들을 가지는 비휘발성 메모리 장치의 프로그램 방법으로서, 어드레스 및 프로그램 커맨드를 수신하는 단계, 상기 스트링 선택 라인들에 대한 스트링 선택 라인 어드레스가 상기 비트 라인 그룹들에 대한 비트 라인 그룹 어드레스보다 하위 비트에 위치하도록, 상기 어드레스를 수정 어드레스로 변환하는 단계, 및 상기 수정 어드레스에 따라, 상기 워드 라인, 상기 스트링 선택 라인들 중 하나, 상기 비트 라인 그룹들 중 하나에 연결된 메모리 셀들을 프로그램하는 단계를 포함한다.

본 개시의 기술적 사상에 따르면, 제1 비트 라인에 연결된 메모리 셀들을 스트링 선택 라인 별로 순차적으로 프로그램하고, 이어서, 제2 비트 라인에 연결된 메모리 셀들을 스트링 선택 라인 별로 순차적으로 프로그램함으로써, 프로그램 디스터브를 감소시킬 수 있다. 구체적으로, 비 선택된 비트 라인에 연결된 스트링에 포함된 메모리 셀들과 같이, 메모리 셀의 게이트와 채널 간의 전압이 낮은 상황에서, 메모리 셀에 강한 FN 스트레스가 먼저 인가되고, 이어서 약한 FN 스트레스가 인가되도록 함으로써, 프로그램 디스터브의 워스트 케이스를 개선할 수 있다.

도 1은 본 개시의 일 실시예에 따른 메모리 시스템을 개략적으로 나타내는 블록도이다.

도 2는 본 개시의 일 실시예에 따라, 도 1의 메모리 장치를 상세하게 나타내는 블록도이다.

도 3a는 본 개시의 일 실시예에 따른 어드레스 변환 동작을 나타낸다.

도 3b는 본 개시의 일 실시예에 따른 수정 어드레스에 포함된 스트링 선택 라인 어드레스를 예시적으로 나타낸다.

도 3c는 본 개시의 일 실시예에 따른 수정 어드레스에 포함된 비트 라인 그룹 어드레스를 예시적으로 나타낸다.

도 4는 본 개시의 일 실시예에 따라, 도 2의 메모리 블록의 일 예의 등가 회로를 나타내는 회로도이다.

도 5는 본 개시의 일 실시예에 따라, 도 2의 메모리 블록의 일 예를 나타내는 사시도이다.

도 6은 본 개시의 일 실시예에 따라, 도 2의 메모리 블록의 일 예의 등가 회로를 나타내는 회로도이다.

도 7은 본 개시의 일 실시예에 따라 QBL(Quadruple Bit Line) 구조의 페이지 버퍼부를 포함하는 메모리 장치를 나타낸다.

도 8은 본 개시의 일 실시예에 따른 SBL(Shielded Bit Line) 구조의 페이지 버퍼부를 포함하는 메모리 장치를 나타낸다.

도 9는 본 개시의 일 실시예에 따른 ABL(All Bit Line) 구조의 페이지 버퍼부를 포함하는 메모리 장치를 나타낸다.

도 10은 본 개시의 일 실시예에 따른 프로그램 바이어스 조건을 예시적으로 나타내는 회로도이다.

도 11은 본 개시의 일 실시예에 따라, 도 10의 회로도에 대응하는 메모리 장치를 나타낸다.

도 12는 본 개시의 일 실시예에 따라, 도 10의 비 선택된 비트 라인에 연결된 스트링의 채널 부스팅 포텐셜을 예시적으로 나타낸다.

도 13은 본 개시의 일 실시예에 따라, 메모리 셀의 게이트와 채널 간의 전압에 따른 FN 전류를 나타내는 그래프이다.

도 14는 본 개시의 일 실시예에 따른 비휘발성 메모리 장치의 프로그램 방법을 나타내는 흐름도이다.

도 15a 및 도 15b는 본 개시의 일 실시예에 따른 비휘발성 메모리 장치의 프로그램 순서를 나타낸다.

도 16은 본 개시의 일 실시예에 따른 비휘발성 메모리 장치의 프로그램 방법에 따른 메모리 컨트롤러와 메모리 장치의 동작을 나타내는 흐름도이다.

도 17a 내지 도 17c는 본 개시의 일 실시예에 따라 비트 라인 그룹들이 네 개인 경우, 메모리 그룹에 대한 프로그램 순서의 다양한 예들을 나타낸다.

도 18은 본 개시의 일 실시예에 따라 비트 라인 그룹이 두 개인 경우, 메모리 셀들에 대한 프로그램 순서를 나타낸다.

도 19는 본 개시의 일 실시예에 따라 MLC들에 대한 프로그램 순서를 나타낸다.

도 20은 본 개시의 일 실시예에 따라 TLC들에 대한 프로그램 순서를 나타낸다.

도 21은 본 개시의 일 실시예에 따라 3D 메모리 장치에 대한 프로그램 순서를 나타낸다.

도 22a 및 도 22b는 본 개시의 일 실시예에 따라 MLC들을 포함하는 3D 메모리 장치에 대한 프로그램 순서를 나타낸다.

도 23a 및 도 23b는 본 개시의 일 실시예에 따라 MLC들을 포함하는 3D 메모리 장치에 대한 프로그램 순서를 나타낸다.

도 24는 본 개시의 일 실시예에 따른 비휘발성 메모리 장치의 프로그램 방법을 나타내는 흐름도이다.

도 25는 도 17a의 메모리 셀들에 대한 16회의 프로그램 디스터브를 나타낸다.

도 26은 본 개시의 실시예들에 따른 메모리 장치를 SSD 시스템에 적용한 예를 나타내는 블록도이다.

도 2는 본 개시의 일 실시예에 따라, 도 1의 메모리 장치를 상세하게 나타내는 블록도이다.

도 3a는 본 개시의 일 실시예에 따른 어드레스 변환 동작을 나타낸다.

도 3b는 본 개시의 일 실시예에 따른 수정 어드레스에 포함된 스트링 선택 라인 어드레스를 예시적으로 나타낸다.

도 3c는 본 개시의 일 실시예에 따른 수정 어드레스에 포함된 비트 라인 그룹 어드레스를 예시적으로 나타낸다.

도 4는 본 개시의 일 실시예에 따라, 도 2의 메모리 블록의 일 예의 등가 회로를 나타내는 회로도이다.

도 5는 본 개시의 일 실시예에 따라, 도 2의 메모리 블록의 일 예를 나타내는 사시도이다.

도 6은 본 개시의 일 실시예에 따라, 도 2의 메모리 블록의 일 예의 등가 회로를 나타내는 회로도이다.

도 7은 본 개시의 일 실시예에 따라 QBL(Quadruple Bit Line) 구조의 페이지 버퍼부를 포함하는 메모리 장치를 나타낸다.

도 8은 본 개시의 일 실시예에 따른 SBL(Shielded Bit Line) 구조의 페이지 버퍼부를 포함하는 메모리 장치를 나타낸다.

도 9는 본 개시의 일 실시예에 따른 ABL(All Bit Line) 구조의 페이지 버퍼부를 포함하는 메모리 장치를 나타낸다.

도 10은 본 개시의 일 실시예에 따른 프로그램 바이어스 조건을 예시적으로 나타내는 회로도이다.

도 11은 본 개시의 일 실시예에 따라, 도 10의 회로도에 대응하는 메모리 장치를 나타낸다.

도 12는 본 개시의 일 실시예에 따라, 도 10의 비 선택된 비트 라인에 연결된 스트링의 채널 부스팅 포텐셜을 예시적으로 나타낸다.

도 13은 본 개시의 일 실시예에 따라, 메모리 셀의 게이트와 채널 간의 전압에 따른 FN 전류를 나타내는 그래프이다.

도 14는 본 개시의 일 실시예에 따른 비휘발성 메모리 장치의 프로그램 방법을 나타내는 흐름도이다.

도 15a 및 도 15b는 본 개시의 일 실시예에 따른 비휘발성 메모리 장치의 프로그램 순서를 나타낸다.

도 16은 본 개시의 일 실시예에 따른 비휘발성 메모리 장치의 프로그램 방법에 따른 메모리 컨트롤러와 메모리 장치의 동작을 나타내는 흐름도이다.

도 17a 내지 도 17c는 본 개시의 일 실시예에 따라 비트 라인 그룹들이 네 개인 경우, 메모리 그룹에 대한 프로그램 순서의 다양한 예들을 나타낸다.

도 18은 본 개시의 일 실시예에 따라 비트 라인 그룹이 두 개인 경우, 메모리 셀들에 대한 프로그램 순서를 나타낸다.

도 19는 본 개시의 일 실시예에 따라 MLC들에 대한 프로그램 순서를 나타낸다.

도 20은 본 개시의 일 실시예에 따라 TLC들에 대한 프로그램 순서를 나타낸다.

도 21은 본 개시의 일 실시예에 따라 3D 메모리 장치에 대한 프로그램 순서를 나타낸다.

도 22a 및 도 22b는 본 개시의 일 실시예에 따라 MLC들을 포함하는 3D 메모리 장치에 대한 프로그램 순서를 나타낸다.

도 23a 및 도 23b는 본 개시의 일 실시예에 따라 MLC들을 포함하는 3D 메모리 장치에 대한 프로그램 순서를 나타낸다.

도 24는 본 개시의 일 실시예에 따른 비휘발성 메모리 장치의 프로그램 방법을 나타내는 흐름도이다.

도 25는 도 17a의 메모리 셀들에 대한 16회의 프로그램 디스터브를 나타낸다.

도 26은 본 개시의 실시예들에 따른 메모리 장치를 SSD 시스템에 적용한 예를 나타내는 블록도이다.

이하, 첨부한 도면을 참조하여 본 개시의 실시 예에 대해 상세히 설명한다.

도 1은 본 개시의 일 실시예에 따른 메모리 시스템(10)을 개략적으로 나타내는 블록도이다. 도 1을 참조하면, 메모리 시스템(10)은 메모리 장치(100) 및 메모리 컨트롤러(200)를 포함할 수 있고, 메모리 장치(100)는 메모리 셀 어레이(110) 및 제어 로직(120)을 포함할 수 있다. 메모리 장치(100)는 비휘발성 메모리 장치일 수 있다. 일부 실시예들에서, 메모리 시스템(10)은 전자 장치에 내장되는 내부 메모리로 구현될 수 있고, 예를 들어, 임베디드 UFS(Universal Flash Storage) 메모리 장치, eMMC(embedded Multi-Media Card), 또는 SSD(Solid State Drive)일 수 있다. 일부 실시예들에서, 메모리 시스템(10)은 전자 장치에 착탈 가능한 외장 메모리로 구현될 수 있고, 예를 들어, UFS 메모리 카드, CF(Compact Flash), SD(Secure Digital), Micro-SD(Micro Secure Digital), Mini-SD(Mini Secure Digital), xD(extreme Digital) 또는 메모리 스틱(Memory Stick)일 수 있다.

메모리 컨트롤러(200)는 호스트(HOST)로부터의 읽기/쓰기 요청에 응답하여 메모리 장치(100)에 저장된 데이터를 독출하도록 또는 메모리 장치(100)에 데이터를 프로그램하도록 메모리 장치(100)를 제어할 수 있다. 구체적으로, 메모리 컨트롤러(200)는 메모리 장치(100)에 어드레스(ADDR), 커맨드(CMD) 및 제어 신호(CTRL)를 제공함으로써, 메모리 장치(100)에 대한 프로그램, 독출 및 소거 동작을 제어할 수 있다. 또한, 프로그램하기 위한 데이터(DATA)와 독출된 데이터(DATA)가 메모리 컨트롤러(200)와 메모리 장치(100) 사이에서 송수신될 수 있다.

메모리 셀 어레이(110)는 복수의 메모리 셀들을 포함할 수 있는데, 예를 들어, 복수의 메모리 셀들은 플래쉬 메모리 셀들일 수 있다. 이하에서는, 복수의 메모리 셀들이 낸드(NAND) 플래쉬 메모리 셀들인 경우를 예로 하여 본 개시의 실시예들을 상술하기로 한다. 그러나, 본 발명은 이에 한정되지 않고, 일부 실시예들에서, 복수의 메모리 셀들은 ReRAM(resistive RAM), PRAM(phase change RAM) 또는 MRAM(magnetic RAM)과 같은 저항형 메모리 셀들일 수 있다.

메모리 셀 어레이(110)는 복수의 스트링 선택 라인들 및 복수의 비트 라인들이 교차하는 지점들에 각각 연결되는 복수의 낸드 스트링들을 포함할 수 있고, 각 낸드 스트링은 복수의 메모리 셀들을 포함할 수 있다. 복수의 스트링 선택 라인들은 동일 레벨에 배치된 워드 라인을 공유할 수 있다. 복수의 비트 라인들은 프로그램 순서에 따라 복수의 비트 라인 그룹들로 나눠질 수 있다. 일 실시예에서, 복수의 비트 라인들은 제1 및 제2 비트 라인 그룹들로 나눠질 수 있고, 이때, 제1 비트 라인 그룹에 연결된 메모리 셀들에 대한 프로그램 동작들이 스트링 선택 라인 별로 순차적으로 수행되고, 이어서, 제2 비트 라인 그룹에 연결된 메모리 셀들에 대한 프로그램 동작들이 스트링 선택 라인 별로 순차적으로 수행될 수 있다. 복수의 비트 라인 그룹들에 대해서는 도 7 내지 도 9를 참조하여 더욱 자세하게 설명하기로 한다.

제어 로직(120)은 메모리 컨트롤러(200)로부터 커맨드(CMD) 및 어드레스(ADDR)를 수신하고, 스트링 선택 라인 어드레스가 비트 라인 그룹 어드레스보다 하위 비트에 위치하도록 어드레스(ADDR)를 수정(corrected) 어드레스로 변환할 수 있다. 이때, 커맨드(CMD)는 프로그램 커맨드에 대응할 수 있다. 또한, 제어 로직(120)는 수정 어드레스에 따라 제1 비트 라인 그룹에 포함된 메모리 셀들을 순차적으로 프로그램하고, 이어서, 제2 비트 라인 그룹에 포함된 메모리 셀들을 순차적으로 프로그램할 수 있다. 제어 로직(120)의 어드레스 변환 동작은 도 3을 참조하여 더욱 자세하게 설명하기로 한다.

도 2는 본 개시의 일 실시예에 따라, 도 1의 메모리 장치(100)를 상세하게 나타내는 블록도이다. 도 2를 참조하면, 메모리 장치(100)는 메모리 셀 어레이(110), 제어 로직(120), 전압 생성부(130), 로우 디코더(140) 및 페이지 버퍼부(150)를 포함할 수 있다. 도시되지는 않았으나, 메모리 장치(100)는 데이터 입출력 회로 또는 입출력 인터페이스를 더 포함할 수 있다.

메모리 셀 어레이(110)는 복수의 메모리 셀들을 포함하고, 워드 라인들(WL), 스트링 선택 라인들(SSL), 그라운드 선택 라인들(GSL) 및 비트 라인들(BL)에 연결될 수 있다. 메모리 셀 어레이(110)는 워드 라인들(WL), 스트링 선택 라인들(SSL) 및 그라운드 선택 라인들(GSL)을 통해 로우 디코더(140)에 연결되고, 비트 라인들(BL)을 통해 페이지 버퍼부(150)에 연결될 수 있다. 본 실시예에서, 비트 라인들(BL)은 프로그램 순서에 따라 복수의 비트 라인 그룹들로 나눠질 수 있다.각 메모리 셀은 하나 또는 그 이상의 비트들을 저장할 수 있으며, 구체적으로, 각 메모리 셀은 싱글 레벨 셀(Single Level Cell, SLC), 멀티 레벨 셀(Multi Level Cell, MLC) 또는 트리플 레벨 셀(Triple Level Cell, TLC)로 이용될 수 있다.

일 실시예에서, 메모리 셀 어레이(110)는 2차원 메모리 셀 어레이를 포함할 수 있고, 2차원 메모리 셀 어레이는 행 및 열 방향을 따라 배치된 복수의 낸드 스트링들을 포함할 수 있으며, 이에 대해, 도 6을 참조하여 상술하기로 한다. 일 실시예에서, 메모리 셀 어레이(110)는 3차원 메모리 셀 어레이를 포함할 수 있고, 3차원 메모리 셀 어레이는 복수의 낸드 스트링들을 포함할 수 있으며, 각 낸드 스트링은 기판 위에 수직으로 적층된 워드 라인들에 각각 연결된 메모리 셀들을 포함할 수 있으며, 이에 대해, 도 4 및 도 5를 참조하여 상술하기로 한다. 미국 특허공개공보 제7,679,133호, 미국 특허공개공보 제8,553,466호, 미국 특허공개공보 제8,654,587호, 미국 특허공개공보 제8,559,235호, 및 미국 특허출원공개공보 제2011/0233648호는 3차원 메모리 어레이가 복수 레벨로 구성되고 워드 라인들 및/또는 비트 라인들이 레벨들 간에 공유되어 있는 3차원 메모리 어레이에 대한 적절한 구성들을 상술하는 것들로서, 본 명세서에 인용 형식으로 결합된다.

제어 로직(120)은 메모리 컨트롤러(200)로부터 수신한 커맨드(CMD), 어드레스(ADDR) 및 제어 신호(CTRL)를 기초로, 메모리 셀 어레이(110)에 데이터를 기입하거나 메모리 셀 어레이(110)로부터 데이터를 독출하기 위한 각종 제어 신호를 출력할 수 있다. 이로써, 제어 로직(120)은 메모리 장치(100) 내의 각종 동작을 전반적으로 제어할 수 있다. 구체적으로, 제어 로직(120)은 전압 생성부(130)에 전압 제어 신호(CTRL_vol)를 제공할 수 있고, 로우 디코더(140)에 로우 어드레스(X-ADDR)를 제공할 수 있으며, 페이지 버퍼부(150)에 칼럼 어드레스(Y-ADDR)를 제공할 수 있다. 그러나, 본 발명은 이에 한정되지 않고, 제어 로직(120)은 전압 생성부(130), 로우 디코더(140) 및 페이지 버퍼부(150)에 다른 제어 신호들을 더 제공할 수 있다. 본 실시예에서, 제어 로직(120)은 어드레스 변환부(121)를 포함할 수 있다. 이하에서는 도 3을 참조하여, 어드레스 변환부(121)의 동작을 상술하기로 한다.

도 3a는 본 개시의 일 실시예에 따른 어드레스 변환 동작을 나타낸다. 도 2 및 도 3a를 함께 참조하면, 어드레스 변환부(121)는 메모리 컨트롤러(200)로부터 수신한 어드레스(ADDR)를 수정 어드레스(ADDR')로 변환할 수 있다. 예를 들어, 어드레스(ADDR)는 복수의 메모리 칩들 중 하나를 선택하기 위한 칩 어드레스(CHIP_ADDR), 및 논리 주소, 예를 들어, 논리적 페이지 넘버(Logical Page Number, LPN)를 포함할 수 있다.

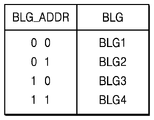

수정 어드레스(ADDR')는 복수의 메모리 블록들 중 하나를 선택하기 위한 블록 어드레스(BLK_ADDR), 복수의 워드 라인들 중 하나를 선택하기 위한 워드 라인 어드레스(WL_ADDR), 복수의 비트 라인 그룹들 중 하나를 선택하기 위한 비트 라인 그룹 어드레스(BLG_ADDR), 및 복수의 스트링 선택 라인들 중 하나를 선택하기 위한 스트링 선택 라인 어드레스(SSL_ADDR)를 포함할 수 있다. 일 실시예에서, 수정 어드레스(ADDR')에서 블록 어드레스(BLK_ADDR)가 가장 상위 비트에 위치하고, 워드 라인 어드레스(WL_ADDR)가 그 다음 비트에 위치하고, 비트 라인 그룹 어드레스(BLG_ADDR)가 그 다음 비트에 위치하고, 스트링 선택 라인 어드레스(SSL_ADDR)가 가장 하위 비트에 위치할 수 있다.

도 3b는 본 개시의 일 실시예에 따른 수정 어드레스(ADDR')에 포함된 스트링 선택 라인 어드레스(SSL_ADDR)를 예시적으로 나타낸다. 스트링 선택 라인 어드레스(SSL_ADDR)는 워드 라인을 공유하는 복수의 스트링 선택 라인들의 개수에 따른 N비트로 생성될 수 있고, N은 1 이상의 정수이다. 예를 들어, 도 10 및 도 11에 예시된 바와 같이, 4개의 스트링 선택 라인들이 워드 라인을 공유하는 경우, 스트링 선택 라인 어드레스(SSL_ADDR)는 2 비트로 생성될 수 있다. 예를 들어, 스트링 선택 라인 어드레스(SSL_ADDR)가 00이면 제1 스트링 선택 라인(SSL1)을 선택할 수 있다.

도 3c는 본 개시의 일 실시예에 따른 수정 어드레스(ADDR')에 포함된 비트 라인 그룹 어드레스(BLG_ADDR)를 예시적으로 나타낸다. 비트 라인 그룹 어드레스(BLG_ADDR)는 복수의 비트 라인 그룹들의 개수에 따른 M비트로 생성될 수 있고, M은 1 이상의 정수이다. 예를 들어, 도 7에 예시된 바와 같이, 복수의 비트 라인들이 4개의 비트 라인 그룹들로 나눠지는 경우, 비트 라인 그룹 어드레스(BLG_ADDR)는 2 비트로 생성될 수 있다. 예를 들어, 비트 라인 그룹 어드레스(BLG_ADDR)가 00이면 제1 비트 라인 그룹(BLG1)을 선택할 수 있다.

다시 도 2를 참조하면, 전압 생성부(130)는 전압 제어 신호(CTRL_vol)를 기초로 하여 메모리 셀 어레이(110)에 대한 프로그램, 독출 및 소거 동작을 수행하기 위한 다양한 종류의 전압들을 생성할 수 있다. 로우 디코더(140)는 제어 로직(120)으로부터 수신한 로우 어드레스(X-ADDR)에 응답하여, 메모리 블록들(BLK1 내지 BLKz) 중 하나를 선택할 수 있고, 선택된 메모리 블록의 워드 라인들(WL) 중 하나를 선택할 수 있고, 복수의 스트링 선택 라인들(SSL) 중 하나를 선택할 수 있다. 여기서, 로우 어드레스(X-ADDR)은 도 3에 예시된, 수정 어드레스(ADDR')에 포함된 블록 어드레스(BLK_ADDR), 워드 라인 어드레스(WL_ADDR) 및 스트링 선택 라인 어드레스(SSL_ADDR)를 포함할 수 있다.

페이지 버퍼부(150)는 비트 라인들(BL)을 통해 메모리 셀 어레이(110)에 연결될 수 있고, 제어 로직(120)으로부터 수신한 칼럼 어드레스(Y-ADDR)에 응답하여 비트 라인들(BL) 중 일부 비트 라인을 선택할 수 있다. 여기서, 칼럼 어드레스(Y-ADDR)은 도 3에 예시된, 수정 어드레스(ADDR')에 포함된 비트 라인 그룹 어드레스(BLG_ADDR)를 포함할 수 있다. 구체적으로, 페이지 버퍼부(150)는 동작 모드에 따라 기입 드라이버 또는 감지 증폭기로서 동작한다. 프로그램 동작 시, 페이지 버퍼부(150)는 메모리 셀 어레이(1100)의 선택된 비트 라인으로, 프로그램될 데이터에 대응하는 비트 라인 전압을 전달한다. 읽기 동작 시, 페이지 버퍼부(150)는 선택된 메모리 셀에 저장된 데이터를 비트 라인을 통해서 감지한다.

도 4는 본 개시의 일 실시예에 따라, 도 2의 메모리 블록의 일 예(BLKa)의 등가 회로를 나타내는 회로도이다.

도 4를 참조하면, 제1 메모리 블록(BLK1)은 복수의 낸드 스트링들(NS11 내지 NS33), 복수의 워드 라인들(WL1 내지 WL8), 복수의 비트 라인들(BL1 내지 BL3), 복수의 그라운드 선택 라인들(GSL1 내지 GSL3), 복수의 스트링 선택 라인들(SSL1 내지 SSL3) 및 공통 소스 라인(CSL)을 포함할 수 있다. 여기서, 낸드 스트링들의 개수, 워드 라인들의 개수, 비트 라인들의 개수, 그라운드 선택 라인의 개수 및 스트링 선택 라인들의 개수는 실시예에 따라 다양하게 변경될 수 있다.

제1 비트 라인(BL1)과 공통 소스 라인(CSL) 사이에 낸드 스트링들(NS11, NS21, NS31)이 제공되고, 제2 비트 라인(BL2)과 공통 소스 라인(CSL) 사이에 낸드 스트링들(NS12, NS22, NS32)이 제공되고 제3 비트 라인(BL3)과 공통 소스 라인(CSL) 사이에 낸드 스트링들(NS13, NS23, NS33)이 제공된다. 각 낸드 스트링(예를 들면, NS11)은 직렬로 연결된 스트링 선택 트랜지스터(SST), 복수의 메모리 셀들(MC) 및 그라운드 선택 트랜지스터(GST)를 포함할 수 있다. 이하에서는, 편의상 낸드 스트링을 스트링이라고 지칭하기로 한다.

스트링 선택 트랜지스터(SST)는 대응하는 스트링 선택 라인(SSL1 내지 SSL3)에 연결된다. 복수의 메모리 셀들(MC)은 각각 대응하는 워드 라인(WL1 내지 WL8)에 연결된다. 그라운드 선택 트랜지스터(GST)는 대응하는 그라운드 선택 라인(GSL1 내지 GSL3)에 연결된다. 스트링 선택 트랜지스터(SST)는 대응하는 비트 라인(BL1 내지 BL3)에 연결되고, 그라운드 선택 트랜지스터(GST)는 공통 소스 라인(CSL)에 연결된다.

본 실시예에서, 동일 높이의 워드 라인(예를 들면, WL1)은 서로 공통으로 연결되어 있고, 스트링 선택 라인들(SSL1 내지 SSL3)은 서로 분리되어 있고, 그라운드 선택 라인들(GSL1 내지 GSL3)도 서로 분리되어 있다. 도 4에서는 세 개의 스트링 선택 라인들(SSL1 내지 SSL3)이 동일 높이의 워드 라인을 공유하는 것으로 도시되어 있으나, 본 발명은 이에 한정되지 않는다. 예를 들어, 두 개의 스트링 선택 라인들이 동일 높이의 워드 라인을 공유할 수 있다. 다른 예를 들어, 네 개의 스트링 선택 라인들이 동일 높이의 워드 라인을 공유할 수 있다.

도 5는 본 개시의 일 실시예에 따라, 도 2의 메모리 블록의 일 예(BLKa)를 나타내는 사시도이다. 도 5를 참조하면, 메모리 블록(BLKa)은 기판(SUB)에 대해 수직 방향으로 형성되어 있다. 기판(SUB)은 제1 도전형(예를 들어, p 타입)을 가지며, 기판(SUB) 상에 제1 방향(예를 들어, Y 방향)을 따라 신장되고, 제2 도전형(예를 들어, n 타입)의 불순물들이 도핑된 공통 소스 라인(CSL)이 제공된다. 인접한 두 공통 소스 라인(CSL) 사이의 기판(SUB)의 영역 상에, 제1 방향을 따라 신장되는 복수의 절연막들(IL)이 제3 방향(예를 들어, Z 방향)을 따라 순차적으로 제공되며, 복수의 절연막들(IL)은 제3 방향을 따라 특정 거리만큼 이격된다. 예를 들어, 복수의 절연막들(IL)은 실리콘 산화물과 같은 절연 물질을 포함할 수 있다.

인접한 두 공통 소스 라인들(CSL) 사이의 기판(SUB)의 영역 상에, 제1 방향을 따라 순차적으로 배치되며, 제3 방향을 따라 복수의 절연막들(IL)을 관통하는 복수의 필라들(pillars)(P)이 제공된다. 예를 들어, 복수의 필라들(P)은 복수의 절연막들(IL)을 관통하여 기판(SUB)과 컨택할 것이다. 구체적으로, 각 필라(P)의 표면층(surface layer)(S)은 제1 타입을 갖는 실리콘 물질을 포함할 수 있고, 채널 영역으로 기능할 수 있다. 한편, 각 필라(P)의 내부층(I)은 실리콘 산화물과 같은 절연 물질 또는 에어 갭(air gap)을 포함할 수 있다.

인접한 두 공통 소스 라인들(CSL) 사이의 영역에서, 절연막들(IL), 필라들(P) 및 기판(SUB)의 노출된 표면을 따라 전하 저장층(charge storage layer, CS)이 제공된다. 전하 저장층(CS)은 게이트 절연층(또는 '터널링 절연층'이라고 지칭함), 전하 트랩층 및 블로킹 절연층을 포함할 수 있다. 예를 들어, 전하 저장층(CS)은 ONO(oxide-nitride-oxide) 구조를 가질 수 있다. 또한, 인접한 두 공통 소스 라인들(CSL) 사이의 영역에서, 전하 저장층(CS)의 노출된 표면 상에, 선택 라인들(GSL, SSL) 및 워드 라인들(WL1 내지 WL8)과 같은 게이트 전극(GE)이 제공된다.

복수의 필라들(P) 상에는 드레인들 또는 드레인 컨택들(DR)이 각각 제공된다. 예를 들어, 드레인들 또는 드레인 컨택들(DR)은 제2 도전형을 갖는 불순물들이 도핑된 실리콘 물질을 포함할 수 있다. 드레인들(DR) 상에, 제2 방향(예를 들어, X 방향)으로 신장되고 제1 방향을 따라 특정 거리만큼 이격되어 배치된 비트 라인들(BL1 내지 BL3)이 제공된다.

도 6은 본 개시의 일 실시예에 따라, 도 2의 메모리 블록의 일 예(BLKb)의 등가 회로를 나타내는 회로도이다.

도 6을 참조하면, 메모리 블록(BLKb)은 수평 구조의 낸드 플래쉬 메모리일 수 있고, 도 2에 도시된 메모리 블록들(BLK1 내지 BLKz) 중 적어도 하나는 도 6과 같이 구현될 수 있다. 메모리 블록(BLKb)은 복수의 스트링들(NS11 내지 NS2n), 복수의 워드 라인들(WL1 내지 WL8), 복수의 비트 라인들(BL1 내지 BLn), 복수의 그라운드 선택 라인들(GSL1, GSL2), 복수의 스트링 선택 라인들(SSL1, SSL2) 및 공통 소스 라인(CSL)을 포함할 수 있다. 여기서, 스트링들의 개수, 워드 라인들의 개수, 비트 라인들의 개수, 그라운드 선택 라인의 개수 및 스트링 선택 라인들의 개수는 실시예에 따라 다양하게 변경될 수 있다.

복수의 스트링들(NS11 내지 NS2n)은 워드 라인들(WL1 내지 WL8)을 공유할 수 있으며, 적어도 두 개의 스트링들은 하나의 비트 라인을 공유할 수 있다. 예를 들어, 제1 및 제2 스트링들(NS11 및 NS21)은 제1 비트 라인(BL1)을 공유할 수 있으며, 제1 스트링(NS11)의 스트링 선택 트랜지스터(SST) 및 그라운드 선택 트랜지스터(GST)는 각각 제1 스트링 선택 라인(SSL1) 및 제1 그라운드 선택 라인(GSL1)에 연결되고, 제2 스트링(NS21)의 스트링 선택 트랜지스터(SST) 및 그라운드 선택 트랜지스터(GST)는 제2 스트링 선택 라인(SSL2) 및 제2 그라운드 선택 라인(GSL2)에 연결될 수 있다.

이에 따라, 제1 워드 라인(WL1)에 연결되어 있고 스트링들(NS11, NS12 내지 NS1n)에 속해 있는 메모리 셀들을 프로그램하는 경우에는, 제1 워드 라인(WL1)과 제1 스트링 선택 라인(SSL1) 및 제1 그라운드 선택 라인(GSL1)이 선택될 수 있고, 제1 워드 라인(WL1)에 연결되어 있고 스트링들(NS21, NS22 내지 NS2n)에 속해 있는 메모리 셀들을 프로그램하는 경우에는, 제1 워드 라인(WL1)과 제2 스트링 선택 라인(SSL2) 및 제2 그라운드 선택 라인(GSL2)이 선택될 수 있다. 따라서, 제1 워드 라인(WL1)에 연결되어 있고 스트링들(NS11, NS12 내지 NS1n)에 속해 있는 메모리 셀들에 대한 프로그램 동작과, 제1 워드 라인(WL1)에 연결되어 있고 스트링들(NS21, NS22 내지 NS2n)에 속해 있는 메모리 셀들에 대한 프로그램 동작은 순차적으로 수행될 수 있다.

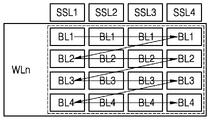

도 7은 본 개시의 일 실시예에 따라 QBL(Quadruple Bit Line) 구조의 페이지 버퍼부(150a)를 포함하는 메모리 장치(100a)를 나타낸다.

도 7을 참조하면, 메모리 셀 어레이(110a)는 복수의 비트 라인들(BL1 내지 BL_4i)에 연결될 수 있고, 여기서, i는 3 이상의 정수이다. 페이지 버퍼부(150a)는 복수의 페이지 버퍼들(151a 내지 153a)을 포함할 수 있다. 일 실시예에서, 복수의 페이지 버퍼들(151a 내지 153a)의 개수는 i개이고, 복수의 비트 라인들(BL1 내지 BL_4i)의 개수는 4i개일 수 있다. 이때, 4개의 비트 라인들(예를 들어, BL1 내지 BL4)은 하나의 페이지 버퍼(예를 들어, 151a)에 연결될 수 있고, 이에 따라, 페이지 버퍼부(150a)를 QBL 구조의 페이지 버퍼라고 지칭할 수 있다.

본 실시예에서, 복수의 비트 라인들(BL1 내지 BL_4i)은 제1 내지 제4 비트 라인 그룹들(BLG1 내지 BLG4)로 나눠질 수 있고, 제1 내지 제4 비트 라인 그룹들(BLG1 내지 BLG4)에 대한 프로그램 순서는 서로 다를 수 있다. 예를 들어, 제1 비트 라인 그룹(BLG1)은 비트 라인들(BL1, BL5, BL_4i-3)을 포함할 수 있고, 제2 비트 라인 그룹(BLG2)은 비트 라인들(BL2, BL6, BL_4i-2)을 포함할 수 있고, 제3 비트 라인 그룹(BLG3)은 비트 라인들(BL3, BL7, BL_4i-1)을 포함할 수 있고, 제4 비트 라인 그룹(BLG4)은 비트 라인들(BL4, BL8, BL_4i)을 포함할 수 있다.

예를 들어, 제1 내지 제4 비트 라인 그룹들(BLG1 내지 BLG4)에 각각 포함된 제1 내지 제4 비트 라인들(BL1 내지 BL4)은 하나의 페이지 버퍼(151a)를 공유할 수 있다. 이때, 제1 내지 제4 비트 라인 그룹들(BLG1 내지 BLG4)에 대한 프로그램 동작들은 순차적으로 수행될 수 있고, 다시 말해, 제1 내지 제4 비트 라인들(BL1 내지 BL4)에 연결된 메모리 셀들에 대한 프로그램 동작들은 순차적으로 수행될 수 있다. 본 명세서에서는, QBL 구조의 페이지 버퍼부(150a)를 포함하는 메모리 장치(100a)에 대한 프로그램 방법을 중심으로 설명하기로 한다. 그러나, 본 발명은 이에 한정되지 않으며, 도 8 및 도 9에 예시된 구조의 페이지 버퍼부를 포함하는 메모리 장치에도 적용될 수 있다.

도 8은 본 개시의 일 실시예에 따른 SBL(Shielded Bit Line) 구조의 페이지 버퍼부(150b)를 포함하는 메모리 장치(100b)를 나타낸다.

도 8을 참조하면, 메모리 셀 어레이(110b)는 복수의 비트 라인들(BL1 내지 BL_2i)에 연결될 수 있고, 여기서, i는 3 이상의 정수이다. 페이지 버퍼부(150b)는 복수의 페이지 버퍼들(151b 내지 153b)을 포함할 수 있다. 일 실시예에서, 복수의 페이지 버퍼들(151b 내지 153b)의 개수는 i개이고, 복수의 비트 라인들(BL1 내지 BL_2i)의 개수는 2i개일 수 있다. 이때, 2개의 비트 라인들(예를 들어, BL1 및 BL2)은 하나의 페이지 버퍼(예를 들어, 151b)에 연결될 수 있고, 이에 따라, 페이지 버퍼부(150b)를 SBL 구조의 페이지 버퍼라고 지칭할 수 있다.

본 실시예에서, 복수의 비트 라인들(BL1 내지 BL_2i)은 제1 및 제2 비트 라인 그룹들(BLG1 및 BLG2)로 나눠질 수 있고, 제1 및 제2 비트 라인 그룹들(BLG1 및 BLG2)에 대한 프로그램 순서는 서로 다를 수 있다. 예를 들어, 제1 비트 라인 그룹(BLG1)은 비트 라인들(BL1, BL3, BL_2i-1)을 포함할 수 있고, 제2 비트 라인 그룹(BLG2)은 비트 라인들(BL2, BL4, BL_2i)을 포함할 수 있다. 예를 들어, 제1 및 제2 비트 라인 그룹들(BLG1 및 BLG2)에 각각 포함된 제1 및 제2 비트 라인들(BL1 및 BL2)은 하나의 페이지 버퍼(151b)를 공유할 수 있다. 이때, 제1 및 제2 비트 라인 그룹들(BLG1 및 BLG2)에 대한 프로그램 동작들은 순차적으로 수행될 수 있고, 다시 말해, 제1 및 제2 비트 라인들(BL1 및 BL2)에 연결된 메모리 셀들에 대한 프로그램 동작들은 순차적으로 수행될 수 있다

도 9는 본 개시의 일 실시예에 따른 ABL(All Bit Line) 구조의 페이지 버퍼부(150c)를 포함하는 메모리 장치(100c)를 나타낸다.

도 9를 참조하면, 메모리 셀 어레이(110c)는 복수의 비트 라인들(BL1 내지 BL_2i)에 연결될 수 있고, 여기서, i는 3 이상의 정수이다. 페이지 버퍼부(150c)는 복수의 페이지 버퍼들(151c 내지 156c)을 포함할 수 있다. 일 실시예에서, 복수의 페이지 버퍼들(151c 내지 156c)의 개수는 2i개이고, 복수의 비트 라인들(BL1 내지 BL_2i)의 개수는 2i개일 수 있다. 이때, 각 비트 라인(예를 들어, BL1)은 하나의 페이지 버퍼(예를 들어, 151c)에 연결될 수 있고, 이에 따라, 페이지 버퍼부(150c)를 ABL 구조의 페이지 버퍼라고 지칭할 수 있다.

본 실시예에서, 복수의 비트 라인들(BL1 내지 BL_2i)은 제1 및 제2 비트 라인 그룹들(BLG1 및 BLG2)로 나눠질 수 있고, 제1 및 제2 비트 라인 그룹들(BLG1 및 BLG2)에 대한 프로그램 순서는 서로 다를 수 있다. 예를 들어, 제1 비트 라인 그룹(BLG1)은 비트 라인들(BL1, BL3, BL_2i-1)을 포함할 수 있고, 제2 비트 라인 그룹(BLG2)은 비트 라인들(BL2, BL4, BL_2i)을 포함할 수 있다. 이때, 제1 및 제2 비트 라인 그룹들(BLG1 및 BLG2)에 대한 프로그램 동작들은 순차적으로 수행될 수 있고, 다시 말해, 제1 및 제2 비트 라인들(BL1 및 BL2)에 연결된 메모리 셀들에 대한 프로그램 동작들은 순차적으로 수행될 수 있다. 그러나, 본 발명은 이에 한정되지 않으며, 복수의 비트 라인들(BL1 내지 BL_2i)는 3개 이상의 비트 라인 그룹들로 나눠질 수도 있다.

도 10은 본 개시의 일 실시예에 따른 프로그램 바이어스 조건을 예시적으로 나타내는 회로도이다. 도 11은 본 개시의 일 실시예에 따라, 도 10의 회로도에 대응하는 메모리 장치를 나타낸다. 이하에서는, 도 10 및 도 11을 함께 참조하여 프로그램 바이어스 조건에 대해 설명하기로 한다.

도 10을 참조하면, 메모리 블록(BLKa')은 제1 내지 제4 비트 라인들(BL1 내지 BL4)과 제1 내지 제4 스트링 선택 라인들(SSL1, SSL4)이 교차하는 지점들에 각각 연결되는 복수의 스트링들을 포함할 수 있다. 메모리 블록(BLKa')은 도 4에 예시된 메모리 블록(BLKa)의 일부에 대응될 수 있다. 본 실시예에서, 프로그램하고자 선택된 메모리 셀은 메모리 셀(MC1)일 수 있고, 제5 워드 라인(WL5), 제1 비트 라인(BL1), 및 제1 스트링 선택 라인(SSL1)이 선택될 수 있다. 이때, 제5 워드 라인(WL5), 제1 내지 제4 비트 라인들(BL1 내지 BL4) 및 제1 내지 제4 스트링 선택 라인들(SS1, SSL4)에 연결된 16개의 메모리 셀들(MC1 내지 MC16)을 "메모리 그룹"이라고 지칭하기로 한다. 메모리 그룹에 포함된 16개의 메모리 셀들(MC1 내지 MC16)을 프로그램하기 위해서는 16회의 순차적인 프로그램 동작들이 수행될 수 있다.

도 11을 참조하면, 제1 비트 라인(BL1)을 공유하는 복수의 스트링들에 연결되는 워드 라인들(WL1 내지 WL8), 제1 내지 제4 스트링 선택 라인들(SSL1 내지 SSL4) 및 제1 내지 제4 그라운드 선택 라인들(GSL1 내지 GS4)이 도시된다. 이때, 제1 내지 제4 스트링 선택 라인들(SSL1 내지 SSL4)은 동일 레벨에 배치된 워드 라인을 공유할 수 있다. 제1 스트링 선택 라인(SSL1)은 선택된 스트링 선택 라인(SSL_SEL)이고, 제2 내지 제4 스트링 선택 라인들(SSL2 내지 SSL4)은 비 선택된 스트링 선택 라인들(SSL_UN)이다. 제1 그라운드 선택 라인(SGL1)은 선택된 그라운드 선택 라인(GSL_SEL)이고, 제2 내지 제4 그라운드 선택 라인들(GSL2 내지 GSL4)은 비 선택된 그라운드 선택 라인들(GSL_UN)이다. 제5 워드 라인(WL5)은 선택된 워드 라인(WL_SEL)이고, 제1 내지 제4, 제6 내지 제8 워드 라인들(WL1 내지 WL4, WL6 내지 WL8)은 비 선택된 워드 라인들(WL_UN)이다.

도 11에 도시된 바와 같이, 3D 메모리 장치에서, 동일한 레벨에 위치하는 복수의 워드 라인들은 서로 연결될 수 있으므로, 동일한 레벨에 위치하는 복수의 워드 라인들에는 동일한 전압이 인가될 수 있다. 이에 따라, 선택된 제5 워드 라인(WL5)에 연결된, 비 선택된 메모리 셀들(MC2 내지 MC16)의 게이트들에 프로그램 전압(Vpgm)이 인가될 수 있다. 따라서, 비 선택된 메모리 셀들(MC2 내지 MC16)에 대한 프로그램을 금지하기 위해, 제1 내지 제4 스트링 선택 라인들(SSL1, SSL4), 제1 내지 제4 그라운드 선택 라인들(GSL1, GSL4) 및 제1 내지 제4 비트 라인들(BL1 내지 BL4)들에 인가되는 전압들을 개별적으로 결정한 프로그램 바이어스 조건이 이용될 수 있다. 이하에서, 프로그램 바이어스 조건에 대해 상술하기로 한다.

프로그램 바이어스 조건에 따르면, 선택된 제5 워드라인(WL5)에는 프로그램 전압(Vpgm)이 인가되고, 비 선택된 워드 라인들, 즉, 제4 및 제6 워드 라인들(WL4, WL6)에는 패스 전압(Vpass)이 인가될 수 있다. 또한, 선택된 제1 비트 라인(BL1)에는 0V가 인가되고, 비 선택된 제2 내지 제4 비트 라인들(BL2 내지 BL4)에는 전원 전압(VDD)이 인가될 수 있다. 또한, 선택된 제1 스트링 선택 라인(SSL1)에는 전원 전압(VDD)이 인가되고, 비 선택된 제4 스트링 선택 라인(SSL4)에는 0V가 인가될 수 있다. 그라운드 선택 라인들(GSL1, GSL4)에는 0V가 인가되고, 공통 소스 라인(CSL)에는 0V보다 높은 전압(예를 들어, VDD)이 인가될 수 있다.

상술한 프로그램 바이어스 조건에서, 선택된 메모리 셀(MC1)의 게이트에 프로그램 전압(Vpgm)이 인가되고, 채널 전압은 0V이다. 이로 인해, 선택된 메모리 셀(MC1)의 게이트와 채널 사이에 강한 전계(electric field)가 생성되므로, 채널에 있는 전자들이 FN 터널링에 의해 전하 트랩층으로 주입될 수 있고, 이로써, 선택된 메모리 셀(MC1)은 프로그램될 수 있다. 한편, 비 선택된 메모리 셀들(MC2 내지 MC16)의 채널은 플로팅(floating) 상태에 있으므로, 채널 전압은 부스팅 전압까지 상승하게 된다. 이로 인해, 비선택된 메모리 셀들(MC2 내지 MC16)의 게이트와 채널 사이에 FN 터널링이 일어나기에 충분한 전계가 형성되지 않으므로, 비선택된 메모리 셀들(MC2 내지 MC16)은 프로그램되지 않을 수 있다.

예를 들어, 비 선택된 제4 비트 라인(BL4)에는 제1 및 제2 스트링들(NSa, NSb)이 연결될 수 있고, 제1 및 제2 스트링들(NSa, NSb)은 제1 및 제2 스트링 선택 트랜지스터들(SSTa, SSTb)을 각각 포함할 수 있다. 제1 및 제2 스트링들(NSa, NSb)의 채널 전압은 부스팅 전압(예를 들어, Vpass)까지 상승하게 된다. 제1 스트링 선택 트랜지스터(SSTa)의 게이트에는 전원 전압(VDD)이 인가되므로, 제1 스트링 선택 트랜지스터(SSTa)의 게이트와 채널 간의 전압의 크기는 "Vpass-VDD"에 대응할 수 있다. 한편, 제2 스트링 선택 트랜지스터(SSTb)의 게이트에는 0V가 인가되므로, 제2 스트링 선택 트랜지스터(SSTb)의 게이트와 채널 간의 전압의 크기는 "Vpass"에 대응할 수 있다.

이때, 제2 스트링 선택 트랜지스터(SSTb)의 게이트와 채널 간의 전압의 크기(즉, Vpass)는 제1 스트링 선택 트랜지스터(SSTa)의 게이트와 채널 간의 전압의 크기(즉, Vpass-VDD)보다 크므로, 제1 스트링 선택 트랜지스터(SSTa)보다 제2 스트링 선택 트랜지스터(SSTb)에서 HCI(Hot Carrier Injection)가 발생할 가능성이 더 크다. 결과적으로, 제1 스트링(NSa)의 채널 전압은 부스팅 전압을 유지하는 반면, 제2 스트링(NSb)의 채널 전압은 부스팅 전압보다 낮아질 수 있다. 이하에서는, 도 12를 참조하여, 제1 및 제2 스트링들(NSa, NSb)에 각각 포함된, 선택된 제5 워드 라인(WL5)에 연결된 메모리 셀들(MC4, MC16)에 대한 FN 스트레스 차이에 대해 설명하기로 한다.

도 12는 본 개시의 일 실시예에 따라, 도 10의 비 선택된 비트 라인(BL_UN)에 연결된 스트링(NS)의 채널 부스팅 포텐셜을 예시적으로 나타낸다. 이하에서는 도 10 내지 도 12를 함께 참조하여 설명하기로 한다.

도 12를 참조하면, 비 선택된 비트 라인(BL_UN)은 도 10의 제2 내지 제4 비트 라인들(BL2 내지 BL4) 중 하나에 대응할 수 있다. 예를 들어, 도 10의 제1 스트링(NSa)과 같이, 스트링 선택 트랜지스터(SST)에 선택된 스트링 선택 라인(SSL_SEL)이 연결되는 경우, 채널 전압(12a)은 제2 전압(V2)까지 부스팅될 수 있다. 이때, 제2 전압(V2)은 패스 전압(Vpass)에 대응할 수 있다. 선택된 제5 워드 라인(WL5)에 연결된 메모리 셀(MC)의 게이트에는 프로그램 전압(Vpgm)이 인가되므로, 메모리 셀(MC)의 게이트와 채널 간의 전압(Vd2)는 "Vpgm-V2"에 대응할 수 있다. 따라서, 메모리 셀(MC)은 Vpgm-V2에 대응하는, 상대적으로 약한 FN 스트레스를 받을 수 있다.

한편, 예를 들어, 도 10의 제2 스트링(NSb)과 같이, 스트링 선택 트랜지스터(SST)에 비 선택된 스트링 선택 라인(SSL_UN)에 연결되는 경우, 채널 전압(12b)은 제2 전압(V2)보다 낮은 제1 전압(V1)에 대응할 수 있다. 선택된 제5 워드 라인(WL5)에 연결된 메모리 셀(MC)의 게이트에는 프로그램 전압(Vpgm)이 인가되므로, 메모리 셀(MC)의 게이트와 채널 간의 전압(Vd1)는 "Vpgm-V1"에 대응할 수 있고, 이때, Vd1은 Vd2보다 크다. 따라서, 메모리 셀(MC)은 Vpgm-V1에 대응하는, 상대적으로 강한 FN 스트레스를 받을 수 있다.

도 13은 본 개시의 일 실시예에 따라, 메모리 셀의 게이트와 채널 간의 전압에 따른 FN 전류를 나타내는 그래프이다. 이하에서는, 도 12 및 도 13을 함께 참조하면 설명하기로 한다. 도 13에서, 가로축은 메모리 셀의 게이트와 채널 간의 전압을 V 단위로 나타내고, 세로축은 메모리 셀에 흐르는 FN 전류를 AU(Arbitrary Unit)로 나타낸다. 여기서, FN 전류는 메모리 셀의 게이트와 채널 간의 전압에 따라, 메모리 셀에서 채널 방향으로 흐를 수 있다. 도 13에 예시된 바와 같이, 게이트와 채널 간의 전압이 증가할수록, FN 전류는 비선형적으로 증가할 수 있다.

비 선택된 스트링 선택 라인(SSL_UN)에 연결된 스트링의 채널 전압(V1)은 선택된 스트링 선택 라인(SSL_SEL)에 연결된 스트링의 채널 전압(V2)보다 낮을 수 있다. 따라서, 비 선택된 스트링 선택 라인(SSL_UN)에 연결된 스트링에 포함된 메모리 셀의 게이트와 채널 간 전압(Vd1)은, 선택된 스트링 선택 라인(SSL_SEL)에 연결된 스트링에 포함된 메모리 셀의 게이트와 채널 간의 전압(Vd2)보다 크기 때문에, 비 선택된 스트링 선택 라인(SSL_UN)에 연결된 스트링에 포함된 메모리 셀에서 FN 전류가 더 많이 흐를 수 있다. 따라서, 비 선택된 스트링 선택 라인(SSL_UN)에 연결된 스트링에 포함된 메모리 셀에는 상대적으로 강한 FN 스트레스가 인가되고, 선택된 스트링 선택 라인(SSL_SEL)에 연결된 스트링에 포함된 메모리 셀에는 상대적으로 약한 FN 스트레스가 인가될 수 있다.

메모리 셀에 강한 FN 스트레스가 인가되면, 메모리 셀에서 FN 전류가 상대적으로 많이 흐를 수 있고, 이에 따라, 메모리 셀의 문턱 전압이 상승할 수 있다. 따라서, 이후에 상기 메모리 셀에 약한 FN 스트레스가 인가되면 채널 전압에 미치는 영향이 줄어들게 되므로, 프로그램 디스터브가 감소될 수 있다. 한편, 메모리 셀에 약한 FN 스트레스가 인가되면, 메모리 셀에서 FN 전류가 상대적으로 적게 흐를 수 있고, 이에 따라, 메모리 셀의 문턱 전압은 별로 상승하지 않을 수 있다. 따라서, 이후에 상기 메모리 셀에 강한 FN 스트레스가 인가되면 FN 전류가 상대적으로 많이 흐름에 따라, 프로그램 디스터브가 증가할 수 있다.

그러므로, 프로그램 디스터브의 관점에서 볼 때, 메모리 셀에 강한 FN 스트레스가 먼저 인가되고, 이어서 약한 FN 스트레스가 인가되는 것이 바람직할 수 있다. 이를 위해, 본 개시의 일 실시예에 따르면, 가능한 많은 개수의 스트링 선택 라인들이 먼저 비 선택되어 메모리 셀들이 강한 FN 스트레스를 경험하고, 이어서 스트링 선택 라인들이 선택되어 메모리 셀들이 약한 FN 스트레스를 경험하도록 스트링 선택 라인 어드레스 및 비트 라인 그룹 어드레스를 스크램블할 수 있고, 이에 따라, 프로그램 디스터브를 최소화할 수 있다. 이러한 어드레스 스크램블 동작에 대해, 이하에서 상세하게 설명하기로 한다.

도 14는 본 개시의 일 실시예에 따른 비휘발성 메모리 장치의 프로그램 방법을 나타내는 흐름도이다. 도 15a 및 도 15b는 본 개시의 일 실시예에 따른 비휘발성 메모리 장치의 프로그램 순서를 나타낸다. 이하에서는, 도 14 내지 도 15b를 함께 참조하여 설명하기로 한다.

도 14를 참조하면, 본 실시예에 따른 프로그램 방법은 워드 라인을 공유하는 복수의 스트링 선택 라인들 및 복수의 비트 라인 그룹들을 포함하는 비휘발성 메모리 장치를 프로그램하는 방법이다. 예를 들어, 본 실시예에 따른 프로그램 방법은 도 2의 메모리 장치(100)에서 시계열적으로 수행될 수 있다. 도 1 내지 도 13을 참조하여 상술된 내용은 본 실시예에도 적용될 수 있다.

단계 S110에서, 순차적으로 인가되는 제1 내지 제N 어드레스들을 기초로, 제1 비트 라인 그룹에 포함된 제1 비트 라인(BL1)에 연결된 메모리 셀들을 제1 내지 제N 스트링 선택 라인들의 순서에 따라 순차적으로 프로그램한다. 예를 들어, 제1 내지 제N 스트링 선택 라인들은 제1 내지 제4 스트링 선택 라인들(SSL1 내지 SSL4)을 포함할 수 있다. 예를 들어, 제1 비트 라인(BL1) 및 제1 스트링 선택 라인(SSL1)에 연결된 메모리 셀이 프로그램되고, 이어서, 제1 비트 라인(BL1) 및 제2 스트링 선택 라인(SSL2)에 연결된 메모리 셀이 프로그램되고, 이어서, 제1 비트 라인(BL1) 및 제3 스트링 선택 라인(SSL3)에 연결된 메모리 셀이 프로그램되고, 이어서, 제1 비트 라인(BL1) 및 제4 스트링 선택 라인(SSL4)에 연결된 메모리 셀이 프로그램될 수 있다.

단계 S130에서, 순차적으로 인가되는 제N+1 내지 제2·N 어드레스들을 기초로, 제2 비트 라인 그룹에 포함된 제2 비트 라인(BL2)에 연결된 메모리 셀들을 제1 내지 제N 스트링 선택 라인들의 순서에 따라 순차적으로 프로그램한다. 예를 들어, 제2 비트 라인(BL2) 및 제1 스트링 선택 라인(SSL1)에 연결된 메모리 셀이 프로그램되고, 이어서, 제2 비트 라인(BL2) 및 제2 스트링 선택 라인(SSL2)에 연결된 메모리 셀이 프로그램되고, 이어서, 제2 비트 라인(BL2) 및 제3 스트링 선택 라인(SSL3)에 연결된 메모리 셀이 프로그램되고, 이어서, 제2 비트 라인(BL2) 및 제4 스트링 선택 라인(SSL4)에 연결된 메모리 셀이 프로그램될 수 있다.

일 실시예에 따르면, 제1 비트 라인 그룹은 복수의 제1 비트 라인들을 포함하고, 복수의 제1 비트 라인들에 연결된 메모리 셀들 중 동일 워드 라인 및 동일 스트링 선택 라인에 연결된 메모리 셀들은 동시에 프로그램될 수 있다. 일 실시예에 따르면, 동일 워드 라인 및 동일 스트링 선택 라인에 연결된 메모리 셀들 중 제1 비트 라인 그룹에 연결된 메모리 셀은, 제2 비트 라인 그룹에 연결된 메모리 셀보다 먼저 프로그램될 수 있다.

도 16은 본 개시의 일 실시예에 따른 비휘발성 메모리 장치의 프로그램 방법에 따른 메모리 컨트롤러와 메모리 장치의 동작을 나타내는 흐름도이다. 예를 들어, 비휘발성 메모리 장치는 4개의 스트링 선택 라인들 및 2개의 비트 라인 그룹들을 포함할 수 있다. 이 경우, 도 16에 예시된 흐름도에서, N은 1이고, M은 1일 수 있다.

도 16을 참조하면, 단계 S210에서, 메모리 장치(100)는 메모리 컨트롤러(200)로부터 제1 어드레스(ADDR1) 및 프로그램 커맨드(CMD)를 수신한다. 또한, 메모리 장치(100)는, 메모리 컨트롤러(200)로부터 프로그램하고자 하는 데이터를 더 수신할 수 있다. 단계 S215에서, 제n 워드 라인(WLn), 제1 스트링 선택 라인(SSL(N)), 및 제1 비트 라인 그룹(BLG(M))에 포함된 비트 라인에 연결되는 메모리 셀을 프로그램한다. 단계 S220에서, 메모리 장치(100)는 제2 어드레스(ADDR2) 및 프로그램 커맨드(CMD)를 수신하고, 단계 S225에서, 제n 워드 라인(WLn), 제2 스트링 선택 라인(SSL(N+1)), 및 제1 비트 라인 그룹(BLG(M))에 포함된 비트 라인에 연결되는 메모리 셀을 프로그램한다. 단계 S230에서, 메모리 장치(100)는 제3 어드레스(ADDR3) 및 프로그램 커맨드(CMD)를 수신하고, 단계 S235에서, 제n 워드 라인(WLn), 제3 스트링 선택 라인(SSL(N+2)), 및 제1 비트 라인 그룹(BLG(M))에 포함된 비트 라인에 연결되는 메모리 셀을 프로그램한다. 단계 S240에서, 메모리 장치(100)는 제4 어드레스(ADDR4) 및 프로그램 커맨드(CMD)를 수신하고, 단계 S245에서, 제n 워드 라인(WLn), 제4 스트링 선택 라인(SSL(N+3)), 및 제1 비트 라인 그룹(BLG(M))에 포함된 비트 라인에 연결되는 메모리 셀을 프로그램한다.

단계 S250에서, 메모리 장치(100)는 제5 어드레스(ADDR5) 및 프로그램 커맨드(CMD)를 수신하고, 단계 S255에서, 제n 워드 라인(WLn), 제1 스트링 선택 라인(SSL(N)), 및 제2 비트 라인 그룹(BLG(M+1))에 포함된 비트 라인에 연결되는 메모리 셀을 프로그램한다. 단계 S260에서, 메모리 장치(100)는 제6 어드레스(ADDR6) 및 프로그램 커맨드(CMD)를 수신하고, 단계 S265에서, 제n 워드 라인(WLn), 제2 스트링 선택 라인(SSL(N+1)), 및 제6 비트 라인 그룹(BLG(M+1))에 포함된 비트 라인에 연결되는 메모리 셀을 프로그램한다. 단계 S270에서, 메모리 장치(100)는 제7 어드레스(ADDR7) 및 프로그램 커맨드(CMD)를 수신하고, 단계 S275에서, 제n 워드 라인(WLn), 제3 스트링 선택 라인(SSL(N+2)), 및 제2 비트 라인 그룹(BLG(M+1))에 포함된 비트 라인에 연결되는 메모리 셀을 프로그램한다. 단계 S280에서, 메모리 장치(100)는 제8 어드레스(ADDR8) 및 프로그램 커맨드(CMD)를 수신하고, 단계 S285에서, 제n 워드 라인(WLn), 제4 스트링 선택 라인(SSL(N+3)), 및 제2 비트 라인 그룹(BLG(M+1))에 포함된 비트 라인에 연결되는 메모리 셀을 프로그램한다.

도 17a은 본 개시의 일 실시예에 따라 비트 라인 그룹들이 네 개인 경우, 메모리 그룹(MGa)에 대한 프로그램 순서를 나타낸다. 도 17a에서, 메모리 셀들(MC1 내지 MC16) 내에 각각 표시된 숫자는 프로그램 순서를 나타낸다. 도 17a를 참조하면, 메모리 그룹(MGa)은 제n 워드 라인에 공통으로 연결된 메모리 셀들(MC1 내지 MC16)을 포함할 수 있다. 예를 들어, 메모리 셀들(MC1 내지 MC16)은 도 10의 선택된 제5 워드 라인(WL5)에 연결된 메모리 셀들(MC1 내지 MC16)에 대응할 수 있다. 제1 내지 제4 비트 라인들(BL1 내지 BL4)은 예를 들어, X 방향으로 연장되고, 하나의 페이지 버퍼를 공유할 수 있다. 또한, 제1 내지 제4 비트 라인들(BL1 내지 BL4)은 제1 내지 제4 비트 라인 그룹들에 각각 포함될 수 있고, 이에 따라, 제1 내지 제4 비트 라인들(BL1 내지 BL4)에 연결된 메모리 셀들에 대한 프로그램 순서는 서로 다를 수 있다. 제1 내지 제4 스트링 선택 라인들(SSL1 내지 SSL4)은 예를 들어, Y 방향으로 연장되고, 동일 레벨에 배치된 워드 라인을 공유할 수 있다.

제1 비트 라인(BL1)에 연결된 메모리 셀들(MC1, MC5, MC9, MC13)은 순차적으로 프로그램될 수 있고, 이어서, 제2 비트 라인(BL2)에 연결된 메모리 셀들(MC2, MC6, MC10, MC14)은 순차적으로 프로그램될 수 있고, 이어서, 제3 비트 라인(BL3)에 연결된 메모리 셀들(MC3, MC7, MC11, MC15)은 순차적으로 프로그램될 수 있고, 이어서, 제4 비트 라인(BL4)에 연결된 메모리 셀들(MC4, MC8, MC12, MC16)은 순차적으로 프로그램될 수 있다.

일 실시예에서, 메모리 셀들(MC1 내지 MC16)은 SLC들일 수 있다. 그러나, 본 발명은 이에 한정되지 않으며, 메모리 셀들(MC1 내지 MC16)은 MLC들 또는 TLC들일 수 있고, 이때, 메모리 셀들(MC1 내지 MC16)에 대해 HSP(High Speed Program)을 수행하는 경우 도 17a에 예시된 프로그램 순서에 따라 프로그램될 수 있다. 또한, 도 17a에서는 동일 비트 라인에 포함된 메모리 셀들에 대하여, 제1 스트링 선택 라인(SSL1)에서 제4 스트링 선택 라인(SSL4)의 방향으로 프로그램 동작이 순차적으로 수행되지만, 본 발명은 이에 한정되지 않는다. 일부 실시예들에서, 동일 비트 라인에 포함된 메모리 셀들에 대하여, 제4 스트링 선택 라인(SSL4)에서 제1 스트링 선택 라인(SSL1)의 방향으로 프로그램 동작이 순차적으로 수행될 수도 있다. 이하에서는, 프로그램 순서의 다양한 변형 예들을 설명하기로 한다.

도 17b은 본 개시의 일 실시예에 따라 비트 라인 그룹들이 네 개인 경우, 메모리 그룹(MGb)에 대한 프로그램 순서를 나타낸다. 도 17b에서, 메모리 셀들(MC1 내지 MC16) 내에 각각 표시된 숫자는 프로그램 순서를 나타낸다. 도 17b를 참조하면, 메모리 그룹(MGb)은 제n 워드 라인에 공통으로 연결된 메모리 셀들(MC1 내지 MC16)을 포함할 수 있다. 도 17b에 예시된, 메모리 그룹(MGb)에 대한 프로그램 순서는 도 17a에 예시된 실시예의 변형 실시예에 대응할 수 있고, 중복된 설명은 생략하기로 한다. 예를 들어, 제1 비트 라인(BL1)에 연결된 메모리 셀들(MC1, MC5, MC9, MC13) 중, 메모리 셀(MC1)이 먼저 프로그램되고, 이어서, 메모리 셀(MC9)이 프로그램되고, 이어서, 메모리 셀(MC5)이 프로그램되고, 이어서, 메모리 셀(MC13)이 프로그램될 수 있다. 이와 같이, 본 실시예에 따르면, 제1 비트 라인(BL1)에 연결된 메모리 셀들(MC1, MC5, MC9 및 MC13)에 대한 프로그램 순서는 스트링 선택 라인들의 배치 순서에 대응하지 않을 수도 있다.

도 17c는 본 개시의 일 실시예에 따라 비트 라인 그룹들이 네 개인 경우, 메모리 그룹(MGc)에 대한 프로그램 순서를 나타낸다. 도 17c에서, 메모리 셀들(MC1 내지 MC16) 내에 각각 표시된 숫자는 프로그램 순서를 나타낸다. 도 17c를 참조하면, 메모리 그룹(MGc)은 제n 워드 라인에 공통으로 연결된 메모리 셀들(MC1 내지 MC16)을 포함할 수 있다. 도 17c에 예시된, 메모리 그룹(MGc)에 대한 프로그램 순서는 도 17a에 예시된 실시예의 변형 실시예에 대응할 수 있고, 중복된 설명은 생략하기로 한다. 예를 들어, 제1 비트 라인(BL1)에 연결된 메모리 셀들(MC1, MC5, MC9, MC13)이 순차적으로 프로그램될 수 있고, 이어서, 제3 비트 라인(BL3)에 연결된 메모리 셀들(MC3, MC7, MC11, MC15)이 순차적으로 프로그램될 수 있고, 이어서, 제2 비트 라인(BL2)에 연결된 메모리 셀들(MC2, MC6, MC10, MC14)이 순차적으로 프로그램될 수 있고, 이어서, 제4 비트 라인(BL4)에 연결된 메모리 셀들(MC4, MC8, MC12, MC16)이 순차적으로 프로그램될 수 있다. 이와 같이, 본 실시예에 따르면, 서로 다른 비트 라인 그룹들에 각각 포함된 비트 라인들에 연결된 메모리 셀들에 대한 프로그램 순서는 비트 라인들의 배치 순서에 대응하지 않을 수도 있다.

도 18은 본 개시의 일 실시예에 따라 비트 라인 그룹이 두 개인 경우, 메모리 셀들에 대한 프로그램 순서를 나타낸다. 도 18에서, 메모리 셀들(MC1 내지 MC16) 내에 각각 표시된 숫자는 프로그램 순서를 나타낸다. 도 18을 참조하면, 제1 내지 제4 비트 라인들(BL1 내지 BL4)은 예를 들어, X 방향으로 연장되고, 제1 및 제3 비트 라인들(BL1, BL3)은 하나의 페이지 버퍼를 공유하고, 제2 및 제4 비트 라인들(BL2, BL4)은 다른 페이지 버퍼를 공유할 수 있다. 또한, 제1 및 제3 비트 라인들(BL1, BL3)은 제1 비트 라인 그룹(BLG1)에 포함될 수 있고, 제2 및 제4 비트 라인들(BL2, BL4)은 제2 비트 라인 그룹(BLG2)에 포함될 수 있다. 이에 따라, 제1 및 제2 비트 라인 그룹들(BLG1, BLG2)에 연결된 메모리 셀들에 대한 프로그램 순서는 서로 다를 수 있다. 제1 내지 제4 스트링 선택 라인들(SSL1 내지 SSL4)은 예를 들어, Y 방향으로 연장되고, 동일 레벨에 배치된 워드 라인을 공유할 수 있다.

일 실시예에서, 메모리 셀들(MC1 내지 MC16)은 SLC들일 수 있다. 제1 비트 라인 그룹(BLG1)에 포함된 제1 및 제3 비트 라인들(BL1, BL3)에 연결된 메모리 셀들(MC1, MC5, MC9, MC13, MC3, MC7, MC11, MC15)이 먼저 프로그램되고, 제2 비트 라인 그룹(BLG2)에 포함된 제2 및 제4 비트 라인들(BL2, BL4)에 연결된 메모리 셀들(MC2, MC6, MC10, MC14, MC4, MC8, MC12, MC16)이 이어서 프로그램될 수 있다. 구체적으로, 메모리 셀들(MC1, MC3)이 동시에 프로그램되고, 이어서, 메모리 셀들(MC5, MC7)이 동시에 프로그램되고, 이어서, 메모리 셀들(MC9, MC11)이 동시에 프로그램되고, 이어서, 메모리 셀들(MC13, MC15)이 동시에 프로그램될 수 있다. 이어서, 메모리 셀들(MC2, MC4)이 동시에 프로그램되고, 이어서, 메모리 셀들(MC6, MC8)이 동시에 프로그램되고, 이어서, 메모리 셀들(MC10, MC12)이 동시에 프로그램되고, 이어서, 메모리 셀들(MC14, MC16)이 동시에 프로그램될 수 있다.

도 19는 본 개시의 일 실시예에 따라 MLC들에 대한 프로그램 순서를 나타낸다. 도 19에서, 메모리 셀들(MC1 내지 MC16) 내에 각각 표시된 숫자는 프로그램 순서를 나타낸다. 도 19를 참조하면, 메모리 셀들(MC1 내지 MC16)은 MLC들일 수 있고, 쉐도우(shadow) 프로그램 방법에 따라 프로그램될 수 있다. 먼저, 메모리 셀들(MC1 내지 MC16)에 대한 LSB(Least Significant Bit) 프로그램 동작들이 순차적으로 수행될 수 있고, 이때, LSB 프로그램 동작들은 도 17a에 예시된 프로그램 순서에 따라 수행될 수 있다. 다음으로, 메모리 셀들(MC1 내지 MC16)에 대한 MSB(Most Significant Bit) 프로그램 동작들이 순차적으로 수행될 수 있고, 이때, MSB 프로그램 동작들은 도 17a에 예시된 프로그램 순서에 따라 수행될 수 있다.

도 20은 본 개시의 일 실시예에 따라 TLC들에 대한 프로그램 순서를 나타낸다. 도 20에서, 메모리 셀들(MC1 내지 MC16) 내에 각각 표시된 숫자는 프로그램 순서를 나타낸다. 도 20을 참조하면, 메모리 셀들(MC1 내지 MC16)은 TLC들일 수 있고, 쉐도우 프로그램 방법에 따라 프로그램될 수 있다. 먼저, 메모리 셀들(MC1 내지 MC16)에 대한 LSB 프로그램 동작들이 순차적으로 수행될 수 있고, 이때, LSB 프로그램 동작들은 도 17a에 예시된 프로그램 순서에 따라 수행될 수 있다. 다음으로, 메모리 셀들(MC1 내지 MC16)에 대한 CSB(Central Significant Bit) 프로그램 동작들이 순차적으로 수행될 수 있고, 이때, CSB 프로그램 동작들은 도 16a에 예시된 프로그램 순서에 따라 수행될 수 있다. 다음으로, 메모리 셀들(MC1 내지 MC16)에 대한 MSB 프로그램 동작들이 순차적으로 수행될 수 있고, 이때, MSB 프로그램 동작들은 도 16a에 예시된 프로그램 순서에 따라 수행될 수 있다.

도 21은 본 개시의 일 실시예에 따라 3D 메모리 장치(300a)에 대한 프로그램 순서를 나타낸다. 도 21에서, 메모리 셀들 내에 각각 표시된 숫자는 프로그램 순서를 나타낸다. 도 21을 참조하면, 3D 메모리 장치(300a)는 제1 및 제2 비트 라인들(BL1, BL2), 제1 내지 제4 스트링 선택 라인들(SSL1 내지 SSL4), 제n 워드 라인(WLn), 제n+1 워드 라인(WLn+1), 제1 내지 제4 그라운드 선택 라인들(GSL1 내지 GSL4)을 포함할 수 있다. 또한, 3D 메모리 장치(300a)는 제1 및 제2 비트 라인들(BL1, BL2)과 제1 내지 제4 스트링 선택 라인들(SSL1 내지 SSL4)이 교차하는 지점들에 각각 연결되는 복수의 스트링들(NS)을 포함할 수 있다.

일 실시예에 따르면, 제n 워드 라인(WLn)에 연결된 메모리 셀들을 포함하는 제n 메모리 그룹(MGn)에 대한 프로그램이 먼저 수행될 수 있다. 구체적으로, 제n 워드 라인(WLn), 제1 비트 라인(BL1) 및 제1 내지 제4 스트링 선택 라인들(SSL1 내지 SSL4)에 연결된 메모리 셀들에 대한 프로그램이 순차적으로 수행되고, 이어서, 제n 워드 라인(WLn), 제2 비트 라인(BL2) 및 제1 내지 제4 스트링 선택 라인들(SSL1 내지 SSL4)에 연결된 메모리 셀들에 대한 프로그램이 순차적으로 수행될 수 있다. 이어서, 제n+1 워드 라인(WLn+1)에 연결된 메모리 셀들을 포함하는 제n+1 메모리 그룹(MGn+1)에 대한 프로그램이 수행될 수 있다. 구체적으로, 제n+1 워드 라인(WLn+1), 제1 비트 라인(BL1) 및 제1 내지 제4 스트링 선택 라인들(SSL1 내지 SSL4)에 연결된 메모리 셀들에 대한 프로그램이 순차적으로 수행되고, 이어서, 제n+1 워드 라인(WLn+1), 제2 비트 라인(BL2) 및 제1 내지 제4 스트링 선택 라인들(SSL1 내지 SSL4)에 연결된 메모리 셀들에 대한 프로그램이 순차적으로 수행될 수 있다.

도 22a 및 도 22b는 본 개시의 일 실시예에 따라 MLC들을 포함하는 3D 메모리 장치(300b)에 대한 프로그램 순서를 나타낸다. 도 22a는 3D 메모리 장치(300b)의 XZ 평면을 나타내고, 도 22b는 3D 메모리 장치(300b)의 XY 평면을 나타낸다. 도 22a 및 도 22b에서, 원통 형상의 메모리 셀들 내에 각각 표시된 숫자는 프로그램 순서를 나타낸다. 도 22a를 참조하면, 3D 메모리 장치(300b)은 제1 비트 라인(BL1)에 공통으로 연결되고, 제1 내지 제4 스트링 선택 라인들(SSL1 내지 SSL4)에 각각 연결되는 스트링들(NS)을 포함할 수 있다. 각 스트링(NS)은 제n 내지 제n+2 워드 라인들(WLn 내지 WLn+2)에 각각 연결되는 복수의 메모리 셀들을 포함할 수 있다. 도 21b를 참조하면, 3D 메모리 장치(300b)는 제n 워드 라인(WLn)에 연결된 복수의 메모리 셀들을 포함할 수 있다. 본 실시예에 따르면, 3D 메모리 장치(300b)에 포함된 MLC들에 대해 쉐도우 프로그램 방법으로 프로그램할 수 있다.

먼저, 제n 워드 라인(WLn)에 연결된 제n 메모리 그룹(MGn)에 포함된 메모리 셀들에 대한 LSB 프로그램 동작들이 순차적으로 수행될 수 있다. 이때, 제n 메모리 그룹(MGn)에 포함된 메모리 셀들에 대한 LSB 프로그램 동작의 순서는 도 21b에 예시된 바와 같다. 이어서, 제n+1 워드 라인(WLn+1)에 연결된 메모리 셀들에 대한 순차적인 LSB 프로그램 동작들, 제n 워드 라인(WLn)에 연결된 메모리 셀들에 대한 순차적인 MSB 프로그램 동작들, 제n+2 워드 라인(WLn+2)에 연결된 메모리 셀들에 대한 순차적인 LSB 프로그램 동작들, 제n+1 워드 라인(WLn+1)에 연결된 메모리 셀들에 대한 순차적인 MSB 프로그램 동작들, 제n+2 워드 라인(WLn+2)에 연결된 메모리 셀들에 대한 순차적인 MSB 프로그램 동작들이 순차적으로 수행될 수 있다.

도 23a 및 도 23b는 본 개시의 일 실시예에 따라 MLC들을 포함하는 3D 메모리 장치(300c)에 대한 프로그램 순서를 나타낸다. 도 23a는 3D 메모리 장치(300c)의 YZ 평면을 나타내고, 도 23b는 3D 메모리 장치(300c)의 XY 평면을 나타낸다. 도 23a 및 도 23b에서, 원통 형상의 메모리 셀들 내에 각각 표시된 숫자는 프로그램 순서를 나타낸다. 도 23a를 참조하면, 3D 메모리 장치(300c)은 제1 내지 제6 비트 라인들(BL1 내지 BL6)에 각각 연결되고, 제1 스트링 선택 라인(SSL1)에 공통으로 연결되는 스트링들(NS)을 포함할 수 있다. 각 스트링(NS)은 제n 내지 제n+2 워드 라인들(WLn 내지 WLn+2)에 각각 연결되는 복수의 메모리 셀들을 포함할 수 있다. 도 23b를 참조하면, 3D 메모리 장치(300c)는 제n 워드 라인(WLn)에 연결된 복수의 메모리 셀들을 포함할 수 있다. 본 실시예에서, 제1 및 제5 비트 라인들(BL1, BL5)은 제1 비트 라인 그룹에 포함되고, 제2 및 제6 비트 라인들(BL2, BL6)은 제2 비트 라인 그룹에 포함되고, 제3 및 제4 비트 라인들(BL3, BL4)은 제3 및 제4 비트 라인 그룹들에 각각 포함될 수 있다. 본 실시예에 따르면, 3D 메모리 장치(300c)에 포함된 MLC들에 대해 쉐도우 프로그램 방법으로 프로그램할 수 있다.

먼저, 제n 워드 라인(WLn)에 연결된 제n 메모리 그룹(MGn)에 포함된 메모리 셀들에 대한 LSB 프로그램 동작들이 순차적으로 수행될 수 있다. 이때, 제n 메모리 그룹(MGn)에 포함된 메모리 셀들에 대한 LSB 프로그램 동작의 순서는 도 22b에 예시된 바와 같다. 이어서, 제n+1 워드 라인(WLn+1)에 연결된 메모리 셀들에 대한 순차적인 LSB 프로그램 동작들, 제n 워드 라인(WLn)에 연결된 메모리 셀들에 대한 순차적인 MSB 프로그램 동작들, 이어서, 제n+2 워드 라인(WLn+2)에 연결된 메모리 셀들에 대한 순차적인 LSB 프로그램 동작들, 이어서, 제n+1 워드 라인(WLn+1)에 연결된 메모리 셀들에 대한 순차적인 MSB 프로그램 동작들, 그리고 이어서, 제n+2 워드 라인(WLn+2)에 연결된 메모리 셀들에 대한 순차적인 MSB 프로그램 동작들이 순차적으로 수행될 수 있다.

도 22a 내지 도 23b에서는 MLC들에 대한 프로그램 순서를 예시하고 있으나, 본 발명은 이에 한정되지 않는다. 일부 실시예들에, TLC들에 대해서도 본 개시의 실시예들에 따른 프로그램 방법 및 쉐도우 프로그램 방법을 함께 적용할 수 있다.

도 24는 본 개시의 일 실시예에 따른 비휘발성 메모리 장치의 프로그램 방법을 나타내는 흐름도이다. 도 24를 참조하면, 본 실시예에 따른 프로그램 방법은 워드 라인을 공유하는 복수의 스트링 선택 라인들 및 복수의 비트 라인 그룹들을 포함하는 비휘발성 메모리 장치를 프로그램하는 방법이다. 예를 들어, 본 실시예에 따른 프로그램 방법은 도 2의 메모리 장치(100)에서 시계열적으로 수행될 수 있다. 도 1 내지 도 23b를 참조하여 상술된 내용은 본 실시예에도 적용될 수 있고, 중복된 설명은 생략한다.

단계 S310에서, 어드레스 및 프로그램 커맨드를 수신한다. 단계 S330에서, 스트링 선택 라인 어드레스가 비트 라인 그룹 어드레스보다 하위 비트에 위치하도록 어드레스를 수정 어드레스로 변환한다. 예를 들어, 어드레스는 논리 주소를 포함하고, 수정 어드레스는 워드 라인 어드레스, 비트 라인 그룹 어드레스, 스트링 선택 라인 어드레스를 포함할 수 있다. 단계 S350에서, 수정 어드레스에 따라 메모리 셀들을 프로그램한다. 예를 들어, 제n 워드 라인에 연결되고, 제1 비트 라인 그룹에 포함된 메모리 셀들을 복수의 스트링 선택 라인들 별로 순차적으로 프로그램하고, 이어서, 제n 워드 라인에 연결되고, 제2 비트 라인 그룹에 포함된 메모리 셀들을 복수의 스트링 선택 라인들 별로 순차적으로 프로그램할 수 있다.

도 25는 도 16a의 메모리 셀들(MC1 내지 MC16)에 대한 16회의 프로그램 디스터브를 나타낸다. 도 25를 참조하면, "U"는 스트링 선택 라인이 비 선택된 경우를 나타내고, "S"는 스트링 선택 라인이 선택된 경우를 나타낸다. 따라서, "U"의 경우 메모리 셀은 강한 FN 스트레스를 받고, "S"의 경우 메모리 셀은 약한 FN 스트레스를 받을 수 있다. 제1 및 제2 디스터브 케이스들(25a, 25b)은 본 개시의 일 실시예에 따른 프로그램 방법을 적용하지 않은 경우의 베스트 케이스 및 워스트 케이스를 각각 나타낸다. 한편, 제3 및 제4 디스터브 케이스들(25c, 25d)은 본 개시의 일 실시예에 따른 프로그램 방법을 적용한 경우의 베스트 케이스 및 워스트 케이스를 각각 나타낸다.

본 개시의 일 실시예에 따른 프로그램 방법을 적용하지 않은 경우에는, 예를 들어, 제1 스트링 선택 라인(SSL1)에 연결된 메모리 셀들(MC1 내지 MC4)을 순차적으로 프로그램하고, 이어서, 제2 스트링 선택 라인(SSL2)에 연결된 메모리 셀들(MC5 내지 MC8)을 순차적으로 프로그램하고, 이어서, 제3 스트링 선택 라인(SSL3)에 연결된 메모리 셀들(MC9 내지 MC12)을 순차적으로 프로그램하고, 이어서, 제4 스트링 선택 라인(SSL4)에 연결된 메모리 셀들(MC13 내지 MC16)을 순차적으로 프로그램할 수 있다.

제1 디스터브 케이스(25a)에서, 강한 12번의 FN 스트레스를 미리 받고, 이어서 약한 4번의 FN 스트레스를 받을 수 있으며, 이 경우 프로그램 디스터브가 감소할 수 있으므로 베스트 케이스에 해당할 수 있다. 한편, 제2 디스터브 케이스(25b)에서, 약한 4번의 FN 스트레스를 미리 받고, 이어서 강한 16번의 FN 스트레스를 받을 수 있으며, 이 경우 프로그램 디스터브가 증가할 수 있으므로 워스트 케이스에 해당할 수 있다. 제1 디스터브 케이스(25a)에서 메모리 셀의 문턱 전압 상승량과 제2 디스터브 케이스(25b)에서 메모리 셀의 문턱 전압 상승량 사이의 차이는 상당히 클 수 있다.

제3 디스터브 케이스(25c)에서, 강한 3번의 FN 스트레스를 미리 받고, 이어서 약한 1번의 FN 스트레스를 받을 수 있으며, 다시 강한 3번의 FN 스트레스를 받고, 이어서 약한 1번의 FN 스트레스를 받을 수 있다. 이 경우 강한 FN 스트레스를 먼저 받으므로 프로그램 디스터브가 감소할 수 있으므로 베스트 케이스에 해당할 수 있다. 한편, 제4 디스터브 케이스(25d)에서, 약한 1번의 FN 스트레스를 미리 받고, 이어서 강한 3번의 FN 스트레스를 받을 수 있으며, 다시 약한 1번의 FN 스트레스를 받고, 이어서 강한 3번의 FN 스트레스를 받을 수 있다. 이 경우 약한 FN 스트레스를 먼저 받으므로 프로그램 디스터브가 증가할 수 있으므로 워스트 케이스에 해당할 수 있다. 그러나, 제3 디스터브 케이스(25c)에서 메모리 셀의 문턱 전압 상승량과 제4 디스터브 케이스(25d)에서 메모리 셀의 문턱 전압 상승량 사이의 차이는, 제1 디스터브 케이스(25a)에서 메모리 셀의 문턱 전압 상승량과 제2 디스터브 케이스(25b)에서 메모리 셀의 문턱 전압 상승량 사이의 차이보다 작을 수 있다. 다시 말해, 본 개시의 일 실시예에 따른 프로그램 방법에 따르면, 워스트 케이스를 개선시킴으로써 베스트 케이스와 워스트 케이스 사이의 프로그램 디스터브 차이를 줄일 수 있고, 전반적으로 프로그램 디스터브가 평준화될 수 있다.

도 26은 본 개시의 실시예들에 따른 메모리 장치를 SSD 시스템(1000)에 적용한 예를 나타내는 블록도이다. 도 26을 참조하면, SSD 시스템(1000)은 호스트(1100) 및 SSD(1200)를 포함할 수 있다. SSD(1200)는 신호 커넥터를 통해 호스트(1100)와 신호를 주고 받으며, 전원 커넥터를 통해 전원을 입력 받는다. SSD(1200)는 SSD 컨트롤러(1210), 보조 전원 장치(1220) 및 메모리 장치들(1230, 1240, 1250)을 포함할 수 있다. 메모리 장치들(1230, 1240, 1250)은 수직 적층형 NAND 플래시 메모리 장치일 수 있다. 이때, SSD(1200)는 도 1 내지 도 25를 참조하여 상술된 실시예들을 이용하여 구현될 수 있다.

이상에서와 같이 도면과 명세서에서 예시적인 실시예들이 개시되었다. 본 명세서에서 특정한 용어를 사용하여 실시예들을 설명되었으나, 이는 단지 본 개시의 기술적 사상을 설명하기 위한 목적에서 사용된 것이지 의미 한정이나 특허청구범위에 기재된 본 개시의 범위를 제한하기 위하여 사용된 것은 아니다. 그러므로 본 기술분야의 통상의 지식을 가진 자라면 이로부터 다양한 변형 및 균등한 타 실시예가 가능하다는 점을 이해할 것이다. 따라서, 본 개시의 진정한 기술적 보호범위는 첨부된 특허청구범위의 기술적 사상에 의해 정해져야 할 것이다.

Claims (20)

- 워드 라인을 공유하는 제1 및 제2 스트링 선택 라인들을 포함하는 제1 내지 제N 스트링 선택 라인들, 및 제1 및 제2 비트 라인 그룹들을 포함하는 비휘발성 메모리 장치의 프로그램 방법으로서,

순차적으로 인가되는 제1 내지 제N 어드레스들을 기초로, 상기 워드 라인, 및 상기 제1 비트 라인 그룹에 포함된 복수의 제1 비트 라인들에 연결된 제1 메모리 셀들을 상기 제1 내지 제N 스트링 선택 라인들의 순서에 따라 순차적으로 프로그램하는 단계; 및

이어서, 순차적으로 인가되는 제N+1 내지 제2·N 어드레스들을 기초로, 상기 워드 라인, 및 상기 제2 비트 라인 그룹에 포함된 복수의 제2 비트 라인들에 연결된 제2 메모리 셀들을 상기 제1 내지 제N 스트링 선택 라인들의 순서에 따라 순차적으로 프로그램하는 단계를 포함하고,

상기 제1 메모리 셀들을 상기 제1 내지 제N 스트링 선택 라인들의 순서에 따라 순차적으로 프로그램하는 단계는,

상기 제1 어드레스 및 제1 프로그램 커맨드를 수신하는 단계;

상기 제1 어드레스 및 상기 제1 프로그램 커맨드에 응답하여, 상기 워드 라인, 상기 복수의 제1 비트 라인들, 및 상기 제1 스트링 선택 라인에 연결된 메모리 셀들을 동시에 프로그램하는 단계;

제2 어드레스 및 제2 프로그램 커맨드를 수신하는 단계; 및

상기 제2 어드레스 및 상기 제2 프로그램 커맨드에 응답하여, 상기 워드 라인, 상기 복수의 제1 비트 라인들, 및 상기 제2 스트링 선택 라인에 연결된 메모리 셀들을 동시에 프로그램하는 단계를 포함하고,

N은 2 이상의 자연수인 것을 특징으로 하는 방법. - 제1 내지 제4 스트링 선택 라인들, 기판 상에 수직으로 적층된 복수의 워드 라인들, 제1 내지 제4 비트 라인 그룹들을 포함하는 3차원 비휘발성 메모리 장치의 프로그램 방법으로서,

제1 어드레스 및 제1 프로그램 커맨드에 응답하여, 상기 복수의 워드 라인들 중 제1 워드 라인, 상기 제1 스트링 선택 라인, 및 상기 제1 비트 라인 그룹에 포함된 제1 비트 라인들에 연결된 제1 메모리 셀들을 프로그램하는 단계;

제2 어드레스 및 제2 프로그램 커맨드에 응답하여, 상기 제1 워드 라인, 상기 제2 및 제4 스트링 선택 라인들 사이에 배치된 상기 제3 스트링 선택 라인, 및 상기 제1 비트 라인들에 연결된 제2 메모리 셀들을 프로그램하는 단계;

제3 어드레스 및 제3 프로그램 커맨드에 응답하여, 상기 제1 워드 라인, 상기 제1 및 제3 스트링 선택 라인들 사이에 배치된 상기 제2 스트링 선택 라인, 및 상기 제1 비트 라인들에 연결된 제3 메모리 셀들을 프로그램하는 단계;

제4 어드레스 및 제4 프로그램 커맨드에 응답하여, 상기 제1 워드 라인, 상기 제4 스트링 선택 라인, 및 상기 제1 비트 라인들에 연결된 제4 메모리 셀들을 프로그램하는 단계; 및

제5 어드레스 및 제5 프로그램 커맨드에 응답하여, 상기 제1 워드 라인, 상기 제1 스트링 선택 라인, 및 상기 제2 비트 라인 그룹에 포함된 제2 비트 라인들에 연결된 제5 메모리 셀들을 프로그램하는 단계를 포함하고,

상기 프로그램 방법은,

상기 제1 내지 제5 어드레스들에 대한 스트링 선택 라인 어드레스가 상기 제1 내지 제4 비트 라인 그룹들에 대한 비트 라인 그룹 어드레스보다 하위 비트에 위치하도록, 상기 제1 내지 제5 어드레스들을 제1 내지 제5 수정 어드레스들로 각각 변환하는 단계를 더 포함하는 방법. - 제1항에 있어서,

상기 워드 라인 및 상기 제1 스트링 선택 라인에 연결된 메모리 셀들 중 상기 복수의 제1 비트 라인들에 연결된 메모리 셀은, 상기 복수의 제2 비트 라인들에 연결된 메모리 셀보다 먼저 프로그램되는 것을 특징으로 하는 방법. - 삭제

- 제1항에 있어서,

상기 제2 메모리 셀들을 순차적으로 프로그램하는 단계는,

제3 어드레스 및 제3 프로그램 커맨드를 수신하는 단계;

상기 제3 어드레스 및 상기 제3 프로그램 커맨드에 응답하여, 상기 워드 라인, 상기 복수의 제2 비트 라인들, 및 상기 제1 스트링 선택 라인에 연결된 메모리 셀들을 동시에 프로그램하는 단계;

제4 어드레스 및 제4 프로그램 커맨드를 수신하는 단계; 및

상기 제4 어드레스 및 상기 제4 프로그램 커맨드에 응답하여, 상기 워드 라인, 상기 복수의 제2 비트 라인들, 및 상기 제2 스트링 선택 라인에 연결된 메모리 셀들을 동시에 프로그램하는 단계를 포함하는 것을 특징으로 하는 방법. - 제1항에 있어서,

상기 제1 어드레스 및 상기 제1 프로그램 커맨드를 수신하는 단계 이후에, 상기 제1 어드레스를 제1 수정 어드레스로 변환하는 단계; 및

상기 제2 어드레스 및 상기 제2 프로그램 커맨드를 수신하는 단계 이후에, 상기 제2 어드레스를 제2 수정 어드레스로 변환하는 단계를 더 포함하고,

상기 제1 어드레스 및 상기 제1 프로그램 커맨드에 응답하여, 상기 워드 라인, 상기 복수의 제1 비트 라인들, 및 상기 제1 스트링 선택 라인에 연결된 상기 메모리 셀들을 동시에 프로그램하는 단계는, 상기 제1 수정 어드레스에 따라 상기 메모리 셀들을 동시에 프로그램하고,

상기 제2 어드레스 및 상기 제2 프로그램 커맨드에 응답하여, 상기 워드 라인, 상기 복수의 제1 비트 라인들, 및 상기 제2 스트링 선택 라인에 연결된 상기 메모리 셀들을 동시에 프로그램하는 단계는, 상기 제2 수정 어드레스에 따라 상기 메모리 셀들을 동시에 프로그램하는 것을 특징으로 하는 방법. - 제6항에 있어서,

상기 제1 수정 어드레스로 변환하는 단계 및 상기 제2 수정 어드레스로 변환하는 단계는, 스트링 선택 라인 어드레스가 비트 라인 그룹 어드레스보다 하위 비트에 위치하도록 상기 제1 및 제2 어드레스들을 상기 제1 및 제2 수정 어드레스들로 각각 변환하는 것을 특징으로 하는 방법. - 제6항에 있어서,

상기 제1 어드레스는, 논리 주소를 포함하고,

상기 제1 수정 어드레스는, 워드 라인 어드레스, 비트 라인 그룹 어드레스, 및 스트링 선택 라인 어드레스를 포함하는 것을 특징으로 하는 방법. - 제1항에 있어서,

상기 제2 메모리 셀들을 순차적으로 프로그램하는 단계 이후에, 순차적으로 인가되는 제2·N+1 내지 제3·N 어드레스들을 기초로, 상기 워드 라인에 인접한 인접 워드 라인, 및 상기 복수의 제1 비트 라인들에 연결된 제3 메모리 셀들을 상기 제1 내지 제N 스트링 선택 라인들의 순서에 따라 순차적으로 프로그램하는 단계; 및

이어서, 순차적으로 인가되는 제3·N+1 내지 제4·N 어드레스들을 기초로, 상기 인접 워드 라인, 및 상기 복수의 제2 비트 라인들에 연결된 제4 메모리 셀들을 상기 제1 내지 제N 스트링 선택 라인들의 순서에 따라 순차적으로 프로그램하는 단계를 더 포함하는 것을 특징으로 하는 방법. - 제1항에 있어서,

상기 메모리 셀들은 MLC(Multi Level Cell)들이고,

상기 제1 메모리 셀들을 순차적으로 프로그램하는 단계는, 상기 제1 메모리 셀들에 대한 LSB(Least Significant Bit) 프로그램 동작들을 순차적으로 수행하고,

상기 제2 메모리 셀들을 순차적으로 프로그램하는 단계는, 상기 제2 메모리 셀들에 대한 LSB 프로그램 동작들을 순차적으로 수행하는 것을 특징으로 하는 방법. - 제10항에 있어서,

상기 제2 메모리 셀들을 순차적으로 프로그램하는 단계 이후에, 상기 워드 라인에 인접한 인접 워드 라인, 및 상기 복수의 제1 비트 라인들에 연결된 제3 메모리 셀들에 대한 LSB 프로그램 동작들을 상기 제1 내지 제N 스트링 선택 라인들의 순서에 따라 순차적으로 수행하는 단계;

이어서, 상기 인접 워드 라인, 및 상기 복수의 제2 비트 라인들에 연결된 제4 메모리 셀들에 대한 LSB 프로그램 동작들을 상기 제1 내지 제N 스트링 선택 라인들의 순서에 따라 순차적으로 수행하는 단계;

이어서, 상기 제1 메모리 셀들에 대한 MSB 프로그램 동작들을 상기 제1 내지 제N 스트링 선택 라인들의 순서에 따라 순차적으로 수행하는 단계;

이어서, 상기 제2 메모리 셀들에 대한 MSB 프로그램 동작들을 상기 제1 내지 제N 스트링 선택 라인들의 순서에 따라 순차적으로 수행하는 단계;

이어서, 상기 제3 메모리 셀들에 대한 MSB 프로그램 동작들을 상기 제1 내지 제N 스트링 선택 라인들의 순서에 따라 순차적으로 수행하는 단계; 및

이어서, 상기 제4 메모리 셀들에 대한 MSB 프로그램 동작들을 상기 제1 내지 제N 스트링 선택 라인들의 순서에 따라 순차적으로 수행하는 단계를 더 포함하는 것을 특징으로 하는 방법. - 워드 라인을 공유하는 제1 내지 제N 스트링 선택 라인들, 및 제1 및 제2 비트 라인 그룹들을 포함하는 비휘발성 메모리 장치의 프로그램 방법으로서,

순차적으로 인가되는 제1 내지 제N 어드레스들을 기초로, 상기 워드 라인, 및 상기 제1 비트 라인 그룹에 포함된 복수의 제1 비트 라인들에 연결된 제1 메모리 셀들을 상기 제1 내지 제N 스트링 선택 라인들의 순서에 따라 순차적으로 프로그램하는 단계; 및

이어서, 순차적으로 인가되는 제N+1 내지 제2·N 어드레스들을 기초로, 상기 워드 라인, 및 상기 제2 비트 라인 그룹에 포함된 복수의 제2 비트 라인들에 연결된 제2 메모리 셀들을 상기 제1 내지 제N 스트링 선택 라인들의 순서에 따라 순차적으로 프로그램하는 단계를 포함하고,

상기 비휘발성 메모리 장치는, 복수의 비트 라인들에 연결되는 수직 낸드 플래시 메모리이고,

상기 복수의 비트 라인들 중 K개의 비트 라인들은 하나의 페이지 버퍼에 연결되며, K는 비트 라인 그룹들의 개수에 대응하는 2 이상의 정수이고,

상기 복수의 제1 비트 라인들 중 하나와 상기 제2 비트 라인들 중 하나는 동일한 페이지 버퍼에 연결되는 것을 특징으로 하는 방법. - 제1항에 있어서,

상기 비휘발성 메모리 장치는, 복수의 비트 라인들에 연결되는 수평 낸드 플래시 메모리이고,

상기 복수의 비트 라인들 중 K개의 비트 라인들은 하나의 페이지 버퍼에 연결되며, K는 비트 라인 그룹들의 개수에 대응하는 2 이상의 정수인 것을 특징으로 하는 방법. - 워드 라인을 공유하는 제1 내지 제N 스트링 선택 라인들, 및 제1 및 제2 비트 라인 그룹들을 포함하는 비휘발성 메모리 장치의 프로그램 방법으로서,

순차적으로 인가되는 제1 내지 제N 어드레스들을 기초로, 상기 워드 라인, 및 상기 제1 비트 라인 그룹에 포함된 복수의 비트 라인들에 연결된 제1 메모리 셀들을 상기 제1 내지 제N 스트링 선택 라인들의 순서에 따라 순차적으로 프로그램하는 단계; 및

이어서, 순차적으로 인가되는 제N+1 내지 제2·N 어드레스들을 기초로, 상기 워드 라인, 및 상기 제2 비트 라인 그룹에 포함된 복수의 비트 라인들에 연결된 제2 메모리 셀들을 상기 제1 내지 제N 스트링 선택 라인들의 순서에 따라 순차적으로 프로그램하는 단계를 포함하고,

상기 비휘발성 메모리 장치는 상기 제1 및 제2 비트 라인 그룹들을 포함하는 4개의 비트 라인 그룹들을 포함하고,

상기 4개의 비트 라인 그룹들 각각에 포함된 제1 내지 제4 비트 라인들은 하나의 페이지 버퍼를 공유하는 것을 특징으로 하는 방법. - 워드 라인을 공유하는 제1 및 제2 스트링 선택 라인들, 및 제1 및 제2 비트 라인 그룹들을 포함하는 비휘발성 메모리 장치의 프로그램 방법으로서,

제1 어드레스 및 제1 프로그램 커맨드에 응답하여, 상기 워드 라인, 상기 제1 스트링 선택 라인, 및 제1 비트 라인 그룹에 포함된 제1 비트 라인들에 연결된 제1 메모리 셀들을 프로그램하는 단계;

이어서, 제2 어드레스 및 제2 프로그램 커맨드에 응답하여, 상기 워드 라인, 제2 스트링 선택 라인, 및 상기 제1 비트 라인 그룹에 포함된 상기 제1 비트 라인들에 연결된 제2 메모리 셀들을 프로그램하는 단계;

이어서, 제3 어드레스 및 제3 프로그램 커맨드에 응답하여, 상기 워드 라인, 상기 제1 스트링 선택 라인 및 상기 제2 비트 라인 그룹에 포함된 제2 비트 라인들에 연결된 제3 메모리 셀들을 프로그램하는 단계; 및

이어서, 제4 어드레스 및 제4 프로그램 커맨드에 응답하여, 상기 워드 라인, 상기 제2 스트링 선택 라인 및 상기 제2 비트 라인 그룹에 포함된 상기 제2 비트 라인들에 연결된 제4 메모리 셀들을 프로그램하는 단계를 포함하고,

상기 프로그램 방법은,

상기 제1 내지 제4 어드레스들에 대한 스트링 선택 라인 어드레스가 상기 제1 및 제2 비트 라인 그룹들에 대한 비트 라인 그룹 어드레스보다 하위 비트에 위치하도록, 상기 제1 내지 제4 어드레스들을 제1 내지 제4 수정 어드레스들로 각각 변환하는 단계를 더 포함하는 것을 특징으로 하는 방법. - 제1 내지 제4 스트링 선택 라인들, 기판 상에 수직으로 적층된 복수의 워드 라인들, 제1 내지 제4 비트 라인 그룹들을 포함하는 3D 비휘발성 메모리 장치의 프로그램 방법으로서,

제1 어드레스 및 제1 프로그램 커맨드에 응답하여, 상기 복수의 워드 라인들 중 제1 워드 라인, 상기 제1 스트링 선택 라인, 및 상기 제1 비트 라인 그룹에 포함된 제1 비트 라인들에 연결된 제1 메모리 셀들을 프로그램하는 단계;

제2 어드레스 및 제2 프로그램 커맨드에 응답하여, 상기 제1 워드 라인, 상기 제1 및 제3 스트링 선택 라인들 사이에 배치된 상기 제2 스트링 선택 라인, 및 상기 제1 비트 라인들에 연결된 제2 메모리 셀들을 프로그램하는 단계;

제3 어드레스 및 제3 프로그램 커맨드에 응답하여, 상기 제1 워드 라인, 상기 제2 및 제4 스트링 선택 라인들 사이에 배치된 상기 제3 스트링 선택 라인, 및 상기 제1 비트 라인들에 연결된 제3 메모리 셀들을 프로그램하는 단계;

제4 어드레스 및 제4 프로그램 커맨드에 응답하여, 상기 제1 워드 라인, 상기 제4 스트링 선택 라인, 및 상기 제1 비트 라인들에 연결된 제4 메모리 셀들을 프로그램하는 단계; 및

제5 어드레스 및 제5 프로그램 커맨드에 응답하여, 상기 제1 워드 라인, 상기 제1 스트링 선택 라인, 및 상기 제2 비트 라인 그룹에 포함된 제2 비트 라인들에 연결된 제5 메모리 셀들을 프로그램하는 단계를 포함하고,

상기 제1 내지 제4 스트링 선택 라인들은 제1 방향으로 연장되고, 제2 방향으로 서로 이격되며, 상기 제1 및 제2 비트 라인들은 상기 제2 방향으로 연장되며,

상기 프로그램 방법은,

상기 제1 내지 제5 어드레스들에 대한 스트링 선택 라인 어드레스가 상기 제1 내지 제4 비트 라인 그룹들에 대한 비트 라인 그룹 어드레스보다 하위 비트에 위치하도록, 상기 제1 내지 제5 어드레스들을 제1 내지 제5 수정 어드레스들로 각각 변환하는 단계를 더 포함하는 것을 특징으로 하는 방법. - 워드 라인을 공유하는 스트링 선택 라인들, 및 비트 라인 그룹들을 가지는 비휘발성 메모리 장치의 프로그램 방법으로서,

어드레스 및 프로그램 커맨드를 수신하는 단계;

상기 스트링 선택 라인들에 대한 스트링 선택 라인 어드레스가 상기 비트 라인 그룹들에 대한 비트 라인 그룹 어드레스보다 하위 비트에 위치하도록, 상기 어드레스를 수정 어드레스로 변환하는 단계; 및

상기 수정 어드레스에 따라, 상기 워드 라인, 상기 스트링 선택 라인들 중 하나, 상기 비트 라인 그룹들 중 하나에 연결된 메모리 셀들을 프로그램하는 단계를 포함하는 방법. - 제17항에 있어서,

상기 어드레스는, 논리 주소를 포함하고,

상기 수정 어드레스는, 워드 라인 어드레스, 상기 비트 라인 그룹 어드레스, 및 상기 스트링 선택 라인 어드레스를 포함하는 것을 특징으로 하는 방법. - 제17항에 있어서,

상기 비휘발성 메모리 장치는, 복수의 비트 라인들에 연결되는 수직 낸드 플래시 메모리이고,

상기 복수의 비트 라인들 중 K개의 비트 라인들은 하나의 페이지 버퍼에 연결되며, K는 비트 라인 그룹들의 개수에 대응하는 2 이상의 정수인 것을 특징으로 하는 방법. - 제17항에 있어서,

상기 비트 라인 그룹들의 개수는 4개이고, 4개의 비트 라인들은 하나의 페이지 버퍼를 공유하는 것을 특징으로 하는 방법.

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US15/793,221 US10325657B2 (en) | 2017-01-25 | 2017-10-25 | Non-volatile memory devices and methods of programming the same |

| CN201711120376.6A CN108346447B (zh) | 2017-01-25 | 2017-11-13 | 非易失性存储器件及其编程方法 |

| US16/441,145 US10490280B2 (en) | 2017-01-25 | 2019-06-14 | Non-volatile memory devices and methods of programming the same |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020170012048 | 2017-01-25 | ||

| KR20170012048 | 2017-01-25 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20180087809A KR20180087809A (ko) | 2018-08-02 |

| KR102400098B1 true KR102400098B1 (ko) | 2022-05-23 |

Family

ID=63251868

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020170051073A KR102400098B1 (ko) | 2017-01-25 | 2017-04-20 | 비휘발성 메모리 장치 및 상기 비휘발성 메모리 장치의 프로그램 방법 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US10490280B2 (ko) |

| KR (1) | KR102400098B1 (ko) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102407571B1 (ko) * | 2017-12-20 | 2022-06-13 | 에스케이하이닉스 주식회사 | 메모리 시스템 및 그것의 동작 방법 |

| CN112424656B (zh) | 2018-07-27 | 2023-09-05 | 株式会社Lg化学 | 用于制造视角补偿膜的方法、用于制造偏光板的方法、视角补偿膜、偏光板和包括其的显示装置 |

| JP2021022412A (ja) * | 2019-07-29 | 2021-02-18 | ウィンボンド エレクトロニクス コーポレーション | 半導体装置および連続読出し方法 |

| JP6876755B2 (ja) | 2019-07-29 | 2021-05-26 | ウィンボンド エレクトロニクス コーポレーション | 半導体装置および連続読出し方法 |

| US11487454B2 (en) * | 2019-12-05 | 2022-11-01 | Sandisk Technologies Llc | Systems and methods for defining memory sub-blocks |

| DE102021106752B4 (de) * | 2020-05-29 | 2023-10-26 | Taiwan Semiconductor Manufacturing Company, Ltd. | Speichervorichtung, integrierte schaltungsvorrichtung und verfahren |

| CN114220471A (zh) * | 2021-01-06 | 2022-03-22 | 长江存储科技有限责任公司 | 3d存储器件及其读取方法 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20130339603A1 (en) | 2011-12-23 | 2013-12-19 | Feng Zhu | Method, apparatus and system for determining access to a memory array |

Family Cites Families (28)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100729351B1 (ko) * | 2004-12-31 | 2007-06-15 | 삼성전자주식회사 | 낸드 플래시 메모리 장치 및 그것의 프로그램 방법 |

| JP4939804B2 (ja) * | 2005-12-21 | 2012-05-30 | 三星電子株式会社 | 不揮発性半導体記憶装置 |

| KR100896190B1 (ko) * | 2007-06-11 | 2009-05-12 | 삼성전자주식회사 | 불휘발성 메모리 장치의 소거 방법 |

| KR100909968B1 (ko) | 2007-06-12 | 2009-07-29 | 삼성전자주식회사 | 구동방식을 개선한 입체 구조의 플래시 메모리 장치 및 그구동방법 |

| US8488381B2 (en) | 2009-02-02 | 2013-07-16 | Samsung Electronics Co., Ltd. | Non-volatile memory device having vertical structure and method of operating the same |

| KR101635504B1 (ko) * | 2009-06-19 | 2016-07-04 | 삼성전자주식회사 | 3차원 수직 채널 구조를 갖는 불 휘발성 메모리 장치의 프로그램 방법 |

| KR101662821B1 (ko) * | 2010-06-16 | 2016-10-05 | 삼성전자주식회사 | 멀티-페이지 프로그램 방법, 그것을 이용한 불 휘발성 메모리 장치, 그리고 그것을 포함한 데이터 저장 시스템 |

| KR101807539B1 (ko) | 2010-08-20 | 2017-12-12 | 삼성전자주식회사 | 3차원 비휘발성 메모리 장치의 메모리 셀 어레이의 어드레스 스케쥴링 방법 |

| KR20120126436A (ko) | 2011-05-11 | 2012-11-21 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 및 반도체 메모리 장치의 프로그램 방법 |

| KR20120133594A (ko) | 2011-05-31 | 2012-12-11 | 에스케이하이닉스 주식회사 | 비휘발성 메모리 장치의 동작방법 |

| US9606730B2 (en) | 2012-05-04 | 2017-03-28 | Samsung Electronics Co., Ltd. | System and method including three dimensional nonvolatile memory device and random access memory |

| KR101996004B1 (ko) * | 2012-05-29 | 2019-07-03 | 삼성전자주식회사 | 비휘발성 메모리 장치의 프로그램 방법 및 그것의 메모리 시스템 |

| KR20140091298A (ko) * | 2013-01-11 | 2014-07-21 | 에스케이하이닉스 주식회사 | 행 디코더를 포함하는 반도체 메모리 장치 및 그것의 프로그램 방법 |

| US9613704B2 (en) | 2013-12-25 | 2017-04-04 | Aplus Flash Technology, Inc | 2D/3D NAND memory array with bit-line hierarchical structure for multi-page concurrent SLC/MLC program and program-verify |

| US9373409B2 (en) | 2014-07-08 | 2016-06-21 | Macronix International Co., Ltd. | Systems and methods for reduced program disturb for 3D NAND flash |

| KR102235492B1 (ko) | 2014-08-25 | 2021-04-05 | 삼성전자주식회사 | 불휘발성 메모리 장치 및 그것의 프로그램 검증 방법 |

| WO2016048846A1 (en) | 2014-09-28 | 2016-03-31 | Aplus Flash Technology, Inc | Self-timed slc nand pipeline and concurrent program without verification |

| KR102217243B1 (ko) * | 2014-10-28 | 2021-02-18 | 삼성전자주식회사 | 저항성 메모리 장치, 저항성 메모리 시스템 및 저항성 메모리 장치의 동작방법 |

| KR20160059745A (ko) * | 2014-11-19 | 2016-05-27 | 에스케이하이닉스 주식회사 | 반도체 장치 |

| KR102392821B1 (ko) | 2015-03-16 | 2022-05-02 | 삼성전자주식회사 | 스토리지 장치 및 스토리지 장치의 동작 방법 |

| KR20160135055A (ko) | 2015-05-15 | 2016-11-24 | 에스케이하이닉스 주식회사 | 더미 메모리 셀들을 포함하는 반도체 메모리 장치 및 그것의 동작 방법 |

| KR20170010620A (ko) * | 2015-07-20 | 2017-02-01 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 및 그것의 동작 방법 |

| US9852795B2 (en) | 2015-09-24 | 2017-12-26 | Samsung Electronics Co., Ltd. | Methods of operating nonvolatile memory devices, and memory systems including nonvolatile memory devices |

| KR102435026B1 (ko) | 2015-12-15 | 2022-08-22 | 삼성전자주식회사 | 저장 장치의 동작 방법 |

| KR102468995B1 (ko) | 2016-03-29 | 2022-11-22 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 및 이의 동작 방법 |

| KR102414186B1 (ko) | 2016-04-04 | 2022-06-28 | 삼성전자주식회사 | 불휘발성 메모리 장치 및 그것의 프로그램 방법 |

| KR102683413B1 (ko) * | 2017-02-02 | 2024-07-10 | 삼성전자주식회사 | 비휘발성 메모리 장치, 비휘발성 메모리 장치의 소프트 이레이즈 방법 및 프로그램 방법 |

| KR102289598B1 (ko) | 2017-06-26 | 2021-08-18 | 삼성전자주식회사 | 불휘발성 메모리 장치 및 그것을 포함하는 메모리 시스템 그리고 그것의 프로그램 방법 |

-

2017

- 2017-04-20 KR KR1020170051073A patent/KR102400098B1/ko active IP Right Grant

-

2019

- 2019-06-14 US US16/441,145 patent/US10490280B2/en active Active

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20130339603A1 (en) | 2011-12-23 | 2013-12-19 | Feng Zhu | Method, apparatus and system for determining access to a memory array |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20180087809A (ko) | 2018-08-02 |

| US20190295651A1 (en) | 2019-09-26 |

| US10490280B2 (en) | 2019-11-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102400098B1 (ko) | 비휘발성 메모리 장치 및 상기 비휘발성 메모리 장치의 프로그램 방법 | |

| KR102326558B1 (ko) | 낸드 스트링을 포함하는 메모리 장치 및 그 동작 방법 | |

| KR101913331B1 (ko) | 비휘발성 메모리 장치, 그것을 포함하는 비휘발성 메모리 시스템, 그것의 프로그램 방법, 그리고 그것을 제어하는 컨트롤러 동작 방법 | |

| KR101734204B1 (ko) | 프로그램 시퀀서를 포함하는 플래시 메모리 장치 및 시스템, 그리고 그것의 프로그램 방법 | |

| KR100819102B1 (ko) | 개선된 멀티 페이지 프로그램 동작을 갖는 불휘발성 반도체메모리 장치 | |

| KR102336659B1 (ko) | 데이터 신뢰성을 향상시키기 위한 메모리 동작을 수행하는 메모리 장치, 이를 포함하는 메모리 시스템 및 메모리 장치의 동작 방법 | |

| KR101792870B1 (ko) | 불휘발성 메모리 장치 및 그것의 읽기 방법 | |

| KR101868377B1 (ko) | 불휘발성 메모리 장치 및 그것의 프로그램 방법 | |

| KR102441580B1 (ko) | 프로그램 성능이 개선된 메모리 장치 및 이의 동작방법 | |

| CN109545260B (zh) | 非易失性存储器装置和对非易失性存储器装置编程的方法 | |

| KR101810640B1 (ko) | 불휘발성 메모리 장치 및 메모리 시스템 그리고 그것의 읽기 방법 | |

| TW201921347A (zh) | 記憶體裝置 | |

| CN110580929A (zh) | 非易失性存储器装置及非易失性存储器装置的擦除方法 | |

| CN108346447B (zh) | 非易失性存储器件及其编程方法 | |

| KR20140025164A (ko) | 불휘발성 메모리 장치 및 그것의 데이터 처리 방법 | |

| CN109493905B (zh) | 非易失性存储装置及其编程方法 | |

| CN106504791B (zh) | 存储装置、存储系统、操作存储装置以及存储系统的方法 | |

| WO2013075067A1 (en) | Low voltage page buffer for use in nonvolatile memory design | |

| KR101643518B1 (ko) | 메모리에서의 지지 회로 공유 | |

| KR101668340B1 (ko) | Nand형 플래시 메모리 및 그의 프로그래밍 방법 | |

| TW202113851A (zh) | 半導體記憶裝置 | |

| JPWO2006059375A1 (ja) | 半導体装置および半導体装置の制御方法 | |

| KR20220015245A (ko) | 프로그래밍 동안 양방향 채널 프리차지를 수행하는 비휘발성 메모리 장치 | |

| KR102434986B1 (ko) | 데이터 신뢰성이 개선된 메모리 장치 및 이의 동작방법 | |

| KR102317784B1 (ko) | 비휘발성 메모리 장치 및 상기 비휘발성 메모리 장치의 프로그래밍 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| E902 | Notification of reason for refusal | ||

| E902 | Notification of reason for refusal | ||

| E90F | Notification of reason for final refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant |