KR101919439B1 - Detection Method of Capacitance and Capacitance Detection Apparatus using the Same - Google Patents

Detection Method of Capacitance and Capacitance Detection Apparatus using the Same Download PDFInfo

- Publication number

- KR101919439B1 KR101919439B1 KR1020170023975A KR20170023975A KR101919439B1 KR 101919439 B1 KR101919439 B1 KR 101919439B1 KR 1020170023975 A KR1020170023975 A KR 1020170023975A KR 20170023975 A KR20170023975 A KR 20170023975A KR 101919439 B1 KR101919439 B1 KR 101919439B1

- Authority

- KR

- South Korea

- Prior art keywords

- signal

- detection

- detection signal

- capacitance

- detection circuit

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

- G06F3/041—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means

- G06F3/0416—Control or interface arrangements specially adapted for digitisers

- G06F3/04164—Connections between sensors and controllers, e.g. routing lines between electrodes and connection pads

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

- G06F3/041—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means

- G06F3/0416—Control or interface arrangements specially adapted for digitisers

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/24—Resetting means

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

- G06F3/041—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means

- G06F3/044—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means by capacitive means

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

- G06F3/041—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means

- G06F3/044—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means by capacitive means

- G06F3/0446—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means by capacitive means using a grid-like structure of electrodes in at least two directions, e.g. using row and column electrodes

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- General Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Human Computer Interaction (AREA)

- Computer Networks & Wireless Communication (AREA)

- Position Input By Displaying (AREA)

Abstract

본 실시예에 의한 커패시턴스 검출 장치는, 상승 에지(rising edge)와 하강 에지(falling edge)가 교번되는 구동 신호를 제공하는 신호원과, 구동 신호를 제공받고, 상승 에지에 의하여 형성되는 상승 에지 검출 신호와 하강 에지에 의하여 형성되는 하강 에지 검출 신호를 제공하는 커패시턴스 검출 패널 및 상승 에지 검출 신호를 제공받고 검출 신호를 제공하는 제1 검출 회로 및 하강 에지 검출 신호를 제공받고 반전 검출 신호를 출력하는 제2 검출 회로를 포함하는 검출 회로부를 포함하며, 검출 신호와 반전 검출 신호는 의사 차동(pseudo differential) 관계에 있다.The capacitance detection apparatus according to the present embodiment includes a signal source for providing a drive signal in which a rising edge and a falling edge alternate with each other and a rising edge detection signal A first detection circuit provided with a rising edge detection signal and providing a detection signal, and a second detection circuit provided with a falling edge detection signal and outputting an inverted detection signal. 2 detection circuit, wherein the detection signal and the inversion detection signal are in a pseudo differential relationship.

Description

본 실시예는 커패시턴스 검출 방법 및 이를 이용한 커패시턴스 검출 장치에 관한 것이다.The present embodiment relates to a capacitance detection method and a capacitance detection apparatus using the same.

커패시턴스 검출 장치에 사용되는 감지 방식들은 저항막 방식, 표면 초음파 방식및 정전 용량 방식이 주류를 이루고 있으며, 정전 용량 방식의 경우 다중 터치 감지가 가능하고 내구성, 시인성 등이 우수하기 때문에 휴대용 모바일 기기의 주 입력 수단으로 채택되고 있는 추세이다.Since the sensing methods used in the capacitance detecting device are mainly composed of the resistive film type, the surface ultrasonic type, and the capacitive type, the capacitive type is capable of multi-touch sensing and has excellent durability and visibility. And is adopted as an input means.

정전 용량 방식 커패시턴스 검출 장치는 사용자 간섭에 의해 터치 스크린 패널 상의 축전 센서 (capacitive sensor)들에 대전된 전하량이 변하는 것을 감지하여 사용자 입력을 인식하며, 전하 축전 방식에 따라 자기 정전 용량 방식(self-capacitive)과 상호 정전 용량 방식(mutual-capacitive)으로 나뉜다. 자기 정전 용량 방식이 하나의 축전 센서 (capacitive sensor) 당 하나의 도전체를 구성하여 터치 스크린 패널 외부의 기준 접지면 (reference ground)과 대전면을 형성하는 반면, 상호 정전 용량 방식은 터치 스크린 패널 상의 두 개의 도전체가 서로 대전면을 형성하여 하나의 축전 센서로 기능하도록 구성된다.The capacitance type capacitance detecting device recognizes a user input by sensing a change in the amount of electric charge charged on capacitive sensors on a touch screen panel by user interference, and recognizes a user input by a self-capacitive ) And mutual-capacitive type. The self-capacitance scheme forms one conductor per capacitive sensor to form a reference ground and a charge plane outside the touch screen panel, while the mutual capacitive scheme forms two reference electrodes on the touch screen panel Of the electric conductors form a charging surface to function as one charging sensor.

일반적인 자기 정전 용량 방식은 X/Y 직교 형태의 도전체 배치를 사용하며, 이 경우 각 축전 센서가 선센서 (line sensor)로 기능하기 때문에 매 터치 스크린 감지 시 X 센서군 (X-line sensor group)과 Y 센서군 (Y-line sensor group) 각각으로부터 하나씩의 X-감지 정보와 Y-감지 정보밖에 제공받지 못한다. 따라서 일반적인 자기 정전 용량 방식 터치 스크린에서는 단일 터치의 감지 및 추적은 가능하나 다중 터치는 지원할 수 없다. 상호 정전 용량 방식도 X/Y 직교 형태의 도전체 배치를 사용하나, 각 축전 센서가 도전체 직교 위치 마다 격자센서 (grid sensor) 형태로 구성되며 터치 스크린 상의 사용자 입력 탐지 시 모든 격자센서의 반응이 독립적으로 감지되는 점이 자기 정전 용량 방식과 다르다. 각 격자센서는 서로 다른 하나의 X/Y 좌표에 대응되고 서로 독립적인 반응 결과를 제공하기 때문에, 상호축전 방식 터치 스크린에서는 X/Y 격자센서 집합으로부터 제공받은 X/Y-감지 정보집합으로부터 사용자 입력 정보를 추출하여 사용자의 다중 터치를 감지하고 추적할 수 있다. In general, the self-capacitance type uses an X / Y orthogonal arrangement of conductors. In this case, each power sensor functions as a line sensor. Therefore, when sensing each touch screen, an X- Detection information and Y-sense information from only one Y-line sensor group and one Y-line sensor group, respectively. Therefore, a single self-capacitance touch screen can detect and track a single touch but can not support multiple touches. The reciprocal capacitance method uses the X / Y orthogonal arrangement of conductors, but each charging sensor is configured in the form of a grid sensor at each orthogonal position of the conductor. When the user input on the touch screen is detected, The point that is detected independently is different from the self-capacitance method. Each lattice sensor corresponds to a different X / Y coordinate and provides independent reaction results. Therefore, in the mutual storage type touch screen, the user inputs from the X / Y-sense information set provided from the X / Information can be extracted and the multi-touch of the user can be detected and tracked.

일반적인 상호 정전 용량 방식 터치스크린 패널의 도전체 구성과 감지 방식은 다음과 같다. 어느 한 방향으로 연장되는 도전체로 구성된 제1 전극들과 제1 전극들에 직교하는 방향으로 연장되는 도전체로 구성된 제2 전극들이 두 개의 전극 사이의 유전물질 (dielectric material)을 매개로 상호 정전 용량 센서(mutual-capacitive sensor)를 형성한다. 이 센서의 정전 용량 (capacitance) C는 두 전극 사이의 거리 (distance) d, 대전면의 면적 (area) a 및 대전면 사이에 존재하는 모든 유전물질의 등가 유전율 (dielectric)을 ε라고 할 때 C= ε*a/d로 정의되며, 이 센서에 축전된 전하량 (charge) Q 및 두 전극/대전면에 인가된 전위차 (voltage) V와 Q=CV의 관계를 가진다. 사용자가 센서에 접근하면 두 전극 사이에 형성된 전계 (electric field)에 대한 간섭이 발생하여 센서에 전하가 축전되는 것을 방해하게 되며, 센서에 축전되는 전하량이 줄어들어 결과적으로 정전 용량이 줄어든 것으로 나타나게 된다. 이것은 사용자 접근으로 인해 대전면 사이의 등가 유전율이 변하여 정전 용량이 변한 것으로도 이해할 수 있으나, 사용자 접근으로 인해 대전면 사이의 전계 일부가 차단 (shunt) 되므로써 전하 대전량/축전량이 감소 하게 되는 것이 실제적인 물리 현상이다. 제1 전극에 교류 전압원을 연결하여 센서의 한쪽 대전면에 교류 파형을 인가하면, 사용자의 접근 정도에 따라 가변되는 C에 대해 ΔQ=CΔV에 해당하는 대전량 변동(ΔQ) 이 발생하며, 이 변동량을 제2 전극에 연결된 리드-아웃 회로 (read-out 회로)가 전류 또는 전압으로 변환한다. 이렇게 변환된 정보는, 일반적으로 노이즈 필터링 (noise filtering), 복조(demodulation), 디지털변환(conversion), 누적 (accumulation) 등의 신호처리 단계를 거쳐 좌표 추적 알고리즘 및 제스쳐 인식 알고리즘에 사용된다. 이러한 커패시티브 터치 감응성 패널에 관한 선행 특허로는 미국 등록특허 제7,920,129호가 있다.The conductive configuration and sensing method of a common mutual capacitive touch screen panel are as follows. The first electrodes composed of a conductor extending in one direction and the second electrodes composed of a conductor extending in a direction perpendicular to the first electrodes are connected to each other through a dielectric material between the two electrodes, to form a mutual-capacitive sensor. The capacitance C of this sensor is the distance d between the two electrodes, the area a of the charge surface, and the equivalent dielectric constant of all the dielectric materials present between the charge surfaces, * a / d, and the relationship between the charge Q stored in the sensor and the voltage V and Q = CV applied to the two electrodes / the charge surface. When the user approaches the sensor, interference occurs in the electric field formed between the two electrodes, which prevents the charge from accumulating in the sensor. As a result, the amount of charge stored in the sensor is reduced, resulting in a decrease in capacitance. It can be understood that the capacitance changes due to the change of the equivalent dielectric constant between the charged surfaces due to the user's approach. However, since the electric charge between the charged surfaces is partially shunted due to the user access, the charge charge / Phenomenon. When an AC voltage source is connected to the first electrode and an AC waveform is applied to one of the charge surfaces of the sensor, a charge amount variation (ΔQ) corresponding to ΔQ = CΔV is generated for C that varies according to the access degree of the user, A read-out circuit (read-out circuit) connected to the second electrode converts the current or voltage. The converted information is generally used for a coordinate tracking algorithm and a gesture recognition algorithm through signal processing steps such as noise filtering, demodulation, digital conversion, and accumulation. A prior patent for such a capacitive touch sensitive panel is US Pat. No. 7,920,129.

커패시턴스 검출 장치의 소형화 박형화 추세에 따라 커패시턴스 검출 장치에 형성된 기생 커패시터의 커패시턴스 값과 기생 저항의 저항값도 따라서 증가한다. 커패시턴스 값과 저항값이 증가함에 따라 RC 지연(Delay) 시간도 증가하여 결국 커패시턴스 검출을 위한 구동 신호의 주파수도 영향을 받는다. The capacitance value of the parasitic capacitor formed in the capacitance detection device and the resistance value of the parasitic resistance increase in accordance with the downsizing trend of the capacitance detection device. As the capacitance value and the resistance value increase, the RC delay time also increases, so that the frequency of the driving signal for capacitance detection is also affected.

커패시턴스 검출 장치에는 높은 주파수의 노이즈 뿐만 아니라 낮은 주파수의 노이즈도 유입되는데, 구동 신호의 주파수가 낮아질수록 낮은 주파수의 노이즈에 의한 영향이 커져 결과적으로 신호 대 잡음비(SNR, Signal to Noise Ratio)가 감소한다. The capacitance detection apparatus not only receives noise of a high frequency but also noise of a low frequency. The lower the frequency of the driving signal is, the more the effect of the noise of the low frequency is increased and the signal to noise ratio (SNR) .

본 실시예는 상술한 과제를 해결하기 위한 것이다. 본 실시예에 의한 커패시턴스 검출 장치 및 검출 방법은, 커패시턴스 검출 장치 구동 신호의 주파수를 증가시켜 그에 따라 커패시턴스 검출 장치에 유입되는 저주파 대역의 노이즈에 의한 영향을 감소시키고, 커패시턴스 검출 장치의 신호 대 잡음비 성능을 향상시키는 것을 주된 목표 중 하나로 한다.The present embodiment is for solving the above-described problems. The capacitance detecting apparatus and the detecting method according to the present embodiment increase the frequency of the capacitance detecting apparatus driving signal to thereby reduce the influence of the noise in the low frequency band flowing into the capacitance detecting apparatus accordingly and improve the signal- Is one of the main goals.

본 실시예에 의한 커패시턴스 검출 장치는, 상승 에지(rising edge)와 하강 에지(falling edge)가 교번되는 구동 신호를 제공하는 신호원과, 구동 신호를 제공받고, 상승 에지에 의하여 형성되는 상승 에지 검출 신호와 하강 에지에 의하여 형성되는 하강 에지 검출 신호를 제공하는 커패시턴스 검출 패널 및 상승 에지 검출 신호를 제공받고 검출 신호를 제공하는 제1 검출 회로 및 하강 에지 검출 신호를 제공받고 반전 검출 신호를 출력하는 제2 검출 회로를 포함하는 검출 회로부를 포함하며, 검출 신호와 반전 검출 신호는 의사 차동(pseudo differential) 관계에 있다.The capacitance detection apparatus according to the present embodiment includes a signal source for providing a drive signal in which a rising edge and a falling edge alternate with each other and a rising edge detection signal A first detection circuit provided with a rising edge detection signal and providing a detection signal, and a second detection circuit provided with a falling edge detection signal and outputting an inverted detection signal. 2 detection circuit, wherein the detection signal and the inversion detection signal are in a pseudo differential relationship.

본 실시예에 의한 커패시턴스 검출 방법은 (a) 커패시턴스 검출 패널이 구동 신호의 상승 에지(rising edge)를 제공받아 상승 에지 검출 신호를 출력하는 단계와, (b) 검출 회로부가 상승 에지 검출 신호를 제공받아 검출 신호를 출력하는 단계와, (c) 커패시턴스 검출 패널이 구동 신호의 하강 에지(rising edge)를 제공받아 하강 에지 검출 신호를 출력하는 단계와, (d) 검출 회로부가 하강 에지 검출 신호를 제공받아 반전 검출 신호를 출력하는 단계를 포함하되, 검출 신호와 반전 검출 신호는 의사 차동(pseudo differential) 관계에 있다.The capacitance detection method according to the present embodiment includes the steps of: (a) a capacitance detection panel receiving a rising edge of a driving signal to output a rising edge detection signal; (b) a detection circuit section providing a rising edge detection signal (C) a capacitance detection panel receiving a falling edge of a driving signal to output a falling edge detection signal, and (d) a detection circuit section providing a falling edge detection signal And outputting an inversion detection signal, wherein the detection signal and the inversion detection signal are in a pseudo differential relationship.

본 실시예에 의하면 구동 신호의 주파수를 증가시킬 수 있어 낮은 주파수 노이즈의 영향을 감소시킬 수 있다는 장점이 제공되며, 그로부터 신호대잡음비 성능이 향상된다는 장점도 제공된다.According to the present embodiment, it is possible to increase the frequency of the drive signal, thereby reducing the influence of the low frequency noise. Thus, the signal-to-noise ratio performance is improved.

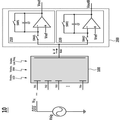

도 1은 본 실시예에 의한 커패시턴스 검출 장치의 개요를 도시한 블록도이다.

도 2는 본 실시예에 의한 커패시턴스 검출 방법의 개요를 도시한 순서도이다.

도 3(a)는 일 실시예에 의한 커패시턴스 검출 패널 구성의 개요를 도시한 도면이고, 도 3(b)는 해당 실시예의 구동 전극에 구동 신호를 제공한 것을 개요적으로 도시한 도면이다. 도 3(c)는 다른 실시예에 의한 커패시턴스 검출 패널(100) 구성의 개요를 도시한 도면이고, 도 3(d)는 해당 실시예의 구동 전극에 구동 신호를 제공한 것을 개요적으로 도시한 도면이다.

도 4는 데이터 정렬부와, 아날로그 디지털 변환기의 개요를 도시한 도면이다.

도 5는 도 1로 도시된 커패시턴스 검출 장치에서, 어느 한 감지 전극에서의 등가 회로를 도시한 도면이다.

도 6은 본 실시예에 의한 커패시턴스 검출 장치(10)의 타이밍 다이어그램이다.

도 7은 구동 신호와 커패시턴스 검출 신호의 개형을 도시한 도면이다.

도 8(a)와 도 8(b)는 구동 신호의 주파수에 따라 검출된 커패시턴스 검출 신호에서 저주파 노이즈가 개입된 양을 비교하기 위한 도면이다.1 is a block diagram showing an outline of a capacitance detecting apparatus according to the present embodiment.

2 is a flowchart showing an outline of a capacitance detection method according to the present embodiment.

Fig. 3 (a) is a diagram showing the outline of the capacitance detection panel configuration according to one embodiment, and Fig. 3 (b) is a diagram schematically showing a drive signal provided to the drive electrodes of the embodiment. Fig. 3 (c) is a diagram showing the outline of the configuration of the

4 is a diagram showing an outline of a data sorting unit and an analog-to-digital converter.

FIG. 5 is a diagram showing an equivalent circuit at one of the sensing electrodes in the capacitance detecting apparatus shown in FIG. 1. FIG.

6 is a timing diagram of the

Fig. 7 is a diagram showing the openings of the drive signal and the capacitance detection signal.

8 (a) and 8 (b) are diagrams for comparing the amount of low frequency noise introduced in the capacitance detection signal detected according to the frequency of the drive signal.

이하에서는 첨부된 도면들을 참조하여 본 실시예에 의한 커패시턴스 검출 장치(10) 및 커패시턴스 검출 방법을 설명한다. 도 1은 본 실시예에 의한 커패시턴스 검출 장치(10)의 개요를 도시한 블록도이다. 도 1을 참조하면, 본 실시예에 의한 커패시턴스 검출 장치(10)는 상승 에지(rising edge)와 하강 에지(falling edge)가 교번하는 구동 신호(VTX)를 제공하는 신호원(Vsig)과, 구동 신호(VTX)를 제공받고, 상승 에지에 의하여 형성되는 상승 에지 검출 신호와 하강 에지에 의하여 형성되는 하강 에지 검출 신호를 제공하는 커패시턴스 검출 패널(100) 및 상승 에지 검출 신호를 제공받고 검출 신호(Vout)를 제공하는 제1 검출 회로(210) 및 하강 에지 검출 신호를 제공받고 반전 검출 신호(VoutB)를 출력하는 제2 검출 회로(220)를 포함하는 검출 회로부(200)를 포함하며, 검출 신호(Vout)와 반전 검출 신호(VoutB)는 의사 차동(pseudo differential) 관계에 있다. Hereinafter, a

도 1에서, 커패시턴스 검출 장치(10)는 액정 디스플레이(LCD, Liquid Crystal Display) 위에 배치될 수 있으며, Vnoise,LCD는 액정 디스플레이에서 제공되는 노이즈를 표시한 것이다. Vnoise,ENV는 커패시턴스 검출 장치가 위치하는 주변 환경에서 제공되는 노이즈를 표시한 것이며, Vnoise,Low Freq는 커패시턴스 검출 장치에 전원을 제공하는 전원부 등으로부터 제공되는 저주파 노이즈를 표시한 것이다. 1, the

도 2는 본 실시예에 의한 커패시턴스 검출 방법의 개요를 도시한 순서도이다. 도 2를 참조하면, 본 실시예에 의한 커패시턴스 검출 방법은 (a) 커패시턴스 검출 패널이 구동 신호의 상승 에지(rising edge)를 제공받아 상승 에지 검출 신호를 출력하는 단계(S100)와, (b) 검출 회로부가 상승 에지 검출 신호를 제공받아 검출 신호를 출력하는 단계(S200)와, (c) 커패시턴스 검출 패널이 구동 신호의 하강 에지(rising edge)를 제공받아 하강 에지 검출 신호를 출력하는 단계(S300)와, (d) 검출 회로부가 하강 에지 검출 신호를 제공받아 반전 검출 신호를 출력하는 단계(S400)를 포함하되, 검출 신호와 반전 검출 신호는 의사 차동(pseudo differential) 관계에 있다.2 is a flowchart showing an outline of a capacitance detection method according to the present embodiment. 2, the capacitance detection method according to the present embodiment includes the steps of: (a) a capacitance detection panel receiving a rising edge of a driving signal and outputting a rising edge detection signal (S100); (b) (C) a step in which the capacitance detection panel receives a falling edge of the driving signal and outputs a falling edge detection signal (S300), wherein the rising edge detection signal is supplied to the capacitance detection panel (D) a step (S400) in which the detection circuit receives the falling edge detection signal and outputs an inversion detection signal, wherein the detection signal and the inversion detection signal are in a pseudo differential relationship.

신호원(Vsig)은 상승 에지와 하강 에지가 교번하는 구동 신호(VTX)를 커패시턴스 검출 패널(100)의 구동 전극(Tx1, Tx2, ..., Txn)에 제공한다. 신호원(Vsig)이 제공하는 구동 신호(VTX)는 일 예로, 사각 구형파(rectangular pulse)일 수 있다. 도시되지 않은 실시예로, 신호원(Vsig)이 제공하는 구동 신호는 램프 펄스열(ramp pulse train), 삼각 펄스열(triangular pulse train) 및 정현 펄스열(sinusoidal pulse train)중 하나일 수 있다. 이외에 도시되지 않은 여러 가지 형태의 신호열들이 사용될 수 있으며, 상기 신호들의 선형 중첩으로 이루어진 신호열들이 구동신호로 제공될 수 있다. 다만, 이하에서는 간결하고 명확한 설명을 위하여 구동 신호는 도 1에 도시된 개형을 가지는 사각 구형파(rectangular pulse)인 것으로 설명한다.The signal source Vsig provides the driving signal V TX having the rising edge and the falling edge alternately to the driving electrodes Tx1, Tx2, ..., Txn of the

도 3(a)는 일 실시예에 의한 커패시턴스 검출 패널(100) 구성의 개요를 도시한 도면이고, 도 3(b)는 해당 실시예의 구동 전극에 구동 신호를 제공한 것을 개요적으로 도시한 도면이다. 도 3(c)는 다른 실시예에 의한 커패시턴스 검출 패널(100) 구성의 개요를 도시한 도면이고, 도 3(d)는 해당 실시예의 구동 전극에 구동 신호를 제공한 것을 개요적으로 도시한 도면이다. 도 3(a)를 참조하면, 커패시턴스 검출 패널은 기판(Sub)의 일면에 배치된 복수의 구동 전극(driving electrode, Tx1, Tx2, ..., Txn)과, 기판(Sub)의 타면에 배치된 복수의 감지 전극(sensing electrode, Rx1, Rx2, ..., Rxn) 및 기판(Sub)을 포함한다. FIG. 3 (a) is a diagram showing the outline of the configuration of the

도 3(b)를 참조하면, 기판의 일면에 형성된 각각의 구동 전극(Tx1, Tx2, ..., Txn)은 감지 전극(Rx1, Rx2, ..., Rxn)과 교차점에서 커패시터를 형성하며, 이를 상호 커패시턴스(Cm, mutual capacitance)라고 한다. 즉, 구동 전극이 커패시터의 일 전극이 되고, 감지 전극이 커패시터의 타 전극이 된다. 구동 전극에 구동신호가 제공되어 구동 전극과 감지 전극 사이에는 전기장(E)이 형성되며, 전기장이 형성되는 공간이 커패시턴스의 유전체(dielectric material)에 해당한다. 도 3(b)는 Tx2에 구동신호가 제공되어 Tx2와 교차하는 감지전극(Rx1, Rx2, ..., Rxn)들 사이에서 전기장이 형성되고, 상호 커패시터(CM)를 형성하는 것을 개요적으로 도시하였다. Referring to FIG. 3B, each of the driving electrodes Tx1, Tx2, ..., Txn formed on one surface of the substrate forms a capacitor at an intersection with the sensing electrodes Rx1, Rx2, ..., Rxn , And this is called mutual capacitance (Cm). That is, the driving electrode becomes one electrode of the capacitor, and the sensing electrode becomes the other electrode of the capacitor. A driving signal is provided to the driving electrode so that an electric field E is formed between the driving electrode and the sensing electrode and a space where the electric field is formed corresponds to a dielectric material of the capacitance. 3 (b) is a schematic diagram illustrating that an electric field is formed between the sensing electrodes Rx1, Rx2, ..., Rxn provided with a driving signal to Tx2 and crossing Tx2 to form a mutual capacitor CM . Respectively.

도 3(c)는 구동 전극들(Tx1, Tx2, ..., Txn)과 감지 전극들(Rx1, Rx2, ..., Rxn)이 기판(Sub)의 동일한 면에 위치한 패널의 실시예를 개요적으로 도시한다. 각각의 구동 전극은 다이아몬드 형태의 패턴과 각각의 다이아몬드 패턴을 연결하는 연결선을 포함하여 이루어지며, 각각의 감지 전극은 다이아몬드 형태의 패턴과 각각의 다이아몬드 패턴을 연결하는 연결선을 포함하여 이루어진다. 구동 전극의 다이아몬드 패턴과 감지 전극의 다이아몬트 패턴은 서로 접촉하지 않으며, 구동 전극과 감지 전극의 연결선은 서로 전기적으로 단락(short)회로를 형성하지 않도록 연결선과 연결선 사이에 절연물질이 개재된다.3 (c) shows an embodiment of the panel in which the driving electrodes Tx1, Tx2, ..., Txn and the sensing electrodes Rx1, Rx2, ..., Rxn are located on the same side of the substrate Sub Outline. Each of the driving electrodes includes a diamond-shaped pattern and a connecting line connecting the diamond patterns. Each of the sensing electrodes includes a diamond-shaped pattern and a connecting line connecting the respective diamond patterns. The diamond pattern of the driving electrode and the diamond pattern of the sensing electrode are not in contact with each other and an insulating material is interposed between the connecting line and the connecting line so that the connecting line of the driving electrode and the sensing electrode do not electrically form a short circuit.

도 3(c)의 패널을 B-B' 절단선을 따라 절단한 단면도인 도 3(d)를 참조하면, 구동 전극 Txn에 구동신호가 인가되면 구동 전극의 각 다이아몬드는 인접한 감지 전극의 다이아몬드와 전기장을 형성하는 바, 그에 따라 상호 커패시턴스(CM)를 형성한다. 도 2(d)에는 Txn이 감지 전극 Rx1 및 Rx2과 상호 커패시턴스를 형성하는 것을 도시하였다.Referring to FIG. 3 (d), which is a cross-sectional view taken along line BB 'of FIG. 3 (c), when a driving signal is applied to the driving electrode Txn, each diamond of the driving electrode generates an electric field Thereby forming mutual capacitance C M. 2 (d) shows that Txn forms a mutual capacitance with the sensing electrodes Rx1 and Rx2.

다시 도 1을 참조하면, 검출 회로부(200)는 구동 신호(VTX)의 상승 에지가 커패시턴스 검출 패널(100)에 제공되어 형성되는 전류 신호인 상승 에지 검출 신호(ir)를 감지 전극(Rxk)으로부터 제공받고, 검출 신호(Vout)를 출력하는 제1 검출 회로(210)와 구동 신호(VTX)의 하강 에지가 커패시턴스 검출 패널(100)에 제공되어 형성되는 전류 신호인 하강 에지 검출 신호(if)를 감지 전극(Rxk)으로부터 제공받고, 반전 검출 신호(VoutB)를 출력하는 제2 검출 회로(220)를 포함한다.1, the

일 실시예로, 제1 검출 회로(210) 및 제2 검출 회로(220)는 각각 차지 앰프(charge amplifier)를 포함할 수 있다. 차지 앰프는 반전 입력(inverting input), 비반전 입력(non-inverting input) 및 출력을 가지는 연산 증폭기(OP-AMP)와, 반전 입력과 출력에 전기적으로 연결되어 전류 신호를 제공받고 이를 누적하여 전압 신호를 형성하는 커패시터(Cf)를 포한한다. 일 실시예로, 차지 앰프는 커패시터(Cf)와 병렬로 연결되어 커패시터에 충전된 전하를 방전하는 방전 스위치(SWf)를 더 포함할 수 있다. 또한, 제1 검출 회로(210) 및 제2 검출 회로(220)는 각 검출 회로와 커패시턴스 검출 패널(100)를 연결하거나 차단하는 연결 스위치(SWd)를 포함한다. In one embodiment, the

제1 검출 회로(210)에 포함된 커패시터는 Cf1, 방전 스위치는 SWf1, 연결 스위치는 SWd1이라고 부호를 붙이고, 제2 검출 회로(220)에 포함된 커패시터는 Cf2, 방전 스위치는 SWf2, 연결 스위치는 SWd2라고 부호를 붙인다. The capacitor included in the

전류 신호인 상승 에지 검출 신호(ir) 및 하강 에지 검출 신호(if)는 각각 연결 스위치 SWd1, SWd2를 통하여 제1 검출 회로(210), 제2 검출 회로(220)에 포함된 차지 앰프의 반전 입력으로 제공된다. 각 차지 앰프의 비반전 입력으로는 기준 전압(Vref)이 제공된다. The rising edge detection signal ir and the falling edge detection signal if of the current signals are input to the

도 4는 데이터 정렬부(300)와, 아날로그 디지털 변환기(ADC,400)의 개요를 도시한 도면이다. 도 4를 참조하면, 커패시턴스 검출 장치(10)는 검출 회로부(200)가 출력한 신호를 정렬하여 출력하는 데이터 정렬부(data alignment unit, 300)와, 데이터 정렬부(300)가 정렬하여 출력한 신호를 디지털 신호로 변환하는 아날로그 디지털 변환기(ADC)를 더 포함한다. 도 4(a) 및 도 4(b)로 도시된 실시예에서, 데이터 정렬부(300)는 검출 회로부(200)가 출력한 신호를 제공받고, 이들을 시간적으로 정렬하여 아날로그 디지털 변환기(ADC, 400)에 제공한다.4 is a diagram showing an outline of a

도 4(a)로 도시된 실시예에서, 데이터 정렬부(300)는 제1 검출 회로(210)가 출력한 검출 신호(Vout) 및 제2 검출 회로(220)가 출력한 반전 검출 신호(VoutB) 중 어느 하나를 제공받고, 다른 하나의 출력시까지 유지하여 출력하는 샘플 앤드 홀드부(Sample and Hold Unit, 310)를 포함한다. 4A, the

일 실시예로, 샘플 앤드 홀드부(310)는 한 번의 샘플(sample) 과정을 수행하고, 샘플된 값을 유지하는 홀드(hold) 동작을 수행하며, 샘플(sample)후 샘플된 데이터를 홀드 하는 동안 아날로그-디지털 변환기 (ADC, 400)에 데이터를 전달한다. 일 예로, 샘플 앤드 홀드부(310)는 ADC(400)에 데이터를 전달한 후 리셋 신호를 제공하여 ADC에 포함된 커패시터를 초기화할 수 있다.In one embodiment, the sample and hold

도 4(b)로 도시된 실시예에서, 데이터 정렬부(300)는 제1 검출 회로(210)가 출력한 검출 신호(Vout) 및 제2 검출 회로(220)가 출력한 반전 검출 신호(VoutB)를 제공받고, 이를 적분하여 출력하는 적분기(Int. 320)를 포함한다. 4B, the

일 실시예로, 적분기(320)는 복수회의 샘플(sample)과 복수회의 누적 동작을 수행할 수 있다. 적분기(320)는 복수회의 샘플 및 누적 동작을 수행하여 아날로그-디지털 변환기(ADC,400)에 형성된 데이터를 전달한다. 일 예로, 적분기(320)는 데이터를 ADC(400)에 전달 후, 적분기에 포함된 피드백 커패시터의 리셋 신호를 제공하여 초기화할 수 있다.In one embodiment, the

아날로그 디지털 변환기(ADC, 400)는 데이터 정렬부(300)가 출력한 신호를 제공받고, 이를 디지털 신호로 변환한다. 변환된 디지털 신호는 내부 회로 또는 외부 회로에서 처리되며, 이를 이용하여 커패시턴스 검출 패널(100)을 터치 하는 오브젝트의 좌표, 움직임, 호버링하는 오브젝트의 유무, 좌표 등을 검출할 수 있다. The analog-to-digital converter (ADC) 400 receives the signal output from the

이하에서는 본 실시예에 의한 커패시턴스 검출 장치(10)의 동작예를 설명한다. 도 5는 도 1로 도시된 커패시턴스 검출 장치에서, 어느 한 감지 전극 에서의 등가 회로를 도시한 도면이고, 도 6은 본 실시예에 의한 커패시턴스 검출 장치(10)의 타이밍 다이어그램이다. Hereinafter, an operation example of the

도 6에서, Pf1은 제1 검출 회로(210)의 차지 앰프 앰프에 포함된 방전 스위치(SWf1)의 제어 전극에 제공되는 신호이고, Pd1은 커패시턴스 검출 패널(100)과 제1 검출 회로(210)의 차지 앰프를 연결하는 연결 스위치(SWd1)의 제어 전극에 제공되는 신호이다. Pf2는 제2 검출 회로(220)의 차지 앰프 앰프에 포함된 방전 스위치(SWf2)의 제어 전극에 제공되는 신호이고, Pd2는 커패시턴스 검출 패널(100)과 제2 검출 회로(220)의 차지 앰프를 연결하는 연결 스위치(SWd2)의 제어 전극에 제공되는 신호이다. 6, Pf1 is a signal provided to the control electrode of the discharge switch SWf1 included in the charge amplifier amplifier of the

설명되는 실시예에서, 방전 스위치(SWf1)과 방전 스위치(SWf2), 연결 스위치(SWd1)과 연결 스위치(SWd2)는 양의 전압을 제공받아 도통되는 NMOS(N-type Metal Oxide Semiconductor) 스위치를 예시하여 설명된다. 다만 이는 단순히 용이한 이해를 위한 것이며, 본 발명의 범위를 제한하고자 하는 것이 아니다. 따라서, 방전 스위치(SWf1)과 방전 스위치(SWf2), 연결 스위치(SWd1)과 연결 스위치(SWd2)는 양극성 접합 트랜지스터(BJT, Bipolar Junction Transistor) 또는 PMOS 스위치를 이용하여 구현할 수 있음은 물론이다.In the illustrated embodiment, the discharge switch SWf1 and the discharge switch SWf2, the connection switch SWd1 and the connection switch SWd2 illustrate an NMOS (N-type Metal Oxide Semiconductor) switch that is made conductive by receiving a positive voltage . However, this is merely for easy understanding, and is not intended to limit the scope of the present invention. Therefore, it goes without saying that the discharge switch SWf1 and the discharge switch SWf2, the connection switch SWd1 and the connection switch SWd2 may be implemented using a bipolar junction transistor (BJT) or a PMOS switch.

Vout은 제1 검출 회로(210)가 출력하는 검출 신호(Vout)의 개형을 개요적으로 도시하며, VoutB는 각각 제2 검출 회로(220)가 출력하는 검출 신호(VoutB)의 개형을 개요적으로 도시한다. Vout schematically shows the opening of the detection signal Vout outputted from the

도 1, 도 5 및 도 6을 참조하면, 구동 신호(VTX)의 상승 에지 이전에 리셋 과정(R)을 수행한다. 리셋 과정(R)은 방전 스위치(SWf1)와 연결 스위치(SWd1)이 동시에 도통되어 수행된다.Referring to FIGS. 1, 5, and 6, a reset process R is performed before the rising edge of the driving signal V TX . The reset process R is performed by making the discharging switch SWf1 and the connecting switch SWd1 conductive at the same time.

일 실시예에서, 방전 스위치(SWf1) 및 연결 스위치(SWd1)이 동시에 도통되어 리셋 과정(R)이 수행됨에 따라 커패시터(Cf)에 충전된 전하가 방전된다. 따라서, 커패시터 Cf 양단의 전압을 초기화할 수 있다. 연결 스위치(SWd1)이 도통됨에 따라 커패시턴스 검출 패널(100)의 기생 커패시턴스 Cp,RX가 기준 전압(Vref)로 충전된다. 따라서, 검출 회로(210)에서 보이는 기생 커패시턴스 CpRX의 영향을 감소시킬 수 있다. In one embodiment, as the discharging switch SWf1 and the connecting switch SWd1 are simultaneously energized to perform the reset process R, the charges charged in the capacitor Cf are discharged. Therefore, the voltage across the capacitor Cf can be initialized. As the connection switch SWd1 is turned on, the parasitic capacitances Cp and RX of the

리셋 과정(R)이 수행된 후, 커패시턴스 검출 패널(100)은 구동 신호(VTX)의 상승 에지에 의하여 형성된 상승 에지 검출 신호(ir)을 출력한다(S100). 상승 에지 검출 신호(ir)는 도통된 연결 스위치(SWd1)을 통하여 제1 검출 회로(210)에 제공된다.After the reset process R is performed, the

상술한 바와 같이 커패시턴스 검출 패널(100)의 구동 전극은 감지 전극과 커패시터(CM)를 형성한다. 커패시터의 일 전극인 구동 전극(Tx)에 구동 신호(VTX)가 제공되면 커패시터의 다른 전극인 감지 전극(Rx)에는 오브젝트의 접근 여부에 따라 변화하는 상승 에지 검출 신호(ir)와 하강 에지 검출 신호(if)가 형성된다. 상승 에지 검출 신호(ir)와 하강 에지 검출 신호(if)는 아래의 수학식 1로 표현될 수 있다.As described above, the driving electrode of the

(CM: 상호 커패시터의 커패시턴스, V: 구동 신호의 진폭)(C M : capacitance of mutual capacitor, V: amplitude of driving signal)

구동 신호의 형태에 따라 전기적 신호(i)의 형태가 다를 수 있다. 일 예로, 구동 신호가 도 7(a)로 도시된 것과 같이 사각 구형파인 경우에, 구동 신호의 상승 에지가 커패시턴스 검출 패널(100)에 제공되어 형성되는 상승 에지 검출 신호(ir) 는 이상적으로 도 7(b)에 도시된 것과 같이 구형파 상승 에지(rising edge) 에서의 미분에 의하여 값을 가지는 델타 함수(Dirac Delta Function)의 형태를 가진다. 마찬가지로, 구동 신호의 하강 에지가 커패시턴스 검출 패널(100)에 제공되어 형성되는 하강 에지 검출 신호(if)는 이상적으로 구형파 하강 에지(falling edge)에서의 미분에 의하여 값을 가지는 델타 함수의 형태를 가진다. The form of the electric signal i may be different depending on the type of the driving signal. 7 (a), the rising edge detection signal ir formed by providing the rising edge of the driving signal to the

그러나, 실제의 커패시턴스 검출 패널(100)은 기생 저항, 기생 커패시턴스 등의 비이상적 특성을 가진다. 이러한 비이상적 특성의 영향으로 상승 에지 검출 신호(ir) 및 하강 에지 검출 신호(if)는 도 7(c)에 도시된 상승 스파이크(spike) 및 하강 스파이크를 가지는 개형을 가진다. However, the actual

일 실시예로, 오브젝트가 커패시턴스 검출 패널(100)에 접근하면 커패시턴스 검출 패널(100)의 구동 전극(Tx)과 감지 전극(Rx) 사이에서 형성된 전기장을 오브젝트가 션트(shunt)하여 감소시킨다. 이것은 유전체가 변화하여 커패시터 내의 전기장 플럭스가 감소하는 것과 동일한 영향을 가져오므로, 커패시턴스 CM 값이 감소하는 것과 유사한 결과를 가져온다. 수학식 1에서 알 수 있는 바와 같이 커패시턴스 값이 감소함에 따라 전기적 신호의 크기는 감소하며, 이는 도 7(c)에서 로 도시된 영역과 같다. The object is shunted by reducing the electric field formed between the driving electrode Tx and the sensing electrode Rx of the

도 7(c)에서 로 표시된 구간은 오브젝트가 커패시턴스 검출 패널에 접근하지 않거나, 충분히 접근하지 않은 구간이며, 로 표시된 구간은 오브젝트가 구동 전극이 제공하는 전기장을 션트할 정도로 충분히 커패시턴스 검출 패널에 접근한 구간이다. 따라서 오브젝트(O)가 커패시턴스 검출 패널(100)에 충분히 접근한 경우에 패널이 구동 신호(VTX)에 상응하여 출력하는 신호를 이용하여 오브젝트에 의한 커패시턴스 변화를 검출할 수 있다.The section indicated by (c) in FIG. 7 is a section in which the object does not approach the capacitance detection panel or is not sufficiently approached, and the section indicated by () indicates that the object approaches the capacitance detection panel sufficiently to shunt the electric field provided by the driving electrode Section. Therefore, when the object O sufficiently approaches the

상승 에지 검출 신호(ir)는 연결 스위치(SWd1)을 거쳐 제1 검출회로(210)에 제공된다. 제1 검출 회로(210)는 연결 스위치가 도통된 시간(B)동안 전류 신호인 상승 에지 검출 신호(ir)를 누적하여 전압 신호로 형성한다. 연결 스위치(SWd1)가 도통되지 않고 차단됨에 따라 전압 신호는 리셋 과정이 수행되기 전까지(S) 유지되며, 이는 도 6에서 Vout의 굵은 실선으로 도시된 바와 같다. 이어서, 제1 검출 회로(210)는 형성된 전압 신호인 검출 신호(Vout)를 출력한다(S200). The rising edge detection signal ir is provided to the

구동 신호(VTX)의 하강 에지 이전에 리셋 과정(R)을 수행한다. 리셋 과정(R)은 방전 스위치(SWf2)와 연결 스위치(SWd2)가 동시에 도통되어 수행된다. 리셋 과정에서, 커패시터(Cf)에 충전된 전하가 방전되어 커패시터 Cf 양단의 전압을 초기화할 수 있다. 연결 스위치(SWd2)이 도통됨에 따라 커패시턴스 검출 패널(100)의 기생 커패시턴스 Cp,RX가 기준 전위 Vref로 충전되며, 검출 회로(220)에서 보이는 기생 커패시턴스 CpRX의 영향을 감소시킬 수 있다.The reset process R is performed before the falling edge of the driving signal V TX . The reset process R is performed by making the discharging switch SWf2 and the connecting switch SWd2 conductive at the same time. In the reset process, the charge charged in the capacitor Cf is discharged, and the voltage across the capacitor Cf can be initialized. As the connection switch SWd2 is turned on, the parasitic capacitances Cp and RX of the

연결 스위치(SWd2)가 도통된 후, 커패시턴스 검출 패널(100)은 구동 신호(VTX)의 하강 에지에 의하여 형성된 하강 에지 검출 신호(if)을 출력한다(S300). 전류 신호인 하강 에지 검출 신호(if)는 연결 스위치(SWd2)을 거쳐 제2 검출회로(220)에 제공된다. 제2 검출 회로(220)는 연결 스위치(SWd2)가 도통된 시간(B)동안 전류 신호인 하강 에지 검출 신호(if)를 누적하여 전압 신호로 형성한다. 연결 스위치(SWd2)가 차단됨에 따라 전압 신호는 리셋 과정이 수행되기 전까지(S) 유지된다. 이어서, 제2 검출 회로(220)는 형성된 전압인 반전 검출 신호(VoutB)을 출력한다(도 6 굵은 실선 참조, S400). After the connection switch SWd2 is turned on, the

검출 신호(Vout)와 반전 검출 신호(VoutB)는 도 6에서 도시된 바와 같이 상보성을 가지는 신호이다. 그러나, 신호가 동시에 형성되는 것이 아닌 의사 차동(pseudo differential) 관계인 신호이다. The detection signal Vout and the inversion detection signal VoutB are complementary signals as shown in Fig. However, the signals are not pseudo-differential signals at the same time.

데이터 정렬부(300)는 검출 신호(Vout)와 반전 검출 신호(VoutB)를 제공받고 시간적으로 정렬하여 아날로그 디지털 변환기(400)에 제공한다. 아날로그 디지털 변환기(400)는 의사 차동 신호쌍인 검출 신호(Vout)와 반전 검출 신호(VoutB)를 디지털 신호로 변환하여 출력한다.The

하나의 검출 회로를 이용하여 구동 신호(VTX)의 한주기에 포함된 상승 에지와 하강 에지에 대한 검출을 수행할 수 있다. 이러한 경우에는 구동 신호의 한 주기 동안 리셋 과정, 에지 검출 신호를 제공받는 과정, 이를 전압 신호로 형성하는 과정 및 해당 값에 대한 샘플링(sampling)이 수행하도록 일정 시간 유지(hold)하는 과정이 두 번 수행되어야 한다. 따라서, 구동 신호의 주파수를 상승시키는 것에 한계가 있다.One detection circuit can be used to detect the rising edge and the falling edge included in one period of the driving signal V TX . In this case, the process of resetting the drive signal for one period, receiving the edge detection signal, forming the voltage signal as a voltage signal, and holding a predetermined time for sampling the corresponding value are performed twice Should be performed. Therefore, there is a limit to raising the frequency of the drive signal.

그러나, 본 실시예에 의하면 에지 도래 이전에 미리 리셋을 수행한 후, 어느 하나의 에지 도래 후 다음 에지 도래까지 에지 검출 신호를 제공받고 이에 대한 전압 형성 및 홀드하는 과정을 수행할 수 있다. 따라서, 두 번의 리셋을 수행하는 과정이 구동 신호의 한 주기에 포함될 필요가 없으므로 하나의 검출 회로를 이용하는 실시예에 비하여 구동 신호의 주파수를 증가시킬 수 있다는 장점이 제공된다. However, according to the present embodiment, after resetting is performed before the arrival of an edge, an edge detection signal is provided until the arrival of any one of the edges and the arrival of the next edge, and a process of forming and holding a voltage therefor can be performed. Therefore, since the process of performing the two reset does not need to be included in one period of the driving signal, the frequency of the driving signal can be increased compared with the embodiment using one detecting circuit.

도 8(a)와 도 8(b)는 구동 신호의 주파수에 따라 검출된 커패시턴스 검출 신호에서 저주파 노이즈가 개입된 양을 비교하기 위한 도면이다. 검정색 실선은 저주파 노이즈를 도시한다. 도 8(a)를 참조하면, 한 주기(1T) 동안 두 번의 샘플을 수행한다. 일 예로, 두 번의 샘플이 각각 구동 신호의 상승 에지에 의하여 형성된 신호와 하강 에지에 의하여 형성된 신호에 대한 샘플이라고 하면, 두 번의 샘플에 의하여 얻어진 의사 차동 신호에는 Vnoise1만큼의 노이즈 성분이 개입되어 있다. 8 (a) and 8 (b) are diagrams for comparing the amount of low frequency noise introduced in the capacitance detection signal detected according to the frequency of the drive signal. The solid black line shows the low frequency noise. Referring to FIG. 8 (a), two samples are performed during one period (1T). For example, if two samples are a sample of a signal formed by a rising edge of a driving signal and a signal formed by a falling edge, noise components as much as

도 8(b)는 도 8(a)에 비하여 높은 주파수로 샘플을 수행하는 경우를 예시한다. 도 8(b)를 참조하면, 위에서 설명된 바와 같이 구동 신호의 주파수를 높일 수 있으며, 그에 따라 샘플을 수행하는 시간 차이를 감소시킬 수 있다. 마찬가지로, 두 번의 샘플이 각각 구동 신호의 상승 에지에 의하여 형성된 신호와 하강 에지에 의하여 형성된 신호에 대한 샘플이라고 하면, 두 번의 샘플에 의하여 얻어진 의사 차동 신호에 개입된 노이즈 성분은 Vnoise2으로, 구동 신호의 주파수가 낮은 경우에 비하여 저주파 노이즈 개입이 감소된 것을 확인할 수 있다.FIG. 8B illustrates a case where samples are performed at a higher frequency than in FIG. 8A. Referring to FIG. 8 (b), it is possible to increase the frequency of the driving signal as described above, thereby reducing the time difference for performing the sample. Similarly, if two samples are respectively a sample formed by the rising edge of the driving signal and a sample formed by the falling edge, the noise component introduced into the pseudo differential signal obtained by the two samples is Vnoise2, It can be confirmed that the low frequency noise intervention is reduced as compared with the case where the frequency is low.

본 실시예에 의하면 제1 검출 회로와 제2 검출 회로가 상승 에지 검출 신호와 하강 에지 검출 신호를 상응하는 전압 신호로 변환하므로, 구동 신호의 주파수를 증가시킬 수 있으며, 그에 따라 낮은 주파수 노이즈의 개입을 방지할 수 있다는 장점과, 신호대 잡음비 특성을 향상시킬 수 있다는 장점이 제공된다.According to the present embodiment, since the first detection circuit and the second detection circuit convert the rising edge detection signal and the falling edge detection signal into corresponding voltage signals, it is possible to increase the frequency of the driving signal, And it is possible to improve the signal-to-noise ratio characteristic.

본 발명에 대한 이해를 돕기 위하여 도면에 도시된 실시 예를 참고로 설명되었으나, 이는 실시를 위한 실시예로, 예시적인 것에 불과하며, 당해 분야에서 통상적 지식을 가진 자라면 이로부터 다양한 변형 및 균등한 타 실시 예가 가능하다는 점을 이해할 것이다. 따라서, 본 발명의 진정한 기술적 보호범위는 첨부된 특허청구범위에 의해 정해져야 할 것이다.While the present invention has been particularly shown and described with reference to exemplary embodiments thereof, it is clearly understood that the same is by way of illustration and example only and is not to be taken by way of illustration, It will be appreciated that other embodiments are possible. Accordingly, the true scope of the present invention should be determined by the appended claims.

100: 커패시턴스 검출 패널 200: 검출 회로부

210: 제1 검출 회로 220: 제2 검출 회로

300: 데이터 정렬부 310: 샘플 앤드 홀드부

320: 적분기 400: 아날로그 디지털 변환기100: capacitance detection panel 200: detection circuit part

210: first detection circuit 220: second detection circuit

300: data sorting unit 310: sample and hold unit

320: integrator 400: analog-to-digital converter

Claims (11)

상기 상승 에지 검출 신호를 제공받고 검출 신호를 제공하는 제1 검출 회로 및 상기 하강 에지 검출 신호를 제공받고 반전 검출 신호를 출력하는 제2 검출 회로를 포함하는 검출 회로부 및

상기 검출 회로부가 출력한 신호를 동시에 출력하는 데이터 정렬부(data alignment unit)를 포함하며,

상기 데이터 정렬부는,

상기 검출 신호와 상기 반전 검출 신호중 어느 하나를 샘플(sample)하여 다른 신호의 출력시까지 유지(hold)하는 샘플앤드홀드 부(sample and hold unit)를 포함하고,

상기 검출 신호와 상기 반전 검출 신호는 함께 출력되는 의사 차동(pseudo differential) 관계에 있는 커패시턴스 검출 장치.A capacitance detection panel provided with a drive signal and providing a falling edge detection signal formed by a rising edge detection signal and a falling edge formed by a rising edge;

A detection circuit portion including a first detection circuit receiving the rising edge detection signal and providing a detection signal and a second detection circuit receiving the falling edge detection signal and outputting an inverted detection signal;

And a data alignment unit for simultaneously outputting signals output from the detection circuit unit,

Wherein the data sorting unit comprises:

And a sample and hold unit that samples one of the detection signal and the inversion detection signal and holds the same until outputting the other signal,

Wherein the detection signal and the inverted detection signal are output in a pseudo differential relationship.

상기 제1 검출 회로는 상기 상승 에지 검출 신호를 제공받고 누적하여 상기 검출 신호를 형성하는 커패시턴스 검출 장치.The method according to claim 1,

Wherein the first detection circuit receives the rising edge detection signal and cumulatively forms the detection signal.

상기 검출 회로부는,

상기 제1 검출 회로는 상기 커패시턴스 검출 패널과 상기 제1 검출 회로를 전기적으로 연결하는 제1 스위치를 더 포함하며,

상기 제1 스위치가 도통된 구간동안 상기 상승 에지 검출 신호를 제공받고 누적하는 커패시턴스 검출 장치.3. The method of claim 2,

The detection circuit section,

The first detection circuit further includes a first switch electrically connecting the capacitance detection panel and the first detection circuit,

And the rising edge detection signal is provided and accumulated during a period in which the first switch is conductive.

상기 제2 검출 회로는 상기 하강 에지 검출 신호를 제공받고 이를 누적하여 상기 반전 검출 신호를 형성하는 커패시턴스 검출 장치.The method according to claim 1,

And the second detection circuit receives the falling edge detection signal and accumulates the falling edge detection signal to form the inverted detection signal.

상기 검출 회로부는,

상기 제2 검출 회로는 상기 커패시턴스 검출 패널과 상기 제2 검출 회로를 전기적으로 연결하는 제2 스위치를 더 포함하며,

상기 제2 스위치가 도통된 구간동안 상기 하강 에지 검출 신호를 제공받고 누적하는 커패시턴스 검출 장치.5. The method of claim 4,

The detection circuit section,

The second detection circuit further includes a second switch for electrically connecting the capacitance detection panel and the second detection circuit,

Wherein the falling edge detection signal is provided and accumulated during a period in which the second switch is conductive.

상기 제1 검출 회로는 상기 상승 에지 이전에 리셋되며,

상기 제2 검출 회로는 상기 하강 에지 이전에 리셋되는 커패시턴스 검출 장치.The method according to claim 1,

The first detection circuit is reset prior to the rising edge,

And the second detection circuit is reset before the falling edge.

상기 커패시턴스 검출 장치는,

상기 데이터 정렬부가 정렬하여 출력한 신호를 디지털 신호로 변환하는 아날로그 디지털 변환기(ADC)를 더 포함하는 커패시턴스 검출 장치.The method according to claim 1,

Wherein the capacitance detection device comprises:

Further comprising an analog-to-digital converter (ADC) for converting the signal output from the data aligner into a digital signal.

(b) 검출 회로부가 상기 상승 에지 검출 신호를 제공받아 검출 신호를 출력하는 단계와,

(c) 상기 커패시턴스 검출 패널이 구동 신호의 하강 에지(rising edge)를 제공받아 하강 에지 검출 신호를 출력하는 단계와,

(d) 상기 검출 회로부가 상기 하강 에지 검출 신호를 제공받아 반전 검출 신호를 출력하는 단계 및

(e) 상기 검출 신호와 상기 반전 검출 신호를 정렬하여 동시에 출력하는 단계를 포함하며,

상기 (e) 단계는 상기 검출 신호와 상기 반전 검출 신호 중 먼저 출력된 신호를 샘플(sample)하여 나중에 출력된 신호와 함께 출력하도록 홀드(hold)하여 수행하고, 상기 검출 신호와 상기 반전 검출 신호는 의사 차동(pseudo differential) 관계에 있는 커패시턴스 검출 방법.(a) a capacitance detection panel receiving a rising edge of a driving signal and outputting a rising edge detection signal;

(b) a detection circuit section receiving the rising edge detection signal and outputting a detection signal;

(c) the capacitance detection panel receiving a falling edge of a driving signal and outputting a falling edge detection signal,

(d) the detection circuit section receives the falling edge detection signal and outputs an inversion detection signal; and

(e) aligning and outputting the detection signal and the inversion detection signal at the same time,

Wherein the step (e) samples and outputs the first signal out of the detection signal and the inversion detection signal and outputs the signal together with a signal output later, and the detection signal and the inversion detection signal are A method for detecting capacitance in a pseudo differential relationship.

상기 커패시턴스 검출 방법은

상기 (a) 단계 이전에 수행되는 상기 검출 회로부를 리셋하는 과정 및

상기 (c) 단계 이전에 수행되는 상기 검출 회로부를 리셋하는 과정을 더 포함하는 커패시턴스 검출 방법. 10. The method of claim 9,

The capacitance detection method

A step of resetting the detection circuit section performed before the step (a)

Further comprising the step of resetting the detection circuit section performed before the step (c).

상기 커패시턴스 검출 방법은

(f) 상기 검출 신호와 상기 반전 검출 신호를 디지털 신호로 변환하는 단계를 더 포함하는 커패시턴스 검출 방법.The method of claim 9, wherein

The capacitance detection method

(f) converting the detection signal and the inversion detection signal into a digital signal.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020170023975A KR101919439B1 (en) | 2017-02-23 | 2017-02-23 | Detection Method of Capacitance and Capacitance Detection Apparatus using the Same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020170023975A KR101919439B1 (en) | 2017-02-23 | 2017-02-23 | Detection Method of Capacitance and Capacitance Detection Apparatus using the Same |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20180097241A KR20180097241A (en) | 2018-08-31 |

| KR101919439B1 true KR101919439B1 (en) | 2019-02-08 |

Family

ID=63407841

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020170023975A KR101919439B1 (en) | 2017-02-23 | 2017-02-23 | Detection Method of Capacitance and Capacitance Detection Apparatus using the Same |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR101919439B1 (en) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102369444B1 (en) * | 2020-02-06 | 2022-03-04 | 삼성전기주식회사 | Self ckeck circuit and touch sensing device having the same |

-

2017

- 2017-02-23 KR KR1020170023975A patent/KR101919439B1/en active IP Right Grant

Also Published As

| Publication number | Publication date |

|---|---|

| KR20180097241A (en) | 2018-08-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7490678B2 (en) | Pressure sensing device and method | |

| KR102267365B1 (en) | Multi-step incremental switching scheme | |

| US7924029B2 (en) | Half-bridge for capacitive sensing | |

| US9442146B2 (en) | Multi-mode capacitive sensing device and method with current conveyor | |

| KR101340860B1 (en) | Methods and systems for detecting a capacitance using sigma-delta measurement techniques | |

| US10641805B2 (en) | Capacitance detection method and capacitance detection apparatus using the same | |

| US8841927B2 (en) | Touch sensing circuit | |

| CN110568952A (en) | Pressure sensing device and method | |

| JP5792334B2 (en) | Capacitance panel control point detection method and apparatus | |

| JP6184317B2 (en) | Input device | |

| US9823790B2 (en) | Touch sensing apparatus and method of driving the same | |

| US8878812B2 (en) | Signal processing circuit for electrostatic capacity type touch sensor | |

| CN108427515B (en) | Capacitance detection device and driving method thereof | |

| TWI517014B (en) | Method and device for identifying touch signal | |

| KR101919439B1 (en) | Detection Method of Capacitance and Capacitance Detection Apparatus using the Same | |

| KR101649750B1 (en) | Proximate Object Detection Method , Proximate Object Detection Apparatus using the same, Touch Detection Method and Touch Detection Apparatus using the Same | |

| CN110050253B (en) | Multi-stage self-capacitance scanning of sensor arrays | |

| US10754469B2 (en) | Touch detection method and touch detection apparatus | |

| US11188166B2 (en) | Input device | |

| KR20180097242A (en) | Detection Method of Capacitance and Capacitance Detection Apparatus using the Same | |

| KR101567587B1 (en) | Charge Amplifier and Touch Detection Apparatus using the Same | |

| KR102719183B1 (en) | Pressure sensing device and method | |

| KR20170025105A (en) | Touch detecting apparatus comprising flexible touch screen and method | |

| JP2015158781A (en) | touch panel |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant |