KR101879328B1 - Double split monotonic successive approximation register analog to digital converter - Google Patents

Double split monotonic successive approximation register analog to digital converter Download PDFInfo

- Publication number

- KR101879328B1 KR101879328B1 KR1020170029312A KR20170029312A KR101879328B1 KR 101879328 B1 KR101879328 B1 KR 101879328B1 KR 1020170029312 A KR1020170029312 A KR 1020170029312A KR 20170029312 A KR20170029312 A KR 20170029312A KR 101879328 B1 KR101879328 B1 KR 101879328B1

- Authority

- KR

- South Korea

- Prior art keywords

- capacitor

- capacitors

- bit

- successive approximation

- output signal

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/12—Analogue/digital converters

- H03M1/34—Analogue value compared with reference values

- H03M1/38—Analogue value compared with reference values sequentially only, e.g. successive approximation type

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/12—Analogue/digital converters

- H03M1/124—Sampling or signal conditioning arrangements specially adapted for A/D converters

- H03M1/1245—Details of sampling arrangements or methods

-

- H03M2201/62—

-

- H03M2201/8152—

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Analogue/Digital Conversion (AREA)

Abstract

Description

본 발명은 아날로그 디지털 변환기에 관한 것으로, 더욱 상세하게는 에너지 효율이 좋은 기존 단조 연속 근사 아날로그 디지털 변환기의 커패시터 개수를 줄일 수 있도록 분리형 기법을 조합하는 이중 분리형 단조 연속 근사 아날로그 디지털 변환기에 관한 것이다.The present invention relates to an analog-to-digital converter, and more particularly to a dual-ended forged successive approximation analog-to-digital converter that combines separate techniques to reduce the number of capacitors in an energy efficient conventional forged consecutive analog-to-digital converter.

기존의 단조 연속 근사 아날로그 디지털 변환기(monotonic successive approximation register analog to digital converter : MSAR ADC)는 비트(N)당 2N-1의 커패시터 개수가 필요하다. 따라서 10 bit의 경우 512개의 커패시터가 필요하며, 1비트 증가할수록 설계 면적이 크게 증가하게 된다. 하지만, 기존의 연속 근사 아날로그 디지털 변환기에 비해 에너지효율이 좋다는 장점이 있다.A conventional monotonic successive approximation register analog to digital converter (MSAR ADC) requires a number of capacitors of 2 N-1 per bit (N). Therefore, it requires 512 capacitors for 10 bits, and the design area increases greatly as 1 bit increases. However, it has the advantage of being more energy efficient than conventional successive approximation analog-to-digital converters.

한편, 기존의 분리형 연속 근사 아날로그 디지털 변환기(Split successive approximation register analog to digital converter : Split SAR ADC)는 브릿지 커패시터(bridge capacitance)를 통해서 적은 개수의 커패시터만으로도 고해상도의 아날로그 디지털 변환이 가능하다. 그러나 브릿지 커패시터의 크기(용량크기)를 정확히 조절하기 어렵기 때문에, 하위비트영역에서의 오차가 커지는 문제가 있다. 예를 들어, 10 bit의 분리형 연속 근사 아날로그 디지털 변환기에서 기본적인 커패시터의 크기를 100 fF으로 설정하면 브릿지 커패시터의 크기가 103.2…fF이 되는데, 이것은 현재의 공정으로 정확히 구현하기가 불가능하다. 따라서 브릿지 커패시터의 공정오차범위에 따라 하위비트의 정확도가 결정되며, 하위비트에서의 정확도를 향상시키기 위해서는 보정회로가 추가되어야 한다.Meanwhile, a conventional split-successive analog-to-digital converter (Split SAR ADC) is capable of high-resolution analog-to-digital conversion with a small number of capacitors through a bridge capacitance. However, since it is difficult to precisely control the size (capacitance size) of the bridge capacitor, there is a problem that the error in the lower bit area becomes larger. For example, in a 10-bit, discrete successive approximation analog-to-digital converter, setting the basic capacitor size to 100 fF results in a bridge capacitor ... fF, which is impossible to accurately implement in the present process. Therefore, the accuracy of the low-order bits is determined according to the process error range of the bridge capacitor, and a correction circuit must be added to improve the accuracy at the low-order bits.

따라서, 본 발명은 상기한 종래 기술의 문제점을 해결하기 위해 이루어진 것으로서, 본 발명의 목적은 추가된 2개의 브릿지 커패시터의 크기를 자연수로 구현한 분리형 기법을 조합함으로써 분리형 기법의 문제점 해결 및 커패시터 개수의 감소시킬 수 있도록 하는 이중 분리형 단조 연속 근사 아날로그 디지털 변환기를 제공하는데 있다.SUMMARY OF THE INVENTION It is therefore an object of the present invention to solve the problem of a separate type technique by combining a separate type technique in which the sizes of two additional bridge capacitors are implemented in a natural number, To-analog converters for analog to digital conversion.

상기와 같은 목적을 달성하기 위한 본 발명의 이중 분리형 단조 연속 근사 아날로그 디지털 변환기는, 연속 근사 레지스터(SAR) 제어 로직에 의해 스위칭 제어에 대응하여 입력신호인 제1입력신호(Vip)와 제2입력신호(Vin)를 입력받아 샘플 동작 및 홀드 동작을 수행하는 샘플 홀드부; 샘플 홀드 시간동안 제1입력신호와 제2입력신호에 대해 각각에 대응되는 출력 전압값인 제1출력신호와 제2출력신호로 생성하며, 2개의 브리지 커패시터(CB1, CB2)를 이용하여 상위비트 또는 하위비트를 결정하기 위한 커패시터 어레이를 2단 구조로 형성한 커패시터 어레이; 상기 샘플 홀드부와 연동되어 상기 상위비트 또는 상기 하위비트를 결정하는 스위치(S7, LSB_SW); 상기 제1출력신호와 제2출력신호의 크기를 비교하여 비교결과에 따라 디지털 값을 출력하는 비교기; 및 디지털 값에 대응하여 최종 디지털 코드값을 결과 신호로 출력하는 연속 근사 레지스터 제어 로직을 포함하는 것을 특징으로 한다.According to an aspect of the present invention, there is provided a dual detached forged successive approximation analog-to-digital converter including a first approximation register (SAR) control logic for controlling a first input signal (V ip ) A sample hold unit that receives the input signal V in and performs a sample operation and a hold operation; And generates a first output signal and a second output signal, which are output voltage values corresponding to the first input signal and the second input signal, respectively, during the sample hold time, using two bridge capacitors (C B1 , C B2 ) A capacitor array in which a capacitor array for determining an upper bit or a lower bit is formed in a two-stage structure; A switch (S7, LSB_SW) interlocked with the sample hold section to determine the upper bit or the lower bit; A comparator for comparing the magnitudes of the first output signal and the second output signal and outputting a digital value according to a comparison result; And successive approximation register control logic for outputting the final digital code value as a result signal corresponding to the digital value.

이 때, 상기 커패시터 어레이는, 상기 브리지 커패시터(CB1, CB2) 및 스위치(S7, LSB_SW)에 의해 결정되는 상위 커패시터 어레이와 하위 커패시터 어레이를 포함한다. 상기 상위 커패시터 어레이 및 하위 커패시터 어레이 각각은, 상위비트를 결정하는 제1커패시터부와, 하위비트를 결정하는 제2커패시터부와, 상기 제1커패시터부와 제2커패시터부 사이에 병렬접속된 중간커패시터(MID)를 포함한다. 상기 제1커패시터부 및 제2커패시터부 각각은, 병렬 연결된 복수의 커패시터를 포함하며, 복수의 커패시터는 레퍼런스 전압 또는 접지되는 바닥 스위치에 일단이 접속되고 타단은 비교기에 접속된다. 상기 제1커패시터부와 제2커패시터부의 비율은 N:N, N:N-1, N:N-2, … , N:1 중에서 어느 하나이다. 그리고, 상기 브리지 커패시터(CB1, CB2)와 제1커패시터부 및 제2커패시터부 각각은 배수관계를 갖는다.At this time, the capacitor array includes an upper capacitor array and a lower capacitor array determined by the bridge capacitors (C B1 , C B2 ) and the switches (S7, LSB_SW). Each of the upper capacitor arrays and the lower capacitor arrays includes a first capacitor portion for determining upper bits, a second capacitor portion for determining a lower bit, and a second capacitor portion for determining an upper half of the intermediate capacitor connected in parallel between the first capacitor portion and the second capacitor portion. (MID). Each of the first capacitor portion and the second capacitor portion includes a plurality of capacitors connected in parallel, and the plurality of capacitors have one end connected to a reference voltage or a bottom switch grounded, and the other end connected to a comparator. Wherein the ratio of the first capacitor unit to the second capacitor unit is N: N, N: N-1, N: N-2, , And N: 1. Each of the bridge capacitors (C B1 , C B2 ) and the first capacitor portion and the second capacitor portion has a drain relation.

한편, 상기 스위치(S7)은 브리지 커패시터(CB1, CB2) 및 중간커패시터(MID)에 일단이 접속되어 있으며, 상위비트에서 레퍼런스 또는 접지에 접속되고, 하위비트에서 개방(OPEN)되며, 상기 스위치(LSB_SW)는 제2커패시터부에 일단이 접속되어 있으며, 상위비트에서 레퍼런스 또는 접지에 타단이 접속되고, 하위비트에서 개방된다.The switch S7 is connected at one end to the bridge capacitors C B1 and C B2 and the intermediate capacitor MID and is connected to the reference or ground at the upper bit and is opened at the lower bit, The switch LSB_SW has one end connected to the second capacitor, the other end connected to the reference or ground at the upper bit, and opened at the lower bit.

상술한 바와 같이, 본 발명에 의한 이중 분리형 단조 연속 근사 아날로그 디지털 변환기에 따르면, 추가된 2개의 브릿지 커패시터의 크기를 자연수로 구현하여 분리형 기법의 문제점을 해결하고, 동시에 기존 단조 연속 근사 아날로그 디지털 변환기의 전체적인 커패시터 개수도 감소시킬 수 있으므로, 에너지 효율을 향상시킴과 아울러 설계 면적을 감소시킬 수 있다.As described above, according to the present invention, the size of the added two bridge capacitors can be solved by solving the problem of the separate type technique, and at the same time, The total number of capacitors can be reduced, so that the energy efficiency can be improved and the design area can be reduced.

또한, 커패시터의 크기를 현재 공정으로 정확히 구현할 수 있을 뿐 아니라, 추가적인 보정회로의 필요 없이 정확도를 향상시킬 수 있다.In addition, the size of the capacitor can be accurately implemented in the current process, and the accuracy can be improved without the need for an additional correction circuit.

즉, 본 발명은 이중 분리형과 단조를 조합하여 커패시터 개수 감소, 에너지 효율 향상, 커패시터 크기 구현 가능, 정확도 향상 등의 효과를 기대할 수 있다.That is, the present invention can reduce the number of capacitors, improve the energy efficiency, realize the capacitor size, and improve the accuracy by combining the dual separation type and the forging.

도 1은 기존의 단조 연속 근사 아날로그 디지털 변환기의 회로도이다.

도 2는 기존의 단조 연속 근사 아날로그 디지털 변환기의 동작을 나타낸 파형도이다.

도 3은 기존의 분리형 연속 근사 아날로그 디지털 변환기의 회로도이다.

도 4는 본 발명의 일 실시예에 의한 이중 분리형 단조 연속 근사 아날로그 디지털 변환기의 회로도이다.

도 5는 본 발명의 상위비트 회로도이다.

도 6은 본 발명의 상위비트 동작 파형도이다.

도 7은 본 발명의 하위비트 회로도이다.

도 8 내지 도 11은 본 발명의 하위비트 커패시터 값 변화 및 전압 변화 과정을 나타낸 개념도이다.

도 12는 본 발명의 하위비트 동작 설명도이다.1 is a circuit diagram of a conventional forged successive approximation analog-to-digital converter.

2 is a waveform diagram illustrating the operation of a conventional monotonic successive approximation analog-to-digital converter.

3 is a circuit diagram of a conventional detachable successive approximation analog-to-digital converter.

4 is a circuit diagram of a dual detachable forged successive approximation analog-to-digital converter according to an embodiment of the present invention.

5 is a circuit diagram of a higher bit of the present invention.

6 is a waveform diagram of an upper bit operation of the present invention.

7 is a lower bit circuit diagram of the present invention.

FIGS. 8 to 11 are conceptual diagrams illustrating a process of changing a lower bit capacitor value and a voltage change of the present invention.

12 is a diagram for explaining the lower bit operation of the present invention.

이하에서는 본 발명의 바람직한 실시예 및 첨부하는 도면을 참조하여 본 발명을 상세히 설명하되, 도면의 동일한 참조부호는 동일한 구성요소를 지칭함을 전제하여 설명하기로 한다.DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT Hereinafter, the present invention will be described in detail with reference to preferred embodiments of the present invention and the accompanying drawings, wherein like reference numerals refer to like elements.

상기한 바와 같이, 기존의 단조 연속 근사 아날로그 디지털 변환기는 비트 증가에 따라 커패시터 개수가 증가하고 설계 면적이 증가하는 문제가 있다. 한편, 분리형 연속 근사 아날로그 디지털 변환기는 브릿지 커패시터의 크기는 현재의 공정기술로 정확한 구현이 불가능하며, 브릿지 커패시터의 공정 오차에 따라 하위비트에서의 오차가 발생하게 되는 문제가 있다.As described above, in the conventional forged successive approximation analog-to-digital converter, the number of capacitors increases with a bit increase, and the design area increases. On the other hand, in the separate-type successive approximation analog-to-digital converter, the size of the bridge capacitor can not be accurately implemented by the current process technology, and there is a problem that an error occurs in the lower bits according to the process error of the bridge capacitor.

이에 본 발명에서는 이중 분리형(Double split) 기법과 단조(Monotonic) 기법을 조합하여 2개의 브릿지 커패시터의 값을 자연수로 만들고 에너지 효율 또한 향상시키면서 동시에 커패시터 개수를 감소시키고자 한다. 즉, 본 발명에서는 기존의 에너지 효율이 좋은 단조 연속 근사 아날로그 디지털 변환기에 대해 커패시터 개수를 줄일 수 있는 이중 분리형 기법을 조합한다. 추가된 2개의 브릿지 커패시터의 크기를 자연수로 구현하여 분리형 기법의 문제점을 해결하고, 동시에 단조 연속 근사 아날로그 디지털 변환기의 전체적인 커패시터 개수도 줄인다. 그 결과 에너지 효율을 향상시키고, 설계 면적을 감소시킬 수 있다. 또한, 커패시터 크기를 현재 공정으로 정확히 구현할 수 있으며, 추가적인 보정회로의 필요 없이 정확도를 향상시킬 수 있다.In the present invention, by combining the double split method and the monotonic method, the values of the two bridge capacitors are made to be natural numbers, the energy efficiency is improved, and at the same time, the number of capacitors is reduced. That is, the present invention combines a double-split technique that can reduce the number of capacitors for a conventional energy-efficient forged consecutive analog-to-digital converter. By implementing the size of the two added bridge capacitors in a natural number, the problem of the separate type technique is solved and at the same time, the number of the whole capacitors of the forged consecutive analog-to-digital converter is also reduced. As a result, the energy efficiency can be improved and the design area can be reduced. In addition, the capacitor size can be accurately implemented in the current process, and the accuracy can be improved without the need for an additional correction circuit.

먼저, 기존 기술에 대해 설명한 후, 본 발명의 이중 분리형 단조 연속 근사 아날로그 디지털 변환기에 대해 설명하기로 한다.First, after explaining the existing technology, a description will be made of a dual-separated forged successive approximation analog-digital converter of the present invention.

도 1은 기존의 단조 연속 근사 아날로그 디지털 변환기의 회로도이다.1 is a circuit diagram of a conventional forged successive approximation analog-to-digital converter.

도 1을 참조하면, 기존의 단조 연속 근사 아날로그 디지털 변환기로서, 10 bit를 예시하고 있다.Referring to FIG. 1, a conventional forged successive approximation analog-to-digital converter is illustrated with 10 bits.

기존의 단조 연속 근사 아날로그 디지털 변환기는 비교기, 커패시터, 샘플링 홀드 스위치(SH)로 구성되어 있다. 커패시터의 일단에 형성된 바닥 스위치(Dp0 ~ Dp8, Dn0 ~ Dn8)는 VREF 또는 GND(접지)에 접속된다. 커패시터는 비교기의 비반전 단자(+)와 반전 단자(-)에 각각 256(2N-2)개의 커패시터가 달려 있으며, 10 bit의 총 512(2N-1)개의 커패시터가 필요하게 된다. 만약 여기에 1 bit를 증가시킬 경우, 즉 11 bit를 만들 경우 총 1024개의 커패시터가 필요하게 된다.Conventional forged successive approximation analog digital converters consist of a comparator, a capacitor, and a sampling hold switch (SH). The bottom switches (D p0 to D p8 , D n0 to D n8 ) formed at one end of the capacitor are connected to V REF or GND (ground). The capacitors have 256 (2 N-2 ) capacitors at the non-inverting terminal (+) and inverting terminal (-) of the comparator, respectively, and a total of 512 (2 N-1 ) capacitors of 10 bits are required. If you increase 1 bit here, that is, make 11 bits, a total of 1024 capacitors will be needed.

도 2는 기존의 단조 연속 근사 아날로그 디지털 변환기의 동작을 나타낸 파형도이다.2 is a waveform diagram illustrating the operation of a conventional monotonic successive approximation analog-to-digital converter.

도 2를 참조하면, 샘플링 홀드(SH) 시간동안 커패시터의 일단에 형성된 바닥 스위치들은(Dp0 ~ Dp8, Dn0 ~ Dn8) 모두 VREF에 접속되고 비교기의 비반전 단자(+)와 반전 단자(-)에 각각 VIN_P과 VIN_N이 충전된다. 비교기의 비반전 단자(+)와 반전 단자(-)에 전압이 충전된 후에 비교기가 두 값을 비교하고 그 결과('1')를 D9에 저장한다. 그 후 비교기의 비반전 단자(+)의 전압이 반전 단자(-)의 전압보다 크기 때문에 Dp8 스위치는 GND에 연결되고 비교기의 비반전 단자(+)의 전압은 VREF/2 만큼의 전압이 감소하게 된다. 그리고 비교기가 두 값을 비교한다. 그 결과 비교기의 비반전 단자(+)의 전압이 반전 단자(-)의 전압보다 크기 때문에 D8은 '1'을 저장한다. 그러면 Dp7 스위치는 GND에 연결되고 비교기의 비반전 단자(+)의 전압은 VREF/22 만큼 감소하고 비교기가 두 값을 비교한다. 그 다음에는 비교기의 비반전 단자(+)의 전압이 반전 단자(-)의 전압보다 크기 때문에, D7에 '0'이라는 값이 저장되고, Dn6 스위치가 GND에 연결되고 비교기의 반전 단자(-)의 전압이 VREF/23 만큼 감소하게 된다. 같은 방식으로 D0까지 계산한다. 이와 같이, 비교기의 비반전 단자(+) 또는 반전 단자(-)의 전압이 감소하는 한쪽방향으로 움직인다. 이에 이러한 아날로그 디지털 변환기를 단조 연속 근사 아날로그 디지털 변환기라 한다.Referring to FIG. 2, bottom switches (D p0 to D p8 , D n0 to D n8 ) formed at one end of the capacitor during the sampling hold (SH) time are all connected to V REF and inverted The terminals (-) are charged with V IN_P and V IN_N , respectively. After the noninverting terminal (+) and inverting terminal (-) of the comparator are charged, the comparator compares the two values and stores the result ('1') in D9. Since the voltage of the non-inverting terminal (+) of the comparator is larger than the voltage of the inverting terminal (-), the D p8 switch is connected to GND and the voltage of the non-inverting terminal (+) of the comparator is V REF / 2 . And the comparator compares the two values. As a result, D8 stores '1' because the voltage of the non-inverting terminal (+) of the comparator is larger than the voltage of the inverting terminal (-). The D p7 switch is then connected to GND and the voltage at the non-inverting terminal (+) of the comparator is reduced by V REF / 2 2 and the comparator compares the two values. Next, since the voltage of the non-inverting terminal (+) of the comparator is greater than the voltage of the inverting terminal (-), a value of '0' is stored in D 7 , the D n6 switch is connected to GND, -) is reduced by V REF / 2 3 . Calculate up to D0 in the same way. In this way, the voltage of the non-inverting terminal (+) or inverting terminal (-) of the comparator moves in one direction decreasing. This analog-to-digital converter is called a forged successive approximation analog-to-digital converter.

도 3은 기존의 분리형 연속 근사 아날로그 디지털 변환기의 회로도이다.3 is a circuit diagram of a conventional detachable successive approximation analog-to-digital converter.

도 3을 참조하면, 기존의 분리형 연속 근사 아날로그 디지털 변환기로서, 10 bit를 예시하고 있다.Referring to FIG. 3, a conventional discrete successive approximation analog-to-digital converter is illustrated with 10 bits.

기존의 분리형 연속 근사 아날로그 디지털 변환기는 상위비트(MSB) 5 bit와 하위비트(LSB) 5 bit를 하나의 브릿지 커패시터(Bridge capacitance)로 분리시키고, 각각의 분리된 영역에서 하위비트(LSB) 5 bit(D0-D4)와 상위비트(MSB) 5 bit(D5-D9)를 결정한다. 이 때, 가장 중요한 것은 두 영역을 분리시킨 브릿지 커패시터의 크기(용량크기)이다. 도 1에서와 같이 상위 비트 영역에서 바라본 하위 비트 영역의 총 커패시터의 크기는 1C여야 한다. 브릿지 커패시터의 크기를 CB라 할 때,In the conventional separable successive approximation analog-to-digital converter, 5 bits of the MSB and 5 bits of the LSB are separated into a bridge capacitance, and 5 bits (LSB) (D0-D4) and 5 bits (D5-D9) of the upper bits (MSB). At this time, the most important thing is the size (capacity size) of the bridge capacitor that separates the two regions. As shown in FIG. 1, the size of the total capacitors in the lower bit region viewed from the upper bit region should be 1C. When the size of the bridge capacitor is C B ,

의 관계식이 성립하고, 가 된다. 따라서 공정으로 정확히 구현하기가 불가능하며, 브릿지 커패시터의 공정오차에 따라 하위비트에서의 오차가 발생하게 된다.And, . Therefore, it is impossible to accurately implement the process, and an error occurs in the lower bit according to the process error of the bridge capacitor.

도 4는 본 발명의 일 실시예에 의한 이중 분리형 단조 연속 근사 아날로그 디지털 변환기의 회로도이다.4 is a circuit diagram of a dual detachable forged successive approximation analog-to-digital converter according to an embodiment of the present invention.

여기서, 도 4는 비교기의 일측단자(비반전단자 또는 반전단자)에 접속되는 이중 분리형 단조 연속 근사 아날로그 디지털 변환기(Double split monotonic successive approximation register analog to digital converter)의 일측만 도시하고 있으며, 대칭되는 회고가 타측단자에 접속된다. 도 4의 회로도는 비교기의 반전단자에 접속되는 회로도를 도시하고 있다.FIG. 4 shows only one side of a double split monotonic successive approximation register analog to digital converter connected to one terminal (non-inverting terminal or inverting terminal) of the comparator, Is connected to the other terminal. The circuit diagram of Fig. 4 shows a circuit diagram connected to the inverting terminal of the comparator.

도 4를 참조하면, 본 발명의 이중 분리형 단조 연속 근사 아날로그 디지털 변환기는, 연속 근사 레지스터(SAR) 제어 로직(Control logic)에 의해 스위칭 제어에 대응하여 입력신호인 제1입력신호(Vip)와 제2입력신호(Vin)를 입력받아 샘플 동작 및 홀드 동작을 수행하는 샘플 홀드부(SH 스위치)(SH)와, 샘플 홀드 시간동안 제1입력신호와 제2입력신호에 대해 각각에 대응되는 출력 전압값인 제1출력신호와 제2출력신호로 생성하며, 2개의 브리지 커패시터(CB1, CB2)를 이용하여 상위비트 또는 하위비트를 결정하기 위한 커패시터 어레이를 2단 구조로 형성한 커패시터 어레이(CA)와, 샘플 홀드부와 연동되어 상기 상위비트 또는 상기 하위비트를 결정하는 스위치(S7, LSB_SW)와, 제1출력신호와 제2출력신호의 크기를 비교하여 비교결과에 따라 디지털 값을 출력하는 비교기(Comp)와, 디지털 값에 대응하여 최종 디지털 코드값을 결과 신호로 출력하는 SAR 제어 로직을 포함한다.Referring to FIG. 4, the dual-ended forged successive approximation analog-to-digital converter of the present invention includes a first approximation register (SAR) control logic, a first input signal V ip A sample hold section (SH switch) SH for receiving a second input signal V in and performing a sample operation and a hold operation, and a sample hold section A capacitor having a two-stage structure in which a capacitor array for generating a first output signal and a second output signal, which are output voltage values, and for determining an upper bit or a lower bit using two bridge capacitors C B1 and C B2 , A switch (S7, LSB_SW) interlocked with the sample hold section to determine the upper bit or the lower bit; and a comparator for comparing the magnitude of the first output signal with the magnitude of the second output signal, Comparison to output And a SAR control logic for outputting the final digital code value as a result signal corresponding to the digital value.

이 때, 커패시터 어레이(CA)는, 브리지 커패시터(CB1, CB2) 및 스위치(S7, LSB_SW)에 의해 결정되는 상위 커패시터 어레이와 하위 커패시터 어레이를 포함한다.At this time, the capacitor array CA includes an upper capacitor array and a lower capacitor array determined by the bridge capacitors C B1 , C B2 and the switches S7, LSB_SW.

또한, 상위 커패시터 어레이 및 하위 커패시터 어레이 각각은, 상위비트를 결정하는 제1커패시터부와, 하위비트를 결정하는 제2커패시터부와, 제1커패시터부와 제2커패시터부 사이에 병렬접속된 중간커패시터(MID)를 포함한다. 이 때, 제1커패시터부 및 제2커패시터부 각각은 병렬 연결된 복수의 커패시터를 포함하며, 복수의 커패시터는 레퍼런스 전압 또는 접지되는 바닥 스위치에 일단이 접속되고 타단은 비교기(Comp)에 접속된다.Each of the upper capacitor array and the lower capacitor array includes a first capacitor portion for determining the upper bit, a second capacitor portion for determining the lower bit, and an intermediate capacitor connected in parallel between the first capacitor portion and the second capacitor portion. (MID). In this case, each of the first capacitor portion and the second capacitor portion includes a plurality of capacitors connected in parallel, and the plurality of capacitors have one end connected to a reference voltage or a ground switch to be grounded, and the other end connected to a comparator (Comp).

일례로서, 제1커패시터부(상위비트)는 6개의 커패시터로 구성되며, 제2커패시터부(하위비트)는 3개의 커패시터로 구성될 수 있다. 이 때, 브리지 커패시터(CB1)는 23C이고, 브리지 커패시터(CB2)는 22C다. 즉, 브리지 커패시터(CB1, CB2)의 용량크기는 자연수이다. 한편, 제1커패시터부와 제2커패시터부의 비율은 N:N, N:N-1, N:N-2, … , N:1 중에서 어느 하나가 선택될 수 있다. 이 때, 브리지 커패시터(CB1, CB2)와 제1커패시터부 및 제2커패시터부 각각은 배수관계를 갖는다. 이에 브리지 커패시터(CB1, CB2)의 용량크기는 자연수 중 어느 하나의 크기로 할 수 있다.For example, the first capacitor unit (upper bit) may be composed of six capacitors, and the second capacitor unit (lower bit) may be composed of three capacitors. At this time, the bridge capacitor C B1 is 2 3 C and the bridge capacitor C B2 is 2 2 C. That is, the capacitance values of the bridge capacitors C B1 and C B2 are natural numbers. On the other hand, the ratio of the first capacitor unit to the second capacitor unit is N: N, N: N-1, N: N-2, , And N: 1 can be selected. At this time, each of the bridge capacitors (C B1 , C B2 ) and the first capacitor portion and the second capacitor portion has a drain relation. Therefore, the capacitance of the bridge capacitors C B1 and C B2 can be any one of natural numbers.

한편, 스위치(S7)는 브리지 커패시터(CB1, CB2) 및 중간커패시터(MID)에 일단이 접속되어 있으며, 상위비트에서 레퍼런스 또는 접지에 타단이 접속되고, 하위비트에서 개방(OPEN)되며, 스위치(LSB_SW)는 제2커패시터부에 일단이 접속되어 있으며, 상위비트에서 레퍼런스 또는 접지에 타단이 접속되고, 하위비트에서 개방(OPEN)된다.On the other hand, a switch (S7) is the one end is connected to the bridge capacitor (C B1, C B2) and an intermediate capacitor (MID), to be connected to the other end to a reference or ground on the high-order bit, is opened (OPEN) on the low-order bit, The switch LSB_SW is connected at one end to the second capacitor, and the other bit is connected to the reference or ground at the upper bit and is opened at the lower bit.

이와 같이 구성된 본 발명의 이중 분리형 단조 연속 근사 아날로그 디지털 변환기는, 상위비트 결정하는 부분과 하위비트를 결정하는 부분을 2개의 브릿지 커패시터(CB1, CB2)및 스위치(S7 , LSB_SW)를 통해서 나눈다. S7 스위치와 LSB_SW 스위치가 닫히면 상위비트를 결정하는 연속 근사 아날로그 디지털 변환기가 되며, S7 스위치와 LSB_SW 스위치가 개방(OPEN)되면 하위비트를 결정하는 연속 근사 아날로그 디지털 변환기가 된다.In the double separated forging successive approximation analog-to-digital converter of the present invention configured as described above, a portion for determining upper bits and a portion for determining lower bits are divided through two bridge capacitors (C B1 and C B2 ) and switches (S7 and LSB_SW) . When the S7 and LSB_SW switches are closed, they become successive approximate analog-to-digital converters that determine the upper bits. When the S7 and LSB_SW switches are opened, they become successive approximate analog-to-digital converters that determine the lower bits.

그러면, 여기서 상기와 같이 구성된 이중 분리형 단조 연속 근사 아날로그 디지털 변환기의 동작에 대해 설명하기로 한다.Hereinafter, the operation of the above-configured double separated forged successive approximation analog-to-digital converter will be described.

도 5는 본 발명의 상위비트 회로도이다.5 is a circuit diagram of a higher bit of the present invention.

도 5를 참조하면, 도 4의 S7 스위치와 LSB_SW 스위치가 VREF 또는 GND에 연결됐을(닫힐 때) 때, 상위비트의 회로도가 된다. 그 결과 도 5처럼 되며, 이중 분리형 단조 연속 근사 아날로그 디지털 변환기의 상위비트를 결정하는 회로도가 된다.Referring to FIG. 5, when the S7 switch and the LSB_SW switch in FIG. 4 are connected (closed) to V REF or GND, a circuit diagram of the upper bit is obtained. The result is as shown in Fig. 5, which is a circuit diagram for determining the upper bits of the double detached forged successive approximation analog-to-digital converter.

도 6은 본 발명의 상위비트 동작 파형도이다.6 is a waveform diagram of an upper bit operation of the present invention.

도 6을 참조하면, 처음에 SH 스위치가 닫힐 때, <S4p:S9p>=<000000>과 <S4n:S9n>=<000000>이 되며 모두 VREF에 연결된다. 그리고 커패시터 상판(C_top)에 입력전압(VIN_n, VIN_p)을 샘플링한다. 입력전압이 커패시터에 샘플링되면, SH 스위치만 열린다. 그 후에, 비교기(Comp)의 비반전 단자(+)의 전압과 반전 단자(-)의 전압을 비교한다. 비교기(Comp)의 비반전 단자(+) 전압이 반전 단자(-) 전압보다 크기 때문에, <D9p>=<1>이 되고 GND에 연결되면서, 비교기(Comp)의 비반전 단자(+)의 전압이 VREF/2 만큼 감소한다. <D9n>=<0>으로 그대로 VREF에 연결되서, 비교기(Comp)의 반전 단자(-)의 전압은 그대로 유지된다. 그 다음에도 비교기(Comp)의 비반전 단자(+)의 전압이 반전 단자(-)의 전압보다 크기 때문에, <D8p>=<1>는 GND에 연결되면서, 비교기(Comp)의 비반전 단자(+)의 전압이 VREF/22 만큼 감소한다. <D8n>=<0>으로 그대로 VREF에 연결되서, 비교기(Comp)의 반전 단자(-)의 전압은 그대로 유지된다. 그 다음에는 비교기(Comp)의 반전 단자(-)의 전압이 비반전 단자(+)의 전압보다 크기 때문에, <D7n>=<1>는 GND에 연결되면서, 비교기(Comp)의 반전 단자(-)의 전압이 VREF/23 만큼 감소한다. <D7p>=<0>으로 그대로 VREF에 연결되서, 비교기(Comp)의 비반전 단자(+)의 전압은 그대로 유지된다. 이러한 방식으로, 나머지 비트도 결정된다. 그 결과 <D4p:Dp9>=<110010>, <D4n:Dn9>=<001101>이 된다. 상위 비트 6비트가 결정되면 S7n, S7p 모두 OPEN에 연결된다.Referring to FIG. 6, when the SH switch is initially closed, <S 4p : S 9p > = <000000> and <S 4n : S 9n > = <000000> are all connected to V REF . Then, the input voltages V IN_n and V IN_p are sampled on the capacitor top plate C_top. When the input voltage is sampled on the capacitor, only the SH switch is opened. Thereafter, the voltage of the non-inverting terminal (+) of the comparator (Comp) is compared with the voltage of the inverting terminal (-). Since the voltage of the non-inverting terminal (+) of the comparator (Comp) is larger than the voltage of the inverting terminal (-), <D 9p > = <1> The voltage decreases by V REF / 2. <D 9n> = doeseo as connected to the V REF <0>, inverting terminal of the comparator (Comp) (-) voltage is maintained. Then, since the voltage of the non-inverting terminal (+) of the comparator (Comp) is larger than the voltage of the inverting terminal (-), <D 8p > = <1> is connected to GND, (+) Voltage decreases by V REF / 2 2 . <D 8n> = doeseo as connected to the V REF <0>, inverting terminal of the comparator (Comp) (-) voltage is maintained. Next, since the voltage of the inverting terminal (-) of the comparator (Comp) is larger than the voltage of the non-inverting terminal (+), <D 7n > = <1> is connected to GND, -) decreases by V REF / 2 3 . <7p D> = doeseo as connected to the V REF <0>, the voltage of the comparator (Comp) a non-inverting terminal (+) of is maintained. In this way, the remaining bits are also determined. As a result, <D 4p : D p9 > = <110010> and <D 4n : D n9 > = <001101>. When the upper 6 bits are determined, both S 7n and S 7p are connected to OPEN.

도 7은 본 발명의 하위비트 회로도이다.7 is a lower bit circuit diagram of the present invention.

도 7을 참조하면, 도 4에서 S7 스위치와 SH 스위치가 모두 열렸을 때, 하위비트의 회로도가 된다. 상위 비트의 스위치 D9,D8,D7,D6,D5,D4는 도 6의 결과로 스위치가 GND에 연결되어 있다. 나머지 D1 ~ D3의 스위치 연결에 따라 하위비트 3bit가 결정된다.Referring to Fig. 7, when both the S7 switch and the SH switch are opened in Fig. 4, a circuit diagram of lower bits is obtained. The switches D 9 , D 8 , D 7 , D 6 , D 5 , and D 4 of the upper bits are connected to GND as a result of FIG. And the lower 3 bits are determined according to the switch connection of the remaining D 1 to D 3 .

도 8 내지 도 11은 본 발명의 하위비트 커패시터 값 변화 및 전압 변화 과정을 나타낸 개념도이다.FIGS. 8 to 11 are conceptual diagrams illustrating a process of changing a lower bit capacitor value and a voltage change of the present invention.

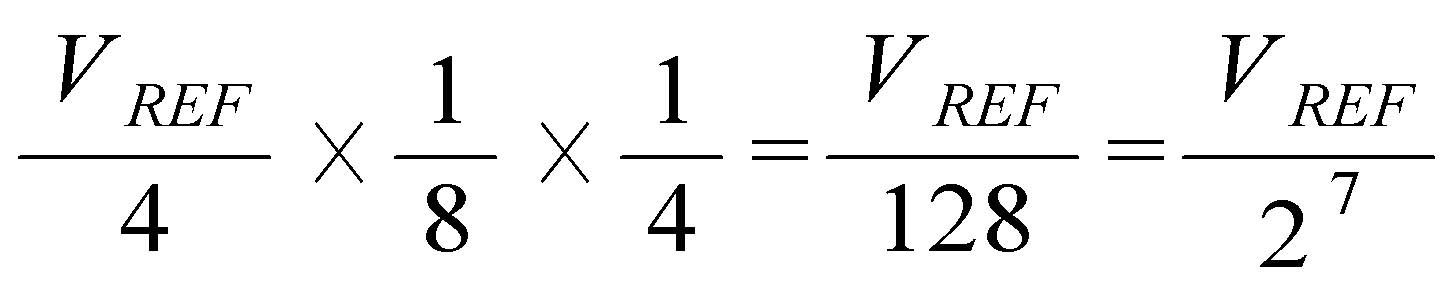

도 8 내지 도 11을 참조하면, 도 8에서 MSB에 해당하는 커패시터의 총합은 56C이며 CB1은 8C이다. 따라서 중간커패시터(MID)에서 MSB로 넘어가는 전압은 과 같이 1/8 만큼 감소되어 넘어간다. 도 9에서는 MSB 커패시터와 CB1의 커패시터 총합을 보여준다. 가 되고, 중간커패시터(MID)에서 커패시터 5C와 7C가 병렬연결이 된다. 도 10은 LSB에서 중간커패시터(MID)로 전압이 넘어가는 것을 설명하고 있다. 도 10은 앞서 도 9에서 5C와 7C가 12C로 합쳐진 회로도이다. 중간커패시터(MID)에 해당하는 커패시터의 총합은 12C이며 CB2는 4C이다. 따라서 LSB에서 중간커패시터(MID)로 넘어가는 전압은 과 같이 1/4 만큼 감소되어 넘어간다. 도 11은 LSB의 전압변화를 설명하고 있다. 앞서 도 10의 4C와 12C가 직렬 연결되어 있으므로, 가 된다. D2의 전압이 만큼 변할 경우 LSB의 상판의 전압은 가 된다. 따라서 D1, D2 각각 , 만큼의 전압이 변하게 된다.Referring to FIGS. 8 to 11, the sum of the capacitors corresponding to MSB in FIG. 8 is 56C and C B1 is 8C. Therefore, the voltage across the intermediate capacitor (MID) As shown in FIG. 9 shows the sum of the capacitors of MSB and C B1 . And the

도 12는 본 발명의 하위비트 동작 설명도이다.12 is a diagram for explaining the lower bit operation of the present invention.

도 12를 참조하면, 도 6에서 상위비트를 설명할 때, VREF/26까지 상위비트 7비트가 결정되었다. 따라서 하위비트에서는 VREF/27부터 VREF/29까지 결정하면 하위비트 3비트가 결정된다. 하위비트 D3의 값 '1' → '0'으로 바뀔 때 전압이 △V 만큼 변하면서, CLSB의 전압은 만큼 변하게 된다. 그 후 브릿지 커패시터(CB1, CB2)에 의해서 전압이 , 만큼 감소하게 된다. 그 결과 LSB에서 만큼의 전압 변화가 MSB에서는 가 만들어지면서 하위비트 D3가 결정된다. 그 후 D2, D1은 커패시터 값이 1/2 만큼 감소하기 때문에, 각각 , 이 만들어 진다. 따라서 하위비트 3비트가 결정된다. Referring to FIG. 12, when explaining the upper bits in FIG. 6, 7 bits of upper bits are determined up to V REF / 2 6 . Therefore, in the lower bit, if the determination is made from V REF / 2 7 to V REF / 2 9 , the lower 3 bits are determined. When the value of the lower bit D 3 changes from '1' to '0', the voltage changes by ΔV, and the voltage of C LSB becomes . Then, the bridge capacitors (C B1 , C B2 ) , . As a result, In the MSB And the lower bit D 3 is determined. Since D 2 and D 1 then decrease the capacitor value by 1/2, , . Therefore, the lower 3 bits are determined.

제시된 실시예들에 대한 설명은 임의의 본 발명의 기술 분야에서 통상의 지식을 가진 자가 본 발명을 이용하거나 또는 실시할 수 있도록 제공된다. 이러한 실시예들에 대한 다양한 변형들은 본 발명의 기술 분야에서 통상의 지식을 가진 자에게 명백할 것이며, 여기에 정의된 일반적인 원리들은 본 발명의 범위를 벗어남이 없이 다른 실시예들에 적용될 수 있다. 그리하여, 본 발명은 여기에 제시된 실시예들로 한정되는 것이 아니라, 여기에 제시된 원리들 및 신규한 특징들과 일관되는 최광의의 범위에서 해석되어야 할 것이다.The description of the disclosed embodiments is provided to enable any person skilled in the art to make or use the present invention. Various modifications to these embodiments will be readily apparent to those skilled in the art, and the generic principles defined herein may be applied to other embodiments without departing from the scope of the invention. Thus, the present invention is not intended to be limited to the embodiments shown herein but is to be accorded the widest scope consistent with the principles and novel features presented herein.

SH : 샘플 홀드부(SH 스위치)

CA : 커패시터 어레이

Comp : 비교기SH: Sample hold section (SH switch)

CA: capacitor array

Comp: Comparator

Claims (7)

상기 커패시터 어레이는, 상기 브리지 커패시터(CB1, CB2) 및 스위치(S7, LSB_SW)에 의해 결정되는 상위 커패시터 어레이와 하위 커패시터 어레이를 포함하고,

상기 상위 커패시터 어레이 및 하위 커패시터 어레이 각각은, 상위비트를 결정하는 제1커패시터부와, 하위비트를 결정하는 제2커패시터부와, 상기 제1커패시터부와 제2커패시터부 사이에 병렬접속된 중간커패시터(MID)를 포함하며,

상기 스위치(S7)은 브리지 커패시터(CB1, CB2) 및 중간커패시터(MID)에 일단이 접속되어 있으며, 상위비트에서 레퍼런스 또는 접지에 접속되고, 하위비트에서 개방(OPEN)되며,

상기 스위치(LSB_SW)는 제2커패시터부에 일단이 접속되어 있으며, 상위비트에서 레퍼런스 또는 접지에 타단이 접속되고, 하위비트에서 개방되는 이중 분리형 단조 연속 근사 아날로그 디지털 변환기.

A sample hold unit for receiving a first input signal V ip and a second input signal V in as input signals in response to a switching control by a consecutive approximation register (SAR) control logic and performing a sample operation and a hold operation; And generates a first output signal and a second output signal, which are output voltage values corresponding to the first input signal and the second input signal, respectively, during the sample hold time, using two bridge capacitors (C B1 , C B2 ) A capacitor array in which a capacitor array for determining an upper bit or a lower bit is formed in a two-stage structure; A switch (S7, LSB_SW) interlocked with the sample hold section to determine the upper bit or the lower bit; A comparator for comparing the magnitudes of the first output signal and the second output signal and outputting a digital value according to a comparison result; And successive approximation register control logic for outputting the final digital code value as a result signal corresponding to the digital value,

The capacitor array includes an upper capacitor array and a lower capacitor array determined by the bridge capacitors (C B1 , C B2 ) and the switches (S7, LSB_SW)

Each of the upper capacitor arrays and the lower capacitor arrays includes a first capacitor portion for determining upper bits, a second capacitor portion for determining a lower bit, and a second capacitor portion for determining an upper half of the intermediate capacitor connected in parallel between the first capacitor portion and the second capacitor portion. (MID)

The switch S7 is connected at one end to the bridge capacitors C B1 and C B2 and the intermediate capacitor MID and is connected to the reference or ground at the upper bit and opened at the lower bit,

The switch LSB_SW is connected at one end to the second capacitor unit, the other end connected to the reference or ground at the upper bit, and opened at the lower bit.

상기 제1커패시터부 및 제2커패시터부 각각은, 병렬 연결된 복수의 커패시터를 포함하며, 복수의 커패시터는 레퍼런스 전압 또는 접지되는 바닥 스위치에 일단이 접속되고 타단은 비교기에 접속되는 이중 분리형 단조 연속 근사 아날로그 디지털 변환기.

The method according to claim 1,

Wherein each of the first capacitor portion and the second capacitor portion includes a plurality of capacitors connected in parallel and the plurality of capacitors are connected to a reference switch or ground switch to which one end is connected and the other end is connected to a comparator, Digital converter.

상기 제1커패시터부와 제2커패시터부의 비율은 N:N, N:N-1, N:N-2, … , N:1 중에서 어느 하나인 이중 분리형 단조 연속 근사 아날로그 디지털 변환기.

5. The method of claim 4,

Wherein the ratio of the first capacitor unit to the second capacitor unit is N: N, N: N-1, N: N-2, , N: 1, respectively.

상기 브리지 커패시터(CB1, CB2)와 제1커패시터부 및 제2커패시터부 각각은 배수관계를 갖는 이중 분리형 단조 연속 근사 아날로그 디지털 변환기.The method according to claim 1,

Wherein the bridge capacitors (C B1 , C B2 ) and the first capacitor portion and the second capacitor portion each have a drain relationship.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020170029312A KR101879328B1 (en) | 2017-03-08 | 2017-03-08 | Double split monotonic successive approximation register analog to digital converter |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020170029312A KR101879328B1 (en) | 2017-03-08 | 2017-03-08 | Double split monotonic successive approximation register analog to digital converter |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR101879328B1 true KR101879328B1 (en) | 2018-07-18 |

Family

ID=63048954

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020170029312A KR101879328B1 (en) | 2017-03-08 | 2017-03-08 | Double split monotonic successive approximation register analog to digital converter |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR101879328B1 (en) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102139939B1 (en) * | 2019-07-26 | 2020-07-31 | 충북대학교 산학협력단 | low power switching successive approximation register(SAR) analog-digital converter(ADC) and analog-digital converting method using the same |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20110015113A (en) * | 2009-08-07 | 2011-02-15 | 한국전자통신연구원 | Dac(digital-analog converter) with pseudo-differential merged-capacitor switching method |

| KR101512098B1 (en) * | 2013-07-16 | 2015-04-14 | 서강대학교산학협력단 | SAR ADC using C-R hybrid DAC |

| KR101660416B1 (en) * | 2015-01-06 | 2016-09-28 | 울산과학기술원 | Sar-adc apparatus using cds and sampling method thereof |

| KR101666575B1 (en) * | 2015-01-06 | 2016-10-17 | 울산과학기술원 | Capacitor array matching apparatus and method in a sar-adc |

-

2017

- 2017-03-08 KR KR1020170029312A patent/KR101879328B1/en active IP Right Grant

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20110015113A (en) * | 2009-08-07 | 2011-02-15 | 한국전자통신연구원 | Dac(digital-analog converter) with pseudo-differential merged-capacitor switching method |

| KR101512098B1 (en) * | 2013-07-16 | 2015-04-14 | 서강대학교산학협력단 | SAR ADC using C-R hybrid DAC |

| KR101660416B1 (en) * | 2015-01-06 | 2016-09-28 | 울산과학기술원 | Sar-adc apparatus using cds and sampling method thereof |

| KR101666575B1 (en) * | 2015-01-06 | 2016-10-17 | 울산과학기술원 | Capacitor array matching apparatus and method in a sar-adc |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102139939B1 (en) * | 2019-07-26 | 2020-07-31 | 충북대학교 산학협력단 | low power switching successive approximation register(SAR) analog-digital converter(ADC) and analog-digital converting method using the same |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8059022B2 (en) | Digital-to-analog converter | |

| CN108574487B (en) | Successive approximation register analog-to-digital converter | |

| US8547270B1 (en) | Systems for sub digital-to-analog converter gain trim in successive-approximation-register analog-to-digital converters | |

| US7893860B2 (en) | Successive approximation register analog-digital converter and method of driving the same | |

| US8004447B2 (en) | Successive approximation analog to digital converter and method thereof | |

| US7773024B2 (en) | SAR analog-to-digital converter with large input range | |

| CN108476024B (en) | DAC capacitor array, SAR analog-to-digital converter and method for reducing power consumption | |

| US11070225B2 (en) | Successive approximation register (SAR) analog to digital converter (ADC) with overlapping reference voltage ranges | |

| CN108631778B (en) | Successive approximation analog-to-digital converter and conversion method | |

| KR101299215B1 (en) | Method for correcting mismatch of capacitors and analog to digital converter using thereof | |

| EP3607659B1 (en) | Successive approximation register (sar) analog to digital converter (adc) dynamic range extension | |

| CN108111171B (en) | Monotonic switching method suitable for differential structure successive approximation type analog-to-digital converter | |

| KR102139939B1 (en) | low power switching successive approximation register(SAR) analog-digital converter(ADC) and analog-digital converting method using the same | |

| KR101834975B1 (en) | Split monotonic successive approximation register analog to digital converter | |

| US20200007143A1 (en) | Successive Approximation Register (SAR) Analog to Digital Converter (ADC) with Switchable Reference Voltage | |

| US10404264B2 (en) | Method of performing analog-to-digital conversion | |

| KR101879328B1 (en) | Double split monotonic successive approximation register analog to digital converter | |

| US5986599A (en) | Voltage comparator for analog-to-digital converter | |

| JP5695629B2 (en) | Successive comparison type A / D converter and multi-bit delta-sigma modulator using the same | |

| KR100696945B1 (en) | Successive approximation register adc reusing a unit block of adc for implementing high bit resolution | |

| US20140062752A1 (en) | Analog-to-digital converter and analog-to-digital conversion method using the same | |

| JP2007013885A (en) | Pipeline a/d converter and pipeline a/d conversion method | |

| CN109792251B (en) | Successive Approximation Register (SAR) analog-to-digital converter (ADC) with switchable reference voltages | |

| US7283077B2 (en) | Divide-add circuit and high-resolution digital-to-analog converter using the same | |

| KR101810490B1 (en) | Split successive approximation register analog to digital converter with unit bridge capacitance and operation method thereof |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant |