KR100622609B1 - 박막 형성 방법 - Google Patents

박막 형성 방법 Download PDFInfo

- Publication number

- KR100622609B1 KR100622609B1 KR1020050012677A KR20050012677A KR100622609B1 KR 100622609 B1 KR100622609 B1 KR 100622609B1 KR 1020050012677 A KR1020050012677 A KR 1020050012677A KR 20050012677 A KR20050012677 A KR 20050012677A KR 100622609 B1 KR100622609 B1 KR 100622609B1

- Authority

- KR

- South Korea

- Prior art keywords

- gas

- thin film

- supplying

- cycle

- source gas

- Prior art date

Links

- 238000007736 thin film deposition technique Methods 0.000 title claims description 12

- 239000007789 gas Substances 0.000 claims abstract description 101

- 238000000034 method Methods 0.000 claims abstract description 54

- 239000012495 reaction gas Substances 0.000 claims abstract description 53

- 239000010409 thin film Substances 0.000 claims abstract description 49

- 238000010926 purge Methods 0.000 claims abstract description 47

- 238000009832 plasma treatment Methods 0.000 claims description 10

- 238000000151 deposition Methods 0.000 abstract description 18

- 230000008021 deposition Effects 0.000 abstract description 11

- 229910052751 metal Inorganic materials 0.000 abstract description 11

- 239000002184 metal Substances 0.000 abstract description 11

- 230000006866 deterioration Effects 0.000 abstract description 3

- 239000010408 film Substances 0.000 description 43

- 238000003860 storage Methods 0.000 description 37

- 230000008569 process Effects 0.000 description 33

- 238000000231 atomic layer deposition Methods 0.000 description 27

- 238000005229 chemical vapour deposition Methods 0.000 description 18

- 238000006243 chemical reaction Methods 0.000 description 11

- 239000003990 capacitor Substances 0.000 description 10

- 239000010410 layer Substances 0.000 description 10

- 238000004519 manufacturing process Methods 0.000 description 7

- 229910052760 oxygen Inorganic materials 0.000 description 7

- 238000010586 diagram Methods 0.000 description 6

- 238000005516 engineering process Methods 0.000 description 6

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 5

- 125000004122 cyclic group Chemical group 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 239000012535 impurity Substances 0.000 description 5

- 239000000463 material Substances 0.000 description 5

- 239000000126 substance Substances 0.000 description 5

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 4

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 4

- 239000001301 oxygen Substances 0.000 description 4

- 239000000376 reactant Substances 0.000 description 4

- 239000004065 semiconductor Substances 0.000 description 4

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 3

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 3

- 238000010521 absorption reaction Methods 0.000 description 3

- 238000000137 annealing Methods 0.000 description 3

- 239000011229 interlayer Substances 0.000 description 3

- 238000011068 loading method Methods 0.000 description 3

- 239000000758 substrate Substances 0.000 description 3

- 238000006557 surface reaction Methods 0.000 description 3

- 229910021341 titanium silicide Inorganic materials 0.000 description 3

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 2

- 230000002776 aggregation Effects 0.000 description 2

- 230000004888 barrier function Effects 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- 238000000280 densification Methods 0.000 description 2

- -1 hydogen Chemical compound 0.000 description 2

- 239000011261 inert gas Substances 0.000 description 2

- 229910052741 iridium Inorganic materials 0.000 description 2

- 238000002955 isolation Methods 0.000 description 2

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 2

- 230000007246 mechanism Effects 0.000 description 2

- 229910052757 nitrogen Inorganic materials 0.000 description 2

- 239000002245 particle Substances 0.000 description 2

- 229920002120 photoresistant polymer Polymers 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 238000000926 separation method Methods 0.000 description 2

- 239000010936 titanium Substances 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- DIIIISSCIXVANO-UHFFFAOYSA-N 1,2-Dimethylhydrazine Chemical compound CNNC DIIIISSCIXVANO-UHFFFAOYSA-N 0.000 description 1

- 229910015801 BaSrTiO Inorganic materials 0.000 description 1

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- 229910021193 La 2 O 3 Inorganic materials 0.000 description 1

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 229910002367 SrTiO Inorganic materials 0.000 description 1

- 229910010413 TiO 2 Inorganic materials 0.000 description 1

- 239000003082 abrasive agent Substances 0.000 description 1

- 238000005054 agglomeration Methods 0.000 description 1

- 238000004220 aggregation Methods 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- 239000005380 borophosphosilicate glass Substances 0.000 description 1

- 239000006227 byproduct Substances 0.000 description 1

- 238000005137 deposition process Methods 0.000 description 1

- 238000011049 filling Methods 0.000 description 1

- 238000010574 gas phase reaction Methods 0.000 description 1

- 229910052735 hafnium Inorganic materials 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- QPJSUIGXIBEQAC-UHFFFAOYSA-N n-(2,4-dichloro-5-propan-2-yloxyphenyl)acetamide Chemical compound CC(C)OC1=CC(NC(C)=O)=C(Cl)C=C1Cl QPJSUIGXIBEQAC-UHFFFAOYSA-N 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 229910052703 rhodium Inorganic materials 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000011232 storage material Substances 0.000 description 1

- 238000000427 thin-film deposition Methods 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/455—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating characterised by the method used for introducing gases into reaction chamber or for modifying gas flows in reaction chamber

- C23C16/45523—Pulsed gas flow or change of composition over time

- C23C16/45525—Atomic layer deposition [ALD]

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/455—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating characterised by the method used for introducing gases into reaction chamber or for modifying gas flows in reaction chamber

- C23C16/45523—Pulsed gas flow or change of composition over time

- C23C16/45525—Atomic layer deposition [ALD]

- C23C16/45527—Atomic layer deposition [ALD] characterized by the ALD cycle, e.g. different flows or temperatures during half-reactions, unusual pulsing sequence, use of precursor mixtures or auxiliary reactants or activations

-

- A—HUMAN NECESSITIES

- A45—HAND OR TRAVELLING ARTICLES

- A45D—HAIRDRESSING OR SHAVING EQUIPMENT; EQUIPMENT FOR COSMETICS OR COSMETIC TREATMENTS, e.g. FOR MANICURING OR PEDICURING

- A45D40/00—Casings or accessories specially adapted for storing or handling solid or pasty toiletry or cosmetic substances, e.g. shaving soaps or lipsticks

- A45D40/24—Casings for two or more cosmetics

-

- A—HUMAN NECESSITIES

- A45—HAND OR TRAVELLING ARTICLES

- A45D—HAIRDRESSING OR SHAVING EQUIPMENT; EQUIPMENT FOR COSMETICS OR COSMETIC TREATMENTS, e.g. FOR MANICURING OR PEDICURING

- A45D33/00—Containers or accessories specially adapted for handling powdery toiletry or cosmetic substances

- A45D33/006—Vanity boxes or cases, compacts, i.e. containing a powder receptacle and a puff or applicator

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/455—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating characterised by the method used for introducing gases into reaction chamber or for modifying gas flows in reaction chamber

- C23C16/45523—Pulsed gas flow or change of composition over time

- C23C16/45525—Atomic layer deposition [ALD]

- C23C16/45527—Atomic layer deposition [ALD] characterized by the ALD cycle, e.g. different flows or temperatures during half-reactions, unusual pulsing sequence, use of precursor mixtures or auxiliary reactants or activations

- C23C16/45536—Use of plasma, radiation or electromagnetic fields

- C23C16/45542—Plasma being used non-continuously during the ALD reactions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02263—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase

- H01L21/02271—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition

- H01L21/0228—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition deposition by cyclic CVD, e.g. ALD, ALE, pulsed CVD

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/285—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation

- H01L21/28506—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers

- H01L21/28512—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table

- H01L21/28556—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table by chemical means, e.g. CVD, LPCVD, PECVD, laser CVD

- H01L21/28562—Selective deposition

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/314—Inorganic layers

- H01L21/3141—Deposition using atomic layer deposition techniques [ALD]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L28/00—Passive two-terminal components without a potential-jump or surface barrier for integrated circuits; Details thereof; Multistep manufacturing processes therefor

- H01L28/40—Capacitors

- H01L28/60—Electrodes

- H01L28/65—Electrodes comprising a noble metal or a noble metal oxide, e.g. platinum (Pt), ruthenium (Ru), ruthenium dioxide (RuO2), iridium (Ir), iridium dioxide (IrO2)

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L28/00—Passive two-terminal components without a potential-jump or surface barrier for integrated circuits; Details thereof; Multistep manufacturing processes therefor

- H01L28/40—Capacitors

- H01L28/60—Electrodes

- H01L28/82—Electrodes with an enlarged surface, e.g. formed by texturisation

- H01L28/90—Electrodes with an enlarged surface, e.g. formed by texturisation having vertical extensions

- H01L28/91—Electrodes with an enlarged surface, e.g. formed by texturisation having vertical extensions made by depositing layers, e.g. by depositing alternating conductive and insulating layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B53/00—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B53/00—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors

- H10B53/30—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors characterised by the memory core region

-

- A—HUMAN NECESSITIES

- A45—HAND OR TRAVELLING ARTICLES

- A45D—HAIRDRESSING OR SHAVING EQUIPMENT; EQUIPMENT FOR COSMETICS OR COSMETIC TREATMENTS, e.g. FOR MANICURING OR PEDICURING

- A45D33/00—Containers or accessories specially adapted for handling powdery toiletry or cosmetic substances

- A45D2033/001—Accessories

-

- A—HUMAN NECESSITIES

- A45—HAND OR TRAVELLING ARTICLES

- A45D—HAIRDRESSING OR SHAVING EQUIPMENT; EQUIPMENT FOR COSMETICS OR COSMETIC TREATMENTS, e.g. FOR MANICURING OR PEDICURING

- A45D40/00—Casings or accessories specially adapted for storing or handling solid or pasty toiletry or cosmetic substances, e.g. shaving soaps or lipsticks

- A45D2040/0006—Accessories

-

- A—HUMAN NECESSITIES

- A45—HAND OR TRAVELLING ARTICLES

- A45D—HAIRDRESSING OR SHAVING EQUIPMENT; EQUIPMENT FOR COSMETICS OR COSMETIC TREATMENTS, e.g. FOR MANICURING OR PEDICURING

- A45D2200/00—Details not otherwise provided for in A45D

- A45D2200/05—Details of containers

- A45D2200/058—Means for mixing different substances prior to application

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/31—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor

- H10B12/318—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor the storage electrode having multiple segments

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Manufacturing & Machinery (AREA)

- Physics & Mathematics (AREA)

- Mechanical Engineering (AREA)

- Materials Engineering (AREA)

- Metallurgy (AREA)

- Organic Chemistry (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Electromagnetism (AREA)

- Plasma & Fusion (AREA)

- Semiconductor Memories (AREA)

- Chemical Vapour Deposition (AREA)

Abstract

본 발명은 박막의 증착율을 개선하고 박막의 특성 열화를 방지하는데 적합한 박막의 증착 방법을 제공하기 위한 것으로, 이를 위한 본 발명의 박막 형성 방법은 소정의 피딩 순서를 한 싸이클로하여 상기 싸이클을 반복 수행하므로써 원하는 박막을 증착하며, 상기 한 싸이클의 피딩 순서는, 소스가스와 반응가스를 동시에 공급하는 제 1 단계; 상기 소스가스와 반응가스의 공급 없이 퍼지가스를 공급하는 제 2 단계; 상기 소스가스와 퍼지가스의 공급 없이 상기 반응가스를 공급하는 제 3 단계; 및 상기 소스가스와 반응가스의 공급 없이 퍼지가스를 공급하는 제 4 단계를 포함한다.

메탈 스토리지노드, ALD, PEALD, CVD, 플라즈마

Description

도 1은 일반적인 원자층 증착법(ALD)의 피딩(feeding) 순서를 나타낸 모식도,

도 2a 및 도 2b는 일반적인 플라즈마 원자층 증착법(PEALD)의 피딩 순서를 나타낸 모식도,

도 3은 플라즈마 처리를 1 싸이클 내에 추가한 원자층 증착 또는 플라즈마 원자층 증착법의 피딩 순서를 나타낸 모식도,

도 4 내지 도 7은 본 발명의 다양한 실시예에 따른 박막의 증착 방법을 설명하기 위한 모식도,

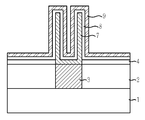

도 8a 내지 도 8e는 본 발명의 박막 증착 방법을 적용한 캐패시터 제조 방법을 나타낸 공정 단면도.

* 도면의 주요 부분에 대한 부호의 설명

1 : 반도체 기판 2 : 층간절연막

3 : 스토리지노드콘택플러그 4 : 식각정지막

5 : SN 산화막 6 : 스토리지노드콘택홀

7 : 스토리지노드 8 : 유전막

9 : 플레이트 전극

본 발명은 반도체 제조 기술에 관한 것으로, 특히 원자층 증착(Atomic Layer Deposition; ALD)을 이용한 박막의 형성 및 그를 이용한 캐패시터의 제조 방법에 관한 것이다.

최근 DRAM의 집적도가 증가함에 따라서 캐패시터의 면적이 작아지게 되어 요구되는 유전용량의 확보가 점점 어려워지게 되었다. 요구되는 유전용량을 확보하기 위해서는 유전박막의 두께를 낮추거나 유전상수가 큰 물질을 적용하여야 한다.

80nm 테크놀로지 이하의 DRAM에서는 누설전류 특성을 확보하면서 유전용량을 확보하기 위하여 HfO2와 Al2O3를 적층하여 적용하는 기술이 개발되고 있다. 이러한 유전막 구조에서는 유전용량을 확보하는데 있어서 콘케이브(Concave) 구조로는 한계에 다다르고 있으며, 실린더(Cylinder) 구조를 적용하여 캐패시터의 면적을 확보해야 한다.

그러나, 스토리지노드로 TiN을 사용하여 실린더 구조를 만든다 하더라도, 유전막의 유효 두께는 11Å 정도가 한계이며, 65nm 테크놀로지 이하급 소자에서는 유 전 용량을 확보하기 위해서는 10Å 이하의 유효 유전막 두께가 필요하다. 이를 위해서는 Ru, Pr, Ir 등의 메탈 전극의 도입이 필수적이다.

스토리지노드로 메탈 전극을 사용하려면 막의 밀도가 높아 후속 공정에서 응집(agglomeration)이 일어나지 않아야하고, 스텝 커버리지(Step Coverage)가 80% 이상이 되어야 한다.

종래의 CVD(Chemical Vapor Deposition) 방식을 사용하여 메탈 스토리지노드로 Ru를 적용한 경우 박막 내 불순물(carbon, hydogen, oxygen)이 많이 포함되어 있고, 밀도가 낮아(~ 7 g/cm3, bulk Ru의 경우 12.2, PVD Ru의 경우 ~11.9) 후속 공정에서 응집 현상에 의해서 안정한 캐패시턴스를 유지할 수 없는 단점이 있었다. 스텝 커버리지 관점에서도 65nm 테크놀로지 이하의 소자에서는 스토리지노드를 형성하기 위한 콘택의 선폭(CD)이 100nm 이하, 종횡비(Aspect Ratio) 20:1 이상의 어려운 조건이 예상된다.

이러한 높은 종횡비를 갖는 콘택에서 스텝 커버리지를 극복하고 불순물이 거의 없는 메탈을 증착하기 위해, 표면 반응을 이용한 ALD 공정이 적용되고 있다.

도 1은 일반적인 ALD 공정의 피딩(feeding) 순서를 나타낸 모식도이다.

도 1에 도시된 바와 같이, ALD는 자기 표면 반응 제한 메카니즘(Self-surface reaction limited mechanism)을 이용한다.

먼저, 제 1단계에서 챔버 내에 웨이퍼를 로딩(loading)시킨 후 챔버 내에 소스가스를 공급(Feeding)하여 웨이퍼 표면에 소스가스의 화학 흡착(Chemical absorption)을 유도하고, 제 2단계인 퍼지 스텝(Purge step)에서 퍼지가스를 주입하여(예컨대 불활성 가스(inert gas)) 여분의 미흡착/반응한 소스가스 혹은 반응 부가물을 제거한다.

이어서, 제 3단계에서 반응가스를 공급하여 웨이퍼 표면에 화학 흡착된 물질과 반응을 유도하여 원자층을 증착하는 과정을 수행한다. 계속해서, 제 4단계로 다시 퍼지가스를 공급하여 여분의 반응가스 및 반응 부가물을 배출시키는 과정을 수행한다.

상술한 네 단계의 과정들을 1 싸이클로 하여 싸이클을 반복 진행하므로써, 원하는 두께의 박막을 증착한다.

ALD 공정은 표면 반응 제한 방법을 이용하기 때문에 원자층 단위로 박막의 두께 제어가 가능하고, 하지막의 토폴로지(topology)에 무관하게 증착 가능하여 컨포멀(conformal)하고 균일(uniformity)한 박막을 얻을 수 있다. 뿐만 아니라, 소스가스와 반응가스를 불활성가스로 서로 분리하여 챔버에 공급하기 때문에 CVD 공정에 비하여 가스 위상 반응(gas phase reaction)에 의한 파티클 생성을 억제할 수 있다. 또한, 소스가스와 웨이퍼의 다중 충돌에 의해 소스가스의 사용 효율을 개선시키고 주기를 줄일 수 있다.

도 2a 및 도 2b는 플라즈마 원자층 증착법(Plasma Enhanced Atomic Layer Deposition; PEALD)을 나타낸 그래프이다.

도 2a에 도시된 바와 같이, 먼저, 제 1단계에서 챔버 내에 웨이퍼를 로딩(loading)시킨 후 챔버 내에 소스가스를 공급(Feeding)하여 웨이퍼 표면에 소스가 스의 화학 흡착(Chemical absorption)을 유도하고, 제 2단계인 퍼지 스텝에서 퍼지가스를 주입하여 여분의 미흡착/반응한 소스가스 혹은 반응 부가물을 제거한다.

계속해서, 제 3단계에서 반응가스를 공급하여 웨이퍼 표면에 화학 흡착된 물질과 반응을 유도하여 박막을 증착하는 과정을 수행한다. 이 때, 반응가스를 공급하는 싸이클에 플라즈마를 인가 하는 것을 특징으로 한다. 이어서, 제 4단계로서, 퍼지가스를 공급하여 여분의 반응가스 및 반응 부가물을 배출시키는 과정을 수행하여 1 싸이클을 완료한다.

이어서, 도 2b는 PEALD 공정을 실시하는 중 반응가스와 소스가스가 반응성이 없는 경우에는 퍼지가스 대신 반응가스를 공급하며, 반응시키고자 하는 시간에 플라즈마를 공급하는 방법을 나타낸 것이다.

도 2b에 도시한 방법은 도 2a에 도시된 방법에 비해 퍼지에 들어가는 시간을 단축할 수 있다.

도 3은 ALD 공정 또는 PEALD 공정의 1 싸이클 마지막 단계로서, 플라즈마 처리를 실시하는 방법을 나타낸 것이다.

도 3에 도시된 바와 같이, 먼저, 제 1단계에서 챔버 내에 웨이퍼를 로딩(loading)시킨 후 챔버 내에 소스가스를 공급(Feeding)하여 웨이퍼 표면에 소스가스의 화학 흡착(Chemical absorption)을 유도한다.

이어서 2 단계로서, 퍼지가스를 주입하여 퍼지를 실시하고 계속해서 제 3단계로서 반응가스를 공급하여 웨이퍼 표면에 화학 흡착된 물질과 반응을 유도하여 박막을 증착하는 과정을 수행한다. 반응가스를 공급할 때, 플라즈마를 동시에 인가 할 수 있다.

계속해서, 제 4단계로서 퍼지를 수행한 후, 제 5단계로서 플라즈마 처리용 가스를 주입하는 단계를 진행한다. 플라즈마 처리는 불순물 없는 순수한 막을 얻고, 스텝 커버리지를 향상시키기 위한 것이다. NH3, H2 등의 가스를 이용하여 진행하고 C, O등을 제거하고 표면 막질의 개선을 목적으로 한다.

상술한 바와 같은 플라즈마 처리를 부가한 ALD 공정은 막질 개선의 효과가 있지만, 1 싸이클이 길어지므로 박막의 증착율이 늦어지는 단점이 발생한다.

상술한 바와 같이, ALD 공정 또는 PEALD 공정은 소스가스, 퍼지가스, 반응가스를 교대로 공급하여 박막을 증착하는방법으로써, 고종횡비를 갖고 저압에서도 균일하게 박막을 형성할 수 있다.

현재 ALD 공정의 경우 원하는 스텝 커버리지를 얻기 위하여 플라즈마를 이용한 PEALD(Plasma Enhanced Atomic Layer Deposition; 'PEALD')를 사용하거나 증착 싸이클 내에 수소나 NH3 플라즈마를 사용하여 남아있는 불순물을 제거하는 공정이 도입되고 있다.

이러한 ALD 공정은 현재 싸이클 당 증착율은 0.5Å~1Å 수준이며 한 싸이클당 소요시간도 1~10초 정도로 분당 6Å 내외의 증착 속도를 보이고 있으며, 싱글 웨이퍼 타입 기준으로 보면 Ru를 200Å 두께로 증착할 경우 1 시간당 2장을 증착하기 어렵다는 단점이 있고 이는 양산성(Throughput) 관점에서 심각한 문제가 될 것으로 판단된다.

본 발명은 상기한 종래 기술의 문제점을 해결하기 위해 제안된 것으로, 박막의 증착율을 개선하고 박막의 특성 열화를 방지하는데 적합한 박막의 증착 방법을 제공하는데 그 목적이 있다.

상기 목적을 달성하기 위한 일 특징적인 본 발명의 박막의 형성 방법은 소정의 피딩 순서를 한 싸이클로하여 상기 싸이클을 반복 수행하므로써 원하는 박막을 증착하며, 상기 한 싸이클의 피딩 순서는, 소스가스와 반응가스를 동시에 공급하는 제 1 단계, 상기 소스가스와 반응가스의 공급 없이 퍼지가스를 공급하는 제 2 단계, 상기 소스가스와 퍼지가스의 공급 없이 상기 반응가스를 공급하는 제 3 단계, 및 상기 소스가스와 반응가스의 공급 없이 퍼지가스를 공급하는 제 4 단계를 포함한다.

또한, 본 발명은 소정의 피딩 순서를 한 싸이클로하여 상기 싸이클을 반복 수행하므로써 원하는 박막을 증착하며, 상기 한 싸이클의 피딩 순서는, 퍼지가스를 지속적으로 공급하면서, 반응가스 없이 소스가스를 공급하는 제 1 단계와, 소스가스 없이 반응가스를 공급하는 제 2 단계를 포함하며, 상기 반복 수행되는 매 싸이클의 마지막 단계로서, 증착된 박막을 플라즈마 처리하는 단계를 포함한다.

또한, 본 발명은 소정의 피딩순서를 한 싸이클로하여 상기 싸이클을 반복 수행하므로써 원하는 박막을 증착하며, 상기 한 싸이클의 피딩 순서는, 소스가스, 반응가스 및 퍼지가스가 공급되는 제 1 단계, 및 소스가스의 공급 없이 반응가스 및 퍼지가스를 공급하는 제 2 단계를 포함한다.

또한, 본 발명은 소정의 피딩 순서를 한 싸이클로하여 상기 싸이클을 반복 수행하므로써 원하는 박막을 증착하며, 상기 한 싸이클의 피딩 순서는, 소스가스, 반응가스 및 퍼지가스가 공급되는 제 1 단계, 및 반응가스의 공급 없이 소스가스 및 퍼지가스를 공급하는 제 2 단계를 포함한다.

이하, 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자가 본 발명의 기술적 사상을 용이하게 실시할 수 있을 정도로 상세히 설명하기 위하여, 본 발명의 가장 바람직한 실시예를 첨부 도면을 참조하여 설명하기로 한다.

도 4는 본 발명의 제 1실시예에 따른 박막 증착 방법에서의 피딩(feeding) 순서를 나타낸 모식도로서, 주기적 CVD(Cyclic CVD) 메카니즘을 이용한 것이다.

도 4에 도시된 바와 같이, 제 1단계로서 챔버 내에 웨이퍼를 로딩시킨 후 챔버 내에 소스가스와 반응가스를 동시에 공급한다. 소스가스와 반응가스가 동시에 공급되는 짧은 시간 동안 CVD 반응이 일어나므로 박막의 증착율이 증가된다.

계속해서 제 2단계로서 소스가스와 반응가스 공급을 멈추고 퍼지가스를 주입하여 여분의 반응 부산물을 제거한다. 이어서, 반응가스만 공급하는 제 3단계를 수행하며 이 때 어닐링(annealing) 효과에 의해서 박막이 치밀화된다

이후, 제 4단계로서 다시 퍼지를 수행한다.

이와 같이, 제 1단계 내지 제 4단계에 의해 1 싸이클이 진행되며, 이러한 싸이클을 반복 진행하므로써, 원하는 두께의 박막을 증착한다.

도 5는 본 발명의 제 2실시예에 따른 박막 증착 방법에서의 피딩 순서를 나타낸 모식도로서, ALD 공정 또는 PEALD 공정의 공급 시간을 변형한 방법을 이용한 것이다.

도 5에 도시된 바와 같이, 먼저, 챔버 내에 웨이퍼를 로딩시킨 후 제 1단계로서 챔버 내에 소스가스와 퍼지가스를 동시에 공급하고, 제 2단계로서 퍼지가스는 계속 공급하고 소스가스의 공급은 멈춘 상태에서, 반응가스를 공급한다. 반응가스의 공급시 플라즈마를 인가할 수 있다. 도 5에 도시된 실시예는 상술한 제 1단계 및 제 2단계에 의해서 1 싸이클이 진행되는바, 일반적인 ALD 공정과 달리 퍼지를 위한 스텝을 따로 마련하지 않고 반응이 진행되는 동안 퍼지를 지속적으로 진행한다.

여기서, 퍼지 스텝이 생략되었기 때문에 CVD 또는 PECVD가 부분적으로 일어날 수 있고, 싸이클이 짧아지고 CVD가 부분적으로 적용되었기 때문에 박막 증착 속도가 향상된다.

도 6은 본 발명의 제 3실시예에 따른 박막 증착 방법에서의 피딩 순서를 나타낸 것으로, 역시 주기적 CVD 공정(Cyclic CVD)을 이용한 것이다.

도 6에 도시된 바와 같이, 챔버 내에 웨이퍼를 로딩시킨 후, 소스가스만을 단속적으로 공급하고 퍼지가스와 반응가스는 지속적으로 공급하는 방식이다.

즉, 소스가스, 퍼지가스 및 반응가스가 한꺼번에 일정 시간 공급되는 제 1단계와, 소스가스 공급을 멈추고 퍼지가스와 반응가스가 동시에 일정 시간 공급되는 제 2단계에 의해 1 싸이클이 이루어진다.

반응가스와 소스가스가 동시에 공급되는 동안 CVD가 일어나고, 반응가스만 공급할 때 어닐링 효과를 기대하여 박막의 치밀화 및 박막대비 우수한 막 특성을 얻을 수 있다. 퍼지 스텝은 소스가스와 반응가스가 공급되는 시점부터 계속 진행된다.

상술한 과정들을 1 싸이클로 하여 반복 진행하므로써, 원하는 두께의 박막을 증착한다.

도 7은 본 발명의 제 4실시예에 따른 박막 증착 방법에서의 피딩 순서를 나타낸 것으로, 역시 주기적 CVD 공정(Cyclic CVD)을 이용한다.

도 7에 도시된 바와 같이, 챔버 내에 웨이퍼를 로딩시킨 후, 반응가스만을 단속적으로 공급하고, 퍼지가스와 공급가스는 지속적으로 공급하는 방식이다.

즉, 소스가스, 퍼지가스 및 반응가스가 한꺼번에 일정 시간 공급되는 제 1 단계와, 반응가스 공급을 멈추고 퍼지가스와 공급가스가 동시에 일정 시간 공급되는 제 2단계에 의해 1 싸이클이 이루어진다.

소스가스와 반응가스가 동시에 공급되는 동안 CVD가 일어나고, 반응가스만 공급될 때 어닐링 효과를 기대하여 박막의 치밀화 및 박막 대비 우수한 막 특성을 얻을 수 있다. 퍼지 스텝은 소스가스와 반응가스가 공급되는 시점부터 계속 진행된다.

상술한 과정들을 1 싸이클로 하여 반복 진행하므로써, 원하는 두께의 박막을 증착한다.

한편, 상술한 제 1내지 제 4 실시예에서, 매 싸이클마다 마지막 단계로서 막 질 개선을 위한 플라즈마 처리 단계를 부가할 수 있다. 플라즈마 처리시에는 그 반응가스로서 O2, NH3, H2O, N2H4(하드라진), Me2N2H2(디메틸하드라진), H2 및 이들의 혼합가스를 사용한다. 또한, 플라즈마 파워는 10W∼1500W를 갖는다.

또한, 플라즈마 처리 단계는 매 싸이클마다 실시하지 않고, 수∼수십 싸이클마다 한번 씩 실시할 수도 있다.

도 8a 내지 도 8e는 상기 도 4∼도 7에서 설명한 박막 증착 방법을 적용한 캐패시터 제조 방법을 나타낸 공정 단면도이다.

도 8a에 도시된 바와 같이, 반도체 기판(1) 상부에 층간절연막(2)을 형성한 후, 층간절연막(2)을 관통하여 반도체 기판(1)의 일부와 연결되는 스토리지노드콘택플러그(3)를 형성한다. 이 때, 스토리지노드콘택플러그(3)를 에치 백하여 일정 깊이로 리세스(recess) 시키고, 티타늄실리사이드(a), 티타늄나이트라이드(b)를 적층 형성하고 화학적 기계적 연마(Chemical Mechanical Polishing; CMP)를 진행한다.

이 때, 스토리지노드콘택플러그(3)로 폴리실리콘플러그(Poly Plug)를 사용할 경우, 티타늄실리사이드(a)를 형성하고, 텅스텐 플러그(W Plug)를 사용할 경우, 티타늄실리사이드(a)는 생략 가능하다. 또한, 티타늄나이트라이드를 플러그로 사용할 수 있고, 본 실시예에서는 티타늄나이트라이드플러그(TiN Plug)를 적용한다.

한편, 스토리지노드콘택플러그(3) 형성 전에 소자분리, 워드라인 및 비트라인 등의 DRAM 구성에 필요한 공정이 진행된다.

다음으로, 스토리지노드콘택플러그(3) 상부에 식각정지막(4)과 SN 산화막(5)을 적층 형성한다. 여기서, SN 산화막(5)은 실린더 구조의 스토리지노드가 형성될 홀을 제공하기 위한 산화막이고, 식각정지막(4)은 SN 산화막(5) 식각시 하부구조물이 식각되는 것을 방지하기 위한 식각베리어 역할을 한다. 바람직하게 식각정지막(5)은 저압화학기상증착법(LPCVD)의 실리콘산화막(Si3N4)으로 형성하며, SN 산화막(5)은 BPSG, USG, PETEOS 또는 HDP 산화막으로 형성한다.

다음으로, SN 산화막(5)과 식각정지막(4)을 순차적으로 식각하여 스토리지노드콘택플러그(3) 상부를 노출시키는 스토리지노드홀(6)을 형성한다.

이어서, 도 8b에 도시된 바와 같이, 스토리지노드홀(6)을 포함하는 SN 산화막(5) 표면 상에 스토리지노드(7)를 형성한다. 스토리지노드는 도 4∼도 7을 통해서 설명한 ALD와 CVD의 혼합 방식 또는 주기성이 있는 CVD를 사용하여 형성한다.

이는 스토리지노드(7)의 증착 속도를 향상시키면서, 스텝 커버리지특성을 강화시킬 수 있기 때문이다. 스토리지노드(7)를 위한 전도성 박막으로 Ru, Pt, Ir, Rh, Pd, Hf, Ti, W 또는 Ta 중에서 선택된 금속막 또는 RuO2 또는 IrO2 중에서 선택된 전도성 금속 산화막으로 형성한다.

스토리지노드용 전극으로서 상기한 박막들을 형성할 때, 소스가스로는 상기 금속의 소스가스를 사용하며, 반응가스로는 O2, NH3, N2O, N2H4(하드라진), Me2N2H2(디메틸히드라진), H2 및 이들의 혼합가스를 사용한다.

이어서, 도 8c에 도시된 바와 같이, 스토리지노드홀(6)의 내부에만 실린더형 스토리지노드(7)를 형성하는 스토리지노드 분리(Storage Node Isolation) 공정을 진행한다.

스토리지노드 분리 공정은, 스토리지노드홀(6)을 제외한 SN 산화막(5) 표면 상부에 형성된 스토리지노드를 CMP 또는 에치백으로 제거하여 실린더형 스토리지노드(7)를 형성하는 것이다. 여기서, CMP 또는 에치백 공정시에 연마재나 식각된 입자 등의 불순물이 스토리지노드(7) 내부에 부착되는 등의 우려가 있으므로, 스텝 커버리지 특성이 좋은 포토레지스트로 스토리지노드홀(6)의 내부를 모두 채운 후에, SN 산화막이 노출될 때까지 연마 또는 에치백을 수행하고, 포토레지스트를 애싱(Ashing)하여 제거하는 것이 좋다.

한편, 스토리지노드 분리 공정이 끝난 후, SN 산화막(5) 상에 유전막을 증착하면 콘케이브 구조이고, SN 산화막(5)을 제거한 후 유전막을 증착하면 실린더형 구조로서, 본 실시예에서는 실린더형 구조를 예로 들어 설명한다.

이어서, 도 8d에 도시된 바와 같이, SN 산화막(5)을 선택적으로 습식 딥아웃하여 스토리지노드(7)의 내벽 및 외벽을 모두 드러낸다.

이 때, 습식 딥아웃 공정은 주로 불산(HF) 용액을 이용하여 실시하는데, 산화막으로 형성한 SN 산화막(5)이 불산용액에 의해 식각된다. 한편, SN 산화막(5) 아래의 식각정지막(4)은 산화막의 습식 식각시 선택비를 갖는 실리콘질화막으로 형성했기 때문에 습식 케미컬에 의해 식각되지 않는다.

이어서, 도 8e에 도시된 바와 같이, 스토리지노드(7) 상에 유전막(8)과 플레이트 전극(9)을 차례로 형성한다. 유전막(8)은 스퍼터링법, CVD, ALD를 이용하여 형성하고, 후처리를 위한 분위기로 산소, 오존, 산소 플라즈마를 사용한다. 이 때, 오존 또는 산소 플라즈마를 사용할 경우 200℃∼500℃의 온도 범위를 갖는다.

계속해서, 유전막(8)은 HfO2, Al2O3, ZrO2, La2O3, Ta2O5, TiO2, BST(BaSrTiO3), SrTiO3, PZT, BLT, SPT, Bi2Ti2O7 단독 또는 복층막으로 형성한다. 복층막은 HfO2/Al2O3, HfO2/Al2O3/HfO2 등 가능한 조합을 갖는 모든 경우를 사용한다.

이어서, 유전막(8) 상에 플레이트 전극(9)은 스토리지물질과 동일한 물질, As, P등을 도핑하여 전도성을 갖는 도핑된 실리콘 또는 TiN과 같은 전도성 박막 중에서 선택한 금속막을 ALD, CVD, PEALD 또는 스토리지노드를 형성한 방법 중에서 선택된 방법을 이용하여 형성한다.

상술한 바와 같이 본 발명은 스토리지노드의 낮은 증착율을 개선하기 위하여 ALD 공정 또는 PEALD 공정에 대하여 소스가스, 반응가스 및 퍼지가스의 공급 주기를 조절하여 박막의 특성 열화를 최소화하며 증착 속도를 향상시킬 수 있다.

본 발명은 DRAM 캐패시터의 저장 전극 제조 뿐만 아니라, 게이트 전극, 베리어메탈, 3차원 구조를 적용하는 고밀도 FeRAM의 강유전 캐패시터의 전극 제조 등 메탈 ALD 공정에 대체 적용할 수 있다.

본 발명의 기술 사상은 상기 바람직한 실시예에 따라 구체적으로 기술되었으나, 상기한 실시예는 그 설명을 위한 것이며 그 제한을 위한 것이 아님을 주의하여야 한다. 또한, 본 발명의 기술 분야의 통상의 전문가라면 본 발명의 기술 사상의 범위 내에서 다양한 실시예가 가능함을 이해할 수 있을 것이다.

상술한 본 발명은, 일반적인 ALD 공정과 CVD 공정의 소스가스, 반응가스의 공급 시간을 조절하므로써 ALD 공정과 PEALD 공정에 비해 단위싸이클의 주기가 짧아 빠른 증착 속도로 박막을 형성할 수 있고, 단위싸이클 동안 퍼지가 계속 진행되므로 순수한 박막을 얻을 수 있다.

또한, 65nm 테크놀로지 이하의 디자인 룰을 갖는 DRAM 소자의 캐패시터 제작시 메탈 스토리지노드 증착 공정의 양산성을 대폭적으로 개선할 수 있는 박막 형성기술로서 캐패시터를 안정적으로 제작할 수 있으며, 그에 따른 원가 절감 효과가 기대된다.

또한, 150nm 테크놀로지 이하의 디자인 룰을 갖는 FeRAM 소자의 캐패시터 제작시 하부전극 형성 공정으로 사용하여 강유전 특성 및 패티그 특성이 우수한 FeRAM을 제작할 수 있다.

Claims (7)

- 소정의 피딩 순서를 한 싸이클로하여 상기 싸이클을 반복 수행하므로써 원하는 박막을 증착하며,상기 한 싸이클의 피딩 순서는,소스가스와 반응가스를 동시에 공급하는 제 1 단계;상기 소스가스와 반응가스의 공급 없이 퍼지가스를 공급하는 제 2 단계;상기 소스가스와 퍼지가스의 공급 없이 상기 반응가스를 공급하는 제 3 단계; 및상기 소스가스와 반응가스의 공급 없이 퍼지가스를 공급하는 제 4 단계를 포함하는박막 증착 방법.

- 소정의 피딩 순서를 한 싸이클로하여 상기 싸이클을 반복 수행하므로써 원하는 박막을 증착하며,상기 한 싸이클의 피딩 순서는,퍼지가스를 지속적으로 공급하면서, 반응가스 없이 소스가스를 공급하는 제 1 단계와, 소스가스 없이 반응가스를 공급하는 제 2 단계를 포함하며, 상기 반복 수행되는 매 싸이클의 마지막 단계로서, 증착된 박막을 플라즈마 처리하는 단계를 포함하는 박막 증착 방법.

- 소정의 피딩 순서를 한 싸이클로하여 상기 싸이클을 반복 수행하므로써 원하는 박막을 증착하며,상기 한 싸이클의 피딩 순서는,소스가스, 반응가스 및 퍼지가스가 공급되는 제 1 단계; 및소스가스의 공급 없이 반응가스 및 퍼지가스를 공급하는 제 2 단계를 포함하는박막 증착 방법.

- 소정의 피딩 순서를 한 싸이클로하여 상기 싸이클을 반복 수행하므로써 원하는 박막을 증착하며,상기 한 싸이클의 피딩 순서는,소스가스, 반응가스 및 퍼지가스가 공급되는 제 1 단계; 및반응가스의 공급 없이 소스가스 및 퍼지가스를 공급하는 제 2 단계를 포함하는박막 증착 방법.

- 제1항, 제3항 및 제4항 중 어느 한 항에 있어서,상기 반복 수행되는 매 싸이클의 마지막 단계로서, 증착된 박막을 플라즈마 처리하는 단계를 더 포함하는 박막 증착 방법.

- 제1항 내지 제4항 중 어느 한 항에 있어서,상기 반복 수행되는 싸이클 중에서 수∼수십 싸이클 마다 한 번씩 증착된 박막을 플라즈마 처리하는 단계를 더 포함하는 박막 증착 방법.

- 제2항에 있어서,상기 소스가스 없이 반응가스를 공급하는 제2단계에서, 플라즈마를 인가하는 박막 증착 방법.

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020050012677A KR100622609B1 (ko) | 2005-02-16 | 2005-02-16 | 박막 형성 방법 |

| US11/321,538 US20060183301A1 (en) | 2005-02-16 | 2005-12-30 | Method for forming thin film |

| US12/365,316 US20090148625A1 (en) | 2005-02-16 | 2009-02-04 | Method for forming thin film |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020050012677A KR100622609B1 (ko) | 2005-02-16 | 2005-02-16 | 박막 형성 방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20060091908A KR20060091908A (ko) | 2006-08-22 |

| KR100622609B1 true KR100622609B1 (ko) | 2006-09-19 |

Family

ID=36816193

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020050012677A KR100622609B1 (ko) | 2005-02-16 | 2005-02-16 | 박막 형성 방법 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US20060183301A1 (ko) |

| KR (1) | KR100622609B1 (ko) |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2010095901A2 (en) * | 2009-02-23 | 2010-08-26 | Synos Technology, Inc. | Method for forming thin film using radicals generated by plasma |

| US8333839B2 (en) | 2007-12-27 | 2012-12-18 | Synos Technology, Inc. | Vapor deposition reactor |

| US8470718B2 (en) | 2008-08-13 | 2013-06-25 | Synos Technology, Inc. | Vapor deposition reactor for forming thin film |

| US8758512B2 (en) | 2009-06-08 | 2014-06-24 | Veeco Ald Inc. | Vapor deposition reactor and method for forming thin film |

| US8840958B2 (en) | 2011-02-14 | 2014-09-23 | Veeco Ald Inc. | Combined injection module for sequentially injecting source precursor and reactant precursor |

| US9506146B2 (en) | 2011-01-04 | 2016-11-29 | Wonik Ips Co., Ltd. | Thin film vapor deposition method and thin film vapor deposition apparatus |

| KR101741688B1 (ko) | 2011-12-26 | 2017-06-16 | 주식회사 원익아이피에스 | 박막 제조방법 및 그 제조장치 |

Families Citing this family (59)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7545031B2 (en) | 2005-04-11 | 2009-06-09 | Stats Chippac Ltd. | Multipackage module having stacked packages with asymmetrically arranged die and molding |

| US20070215987A1 (en) * | 2006-03-15 | 2007-09-20 | Schwerin Ulrike G | Method for forming a memory device and memory device |

| JP5018772B2 (ja) * | 2006-03-30 | 2012-09-05 | 富士通セミコンダクター株式会社 | 半導体装置の製造方法 |

| US20100037824A1 (en) * | 2008-08-13 | 2010-02-18 | Synos Technology, Inc. | Plasma Reactor Having Injector |

| US20100037820A1 (en) * | 2008-08-13 | 2010-02-18 | Synos Technology, Inc. | Vapor Deposition Reactor |

| US8851012B2 (en) * | 2008-09-17 | 2014-10-07 | Veeco Ald Inc. | Vapor deposition reactor using plasma and method for forming thin film using the same |

| US8770142B2 (en) * | 2008-09-17 | 2014-07-08 | Veeco Ald Inc. | Electrode for generating plasma and plasma generator |

| US8871628B2 (en) * | 2009-01-21 | 2014-10-28 | Veeco Ald Inc. | Electrode structure, device comprising the same and method for forming electrode structure |

| JP5787488B2 (ja) * | 2009-05-28 | 2015-09-30 | 株式会社日立国際電気 | 半導体装置の製造方法及び基板処理装置 |

| KR101025737B1 (ko) * | 2009-06-30 | 2011-04-04 | 주식회사 하이닉스반도체 | 캐패시터 제조 방법 |

| US20110076421A1 (en) * | 2009-09-30 | 2011-03-31 | Synos Technology, Inc. | Vapor deposition reactor for forming thin film on curved surface |

| KR101211043B1 (ko) * | 2010-04-05 | 2012-12-12 | 에스케이하이닉스 주식회사 | 매립게이트를 구비한 반도체 장치 제조방법 |

| US20110256734A1 (en) | 2010-04-15 | 2011-10-20 | Hausmann Dennis M | Silicon nitride films and methods |

| US9892917B2 (en) | 2010-04-15 | 2018-02-13 | Lam Research Corporation | Plasma assisted atomic layer deposition of multi-layer films for patterning applications |

| US8956983B2 (en) | 2010-04-15 | 2015-02-17 | Novellus Systems, Inc. | Conformal doping via plasma activated atomic layer deposition and conformal film deposition |

| US9076646B2 (en) | 2010-04-15 | 2015-07-07 | Lam Research Corporation | Plasma enhanced atomic layer deposition with pulsed plasma exposure |

| US9287113B2 (en) | 2012-11-08 | 2016-03-15 | Novellus Systems, Inc. | Methods for depositing films on sensitive substrates |

| US9997357B2 (en) | 2010-04-15 | 2018-06-12 | Lam Research Corporation | Capped ALD films for doping fin-shaped channel regions of 3-D IC transistors |

| US9257274B2 (en) | 2010-04-15 | 2016-02-09 | Lam Research Corporation | Gapfill of variable aspect ratio features with a composite PEALD and PECVD method |

| US9373500B2 (en) | 2014-02-21 | 2016-06-21 | Lam Research Corporation | Plasma assisted atomic layer deposition titanium oxide for conformal encapsulation and gapfill applications |

| US9611544B2 (en) | 2010-04-15 | 2017-04-04 | Novellus Systems, Inc. | Plasma activated conformal dielectric film deposition |

| US8637411B2 (en) | 2010-04-15 | 2014-01-28 | Novellus Systems, Inc. | Plasma activated conformal dielectric film deposition |

| US9390909B2 (en) | 2013-11-07 | 2016-07-12 | Novellus Systems, Inc. | Soft landing nanolaminates for advanced patterning |

| US9685320B2 (en) | 2010-09-23 | 2017-06-20 | Lam Research Corporation | Methods for depositing silicon oxide |

| US8524612B2 (en) | 2010-09-23 | 2013-09-03 | Novellus Systems, Inc. | Plasma-activated deposition of conformal films |

| US8771791B2 (en) | 2010-10-18 | 2014-07-08 | Veeco Ald Inc. | Deposition of layer using depositing apparatus with reciprocating susceptor |

| KR101804127B1 (ko) * | 2011-01-28 | 2018-01-10 | 주식회사 원익아이피에스 | 박막 증착 방법 |

| US8877300B2 (en) | 2011-02-16 | 2014-11-04 | Veeco Ald Inc. | Atomic layer deposition using radicals of gas mixture |

| US9163310B2 (en) | 2011-02-18 | 2015-10-20 | Veeco Ald Inc. | Enhanced deposition of layer on substrate using radicals |

| US8647993B2 (en) | 2011-04-11 | 2014-02-11 | Novellus Systems, Inc. | Methods for UV-assisted conformal film deposition |

| CN107342216B (zh) * | 2011-09-23 | 2022-05-31 | 诺发系统公司 | 等离子体活化保形电介质膜沉积 |

| US8592328B2 (en) | 2012-01-20 | 2013-11-26 | Novellus Systems, Inc. | Method for depositing a chlorine-free conformal sin film |

| US8728955B2 (en) | 2012-02-14 | 2014-05-20 | Novellus Systems, Inc. | Method of plasma activated deposition of a conformal film on a substrate surface |

| KR102207992B1 (ko) | 2012-10-23 | 2021-01-26 | 램 리써치 코포레이션 | 서브-포화된 원자층 증착 및 등각막 증착 |

| SG2013083241A (en) | 2012-11-08 | 2014-06-27 | Novellus Systems Inc | Conformal film deposition for gapfill |

| US9214334B2 (en) | 2014-02-18 | 2015-12-15 | Lam Research Corporation | High growth rate process for conformal aluminum nitride |

| US9478411B2 (en) | 2014-08-20 | 2016-10-25 | Lam Research Corporation | Method to tune TiOx stoichiometry using atomic layer deposited Ti film to minimize contact resistance for TiOx/Ti based MIS contact scheme for CMOS |

| US9478438B2 (en) | 2014-08-20 | 2016-10-25 | Lam Research Corporation | Method and apparatus to deposit pure titanium thin film at low temperature using titanium tetraiodide precursor |

| US9214333B1 (en) | 2014-09-24 | 2015-12-15 | Lam Research Corporation | Methods and apparatuses for uniform reduction of the in-feature wet etch rate of a silicon nitride film formed by ALD |

| US9589790B2 (en) | 2014-11-24 | 2017-03-07 | Lam Research Corporation | Method of depositing ammonia free and chlorine free conformal silicon nitride film |

| US9564312B2 (en) | 2014-11-24 | 2017-02-07 | Lam Research Corporation | Selective inhibition in atomic layer deposition of silicon-containing films |

| US10566187B2 (en) | 2015-03-20 | 2020-02-18 | Lam Research Corporation | Ultrathin atomic layer deposition film accuracy thickness control |

| US9502238B2 (en) | 2015-04-03 | 2016-11-22 | Lam Research Corporation | Deposition of conformal films by atomic layer deposition and atomic layer etch |

| US10526701B2 (en) | 2015-07-09 | 2020-01-07 | Lam Research Corporation | Multi-cycle ALD process for film uniformity and thickness profile modulation |

| US9601693B1 (en) | 2015-09-24 | 2017-03-21 | Lam Research Corporation | Method for encapsulating a chalcogenide material |

| US9773643B1 (en) | 2016-06-30 | 2017-09-26 | Lam Research Corporation | Apparatus and method for deposition and etch in gap fill |

| US10062563B2 (en) | 2016-07-01 | 2018-08-28 | Lam Research Corporation | Selective atomic layer deposition with post-dose treatment |

| US10629435B2 (en) | 2016-07-29 | 2020-04-21 | Lam Research Corporation | Doped ALD films for semiconductor patterning applications |

| US10074543B2 (en) | 2016-08-31 | 2018-09-11 | Lam Research Corporation | High dry etch rate materials for semiconductor patterning applications |

| US10037884B2 (en) | 2016-08-31 | 2018-07-31 | Lam Research Corporation | Selective atomic layer deposition for gapfill using sacrificial underlayer |

| US9865455B1 (en) | 2016-09-07 | 2018-01-09 | Lam Research Corporation | Nitride film formed by plasma-enhanced and thermal atomic layer deposition process |

| US10454029B2 (en) | 2016-11-11 | 2019-10-22 | Lam Research Corporation | Method for reducing the wet etch rate of a sin film without damaging the underlying substrate |

| US10832908B2 (en) | 2016-11-11 | 2020-11-10 | Lam Research Corporation | Self-aligned multi-patterning process flow with ALD gapfill spacer mask |

| US10134579B2 (en) | 2016-11-14 | 2018-11-20 | Lam Research Corporation | Method for high modulus ALD SiO2 spacer |

| US11942365B2 (en) * | 2017-06-02 | 2024-03-26 | Eugenus, Inc. | Multi-region diffusion barrier containing titanium, silicon and nitrogen |

| KR102416568B1 (ko) | 2017-08-14 | 2022-07-04 | 삼성디스플레이 주식회사 | 금속 산화막 형성 방법 및 플라즈마 강화 화학기상증착 장치 |

| US10269559B2 (en) | 2017-09-13 | 2019-04-23 | Lam Research Corporation | Dielectric gapfill of high aspect ratio features utilizing a sacrificial etch cap layer |

| WO2019169335A1 (en) | 2018-03-02 | 2019-09-06 | Lam Research Corporation | Selective deposition using hydrolysis |

| SG11202111962QA (en) | 2019-05-01 | 2021-11-29 | Lam Res Corp | Modulated atomic layer deposition |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5262662A (en) * | 1991-10-31 | 1993-11-16 | Micron Technology, Inc. | Storage node capacitor having tungsten and etched tin storage node capacitor plate |

| US5733816A (en) * | 1995-12-13 | 1998-03-31 | Micron Technology, Inc. | Method for depositing a tungsten layer on silicon |

| KR100363088B1 (ko) * | 2000-04-20 | 2002-12-02 | 삼성전자 주식회사 | 원자층 증착방법을 이용한 장벽 금속막의 제조방법 |

-

2005

- 2005-02-16 KR KR1020050012677A patent/KR100622609B1/ko not_active IP Right Cessation

- 2005-12-30 US US11/321,538 patent/US20060183301A1/en not_active Abandoned

-

2009

- 2009-02-04 US US12/365,316 patent/US20090148625A1/en not_active Abandoned

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8333839B2 (en) | 2007-12-27 | 2012-12-18 | Synos Technology, Inc. | Vapor deposition reactor |

| US8470718B2 (en) | 2008-08-13 | 2013-06-25 | Synos Technology, Inc. | Vapor deposition reactor for forming thin film |

| WO2010095901A2 (en) * | 2009-02-23 | 2010-08-26 | Synos Technology, Inc. | Method for forming thin film using radicals generated by plasma |

| WO2010095901A3 (en) * | 2009-02-23 | 2010-11-25 | Synos Technology, Inc. | Method for forming thin film using radicals generated by plasma |

| US8758512B2 (en) | 2009-06-08 | 2014-06-24 | Veeco Ald Inc. | Vapor deposition reactor and method for forming thin film |

| US9506146B2 (en) | 2011-01-04 | 2016-11-29 | Wonik Ips Co., Ltd. | Thin film vapor deposition method and thin film vapor deposition apparatus |

| US8840958B2 (en) | 2011-02-14 | 2014-09-23 | Veeco Ald Inc. | Combined injection module for sequentially injecting source precursor and reactant precursor |

| KR101741688B1 (ko) | 2011-12-26 | 2017-06-16 | 주식회사 원익아이피에스 | 박막 제조방법 및 그 제조장치 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20060183301A1 (en) | 2006-08-17 |

| US20090148625A1 (en) | 2009-06-11 |

| KR20060091908A (ko) | 2006-08-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100622609B1 (ko) | 박막 형성 방법 | |

| US9214467B2 (en) | Method for fabricating capacitor | |

| US7102875B2 (en) | Capacitor with aluminum oxide and lanthanum oxide containing dielectric structure and fabrication method thereof | |

| KR100519800B1 (ko) | 란타늄 산화막의 제조방법 및 이를 이용한 모스 전계효과트랜지스터 및 캐패시터의 제조방법 | |

| US6486022B2 (en) | Method of fabricating capacitors | |

| KR100818652B1 (ko) | 산소포획막을 구비한 캐패시터 및 그의 제조 방법 | |

| KR20040100766A (ko) | 원자층 증착법을 이용한 복합 유전막의 연속 형성방법 및이를 이용한 캐패시터의 제조방법 | |

| US20070264770A1 (en) | Capacitor forming method | |

| KR100655140B1 (ko) | 캐패시터 및 그 제조 방법 | |

| KR100772531B1 (ko) | 캐패시터의 제조 방법 | |

| KR100780631B1 (ko) | 티타늄산화막의 증착 방법 및 그를 이용한 캐패시터의제조 방법 | |

| KR100532960B1 (ko) | 반도체소자의 캐패시터 형성방법 | |

| KR20070106286A (ko) | 루틸구조로 결정화된 티타늄산화막의 형성 방법 및 그를이용한 캐패시터의 제조 방법 | |

| KR100533981B1 (ko) | 반도체 장치의 캐패시터 제조방법 | |

| KR100604664B1 (ko) | 이중 유전막을 구비한 캐패시터 및 그 제조 방법 | |

| KR100937988B1 (ko) | 반도체 소자의 캐패시터 제조방법 | |

| KR100656282B1 (ko) | 캐패시터 제조 방법 | |

| KR100798735B1 (ko) | 캐패시터 및 그 제조 방법 | |

| KR100761406B1 (ko) | 탄탈륨산화막을 유전막으로 갖는 캐패시터의 제조 방법 | |

| KR100538808B1 (ko) | 금속막으로 된 하부전극을 구비하는 캐패시터의 제조 방법 | |

| KR100744666B1 (ko) | 반도체 소자의 캐패시터 및 그 제조 방법 | |

| KR100596439B1 (ko) | 알갱이 형태의 티타늄실리사이드가 형성된 금속하부전극을포함하는 캐패시터의 제조 방법 | |

| KR101067022B1 (ko) | 반도체 소자의 커패시터 형성방법 | |

| KR101026477B1 (ko) | 반도체 소자의 캐패시터 형성방법 | |

| KR20050062099A (ko) | 알루미늄산화막과 하프늄산화막의 적층 유전막을 갖는캐패시터의 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20090828 Year of fee payment: 4 |

|

| LAPS | Lapse due to unpaid annual fee |