JP6084357B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP6084357B2 JP6084357B2 JP2011240860A JP2011240860A JP6084357B2 JP 6084357 B2 JP6084357 B2 JP 6084357B2 JP 2011240860 A JP2011240860 A JP 2011240860A JP 2011240860 A JP2011240860 A JP 2011240860A JP 6084357 B2 JP6084357 B2 JP 6084357B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- semiconductor device

- groove

- insulating layer

- drift region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 243

- 239000000758 substrate Substances 0.000 claims description 115

- 239000012535 impurity Substances 0.000 claims description 53

- 238000002955 isolation Methods 0.000 claims description 46

- 150000004767 nitrides Chemical class 0.000 claims description 28

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 claims description 3

- 229910052594 sapphire Inorganic materials 0.000 claims description 2

- 239000010980 sapphire Substances 0.000 claims description 2

- 239000010410 layer Substances 0.000 description 213

- 230000005684 electric field Effects 0.000 description 34

- 238000004519 manufacturing process Methods 0.000 description 30

- 238000000034 method Methods 0.000 description 27

- 229920002120 photoresistant polymer Polymers 0.000 description 23

- 230000015556 catabolic process Effects 0.000 description 16

- 230000000694 effects Effects 0.000 description 15

- 239000011229 interlayer Substances 0.000 description 15

- 239000000463 material Substances 0.000 description 14

- 235000004522 Pentaglottis sempervirens Nutrition 0.000 description 12

- 230000000052 comparative effect Effects 0.000 description 11

- 238000001020 plasma etching Methods 0.000 description 11

- 239000002184 metal Substances 0.000 description 10

- 238000004544 sputter deposition Methods 0.000 description 9

- 229910004298 SiO 2 Inorganic materials 0.000 description 8

- 238000005229 chemical vapour deposition Methods 0.000 description 7

- 238000004380 ashing Methods 0.000 description 6

- 238000010586 diagram Methods 0.000 description 6

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 5

- 125000004429 atom Chemical group 0.000 description 5

- 239000012141 concentrate Substances 0.000 description 5

- 238000005530 etching Methods 0.000 description 5

- 238000001039 wet etching Methods 0.000 description 5

- 240000004050 Pentaglottis sempervirens Species 0.000 description 4

- 229910004541 SiN Inorganic materials 0.000 description 4

- 238000005468 ion implantation Methods 0.000 description 4

- 238000000137 annealing Methods 0.000 description 3

- 210000000746 body region Anatomy 0.000 description 3

- 239000003990 capacitor Substances 0.000 description 3

- 239000013078 crystal Substances 0.000 description 3

- 239000007789 gas Substances 0.000 description 3

- 125000005843 halogen group Chemical group 0.000 description 3

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 3

- 229920005591 polysilicon Polymers 0.000 description 3

- 238000004088 simulation Methods 0.000 description 3

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 2

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 2

- 229910020177 SiOF Inorganic materials 0.000 description 2

- 230000001133 acceleration Effects 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 239000000460 chlorine Substances 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 238000005192 partition Methods 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- 229910002704 AlGaN Inorganic materials 0.000 description 1

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 1

- 229910005191 Ga 2 O 3 Inorganic materials 0.000 description 1

- 230000001154 acute effect Effects 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 229910052801 chlorine Inorganic materials 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000002513 implantation Methods 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 230000002040 relaxant effect Effects 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 239000011800 void material Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7833—Field effect transistors with field effect produced by an insulated gate with lightly doped drain or source extension, e.g. LDD MOSFET's; DDD MOSFET's

- H01L29/7835—Field effect transistors with field effect produced by an insulated gate with lightly doped drain or source extension, e.g. LDD MOSFET's; DDD MOSFET's with asymmetrical source and drain regions, e.g. lateral high-voltage MISFETs with drain offset region, extended drain MISFETs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42356—Disposition, e.g. buried gate electrode

- H01L29/4236—Disposition, e.g. buried gate electrode within a trench, e.g. trench gate electrode, groove gate electrode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66568—Lateral single gate silicon transistors

- H01L29/66659—Lateral single gate silicon transistors with asymmetry in the channel direction, e.g. lateral high-voltage MISFETs with drain offset region, extended drain MISFETs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0642—Isolation within the component, i.e. internal isolation

- H01L29/0649—Dielectric regions, e.g. SiO2 regions, air gaps

- H01L29/0653—Dielectric regions, e.g. SiO2 regions, air gaps adjoining the input or output region of a field-effect device, e.g. the source or drain region

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0684—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape, relative sizes or dispositions of the semiconductor regions or junctions between the regions

- H01L29/0692—Surface layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/20—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only AIIIBV compounds

- H01L29/2003—Nitride compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41725—Source or drain electrodes for field effect devices

- H01L29/41758—Source or drain electrodes for field effect devices for lateral devices with structured layout for source or drain region, i.e. the source or drain region having cellular, interdigitated or ring structure or being curved or angular

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42364—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the insulating layer, e.g. thickness or uniformity

- H01L29/42368—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the insulating layer, e.g. thickness or uniformity the thickness being non-uniform

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42372—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the conducting layer, e.g. the length, the sectional shape or the lay-out

- H01L29/4238—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the conducting layer, e.g. the length, the sectional shape or the lay-out characterised by the surface lay-out

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/785—Field effect transistors with field effect produced by an insulated gate having a channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Thin Film Transistor (AREA)

Description

表面を第1面とする半導体基板と、

前記半導体基板の前記第1面側に設けられた溝部と、

前記溝部の側面の一つである第2面に面し、少なくとも一部が前記第1面および前記第2面の交線と平行な方向に延在する第1導電型のソース領域と、

前記溝部のうち前記第2面と反対の第3面に面し、少なくとも一部が前記第1面および前記第3面の交線と平行な方向に延在して設けられ、前記ソース領域よりも低濃度の第1導電型のドリフト領域と、

前記ドリフト領域を介して前記溝部の反対側に位置し、前記ドリフト領域と接するように設けられ、前記ドリフト領域よりも高濃度の第1導電型のドレイン領域と、

前記半導体基板に設けられ、平面視で前記ソース領域と前記ドリフト領域で挟まれたチャネル領域と、

前記溝部の前記側面のうち前記第2面および前記第3面に交わる方向の面である第4面と接するとともに、前記第1面上のうち少なくとも前記チャネル領域と接するように設けられた第1ゲート絶縁層と、

前記第1ゲート絶縁層上に設けられたゲート電極と、

を備え、

前記溝部は前記ドリフト領域よりも深く形成されている半導体装置が提供される。

半導体基板の第1面側に、溝部を形成する溝部形成工程と、

前記溝部の側面の一つである第2面に面し、少なくとも一部が前記第1面および前記第2面の交線と平行な方向に延在する位置に、第1導電型の不純物を注入してソース領域を形成する工程と、

前記溝部のうち前記第2面と反対の第3面から離間する位置に、第1導電型の不純物を注入してドレイン領域を形成する工程と、

前記ドレイン領域と接するとともに前記第3面に面し、少なくとも一部が前記第1面および前記第3面の交線と平行な方向に延在する位置に、前記ソース領域および前記ドレイン領域よりも低濃度の第1導電型の不純物を注入して、ドリフト領域を形成する工程と、

前記溝部の前記側面のうち前記第2面と前記第3面に交わる方向の面である第4面と接するとともに、前記第1面上のうち少なくとも平面視で前記ソース領域と前記ドリフト領域で挟まれたチャネル領域と接するように、第1ゲート絶縁層を形成する工程と、

前記第1ゲート絶縁層上にゲート電極を形成する工程と、

を備え、

前記溝部形成工程において、

前記溝部を前記ドリフト領域よりも深く形成する半導体装置の製造方法が提供される。

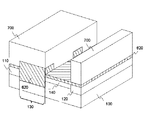

図1〜図5を用い、第1の実施形態に係る半導体装置10について説明する。この半導体装置10は、以下の構成を備えている。溝部300は、半導体基板100の第1面31側に設けられている。第1導電型のソース領域110は、溝部300の側面の一つである第2面32に面し、少なくとも一部が第1面31および第2面32の交線と平行な方向に延在している。第1導電型のドリフト領域140は、溝部300のうち第2面32の反対の第3面33に面し、少なくとも一部が第1面31および第3面33の交線と平行な方向に延在して設けられており、ソース領域110よりも低濃度に形成されている。第1導電型のドレイン領域120は、ドリフト領域140を介して溝部300の反対側に位置し、ドリフト領域140と接するように設けられ、ドリフト領域140よりも高濃度に形成されている。チャネル領域130は、半導体基板100に設けられ、平面視でソース領域110とドリフト領域140で挟まれた領域に形成されている。第1ゲート絶縁層200は、溝部300の側面のうち第2面32と第3面33に交わる方向の面である第4面34と接するとともに、第1面31上のうち少なくともチャネル領域130と接するように設けられている。ゲート電極400は、第1ゲート絶縁層200上に設けられている。また、溝部300はドリフト領域140よりも深く形成されている。以下、詳細を説明する。

図16は、第2の実施形態に係る半導体装置10の構成を示す鳥瞰図である。第2の実施形態は、フィールドプレート電極420が設けられている点を除いて、第1の実施形態と同様である。以下、詳細を説明する

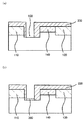

図17は、第3の実施形態に係る半導体装置10の構成を示す断面図である。また、当該断面図は、図1のB−B'線の矢印側から見た断面図に対応している。第3の実施形態は、以下の点を除いて、第1の実施形態と同様である。半導体基板100の第1面31側に設けられ、平面視でドリフト領域140と重なるように設けられ、第3面33から離間して設けられた素子分離領域280をさらに備えている。ドリフト領域140は、素子分離領域280のうち第3面33側の側面および底面と接している。以下、詳細を説明する。

図21は、第4の実施形態に係る半導体装置10の構成を示す断面図である。第4の実施形態は、ゲート電極400が溝部300の第3面33から離間して設けられている点を除いて、第1の実施形態、または第3の実施形態の一部と同様である。

図24は、第5の実施形態に係る半導体装置10の構成を示す断面図である。第5の実施形態は、ゲート電極400および溝部300の第3面33の間に空隙(符号不図示)が設けられている点を除いて、第1の実施形態および第4の実施形態と同様である。

第6の実施形態は、半導体基板100がSiである点を除いて、第1の実施形態と同様である。

図25は、第7の実施形態に係る半導体装置10の構成を示す断面図である。第7の実施形態は、第2ゲート絶縁層220は第1ゲート絶縁層200を介して第3面33と接している点を除いて、第1の実施形態、または第5の実施形態と同様である。

11 FET

31 第1面

32 第2面

33 第3面

34 第4面

100 半導体基板

102 下地基板

104 III族窒化物半導体層

110 ソース領域

120 ドレイン領域

130 チャネル領域

140 ドリフト領域

200 第1ゲート絶縁層

220 第2ゲート絶縁層

280 素子分離領域

282 絶縁層

300 溝部

320 開口部

400 ゲート電極

420 フィールドプレート電極

440 ソース電極

460 ドレイン電極

520 第1層間絶縁層

620 第1マスク層

640 第2マスク層

700 フォトレジスト層

800 DC−DCコントローラ

820 インダクタ

840 コンデンサ

Claims (15)

- 表面を第1面とする半導体基板と、

前記半導体基板の前記第1面側に設けられた溝部と、

前記溝部の側面の一つである第2面に面し、少なくとも一部が前記第1面および前記第2面の交線と平行な方向に延在する第1導電型のソース領域と、

前記溝部のうち前記第2面と反対の第3面に面し、少なくとも一部が前記第1面および前記第3面の交線と平行な方向に延在して設けられ、前記ソース領域よりも低濃度の第1導電型のドリフト領域と、

前記ドリフト領域を介して前記溝部の反対側に位置し、前記ドリフト領域と接するように設けられ、前記ドリフト領域よりも高濃度の第1導電型のドレイン領域と、

前記半導体基板に設けられ、平面視で前記ソース領域と前記ドリフト領域で挟まれたチャネル領域と、

前記溝部の前記側面のうち前記第2面および前記第3面に交わる方向の面である第4面と接するとともに、前記第1面上のうち少なくとも前記チャネル領域と接するように設けられた第1ゲート絶縁層と、

前記第1ゲート絶縁層上に設けられたゲート電極と、

を備え、

前記溝部は前記ドリフト領域よりも深く形成されており、

前記ゲート電極は、前記溝部の前記第3面から離間して設けられており、

前記第3面と接し、前記第1ゲート絶縁層よりも厚い第2ゲート絶縁層をさらに備える半導体装置。 - 表面を第1面とする半導体基板と、

前記半導体基板の前記第1面側に設けられた溝部と、

前記溝部の側面の一つである第2面に面し、少なくとも一部が前記第1面および前記第2面の交線と平行な方向に延在する第1導電型のソース領域と、

前記溝部のうち前記第2面と反対の第3面に面し、少なくとも一部が前記第1面および前記第3面の交線と平行な方向に延在して設けられ、前記ソース領域よりも低濃度の第1導電型のドリフト領域と、

前記ドリフト領域を介して前記溝部の反対側に位置し、前記ドリフト領域と接するように設けられ、前記ドリフト領域よりも深く形成され、前記ドリフト領域よりも高濃度の第1導電型のドレイン領域と、

前記半導体基板に設けられ、平面視で前記ソース領域と前記ドリフト領域で挟まれたチャネル領域と、

前記溝部の前記側面のうち前記第2面および前記第3面に交わる方向の面である第4面と接するとともに、前記第1面上のうち少なくとも前記チャネル領域と接するように設けられた第1ゲート絶縁層と、

前記第1ゲート絶縁層上に設けられたゲート電極と、

を備え、

前記溝部は前記ドリフト領域よりも深く形成されており、

前記ゲート電極は、前記溝部の前記第3面から離間して設けられており、

前記第3面と接し、前記第1ゲート絶縁層よりも厚い第2ゲート絶縁層をさらに備える半導体装置。 - 請求項1又は2に記載の半導体装置において、

前記第1面および前記第2面の交線と平行な方向に直列に配置され、互いに離間して設けられた複数の前記溝部を備え、

前記チャネル領域は、隣接する前記溝部の間に形成されている半導体装置。 - 請求項1〜3のいずれか一項に記載の半導体装置において、

前記ゲート電極に接し、平面視で前記ドリフト領域と重なるように設けられたフィールドプレート電極をさらに備え、

前記第1ゲート絶縁層のうち、前記ドリフト領域上に接する部分の膜厚は、前記チャネル領域上に接する部分よりも厚い半導体装置。 - 請求項1〜4のいずれか一項に記載の半導体装置において、

前記半導体基板の前記第1面側に設けられ、平面視で前記ドリフト領域と重なるように設けられ、前記第3面から離間して設けられた素子分離領域をさらに備え、

前記ドリフト領域は、前記素子分離領域のうち前記第3面側の側面および底面と接している半導体装置。 - 請求項1〜5のいずれか一項に記載の半導体装置において、

前記半導体基板の前記第1面側に設けられた素子分離領域をさらに備え、

前記溝部の深さは前記素子分離領域と等しい半導体装置。 - 請求項1〜6のいずれか一項に記載の半導体装置において、

前記半導体基板の少なくとも前記第1面側は、III族窒化物半導体層であり、

前記ソース領域、前記チャネル領域、前記ドリフト領域および前記ドレイン領域は、前記III族窒化物半導体層に形成されている半導体装置。 - 請求項7に記載の半導体装置において、

前記チャネル領域の不純物濃度は、1×1016atoms/cm3以下である半導体装置。 - 請求項7又は8に記載の半導体装置において、

前記III族窒化物半導体層は、真性半導体である半導体装置。 - 請求項7〜9のいずれか一項に記載の半導体装置において、

前記ソース領域、前記ドリフト領域および前記ドレイン領域は、n型であり、

当該n型の不純物は、Siである半導体装置。 - 請求項10に記載の半導体装置において、

前記III族窒化物半導体層のうち、前記ソース領域および前記ドレイン領域の間に位置する部分には、p型の不純物領域が形成されていない半導体装置。 - 請求項7〜11のいずれか一項に記載の半導体装置において、

前記半導体基板のうち、前記III族窒化物半導体層は、下地基板上に設けられ、

当該下地基板は、Si基板、サファイア基板、SiC基板またはGaN基板である半導体装置。 - 請求項7〜12のいずれか一項に記載の半導体装置において、

前記ソース領域から前記ドレイン領域に向かう方向は、[2−1−10]方向または[01−10]方向である半導体装置。 - 請求項1〜6のいずれか一項に記載の半導体装置において、

前記半導体基板は、Si基板である半導体装置。 - 請求項14に記載の半導体装置において、

前記ソース領域から前記ドレイン領域に向かう方向は、[100]方向または[110]方向である半導体装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011240860A JP6084357B2 (ja) | 2011-11-02 | 2011-11-02 | 半導体装置 |

| US13/666,507 US8748979B2 (en) | 2011-11-02 | 2012-11-01 | Trench lateral MOSFET having a multi-plane gate structure |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011240860A JP6084357B2 (ja) | 2011-11-02 | 2011-11-02 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2013098402A JP2013098402A (ja) | 2013-05-20 |

| JP6084357B2 true JP6084357B2 (ja) | 2017-02-22 |

Family

ID=48171470

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011240860A Expired - Fee Related JP6084357B2 (ja) | 2011-11-02 | 2011-11-02 | 半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8748979B2 (ja) |

| JP (1) | JP6084357B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11251293B2 (en) | 2019-09-02 | 2022-02-15 | Kabushiki Kaisha Toshiba | Semiconductor device |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN105405880B (zh) * | 2014-08-08 | 2019-05-07 | 瑞昱半导体股份有限公司 | 半导体元件及多栅极场效应晶体管 |

Family Cites Families (38)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH033272A (ja) * | 1989-05-30 | 1991-01-09 | Mitsubishi Electric Corp | 半導体装置 |

| JPH0444327A (ja) * | 1990-06-11 | 1992-02-14 | Oki Electric Ind Co Ltd | 絶縁ゲート電界効果トランジスタ及びその製造方法 |

| JPH05243563A (ja) * | 1992-02-27 | 1993-09-21 | Mitsubishi Electric Corp | Nチャネルトランジスタ |

| JP3356162B2 (ja) * | 1999-10-19 | 2002-12-09 | 株式会社デンソー | 半導体装置及びその製造方法 |

| GB0012138D0 (en) * | 2000-05-20 | 2000-07-12 | Koninkl Philips Electronics Nv | A semiconductor device |

| GB0028031D0 (en) * | 2000-11-17 | 2001-01-03 | Koninkl Philips Electronics Nv | Trench-gate field-effect transistors and their manufacture |

| JP2003007846A (ja) * | 2001-06-21 | 2003-01-10 | Seiko Instruments Inc | 半導体装置 |

| US8080459B2 (en) * | 2002-09-24 | 2011-12-20 | Vishay-Siliconix | Self aligned contact in a semiconductor device and method of fabricating the same |

| JP4042530B2 (ja) | 2002-10-30 | 2008-02-06 | 富士電機デバイステクノロジー株式会社 | 半導体装置 |

| JP4166627B2 (ja) * | 2003-05-30 | 2008-10-15 | 株式会社デンソー | 半導体装置 |

| JP4590884B2 (ja) * | 2003-06-13 | 2010-12-01 | 株式会社デンソー | 半導体装置およびその製造方法 |

| JP4623956B2 (ja) * | 2003-11-12 | 2011-02-02 | 株式会社豊田中央研究所 | Igbt |

| JP4179147B2 (ja) * | 2003-11-28 | 2008-11-12 | 株式会社デンソー | 炭化珪素半導体装置 |

| DE102004026233B4 (de) * | 2004-05-28 | 2015-02-12 | Infineon Technologies Ag | Trenchtransistor |

| JP2006278674A (ja) * | 2005-03-29 | 2006-10-12 | Nec Electronics Corp | 電界効果トランジスタとその製造方法、及び半導体装置 |

| JP2007027641A (ja) | 2005-07-21 | 2007-02-01 | Toshiba Corp | 半導体装置及びその製造方法 |

| DE102005052734B4 (de) * | 2005-10-06 | 2012-02-23 | Infineon Technologies Ag | Halbleiterstruktur, Verfahren zum Betreiben einer Halbleiterstruktur und Verfahren zum Herstellen einer Halbleiterstruktur |

| US7449762B1 (en) * | 2006-04-07 | 2008-11-11 | Wide Bandgap Llc | Lateral epitaxial GaN metal insulator semiconductor field effect transistor |

| US7598517B2 (en) * | 2006-08-25 | 2009-10-06 | Freescale Semiconductor, Inc. | Superjunction trench device and method |

| JP4324218B2 (ja) | 2006-12-08 | 2009-09-02 | シャープ株式会社 | 高耐圧mosfetを備えた半導体装置及びその製造方法 |

| US7851853B2 (en) | 2006-12-08 | 2010-12-14 | Sharp Kabushiki Kaisha | Semiconductor device comprising high-withstand voltage MOSFET and its manufacturing method |

| JP2008210994A (ja) * | 2007-02-27 | 2008-09-11 | Nec Electronics Corp | 横型mosfetおよびその製造方法 |

| US7564099B2 (en) * | 2007-03-12 | 2009-07-21 | International Rectifier Corporation | Monolithic MOSFET and Schottky diode device |

| US7646058B2 (en) * | 2007-06-05 | 2010-01-12 | Force-Mos Technology Corporation | Device configuration and method to manufacture trench MOSFET with solderable front metal |

| JP2009049260A (ja) * | 2007-08-22 | 2009-03-05 | Seiko Instruments Inc | トレンチ構造を利用した横型高駆動能力半導体装置 |

| JP5442951B2 (ja) * | 2008-02-26 | 2014-03-19 | セイコーインスツル株式会社 | 半導体装置の製造方法 |

| JP2009277960A (ja) * | 2008-05-16 | 2009-11-26 | Fuji Electric Device Technology Co Ltd | 半導体装置 |

| JP2009277956A (ja) | 2008-05-16 | 2009-11-26 | Fuji Electric Device Technology Co Ltd | 半導体装置 |

| JP2009302450A (ja) * | 2008-06-17 | 2009-12-24 | Sharp Corp | 半導体装置およびその製造方法 |

| JP2010028029A (ja) * | 2008-07-24 | 2010-02-04 | Renesas Technology Corp | 半導体装置および半導体装置の製造方法 |

| JP5325534B2 (ja) * | 2008-10-29 | 2013-10-23 | 株式会社東芝 | 窒化物半導体素子 |

| JP5369300B2 (ja) * | 2009-09-16 | 2013-12-18 | 三菱電機株式会社 | 半導体装置およびその製造方法 |

| JP5492610B2 (ja) * | 2010-03-11 | 2014-05-14 | パナソニック株式会社 | 半導体装置及びその製造方法 |

| JP2012059931A (ja) * | 2010-09-09 | 2012-03-22 | Toshiba Corp | 半導体装置 |

| JP5214704B2 (ja) * | 2010-10-26 | 2013-06-19 | 株式会社東芝 | 半導体装置 |

| US8580650B2 (en) * | 2010-10-28 | 2013-11-12 | Texas Instruments Incorporated | Lateral superjunction extended drain MOS transistor |

| US8431470B2 (en) * | 2011-04-04 | 2013-04-30 | Alpha And Omega Semiconductor Incorporated | Approach to integrate Schottky in MOSFET |

| US8921933B2 (en) * | 2011-05-19 | 2014-12-30 | Macronix International Co., Ltd. | Semiconductor structure and method for operating the same |

-

2011

- 2011-11-02 JP JP2011240860A patent/JP6084357B2/ja not_active Expired - Fee Related

-

2012

- 2012-11-01 US US13/666,507 patent/US8748979B2/en active Active

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11251293B2 (en) | 2019-09-02 | 2022-02-15 | Kabushiki Kaisha Toshiba | Semiconductor device |

Also Published As

| Publication number | Publication date |

|---|---|

| US20130105813A1 (en) | 2013-05-02 |

| US8748979B2 (en) | 2014-06-10 |

| JP2013098402A (ja) | 2013-05-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102210449B1 (ko) | 추가적인 소자를 생성하기 위한 폴리실리콘 층을 갖는 GaN 트랜지스터 | |

| KR101315009B1 (ko) | 고전압 접합 종단을 갖는 고전압 저항기 | |

| US10522532B2 (en) | Through via extending through a group III-V layer | |

| US10418480B2 (en) | Semiconductor device capable of high-voltage operation | |

| US7935992B2 (en) | Transistor, display driver integrated circuit including a transistor, and a method of fabricating a transistor | |

| JP5731904B2 (ja) | 半導体装置及び半導体装置の製造方法 | |

| US8643067B2 (en) | Strapped dual-gate VDMOS device | |

| US10879389B2 (en) | Semiconductor device capable of high-voltage operation | |

| JP6091941B2 (ja) | 半導体装置 | |

| JP5404550B2 (ja) | 半導体装置の製造方法及び半導体装置 | |

| US20220302322A1 (en) | Diode | |

| JP2020061412A (ja) | 半導体装置 | |

| US20210184009A1 (en) | Trench mosfet and method for manufacturing the same | |

| US9397092B2 (en) | Semiconductor device in a semiconductor substrate and method of manufacturing a semiconductor device in a semiconductor substrate | |

| US20180219070A1 (en) | Semiconductor device and method for manufacturing the same | |

| JP2013093482A (ja) | 半導体装置および半導体装置の製造方法 | |

| US20130069156A1 (en) | Semiconductor device | |

| JP6084357B2 (ja) | 半導体装置 | |

| US8482060B2 (en) | Semiconductor device | |

| TW201906159A (zh) | 高壓半導體裝置及其製造方法 | |

| US9324786B2 (en) | Semiconductor device and method for fabricating the same | |

| CN108257955B (zh) | 半导体元件 | |

| US20050104126A1 (en) | Semiconductor device and method for manufacturing semiconductor device | |

| JP2009164183A (ja) | 半導体装置及びその製造方法 | |

| JP2008004600A (ja) | 半導体装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140812 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150519 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150616 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150804 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160301 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20160913 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161206 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20161214 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170124 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170125 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6084357 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |