JP5854104B2 - Semiconductor device - Google Patents

Semiconductor device Download PDFInfo

- Publication number

- JP5854104B2 JP5854104B2 JP2014200645A JP2014200645A JP5854104B2 JP 5854104 B2 JP5854104 B2 JP 5854104B2 JP 2014200645 A JP2014200645 A JP 2014200645A JP 2014200645 A JP2014200645 A JP 2014200645A JP 5854104 B2 JP5854104 B2 JP 5854104B2

- Authority

- JP

- Japan

- Prior art keywords

- impurity

- layer

- region

- insulating film

- semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Description

本発明は、半導体装置に関する。 The present invention relates to semiconductor equipment.

半導体装置の微細化・高集積化に伴い、チャネル不純物の統計的揺らぎによるトランジスタの閾値電圧ばらつきが顕在化している。閾値電圧はトランジスタの性能を決定づける重要なパラメータの一つであり、高性能且つ高信頼性の半導体装置を製造するために、不純物の統計的揺らぎによる閾値電圧ばらつきを低減することは重要である。 As semiconductor devices are miniaturized and highly integrated, transistor threshold voltage variations due to statistical fluctuations of channel impurities are becoming apparent. The threshold voltage is one of the important parameters that determine the performance of the transistor. In order to manufacture a high-performance and high-reliability semiconductor device, it is important to reduce variations in threshold voltage due to statistical fluctuations of impurities.

不純物の統計的揺らぎによる閾値電圧のばらつきを低減する技術の一つとして、急峻な不純物濃度分布を有する高濃度のチャネル不純物層上にノンドープのエピタキシャルシリコン層を形成する方法が提案されている。 As one technique for reducing the variation in threshold voltage due to statistical fluctuation of impurities, a method of forming a non-doped epitaxial silicon layer on a high-concentration channel impurity layer having a steep impurity concentration distribution has been proposed.

しかしながら、提案されている上記技術を半導体装置の製造プロセスに組み込むための方法については、具体的な提案はなされていなかった。例えば、低電圧動作のトランジスタと高電圧動作のトランジスタとを含む半導体装置の製造プロセスに適用した場合に生じる新たな課題やその解決手段について、具体的な検討はなされていなかった。 However, no specific proposal has been made for a method for incorporating the proposed technique into the semiconductor device manufacturing process. For example, specific studies have not been made on new problems and solutions for the problems that occur when applied to a manufacturing process of a semiconductor device including a low-voltage operation transistor and a high-voltage operation transistor.

本発明の目的は、低電圧動作のトランジスタ及び高電圧動作のトランジスタの双方の要求を満たし、高性能・高信頼性を実現しうる半導体装置を提供することにある。 An object of the present invention satisfies both requirements of the transistors of the transistor and the high voltage operation of low voltage operation, there is provided a semiconductor equipment capable of high performance and high reliability.

実施形態の一観点によれば、第1の領域及び第2の領域を有する半導体基板と、前記半導体基板の前記第1の領域に形成され、第1の導電型の第1の不純物を有する第1の不純物層と、前記第1の不純物層上に形成された第1の半導体層と、前記第1の半導体層上に形成された第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成された第1のゲート電極と、前記第1の半導体層及び前記第1の領域の前記半導体基板に形成された第1のソース/ドレイン領域と、前記半導体基板の前記第2の領域に形成され、前記第1の不純物よりも拡散定数の小さい前記第1導電型の第2の不純物を有する第2の不純物層と、前記第2の不純物層上に形成された第2の半導体層と、前記第2の半導体層上に形成され前記第1のゲート絶縁膜よりも薄い第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成された第2のゲート電極と、前記第2の半導体層及び前記第2の領域の前記半導体基板に形成された第2のソース/ドレイン領域と、を有し、前記第1の半導体層の前記第1の不純物の不純物濃度は、前記第1の不純物層の前記第1の不純物の不純物濃度よりも低く、 前記第2の半導体層の前記第2の不純物の不純物濃度は、前記第2の不純物層の前記第2の不純物の不純物濃度よりも低いことを特徴とする半導体装置が提供される。

また、実施形態の他の観点によれば、第1の領域及び第2の領域を有する半導体基板と、前記半導体基板の前記第1の領域に形成され、第1の導電型の第1の不純物を有する第1の不純物層と、前記第1の不純物層上に形成された第1の半導体層と、前記第1の半導体層上に形成された第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成された第1のゲート電極と、前記第1の半導体層及び前記第1の領域の前記半導体基板に形成された第1のソース/ドレイン領域と、前記半導体基板の前記第2の領域に形成され、前記第1の不純物及び前記第1の不純物の拡散を抑制する第3の不純物を有する第2の不純物層と、前記第2の不純物層上に形成された第2の半導体層と、前記第2の半導体層上に形成され前記第1のゲート絶縁膜よりも薄い第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成された第2のゲート電極と、前記第2の半導体層及び前記第2の領域の前記半導体基板に形成された第2のソース/ドレイン領域と、を有することを特徴とする半導体装置が提供される。

According to one aspect of the embodiment, a semiconductor substrate having a first region and a second region, and a first substrate formed in the first region of the semiconductor substrate and having a first impurity of a first conductivity type. 1 impurity layer, a first semiconductor layer formed on the first impurity layer, a first gate insulating film formed on the first semiconductor layer, and the first gate insulating film A first gate electrode formed thereon; a first source / drain region formed in the semiconductor substrate of the first semiconductor layer and the first region; and the second region of the semiconductor substrate. is formed, said second impurity layer having a first second impurity of a small first conductivity type diffusion constant than the impurity, a second semiconductor formed on the second impurity layer And a layer formed on the second semiconductor layer and thinner than the first gate insulating film A second gate insulating film, a second gate electrode formed on the second gate insulating film, a second source formed on the semiconductor substrate in the second semiconductor layer and the second region / drain region, was closed, the impurity concentration of the first impurity in the first semiconductor layer, said first lower than the impurity concentration of said first impurity in the impurity layer, the second semiconductor The semiconductor device is characterized in that the impurity concentration of the second impurity in the layer is lower than the impurity concentration of the second impurity in the second impurity layer .

According to another aspect of the embodiment, a semiconductor substrate having a first region and a second region, and a first impurity of the first conductivity type formed in the first region of the semiconductor substrate. A first impurity layer comprising: a first semiconductor layer formed on the first impurity layer; a first gate insulating film formed on the first semiconductor layer; A first gate electrode formed on a gate insulating film; a first source / drain region formed in the semiconductor substrate of the first semiconductor layer and the first region; and the first source electrode of the semiconductor substrate. A second impurity layer formed in the second region and having a first impurity and a third impurity that suppresses diffusion of the first impurity, and a second impurity layer formed on the second impurity layer. More than the first gate insulating film formed on the semiconductor layer and the second semiconductor layer A thin second gate insulating film, a second gate electrode formed on the second gate insulating film, and a second semiconductor layer and a second region formed on the semiconductor substrate in the second region. And a source / drain region of the semiconductor device.

開示の半導体装置によれば、チャネル不純物層上にエピタキシャル層を有するトランジスタにおいて、低電圧トランジスタのチャネル不純物層を急峻な不純物分布にするとともに、高電圧トランジスタのチャネル不純物層をなだらかな不純物分布にすることができる。これにより、低電圧トランジスタの閾値電圧の安定化し、高電圧トランジスタの接合耐圧やホットキャリア耐性を向上することができ、高性能・高信頼性を有する半導体装置を実現することができる。 According to the semiconductor equipment disclosed, in a transistor having an epitaxial layer on the channel impurity layer, while the channel impurity layer of the low-voltage transistor steep impurity distribution, on a gentle impurity distribution channel impurity layer of the high-voltage transistor can do. Thereby, the threshold voltage of the low voltage transistor can be stabilized, the junction breakdown voltage and hot carrier resistance of the high voltage transistor can be improved, and a semiconductor device having high performance and high reliability can be realized.

[第1実施形態]

第1実施形態による半導体装置及びその製造方法について図1乃至図20を用いて説明する。

[First Embodiment]

The semiconductor device and the manufacturing method thereof according to the first embodiment will be described with reference to FIGS.

図1及び図2は、本実施形態による半導体装置の構造を示す概略断面図である。図3乃至図20は、本実施形態による半導体装置の製造方法を示す工程断面図である。 1 and 2 are schematic cross-sectional views illustrating the structure of the semiconductor device according to the present embodiment. 3 to 20 are process cross-sectional views illustrating the method for fabricating the semiconductor device according to the present embodiment.

はじめに、本実施形態による半導体装置の構造について図1及び図2を用いて説明する。 First, the structure of the semiconductor device according to the present embodiment will be explained with reference to FIGS.

シリコン基板10上には、低電圧NMOSトランジスタ(LV NMOS)と、低電圧PMOSトランジスタ(LV PMOS)と、高電圧NMOSトランジスタ(HV NMOS)と、高電圧PMOSトランジスタ(HV PMOS)とが形成されている。低電圧トランジスタは、主に、高速動作が必要とされる回路部分に用いられるものである。高電圧トランジスタは、3.3V I/O等、高電圧の印加される回路部分に用いられるものである。

A low voltage NMOS transistor (LV NMOS), a low voltage PMOS transistor (LV PMOS), a high voltage NMOS transistor (HV NMOS), and a high voltage PMOS transistor (HV PMOS) are formed on the

低電圧NMOSトランジスタ(LV NMOS)は、シリコン基板10の低電圧NMOSトランジスタ形成領域16に形成されている。

The low voltage NMOS transistor (LV NMOS) is formed in the low voltage NMOS

低電圧NMOSトランジスタ形成領域16のシリコン基板10内には、Pウェル20と、P型高濃度不純物層22とが形成されている。P型高濃度不純物層22上には、シリコン基板10上にエピタキシャル成長されたシリコン層48が形成されている。シリコン層48上には、ゲート絶縁膜64aが形成されている。ゲート絶縁膜64a上には、ゲート電極66が形成されている。ゲート電極66の両側のシリコン層48及びシリコン基板10内には、ソース/ドレイン領域78が形成されている。これらにより、低電圧NMOSトランジスタ(LV NMOS)が形成されている。

A P well 20 and a P type high

低電圧PMOSトランジスタは、シリコン基板10の低電圧PMOSトランジスタ形成領域24に形成されている。

The low voltage PMOS transistor is formed in the low voltage PMOS

低電圧PMOSトランジスタ形成領域24のシリコン基板10内には、Nウェル28と、N型高濃度不純物層30とが形成されている。N型高濃度不純物層30上には、シリコン基板10上にエピタキシャル成長されたシリコン層48が形成されている。シリコン層48上には、ゲート絶縁膜64aが形成されている。ゲート絶縁膜64a上には、ゲート電極66が形成されている。ゲート電極66の両側のシリコン層48及びシリコン基板10内には、ソース/ドレイン領域80が形成されている。これらにより、低電圧PMOSトランジスタ(LV PMOS)が形成されている。

An N well 28 and an N type high

高電圧NMOSトランジスタ(HV NMOS)は、シリコン基板10の高電圧NMOSトランジスタ形成領域32に形成されている。

The high voltage NMOS transistor (HV NMOS) is formed in the high voltage NMOS

高電圧NMOSトランジスタ形成領域32のシリコン基板10内には、Pウェル36と、P型不純物層38とが形成されている。P型不純物層38は、接合耐圧やホットキャリア耐性を向上するために、低電圧NMOSトランジスタのP型高濃度不純物層22よりも低濃度且つなだらかな不純物分布になっている。P型不純物層38上には、シリコン基板10上にエピタキシャル成長されたシリコン層48が形成されている。シリコン層48上には、低電圧トランジスタのゲート絶縁膜64aよりも厚いゲート絶縁膜60aが形成されている。ゲート絶縁膜60a上には、ゲート電極66が形成されている。ゲート電極66の両側のシリコン層48及びシリコン基板10内には、ソース/ドレイン領域78が形成されている。これらにより、高電圧NMOSトランジスタ(HV NMOS)が形成されている。

A P well 36 and a P

高電圧PMOSトランジスタ(HV PMOS)は、シリコン基板10の高電圧PMOSトランジスタ形成領域40に形成されている。

The high voltage PMOS transistor (HV PMOS) is formed in the high voltage PMOS

高電圧PMOSトランジスタ形成領域40のシリコン基板10内には、Nウェル44と、N型不純物層46とが形成されている。N型不純物層46は、接合耐圧やホットキャリア耐性を向上するために、低電圧PMOSトランジスタのN型高濃度不純物層30よりも低濃度且つなだらかな不純物分布になっている。N型不純物層46上には、シリコン基板10上にエピタキシャル成長されたシリコン層48が形成されている。シリコン層48上には、低電圧トランジスタのゲート絶縁膜64aよりも厚いゲート絶縁膜60aが形成されている。ゲート絶縁膜60a上には、ゲート電極66が形成されている。ゲート電極66の両側のシリコン層48及びシリコン基板10内には、ソース/ドレイン領域80が形成されている。これらにより、高電圧PMOSトランジスタ(HV PMOS)が形成されている。

An N well 44 and an N

各トランジスタのゲート電極66上及びソース/ドレイン領域78,80上には、金属シリサイド膜84が形成されている。

A

4種類のトランジスタが形成されたシリコン基板10上には、層間絶縁膜86が形成されている。層間絶縁膜86には、トランジスタに接続されたコンタクトプラグ88が埋め込まれている。コンタクトプラグ88には、配線90が接続されている。

An interlayer insulating

このように、本実施形態による半導体装置は、2種類の低電圧トランジスタと、2種類の高電圧トランジスタとを有している。 Thus, the semiconductor device according to the present embodiment has two types of low voltage transistors and two types of high voltage transistors.

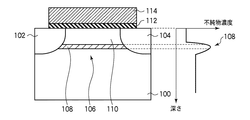

低電圧トランジスタは、いずれも、例えば図2に示すように、チャネル領域106に、急峻な不純物濃度分布を有する高濃度不純物層108と、高濃度不純物層108上にエピタキシャル成長されたノンドープのシリコン層110とを有するものである。このようなトランジスタの構造は、不純物の統計的揺らぎによるトランジスタの閾値電圧ばらつきを抑制するために有効である。閾値電圧ばらつきを抑制するためには、高濃度不純物層108の不純物濃度分布が急峻であることが重要である。

In each of the low voltage transistors, for example, as shown in FIG. 2, a high

急峻な不純物濃度分布を実現するために、低電圧NMOSトランジスタの高濃度不純物層22には、アクセプタ不純物としてのボロンのほかに、ボロンの拡散を防止するための炭素が導入されている。また、低電圧PMOSトランジスタの高濃度不純物層30には、ドナー不純物として拡散定数の小さい砒素又はアンチモンが導入されている。

In order to realize a steep impurity concentration distribution, carbon for preventing boron diffusion is introduced into the high

一方、高電圧NMOSトランジスタの不純物層38及び高電圧PMOSトランジスタの不純物層46を高濃度で急峻な不純物濃度分布とすると、接合耐圧やホットキャリア耐性が低下する。このため、高電圧NMOSトランジスタの不純物層38には、アクセプタ不純物としてボロンは導入されているが、拡散防止作用のある炭素は導入されていない。また、高電圧PMOSトランジスタの不純物層46には、砒素やアンチモンよりも拡散定数の大きいリンが導入されている。これにより、不純物層38及び不純物層46は、高濃度不純物層22及び高濃度不純物層30と比較して、低濃度且つなだらかな分布とされている。

On the other hand, if the

次に、本実施形態による半導体装置の製造方法について図3乃至図20を用いて説明する。 Next, the method for fabricating the semiconductor device according to the present embodiment will be explained with reference to FIGS.

まず、フォトリソグラフィ及びエッチングにより、シリコン基板10の製品形成領域外(例えば、スクライブ領域)に、マスクアライメント用のマークとして用いる溝12を形成する。

First, a

本実施形態による半導体装置の製造方法では、素子分離絶縁膜58の形成前に、ウェルやチャネル不純物層を形成する。溝12は、素子分離絶縁膜58の形成前に行われるリソグラフィー工程(ウェルやチャネル不純物層の形成等)において、マスクアライメント用のマークとして用いられるものである。

In the method for manufacturing the semiconductor device according to the present embodiment, a well and a channel impurity layer are formed before the element

なお、素子分離絶縁膜58の形成前にウェルやチャネル不純物層を形成するのは、シリコン酸化膜14,52,60を除去する際の素子分離絶縁膜58の膜減りを抑制するためである(後述の第1参考例を参照)。

The reason why the well and the channel impurity layer are formed before the formation of the element

次いで、シリコン基板10の全面に、例えば熱酸化法により、シリコン基板10の表面の保護膜としてのシリコン酸化膜14を形成する(図3)。

Next, a

次いで、フォトリソグラフィにより、低電圧NMOSトランジスタ形成領域16を露出し、他の領域を覆うフォトレジスト膜18を形成する。フォトリソグラフィの位置合わせには、溝12のマークを用いる。

Next, a

次いで、フォトレジスト膜18をマスクとしてイオン注入を行い、シリコン基板10の低電圧NMOSトランジスタ形成領域16に、Pウェル20と、P型高濃度不純物層22とを形成する(図4)。

Next, ion implantation is performed using the

Pウェル20は、例えば、ボロンイオン(B+)を、加速エネルギー150keV、ドーズ量7.5×1012cm−2の条件で、基板法線方向に対して傾斜した4方向から、それぞれイオン注入することにより形成する。P型高濃度不純物層22は、ゲルマニウムイオン(Ge+)を、例えば、加速エネルギー50keV、ドーズ量5×1014cm−2の条件で、炭素イオン(C+)を、例えば、加速エネルギー3keV、ドーズ量3×1014cm−2の条件で、ボロンイオンを、例えば、加速エネルギー2keV、ドーズ量3×1013cm−2の条件で、それぞれイオン注入することにより形成する。ゲルマニウムは、シリコン基板10を非晶質化してボロンイオンのチャネリングを防止するとともに、シリコン基板10を非晶質化して炭素が格子点に配される確率を高めるように作用する。格子点に配された炭素は、ボロンの拡散を抑制するように作用する。かかる観点から、ゲルマニウムは、炭素及びボロンよりも先にイオン注入する。Pウェル20は、P型高濃度不純物層22よりも先に形成することが望ましい。

The P well 20, for example, implants boron ions (B + ) from four directions inclined with respect to the substrate normal direction under the conditions of acceleration energy 150 keV and dose amount 7.5 × 10 12 cm −2. To form. The P-type high-

次いで、例えばアッシングにより、フォトレジスト膜18を除去する。

Next, the

次いで、フォトリソグラフィにより、低電圧PMOSトランジスタ形成領域24を露出し、他の領域を覆うフォトレジスト膜26を形成する。フォトリソグラフィの位置合わせには、溝12のマークを用いる。

Next, a

次いで、フォトレジスト膜26をマスクとしてイオン注入を行い、シリコン基板10の低電圧PMOSトランジスタ形成領域24に、Nウェル28と、N型高濃度不純物層30とを形成する(図5)。

Next, ion implantation is performed using the

Nウェル28は、例えば、リンイオン(P+)を、加速エネルギー360keV、ドーズ量7.5×1012cm−2の条件で、基板法線方向に対して傾斜した4方向から、それぞれイオン注入することにより形成する。N型高濃度不純物層30は、例えば、砒素イオンを、例えば、加速エネルギー6keV、ドーズ量2×1013cm−2の条件でイオン注入することにより形成する。Nウェル28は、N型高濃度不純物層30よりも先に形成することが望ましい。

In the N well 28, for example, phosphorus ions (P + ) are respectively ion-implanted from four directions inclined with respect to the substrate normal direction under the conditions of an acceleration energy of 360 keV and a dose amount of 7.5 × 10 12 cm −2. To form. The N-type high

次いで、例えばアッシングにより、フォトレジスト膜26を除去する。

Next, the

次いで、フォトリソグラフィにより、高電圧NMOSトランジスタ形成領域32を露出し、他の領域を覆うフォトレジスト膜34を形成する。フォトリソグラフィの位置合わせには、溝12のマークを用いる。

Next, a

次いで、フォトレジスト膜34をマスクとしてイオン注入を行い、シリコン基板10の高電圧NMOSトランジスタ形成領域32に、Pウェル36と、P型不純物層38とを形成する(図6)。

Next, ion implantation is performed using the

Pウェル36は、例えば、ボロンイオンを、加速エネルギー150keV、ドーズ量7.5×1012cm−2の条件で、基板法線方向に対して傾斜した4方向から、それぞれイオン注入することにより形成する。P型不純物層38は、ボロンイオンを、例えば、加速エネルギー2keV、ドーズ量5×1012cm−2の条件でイオン注入することにより形成する。なお、高電圧NMOSトランジスタでは、チャネル領域の不純物濃度分布をなだらかにして接合耐圧、ホットキャリア耐性を改善する観点から、炭素及びゲルマニウムのイオン注入を行わない。

The P well 36 is formed, for example, by implanting boron ions from four directions inclined with respect to the normal direction of the substrate under conditions of an acceleration energy of 150 keV and a dose of 7.5 × 10 12 cm −2. To do. The P-

次いで、例えばアッシングにより、フォトレジスト膜34を除去する。

Next, the

次いで、フォトリソグラフィにより、高電圧PMOSトランジスタ形成領域40を露出し、他の領域を覆うフォトレジスト膜42を形成する。フォトリソグラフィの位置合わせには、溝12のマークを用いる。

Next, a

次いで、フォトレジスト膜42をマスクとしてイオン注入を行い、シリコン基板10の高電圧PMOSトランジスタ形成領域40に、Nウェル44と、N型不純物層46とを形成する(図7)。

Next, ion implantation is performed using the

Nウェル44は、例えば、リンイオンを、加速エネルギー360keV、ドーズ量7.5×1012cm−2の条件で、基板法線方向に対して傾斜した4方向から、それぞれイオン注入することにより形成する。N型不純物層46は、リンイオンを、例えば、加速エネルギー2keV、ドーズ量5×1012cm−2の条件でイオン注入することにより形成する。なお、高電圧PMOSトランジスタでは、チャネル領域の不純物濃度分布をなだらかにして接合耐圧、ホットキャリア耐性を改善する観点から、砒素よりも拡散定数の大きいリンを用いている。

The N well 44 is formed, for example, by implanting phosphorous ions from four directions inclined with respect to the substrate normal direction under the conditions of an acceleration energy of 360 keV and a dose of 7.5 × 10 12 cm −2. . The N-

次いで、例えばアッシングにより、フォトレジスト膜42を除去する。

Next, the

次いで、不活性雰囲気中で熱処理を行い、シリコン基板10を再結晶化するとともに、注入した不純物を格子位置に配置する。例えば、窒素雰囲気中で、600℃150秒間の熱処理を行い、次いで1000℃0秒間の熱処理を行う。

Next, heat treatment is performed in an inert atmosphere to recrystallize the

次いで、例えばCVD法により、シリコン基板10の表面に、例えば膜厚30nmのノンドープのシリコン層48をエピタキシャル成長する(図8)。

Next, a

次いで、例えばISSG(in-situ steam generation)法により、減圧下でシリコン層48の表面をウェット酸化し、例えば膜厚3nmのシリコン酸化膜52を形成する。処理条件は、例えば、温度を810℃、時間を20秒間とする。

Next, the surface of the

次いで、シリコン酸化膜52上に、例えばLPCVD法により、例えば膜厚70nmのシリコン窒化膜54を堆積する。処理条件は、例えば、温度を700℃、時間を150分間とする。

Next, a

次いで、フォトリソグラフィ及びドライエッチングにより、シリコン窒化膜54、シリコン酸化膜52、シリコン層48、及びシリコン基板10を異方性エッチングし、各トランジスタ形成領域の間の領域を含む素子分離領域に、素子分離溝56を形成する(図9)。なお、フォトリソグラフィの位置合わせには、溝12のマークを用いる。

Next, the

次いで、例えばISSG法により、減圧下でシリコン層48及びシリコン基板10の表面をウェット酸化し、素子分離溝56の内壁に、ライナー膜として、例えば膜厚2nmのシリコン酸化膜を形成する。処理条件は、例えば、温度を810℃、時間を12秒間とする。

Next, the surface of the

次いで、例えば高密度プラズマCVD法により、例えば膜厚500nmのシリコン酸化膜を堆積し、素子分離溝56をシリコン酸化膜によって埋め込む。

Next, a silicon oxide film having a film thickness of, for example, 500 nm is deposited by, for example, high-density plasma CVD, and the

次いで、例えばCMP法により、シリコン窒化膜54上のシリコン酸化膜を除去する。こうして、いわゆるSTI(Shallow Trench Isolation)法により、素子分離溝56に埋め込まれたシリコン酸化膜により、素子分離絶縁膜58を形成する(図10)。

Next, the silicon oxide film on the

次いで、シリコン窒化膜54をマスクとして、例えば弗酸水溶液を用いたウェットエッチングにより、素子分離絶縁膜58を、例えば30nm程度エッチングする。このエッチングは、完成したトランジスタにおいて、シリコン層48の表面の高さと素子分離絶縁膜58の表面の高さとが同程度になるように調整するためのものである。

Next, using the

次いで、例えばホットリン酸を用いたウェットエッチングにより、シリコン窒化膜54を除去する(図11)。

Next, the

次いで、例えば弗酸水溶液を用いたウェットエッチングにより、シリコン酸化膜52を除去する。この際、シリコン酸化膜52を完全に除去するために、膜厚3nmのシリコン酸化膜52に対して、熱酸化膜で5nm相当のエッチングを行う。

Next, the

素子分離絶縁膜58のシリコン酸化膜は、高密度プラズマCVD法により堆積した膜であり、弗酸水溶液に対するエッチングレートは、熱酸化膜の2倍程度である。また、もしシリコン酸化膜中にイオン注入されると、イオン種にも依存するが、エッチングレートは更に増大する。高温の熱処理を施せばエッチングレートを小さくできるが、急峻なチャネル不純物分布を実現されるためには好ましくない。

The silicon oxide film of the element

本実施形態では、素子分離絶縁膜58を形成するシリコン酸化膜に不純物がイオン注入されていないため、シリコン酸化膜52のエッチングに伴う素子分離絶縁膜58の沈み込み量は、10nmと小さく抑えることができる。

In this embodiment, since impurities are not ion-implanted into the silicon oxide film forming the element

次いで、熱酸化法により、例えば膜厚7nmのシリコン酸化膜60を形成する(図12)。処理条件は、例えば、温度を750℃、時間を52分間とする。

Next, a

次いで、フォトリソグラフィにより、高電圧NMOSトランジスタ形成領域32及び高電圧PMOSトランジスタ形成領域40を覆い、他の領域を露出するフォトレジスト膜62を形成する。

Next, a photolithography is performed to form a

次いで、例えば弗酸水溶液を用いたウェットエッチングにより、フォトレジスト膜62をマスクとしてシリコン酸化膜60をエッチングする。これにより、低電圧NOSトランジスタ形成領域16及び低電圧PMOSトランジスタ形成領域24のシリコン酸化膜60を除去する(図13)。この際、シリコン酸化膜60を完全に除去するために、膜厚7nmのシリコン酸化膜60に対して、熱酸化膜で10nm相当のエッチングを行う。

Next, the

素子分離絶縁膜58のシリコン酸化膜は、高密度プラズマCVD法により堆積した膜であり、弗酸水溶液に対するエッチングレートは、熱酸化膜の2倍程度である。また、もしシリコン酸化膜中にイオン注入されると、イオン種にも依存するが、エッチングレートは更に増大する。高温の熱処理を施せばエッチングレートを小さくできるが、急峻なチャネル不純物分布を実現されるためには好ましくない。

The silicon oxide film of the element

本実施形態では、素子分離絶縁膜58を形成するシリコン酸化膜に不純物がイオン注入されていないため、シリコン酸化膜60のエッチングに伴う素子分離絶縁膜58の沈み込み量は、20nmと小さく抑えることができる。

In the present embodiment, since impurities are not ion-implanted into the silicon oxide film forming the element

これにより、シリコン酸化膜52,60を除去する際の素子分離絶縁膜58の沈み込み量の総和は、高電圧トランジスタ形成領域32,40で10nm程度、低電圧トランジスタ形成領域16,24で30nm程度と、小さく抑えることができる。

As a result, the total amount of sinking of the element

次いで、例えばアッシングにより、フォトレジスト膜62を除去する。

Next, the

次いで、熱酸化法により、例えば膜厚2nmのシリコン酸化膜64を形成する。処理条件は、例えば、温度を810℃、時間を8秒間とする。

Next, a

次いで、NO雰囲気中で、例えば870℃、13秒間の熱処理を行い、シリコン酸化膜60,64内に窒素を導入する。

Next, in a NO atmosphere, for example, heat treatment is performed at 870 ° C. for 13 seconds to introduce nitrogen into the

こうして、高電圧NMOSトランジスタ形成領域32及び高電圧PMOSトランジスタ形成領域32に、シリコン酸化膜60のゲート絶縁膜60aを形成する。また、低電圧NMOSトランジスタ形成領域16及び低電圧PMOSトランジスタ形成領域24に、シリコン酸化膜60よりも薄いシリコン酸化膜64のゲート絶縁膜64aを形成する(図14)。

Thus, the

次いで、全面に、例えばLPCVD法により、例えば膜厚100nmのノンドープのポリシリコン膜を堆積する。処理条件は、例えば、温度を605℃とする。 Next, a non-doped polysilicon film of, eg, a 100 nm-thickness is deposited on the entire surface by, eg, LPCVD. The processing conditions are, for example, a temperature of 605 ° C.

次いで、フォトリソグラフィ及びドライエッチングにより、ポリシリコン膜をパターニングし、各トランジスタ形成領域にゲート電極66を形成する(図15)。

Next, the polysilicon film is patterned by photolithography and dry etching, and a

次いで、フォトリソグラフィ及びイオン注入により、高電圧NMOSトランジスタ形成領域32に、ゲート電極66をマスクとしてN型不純物を選択的にイオン注入し、LDD領域となるN型不純物層68を形成する。例えば、リンイオンを、加速エネルギー35keV、ドーズ量2×1013cm−2の条件でイオン注入し、N型不純物層68を形成する。

Next, by photolithography and ion implantation, N-type impurities are selectively ion-implanted into the high-voltage NMOS

次いで、フォトリソグラフィ及びイオン注入により、高電圧PMOSトランジスタ形成領域40に、ゲート電極66をマスクとしてP型不純物を選択的にイオン注入し、LDD領域となるP型不純物層70を形成する。例えば、ボロンイオンを、加速エネルギー10keV、ドーズ量2×1013cm−2の条件でイオン注入し、P型不純物層70を形成する。

Next, by photolithography and ion implantation, P-type impurities are selectively ion-implanted into the high-voltage PMOS

次いで、フォトリソグラフィ及びイオン注入により、低電圧NMOSトランジスタ形成領域16に、ゲート電極66をマスクとしてN型不純物を選択的にイオン注入し、エクステンション領域となるN型不純物層72を形成する。例えば、砒素イオンを、加速エネルギー6keV、ドーズ量2×1014cm−2の条件でイオン注入し、N型不純物層72を形成する。

Next, by photolithography and ion implantation, N-type impurities are selectively ion-implanted into the low-voltage NMOS

次いで、フォトリソグラフィ及びイオン注入により、低電圧PMOSトランジスタ形成領域24に、ゲート電極66をマスクとして選択的にイオン注入し、エクステンション領域となるP型不純物層74を形成する(図16)。例えば、ボロンイオンを、加速エネルギー0.6keV、ドーズ量7×1014cm−2の条件でイオン注入し、P型不純物層74を形成する。

Next, by photolithography and ion implantation, ions are selectively implanted into the low voltage PMOS

次いで、全面に、例えばCVD法により、例えば膜厚80nmのシリコン酸化膜を堆積する。処理条件は、例えば、温度を520℃とする。 Next, a silicon oxide film of, eg, a 80 nm-thickness is deposited on the entire surface by, eg, CVD. The processing conditions are, for example, a temperature of 520 ° C.

次いで、全面に堆積したシリコン酸化膜を異方性エッチングし、ゲート電極66の側壁部分に選択的に残存させる。これにより、シリコン酸化膜のサイドウォールスペーサ76を形成する(図17)。

Next, the silicon oxide film deposited on the entire surface is anisotropically etched to selectively remain on the side wall portion of the

次いで、フォトリソグラフィ及びイオン注入により、低電圧NMOSトランジスタ形成領域16及び高電圧NMOSトランジスタ形成領域32に、ゲート電極66及びサイドウォールスペーサ76をマスクとして選択的にイオン注入する。これにより、ソース/ドレイン領域となるN型不純物層78を形成するとともに、NMOSトランジスタのゲート電極66にN型不純物を添加する。イオン注入条件は、例えば、リンイオンを、加速エネルギー8keV、ドーズ量1.2×1016cm−2とする。

Next, ions are selectively implanted into the low voltage NMOS

次いで、フォトリソグラフィ及びイオン注入により、低電圧PMOSトランジスタ形成領域24及び高電圧PMOSトランジスタ形成領域40に、ゲート電極66及びサイドウォールスペーサ76をマスクとして選択的にイオン注入する。これにより、ソース/ドレイン領域となるP型不純物層80を形成するとともに、PMOSトランジスタのゲート電極66にP型不純物を添加する。イオン注入条件は、例えば、ボロンイオンを、加速エネルギー4keV、ドーズ量6×1015cm−2とする。

Next, ions are selectively implanted into the low-voltage PMOS

次いで、不活性ガス雰囲気中で、例えば1025℃、0秒間の短時間熱処理を行い、注入した不純物の活性化及びゲート電極66中の拡散を行う。1025℃、0秒間の短時間熱処理は、ゲート電極66とゲート絶縁膜との界面まで不純物を拡散させるのに十分である。

Next, short-time heat treatment is performed in an inert gas atmosphere at 1025 ° C. for 0 second, for example, to activate the implanted impurities and diffuse the

また、低電圧NMOSトランジスタのチャネル部は炭素がボロンの拡散を抑制することにより、低電圧PMOSトランジスタのチャネル部は砒素の拡散が遅いことにより、急峻な不純物分布を維持することができる。一方、高電圧NMOSトランジスタのチャネル部は炭素が導入されていないことにより拡散は抑制されず、高電圧PMOSトランジスタのチャネル部には砒素よりも拡散定数の大きいリンが導入されているため、なだらかな不純物分布を形成することができる。 The channel portion of the low-voltage NMOS transistor can maintain a steep impurity distribution by suppressing diffusion of boron by carbon, and the channel portion of the low-voltage PMOS transistor can be diffused slowly by arsenic. On the other hand, diffusion is not suppressed in the channel portion of the high-voltage NMOS transistor because carbon is not introduced, and phosphorus having a diffusion constant larger than that of arsenic is introduced in the channel portion of the high-voltage PMOS transistor. Impurity distribution can be formed.

こうして、シリコン基板10上に、4種類のトランジスタを完成する。すなわち、低電圧NMOSトランジスタ形成領域16に、低電圧NMOSトランジスタ(LV NMOS)を形成する。また、低電圧PMOSトランジスタ形成領域24に、低電圧PMOSトランジスタ(LV PMOS)を形成する。また、高電圧NMOSトランジスタ形成領域に、高電圧NMOSトランジスタ(HV NMOS)を形成する。また、高電圧PMOSトランジスタ形成領域に、高電圧PMOSトランジスタ(HV PMOS)を形成する(図18)。

Thus, four types of transistors are completed on the

次いで、サリサイドプロセスにより、ゲート電極66上、N型不純物層78上、及びP型不純物層80上に、金属シリサイド膜84、例えばコバルトシリサイド膜を形成する。

Next, a

次いで、全面に、例えばCVD法により、例えば膜厚50nmのシリコン窒化膜を堆積し、エッチングストッパ膜としてのシリコン窒化膜を形成する。 Next, a silicon nitride film of, eg, a 50 nm-thickness is deposited on the entire surface by, eg, CVD, to form a silicon nitride film as an etching stopper film.

次いで、シリコン窒化膜上に、例えば高密度プラズマCVD法により、例えば膜厚500nmのシリコン酸化膜を堆積する。 Next, a silicon oxide film of, eg, a 500 nm-thickness is deposited on the silicon nitride film by, eg, high density plasma CVD.

これにより、シリコン窒化膜とシリコン酸化膜との積層膜の層間絶縁膜86を形成する。

Thereby, an

次いで、例えばCMP法により、層間絶縁膜86の表面を研磨し、平坦化する。

Next, the surface of the

この後、層間絶縁膜86に埋め込まれたコンタクトプラグ88、コンタクトプラグ88に接続された配線90等を形成し、半導体装置を完成する(図19)。

Thereafter, contact plugs 88 embedded in the

このように、本実施形態によれば、低電圧NMOSトランジスタの高濃度不純物層22をボロン及び炭素を含む不純物層により、低電圧PMOSトランジスタの高濃度不純物層30を砒素を含む不純物層により形成するので、急峻な不純物分布を実現することができる。他方、高電圧NMOSトランジスタの不純物層38をボロンを含む不純物層により、高電圧PMOSトランジスタの不純物層46をリンを含む不純物層により形成するので、なだらかな不純物分布を実現することができる。これにより、閾値電圧の安定した信頼性の高い低電圧トランジスタを実現できるとともに、接合耐圧やホットキャリア耐性の高い高電圧トランジスタを実現することができる。

Thus, according to the present embodiment, the high-

また、ウェル及びチャネル不純物層を形成した後に素子分離絶縁膜を形成するので、素子分離絶縁膜に高濃度のチャネル不純物が導入されるのを防止することができ、エッチング工程においける素子分離絶縁膜の膜減りを大幅に抑制することができる。これにより、基板表面の平坦性が向上するとともに、寄生トランジスタチャネルの発生を防止することができ、信頼性が高く高性能の半導体装置を実現することができる。 In addition, since the element isolation insulating film is formed after the well and channel impurity layers are formed, it is possible to prevent high-concentration channel impurities from being introduced into the element isolation insulating film, and to isolate the element isolation in the etching process. The film loss of the film can be greatly suppressed. As a result, the flatness of the substrate surface is improved and the generation of a parasitic transistor channel can be prevented, and a highly reliable semiconductor device with high performance can be realized.

[第2実施形態]

第2実施形態による半導体装置の製造方法について図20乃至図23を用いて説明する。図1乃至図19に示す第1実施形態による半導体装置及びその製造方法と同様の構成要素には同一の符号を付し説明を省略し或いは簡潔にする。

[Second Embodiment]

A method for fabricating a semiconductor device according to the second embodiment will be described with reference to FIGS. The same components as those of the semiconductor device and the manufacturing method thereof according to the first embodiment shown in FIGS. 1 to 19 are denoted by the same reference numerals, and description thereof will be omitted or simplified.

図20乃至図23は、本参考例による半導体装置の製造方法を示す工程断面図である。 20 to 23 are process cross-sectional views illustrating a method of manufacturing a semiconductor device according to this reference example.

第1実施形態による半導体装置の製造方法では、エッチングに伴う素子分離絶縁膜58の沈み込み量を、高電圧トランジスタ形成領域32,40で10nm程度、低電圧トランジスタ形成領域16,24で30nm程度と、小さく抑えることができた。しかしながら、高電圧トランジスタ形成領域32,40と比較すると、低電圧トランジスタ形成領域16,24における素子分離絶縁膜58の沈み込み量は大きい。

In the manufacturing method of the semiconductor device according to the first embodiment, the amount of sinking of the element

本実施形態では、低電圧トランジスタ形成領域16,24における素子分離絶縁膜58の沈み込み量を更に抑制しうる方法について説明する。

In the present embodiment, a method for further suppressing the sinking amount of the element

まず、図3乃至図11に示す第1実施形態による半導体装置の製造方法と同様にして、活性領域を画定する素子分離絶縁膜58を形成する。活性領域の表面には、膜厚3nm程度のシリコン酸化膜52が残存している(図20)。

First, an element

次いで、フォトリソグラフィにより、低電圧NMOSトランジスタ形成領域16及び低電圧PMOSトランジスタ形成領域24を覆い、高電圧NMOSトランジスタ形成領域32及び高電圧PMOSトランジスタ形成領域40を露出するフォトレジスト膜92を形成する。

Next, a

次いで、例えば弗酸水溶液を用いたウェットエッチングにより、フォトレジスト膜92をマスクとしてシリコン酸化膜52をエッチングする。これにより、高電圧NMOSトランジスタ形成領域32及び高電圧PMOSトランジスタ形成領域40のシリコン酸化膜52を除去する(図21)。

Next, the

この際、シリコン酸化膜52を完全に除去するために、膜厚3nmのシリコン酸化膜52に対して、熱酸化膜で5nm相当のエッチングを行う。

At this time, in order to completely remove the

素子分離絶縁膜58のシリコン酸化膜は、高密度プラズマCVD法により堆積した膜であり、弗酸水溶液に対するエッチングレートは、熱酸化膜の2倍程度である。また、もしシリコン酸化膜中にイオン注入されると、イオン種にも依存するが、エッチングレートは更に増大する。高温の熱処理を施せばエッチングレートを小さくできるが、急峻なチャネル不純物分布を実現されるためには好ましくない。

The silicon oxide film of the element

本実施形態では、素子分離絶縁膜58を形成するシリコン酸化膜に不純物がイオン注入されていないため、シリコン酸化膜52のエッチングに伴う高電圧トランジスタ形成領域32,40の素子分離絶縁膜58の沈み込み量は、10nmと小さく抑えることができる。一方、低電圧トランジスタ形成領域16,24はフォトレジスト膜92で覆われているため、低電圧トランジスタ形成領域16,24の素子分離絶縁膜58はエッチングされない。

In this embodiment, since impurities are not ion-implanted into the silicon oxide film forming the element

次いで、例えばアッシングにより、フォトレジスト膜92を除去する。

Next, the

次いで、熱酸化法により、例えば膜厚7nmのシリコン酸化膜60を形成する(図22)。処理条件は、例えば、温度を750℃、時間を52分間とする。

Next, a

この際、低電圧トランジスタ形成領域16,24に残存しているシリコン酸化膜52も追加酸化され、膜厚が8nm程度となる。

At this time, the

次いで、フォトリソグラフィにより、高電圧NMOSトランジスタ形成領域32及び高電圧PMOSトランジスタ形成領域40を覆い、低電圧NMOSトランジスタ形成領域16及び低電圧PMOSトランジスタ形成領域24を露出するフォトレジスト膜62を形成する。

Next, a

次いで、例えば弗酸水溶液を用いたウェットエッチングにより、フォトレジスト膜62をマスクとしてシリコン酸化膜60をエッチングする。これにより、低電圧NOSトランジスタ形成領域16及び低電圧PMOSトランジスタ形成領域24のシリコン酸化膜60を除去する(図23)。この際、シリコン酸化膜52を完全に除去するために、膜厚8nmのシリコン酸化膜52に対して、熱酸化膜で11nm相当のエッチングを行う。

Next, the

素子分離絶縁膜58のシリコン酸化膜は、高密度プラズマCVD法により堆積した膜であり、弗酸水溶液に対するエッチングレートは、熱酸化膜の2倍程度である。また、もしシリコン酸化膜中にイオン注入されると、イオン種にも依存するが、エッチングレートは更に増大する。高温の熱処理を施せばエッチングレートを小さくできるが、急峻なチャネル不純物分布を実現されるためには好ましくない。

The silicon oxide film of the element

本実施形態では、素子分離絶縁膜58を形成するシリコン酸化膜に不純物がイオン注入されていないため、シリコン酸化膜52のエッチングに伴う素子分離絶縁膜58の沈み込み量は、22nmと小さく抑えることができる。

In this embodiment, since impurities are not ion-implanted into the silicon oxide film forming the element

これにより、シリコン酸化膜52,60を除去する際の素子分離絶縁膜58の沈み込み量の総和は、高電圧トランジスタ形成領域32,40で10nm程度、低電圧トランジスタ形成領域16,24で22nm程度と、小さく抑えることができる。

As a result, the total amount of sinking of the element

第1実施形態による半導体装置の製造方法と比較すると、低電圧トランジスタ形成領域16,24における素子分離絶縁膜58の沈み込み量を、25%程度改善することができた。

Compared with the manufacturing method of the semiconductor device according to the first embodiment, the sinking amount of the element

この後、図14乃至図19に示す第1実施形態による半導体装置の製造方法と同様にして、半導体装置を完成する。 Thereafter, the semiconductor device is completed in the same manner as in the method of manufacturing the semiconductor device according to the first embodiment shown in FIGS.

このように、本実施形態によれば、高電圧トランジスタのゲート絶縁膜を形成する前に、高電圧トランジスタ形成領域に形成されている絶縁膜を選択的に除去するので、低電圧トランジスタ形成領域の素子分離絶縁膜の膜減りを大幅に抑制することができる。これにより、基板表面の平坦性が向上し、信頼性が高く高性能の半導体装置を実現することができる。 As described above, according to this embodiment, the insulating film formed in the high voltage transistor formation region is selectively removed before forming the gate insulating film of the high voltage transistor. The reduction of the element isolation insulating film can be greatly suppressed. Thereby, the flatness of the substrate surface is improved, and a highly reliable semiconductor device with high performance can be realized.

[第1参考例]

第1参考例による半導体装置の製造方法について図24乃至図26を用いて説明する。図1乃至図23に示す第1及び第2実施形態による半導体装置及びその製造方法と同様の構成要素には同一の符号を付し説明を省略し或いは簡潔にする。

[First Reference Example]

A method of manufacturing a semiconductor device according to the first reference example will be described with reference to FIGS. The same components as those in the semiconductor device and the manufacturing method thereof according to the first and second embodiments shown in FIGS. 1 to 23 are denoted by the same reference numerals, and description thereof is omitted or simplified.

図24乃至図26は、本参考例による半導体装置の製造方法を示す工程断面図である。 24 to 26 are process cross-sectional views illustrating a method of manufacturing a semiconductor device according to this reference example.

本参考例では、素子分離絶縁膜58の形成の後にP型高濃度不純物層22及びN型高濃度不純物層30等のチャネルイオン注入を行うプロセスについて説明する。

In this reference example, a process for performing channel ion implantation of the P-type high

まず、シリコン基板10に、STI法により、素子分離絶縁膜58を形成する。

First, the element

次いで、素子分離絶縁膜58により画定された活性領域上に、保護酸化膜としてのシリコン酸化膜14を形成する(図24(a))。

Next, a

次いで、フォトリソグラフィ及びイオン注入により、低電圧NMOSトランジスタ形成領域16に、P型高濃度不純物層22を形成する。

Next, a P-type high

次いで、フォトリソグラフィ及びイオン注入により、低電圧PMOSトランジスタ形成領域24に、N型高濃度不純物層30を形成する。

Next, an N-type high

次いで、フォトリソグラフィ及びイオン注入により、高電圧NMOSトランジスタ形成領域32に、P型不純物層38を形成する。

Next, a P-

次いで、フォトリソグラフィ及びイオン注入により、高電圧PMOSトランジスタ形成領域40に、N型不純物層46を形成する(図24(b))。

Next, an N-

次いで、熱処理を行い、イオン注入ダメージを回復するとともに、注入した不純物を活性化する。 Next, heat treatment is performed to recover the ion implantation damage and activate the implanted impurities.

次いで、弗酸水溶液を用いたウェットエッチングにより、シリコン酸化膜14を除去し、活性領域のシリコン基板10を露出する。

Next, the

このとき、素子分離絶縁膜58にはP型高濃度不純物層22及びN型高濃度不純物層30の形成の際のイオン注入によって高濃度の不純物が導入されているため、素子分離絶縁膜58におけるエッチングが増速される。特に、急峻な不純物プロファイルを得る等の目的で、N型不純物層30の形成のために砒素をイオン注入した場合には、低電圧PMOSトランジスタ形成領域24におけるエッチングレートの増加は顕著である。

At this time, since the high-concentration impurities are introduced into the element

この結果、低電圧NMOSトランジスタ形成領域16及び低電圧PMOSトランジスタ形成領域24において、シリコン酸化膜14のエッチングの際に素子分離絶縁膜58が過剰にエッチングされ、活性領域の側面部分が露出されてしまう。

As a result, in the low voltage NMOS

なお、P型不純物層38及びN型不純物層46はP型高濃度不純物層22及びN型高濃度不純物層30と比較すると不純物濃度が1桁程度低い。このため、高電圧NMOSトランジスタ形成領域32及び高電圧PMOSトランジスタ形成領域40における素子分離絶縁膜58のエッチング量は、比較的に少ない。

The P-

次いで、シリコン基板10上に、ノンドープのシリコン層48をエピタキシャル成長する(図25(a))。この際、シリコン層48の成長は活性領域の表面及び側面から進行するため、異なる面方位に沿って形成されたシリコン層が重なる部分、すなわち素子分離絶縁膜58の端部に、結晶欠陥が導入されてしてしまう。

Next, a

シリコン層48に導入された結晶欠陥は、リーク電流の増加等、トランジスタの特性に多大な影響を与えるため、好ましくない。

Crystal defects introduced into the

次いで、活性領域上に、高電圧NMOSトランジスタ及び高電圧PMOSトランジスタ用のゲート絶縁膜60aとなるシリコン酸化膜60を形成する(図25(b))。

Next, a

次いで、フォトリソグラフィ及びウェットエッチングにより、低電圧NMOSトランジスタ形成領域16及び低電圧PMOSトランジスタ形成領域24のシリコン酸化膜60を選択的に除去する(図26(a))。

Next, the

この際、シリコン酸化膜60のエッチングとともに素子分離絶縁膜58もエッチングされ、低電圧NMOSトランジスタ形成領域16及び低電圧PMOSトランジスタ形成領域24では、素子分離絶縁膜58の端部においてシリコン層48の下面が露出される。

At this time, the element

次いで、低電圧NMOSトランジスタ領域16及び低電圧PMOSトランジスタ領域24の活性領域上に、ゲート絶縁膜64aとなるシリコン酸化膜64を形成する(図26(b))。

Next, a

この後、ゲート絶縁膜64a上にゲート電極66を形成すると、素子分離絶縁膜58の端部のシリコン層48の下方には、シリコン層48を介さずにゲート電極66と対向する寄生トランジスタチャネルが形成されてしまう。素子分離絶縁膜58の形成後にシリコン層48をエピタキシャル成長し、次いで、膜厚の異なる2種類以上のゲート絶縁膜を形成すると、この寄生トランジスタチャネルの形成は避けられない。

Thereafter, when the

また、素子分離絶縁膜58の膜減りは、以降のエッチングプロセスにおいても生じる。素子分離絶縁膜58の膜減りが生じると、基板表面の平坦性が低下し、後工程のプロセスに不具合を生じることもある。

Further, the reduction of the element

[第2参考例]

第2参考例による半導体装置の製造方法について図27乃至図32を用いて説明する。図1乃至図23に示す第1及び第2実施形態による半導体装置及びその製造方法と同様の構成要素には同一の符号を付し説明を省略し或いは簡潔にする。

[Second Reference Example]

A method of manufacturing a semiconductor device according to the second reference example will be described with reference to FIGS. The same components as those in the semiconductor device and the manufacturing method thereof according to the first and second embodiments shown in FIGS. 1 to 23 are denoted by the same reference numerals, and description thereof is omitted or simplified.

図27乃至図32は、本参考例による半導体装置の製造方法を示す工程断面図である。 27 to 32 are process cross-sectional views illustrating a method of manufacturing a semiconductor device according to this reference example.

本参考例では、P型高濃度不純物層22及びN型高濃度不純物層30の形成の後に素子分離絶縁膜58を形成するプロセスについて説明する。

In this reference example, a process for forming the element

まず、フォトリソグラフィ及びエッチングにより、シリコン基板10の製品形成領域外に、マスクアライメント用のマークとして用いる溝12を形成する。

First,

次いで、シリコン基板10の全面に、シリコン基板10の表面の保護膜としてのシリコン酸化膜14を形成する(図27(a))。

Next, a

次いで、フォトリソグラフィ及びイオン注入により、低電圧NMOSトランジスタ形成領域16及び高電圧NMOSトランジスタ形成領域32に、Pウェル20及びP型高濃度不純物層22を形成する。Pウェル20及びP型高濃度不純物層22は、例えば、ボロン又は弗化ボロン(BF2)を2重にイオン注入することにより形成する。

Next, the P well 20 and the P type high

次いで、フォトリソグラフィ及びイオン注入により、低電圧PMOSトランジスタ形成領域24及び高電圧PMOSトランジスタ形成領域40に、Nウェル28及びN型高濃度不純物層30を形成する(図27(b))。Nウェル28及びN型高濃度不純物層30は、例えば、リン又は砒素若しくはアンチモン(Sb)を2重にイオン注入することにより形成する。

Next, the N well 28 and the N type high

次いで、熱処理を行い、イオン注入ダメージを回復するとともに、注入した不純物を活性化する。 Next, heat treatment is performed to recover the ion implantation damage and activate the implanted impurities.

次いで、弗酸水溶液を用いたウェットエッチングにより、シリコン酸化膜14を除去する。

Next, the

次いで、シリコン基板10上に、ノンドープのシリコン層48をエピタキシャル成長する(図28(a))。

Next, a

次いで、STI法により、シリコン基板10及びシリコン層48に、素子分離絶縁膜58を形成する(図28(b))。

Next, an element

次いで、活性領域上に、高電圧NMOSトランジスタ及び高電圧PMOSトランジスタ用のゲート絶縁膜60aとなるシリコン酸化膜60を形成する(図29(a))。

Next, a

次いで、フォトリソグラフィ及びウェットエッチングにより、低電圧NMOSトランジスタ形成領域16及び低電圧PMOSトランジスタ形成領域24のシリコン酸化膜60を選択的に除去する(図29(b))。

Next, the

次いで、低電圧NMOSトランジスタ領域16及び低電圧PMOSトランジスタ領域24の活性領域上に、ゲート絶縁膜64aとなるシリコン酸化膜64を形成する(図30(a))。

Next, a

次いで、全面に、ポリシリコン膜66aを形成する。

Next, a

次いで、フォトリソグラフィ及びイオン注入により、低電圧NMOSトランジスタ領域16及び高電圧NMOSトランジスタ形成領域32のポリシリコン膜66aに、N型不純物を添加する。また、低電圧PMOSトランジスタ領域24及び高電圧PMOSトランジスタ形成領域40のポリシリコン膜66aに、P型不純物を添加する(図30(b))。

Next, an N-type impurity is added to the

次いで、ポリシリコン膜66aをパターニングし、各トランジスタ形成領域に、ゲート電極66を形成する。

Next, the

次いで、フォトリソグラフィ及びイオン注入により、低電圧NMOSトランジスタ領域16に、エクステンション領域となるN型不純物層72を形成する。また、低電圧PMOSトランジスタ領域24に、エクステンション領域となるP型不純物層74を形成する。また、高電圧NMOSトランジスタ形成領域32に、LDD領域となるN型不純物層68を形成する。また、高電圧PMOSトランジスタ形成領域40に、LDD領域となるP型不純物層70を形成する(図31(a))。

Next, an N-

次いで、シリコン酸化膜を堆積して異方性エッチングし、ゲート電極66の側壁部分に、サイドウォールスペーサ68を形成する(図31(b))。

Next, a silicon oxide film is deposited and anisotropically etched to form

次いで、フォトリソグラフィ及びイオン注入により、低電圧NMOSトランジスタ領域16及び高電圧NMOSトランジスタ形成領域32に、ソース/ドレイン領域となるN型不純物層78を形成する。また、低電圧PMOSトランジスタ領域24及び高電圧PMOSトランジスタ形成領域40に、ソース/ドレイン領域となるP型不純物層80を形成する(図32)。

Next, an N-

次いで、熱処理を行い、注入した不純物を活性化する。 Next, heat treatment is performed to activate the implanted impurities.

こうして、シリコン基板10上に、低電圧NMOSトランジスタと、低電圧PMOSトランジスタと、高電圧NMOSトランジスタと、高電圧PMOSトランジスタを形成する。

Thus, a low voltage NMOS transistor, a low voltage PMOS transistor, a high voltage NMOS transistor, and a high voltage PMOS transistor are formed on the

本参考例では、低電圧トランジスタのウェル(チャネル不純物層を含む)と、高電圧トランジスタのウェル(チャネル不純物層を含む)とを同時に形成している。しかしながら、低電圧トランジスタのチャネル不純物層には急峻な不純物分布が求められる一方、高電圧トランジスタのチャネル不純物層層は急峻な不純物分布を必要としない。むしろ、急峻な分布による接合耐圧の低下やホットキャリア耐性の低下を生じるため、好ましくない。かかる観点から、低電圧トランジスタのウェルと高電圧トランジスタのウェルとは、別々に形成することが望ましい。 In this reference example, the well of the low voltage transistor (including the channel impurity layer) and the well of the high voltage transistor (including the channel impurity layer) are formed at the same time. However, a steep impurity distribution is required for the channel impurity layer of the low-voltage transistor, while the channel impurity layer layer of the high-voltage transistor does not require a steep impurity distribution. Rather, it is not preferable because it causes a decrease in junction breakdown voltage and a decrease in hot carrier resistance due to a steep distribution. From this point of view, it is desirable to form the well of the low voltage transistor and the well of the high voltage transistor separately.

[変形実施形態]

上記実施形態に限らず種々の変形が可能である。

[Modified Embodiment]

The present invention is not limited to the above embodiment, and various modifications are possible.

例えば、上記実施形態では、P型高濃度不純物層22を形成する際に、非晶質化のためにゲルマニウムをイオン注入しているが、非晶質化に用いるイオン種は、これに限定されるものではない。例えば、シリコン、窒素、アルゴン、キセノン等を用いるようにしてもよい。

For example, in the above embodiment, germanium is ion-implanted for amorphization when forming the P-type high-

また、上記実施形態では、下地の半導体基板としてシリコン基板を用いたが、下地の半導体基板は、必ずしもバルクのシリコン基板である必要はない。SOI基板など、他の半導体基板を適用してもよい。 In the above embodiment, a silicon substrate is used as the underlying semiconductor substrate. However, the underlying semiconductor substrate is not necessarily a bulk silicon substrate. Other semiconductor substrates such as an SOI substrate may be applied.

また、上記実施形態では、エピタキシャル半導体層としてシリコン層を用いたが、必ずしもシリコン層である必要はない。シリコン層の代わりに、SiGe層やSiC層等の他の半導体層を適用してもよい。 Moreover, in the said embodiment, although the silicon layer was used as an epitaxial semiconductor layer, it does not necessarily need to be a silicon layer. Instead of the silicon layer, another semiconductor layer such as a SiGe layer or a SiC layer may be applied.

また、上記実施形態に記載した半導体装置の構造、構成材料、製造条件等は、一例を示したものにすぎず、当業者の技術常識等に応じて適宜修正や変更が可能である。 In addition, the structure, constituent materials, manufacturing conditions, and the like of the semiconductor device described in the above embodiment are merely examples, and can be appropriately modified or changed according to technical common sense of those skilled in the art.

以上の実施形態に関し、更に以下の付記を開示する。 Regarding the above embodiment, the following additional notes are disclosed.

(付記1) 半導体基板の第1の領域を露出する第1のマスクを用いて、前記第1の領域に、第1導電型の第1の不純物をイオン注入する工程と、

前記半導体基板の第2の領域を露出する第2のマスクを用いて、前記第2の領域に、第1の不純物よりも拡散定数の小さい前記第1導電型の第2の不純物、又は、前記第1の不純物及び前記第1の不純物の拡散を抑制する第3の不純物をイオン注入する工程と、

前記第1の不純物及び前記第2の不純物を活性化し、前記第1の領域に第1の不純物層を、前記第2の領域に第2の不純物層を、それぞれ形成する工程と、

前記第1の不純物層及び前記第2の不純物層が形成された前記半導体基板上に、半導体層をエピタキシャル成長する工程と、

前記半導体層の前記第1の領域上及び前記第2の領域上に、第1のゲート絶縁膜を成長する工程と、

前記第2の領域を露出する第3のマスクを用いて、前記第2の領域の前記第1のゲート絶縁膜を除去する工程と、

前記半導体層の前記第2の領域上に、前記第1のゲート絶縁膜よりも薄い第2のゲート絶縁膜を成長する工程と、

前記第1のゲート絶縁膜上に第1のゲート電極を、前記第2のゲート絶縁膜上に第2のゲート電極を、それぞれ形成する工程と

を有することを特徴とする半導体装置の製造方法。

(Additional remark 1) The process of ion-implanting the 1st conductivity type 1st impurity into the said 1st area | region using the 1st mask which exposes the 1st area | region of a semiconductor substrate,

Using the second mask exposing the second region of the semiconductor substrate, the second impurity of the first conductivity type having a smaller diffusion constant than the first impurity in the second region; or Ion-implanting a first impurity and a third impurity that suppresses diffusion of the first impurity;

Activating the first impurity and the second impurity to form a first impurity layer in the first region and a second impurity layer in the second region;

Epitaxially growing a semiconductor layer on the semiconductor substrate on which the first impurity layer and the second impurity layer are formed;

Growing a first gate insulating film on the first region and the second region of the semiconductor layer;

Removing the first gate insulating film in the second region using a third mask exposing the second region;

Growing a second gate insulating film thinner than the first gate insulating film on the second region of the semiconductor layer;

Forming a first gate electrode on the first gate insulating film and forming a second gate electrode on the second gate insulating film, respectively.

(付記2) 付記1記載の半導体装置の製造方法において、

前記第1の不純物は、ボロンであり、

前記第3の不純物は、炭素である

ことを特徴とする半導体装置の製造方法。

(Additional remark 2) In the manufacturing method of the semiconductor device of Additional remark 1,

The first impurity is boron;

The method for manufacturing a semiconductor device, wherein the third impurity is carbon.

(付記3) 付記2記載の半導体装置の製造方法において、

前記第1の不純物及び前記第3の不純物のイオン注入に先立ち、前記第2の領域に、前記半導体基板の表面領域を非晶質化するための第4の不純物をイオン注入する

ことを特徴とする半導体装置の製造方法。

(Additional remark 3) In the manufacturing method of the semiconductor device of

Prior to the ion implantation of the first impurity and the third impurity, a fourth impurity for amorphizing the surface region of the semiconductor substrate is ion-implanted into the second region. A method for manufacturing a semiconductor device.

(付記4) 付記3記載の半導体装置の製造方法において、

前記第4の不純物は、ゲルマニウムである

ことを特徴とする半導体装置の製造方法。

(Additional remark 4) In the manufacturing method of the semiconductor device of

The method for manufacturing a semiconductor device, wherein the fourth impurity is germanium.

(付記5) 付記1記載の半導体装置の製造方法において、

前記第1の不純物は、リンであり、

前記第2の不純物は、砒素である

ことを特徴とする半導体装置の製造方法。

(Additional remark 5) In the manufacturing method of the semiconductor device of Additional remark 1,

The first impurity is phosphorus;

The method of manufacturing a semiconductor device, wherein the second impurity is arsenic.

(付記6) 付記1乃至4のいずれか1項に記載の半導体装置の製造方法において、

前記半導体層を形成する工程の後、前記半導体層を形成した前記半導体基板に素子分離絶縁膜を形成する工程を更に有する

ことを特徴とする半導体装置の製造方法。

(Appendix 6) In the method for manufacturing a semiconductor device according to any one of appendices 1 to 4,

After the step of forming the semiconductor layer, the method further includes the step of forming an element isolation insulating film on the semiconductor substrate on which the semiconductor layer is formed.

(付記7) 付記1乃至5のいずれか1項に記載の半導体装置の製造方法において、

前記第1のゲート絶縁膜を成長する工程では、前記第1の領域を露出する第3のマスクを用いてエッチングを行い、前記第1の領域の前記半導体層の表面を露出した後、前記第1のゲート絶縁膜を成長する

ことを特徴とする半導体装置の製造方法。

(Appendix 7) In the method for manufacturing a semiconductor device according to any one of appendices 1 to 5,

In the step of growing the first gate insulating film, etching is performed using a third mask that exposes the first region, the surface of the semiconductor layer in the first region is exposed, and then the first region is exposed. A method for manufacturing a semiconductor device, comprising: growing a gate insulating film.

(付記8) 半導体基板の第1の領域を露出する第1のマスクを用いて、前記第1の領域に、第1の不純物をイオン注入する工程と、

前記半導体基板の第2の領域を露出する第2のマスクを用いて、前記第2の領域に、前記第1の不純物と同導電型の第2の不純物をイオン注入する工程と、

前記半導体基板の第3の領域を露出する第3のマスクを用いて、前記第3の領域に、前記第1の不純物と逆導電型の第3の不純物をイオン注入する工程と、

前記半導体基板の第4の領域を露出する第4のマスクを用いて、前記第4の領域に、前記第1の不純物と逆導電型の第4の不純物をイオン注入する工程と、

前記第1の不純物、第2の不純物、第3の不純物、及び前記第4の不純物を活性化し、前記第1の領域に第1の不純物層を、前記第2の領域に第2の不純物層を、前記第3の領域に第3の不純物層を、前記第4の領域に第4の不純物層を、それぞれ形成する工程と、

前記第1の不純物層、前記第2の不純物層、前記第3の不純物層、及び前記第4の不純物層が形成された前記半導体基板上に、半導体層をエピタキシャル成長する工程と、

前記半導体層の前記第1の領域上、前記第2の領域上、前記第3の領域上、及び前記第4の領域上に、第1のゲート絶縁膜を成長する工程と、

前記第2の領域及び前記第4の領域を露出する第5のマスクを用いて、前記第2の領域及び前記第4の領域の前記第1のゲート絶縁膜を除去する工程と、

前記半導体層の前記第2の領域上及び前記第4の領域上に、前記第1のゲート絶縁膜よりも薄い第2のゲート絶縁膜を成長する工程と、

前記第1の領域の前記第1のゲート絶縁膜上に第1のゲート電極を、前記第2の領域の前記第2のゲート絶縁膜上に第2のゲート電極を、前記第3の領域の前記第1のゲート絶縁膜上に第3のゲート電極を、前記第4の領域の前記第2のゲート絶縁膜上に第4のゲート電極を、それぞれ形成する工程と

を有することを特徴とする半導体装置の製造方法。

(Appendix 8) Ion implantation of a first impurity into the first region using a first mask exposing the first region of the semiconductor substrate;

Ion-implanting a second impurity having the same conductivity type as the first impurity into the second region using a second mask exposing the second region of the semiconductor substrate;

Ion-implanting a third impurity having a conductivity type opposite to that of the first impurity into the third region by using a third mask exposing the third region of the semiconductor substrate;

Ion-implanting a fourth impurity having a conductivity type opposite to the first impurity into the fourth region using a fourth mask exposing the fourth region of the semiconductor substrate;

The first impurity, the second impurity, the third impurity, and the fourth impurity are activated, a first impurity layer is formed in the first region, and a second impurity layer is formed in the second region. Forming a third impurity layer in the third region and a fourth impurity layer in the fourth region;

Epitaxially growing a semiconductor layer on the semiconductor substrate on which the first impurity layer, the second impurity layer, the third impurity layer, and the fourth impurity layer are formed;

Growing a first gate insulating film on the first region, on the second region, on the third region, and on the fourth region of the semiconductor layer;

Removing the first gate insulating film in the second region and the fourth region using a fifth mask exposing the second region and the fourth region;

Growing a second gate insulating film thinner than the first gate insulating film on the second region and the fourth region of the semiconductor layer;

A first gate electrode on the first gate insulating film in the first region, a second gate electrode on the second gate insulating film in the second region, and a third gate electrode on the third region. Forming a third gate electrode on the first gate insulating film and forming a fourth gate electrode on the second gate insulating film in the fourth region, respectively. A method for manufacturing a semiconductor device.

(付記9) 付記8記載の半導体装置の製造方法において、

前記第1の不純物は、ボロンであり、

前記第2の不純物は、ボロンと炭素を含み、

前記第3の不純物は、リンであり、

前記第4の不純物は、砒素又はアンチモンである

ことを特徴とする半導体装置の製造方法。

(Supplementary note 9) In the method for manufacturing a semiconductor device according to

The first impurity is boron;

The second impurity includes boron and carbon,

The third impurity is phosphorus;

The method of manufacturing a semiconductor device, wherein the fourth impurity is arsenic or antimony.

(付記10) 付記8又は9記載の半導体装置の製造方法において、

前記第2の不純物をイオン注入する工程では、前記第2の不純物のイオン注入に先立ち、前記半導体基板の表面領域を非晶質化するための第5の不純物をイオン注入する

ことを特徴とする半導体装置の製造方法。

(Additional remark 10) In the manufacturing method of the semiconductor device of

In the step of ion-implanting the second impurity, a fifth impurity for amorphizing the surface region of the semiconductor substrate is ion-implanted prior to ion implantation of the second impurity. A method for manufacturing a semiconductor device.

(付記11) 付記10記載の半導体装置の製造方法において、

前記第5の不純物は、ゲルマニウムである

ことを特徴とする半導体装置の製造方法。

(Additional remark 11) In the manufacturing method of the semiconductor device of

The fifth impurity is germanium. A method of manufacturing a semiconductor device, wherein the fifth impurity is germanium.

(付記12) 付記8乃至11のいずれか1項に記載の半導体装置の製造方法において、

前記半導体層を形成する工程の後、前記半導体層を形成した前記半導体基板に素子分離絶縁膜を形成する工程を更に有する

ことを特徴とする半導体装置の製造方法。

(Appendix 12) In the method for manufacturing a semiconductor device according to any one of

After the step of forming the semiconductor layer, the method further includes the step of forming an element isolation insulating film on the semiconductor substrate on which the semiconductor layer is formed.

(付記13) 付記8乃至12のいずれか1項に記載の半導体装置の製造方法において、

前記第1のゲート絶縁膜を成長する工程では、前記第1の領域及び前記第3の領域を露出する第6のマスクを用いてエッチングを行い、前記第1の領域及び前記第3の領域の前記半導体層の表面を露出した後、前記第1のゲート絶縁膜を成長する

ことを特徴とする半導体装置の製造方法。

(Supplementary note 13) In the method for manufacturing a semiconductor device according to any one of

In the step of growing the first gate insulating film, etching is performed using a sixth mask exposing the first region and the third region, and the first region and the third region are etched. After the surface of the semiconductor layer is exposed, the first gate insulating film is grown. A method for manufacturing a semiconductor device, comprising:

(付記14) 半導体基板の第1の領域に形成され、ボロンを含む第1の不純物層と、

前記第1の不純物層上に形成された第1のエピタキシャル半導体層と、

前記第1のエピタキシャル半導体層上に形成された第1のゲート絶縁膜と、

前記第1のゲート絶縁膜上に形成された第1のゲート電極と、

前記第1のエピタキシャル半導体層及び前記第1の領域の前記半導体基板内に形成された第1のソース/ドレイン領域とを有する第1のトランジスタと、

前記半導体基板の第2の領域に形成され、ボロン及び炭素を含む第3の不純物層と、

前記第2の不純物層上に形成された第2のエピタキシャル半導体層と、

前記第2のエピタキシャル半導体層上に形成され、前記第1のゲート絶縁膜よりも薄い第2のゲート絶縁膜と、

前記第2のゲート絶縁膜上に形成された第2のゲート電極と、

前記第2のエピタキシャル半導体層及び前記第2の領域の前記半導体基板内に形成された第2のソース/ドレイン領域とを有する第2のトランジスタと、

前記半導体基板の第3の領域に形成され、リンを含む第3の不純物層と、

前記第3の不純物層上に形成された第3のエピタキシャル半導体層と、

前記第3のエピタキシャル半導体層上に形成され、前記第1のゲート絶縁膜と膜厚の等しい第3のゲート絶縁膜と、

前記第3のゲート絶縁膜上に形成された第3のゲート電極と、

前記第3のエピタキシャル半導体層及び前記第3の領域の前記半導体基板内に形成された第3のソース/ドレイン領域とを有する第3のトランジスタと、

前記半導体基板の第4の領域に形成され、砒素又はアンチモンを含む第3の不純物層と、

前記第4の不純物層上に形成された第4のエピタキシャル半導体層と、

前記第4のエピタキシャル半導体層上に形成され、前記第2のゲート絶縁膜と膜厚の等しい第4のゲート絶縁膜と、

前記第4のゲート絶縁膜上に形成された第4のゲート電極と、

前記第4のエピタキシャル半導体層及び前記第4の領域の前記半導体基板内に形成された第4のソース/ドレイン領域とを有する第4のトランジスタと

を有することを特徴とする半導体装置。

(Supplementary Note 14) A first impurity layer formed in a first region of a semiconductor substrate and containing boron;

A first epitaxial semiconductor layer formed on the first impurity layer;

A first gate insulating film formed on the first epitaxial semiconductor layer;

A first gate electrode formed on the first gate insulating film;

A first transistor having the first epitaxial semiconductor layer and a first source / drain region formed in the semiconductor substrate of the first region;

A third impurity layer formed in the second region of the semiconductor substrate and containing boron and carbon;

A second epitaxial semiconductor layer formed on the second impurity layer;

A second gate insulating film formed on the second epitaxial semiconductor layer and thinner than the first gate insulating film;

A second gate electrode formed on the second gate insulating film;

A second transistor having the second epitaxial semiconductor layer and a second source / drain region formed in the semiconductor substrate of the second region;

A third impurity layer formed in a third region of the semiconductor substrate and containing phosphorus;

A third epitaxial semiconductor layer formed on the third impurity layer;

A third gate insulating film formed on the third epitaxial semiconductor layer and having the same thickness as the first gate insulating film;

A third gate electrode formed on the third gate insulating film;

A third transistor having the third epitaxial semiconductor layer and a third source / drain region formed in the semiconductor substrate of the third region;

A third impurity layer formed in a fourth region of the semiconductor substrate and containing arsenic or antimony;

A fourth epitaxial semiconductor layer formed on the fourth impurity layer;

A fourth gate insulating film formed on the fourth epitaxial semiconductor layer and having the same thickness as the second gate insulating film;

A fourth gate electrode formed on the fourth gate insulating film;

And a fourth transistor having the fourth epitaxial semiconductor layer and a fourth source / drain region formed in the semiconductor substrate of the fourth region.

(付記15) 付記14記載の半導体装置において、

前記第2の不純物層は、ゲルマニウムを含む

ことを特徴とする半導体装置。

(Supplementary Note 15) In the semiconductor device according to

The semiconductor device, wherein the second impurity layer contains germanium.

10…シリコン基板

12…溝

14,52,60,64…シリコン酸化膜

16…低電圧NMOSトランジスタ形成領域

18,26,34,42,50,62…フォトレジスト膜

20,36…Pウェル

22…P型高濃度不純物層

24…低電圧PMOSトランジスタ形成領域

28,44…Nウェル

30…N型高濃度不純物層

32…高電圧NMOSトランジスタ形成領域

38,70,74…P型不純物層

40…高電圧PMOSトランジスタ形成領域

46,68,72…N型不純物層

48…シリコン層

54…シリコン窒化膜

56…素子分離溝

58…素子分離絶縁膜

60a,64a…ゲート絶縁膜

66a…ポリシリコン膜

66…ゲート電極

76…サイドウォールスペーサ

78…N型不純物層(ソース/ドレイン領域)

80…P型不純物層(ソース/ドレイン領域)

84…金属シリサイド膜

86…層間絶縁膜

88…コンタクトプラグ

90…配線

100…シリコン基板

102…ソース領域

104…ドレイン領域

106…チャネル領域

108…高濃度不純物層

110…シリコン層

112…ゲート絶縁膜

114…ゲート電極

DESCRIPTION OF

80... P-type impurity layer (source / drain region)

84 ...

Claims (7)

前記半導体基板の前記第1の領域に形成され、第1の導電型の第1の不純物を有する第1の不純物層と、

前記第1の不純物層上に形成された第1の半導体層と、

前記第1の半導体層上に形成された第1のゲート絶縁膜と、

前記第1のゲート絶縁膜上に形成された第1のゲート電極と、

前記第1の半導体層及び前記第1の領域の前記半導体基板に形成された第1のソース/ドレイン領域と、

前記半導体基板の前記第2の領域に形成され、前記第1の不純物よりも拡散定数の小さい前記第1導電型の第2の不純物を有する第2の不純物層と、

前記第2の不純物層上に形成された第2の半導体層と、

前記第2の半導体層上に形成され前記第1のゲート絶縁膜よりも薄い第2のゲート絶縁膜と、

前記第2のゲート絶縁膜上に形成された第2のゲート電極と、

前記第2の半導体層及び前記第2の領域の前記半導体基板に形成された第2のソース/ドレイン領域と、

を有し、

前記第1の半導体層の前記第1の不純物の不純物濃度は、前記第1の不純物層の前記第1の不純物の不純物濃度よりも低く、

前記第2の半導体層の前記第2の不純物の不純物濃度は、前記第2の不純物層の前記第2の不純物の不純物濃度よりも低い

ことを特徴とする半導体装置。 A semiconductor substrate having a first region and a second region;

A first impurity layer formed in the first region of the semiconductor substrate and having a first impurity of a first conductivity type;

A first semiconductor layer formed on the first impurity layer;

A first gate insulating film formed on the first semiconductor layer;

A first gate electrode formed on the first gate insulating film;

A first source / drain region formed in the semiconductor substrate of the first semiconductor layer and the first region;

Said formed on the second region of the semiconductor substrate, the second impurity layer having a second impurity of a small first conductivity type diffusion constant than the first impurity,

A second semiconductor layer formed on the second impurity layer;

A second gate insulating film formed on the second semiconductor layer and thinner than the first gate insulating film;

A second gate electrode formed on the second gate insulating film;

A second source / drain region formed in the semiconductor substrate of the second semiconductor layer and the second region;

I have a,

The impurity concentration of the first impurity in the first semiconductor layer is lower than the impurity concentration of the first impurity in the first impurity layer,

The semiconductor device according to claim 1, wherein an impurity concentration of the second impurity in the second semiconductor layer is lower than an impurity concentration of the second impurity in the second impurity layer .

前記半導体基板の前記第1の領域に形成され、第1の導電型の第1の不純物を有する第1の不純物層と、A first impurity layer formed in the first region of the semiconductor substrate and having a first impurity of a first conductivity type;

前記第1の不純物層上に形成された第1の半導体層と、A first semiconductor layer formed on the first impurity layer;

前記第1の半導体層上に形成された第1のゲート絶縁膜と、A first gate insulating film formed on the first semiconductor layer;

前記第1のゲート絶縁膜上に形成された第1のゲート電極と、A first gate electrode formed on the first gate insulating film;

前記第1の半導体層及び前記第1の領域の前記半導体基板に形成された第1のソース/ドレイン領域と、A first source / drain region formed in the semiconductor substrate of the first semiconductor layer and the first region;

前記半導体基板の前記第2の領域に形成され、前記第1の不純物及び前記第1の不純物の拡散を抑制する第3の不純物を有する第2の不純物層と、A second impurity layer formed in the second region of the semiconductor substrate and having a third impurity for suppressing diffusion of the first impurity and the first impurity;

前記第2の不純物層上に形成された第2の半導体層と、A second semiconductor layer formed on the second impurity layer;

前記第2の半導体層上に形成され前記第1のゲート絶縁膜よりも薄い第2のゲート絶縁膜と、A second gate insulating film formed on the second semiconductor layer and thinner than the first gate insulating film;

前記第2のゲート絶縁膜上に形成された第2のゲート電極と、A second gate electrode formed on the second gate insulating film;

前記第2の半導体層及び前記第2の領域の前記半導体基板に形成された第2のソース/ドレイン領域と、A second source / drain region formed in the semiconductor substrate of the second semiconductor layer and the second region;

を有することを特徴とする半導体装置。A semiconductor device comprising:

前記第1の不純物はリンであり、

前記第2の不純物は砒素又はアンチモンである

ことを特徴とする請求項1に記載の半導体装置。 The second impurity layer has the second impurity;

The first impurity is phosphorus;

The semiconductor device according to claim 1 , wherein the second impurity is arsenic or antimony.

前記第1の半導体層の前記第1の不純物の不純物濃度は、前記第1の不純物層の前記第1の不純物の不純物濃度よりも低く、

前記第2の半導体層の前記第1の不純物の不純物濃度は、前記第2の不純物層の前記第2の不純物の不純物濃度よりも低い

ことを特徴とする請求項2に記載の半導体装置。 The second impurity layer includes the first impurity and the third impurity;

The impurity concentration of the first impurity in the first semiconductor layer is lower than the impurity concentration of the first impurity in the first impurity layer,

The impurity concentration of said first impurity of the second semiconductor layer, the semiconductor device according to claim 2, wherein the lower than the impurity concentration of said second impurity of the second impurity layer.

前記第1の不純物はボロンであり、

前記第3の不純物は炭素である

ことを特徴とする請求項2又は4に記載の半導体装置。 The second impurity layer includes the first impurity and the third impurity;

The first impurity is boron;

The semiconductor device according to claim 2, wherein the third impurity is carbon.

ことを特徴とする請求項5に記載の半導体装置。 The semiconductor device according to claim 5, wherein the second impurity layer contains germanium.

前記半導体基板の第2の領域に形成され、前記第2の不純物層の下に位置する前記第2の導電型の第1のウェルと、

を有し、

前記第1の不純物層の不純物濃度は、前記第1のウェルの不純物濃度及び前記第1の半導体層の不純物濃度よりも高く、

前記第2の不純物層の不純物濃度は、前記第2のウェルの不純物濃度及び前記第2の半導体層の不純物濃度よりも高い

ことを特徴とする請求項1乃至6のいずれか一項に記載の半導体装置。 A first well of the first conductivity type formed in a first region of the semiconductor substrate and located under the first impurity layer;

A first well of the second conductivity type formed in a second region of the semiconductor substrate and located under the second impurity layer;

Have

The impurity concentration of the first impurity layer is higher than the impurity concentration of the first well and the impurity concentration of the first semiconductor layer,

7. The impurity concentration of the second impurity layer is higher than the impurity concentration of the second well and the impurity concentration of the second semiconductor layer. 7. Semiconductor device.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014200645A JP5854104B2 (en) | 2014-09-30 | 2014-09-30 | Semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014200645A JP5854104B2 (en) | 2014-09-30 | 2014-09-30 | Semiconductor device |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010220774A Division JP5630185B2 (en) | 2010-09-30 | 2010-09-30 | Semiconductor device and manufacturing method thereof |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2015026855A JP2015026855A (en) | 2015-02-05 |

| JP5854104B2 true JP5854104B2 (en) | 2016-02-09 |

Family

ID=52491223

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014200645A Expired - Fee Related JP5854104B2 (en) | 2014-09-30 | 2014-09-30 | Semiconductor device |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5854104B2 (en) |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4501183B2 (en) * | 1999-09-14 | 2010-07-14 | 株式会社デンソー | Manufacturing method of semiconductor device |

| JP4149980B2 (en) * | 2004-09-17 | 2008-09-17 | シャープ株式会社 | Manufacturing method of semiconductor manufacturing equipment |

| JP2007088054A (en) * | 2005-09-20 | 2007-04-05 | Nec Electronics Corp | Semiconductor device |

| JP2007281027A (en) * | 2006-04-03 | 2007-10-25 | Renesas Technology Corp | Semiconductor device and its manufacturing method |

| JP5173582B2 (en) * | 2008-05-19 | 2013-04-03 | 株式会社東芝 | Semiconductor device |

| JP2010157570A (en) * | 2008-12-26 | 2010-07-15 | Toshiba Corp | Method of manufacturing semiconductor device |

-

2014

- 2014-09-30 JP JP2014200645A patent/JP5854104B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2015026855A (en) | 2015-02-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5630185B2 (en) | Semiconductor device and manufacturing method thereof | |

| JP5605134B2 (en) | Semiconductor device and manufacturing method thereof | |

| JP5286701B2 (en) | Semiconductor device and manufacturing method of semiconductor device | |

| JP5772068B2 (en) | Semiconductor device and manufacturing method thereof | |

| JP4493536B2 (en) | Semiconductor device and manufacturing method thereof | |

| US10411112B2 (en) | Semiconductor device with silicon layer containing carbon | |

| US20100078735A1 (en) | Cmos device comprising nmos transistors and pmos transistors having increased strain-inducing sources and closely spaced metal silicide regions | |

| JP5870478B2 (en) | Manufacturing method of semiconductor device | |

| JP5578001B2 (en) | Manufacturing method of semiconductor device | |

| JP5821174B2 (en) | Manufacturing method of semiconductor device | |

| JP2009111046A (en) | Semiconductor device and method of manufacturing semiconductor device | |

| JP5854104B2 (en) | Semiconductor device | |

| TWI626678B (en) | High gain transistor for analog applications | |

| JP2004253707A (en) | Semiconductor device, and manufacturing method thereof | |

| JP2006108703A (en) | Semiconductor device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150728 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150731 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150928 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20151110 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20151123 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5854104 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |