JP5511203B2 - 撮像素子及び撮像装置 - Google Patents

撮像素子及び撮像装置 Download PDFInfo

- Publication number

- JP5511203B2 JP5511203B2 JP2009063238A JP2009063238A JP5511203B2 JP 5511203 B2 JP5511203 B2 JP 5511203B2 JP 2009063238 A JP2009063238 A JP 2009063238A JP 2009063238 A JP2009063238 A JP 2009063238A JP 5511203 B2 JP5511203 B2 JP 5511203B2

- Authority

- JP

- Japan

- Prior art keywords

- pixel

- area

- light

- region

- transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000003384 imaging method Methods 0.000 title claims description 51

- 238000006243 chemical reaction Methods 0.000 claims description 102

- 238000012937 correction Methods 0.000 claims description 51

- 238000012546 transfer Methods 0.000 claims description 19

- 230000003287 optical effect Effects 0.000 claims description 12

- 230000000694 effects Effects 0.000 description 40

- 239000003990 capacitor Substances 0.000 description 26

- 238000012545 processing Methods 0.000 description 25

- 230000009467 reduction Effects 0.000 description 24

- 238000010586 diagram Methods 0.000 description 19

- 238000000034 method Methods 0.000 description 19

- 230000003321 amplification Effects 0.000 description 18

- 238000003199 nucleic acid amplification method Methods 0.000 description 18

- 238000007781 pre-processing Methods 0.000 description 12

- 230000007547 defect Effects 0.000 description 9

- 230000006870 function Effects 0.000 description 8

- 238000012986 modification Methods 0.000 description 8

- 230000004048 modification Effects 0.000 description 8

- 238000003860 storage Methods 0.000 description 8

- 230000000875 corresponding effect Effects 0.000 description 7

- 230000000903 blocking effect Effects 0.000 description 4

- 238000004519 manufacturing process Methods 0.000 description 4

- 230000009471 action Effects 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- 230000035945 sensitivity Effects 0.000 description 2

- 238000012935 Averaging Methods 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 238000012790 confirmation Methods 0.000 description 1

- 230000002596 correlated effect Effects 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 230000007257 malfunction Effects 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 238000005070 sampling Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14603—Special geometry or disposition of pixel-elements, address-lines or gate-electrodes

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/63—Noise processing, e.g. detecting, correcting, reducing or removing noise applied to dark current

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1462—Coatings

- H01L27/14623—Optical shielding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14643—Photodiode arrays; MOS imagers

- H01L27/14645—Colour imagers

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N23/00—Cameras or camera modules comprising electronic image sensors; Control thereof

- H04N23/60—Control of cameras or camera modules

- H04N23/667—Camera operation mode switching, e.g. between still and video, sport and normal or high- and low-resolution modes

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/63—Noise processing, e.g. detecting, correcting, reducing or removing noise applied to dark current

- H04N25/633—Noise processing, e.g. detecting, correcting, reducing or removing noise applied to dark current by using optical black pixels

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/68—Noise processing, e.g. detecting, correcting, reducing or removing noise applied to defects

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Electromagnetism (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

- Solid State Image Pick-Up Elements (AREA)

Description

(1)操作部9の電源スイッチからの指示により電源がオンされる。

(2)信号処理部5で撮像素子2からの画像信号を表示用の画像データに変換して、画像表示部7に表示するとともに、測光データを検出し、同期制御部10に送出する。

(3)測光データに基づいて同期制御部10は光学系1を制御する。

(4)(2)および(3)を繰り返すとともに、操作部9からの指示を待つ。

(1)操作部9の撮影スイッチからの指示により静止画撮影の制御が開始される。

(2)信号処理部5で撮像素子2からの画像信号から測光データを検出し、同期制御部10に送出する。

(3)測光データに基づいて同期制御部10が光学系1を制御する。

(4)撮像素子2において、静止画記録用の露光と信号の出力を行う。

(5)信号処理部5で、撮像素子2からの画像信号を記録用の画像データに変換して、画像記録部8に送出し、着脱可能なメモリに記録するとともに、表示用の画像データに変換して、画像表示部7に表示する。

(6)<表示画像の制御>の(4)に戻る。

(1)操作部9の撮影スイッチからの指示により動画撮影の制御が開始される。

(2)信号処理部5で撮像素子2からの画像信号を記録用の画像データに変換して、画像記録部8に送出し、着脱可能なメモリに記録するとともに、表示用の画像データに変換して、画像表示部7に表示する。

(3)信号処理部5で撮像素子2からの画像信号から測光データを検出し、同期制御部10に送出する。

(4)測光データに応じて同期制御部10は光学系1を制御する。撮像素子2において、動画記録用の露光と信号の出力を行う。

(5)(2)〜(4)を繰り返すとともに、操作部9からの指示を待つ。

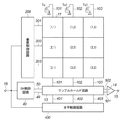

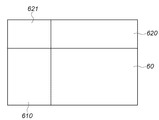

図1から図4に加えて、図5から図9を参照して、本発明の第1の実施形態について説明する。

(1)HOB領域の水平方向の遮光画素数が不足している場合

HOB領域である第1のOB領域61の駆動トランジスタTd1のゲート幅(チャネル幅)W2およびゲート長(チャネル長)L2と、有効画素領域60の駆動トランジスタTd1のゲート幅(チャネル幅)W1およびゲート長(チャネル長)L1の関係を、

第1のOB領域のW2>有効画素領域のW1、かつ、

第1のOB領域のL2>有効画素領域のL1

とすれば、HOB領域の駆動トランジスタTd1が発生するノイズを低減することができるので、誤クランプを防止することができる。

第1のOB領域のW2>有効画素領域のW1、かつ、

第1のOB領域のL2=有効画素領域のL1

でもノイズ低減効果はあるし、

第1のOB領域のW2=有効画素領域のW1、かつ、

第1のOB領域のL2>有効画素領域のL1

でもノイズ低減効果はある。

第2のOB領域のW2=有効画素領域のW1、かつ、

第2のOB領域のL2=有効画素領域のL1

でもよい。

(2)VOB領域の垂直方向の遮光画素数が不足している場合

VOB領域である第2のOB領域62の駆動トランジスタTd1のゲート幅(チャネル幅)W2およびゲート長(チャネル長)L2と、有効画素領域60の駆動トランジスタTd1のゲート幅(チャネル幅)W1およびゲート長(チャネル長)L1の関係を、

第2のOB領域のW2>有効画素領域のW1、かつ、

第2のOB領域のL2>有効画素領域のL1

とすれば、VOB領域の駆動トランジスタTd1が発生するノイズを低減することができるので、縦スジノイズの誤補正を防止することができる。

第2のOB領域のW2>有効画素領域のW1、かつ、

第2のOB領域のL2=有効画素領域のL1

でもノイズ低減効果はあるし、

第2のOB領域のW2=有効画素領域のW1、かつ、

第2のOB領域のL2>有効画素領域のL1

でもノイズ低減効果はある。

第1のOB領域のW2=有効画素領域のW1、かつ、

第1のOB領域のL2=有効画素領域のL1

でもよい。

(3)HOB領域の水平方向の遮光画素数、および、VOB領域の垂直方向の遮光画素数が不足している場合

HOB領域である第1のOB領域61の駆動トランジスタTd1のゲート幅(チャネル幅)W2およびゲート長(チャネル長)L2と、VOB領域である第2のOB領域62の駆動トランジスタTd1のゲート幅(チャネル幅)W2およびゲート長(チャネル長)L2と、有効画素領域60の駆動トランジスタTd1のゲート幅(チャネル幅)W1およびゲート長(チャネル長)L1の関係を、

第1のOB領域のW2>有効画素領域のW1、かつ、

第1のOB領域のL2>有効画素領域のL1、かつ

第2のOB領域のW2>有効画素領域のW1、かつ、

第2のOB領域のL2>有効画素領域のL1

とすることで、HOB領域の駆動トランジスタTd1が発生するノイズの低減による誤クランプの防止とともに、VOB領域の駆動トランジスタTd1が発生するノイズの低減による縦スジノイズの誤補正を防止することができる。

第2のOB領域のW2>第1のOB領域のW2>有効画素領域のW1、かつ、

第2のOB領域のL2>第1のOB領域のL2>有効画素領域のL1

とすることで、VOB領域の駆動トランジスタTd1が発生するノイズの方をより低減することができるので、ノイズに敏感な縦スジノイズの誤補正を防止することができる。

次に、図1から図9に加えて、図10を参照して、本発明の第2の実施形態である撮像装置について説明する。なお、本実施形態では、撮像装置の基本的な構成と動作及び撮像素子の基本的な構成と動作は、上記第1の実施形態と同様であるので、図および符号を流用して説明する。

(1)第1のOB領域61および第2のOB領域62それぞれに、第2の遮光画素920を配列させた場合

有効画素領域60のゲート幅(チャネル幅)W1とゲート長(チャネル長)L1に対する、第1のOB領域61および第2のOB領域62それぞれのゲート幅(チャネル幅)W3とゲート長(チャネル長)L3の関係を、第1の実施形態と同様にして実施することで、ノイズ低減効果があることは明らかである。

(2)第1のOB領域61に第1の遮光画素910を配列させ、第2のOB領域62に第2の遮光画素920を配列させた場合

有効画素領域60のゲート幅(チャネル幅)W1とゲート長(チャネル長)L1に対する、第1のOB領域61のゲート幅(チャネル幅)W2とゲート長(チャネル長)L2の関係を、第1の実施形態と同様にして実施することで、ノイズ低減効果があることは明らかである。

第2のOB領域のW3>第1のOB領域のW2>有効画素領域のW1、かつ、

第2のOB領域のL3>第1のOB領域のL2>有効画素領域のL1

とすることで、VOB領域の駆動トランジスタTd1が発生するノイズの方をより低減することができるので、ノイズに敏感な縦スジノイズの誤補正を防止することができる。

この時、第1のOB領域のW2とL2のどちらか一方、あるいは、第2のOB領域のW3とL3のどちらか一方であれば、有効画素領域のW1とL1と同じにしてもノイズ低減効果はある。

次に、図1から図10に加えて、図11から図13を参照して、本発明の第3の実施形態である撮像装置について説明する。なお、本実施形態では、撮像装置の基本的な構成と動作及び撮像素子の基本的な構成と動作は、上記第1および第2の実施形態と同様であるので、図および符号を流用して説明する。

(1)第1のOB領域61に第1の遮光画素910を配列させ、第2のOB領域62に第3の遮光画素930を配列させた場合

有効画素領域60のゲート幅(チャネル幅)W1とゲート長(チャネル長)L1に対する、第1のOB領域61のゲート幅(チャネル幅)W2とゲート長(チャネル長)L2の関係を、第1の実施形態と同様にして実施することで、ノイズ低減効果があることは明らかである。

第2のOB領域のW4>第1のOB領域のW2>有効画素領域のW1、かつ、

第2のOB領域のL4>第1のOB領域のL2>有効画素領域のL1

とすることで、VOB領域の駆動トランジスタTd1が発生するノイズの方をより低減することができるので、ノイズに敏感な縦スジノイズの誤補正をさらに防止することができる。

次に、図1からから図13に加えて、図14から図18を参照して、本発明の第4の実施形態である撮像装置について説明する。なお、本実施形態では、撮像装置の基本的な構成と動作及び撮像素子の基本的な構成と動作は、上記第1から第3の実施形態と同様であるので、図および符号を流用して説明する。

(1)HOB領域である第3のOB領域63および第4のOB領域64の両方に、第1の遮光画素910、第2の遮光画素920、第3の遮光画素930および第4の遮光画素940のいずれか一つが配列された場合

この時は、第3のOB領域および第4のOB領域のゲート幅(チャネル幅)Wおよびゲート長(チャネル長)Lの条件を

第4のOB領域のW>第3のOB領域のW>有効画素領域のW1、かつ、

第4のOB領域のL>第3のOB領域のL>有効画素領域のL1

とすることで、第4のOB領域64の駆動トランジスタTd1が発生するノイズの方をより低減することができるので、ノイズに敏感なHOBクランプの誤補正をさらに防止することができる。

(2)HOB領域である第3のOB領域63および第4のOB領域64に、第1の遮光画素910、第2の遮光画素920、第3の遮光画素930および第4の遮光画素940の内の2つを組み合わせて配列させる場合

第3のOB領域63が、第1の遮光画素910の時には、第4のOB領域64には、第2の遮光画素920、第3の遮光画素930および第4の遮光画素940のいずれか一つを配列させることで、第1の遮光画素910に比べて、ゲート幅(チャネル幅)Wおよびゲート長(チャネル長)Lを大きくする余裕が生じるので、本実施形態の(1)の条件を満たすことができる。

(3)VOB領域である第5のOB領域65および第6のOB領域66の両方に、第1の遮光画素910、第2の遮光画素920、第3の遮光画素930および第4の遮光画素940のいずれか一つが配列された場合

この時は、第5のOB領域および第6のOB領域のゲート幅(チャネル幅)Wおよびゲート長(チャネル長)Lの条件を

第5のOB領域のW>第6のOB領域のW>有効画素領域のW1、かつ、

第5のOB領域のL>第6のOB領域のL>有効画素領域のL1

とすることで、第5のOB領域65の駆動トランジスタTd1が発生するノイズの方をより低減することができるので、ノイズに敏感な縦スジノイズの誤補正をさらに防止することができる。

(4)VOB領域である第5のOB領域65および第6のOB領域66に、第1の遮光画素910、第2の遮光画素920、第3の遮光画素930および第4の遮光画素940の内の2つを組み合わせて配列させる場合

第6のOB領域66が、第1の遮光画素910の時には、第5のOB領域65には、第2の遮光画素920、第3の遮光画素930および第4の遮光画素940のいずれか一つを配列させることで、第1の遮光画素910に比べて、ゲート幅(チャネル幅)Wおよびゲート長(チャネル長)Lを大きくする余裕が生じるので、本実施形態の(1)の条件を満たすことができる。

次に、図1から図18に加えて、図19から図21を参照して、本発明の第5の実施形態である撮像装置について説明する。なお、本実施形態では、撮像装置の基本的な構成と動作及び撮像素子の基本的な構成と動作は、上記第1から第4の実施形態と同様であるので、図および符号を流用して説明する。

(1)第4の実施形態と同様に、HOB領域である第3のOB領域63および第4のOB領域64の両方に、第1の遮光画素910、第2の遮光画素920、第3の遮光画素930および第4の遮光画素940のいずれか一つが配列された場合

この時は、第3のOB領域および第4のOB領域のゲート幅(チャネル幅)Wおよびゲート長(チャネル長)Lの条件を

第4のOB領域のW>第3のOB領域のW>有効画素領域のW1、かつ、

第4のOB領域のL>第3のOB領域のL>有効画素領域のL1

とすることで、第4のOB領域64の駆動トランジスタTd1が発生するノイズの方をより低減することができるので、ノイズに敏感なHOBクランプの誤補正をさらに防止することができる。

(2)第4の実施形態と同様に、HOB領域である第3のOB領域63および第4のOB領域64に、第1の遮光画素910、第2の遮光画素920、第3の遮光画素930および第4の遮光画素940の内の2つを組み合わせて配列させる場合

第3のOB領域63が、第1の遮光画素910の時には、第4のOB領域64には、第2の遮光画素920、第3の遮光画素930および第4の遮光画素940のいずれか一つを配列させることで、第1の遮光画素910に比べて、ゲート幅(チャネル幅)Wおよびゲート長(チャネル長)Lを大きくする余裕が生じるので、本実施形態の(1)の条件を満たすことができる。

(3)VOB領域である第9のOB領域69および第10のOB領域70の両方に、第1の遮光画素910、第2の遮光画素920、第3の遮光画素930および第4の遮光画素940のいずれか一つが配列された場合

この時は、第9のOB領域および第10のOB領域のゲート幅(チャネル幅)Wおよびゲート長(チャネル長)Lの条件を

第10のOB領域のW>第9のOB領域のW>有効画素領域のW1、かつ、

第10のOB領域のL>第9のOB領域のL>有効画素領域のL1

とすることで、第10のOB領域70の駆動トランジスタTd1が発生するノイズの方をより低減することができるので、ノイズに敏感な縦スジノイズの誤補正をさらに防止することができる。

(4)VOB領域である第9のOB領域69および第10のOB領域70に、第1の遮光画素910、第2の遮光画素920、第3の遮光画素930および第4の遮光画素940の内の2つを組み合わせて配列させる場合

第9のOB領域69が、第1の遮光画素910の時には、第10のOB領域70には、第2の遮光画素920、第3の遮光画素930および第4の遮光画素940のいずれか一つを配列させることで、第1の遮光画素910に比べて、ゲート幅(チャネル幅)Wおよびゲート長(チャネル長)Lを大きくする余裕が生じるので、本実施形態の(1)の条件を満たすことができる。

次に、図1から図21に加えて、図22から図29を参照して、本発明の第6の実施形態である撮像装置について説明する。なお、本実施形態では、撮像装置の基本的な構成と動作及び撮像素子の基本的な構成と動作は、上記第1から第5の実施形態と同様であるので、図および符号を流用して説明する。

(1)HOB領域に遮光画素911あるいは931を配列し、VOB領域に遮光画素910あるいは930を配列した場合

感光画素110と比べて、駆動トランジスタTd1が発生するノイズを低減する効果があるのは、第1から第3の実施形態から明らかである。それに加えて、遮光画素911あるいは931の水平方向の大きさが、感光画素110より小さくなっているので、同じ面積であれば、遮光画素の数を増やすことができるので、その分、ノイズを低減する効果が向上することになる。また、遮光画素の数が同じで十分な場合は、HOB領域の面積を削減できるので、製造コストの削減になる。

(2)HOB領域に遮光画素910あるいは930を配列し、VOB領域に遮光画素912、932あるいは934を配列した場合

感光画素110と比べて、駆動トランジスタTd1が発生するノイズを低減する効果があるのは、第1から第3の実施形態から明らかである。それに加えて、遮光画素912、932あるいは934の垂直方向の大きさが、感光画素110より小さくなっているので、同じ面積であれば、遮光画素の数を増やすことができるので、その分、ノイズを低減する効果が向上することになる。また、遮光画素の数が同じで十分な場合は、VOB領域の面積を削減できるので、製造コストの削減になる。

(3)HOB領域に遮光画素911あるいは931を配列し、VOB領域に遮光画素912、932あるいは934を配列した場合

感光画素110と比べて、駆動トランジスタTd1が発生するノイズを低減する効果があるのは、第1から第3の実施形態から明らかである。それに加えて、遮光画素911あるいは931の水平方向の大きさが、感光画素110より小さくなっていること、および、遮光画素912、932あるいは934の垂直方向の大きさが、感光画素110より小さくなっていることにより、同じ面積であれば、遮光画素の数を増やすことができるので、その分、ノイズを低減する効果が向上することになる。また、遮光画素の数が同じで十分な場合は、HOB領域およびVOB領域の面積を削減できるので、製造コストの削減になる。

OB領域630には、第1のHOB領域として遮光画素911を配列させる。OB領域640には、第2のHOB領域として遮光画素911を配列させる。OB領域650には、第1のVOB領域として遮光画素912を配列させる。OB領域651には、第1のVOB領域として遮光画素913を配列させる。OB領域652には、第2のHOB領域として遮光画素913を配列させる。OB領域660には、第2のVOB領域として遮光画素912を配列させる。OB領域661および662には、第2のVOB領域として遮光画素913を配列させる。

第2のHOB領域のW>第1のHOB領域のW>有効画素領域のW1、かつ、

第2のHOB領域のL>第1のHOB領域のL>有効画素領域のL1

とすることで、第2のHOBの駆動トランジスタTd1が発生するノイズの方をより低減することができる。そのため、ノイズに敏感なHOBクランプの誤補正をさらに防止することができる。

第1のVOB領域のW>第2のVOB領域のW>有効画素領域のW1、かつ、

第1のVOB領域のL>第2のVOB領域のL>有効画素領域のL1

とすることで、第1のVOB領域の駆動トランジスタTd1が発生するノイズの方をより低減することができる。そのため、ノイズに敏感な縦スジノイズの誤補正をさらに防止することができる。

OB領域630には、第1のHOB領域として遮光画素911を配列させる。OB領域640には、第2のHOB領域として遮光画素931を配列させる。OB領域650には、第1のVOB領域として遮光画素912を配列させる。OB領域651には、第1のVOB領域として遮光画素913を配列させる。OB領域652には、第2のHOB領域として遮光画素933を配列させる。OB領域660には、第2のVOB領域として遮光画素932を配列させる。OB領域661には、第2のVOB領域として遮光画素933を配列させる。OB領域662には、第2のVOB領域として遮光画素933を配列させる。

OB領域630には、第1のHOB領域として遮光画素911を配列させる。OB領域640には、第2のHOB領域として遮光画素931を配列させる。OB領域650には、第1のVOB領域として遮光画素932を配列させる。OB領域651には、第1のVOB領域として遮光画素933を配列させる。OB領域652には、第2のHOB領域として遮光画素933を配列させる。OB領域660には、第2のVOB領域として、遮光画素934を配列させる。OB領域661には、第2のVOB領域として遮光画素935を配列させる。OB領域662には、第2のVOB領域として遮光画素935を配列させる。

OB領域630には、第1のHOB領域として遮光画素911を配列させる。OB領域640には、第2のHOB領域として遮光画素911を配列させる。OB領域690には、第4のVOB領域として遮光画素912を配列させる。OB領域691には、第4のVOB領域として遮光画素913を配列させる。OB領域692には、第4のVOB領域として遮光画素913を配列させる。OB領域700には、第5のVOB領域として遮光画素932を配列させる。OB領域701および702には、第5のVOB領域として遮光画素933を配列させる。

第5のVOB領域のW>第4のVOB領域のW>有効画素領域のW1、かつ、

第5のVOB領域のL>第4のVOB領域のL>有効画素領域のL1

とすることで、第5のVOB領域の駆動トランジスタTd1が発生するノイズの方をより低減することができる。そのため、ノイズに敏感な縦スジノイズの誤補正をさらに防止することができる。

OB領域630には、第1のHOB領域として遮光画素911を配列させる。OB領域640には、第2のHOB領域として遮光画素931を配列させる。OB領域690には、第4のVOB領域として遮光画素932を配列させる。OB領域691には、第4のVOB領域として遮光画素933を配列させる。OB領域692には、第4のVOB領域として遮光画素933を配列させる。OB領域700には、第5のVOB領域として遮光画素934を配列させる。OB領域701には、第5のVOB領域として遮光画素935を配列させる。OB領域702には、第2のHOB領域として遮光画素935を配列させる。

Claims (10)

- 光信号を電荷に変換する光電変換部と、前記電荷を電圧に変換する電荷電圧変換部と、該電荷電圧変換部の電圧を増幅する画素内アンプとを有する有効画素と、

光電変換部と、電荷電圧変換部と、画素内アンプとを有する第1の黒基準画素と、

光電変換部を持たず、電荷電圧変換部と、画素内アンプとを有する第2の黒基準画素とを備え、

前記有効画素の画素内アンプ、前記第1の黒基準画素の画素内アンプ、及び前記第2の黒基準画素の画素内アンプは、各々の電荷電圧変換部に接続されてソースフォロア回路を構成する少なくともひとつのトランジスタを有し、前記有効画素と前記第2の黒基準画素とで前記画素内アンプのトランジスタのゲート幅およびゲート長のうちの少なくともひとつが異なり、前記第1の黒基準画素と前記第2の黒基準画素とで前記画素内アンプのトランジスタのゲート幅及びゲート長のうちの少なくともひとつが異なることを特徴とする撮像素子。 - 前記第2の黒基準画素の画素内アンプのトランジスタのゲート幅が、前記有効画素の画素内アンプのトランジスタのゲート幅より広い、または、前記第2の黒基準画素の画素内アンプのトランジスタのゲート長が、前記有効画素の画素内アンプのトランジスタのゲート長より長いことを特徴とする請求項1に記載の撮像素子。

- 前記第2の黒基準画素の画素内アンプのトランジスタのゲート幅が、前記第1の黒基準画素の画素内アンプのトランジスタのゲート幅より広い、または、前記第2の黒基準画素の画素内アンプのトランジスタのゲート長が、前記第1の黒基準画素の画素内アンプのトランジスタのゲート長より長いことを特徴とする請求項1又は2に記載の撮像素子。

- 前記第1の黒基準画素の画素内アンプのトランジスタのゲート幅が、前記有効画素の画素内アンプのトランジスタのゲート幅より広い、または、前記第1の黒基準画素の画素内アンプのトランジスタのゲート長が、前記有効画素の画素内アンプのトランジスタのゲート長より長いことを特徴とする請求項1乃至3のいずれか1項に記載の撮像素子。

- 前記第1の黒基準画素及び前記第2の黒基準画素が、前記電荷電圧変換部をリセットするリセットトランジスタを有することを特徴とする請求項1乃至4のいずれか1項に記載の撮像素子。

- 前記第2の黒基準画素が、光電変換部から電荷電圧変換部への電荷の転送を制御する転送トランジスタを有することを特徴とする請求項1乃至5のいずれか1項に記載の撮像素子。

- 前記有効画素及び前記第1の黒基準画素が、前記光電変換部から前記電荷電圧変換部への電荷の転送を制御する転送トランジスタを有し、前記第2の黒基準画素が、前記転送トランジスタを有することを特徴とする請求項6に記載の撮像素子。

- 請求項1乃至7のいずれか1項に記載の撮像素子を備えることを特徴とする撮像装置。

- 前記黒基準画素から出力される黒基準信号を用いて、前記有効画素から出力される画像信号を補正する補正回路をさらに備えることを特徴とする請求項8に記載の撮像装置。

- 前記黒基準画素から出力される黒基準信号をクランプするクランプ回路をさらに備えることを特徴とする請求項8又は9に記載の撮像装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009063238A JP5511203B2 (ja) | 2009-03-16 | 2009-03-16 | 撮像素子及び撮像装置 |

| US12/717,474 US20100231761A1 (en) | 2009-03-16 | 2010-03-04 | Image sensor and image capturing apparatus |

| CN2010101322080A CN101841666B (zh) | 2009-03-16 | 2010-03-16 | 图像传感器和摄像设备 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009063238A JP5511203B2 (ja) | 2009-03-16 | 2009-03-16 | 撮像素子及び撮像装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010219234A JP2010219234A (ja) | 2010-09-30 |

| JP2010219234A5 JP2010219234A5 (ja) | 2012-04-26 |

| JP5511203B2 true JP5511203B2 (ja) | 2014-06-04 |

Family

ID=42730382

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009063238A Active JP5511203B2 (ja) | 2009-03-16 | 2009-03-16 | 撮像素子及び撮像装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US20100231761A1 (ja) |

| JP (1) | JP5511203B2 (ja) |

| CN (1) | CN101841666B (ja) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5632703B2 (ja) | 2010-10-21 | 2014-11-26 | キヤノン株式会社 | 画像処理装置、制御方法、及びプログラム |

| JP5631153B2 (ja) * | 2010-10-21 | 2014-11-26 | キヤノン株式会社 | 画像処理装置、制御方法、及びプログラム |

| JP6150457B2 (ja) * | 2011-05-12 | 2017-06-21 | キヤノン株式会社 | 固体撮像装置、固体撮像装置の駆動方法、固体撮像システム |

| FR2984606B1 (fr) * | 2011-12-14 | 2015-06-26 | Soc Fr Detecteurs Infrarouges Sofradir | Matrice de detection avec suivi du comportement des photodetecteurs |

| JP6214132B2 (ja) | 2012-02-29 | 2017-10-18 | キヤノン株式会社 | 光電変換装置、撮像システムおよび光電変換装置の製造方法 |

| US9918017B2 (en) | 2012-09-04 | 2018-03-13 | Duelight Llc | Image sensor apparatus and method for obtaining multiple exposures with zero interframe time |

| JP6174902B2 (ja) * | 2012-09-14 | 2017-08-02 | キヤノン株式会社 | 固体撮像装置及びカメラ |

| JP6271926B2 (ja) * | 2013-09-18 | 2018-01-31 | キヤノン株式会社 | 撮像装置、その制御方法、及びプログラム |

| JP6324184B2 (ja) * | 2014-04-18 | 2018-05-16 | キヤノン株式会社 | 光電変換装置、撮像システム、および光電変換装置の駆動方法 |

| KR102366416B1 (ko) | 2014-08-11 | 2022-02-23 | 삼성전자주식회사 | Cmos 이미지 센서 |

| JP6492991B2 (ja) * | 2015-06-08 | 2019-04-03 | 株式会社リコー | 固体撮像装置 |

| JP2017163010A (ja) * | 2016-03-10 | 2017-09-14 | ソニー株式会社 | 撮像装置、電子機器 |

| JP6815777B2 (ja) * | 2016-07-25 | 2021-01-20 | キヤノン株式会社 | 撮像装置及び撮像装置の制御方法 |

| JP6857061B2 (ja) * | 2017-03-22 | 2021-04-14 | キヤノン株式会社 | 撮像素子および撮像装置 |

| JP6746547B2 (ja) * | 2017-09-12 | 2020-08-26 | キヤノン株式会社 | 光電変換装置、撮像システムおよび光電変換装置の製造方法 |

| JP7159568B2 (ja) * | 2018-02-23 | 2022-10-25 | 株式会社リコー | 光電変換素子、画像読取装置、および画像形成装置 |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3142239B2 (ja) * | 1996-06-11 | 2001-03-07 | キヤノン株式会社 | 固体撮像装置 |

| GB2318473B (en) * | 1996-10-17 | 2000-11-29 | Sony Corp | Solid state imaging device,signal processing method and camera |

| JP3870137B2 (ja) * | 2001-08-02 | 2007-01-17 | キヤノン株式会社 | 固体撮像装置及び固体撮像システム |

| JP4132850B2 (ja) * | 2002-02-06 | 2008-08-13 | 富士通株式会社 | Cmosイメージセンサおよびその制御方法 |

| JP4251811B2 (ja) * | 2002-02-07 | 2009-04-08 | 富士通マイクロエレクトロニクス株式会社 | 相関二重サンプリング回路とこの相関二重サンプリング回路を備えたcmosイメージセンサ |

| JP4341297B2 (ja) * | 2003-05-23 | 2009-10-07 | 株式会社ニコン | 信号処理装置、および電子カメラ |

| JP4274533B2 (ja) * | 2003-07-16 | 2009-06-10 | キヤノン株式会社 | 固体撮像装置及びその駆動方法 |

| JP4517660B2 (ja) * | 2004-02-09 | 2010-08-04 | ソニー株式会社 | 固体撮像装置、画像入力装置および固体撮像素子の駆動方法 |

| JP4396425B2 (ja) * | 2004-07-07 | 2010-01-13 | ソニー株式会社 | 固体撮像装置及び信号処理方法 |

| JP2006147816A (ja) * | 2004-11-19 | 2006-06-08 | Sony Corp | 物理量分布検知装置および物理情報取得装置 |

| JP4425809B2 (ja) * | 2005-02-03 | 2010-03-03 | 富士通マイクロエレクトロニクス株式会社 | 撮像装置 |

| JP2006253316A (ja) * | 2005-03-09 | 2006-09-21 | Sony Corp | 固体撮像装置 |

| JP4687155B2 (ja) * | 2005-03-09 | 2011-05-25 | ソニー株式会社 | 固体撮像装置およびその駆動方法 |

| JP2007081453A (ja) * | 2005-09-09 | 2007-03-29 | Sony Corp | 撮像装置及び信号処理方法並びにプログラム |

| CN101313413B (zh) * | 2005-11-18 | 2011-08-31 | 株式会社半导体能源研究所 | 光电转换装置 |

| JP4827508B2 (ja) * | 2005-12-02 | 2011-11-30 | キヤノン株式会社 | 撮像システム |

| JP4479736B2 (ja) * | 2007-03-02 | 2010-06-09 | ソニー株式会社 | 撮像装置およびカメラ |

| JP4619375B2 (ja) * | 2007-02-21 | 2011-01-26 | ソニー株式会社 | 固体撮像装置および撮像装置 |

| JP4971834B2 (ja) * | 2007-03-01 | 2012-07-11 | キヤノン株式会社 | 撮像装置及び撮像システム |

| JP2008301030A (ja) * | 2007-05-30 | 2008-12-11 | Olympus Corp | 固体撮像装置 |

| JP5215681B2 (ja) * | 2008-01-28 | 2013-06-19 | キヤノン株式会社 | 撮像装置及び撮像システム |

| JP5322816B2 (ja) * | 2009-07-15 | 2013-10-23 | キヤノン株式会社 | 撮像装置およびその制御方法 |

-

2009

- 2009-03-16 JP JP2009063238A patent/JP5511203B2/ja active Active

-

2010

- 2010-03-04 US US12/717,474 patent/US20100231761A1/en not_active Abandoned

- 2010-03-16 CN CN2010101322080A patent/CN101841666B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN101841666B (zh) | 2013-08-28 |

| CN101841666A (zh) | 2010-09-22 |

| US20100231761A1 (en) | 2010-09-16 |

| JP2010219234A (ja) | 2010-09-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5511203B2 (ja) | 撮像素子及び撮像装置 | |

| JP5322816B2 (ja) | 撮像装置およびその制御方法 | |

| JP5891451B2 (ja) | 撮像装置 | |

| JP5614993B2 (ja) | 撮像装置及び固体撮像素子の駆動方法 | |

| JP5128889B2 (ja) | 固体撮像素子及びそれを用いた固体撮像システム | |

| JP5959834B2 (ja) | 撮像装置 | |

| JP4517660B2 (ja) | 固体撮像装置、画像入力装置および固体撮像素子の駆動方法 | |

| JP2013211770A (ja) | 撮像装置および信号処理方法 | |

| JP5222068B2 (ja) | 撮像装置 | |

| US20100053397A1 (en) | Imaging apparatus | |

| JP5003127B2 (ja) | 撮像装置とその制御方法およびカメラ | |

| JP2008306565A (ja) | 撮像装置及びその信号補正方法 | |

| JP3977342B2 (ja) | 固体撮像装置の設計方法及び撮像システム | |

| JP2012235193A (ja) | 撮像素子、撮像装置、およびその制御方法、並びに制御プログラム | |

| JP2013102288A (ja) | 撮像装置及び撮像装置の制御方法 | |

| JP2013192058A (ja) | 撮像装置 | |

| US20120038806A1 (en) | Image shooting device | |

| JP5334113B2 (ja) | 増幅部制御装置、及び、増幅部制御プログラム | |

| JP5737924B2 (ja) | 撮像装置 | |

| JP4208547B2 (ja) | 電子カメラ | |

| JP2015099989A (ja) | 撮像装置 | |

| JP4542063B2 (ja) | 固体撮像装置およびそれを用いた撮像システム | |

| JP2010166479A (ja) | 撮像装置及び撮像画像の補正方法 | |

| JP2008228118A (ja) | 固体電子撮像素子の補正装置およびその補正方法 | |

| CN118743242A (zh) | 摄像设备及其控制方法、程序和存储介质 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120309 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120309 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130807 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130812 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131007 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140224 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140325 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5511203 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |