JP5165954B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP5165954B2 JP5165954B2 JP2007195492A JP2007195492A JP5165954B2 JP 5165954 B2 JP5165954 B2 JP 5165954B2 JP 2007195492 A JP2007195492 A JP 2007195492A JP 2007195492 A JP2007195492 A JP 2007195492A JP 5165954 B2 JP5165954 B2 JP 5165954B2

- Authority

- JP

- Japan

- Prior art keywords

- gate electrode

- region

- trench

- drain region

- source region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 29

- 239000000758 substrate Substances 0.000 claims description 16

- 238000009792 diffusion process Methods 0.000 claims description 7

- 238000000034 method Methods 0.000 description 12

- 239000012535 impurity Substances 0.000 description 7

- 150000004767 nitrides Chemical class 0.000 description 6

- 238000004519 manufacturing process Methods 0.000 description 4

- 238000000059 patterning Methods 0.000 description 4

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 238000005520 cutting process Methods 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/08—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/0843—Source or drain regions of field-effect devices

- H01L29/0847—Source or drain regions of field-effect devices of field-effect transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/1025—Channel region of field-effect devices

- H01L29/1029—Channel region of field-effect devices of field-effect transistors

- H01L29/1033—Channel region of field-effect devices of field-effect transistors with insulated gate, e.g. characterised by the length, the width, the geometric contour or the doping structure

- H01L29/1037—Channel region of field-effect devices of field-effect transistors with insulated gate, e.g. characterised by the length, the width, the geometric contour or the doping structure and non-planar channel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42372—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the conducting layer, e.g. the length, the sectional shape or the lay-out

- H01L29/4238—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the conducting layer, e.g. the length, the sectional shape or the lay-out characterised by the surface lay-out

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66568—Lateral single gate silicon transistors

- H01L29/66575—Lateral single gate silicon transistors where the source and drain or source and drain extensions are self-aligned to the sides of the gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66568—Lateral single gate silicon transistors

- H01L29/66613—Lateral single gate silicon transistors with a gate recessing step, e.g. using local oxidation

- H01L29/66621—Lateral single gate silicon transistors with a gate recessing step, e.g. using local oxidation using etching to form a recess at the gate location

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7816—Lateral DMOS transistors, i.e. LDMOS transistors

- H01L29/7825—Lateral DMOS transistors, i.e. LDMOS transistors with trench gate electrode

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Electrodes Of Semiconductors (AREA)

Description

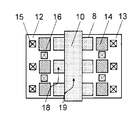

以下、図4を用いて、従来の半導体装置について説明する。図4(a)の斜視図に示したように、ウェル17にトレンチ部8を設け、ゲート絶縁膜9を介してトレンチ部の上面と内部にゲート電極10を形成したものである。ウェル17の表面部分において、ゲート電極10の一方の側にはソース領域12が設けられており、他方の側にはドレイン領域13が設けられている。図4(b)は、図4(a)の切断面A−Aに沿ったプレーナー部の断面図であり、図4(c)は、図4(a)の切断面B−Bに沿った断面図である。図4(c)に示したように、トレンチ部8内にゲート電極10が形成されているため、ゲート電極10がゲート絶縁膜9に接している曲線のB−B方向の総延長がゲート幅となる。

(1)第1導電型半導体基板に形成された、ゲート幅方向に側面と底面を有するトレンチ部と、ゲート絶縁膜を介して前記トレンチ部の内部およびプレーナー部上面に形成されたゲート電極と、前記ゲート電極の一方の側に形成された第2導電型のソース領域と、前記ゲート電極の他方の側に形成された第2導電型のドレイン領域を備えた半導体装置において、前記ソース領域と前記ドレイン領域のゲート電極近傍の一部の表面を他の表面よりも低い位置に配置すると共に前記ソースおよびドレイン領域の拡散深さも前記低い位置に配置された表面の下方部分においては前記他の表面の下方部分よりも深くなっていることを特徴とする半導体装置とした。

(2)第1導電型半導体基板と、前記第1導電型半導体基板の表面近傍に離間して配置された第2導電型のソース領域およびドレイン領域と、前記ソース領域およびドレイン領域の間に配置された第1のチャネル領域となる平坦なプレーナー部と、前記プレーナー部に沿って配置された、その側面および底面が第2のチャネル領域となる、一定の深さを有するトレンチ部と、前記プレーナー部および前記トレンチ部の表面に設けられたゲート絶縁膜と、前記ゲート絶縁膜の上に設けられたゲート電極とからなる半導体装置であって、前記ソース領域およびドレイン領域のうち前記トレンチ部を介して向き合う部分の表面は他の部分の表面よりも低い位置に配置するとともに、前記ソースおよびドレイン領域の拡散深さも前記トレンチ部を介して向き合う部分においては他の部分よりも深くなっていることを特徴とする半導体装置とした。

(3)第1導電型の半導体基板を用意する工程と、ソース領域およびドレイン領域となる領域のうちのそれぞれ一部を前記半導体基板の表面から除去し、凹部を形成する工程と、チャネルとなる領域に側面と底面を有するトレンチを形成してプレーナー部とトレンチ部を配置する工程と、前記トレンチ部の側面と底面および前記プレーナー部の表面にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜の上にゲート電極を形成する工程と、前記ゲート電極を挟んで前記凹部の周囲に第2導電型のソース領域とドレイン領域を形成する工程とからなる半導体装置の製造方法とした。

2 酸化膜

3 窒化膜

4、5、7、11 レジスト膜

6 チャネルカット領域低濃度拡散層

8 トレンチ部

9 ゲート絶縁膜

10 ゲート電極

12 ソース領域

13 ドレイン領域

14 LOCOS酸化膜の除去領域

15 トレンチ部コンタクト

16 プレーナー部コンタクト

17 ウェル

18 トレンチ部トランジスタ

19 プレーナー部トランジスタ

Claims (3)

- 第1導電型半導体基板に形成された、ゲート幅方向に側面と底面を有するトレンチ部と、

ゲート絶縁膜を介して前記トレンチ部の内部およびプレーナー部上面に形成されたゲート電極と、

前記ゲート電極の一方の側に形成された第2導電型のソース領域と、

前記ゲート電極の他方の側に形成された第2導電型のドレイン領域と、

を備え、

前記ソース領域と前記ドレイン領域のゲート電極近傍の一部の表面を他の表面よりも低い位置に配置すると共に前記ソースおよびドレイン領域の拡散深さも前記低い位置に配置された表面の下方部分においては前記他の表面の下方部分よりも深くなっていて、

前記プレーナー部のソース領域およびドレイン領域表面のコンタクトとゲート電極との距離は、前記トレンチ部のソース領域およびドレイン領域表面のコンタクトとゲート電極との距離よりも短いことを特徴とする半導体装置。 - 第1導電型半導体基板と、

前記第1導電型半導体基板の表面近傍に離間して配置された第2導電型のソース領域およびドレイン領域と、

前記ソース領域およびドレイン領域の間に配置された第1のチャネル領域となる平坦なプレーナー部と、

前記プレーナー部に沿って配置された、その側面および底面が第2のチャネル領域となる、一定の深さを有するトレンチ部と、

前記プレーナー部および前記トレンチ部の表面に設けられたゲート絶縁膜と、

前記ゲート絶縁膜の上に設けられたゲート電極と、

を備え、

前記ソース領域およびドレイン領域のうち前記トレンチ部を介して向き合う部分の表面は他の部分の表面よりも低い位置に配置するとともに、前記ソースおよびドレイン領域の拡散深さも前記トレンチ部を介して向き合う部分においては他の部分よりも深くなっていて、

前記プレーナー部のソース領域およびドレイン領域表面のコンタクトとゲート電極との距離は、前記トレンチ部のソース領域およびドレイン領域表面のコンタクトとゲート電極との距離よりも短いことを特徴とする半導体装置。 - 前記低い位置に配置された前記ソース領域およびドレイン領域の表面に配線のためのコンタクトを有することを特徴とする請求項1あるいは2に記載の半導体装置。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007195492A JP5165954B2 (ja) | 2007-07-27 | 2007-07-27 | 半導体装置 |

| TW097127794A TWI459472B (zh) | 2007-07-27 | 2008-07-22 | 半導體裝置及其製造方法 |

| US12/178,316 US8716142B2 (en) | 2007-07-27 | 2008-07-23 | Semiconductor device and method of manufacturing the same |

| CN200810144745XA CN101355105B (zh) | 2007-07-27 | 2008-07-25 | 半导体装置及其制造方法 |

| KR1020080072871A KR101520485B1 (ko) | 2007-07-27 | 2008-07-25 | 반도체 소자 및 그 제조 방법 |

| US14/208,911 US9276065B2 (en) | 2007-07-27 | 2014-03-13 | Semiconductor device and method of manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007195492A JP5165954B2 (ja) | 2007-07-27 | 2007-07-27 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009032905A JP2009032905A (ja) | 2009-02-12 |

| JP2009032905A5 JP2009032905A5 (ja) | 2010-05-27 |

| JP5165954B2 true JP5165954B2 (ja) | 2013-03-21 |

Family

ID=40294497

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007195492A Expired - Fee Related JP5165954B2 (ja) | 2007-07-27 | 2007-07-27 | 半導体装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US8716142B2 (ja) |

| JP (1) | JP5165954B2 (ja) |

| KR (1) | KR101520485B1 (ja) |

| CN (1) | CN101355105B (ja) |

| TW (1) | TWI459472B (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5738094B2 (ja) * | 2010-09-14 | 2015-06-17 | セイコーインスツル株式会社 | 半導体装置の製造方法 |

| JP5881100B2 (ja) * | 2011-12-22 | 2016-03-09 | エスアイアイ・セミコンダクタ株式会社 | 半導体装置の製造方法 |

| DE102015106688B4 (de) | 2015-04-29 | 2020-03-12 | Infineon Technologies Ag | Schalter mit einem feldeffekttransistor, insbesondere in einer integrierten schaltung zur verwendung in systemen mit lasten |

| JP2018089845A (ja) * | 2016-12-02 | 2018-06-14 | 大日本印刷株式会社 | 個体認証用半導体チップ、個体認証媒体及び個体認証方法 |

Family Cites Families (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08264764A (ja) * | 1995-03-22 | 1996-10-11 | Toshiba Corp | 半導体装置 |

| JPH1065150A (ja) * | 1996-08-14 | 1998-03-06 | Yokogawa Electric Corp | Dmos fet |

| JP3405681B2 (ja) * | 1997-07-31 | 2003-05-12 | 株式会社東芝 | 半導体装置 |

| JP3461277B2 (ja) * | 1998-01-23 | 2003-10-27 | 株式会社東芝 | 半導体装置及びその製造方法 |

| US6066533A (en) * | 1998-09-29 | 2000-05-23 | Advanced Micro Devices, Inc. | MOS transistor with dual metal gate structure |

| US6956263B1 (en) | 1999-12-28 | 2005-10-18 | Intel Corporation | Field effect transistor structure with self-aligned raised source/drain extensions |

| US6531347B1 (en) * | 2000-02-08 | 2003-03-11 | Advanced Micro Devices, Inc. | Method of making recessed source drains to reduce fringing capacitance |

| JP4780818B2 (ja) * | 2000-03-03 | 2011-09-28 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| JP3651802B2 (ja) * | 2002-09-12 | 2005-05-25 | 株式会社東芝 | 半導体装置の製造方法 |

| KR100521369B1 (ko) * | 2002-12-18 | 2005-10-12 | 삼성전자주식회사 | 고속도 및 저전력 소모 반도체 소자 및 그 제조 방법 |

| JP2005136150A (ja) * | 2003-10-30 | 2005-05-26 | Oki Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP4837902B2 (ja) * | 2004-06-24 | 2011-12-14 | 富士通セミコンダクター株式会社 | 半導体装置 |

| JP5110776B2 (ja) * | 2004-07-01 | 2012-12-26 | セイコーインスツル株式会社 | 半導体装置の製造方法 |

| JP2006019518A (ja) * | 2004-07-01 | 2006-01-19 | Seiko Instruments Inc | 横型トレンチmosfet |

| US7102201B2 (en) * | 2004-07-15 | 2006-09-05 | International Business Machines Corporation | Strained semiconductor device structures |

| JP4515305B2 (ja) * | 2005-03-29 | 2010-07-28 | 富士通セミコンダクター株式会社 | pチャネルMOSトランジスタおよびその製造方法、半導体集積回路装置の製造方法 |

| JP4976658B2 (ja) * | 2005-04-05 | 2012-07-18 | セイコーインスツル株式会社 | 半導体装置の製造方法 |

| US7569443B2 (en) * | 2005-06-21 | 2009-08-04 | Intel Corporation | Complementary metal oxide semiconductor integrated circuit using raised source drain and replacement metal gate |

| KR100714307B1 (ko) * | 2005-08-05 | 2007-05-02 | 삼성전자주식회사 | 활성영역 가장자리에 리세스영역을 갖는 반도체 장치 및 그형성방법 |

| JP4410195B2 (ja) * | 2006-01-06 | 2010-02-03 | 株式会社東芝 | 半導体装置及びその製造方法 |

| DE102006015077B4 (de) * | 2006-03-31 | 2010-12-23 | Advanced Micro Devices, Inc., Sunnyvale | Transistor mit abgesenkten Drain- und Source-Gebieten und Verfahren zur Herstellung desselben |

| US7410875B2 (en) * | 2006-04-06 | 2008-08-12 | United Microelectronics Corp. | Semiconductor structure and fabrication thereof |

| US7719062B2 (en) * | 2006-12-29 | 2010-05-18 | Intel Corporation | Tuned tensile stress low resistivity slot contact structure for n-type transistor performance enhancement |

| JP2008192985A (ja) * | 2007-02-07 | 2008-08-21 | Seiko Instruments Inc | 半導体装置、及び半導体装置の製造方法 |

| JP2009152394A (ja) * | 2007-12-20 | 2009-07-09 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP5442951B2 (ja) * | 2008-02-26 | 2014-03-19 | セイコーインスツル株式会社 | 半導体装置の製造方法 |

| JP4770885B2 (ja) * | 2008-06-30 | 2011-09-14 | ソニー株式会社 | 半導体装置 |

-

2007

- 2007-07-27 JP JP2007195492A patent/JP5165954B2/ja not_active Expired - Fee Related

-

2008

- 2008-07-22 TW TW097127794A patent/TWI459472B/zh not_active IP Right Cessation

- 2008-07-23 US US12/178,316 patent/US8716142B2/en not_active Expired - Fee Related

- 2008-07-25 KR KR1020080072871A patent/KR101520485B1/ko active IP Right Grant

- 2008-07-25 CN CN200810144745XA patent/CN101355105B/zh not_active Expired - Fee Related

-

2014

- 2014-03-13 US US14/208,911 patent/US9276065B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN101355105B (zh) | 2012-06-27 |

| TWI459472B (zh) | 2014-11-01 |

| KR101520485B1 (ko) | 2015-05-14 |

| KR20090012159A (ko) | 2009-02-02 |

| CN101355105A (zh) | 2009-01-28 |

| US8716142B2 (en) | 2014-05-06 |

| TW200924071A (en) | 2009-06-01 |

| JP2009032905A (ja) | 2009-02-12 |

| US20140191313A1 (en) | 2014-07-10 |

| US9276065B2 (en) | 2016-03-01 |

| US20090026537A1 (en) | 2009-01-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5307973B2 (ja) | 半導体装置 | |

| JP6365165B2 (ja) | 半導体装置の製造方法 | |

| JP5567711B2 (ja) | 半導体装置 | |

| JP5159365B2 (ja) | 半導体装置およびその製造方法 | |

| JP5184831B2 (ja) | フィン型トランジスタの形成方法 | |

| JP2009105374A (ja) | 半導体装置 | |

| JP6700648B2 (ja) | 半導体装置の製造方法 | |

| US7705399B2 (en) | Semiconductor device with field insulation film formed therein | |

| JP5616720B2 (ja) | 半導体装置およびその製造方法 | |

| JP5165954B2 (ja) | 半導体装置 | |

| JP2008159916A (ja) | 半導体装置 | |

| JP2009272453A (ja) | トランジスタ、半導体装置及びその製造方法 | |

| JP2009004493A (ja) | 半導体装置及びその製造方法 | |

| JP5452146B2 (ja) | 半導体装置 | |

| JP2005093456A (ja) | 横型短チャネルdmos及びその製造方法並びに半導体装置 | |

| JP2011210905A (ja) | 半導体装置の製造方法 | |

| JP2009088449A (ja) | 半導体装置およびその製造方法 | |

| JP2023024802A (ja) | スイッチング素子 | |

| JP2009164651A (ja) | 半導体装置 | |

| JP2007184360A (ja) | 半導体装置およびその製造方法 | |

| JP2005285950A (ja) | 半導体装置及びその製造方法 | |

| JP2010182820A (ja) | 半導体装置およびその製造方法 | |

| JP2006140337A (ja) | Mos半導体装置およびその製造方法 | |

| JP2011199195A (ja) | 半導体装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20091105 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20091113 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100414 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100414 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120911 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120913 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121108 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121204 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121220 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151228 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5165954 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |